## Technische Universität München TUM School of Computation, Information and Technology

# **Performance Prediction of Microcontrollers based upon integrated Technology Monitors**

## Tobias Kilian

Vollständiger Abdruck der von der TUM School of Computation, Information and Technology der Technischen Universität München zur Erlangung eines

## Doktors der Ingenieurwissenschaften (Dr.-Ing.)

genehmigten Dissertation.

Vorsitz:

Prof. Dr.-Ing. Georg Sigl

## Prüfende der Dissertation:

- 1. Prof. Dr.-Ing. Ulf Schlichtmann

- 2. Prof. Matteo Sonza Reorda, Ph.D.

Die Dissertation wurde am 10.04.2024 bei der Technischen Universität München eingereicht und durch die TUM School of Computation, Information and Technology am 24.01.2025 angenommen.

## Abstract

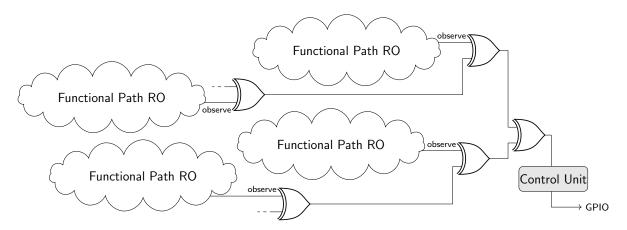

Microcontrollers (MCUs) are used for a broad range of applications. The testing of such MCUs is an essential topic for MCU manufacturers, particularly in safety-critical MCUs. Such MCUs are used in the automotive industry to operate braking, steering, and airbag systems. A critical test of the MCU testing process is the performance screening in which the maximum clock frequency of the MCU is determined under worst-case conditions. Indirect monitors, like Ring Oscillators (ROs), are used for this performance screening. This work presents the functional path ROs as an indirect monitoring structure used for performance screening. A holistic overview of the functional path ROs from the pre-silicon to the post-silicon is presented.

The implementation of such ROs and the associated advantages in terms of area consumption, leakage, and routing are presented. In addition, advanced implementation methodologies are proposed to save further routing resources. A considerable framework is suggested to select promising functional paths based on sensitivity analysis, and the entire implementation selection flow is validated. In the post-silicon phase, a statistically significant amount of MCUs that contain the functional path ROs are manufactured and tested. The measured functional path RO frequencies are correlated with the MCU performance using machine learning approaches and compared with traditional RO structures. The performance screening uses the implemented RO types, and the results yield is evaluated.

## Acknowledgments

This thesis results from my work as a doctoral candidate at Infineon Technologies AG, Neubiberg, Germany.

First of all, I thank Prof. Dr.-Ing. Ulf Schlichtmann for offering me the generous opportunity for this research work. He guided me through the work with his passion, constructive advice, and valuable discussions. I truthfully appreciate his genius academic support and feedback on publishing my papers.

I also would like to thank the co-examiner, Prof. Matteo Sonza Reorda, Ph.D., for his interest in my thesis and his time.

Also, I would like to thank my colleagues at Infineon Technologies AG. Thank you to my managers, Carsten Doerrhoefer and Dr. rer. nat. Jochen Roeder, for admitting me to the opportunity in your team. A special thanks to my supervisors, Dr.-Ing. Martin Huch and Dr.-Ing. Daniel Tille. Martin, thank you for the inspiring discussions and technical guidance through this work. Daniel, thank you for the academic guidance in the test community, the constructive discussions, and the distinguished feedback.

In addition, thank you to the teams that supported and helped me make this research work successful from the concept to the first silicon and beyond, especially the DFX, chip integration, test, and product engineering teams. With your support, this work is in the state as it is now. I want to thank Dr.-Ing. Juergen Alt for the review of this thesis and the discussions.

I would also like to thank the students who contributed to this work, especially Markus Hanel. Also, I am deeply thankful for the great collaboration and research conducted with the Politecnico di Torino (Turin, Italy), thanks to Nicolò Bellarmino, Prof. Riccardo Cantoro, and Prof. Giovanni Squillero.

Finally, I would like to thank my family and friends for their support and understanding of my lack of time and presence over the recent years. Mainly, I sincerely thank my wife, Kerstin, for her continuous support and motivation.

## Contents

| Al              | Abstract                                        |    |  |  |

|-----------------|-------------------------------------------------|----|--|--|

| Acknowledgments |                                                 |    |  |  |

| 1.              | Introduction                                    | 1  |  |  |

|                 | 1.1. Motivation and Problem Statement           | 1  |  |  |

|                 | 1.2. Related Work                               | 3  |  |  |

|                 | 1.3. Contribution of this Work                  | 6  |  |  |

|                 | 1.4. Outline of this Dissertation               | 7  |  |  |

| 2.              | Background                                      | 8  |  |  |

|                 | 2.1. Digital MCU Development Flow               | 8  |  |  |

|                 | 2.2. Timing and Performance of digital Circuits | 10 |  |  |

|                 | 2.3. PVT Variations                             | 12 |  |  |

|                 | 2.4. Testing of MCUs                            | 19 |  |  |

|                 | 2.5. Performance testing                        | 24 |  |  |

|                 | 2.6. Machine Learning in IC Testing             | 27 |  |  |

|                 | 2.7. Automotive Quality                         | 29 |  |  |

| I.              | PRE-Silicon                                     | 31 |  |  |

| 3.              | Functional Path Ring Oscillators                | 32 |  |  |

|                 | 3.1. Basic Concept                              | 32 |  |  |

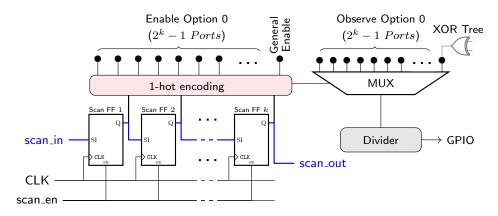

|                 | 3.2. Advanced Implementation Concepts           | 35 |  |  |

|                 | 3.3. Self Enabling                              | 38 |  |  |

|                 | 3.4. Control Infrastructure                     | 43 |  |  |

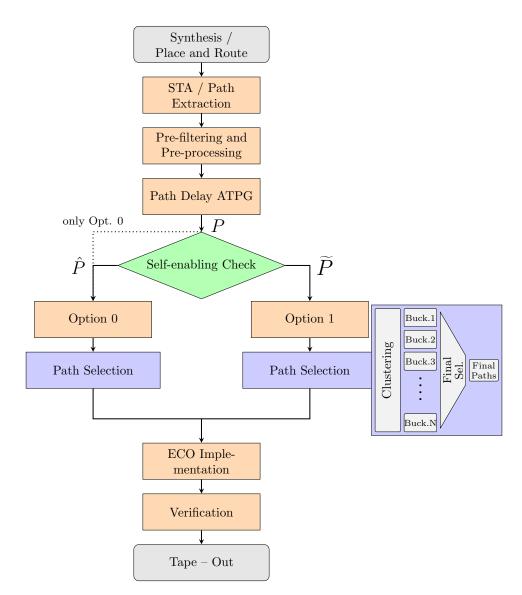

|                 | 3.5. Implementation Flow                        | 46 |  |  |

|                 | 3.6. Results                                    | 49 |  |  |

| <b>4</b> .      | Path Selection Methodology                      | 61 |  |  |

|                 | 4.1. Selection Flow                             | 61 |  |  |

|     | 4.2.            | Results                                             | 64              |  |

|-----|-----------------|-----------------------------------------------------|-----------------|--|

| 5   | PRF             | PRE-Silicon Verification and Validation             |                 |  |

| 0.  |                 | PRE-Silicon Verification of the Functional Path ROs | <b>68</b><br>68 |  |

|     |                 | SI Bring-up Preparation                             | 71              |  |

|     |                 | PRE- Silicon Validation and Improvement             | 75              |  |

|     | 5.5.            |                                                     | 15              |  |

| 6.  | PRE             | -SI Summary                                         | 83              |  |

| II. | PO              | ST-Silicon                                          | 85              |  |

| 7.  | Mea             | surement and Validation of the Functional Path RO   | 87              |  |

|     | 7.1.            | Functional Path RO Measurement Results              | 87              |  |

| 8.  |                 | ormance Screening Using Functional Path RO          | 91              |  |

|     |                 | Method and Data Set for the Performance Screening   | 91              |  |

|     |                 | Preprocessing of the Data Set                       | 97              |  |

|     |                 | Performance Screening Flow                          | 97              |  |

|     |                 | Deploy the Performance Screening                    | 104             |  |

|     | 8.5.            | Results of the Performance Screening                | 104             |  |

| 9.  | POS             | T-SI Summary                                        | 115             |  |

| 10. | 10. Conclusion  |                                                     |                 |  |

|     | 10.1.           | Summary of Key Contributions                        | 116             |  |

|     |                 | Obstacles in an Industrial Context                  |                 |  |

|     | 10.3.           | Future Work                                         | 118             |  |

| Lis | List of Figures |                                                     |                 |  |

| Lis | List of Tables  |                                                     |                 |  |

| Ac  | Acronyms        |                                                     |                 |  |

| Bi  | Bibliography    |                                                     |                 |  |

## 1. Introduction

Semiconductor electronics are an essential element in today's digitized world. This has become common knowledge in 2022 since the U.S. and European governments have released billions of dollars in subsidies to strengthen and foster the semiconductor ecosystem in the U.S. [1] and European [2] chips acts. Essential semiconductor devices are integrated circuits (ICs). ICs are small semiconductor devices that are fundamental components in nearly everything in life and the economy.

A subgroup of ICs are microcontrollers (MCUs). An MCU is an IC that combines different systems on one chip; also, the term system-on-chip (SoC) is used. An MCU combines the processor, memory, input/output (I/O) peripherals, and communication interfaces on a single chip. The field of applications is enormous. It ranges from tiny household and commercial applications to high-reliable technologies, like space applications and automotive technology. Depending on the application, MCUs must meet different quality, power consumption, performance, and cost requirements. MCUs used in the automotive industry have special needs regarding quality [3] and reliability [4]. This work focuses on MCUs for automotive applications; however, the method can be used for every MCU.

## 1.1. Motivation and Problem Statement

More than 100 of these MCUs are incorporated in modern vehicles [4] and are used in safety-critical steering and braking systems as well as in advanced driver assistance systems (ADAS). The MCUs must work under extreme temperature conditions from -40 °C up to 150 °C. They are exposed to vibrations and harsh conditions. Moreover, the automotive MCU must ensure to work for up to 15 years [5]. A not correctly working MCU can cause tremendous damage and risk human lives. Therefore, much effort is invested in testing and validating automotive MCUs to satisfy quality requirements. The MCU test is essential for finding defects provoked by the manufacturing process, ensuring proper functionality, and meeting the required specifications.

The major challenge in testing automotive MCUs is to achieve *zero-defect quality* [6]. This means only MCUs, which are error-free, will be delivered to the customer. However, zero-defect quality is not easy to achieve for large and complex automotive MCUs. Therefore,

automotive MCU manufacturers invest much effort in testing all devices to deliver zero-defect quality.

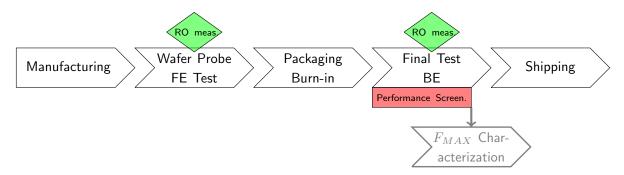

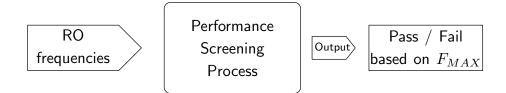

There are many test stages along the manufacturing process, and modern MCUs have an extensive DFT infrastructure on board to support and enable the various tests. An essential test of the MCUs test procedure is performance screening. The performance of an MCU is the maximum achievable clock frequency at which the device can execute all use cases under worst-case conditions, denoted as  $F_{MAX}$ . Performance screening describes the test in which  $F_{MAX}$  is determined. Therefore, each device shipped to the customer must pass the performance screening by achieving the performance specified in the data sheet. The timing of the design in the MCU determines the  $F_{MAX}$ .

Since the technology node in MCU is shrinking, the timing variability becomes more sensitive to manufacturing, environment, and aging. This timing variability is called PVTA (process, voltage, temperature, aging) variation. The aging component is neglected in this work since it is an elaborate topic that is out of scope. Thus, Process-Voltage-Temperature (PVT) variability is addressed in this work. The timing of the MCU and  $F_{MAX}$  should be satisfied regardless of the PVT variability. This makes the performance screening even more challenging since the  $F_{MAX}$  should be guaranteed under worst-case conditions.

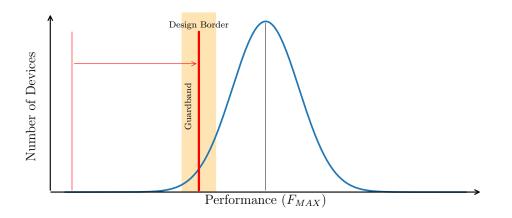

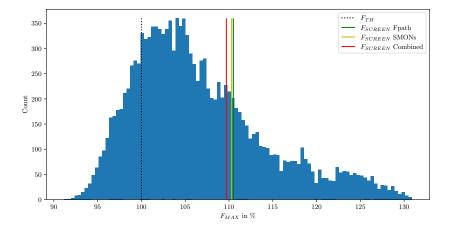

Figure 1.1 provides a simplified illustration of the performance in MCU manufacturing. The performance of manufactured MCUs can be approximated as Gaussian distribution colored in blue [7]. Thus, many of the devices are well centered around the mean. However, there are also devices with lower  $F_{MAX}$ , the so-called slow tail on the left side of the distribution, and devices with higher  $F_{MAX}$  on the right side, called the fast tail of the distribution. The reason for this distribution lies in the semiconductor manufacturing process itself. The aim is for many components within this Gaussian distribution to fulfill the requirement  $F_{MAX}$ , which in turn depends on the design border. This design border is the value that is required as a design specification. The exact position of the design border depends on many technical as well as financial factors.

The brute force approach would shift the design border (red) far to the left sides of the distribution - which means all MCUs are indeed fast. Unfortunately, that does not work since this would result in an MCU design that is not competitive due to area, design effort, and economic reasons. The design border in realistic scenarios is much closer to the distribution and can even cut into this distribution. The performance screening targets testing the performance near the design border.

However, the performance cannot be measured directly, and the entire multidimensional PVT space must be considered. In recent years, various methods for determining performance have been proposed. The methods range from structural tests to system-level-tests and indirect monitoring structures [8, 9, 10, 11, 12, 13, 14, 15, 16]. Due to the fact that a hundred

Figure 1.1.: Process window after tightening the limits.

percent accurate determination of the performance is not possible, it is an attempt to predict the performance as accurately as possible. What remains is an inaccuracy that must be priced into the performance screening. In order to safeguard the inaccuracy of the screening, a so-called Guardband (colored orange in Figure 1.1) is used. This margin is added to the performance screening to meet the high-quality requirements - better performance screening methods result in higher screening accuracy, and thus less Guardband is required.

In order to determine the performance for the performance screening, indirect monitors are often used. Such indirect monitor structures are ring oscillators (ROs). The oscillation frequency of such ROs is measured, and this measured frequency correlates with  $F_{MAX}$ . However, the RO structures usually have a significant area overhead, but in turn, have a high resolution and are easy and fast to measure [17]. Furthermore, the quality and accuracy of performance screening depend significantly on the design of such RO structures [18, 19, 20].

The *functional path ROs* [21] are a subtype of ROs that promise advantages in terms of area and accuracy since they use functional paths which are already on the design. However, the functional path ROs need further research on how to implement and control, which paths to select, and how to establish the functional path RO for performance screening on silicon in a large automotive MCU. This work is an important contribution to these endeavors.

## 1.2. Related Work

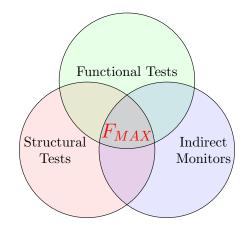

Determining the performance of modern SoCs is challenging due to their complexity - especially for large MCUs. Three significant approaches in  $F_{MAX}$  testing are widely used and visualized in Figure 1.2.

One way to test performance is to use structural at-speed test patterns, such as *Transition Delay Fault* [22] patterns or *Path Delay Fault* [23] patterns [8, 9]. However, such at-speed

Figure 1.2.: Test approaches for  $F_{MAX}$  testing.

patterns can only provide a pass or fail categorization of the chip. Performance testing requires an accurate determination of the numerical performance value.

A straightforward approach is determining the MCU's performance with a *Functional Test* on the automatic test equipment (ATE) [10]. Small critical code blocks as part of the ATE test program are executed, and the clock frequency is increased until the point of failure [11]. However, ATE systems usually have limited power integrity, making the exact performance prediction inaccurate [24]. As a result, *System-Level Test* (SLT) is gaining increasing attention [12, 13]. In contrast to the functional test on the ATE, the SLT is performed on an application-like board with software close to the device's final application. However, several thousand applications are conceivable. Therefore, all possible applications must be tested under different voltage and temperature conditions to determine the maximum performance of every device [24]- which is not an option due to the limited test budget. Thus, SLT is expensive in terms of test time and handling [25].

The third approach is to use indirect monitoring structures. There are many types of such indirect methods. However, they all used indirect metrics that allowed them to conclude performance [26, 27, 28, 29, 30, 31, 21].

*Razor FF* [26, 27] and *In-situ* slack monitors [28] are some types of indirect monitoring structures. Razor FFs are additional FFs that observe specific paths on the design and check if the timing is met. Also, in-situ slack monitors observe the remaining slack of a specific path and give an alarm if the slack margin disappears. Both approaches can be used for performance determination in small circuits where some known paths are timing critical.

However, for large MCUs in state-of-the-art CMOS technology, the timing of a design gets more complex [32], and it is challenging to define discrete time-critical paths. It may be that paths, which seem non-critical in the pre-silicon phase may become critical in the post-silicon phase due to process variations in manufacturing [33]. The degradation mechanism also

affects the performance [34]. Thus, it is essential to monitor numerous paths in the design. Consequently, many Razor FFs and in-situ monitors will add a considerable area – which should be prevented due to cost reasons.

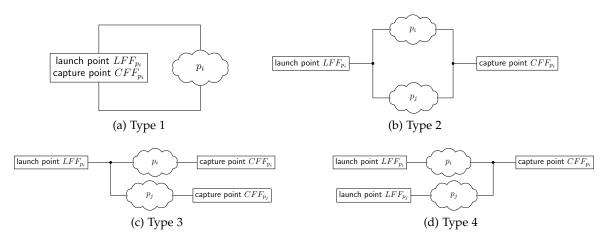

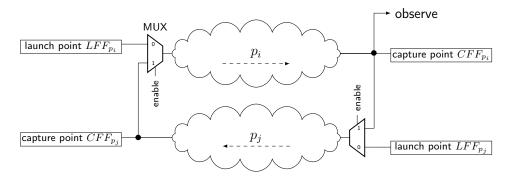

Another indirect monitoring structure for performance screening is the use of ring oscillators (ROs). Such ROs are divided into two basic variants - generic ROs and design-dependent ROs [29]. Generic ROs are made from precisely one kind of standard library cell, e.g., inverters or AND gates. Design-dependent ROs are synthesized according to the design of the chip. Several paths of the chip are being selected, synthesized, and designed as ROs. However, such RO structures occupy much area because all structures need to be placed on the chip; in contrast, *functional path ROs* can solve the disadvantage of the area requirement.

Wu et al. [30] proposed the basic concept of functional path ROs. A functional path RO uses existing paths in the design and creates an RO structure from such paths. In the basic concept, path ROs are used to test small circuits. Further development of functional path RO was proposed by Wang et al. [31, 21] - called *Path-RO*. Here, the main focus is on measuring specific path delays as precisely as possible, which is only accompanied by high area and effort.

However, efficient implementation is only one aspect of performance screening with functional path ROs. There are millions of functional paths on a large MCU, and the path selection directly affects the quality of performance monitoring. Many previous research was conducted to characterize timing effects [35, 36, 37, 33] in functional path ROs. Rangan et al. investigated the design of ROs in terms of PVT sensitivity [38]. Therefore, the accuracy of the performance screening strongly depends on the sensitivity of the performance monitors used. [39].

In summary, there is a lack of efficient and automatic implementation of functional path ROs. The implemented ROs should fit into industrial design flows and use the industrial test and control infrastructures like the DFT environment. Another open point is selecting the functional paths to catch the right paths for performance screening. There is also a lack of measurement data from silicon. Furthermore, last but not least, how good are the functional path ROs for performance screening?

#### 1.2.1. SMON Benchmark Module in this Work

In order to have a baseline against which the functional path ROs can be compared, an SMON (Speed MONitor) module is used in this work. This SMON module, utilized as a benchmark, contains different types of ROs as performance monitors. The structure of the SMON module originates from [24], but the SMONs have been re-implemented in the newer 28 nm CMOS technology used for this research to serve as a valid baseline.

Inside the SMON module is a mix of generic and design-dependent ROs. The module is conceptualized as a compact block positioned on the MCU. The various generic ROs consist of inverter gates, NAND gates, and NOR gates from different cell libraries. The design-dependent ROs on the SMON module emulate functional paths from the design. The SMON module is designed to contain up to 255 different ROs. However, to serve as a benchmark, the SMONs contain 27 ROs that have been used in previous work ([24]).

## **1.3.** Contribution of this Work

The main contribution of this work is in the area of functional path ROs for performance screening. In particular, the contribution can be settled along the development process of an MCU from the per-silicon design part through the manufacturing until the post-silicon evaluation of an MCU in state-of-the-art technology.

Parts of the approaches proposed in this work have been peer-reviewed and published in official scientific conferences proceedings [40, 41, 42, 43] and workshop proceedings [44, 45, 46, 47, 48]. In addition, parts of this work have been published in the **IEEE Transactions on Very Large Scale Integration (VLSI) Systems** in June 2023 [49]. In order to emphasize the novelty of this work, **two patents** are published and granted in two different countries. Another outstanding achievement of this work is that [41] was honored with the **Best Paper Award** at the IEEE European Test Symposium (ETS) 2022.

Besides this, there are considerable co-contributions in peer-reviewed conferences [24, 50] and a publication in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD) [51].

The following listing associates the core contributions with this work's publications and related sections in this thesis.

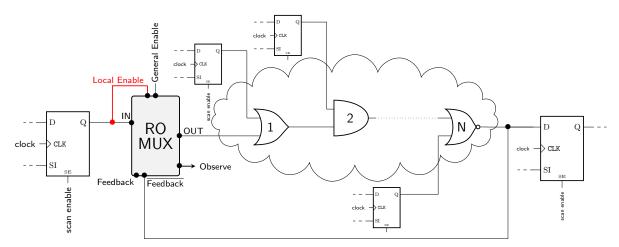

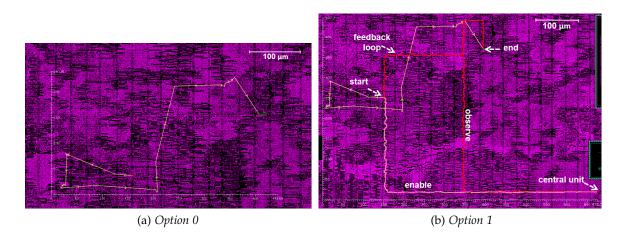

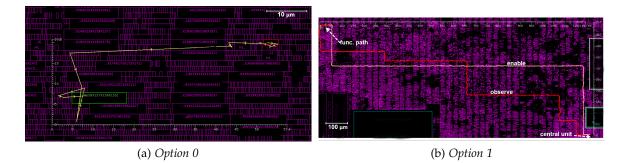

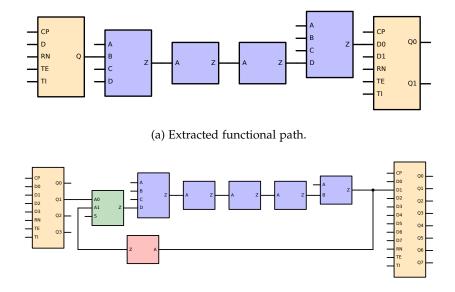

- Automatic and scalable implementation of functional path ROs in large automotive MCU designs is presented in Section 3.1 of which parts are published in [40, 44, 45].

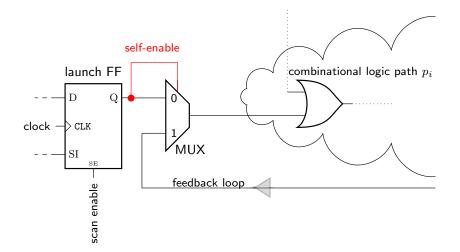

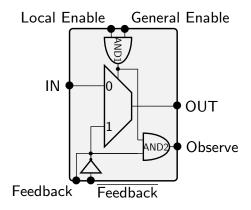

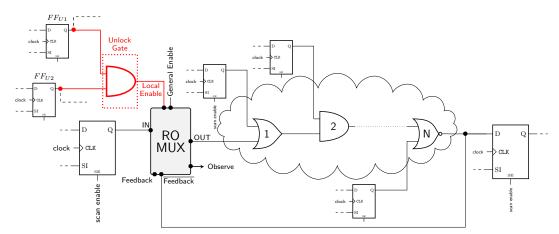

- The development of advanced implementation methods is presented in Section 3.2, which emphasizes the so-called self-enabling approach and natural loops. The self-enabling approach was published in [41], and a DE and US patent [52] was granted. The natural loop approach was published in [47] and patented in DE (granted) and US (published) [53].

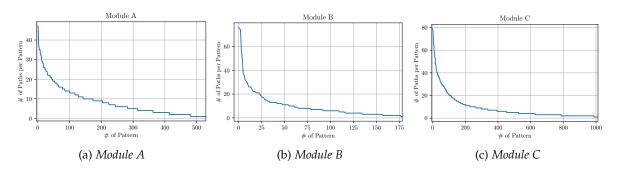

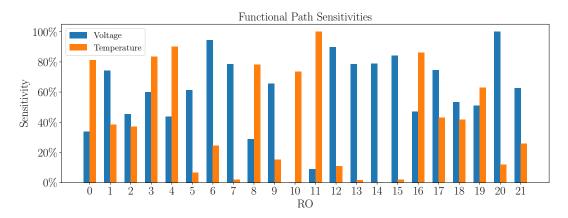

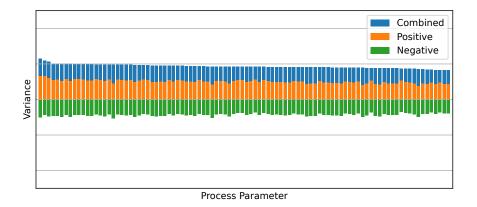

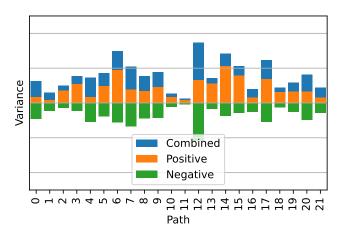

- A path selection methodology was developed and validated using analog simulation and sensitivity analysis of the circuitry, this is presented in Section 4, and parts were published in [42, 46].

• Functional path RO results are presented, derived from a large automotive MCU, and their benefits for performance screening are presented in Part II. Sections of this part were presented in [42, 43, 48] and [49].

## 1.4. Outline of this Dissertation

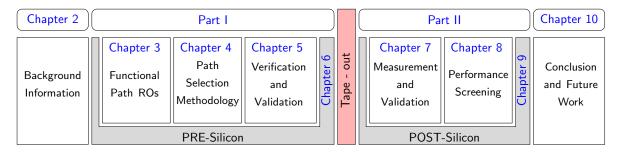

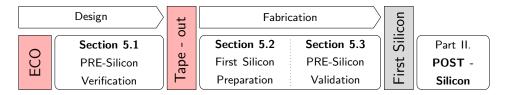

Figure 1.3.: Outline of the thesis.

The structure of this thesis is presented in Figure 1.3. Chapter 2 provides the background knowledge for this work. The industrial development flow of an MCU is recapped, and the timing and performance challenges are explained. Also, the fundamental testing knowledge is provided, and the most substantial Machine Learning (ML) approaches are explained.

The subsequent work is then divided into two parts: Part I: pre-silicon and Part II: postsilicon.

Part I presents the concept and implementation of the functional path ROs in Chapter 3. Chapter 4 presents the path selection methodology to find the best suitable functional paths for RO implementation. The pre-silicon verification and validation is explained in Chapter 5, followed by a comprehensive summary of Part I.

Part II presents the first measurement results and their validation in Chapter 7. Chapter 8 presents the use and results of functional path ROs for performance screening. A summary in Chapter 9 concludes Part II. The last Chapter – Chapter 10 – in this work concludes the thesis, including obstacles in an industrial context and further work.

## 2. Background

The background section provides an overview of the microcontroller (MCU) development and timing of digital circuits. Afterward, the testing of modern MCUs is reviewed, especially the performance screening. Machine learning (ML) use cases in SoC testing and the quality standards for automotive MCUs are also elaborated. The terms SoC and MCU are used as synonyms in this work and are not further distinguished.

## 2.1. Digital MCU Development Flow

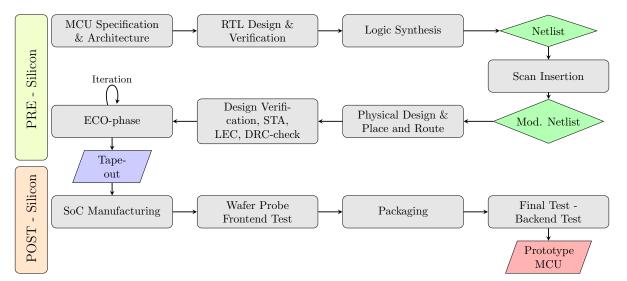

In order to get an overview of the phases in which the proposed methods proceed, the industrial MCU design and test flow are presented. All methods in this work are suitable for industrial development flows. However, only a condensed overview of the MCU development flow is presented, as the detailed process is much more extensive [54]. The digital MCU development flow to develop a prototype MCU is shown in Figure 2.1.

Figure 2.1.: Development flow of a prototype MCU divided into Pre-Silicon and Post-Silicon.

In general, the development process can be divided into the Pre-Silicon (Pre-Si) and Post-Silicon (Post-Si) phases. The arrival of the first MCU prototype indicates the transition from **Pre-Si** to Post-Si. The functional specification has to be defined in the initial phase, and the architectural chip elements, including all modules and submodules, are defined. The described functionality is translated into a hardware description language and a synthesizable register-transfer level (RTL) representation. With a proper RTL representation, the logic synthesis is started, and the abstracted RTL representation of the functionality is then translated into a logical gate-level design called *netlist*. The netlist of a design is a composition of logic gates and flip-flops (FFs) implementing a particular functionality previously described in RTL. The RTL representation and the netlist are constantly verified to check the desired functionality [55].

Once the netlist is verified, it is further modified with the Design for Testability (DfT) process (e.g., *scan insertion*), which results in a modified netlist. The DfT process enables proper testing of the manufactured chips; more details are explained in Section 2.4.1.

The modified netlist is then passed to the physical design. Floorplanning of the design, including power planning, clock tree synthesis, and place-and-route, is performed. The physical design is extensively verified and, if necessary, optimized.

An essential step in the design verification is ensuring the design's timing closure with the static timing analysis (STA). All setup and hold times must be within the specifications under all allowed conditions. Plenty of other verification steps are also done, for example, the Logic Equivalence Check (LEC), Design Rule Check (DRC), IR droop is verified and cross-talk, and many more checks [55].

If there are issues with the functionality and timing of the design, an engineering change order (ECO) is usually used to solve the issue. An ECO is a process for fixing any design problems in a late design stage and is typically one of the last stages in the Pre-Si phase. The ECO can cause a minor modification in the netlist and the resulting change in the physical design. This ECO process is executed, and an incremental compilation run is performed. This means that only the parts of the design that are affected by the ECO process are changed. The rest of the design remains unchanged. Once the whole design is successfully verified, and all targets are met, the manufacturing of the MCU design is started, which is known as the *tape-out*. This is also the transition from Pre-Si to Post-Si phase.

The manufacturing process of MCUs in advanced complementary metal oxide semiconductor (CMOS) technology is a complex and elaborating process with plenty of chemical and physical steps on a silicon wafer. Multiple chips, also denoted as *dies*, are contained on a single wafer. After the wafer manufacturing, the MCUs are tested for the first time, called the front-end (FE) wafer test. The wafer is mounted on a chuck during the front-end (FE) wafer test. Afterward, the dies are separated by sawing the wafer into bare dies. The bare die, where the FE test is passed, is assembled in a package. The next step is the burn-in to detect early fails and ensure high reliability, followed by the final back-end (BE) test. The finally produced MCU is extensively characterized, and it is validated, if the functionality is correct and all requirements are fulfilled. This is the terminus of the prototype development. If issues are identified, a redesign might be performed, or minor improvements are required. Finally, the MCU is transferred to mass production [56].

Note that the development process explained is a high-level overview; the entire MCU flow has much more detail that is neglected in this explanation.

## 2.2. Timing and Performance of digital Circuits

Modern MCUs consist of numerous architectural components. A large part consists of digital circuit elements, which is also the focus of this work. Besides that, there are also memories, analog circuit parts, and various interfaces on modern MCUs. Digital circuits are built on CMOS combinational and sequential circuit elements. All such circuit elements are part of a cell library containing CMOS circuit elements (FFs, Inverter, NOR - gates, AND - gates, ...) of different sizes, speeds, power, and other factors and denoted as *standard cells*. All CMOS elements are built using NMOS and PMOS transistors. The logic synthesis translates the RTL description into a netlist using such cell libraries.

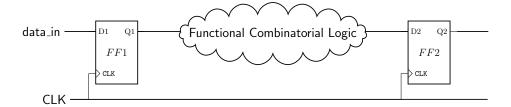

The synchronous digital design uses edge-triggered FFs as sequential circuit elements. The FFs are triggered by a synchronous clock signal *CLK* distributed via the clock tree. Thus, there can be distinguished between clock paths and data paths. The clock tree distributes the clock signal over the chip, and data paths care for the chip's functionality. The data paths with combinational logic elements are arranged between the clock-triggered FFs. Thus, the data signal must propagate from the designated launch FF (*FF*1) through the combinatorial logic to the desired capture FF (*FF*2) in each clock cycle, as shown in Figure 2.2.

Figure 2.2.: Synchronous combinational logic path with launch and capture FF.

The clock-triggered FFs typically have 3 ports, 2 input ports and 1 output port. The port D is the input from the data path (data\_in), and the port Q is the output for the data path. The clock signal is connected to the port *CLK*. Once the *CLK* port detects a positive edge, the data is transferred from D to Q.

Thus, the data on D1 in Figure 2.2 is latched from D1 to Q1 with a rising clock edge. The

data then traverses the data path and the data should arrive at *D*2 before the rising clock edge and then be latched from *D*2 to *Q*2 on another rising clock edge.

However, there is no instantaneous propagation from launch FF to capture FF due to individual delay time of the combinational logic elements of the data path. The data path delay is the sum of the delay of the individual library gates and the respective interconnects. In order to ensure proper functionality of the synchronous circuit, the timing between clock and circuit is essential. Therefore, certain timing constraints have to be met within the sequential circuits. Important timing constraints for the FF are the *setup* and *hold* time. The setup time  $t_{setup}$  is the minimal time previous to the positive clock edge in which the data input requires a stable signal. During the hold time  $t_{hold}$ , the data input has to remain stable after the positive clock edge. The relation between the minimum clock period *T* and the time constraints can be expressed as [57]

$$T \ge t_{c-q} + d_{Path_{MAX}} + t_{setup},\tag{2.1}$$

and the hold time hast to ensure such timing constrains

$$t_{c-q} + d_{Path_{MIN}} \ge t_{hold}.$$

(2.2)

Here, the clock-to-Q-delay  $t_{c-q}$  is the internal propagation delay required by the FFs to propagate the D to Q on a positive clock edge. For Equation 2.1, the worst-case propagation delay  $d_{Path_{MAX}}$  of the path must be considered. Whereas in Equation 2.2 the best case consideration  $d_{Path_{MIN}}$  of the path is taken into account.

Timing constraints must be met in terms of setup and hold time for a given clock period; otherwise, timing is violated. A valid timing of the circuit illustrated in Figure 2.2 is shown in Figure 2.3.

Figure 2.3.: Timing diagram of a capture FF in a synchronous digital circuit illustrating setup and hold time and slack.

The *slack* is also indicated in the Figure 2.3. The slack is the difference between the required arrival time where the  $t_{setup}$  is met and the actual arrival time. The setup timing is met when

the slack is positive (greater or equal to 0).

A synchronous MCU design consists of several millions of paths which all have to meet the timing given the clock period. Thus the performance  $F_{MAX}$  (maximum achievable clock frequency) of an MCU can be expressed as

$$F_{MAX} = \frac{1}{T}.$$

(2.3)

The shorter the clock period *T*, the higher the performance of an MCU. However, the timing constraints must be observed under all circumstances. The Process-Voltage-Temperature (PVT) variation plays an important role here.

### 2.3. PVT Variations

The Process-Voltage-Temperature (PVT) variation significantly impacts the timing of digital circuits, and it is becoming more critical in shrinking technology nodes [58, 59]. The digital circuitry has to ensure error-free working within the specified PVT range. The *process* variation is related to the variation in semiconductor manufacturing due to the complex process steps. The *voltage* variation impacts the operating voltage of the CMOS transistors, and the *temperature* is related to the die temperature, which also has a significant impact. In this section, PVT variations and their effects are explained. It also presents the methodology for handling the sources of variation in modern MCUs.

#### 2.3.1. Process Variations

Process variation arises from the variability of process parameters during the complex manufacturing process of semiconductors. The process variation is caused by the limited control of such process parameters, which results in variability from the defined design target [60].

MCUs are manufactured by multiple chemical and mechanical processes based on a silicon wafer. A sequence of different process steps is executed called photolithography. Masks are used in the steps to build CMOS transistors on the plain silicon wafer. The hypothetical number of masks for building an inverter is six; however, the number and complexity of masks used for large MCUs can be enormous. The process steps, e.g., epitaxy, deposition, and implantation, are repeated until the MCU is manufactured. The metallization and interconnects are also part of the manufacturing process. Such parts connect the sources, drains, and gates accordingly and ensure power distribution [61].

The process variation impacts the film thickness, lateral dimensions, and doping concentration, resulting in variations in channel length and threshold voltage [62]. This impacts the timing of the MCU and, therefore, the performance of each manufactured device [60]. The impact of the process variation can be classified into *inter-die* and *intra-die* variations.

#### 2.3.1.1. Inter-die variation

Inter-die variations are process variations that affect all transistors on a die similarly, e.g., all transistors' channel length on a die might be too long related to the specified value. Those process variations are also called global process variations. The inter-die variation is further distinguished into lot-to-lot (L2L) variations, wafer-to-wafer (W2W) variations, and die-to-die (D2D) variations [61].

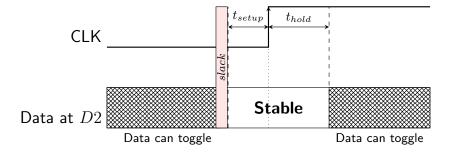

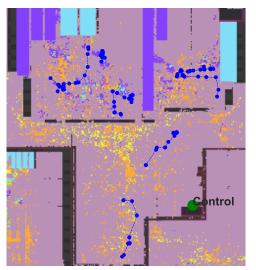

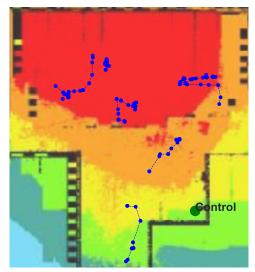

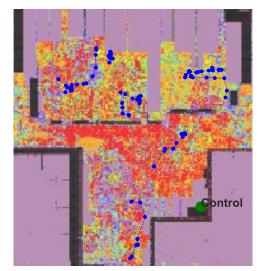

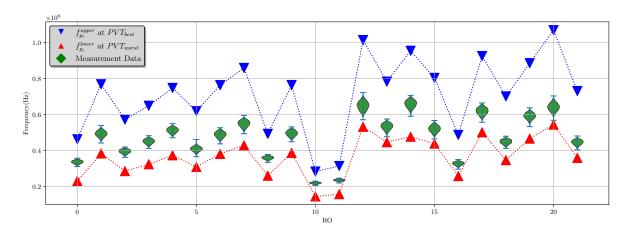

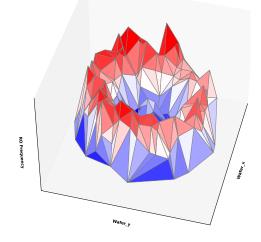

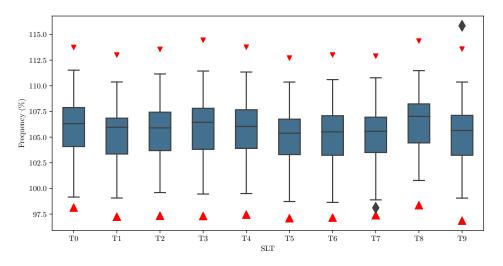

The wafers are processed in stacks called lots. There might be some maintenance steps from lot to lot, impacting the process variation. The same is also for W2W variation, which causes a different timing behavior from wafer to wafer. The D2D variation is visible on the wafer; e.g., a die on the wafer edge behaves differently from the die in the wafer center, mainly caused by D2D variations in manufacturing [61]. A wafer signature caused by D2D variation is shown in Figure 2.4, where the frequency of an RO is plotted for each die on the wafer.

Figure 2.4.: Wafermap shows the D2D variations from the frequency of an RO.

The same RO is integrated at each die on the wafer. The dies on the wafer edge have a lower frequency of the RO than those in the center. Thus there is a radial D2D variation visible on the wafer [60]. Besides such centric radial D2D variation, several other wafer signatures are present in semiconductor manufacturing, which can also lead to defects on the wafer [63].

#### 2.3.1.2. Intra-die variation

The intra-die variations affect various parts of the chip or transistors differently. They are also known as local variations or within-die (WID) variations. The WID variations were smaller in mature nodes than the D2D variations; however, they became more important in nanometer process nodes [61, 64]. Such WID variations can be categorized into two types: pure random variation and spatially correlated variations.

Pure random variations are local variations that are, by nature, randomly distributed across the chip with no recognizable pattern or signature. The main root cause of such variations are random dopant fluctuations (RDF) and line edge roughness (LER) [65].

The spatially correlated variations are also known as location-dependent variations. It shows that the parameter change of one device is correlated with the change of the same parameter of all other devices on the chip. The magnitude of the correlation between the parameters varies depending on their physical position on the chip. The main physical transistor parameters affected by spatially correlated variations are channel length (*L*), channel width (*W*), and oxide thickness ( $T_{ox}$ ) [60].

#### 2.3.1.3. Interconnects

In addition to process variation in transistors, process variation in interconnects is also an important factor. The interconnects are wires that are used to connect the transistors, and they also have a significant contribution to the delay due to their resistance and capacitive components called *RC delay*. The process variations affect the line width and spacing, the metal and dielectric thickness, and the contact resistance. This variation, in turn, affects the RC delay. Also, long wires have significant resistance that dominates the RC delay of an interconnect. State-of-the-art MCU do have multiple layers of closely packed interconnects to cope with the design complexity on the MCU; therefore, the interconnects, and their RC delay become increasingly important [61].

#### 2.3.2. Voltage Variations

Besides the process variation, the environmental operating conditions, such as voltage and temperature, significantly impact the timing of the circuitry and, therefore, its performance. The voltage variation is due to the supply voltage of the transistor. Since the manufactured nodes are rapidly decreasing, the power delivery network (PDN) and packaging follow at different paces. The supply voltage variation can be caused outside the chip due to the power supply and within the chip due to the package and interconnects. State-of-the-art MCUs operate in the sub-threshold region and are even more sensitive to voltage variation.

Voltage variations are categorized into two main categories: *IR drop* and *current derivative* di/dt noise [66]. The IR drop is also called voltage drop. It is caused mainly by the resistive components. That can be either off-chip (e.g., contact resistance, imperfect power supply) or on-chip caused by PDN. The IR drop is independent of the frequency and follows *Ohm's Law*. On the other hand, the parasitic inductance causes the noise of the current derivative. The switching activity of the transistors has the most significant influence on the noise of the current derivative. Strong load jumps can cause voltage undershoots or voltage overshoots [66].

Depending on the root cause of the voltage variation, the duration can be in the nanosecond

range for high-dynamic events until voltage variations in the microsecond range, depending on how fast the power supply can compensate for the variation. The voltage deviations impact the timing of the entire chip. The gate delay time is proportional to the voltage and follows the formula [67]

$$t_{gate} \propto \frac{V}{(V_{TH} - V)^{\alpha}}.$$

(2.4)

Where  $V (V_{DD} - V_{SS})$  is the supply voltage,  $V_{TH}$  is the threshold voltage of the transistor, and  $\alpha$  is a technology-dependent parameter. Thus, if the *V* is close to the  $V_{TH}$ , the voltage variation does have a major impact on the timing. There is a need to monitor the voltage precisely and react to occurring voltage variations immediately in designing a robust PDN, e.g., by using considerable supporting capacities. The tolerable voltage variation often found in the literature and on product data sheets is  $\pm 10\%$  of *V* [68, 69, 17, 61].

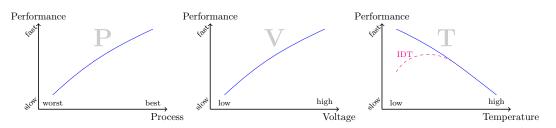

#### 2.3.3. Temperature Variations

The second environmental condition which has a major impact on the timing behavior is the temperature. The temperature of the chips can be influenced by the ambient temperature or thermal hotspots on the chip itself. The ambient temperature depends on whether the chip is operated in different climatic regions (desert climate or polar regions) or how powerful the external thermal system (heating or cooling) is at the system level as well as on the application area (e.g., commercial, military) [61]. Thermal hotspots occur in high-switching active areas due to the power dissipated by the transistors. This also depends on how effective the thermal conduction of the chip can dissipate the heat from chip regions. Compared with the voltage variations, the temperature variations have a higher time constant in the range of milliseconds to seconds [69].

An increase in temperature elevates the delay of the interconnects due to their parasitic resistance. The temperature behavior of the gate propagation delay depends on the voltage, especially if the device is operated in the sub-threshold region due to weak carrier mobility [70]. This effect is called inverse temperature dependence (IDT). The timing behavior and, therefore, the performance of a device depends on the dominance of the IDT. If long interconnect delays dominate the timing behavior of a device, the device will most likely be limited at high temperatures. If logic gates dominate the timing, cold temperatures are worse.

In conclusion, considering PVT variation in MCUs is crucial for reliable device timing and performance. Much effort is needed to ensure a proper function over the specified operation window. This includes that all hold and setup constraints are met. In order to achieve this, the timing behavior for each PVT case must be covered and verified during the design phase as well as validated in the Post-Si phase.

#### 2.3.4. Methods to cope with PVT Variation

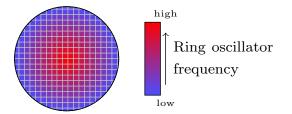

The PVT variations need to be considered during the design in the Pre-Si and the Post-Si phase since their timing influence is tremendous. Figure 2.5 comprehensively demonstrates the influence of the PVT variations with respect to the performance [71].

Figure 2.5.: Relation between PVT variations and performance.

The most common methodology to cope with the PVT variations in the Pre-Si design phase is performing *corner analysis* to investigate the specified PVT space with the help of powerful electronic design automation (EDA) tools. The Post-Si validation uses *corner lots* to explore the process range in manufacturing, and voltage and temperature are environmental components addressed with the test setup.

#### 2.3.4.1. Corner Analysis in Design Phase

Corner analysis, also known as corner case analysis or process corner analysis, is a technique used in design to evaluate the timing and performance of integrated circuits under different operating conditions. It involves simulating the circuit behavior across the PVT range in so-called corners. Especially, corner analysis aims to assess how the circuit behaves under the worst-case conditions.

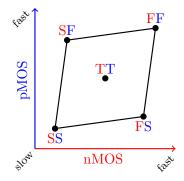

In terms of process corners, the transistor manufacturing processes are clustered into *slow* (*S*), *typical* (*T*) (also called *nominal*), and *fast* (*F*). The CMOS technology uses two types of transistors: the nMOS and pMOS. The two transistor types are treated independently. That results in the process corners shown in Figure 2.6. The first character corresponds to the process corner of the nMOS, and the second character to the pMOS - as color-coded in Figure 2.6 [61].

Besides the transistor process corners, the interconnects are also considered with their parasitic RC components. The RC components are also simulated as slow, typical, and fast.

The environmental conditions - voltage and temperature - are also considered in the same way to be *S*, *T*, or *F*. The fast corresponds to high voltage and low temperature and slow corresponds to low voltage and high temperature, in between such conditions is the typical case [61]. Due to the IDT, the worst temperature case can change depending on the design,

Figure 2.6.: Corner cases of a CMOS transistor.

as explained in Section 2.3.3.

In order to ensure a proper function of the design, a multi-corner analysis is required to ensure the correct timing behavior in each specified corner. The nomenclature of such a multi-corner is usually expressed in the three design corners (*S*, *T*, *F*) cases. Therefore an *SFTSS* corresponds to a *slow* nMOS, a *fast* pMOS, a *typical* RC, *slow* voltage (min), and *slow* temperature (hot). The design must be verified in every corner.

Timing verification using tools like Simulation Program with Integrated Circuit Emphasis (SPICE) is not feasible due to the complexity of large designs and limited computing power [72]. In addition, such tools are primarily intended for analog simulations at the transistor level. Therefore, a powerful method called static timing analysis (STA) is used to perform timing verification in digital circuits.

The STA is a method to investigate and verify the timing of the MCU without simulating the full design. The entire design is analyzed to determine if all timing constraints are met for every corner. The setup critical timing paths are typically suspected in the slow corners, whereas the fast corners face hold time violations. The term static refers to the circumstance that the design is analyzed in a static condition by not taking care of any input or output data - which is the case in performing a simulation. The STA is performed as one of the last steps before tape out to ensure the design's timing closure. EDA tools exist to accomplish an STA on the design and identify weaknesses. Especially the worst-case corners are focused on ensuring a robust design [71, 73].

However, the STA using the corner-based approach has limitations. Especially when WID variation becomes dominant, this can not be handled with the corner-based STA [74, 17]. There are methods like statistical static timing analysis (SSTA) [64] that manage the WID variations in designs - however, SSTA still needs to be consistently adopted across the industry [75, 32]. The typical approach to mitigate timing uncertainties caused by WID and noise is the use of additional margins. Those margins are on top added to the STA results,

adding pessimism and reducing the risk in the overall timing verification [71].

#### 2.3.4.2. Corner Lots in Post-Silicon

In distinction to Pre-Si verification, the manufactured device must also be validated across the PVT corners in Post-Si. In order to cover the entire PVT space, corner lot wafers are manufactured. Such corner lot wafers are special flavors of wafer in which the manufacturing parameters are reflected. For example, the manufacturing parameters of all nMOS transistors on the wafer are tweaked to be slow. In contrast, all pMOS transistors in the wafer are manufactured to be fast - in other words, an *SF* corner lot wafer. The same parameter changes can be made for all manufacturing parameters that can be selectively influenced - these can be transistor parameters as well as interconnect parameters. The amplitude of the deviation can also be adjusted from the typical value, which is given in *sigma steps*.

The corner analysis of the environmental parameters voltage and temperature is easier to cover. The ambient temperature of the chip is adjusted using advanced temperature sources in the validation set-up. Even when the devices are on the wafer, such wafers are mounted on a chuck with very high-temperature stability. High-performance, high-precision power supplies can take over the power supply and allow the entire operating voltage range to be validated. The PVT validation of a device is part of the product characterization process [76].

#### 2.3.5. Additional Safety Margins

Besides the PVT variation considered with the corner-based analysis, additional safety margins are required to ensure proper function. There are several reasons why those additional safety margins are required. Two reasons for additional margins in the timing verification are explained.

Modern MCUs operate with a clock frequency of several hundred megahertz. In operating mode with such high frequencies, electromagnetic cross-talk can occur, which impairs the signal integrity and, thus, the timing behavior. That electromagnetic cross-talk is, in most cases, an aggressor-victim scenario where the noise and emission of one particular region affect another region in which the timing error occurs [54].

The second added margin is the safety margin for aging. The MCU manufacturer has to ensure proper function in the delivery status and at the end of the life of the MCU. Several aging effects become more important in shrinking technology nodes, such as negative bias temperature instability (NBTI) and hot carrier injection (HCI), which also affect the timing behavior of the circuit [34, 77, 78]. The margins required to *guardband* the aging over the lifetime depend strongly on the mission profile. In order to ensure a proper function independent from the mission profile, the added safety margins are intended to

cover the worst-case scenarios. This leads to the claim that the added safety margins are too pessimistic [79].

However, the additional safety margins in electromagnetic cross-talk and aging are mandatory if the MCU controls safety-critical applications in automotive.

## 2.4. Testing of MCUs

Since modern MCUs consist of more than hundreds of millions of transistors, the complex manufacturing process might lead to defects. Due to these defects, the MCUs might not be working properly. Thus, testing MCUs is essential in detecting such defects and ensuring an error-free operation. Efficient testing ensures functionality, timing, and performance, making it crucial for modern electronic devices. Design for Testability (DfT) is an essential method to enable test. The basic principle of DfT and its infrastructure and approaches are explained in this section.

#### 2.4.1. Design for Testability (DfT)

DfT is a bunch of approaches used to make testing easier and more effective. DfT is adding further logic and components to the design to create an infrastructure for the test of the design. This infrastructure is inserted along the industrial design process, as Figure 2.1 explains with an important DfT step - the scan insertion.

A common DfT technique is the *scan test;* this includes *scan insertion* and *scan compression* and utilizing various fault models to detect defects efficiently. The following section (section 2.4.1.1) will describe this method because of the fundamental importance of this work. Another common technique in DfT are boundary scan and memory/logic built-in self-test (BIST). Boundary Scan, or Joint Test Action Group (JTAG), is a technology used to test and debug MCUs without direct access to their pins. Instead, a standardized interface called JTAG is used to communicate with the MCUs. BIST is an on-chip test infrastructure to detect defects without using external test equipment. There are approaches to testing digital logic built-in self-test (LBIST) and on-board memory built-in self-test (MBIST), and those methods can also perform in-field tests [55].

#### 2.4.1.1. Scan Test

Scan test is a standard technique used in digital MCUs nowadays. This is a structural test method to detect defects in the circuit deterministically. In order to realize this, some scan infrastructure is necessary. This process is called scan insertion.

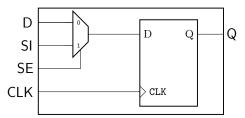

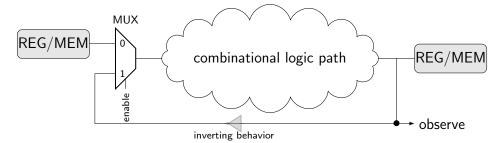

**Scan Insertion** The scan insertion is done in two steps. First, the FFs and latches in the design are replaced with the so-called *scan FFs*. The scan FF is built with a multiplexer (MUX) and an ordinary FF; the scan FF is shown in Figure 2.7.

Figure 2.7.: Scan FF contains an ordinary FF and a MUX.

Besides the data input port (D) and data output port (Q), and the clock (CLK), the scan FF has two additional ports: the scan input port (SI, scan\_in) and the scan enable port (SE, scan\_en). The scan\_en controls whether the latched input data of the internal FF captures from D input - called functional (or mission) mode- or the data is captured via the scan\_in port - called scan mode.

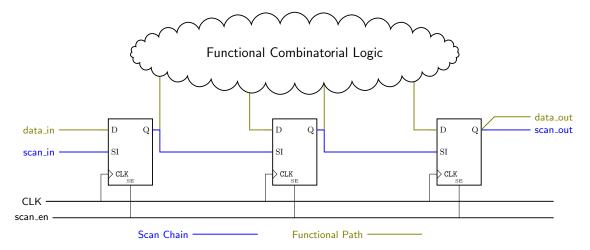

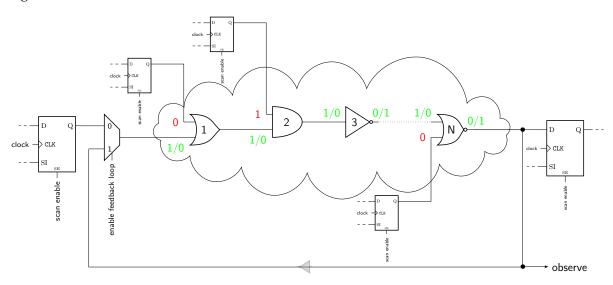

The second step is the connection of the previously placed scan FF to the so-called *scan chains*. The circuitry connectivity after the scan insertion is schematically shown in Figure 2.8 for a small circuit, demonstrating three scan FFs connected in one scan chain.

Figure 2.8.: Scan insertion replaces three FFs with scan FFs and connects them to a scan chain.

The scan chain is colored in blue and runs from the scan\_in through the SI of the first scan FF. From the Q of the first scan FF, the scan chain is connected to the SI of the next FF; this interconnection continues in this way. This is repeated until the last output of the scan FF within the scan chain, which is the scan\_out - the output of the scan chain.

Large MCUs contain a large number of scan chains. The scan\_en is valid for all scan chains.

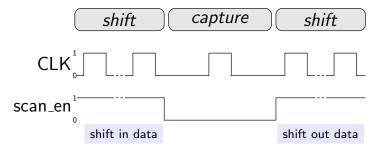

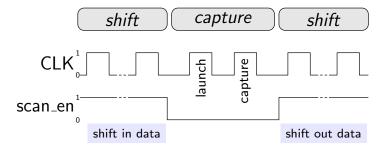

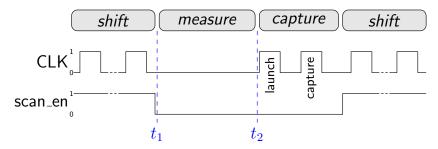

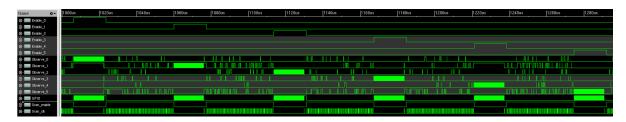

If the MCU is in scan mode (scen\_en is high), the scan chains are sequentially loaded with 0 or 1 until all scan FFs have the desired value. After that load phase, the scan\_en is switched off, and one or more functional at-speed pulses occur, called launch and capture. Once this is done, the scan\_en turns on again, and captured values are unloaded from the scan chains. Such unload values are compared with the expected values. The MCU passes the test if every captured value equals the expected value. Such scan test procedure is shown in Figure 2.9.

Figure 2.9.: Scan test procedure with a capture pulse.

The input values are called test/scan vectors or patterns. The scan test is repeated and consists of thousands of scan patterns. This provides controllability and observability for every scan FF during the scan test.

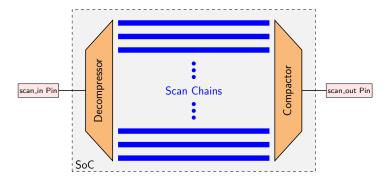

**Scan Compression** The scan chains become more extensive since more sequential scan FFs are included to cover the entire MCU. This would result in long scan chains and high effort to load and unload all scan chains with the scan pattern. Scan compression is an efficient method to reduce the length of the scan chain and subsequently reduce the test time by introducing a decompressor and compactor. Figure 2.10 shows the scan compression methodology.

Figure 2.10.: Scan compression allows the parallel loading of scan chains with a decompressor and compactor through a single pin.

The scan chains are arranged between the decompressor and the compactor. In that way, the length of the scan chains is reduced. The scan chains are loaded and unloaded at high-speed

scan\_in and scan\_out ports. The shift speed of the scan chains remains nearly the same. However, the overall test time is reduced with this approach.

#### 2.4.2. Fault Models

The test vectors/ scan patterns are not randomly chosen sequences of bits; instead, the test vectors are associated with fault models. Fault models are a formal abstraction where a fault is a logic description of the effect when a defect is present in the digital logic circuitry of the MCU. Dedicated test vectors are calculated using such fault models to test the digital logic for correct functionality. Such fault models aim to ensure defect-free circuitry after applying all variants of the dedicated fault model to all gates of the logic circuit. The metric to quantify the covered defect-free logic is called *fault coverage*. The fault coverage is calculated for each fault model, and several fault models are in use.

There are two classes of fault models: *static* fault models and *dynamic* fault models. Static fault models focus on static defects in the circuitry independent of any timing constraint. Commonly used static fault models are the Stuck-at-Fault model and the Bridging-Fault model [80, 81]. Such fault models are also used for IDDQ tests. Dynamic fault models, in turn, consider the circuit's timing behavior and are executed at speed. Widely used dynamic fault models are the Transition Fault, Gate Delay Fault, and Path Delay Fault Models. The Transition Fault model and Gate Delay Fault are aiming localized timing faults within the logic circuit. The path delay fault model considers the timing behavior of the entire path. The path delay fault model is used in this work and described in detail in the following.

**Path Delay Fault Model** The path delay fault model [82] aims to check if the path's timing is met within the clock cycle. In order to do this, the path delay fault model is executed at speed in the capture phase in contrast to the sequence shown in Figure 2.9. Therefore, two clock pulses are executed during the capture phase; the first is the launch pulse, and the second is the capture clock pulse. The test sequence is shown in Figure 2.11.

Figure 2.11.: Scan test using a path delay fault model.

During the shift in phase, the path to be tested is prepared, also known as path sensitization.

This means that all side inputs of the path need to be on a stable value. In addition, the side input needs to be on a non-controlling value. Once these requirements are fulfilled and the path is sensitized, the launch pulse is executed at the launch point; this is a controllable and observable point in the circuitry - a scan FF. The launched transition is then propagated through the sensitized path and is captured with the second clock pulse - the capture pulse - at the capture point, which is usually also a scan FF. The time between launch and capture clock pulse is at regular operation clock speed. The captured value is then shifted out, and the actual captured values are compared with expected values. If the expected values equal the actual values, the path delay test is successful. The path description to be tested must be provided for every path delay test.

The path delay fault patterns are distinguished in several modes based on sensitization criteria. The weakest path sensitization is functional sensitizable, which means that the path propagates the transition during the test, but the side inputs do not need to be stable. The non-robust mode ensures that the side inputs are only on a stable non-controlling value during the capture clock pulse. The tightest mode is the robust one, which requires stable non-controlling values at all side inputs during the launch and capture clock pulse [83, 84]. There is also the additional option of the hazard-free mode, which is even a little stricter than the robust mode. In this mode, an attempt is made to prevent glitches and reconvergence in the path [68]. Dependent on the sensitization mode chosen, it becomes more challenging to calculate a path delay test pattern that fulfills all sensitization requirements.

In addition to the sensitization mode, the clock handling can also be adjusted, the launch-off-shift (LOS) and launch-off-capture (LOC) mode [85, 86]. The LOC method was implicitly introduced in Figure 2.11. Such a mode allows a clear distinction between shift and capture - the shift phase cares for path sensitization, and the two at-speed clock pulses are executed in the capture phase. Instead, LOS squeezes the launch clock pulse into the end of the shift phase. Both approaches have their advantages and disadvantages [68]. Due to strict separation in shift and capture, the LOC will be the essential mode in this work.

There are many constraints in the calculation of scan patterns for large MCUs, so EDA tools are used, especially the automatic test pattern generation (ATPG).

#### 2.4.2.1. Automatic Test Pattern Generation

ATPG is a methodology to generate test patterns used in the industrial environment by considering the fault models mentioned in Section 2.4.2. An ATPG tool is a software tool that generates test patterns for a given MCU design. The ATPG tool requires the netlist of the design with the already placed scan infrastructure. Based on the fault model determined, the ATPG tool calculates scan patterns to achieve high fault coverage for a wide range of potential faults in the circuit. The resulting scan patterns are in an ASCII file format called

waveform generation logic (WGL) or standard test interface language (STIL). The scan pattern in WGL/STIL format is required to test an MCU in an industrial test environment using automatic test equipment (ATE).

#### 2.4.3. Automatic Test Equipment

The automatic test equipment (ATE) is the hardware instrument on which the DUT is mounted during the test procedure. The ATE provides power to the DUT and applies all test patterns. The ATE itself is a complex real-time system that can leverage many DfT methodologies. The scan patterns in WGL format are read into the ATE. Regarding the execution of the test, the ATE generates the stimuli for the scan\_in port and loads the scan chains. The clock signal is also controlled via the ATE, as well as the comparison of the scan\_out values with the expected values is checked on the ATE. Such MCU testing can be done on the wafer level where the pads on the die are connected with needles from a probe card to the ATE or with package MCU which is then mounted on a socket through the ATE. With the ATE, fast, precise, and automated execution is enabled [87, 55].

### 2.5. Performance testing

In this section, the performance testing is explained. The performance of an MCU is the maximal achievable clock frequency of the device under worst case conditions. The performance of an MCU is also denoted as  $F_{MAX}$ . The approach to test the performance is called *performance screening*, in which the  $F_{MAX}$  of every device is checked. The term *speed binning* is also used for this approach which suggests an instantaneous sorting in categories according to the speed of the devices.

The performance testing of large modern MCUs is challenging due to the complex design and PVT variations. Structural dynamic scan patterns (see Section 2.4.1.1 - transition fault pattern, path delay fault pattern) are not suitable for precise performance testing. This has two reasons, the scan patterns provide only a pass/fail criterion, and second is not possible to determine the unique performance limiting paths. Many near-critical timing paths are in modern MCU designs, resulting in a timing wall. As a result, it is practically impossible to determine the path that is causing the performance limitation on large MCUs.

Therefore, other approaches are necessary to determine the performance of the chip. The following sections present two commonly used methods which are central pillars of this work.

Note that the performance testing does not aim to detect devices with physical defects (e.g., shorts, opens); structural scan tests are used for this purpose.

#### 2.5.1. Performance Monitors

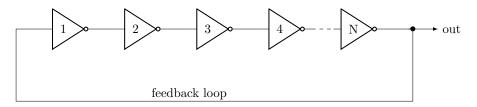

One way to determine the performance of a chip is to use indirect performance monitors [26, 27, 28, 29, 30, 31, 21]. Such performance monitors are ring oscillators (ROs). An RO is an odd number of *N* inverting logic gates connected serially, forming a closed loop. The basic structure of an RO using inverter gates is shown in Figure 2.12.

Figure 2.12.: Basic principle of an RO using inverter gates.

Each logic gate in the RO and the interconnects in between add delay to the overall timing of the RO. A positive or negative edge is launched at the start of the RO once the power supply is switched on, and the signal propagates through the logic gates in the RO. Due to the odd number of logic gates and, therefore, the implicit inverting behavior of the RO, the positive/negative edge becomes inverted at the end of the RO. Then the inverted edge is propagated through the feedback loop, triggering the next negative/positive edge. This results in a continuous oscillation where the frequency of the RO is the critical metric that is measured on the output.

The oscillation frequency f of an RO is expressed as

$$f = \frac{1}{2T_{RO}},\tag{2.5}$$

where  $T_{RO}$  is the delay time of the RO.  $T_{RO}$  is calculated as follows,

$$T_{RO} = T_{Gate} \cdot N + T_{Loop}. \tag{2.6}$$

$T_{Gate}$  is the propagation delay for each of the *N* gates in the RO, and  $T_{Loop}$  is the interconnect delay. The timing of the gates used in the circuit behaves similarly to those used for the ROs. This is why such ROs can be used as indirect performance monitors.

In order to utilize ROs for performance testing, more than the basic RO structure shown in Figure 2.12 is needed. Thus there are various RO designs proposed and analyzed in literature. A fundamental distinction can be made between the two types of ROs: *generic ROs* and *design-dependent ROs* [29].

Generic ROs consist of a homogeneous logic gate type, e.g., inverter or NAND gate. Standard gate libraries used in large MCUs designs typically consist of several standard logic gates in different driver strengths and further variations in the number of inputs/outputs and threshold voltages. Building one RO out of each used logic gate in the cell libraries would result in hundreds of generic ROs. Another way is to leverage the design information of the chip and build so-called design-dependent ROs. Such ROs aim to mimic the design of the chip. In order to do this, several methods are used, from straightforward path replicas to sophisticated synthesis algorithms considering the entire PVT space [38]. In the end, the performance test's accuracy and quality highly depend on the sensitivity of the performance monitors used [39, 88].

Also, the value of *N* has a significant impact. The visibility of D2D and WID process variation within an RO depends on the number of logic gates *N* in the RO. Especially for smaller technology nodes (<40 nm), the WID variability is only visible with short ROs containing less than 10 gates. In comparison, the D2D variation is independent of *N* [88, 89]. Such ROs follow the process variation, usually Gaussian distributed [90]. In addition, *N* also affects the oscillation frequency, which is a considerable limitation for the frequency measuring gear and the resulting accuracy, and each additional gate contributes to the leakage current, which is also a critical variable in MCU requirements [87].

#### 2.5.2. Functional Testing

Another fundamental approach in performance testing is the execution of functional tests. A functional test is named due to the fact that the functional test cases are executed on the MCU. Such functional test cases simulate different workloads or functional test cases of the MCU to find defects and complement structural testing [10].

The functional test is distinguished into two subgroups. The first method is the traditional functional testing where small code pieces are uploaded to the MCU on the automatic test equipment (ATE) and executed. The second method is the system-level test (SLT). The SLT is a time-consuming test where the MCU is mounted in an application-like board, and several test cases are executed. Such test cases can be customer application test cases of reusing verification stimuli [13]. SLTs require lots of test time and are challenging in high volume production [25].

In contrast to the structural scan test, traditional functional testing and SLT do not have straightforward coverage metrics, making it difficult to determine the testing quality [13].

In order to use the functional test for performance testing, there is a particular procedure. The clock frequency (execution frequency) of the DUT is executed at a low frequency in an infinite loop. Then step by step, the clock frequency is increased. This is continued until the maximal execution frequency without a failure. Using that approach, the performance of a device is determined given the particular functional test case [11].

## 2.6. Machine Learning in IC Testing

#### 2.6.1. Machine Learning Basics

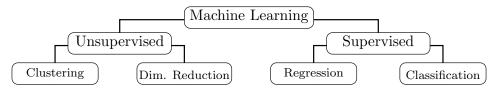

The term *machine learning* was introduced by Arthur Samuel in 1959 [91]. machine learning (ML) describes a subfield of *artificial intelligence*. ML facilitates computers (machines) to learn from existing data and predict the outcome of non-seen data without explicitly programming the computer. ML uses mathematical and statistical methods to identify the provided data's patterns, relations, or similarities. The field of ML has been rapidly increasing in the last decades. Meanwhile, ML-based techniques can be found in numerous applications and industrial scenarios.

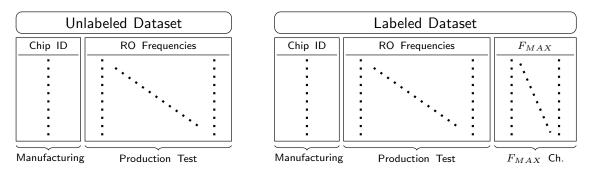

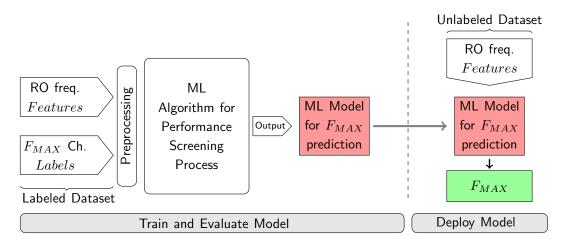

The scope of ML is to find a function f that describes the relation between the input data x and the output data  $y: f: x \mapsto y$ . Since the function f is unknown and shall be learned by ML, the ML calculates an approximation function  $\hat{f}$  using the provided dataset  $X - \hat{f}$  is also known as the ML model. Thus the input data x and output data y are vectors. Each input  $x_i$  is called a *feature*, and the output  $y_i$  is called a *label*. In order to create an ML model, the provided dataset is split into a *training set* S and a *test set* T (or validation set). The training set is used to train the ML model, which means finding a suitable approximation function that maps the features of S to the labels. Once the training is done and the ML model exists, the ML model is validated. The ML model validation feeds unseen features from the test set T into the ML model, and  $\hat{y}_j$  is calculated. Then the  $\hat{y}_j$  and known  $y_j$  deviation from the test set is compared. The ML model is scored depending on how well the predicted data and the known data fit. Scoring metrics are, for example, the mean absolute error (MAE) and the root mean square error (RMSE).

ML can be divided into different subfields as shown in Figure 2.13. The subfields used in this work are *supervised learning* and *unsupervised learning*.

Figure 2.13.: ML overview of approaches in this work.

**Supervised ML** is the learning approach in which the features are mapped to the labels, and the ML model is considered a black box. Such a supervised learning algorithm aims to calculate a model that maps the input to the output data. Using the trained ML model, it is possible to predict the outcome of non-seen data using only the input data. The supervised ML can be categorized into *classification* and *regression* [92].

#### 2. Background

The classification-based ML classifies the labels into discrete categories or classes. Therefore the labels should be in a categorial data format. A straightforward example is the classification into TRUE or FALSE based on the given features. The feature data type does not have to be categorical.

In contrast, regression-based ML provides continuous numerical values for the output variable. They are often used to make precise numerical predictions.

**Unsupervised ML** is applied when only features are available for the training, and the labels are unknown. Thus it is not supervised by the labels - therefore, unsupervised. This type of learning intends to find patterns and statistical dependence in the features without prior knowledge of the outcome. Two often used unsupervised methodologies in ML are *clustering* and *dimensionality reduction* [92].

Clustering describes the process of dividing a dataset with features into groups or clusters with the same or similar characteristics. The clustering algorithm uses distance-based, density-based, or hierarchical approaches to cluster the dataset into distinct groups [93, 94, 95].

On the other hand, dimensionality reduction intends to transform (or filter) the features into a reduced feature set. This should be done by keeping valuable information from the dataset. An often-used approach in dimensionality reduction is principal component analysis (PCA) which transforms the feature space into a reduced feature space by considering the eigenvalues [96].

Dependent on the ML approach, there are different scoring and error metrics explained once used in the later sections.

#### 2.6.2. Machine Learning in Testing

Modern MCUs have become larger and more complex over recent years. This results in higher effort in testing to ensure the same or even higher quality. ML has become a well-established method for making testing more efficient and manageable in the testing of MCUs [97, 98].

However, once ML is applied to real-world problems, it can help and harm. One of the most crucial things in ML applied to test is the choice of the training set. On the one hand, it shall identify outliers that are a risk for proper training. On the other hand, the trained ML model shall be robust and able to generalize. Thus, ML helps to determine devices in pass and fail and many other areas in testing. This work uses ML to manage the difficult task of performance screening in automotive MCUs.

## 2.7. Automotive Quality

Automotive MCUs means that such MCUs are used in automotive applications that are often responsible for safety-critical systems. Such functional safety systems can be braking, steering, airbag systems, and numerous other automotive applications. Also, functional safety is essential for advanced driver-assistance systems (ADAS) and autonomous vehicles. The guidelines and standards for electronic components in functional safety automotive environments are described in ISO 26262 [99]. In addition, there are qualification specifications and requirements defined in AEC Component Technical Committee [5] agreed upon and defined by a large automotive community. These guidelines and requirements show how important it is to deliver high-quality automotive MCUs.

The quality and reliability of automotive MCUs are specified in defective parts per million (DPPM). In literature, the term PPM and the notation in defective parts per *billion* (DPPB) can be found. The critical metric remains the number of defective devices that successfully pass the test. Here, the devices are related to several ground truths (millions, billions). However, no severe rule exists for DPPM rates in the automotive industry [100]. Nevertheless, there is a solid strive to ensure zero defect quality, which means 0 DPPM accepted [101]. One of the most essential things to ensure zero defect quality is high qualitative testing [100, 102, 6].

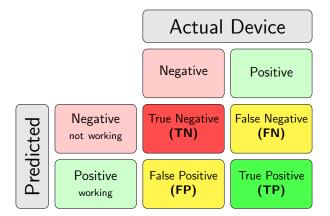

The outcome of semiconductor testing is either the device passes all tests, or it fails the testing (one or more tests). On the other hand, there is the chance that the testing result is not correct. Either the test indicates that the device is pass whereas the actual device should fail or vice versa. This circumstance can be visualized in the confusion matrix shown in Figure 2.14. Such a metric can be used for all classification problems and ML classification.

Figure 2.14.: Confusion matrix of a classification problem.

The confusion matrix have four potential outcomes. The true positive (TP) and true negative (TN) is clear - the test (predicted) result equals the actual state of the device. A false negative

(FN) that is tested fail but is actually pass will cause yield loss. Yield describes the proportion between devices tested as non-defective and the total number of tested devices. In order to make it clear: FN are fault-free devices that are thrown away due to the test result - the yield decreases. However, concerning automotive quality, the false positive (FP) devices are the most critical, also known as escapes, and harm the quality. In order to handle and manage this issue to guarantee automotive quality, the six sigma criterion can be deployed.

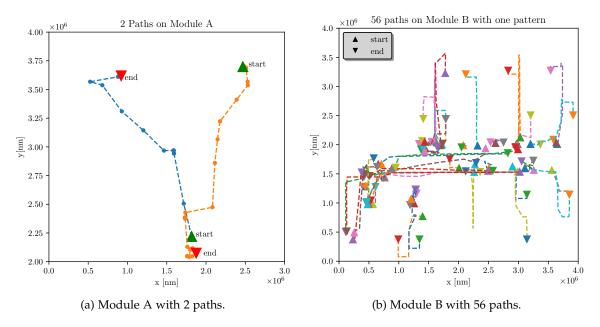

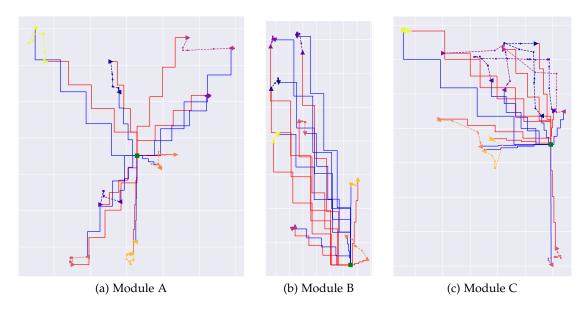

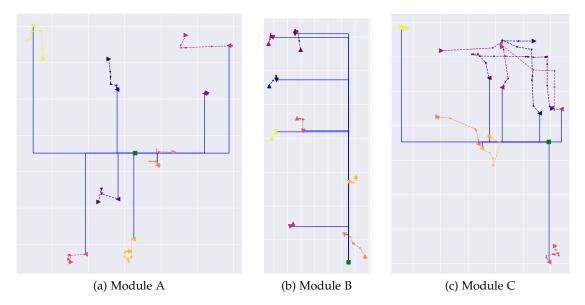

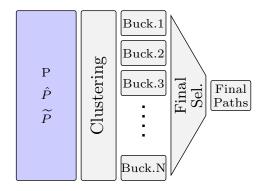

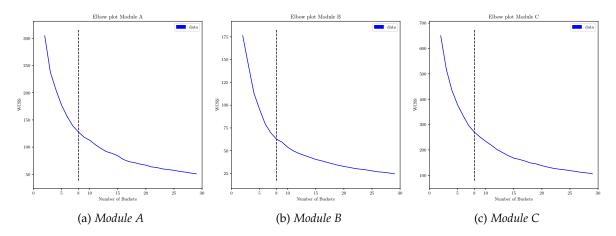

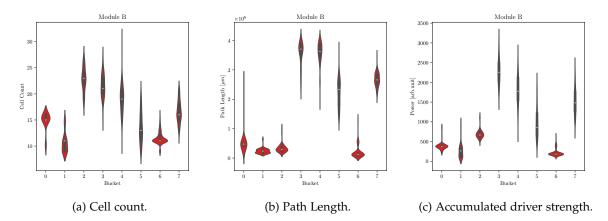

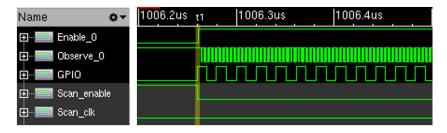

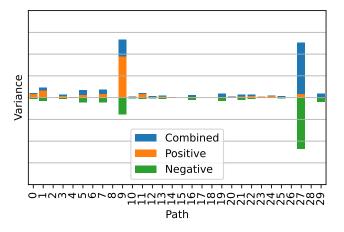

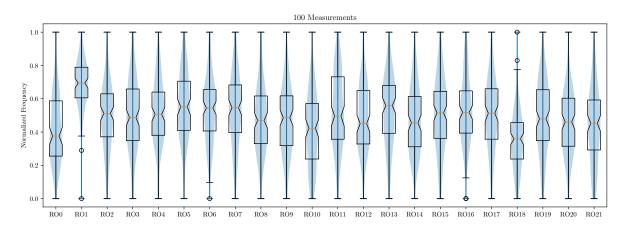

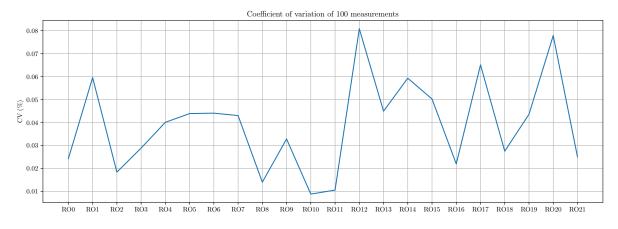

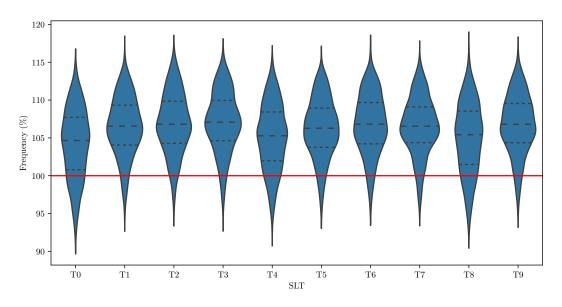

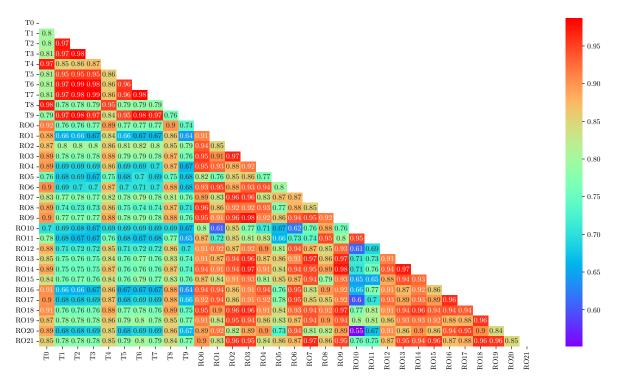

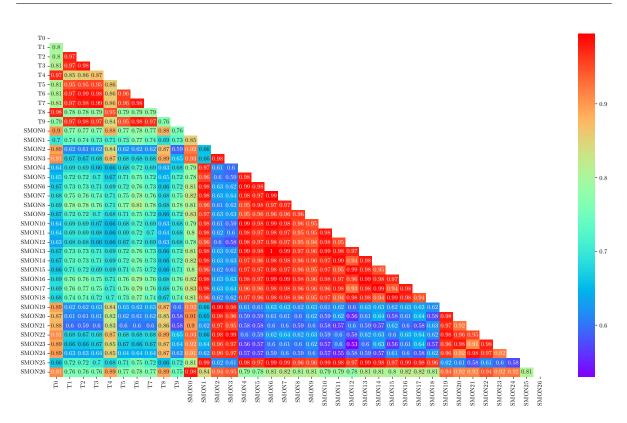

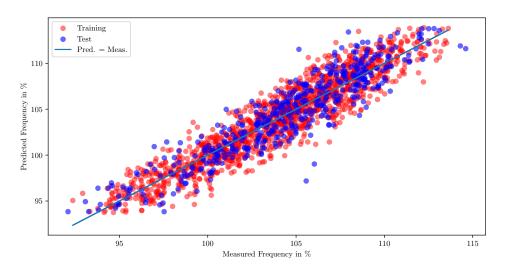

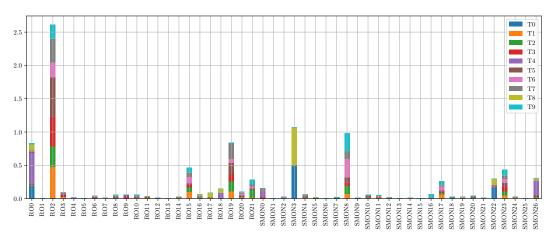

#### 2.7.1. The Six Sigma Guardband