## TECHNISCHE UNIVERSITÄT MÜNCHEN

Master's Thesis in Informatics: Robotics, Cognition, Intelligence

# Routing Strategy for Multi-Layer Microfluidic Devices Using ILP

Minxing Wang

### TECHNISCHE UNIVERSITÄT MÜNCHEN

Master's Thesis in Informatics: Robotics, Cognition, Intelligence

# Routing Strategy for Multi-Layer Microfluidic Devices Using ILP

# Routing-Strategie für mehrschichtige Mikrofluidikchips mit ganzzahliger linearer Programmierung

Author: Minxing Wang

Supervisor: Prof. Dr.-Ing. Ulf Schlichtmann

Advisor: Yushen Zhang Submission Date: 2023.11.10

| I confirm that this master's thesis in informatics: robotics, cognition, intelligence is my own work and I have documented all sources and material used. |  |              |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--------------|--|--|--|--|

| Munich, 2023.11.10                                                                                                                                        |  | Minxing Wang |  |  |  |  |

|                                                                                                                                                           |  |              |  |  |  |  |

## Acknowledgments

I would like to express my sincere gratitude to all those who have supported me throughout my journey to attain my Master's degree. I am deeply thankful for the unwavering encouragement, guidance, and assistance I have received from my professors, advisors, and mentors. Their expertise and commitment to education have been invaluable in shaping my academic growth.

I am also grateful for the camaraderie and collaboration I have experienced with my fellow students. Together, we have shared knowledge, faced challenges, and celebrated successes, creating a rich and inspiring learning environment.

Furthermore, I extend my appreciation to my family and friends for their unwavering support, patience, and understanding during this demanding academic endeavor. Their love and encouragement have been my pillars of strength.

To all of you, I extend my heartfelt thanks. Your contributions have played a crucial role in my academic and personal development, and I am grateful beyond words for your belief in me and my aspirations.

# **Abstract**

Nowadays, most microfluidic chips are manufactured by soft lithography technology. However, with the development of 3D printing technology and the emergence of new materials, microfluidic chips can also be produced by 3D printing. Compared with microfluidic chips produced by soft lithography, 3D-printed microfluidic chips allow for the rapid prototyping and production of complex, multi-layered microfluidic architectures, which would be laborious and time-consuming to create using soft lithography. In the future, 3D-printed microfluidic chips will be used in a broader range of fields.

To simplify the 3D-printed chip design process, this thesis designs a program that can generate layouts of channels automatically if given the chip's size parameters, the placement information of modules inside the chip, and the connection relationship between modules. In addition, users can specify the pressure difference between the two modules, and the program can design the layouts of channels according to the required pressure loss. Besides that, to ensure the response speed of the program, the thesis uses the A\* algorithm, scaling, and channel merging to avoid introducing too many parameters that need to be calculated.

After testing, the program can generate placement information of channels for a three-layer microfluidic chip with six modules within 1 second. In the future, the accuracy and application scope of the program's output results will be further improved.

# **Contents**

| A  | Acknowledgments |                                                                          |                                                                      | iii |  |

|----|-----------------|--------------------------------------------------------------------------|----------------------------------------------------------------------|-----|--|

| A۱ | bstrac          | et                                                                       |                                                                      | iv  |  |

| 1  | Intr            | Introduction                                                             |                                                                      |     |  |

|    | 1.1             | Resea                                                                    | rch background                                                       | 1   |  |

|    | 1.2             | Resea                                                                    | rch status                                                           | 4   |  |

|    | 1.3             | Resea                                                                    | rch significance                                                     | 7   |  |

| 2  | Con             | straint                                                                  | Programming                                                          | 8   |  |

|    | 2.1             | Defini                                                                   | ition of constraint programming                                      | 8   |  |

|    | 2.2             | Types                                                                    | of constraint programming                                            | 8   |  |

|    | 2.3             | Metho                                                                    | ods for solving constraint programming problems                      | 9   |  |

|    |                 | 2.3.1                                                                    | Backtracking search                                                  | 9   |  |

|    |                 | 2.3.2                                                                    | Local search                                                         | 10  |  |

|    |                 | 2.3.3                                                                    | Dynamic programming                                                  | 10  |  |

| 3  | Mat             | hemati                                                                   | cal modeling of microfluidic chips                                   | 12  |  |

|    | 3.1             | Chip 1                                                                   | modeling                                                             | 12  |  |

|    |                 | 3.1.1                                                                    | Module modeling                                                      | 13  |  |

|    |                 | 3.1.2                                                                    | Pin modeling                                                         | 14  |  |

|    |                 | 3.1.3                                                                    | Channel modeling                                                     | 15  |  |

|    | 3.2             | <u>e</u>                                                                 |                                                                      |     |  |

|    |                 | 3.2.1                                                                    | Basic constraints of a channel                                       | 17  |  |

|    |                 | 3.2.2                                                                    | Constraints of non-collision                                         | 18  |  |

|    |                 | 3.2.3                                                                    | Constraints of channels belonging to the same connection             | 29  |  |

|    |                 | 3.2.4                                                                    | Constraints on pressure losses in channels                           | 30  |  |

| 4  | Prog            | Program performance optimization                                         |                                                                      |     |  |

|    | 4.1             |                                                                          |                                                                      |     |  |

|    | 4.2             | An advance estimate of the number of channels required in a connection 3 |                                                                      |     |  |

|    | 4.3             |                                                                          | ng part of channels of different connections that have the same pins | 43  |  |

| 5  | Calo            | culation                                                                 | n examples and analysis of experimental results                      | 44  |  |

|    | 5.1             |                                                                          | lation case design and experimental equipment setup                  | 44  |  |

|    |                 | 5.1.1                                                                    | Test case without a constraint of pressure losses                    | 44  |  |

|    |                 | 5.1.2                                                                    |                                                                      | 46  |  |

### Contents

|         |                                          | Experimental equipment setup                                               |    |

|---------|------------------------------------------|----------------------------------------------------------------------------|----|

| 5.2     | imental results and feasibility analysis | 48                                                                         |    |

|         | 5.2.1                                    | Experimental results of the test case without a constraint of pressure     |    |

|         |                                          | losses                                                                     | 48 |

|         | 5.2.2                                    | Experimental results of the test case with a constraint of pressure losses | 51 |

|         | 5.2.3                                    | Feasibility analysis                                                       | 52 |

| 5.3     | Short                                    | comings and future improvement directions                                  | 53 |

| List of | Figures                                  | 5                                                                          | 54 |

| List of | List of Tables                           |                                                                            |    |

| Bibliog | graphy                                   |                                                                            | 58 |

# 1 Introduction

## 1.1 Research background

Microfluidic chips are devices that incorporate micro-scale channels and chambers, designed to handle and analyze fluids in extremely small volumes. The core principle of these chips is the manipulation of fluid behavior at a micro-scale through tiny fluidic channels. Microfluidic technology allows experiments to be conducted in a minuscule space, which saves reagents, reduces costs, enhances reaction speeds, and improves efficiency. Commonly used in fields like chemical analysis, biological assays, and pharmaceutical development, microfluidic chips enable precise control and manipulation of minute samples such as cells, DNA molecules, or chemical reagents, providing a high level of automation and integration for experiments. By precisely controlling the flow, temperature, and chemical environment of fluids, microfluidic chips can simulate and analyze complex biochemical processes. For example, microfluidic chips can produce chemicals because the velocity and the property of reaction fluid can be precisely controlled. With the help of microfluidic chips, reactions will be carried out on a small scale and not require hands-on, saving raw materials and guaranteeing safety. For instance, a microfluidic chip can synthesize a common pharmaceutical, aspirin. The chip's channels are designed to mix acetic anhydride with salicylic acid, and an acid catalyzes the reaction within a controlled temperature environment. Due to the microscale environment, the reaction is highly efficient, and the aspirin produced can be collected continuously from the chip output. [1].

Currently, the majority of microfluidic chips are fabricated using soft lithography techniques. However, with the development of 3D printing technology and a more broader range of available printing materials, microfluidic chips can also be produced by 3D printing. Currently, the most commonly used method for 3D printing microfluidic chips is stereolithography(SLA). This is a widely used 3D printing technology for microfluidics, which uses a laser to cure liquid resin into solid plastic. SLA can produce high-resolution features suitable for the tiny channels and structures often required in microfluidic devices [2] [3].

3D printing technology stands to broaden the application of microfluidic chips beyond the reach of traditional photolithography due to several compelling reasons. Firstly, 3D printing allows for rapid prototyping, enabling researchers and developers to iterate design modifications swiftly and cost-effectively. This agility in design and testing significantly accelerates the development process. Secondly, 3D printing is not constrained by the layer-by-layer fabrication method inherent to photolithography, allowing for more complex, three-dimensional structures that can integrate multiple functions within a single chip. This capability can

lead to more sophisticated and multifaceted microfluidic devices. Thirdly, the materials available for 3D printing are diversifying, offering a range of properties such as flexibility, transparency, and chemical resistance that can be tailored to specific applications. Moreover, the accessibility of 3D printers increases the democratization of microfluidic chip fabrication, making it available to a broader audience and potentially spurring innovation. Lastly, the reduction in cost and time, coupled with the increase in design complexity, positions 3D-printed microfluidic chips as a versatile and attractive option for various applications in medical diagnostics, environmental monitoring, and educational purposes, among others.

Specifically, 3D-printed microfluidic chips have the following three adavantages compared to those produced by soft lithography.

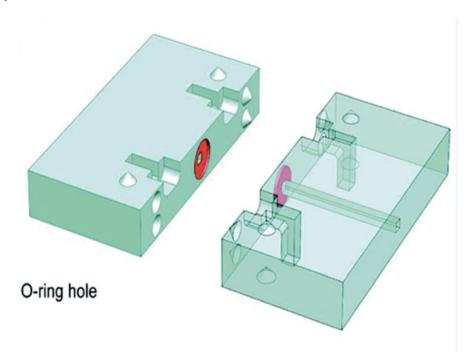

First, 3D-printed microfluidic chips have reliable connection ports. Sometimes, it is necessary to connect the microfluidic chip to other devices. For PDMS-based chips, the channels can be sealed to chips by inserting holes or using adhesive. However, this kind of channel intervention may lead to leakage or back pressure due to the lack of reliable connection protocols [4]. 3D-printed microfluidic chips can solve this problem by implementing connection mechanisms such as threaded porters that fit commercial finger-tight adapters, which soft lithography cannot achieve [5].

Figure 1.1: Example of connection - O-ring hole [6]

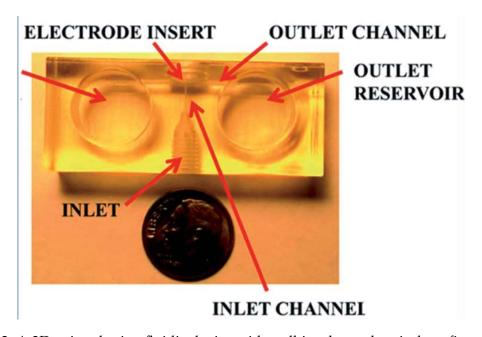

Second, 3D-printed microfluidic chips enable modular installation and disassembly of detectors and sensors. Electrochemical detection is widely used in microfluidic chips for

molecule detection. Nowadays, there are many PDMS-based microfluidic chips integrating electrodes inside. However, this kind of chip is disposable because, once the electrode inside fouls, the chip cannot work. In contrast, if people use 3D-printed microfluidic chips, they can assemble and disassemble the electrodes through threads, clean them, and reuse them [6].

Figure 1.2: A 3D-printed microfluidic device with wall-jet electrochemical configuration. [6]

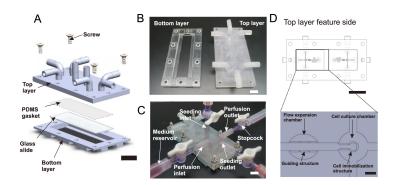

Last, 3D-printed microfluidic chips support a robust on-chip cell integration. At present, on-chip cell culture is a trendy technology. By controlling the flow of liquid, people can not only provide cells with a continuous supply of nutrients but also take away the waste produced by the cells from the culture environment. In addition, by controlling the speed of the fluid, people can also simulate the biological forces received by cells in the natural environment. Although there are already many PDMS-based microfluidic chips that can serve as a cell culture, 3D-printed microfluidic chips serving as a cell culture is more advantageous. For example, 3D-printed microfluidic chips can implement interface modularization, which is difficult for PDMS-based microfluidic chips to achieve. People can insert the cell culture dish into the chip as a module. If the culture dish is contaminated, people only need to replace the cell culture dish module instead of the entire equipment [6].

Figure 1.3: Design and instance of the 3D printed microfluidic spheroid culture system. [7]

Since 3D-printed microfluidic chips have many advantages over those manufactured by soft lithography technology, more and more industries will apply 3D-printed microfluidic chips. In this thesis, we mainly focus on the assisted design tool for 3D-printed microfluidic chips, aiming to make the design process of 3D-printed microfluidic chips less time-consuming and labor-intensive.

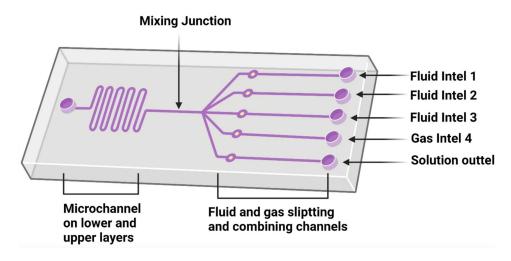

Figure 1.4: Example of microfluidic chip implementing simple mixing function [8]

#### 1.2 Research status

Currently, there are already two famous assisted design tools for 2D microfluidic chips, which can help us automatically generate the layout of modules and channels inside the chip. These two tools are first introduced below.

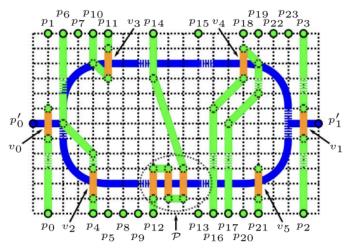

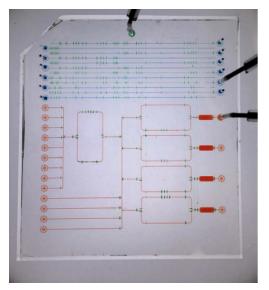

In 2017, the first automated design tool, which can be seamlessly connected with the microfluidic chip manufacturing process, was invented, called Columba. Columba constructs a module model library to simulate microfluidic elements involved in interactions precisely

and uses linear constraint programming to construct the overall layout of each module on the chip and the channels connecting each module with the help of Gurobi. Regarding the working process of this software, Columba takes a plain-text netlist as input, and its output is compatible with AutoCAD, which means the output can be directly used for mask fabrication [9].

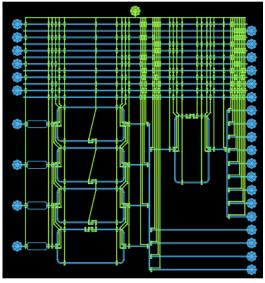

(a) Model example output by Columba 2.0.

(b) Fabricated chips based on the output model output instance.

Figure 1.5: Output of Columba 2.0 [9].

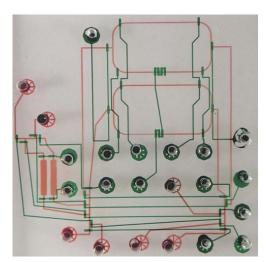

Furthermore, in 2018, to solve the excessive computational burden caused by large-size chip design, a new architectural framework, and a straight channel routing discipline were applied to Columba. Besides that, the new version of Columba also synthesizes multiplexers for efficient and reconfigurable valve control. With the help of the above methods, the new version of Columba can construct a chip layout design containing 200 modules within 3

#### minutes [10].

(b) Fabricated chips based on the output model output instance.

Figure 1.6: Output of Columba S [10].

As for assisted design tools for 3D-printed microfluidic chips, there are two popular: Flui3d and a program that can automatically design microfluidic chip layouts based on deep reinforcement learning. Through Flui3d, we can drag modules and channels in the visual interface to design the chip, which is intuitive. Besides that, Flui3d can generate an STL format file of the designed chip, which can be directly input into a 3D printer for production [11]. And about the program, users enter the selected modules and their corresponding size parameters into the program. Then, the program can output a chip design plan that includes the placement information about modules and channels [12].

We can notice that neither of the two tools mentioned above has the ability to automatically design a complete 3D-printed chip that has detailed placement information about both modules and channels if users specify the pressure loss between two modules. Existing methodologies for channel layout design that contain constraints on pressure loss are predominantly manual, leading to a high propensity for errors and significant demands on time. To address the current deficit in design automation tools, which lack the capability to determine the precise placement of channels within microfluidic chips based on the interconnectivity of modules and the requirement for pressure loss, this thesis proposes the development of an innovative program.

This thesis endeavor seeks to bridge this gap by introducing a software solution specifically engineered to autonomously generate channel configurations for 3D-printed microfluidic

chips that meet the requirement for pressure loss between modules by users. The program is designed to accept as input the spatial placement of modules, their interconnecting relationships, and desired pressure loss between modules and subsequently outputs the optimal arrangement of channels. This work aims to significantly enhance the efficiency and accuracy of microfluidic chip design.

## 1.3 Research significance

In this thesis, a program is designed that uses both linear constraint programming and nonlinear constraint programming with the help of Gurobi, a large-scale mathematical programming optimizer, to generate channel layouts between specified input and output ports automatically according to the connection relationship of the module pins. In addition, some optimizations are made to speed up the program, such as using a modified A\* algorithm to estimate the necessary number of turns in the channel, which can help reduce the number of parameters in the model.

With the help of this program, as long as the placement information of each module on the chip and the connection relationship between modules are given, the layouts of the channels in the chip can be calculated quickly. After testing, this program can complete the channel layout design of a three-layer chip containing six components within one second. Besides that, if the pressure and the steady flow velocity on the inlet side are specified, and a request on the flow pressure at the outlet is made, the program can also generate a path that meets the pressure constraints by calculating with the Navier-Stokes equation.

In conclusion, this program can automatically generate the connection path data of each module pin in the chip quickly and easily, which can be used for 3D printing, saving time and labor costs.

# 2 Constraint Programming

Before we discuss the implementation details of the program, first introduce the basic knowledge about constraint programming because this is the basic idea of solving the problem in our program.

## 2.1 Definition of constraint programming

The working principle of constraint programming is that given a set of variables and possible values for each variable, the constraint programming can reduce the set of values every variable can take according to given constraints and then find a viable solution [13].

In summary, a standard constraint programming problem consists of three parts:

- A set of variables  $X = \{x_1, x_2, ..., x_n\}$

- A set of domains D =  $\{d_1, d_2, ..., d_n\}$

- A set of constraints  $C = \{c_1, c_2, ..., c_m\}$

# 2.2 Types of constraint programming

According to the exponent of the variable in the constraint, people divide constraint programming into two categories: linear constraint programming and non-linear constraint programming [14].

Linear constraint programming refers to the situation in which the exponents of variables in constraints all equal one. See Equation 2.1.

And non-linear constraint programming refers to a situation in which some variables' exponents exist that do not equal one. See Equation 2.2.

$$Ax + b = 0 (2.1)$$

$$Ax^2 + bx + c = 0 (2.2)$$

## 2.3 Methods for solving constraint programming problems

Currently, there are three main methods to solve the constraint satisfaction problem: backtracking search, local search, and dynamic programming.

### 2.3.1 Backtracking search

Backtracking search is a primary method to solve constraint satisfaction problems, and its essence is a depth-first search algorithm. The backtracking search consists of three steps:

- Start with an empty assignment.

- Assign a possible value to a variable at each step.

- Undo the last assignment operation and continue exploring when it is impossible to achieve a solution in the current situation.

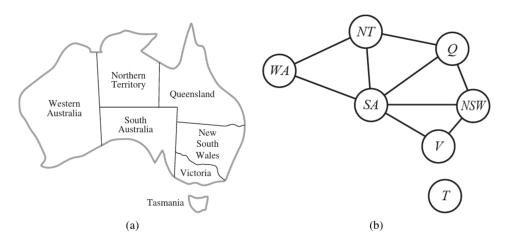

Figure 2.1: An example solved by backtracking search. (a) The map of Australia. (b) The connection relationship between Australia's different regions. The goal is to color every region and ensure that neighboring regions have different colors. [15]

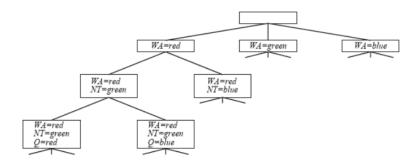

Figure 2.2: Part of the search tree for the coloring problem. [15]

#### 2.3.2 Local search

Local search algorithm solves constraint satisfaction problems effectively through a complete state formulation. First, the algorithm will assign a possible value within the value domain to each variable, during which the assignment is likely to conflict with certain constraints. Second, this algorithm will change the value of one variable at one time until there are no conflicts between assignments and constraints [15] [16].

The min-conflicts algorithm is a popular algorithm that uses local search to solve constraint satisfaction problems. The underlying principle of this algorithm is assigning values that cause minimal conflicts with constraints to the variable each time [15].

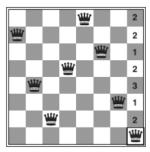

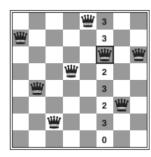

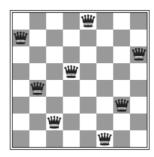

The following Figure 2.3 introduces a classic problem - 8-queens problem solved by the min-conflicts constraints. The 8-queens problem is to place the 8-queens in appropriate positions on the chess board so that they cannot attack each other.

Figure 2.3: 8-queens problem. The numbers in the chessboard grid refer to the number of constraints conflicts that occur when the queen of the current column moves to each position. And the algorithm tends to move the queen to the grid with the least number of constraints conflicts. [15]

After many experiments, it has been proven that the min-conflicts algorithm can effectively solve many CSP problems. For example, the min-conflicts algorithm has been used to schedule observations for the Hubble Space Telescope, reducing the scheduling time from 3 weeks to 10 minutes [15].

#### 2.3.3 Dynamic programming

Dynamic programming is a powerful technique used to solve constraint satisfaction problems efficiently. In computer science and optimization, constraint satisfaction problems involve finding a solution that meets a set of constraints or conditions. Dynamic programming offers a practical approach to tackling these problems by breaking them down into smaller subproblems and solving them systematically and organized [17].

The core idea of dynamic programming involves solving complex problems by dividing them into more straightforward, manageable subproblems. Each subproblem is decrypted only once, and its solution is stored in a table, ensuring that overlapping subproblems are addressed efficiently. By using this approach, dynamic programming significantly reduces redundant calculations and computational effort, resulting in a more optimized and quicker resolution of the overall problem.

In constraint satisfaction problems, dynamic programming helps find an optimal solution that satisfies given constraints. It achieves this by iteratively solving subproblems and utilizing the keys to build the answer for the entire problem. This approach ensures that regulations are met and that the resulting solution is the most efficient and optimal within the given conditions.

By employing dynamic programming, the computational complexity of constraint satisfaction problems is substantially reduced, making it a fundamental technique for solving a wide range of real-world optimization challenges. Its applications extend across various domains, including artificial intelligence, operations research, economics, and many more, providing an invaluable tool for addressing complex problems and enhancing decision-making processes.

# 3 Mathematical modeling of microfluidic chips

As can be seen chapter 2, constraint programming is expressed by mathematical expressions. Therefore, before introducing how the program establishes constraints on modules and channels, we first need to introduce how to mathematically model chips, modules, and channels, that is, express their boundaries in mathematical form.

In this chapter, we will first introduce the mathematical modeling of chips, modules, and channels. It should be noted that in the mathematical modeling of microfluidic chips, certain idealizations are employed for simplicity. For simplicity in mathematical modeling, channels are typically represented as circular pipes, despite often having square cross-sections in actual microfluidic chips. This approximation simplifies the computational process and typically yields results that do not significantly deviate from actual conditions. And chips and modules are modeled as rectangles. In addition, we also suppose that the flow in channels is laminar because microfluidic flow usually has a low Reynolds number.

Then, we will introduce the fundamental constraints on modules and channels.

## 3.1 Chip modeling

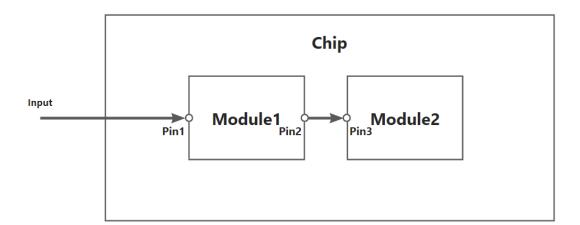

Chips consist of modules and channels, and modules contain pins. Channels connect different modules via pins to work together to complete tasks. The modeling of modules, pins, and channels will be introduced below.

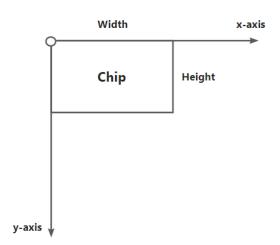

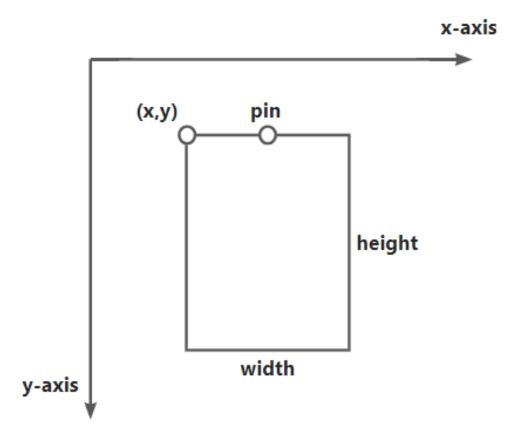

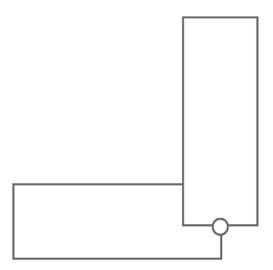

First, the coordinate's origin and positive direction should be determined before modeling. As shown in Figure 3.1, the coordinate system's origin coincides with the chip's upper left corner endpoint. The side representing the width of the chip is parallel to the X-axis, and the side representing the height is parallel to the Y-axis. In addition, the coordinate system used in this thesis has the positive direction of the X-axis on the right and the positive direction of the Y-axis on the bottom.

Figure 3.1: The coordinate used in this thesis.

## 3.1.1 Module modeling

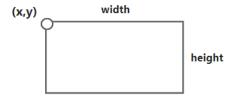

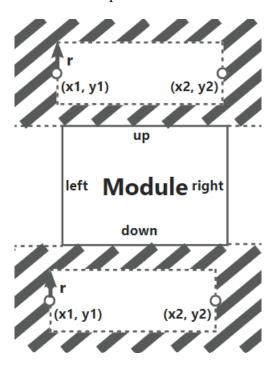

Modules include chambers, mixers, filters, and any other functional components inside a chip. The module of the chip has four main parameters: the coordinates of the upper left corner vertex, the module's length and width, and the module's direction. And after determining the coordinates of the module's upper left corner endpoint and the module's length and width, the module's upper, lower, left, and right boundary values can be determined based on the module's direction.

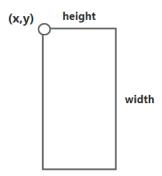

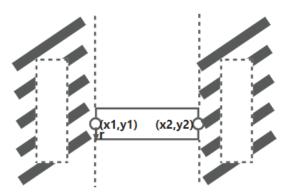

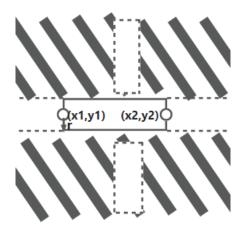

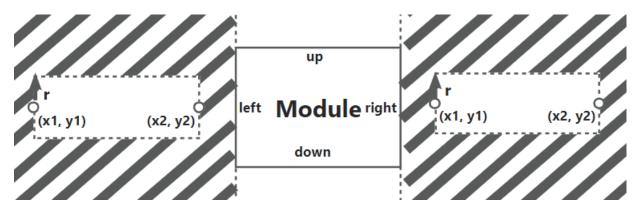

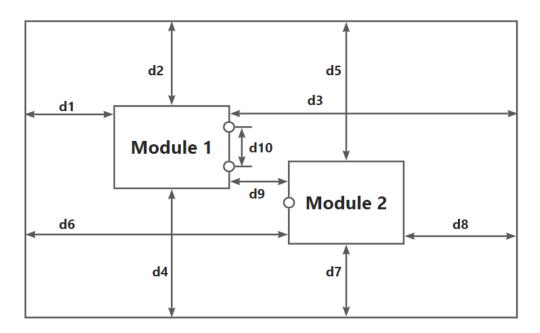

According to the module's direction, the discussion about modules' boundaries can be divided into two situations: 0 degree and 180 degrees are one situation, 90 degrees and 270 degrees are the other situation. Figure 3.2 and Equation 3.1 introduce the modules upper, lower, left, and right boundaries when the module's orientation is 0 degree or 180 degrees. Figure 3.3 and Equation 3.2 introduce the values of the module's boundaries when module's orientation is 90 degrees or 270 degrees. Among them, x and y refer to the horizontal and vertical coordinates of the upper left corner endpoint of the module.

Figure 3.2: The state of module when the orientation is 0 degree or 180 degrees.

$$\begin{cases} left = x \\ right = x + width \\ up = y \\ down = y + height \end{cases}$$

(3.1)

Figure 3.3: The state of module when the orientation is 90 degrees or 270 degrees.

$$\begin{cases} left = x \\ right = x + height \\ up = y \\ down = y + width \end{cases}$$

(3.2)

## 3.1.2 Pin modeling

Pins are ports that allow modules to interact with the outside world. Each module in the chip has many pins that can interact with other modules. Pins in this thesis have two main parameters: horizontal and vertical coordinate position offsets relative to the upper left corner endpoint of the module to which they belong. And through these two offset values, the absolute coordinates of each pin can be calculated.

The following is an example: Suppose there is a module with width w, height h, and orientation 0 degree. The module has a pin with a horizontal relative offset of w/2 and a vertical relative offset of 0. The location of the pin is shown in Figure 3.4.

Figure 3.4: Example of a pin's location.

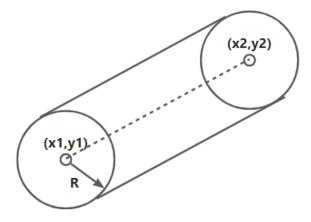

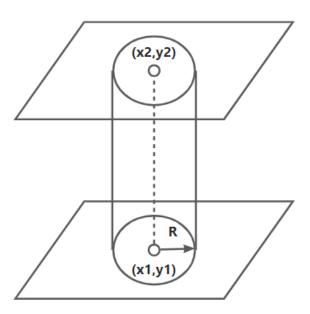

### 3.1.3 Channel modeling

Channels are mainly responsible for connecting pins or pins to external pins to ensure interactions between modules. There are two kinds of channels: one is a channel that connects on the same horizontal layer, and the other is a channel that connects two pins on different layers.

Although in reality, the channels of microfluidic chips are usually square, in this thesis, channels are modeled as round shape tubes because the primary interest is in understanding the average behavior of the fluid rather than edge effects or corner vortices that might develop in a square channel so that a circular approximation could be sufficiently accurate. Experimental evidence suggests that when operating within sufficiently low Reynolds number regimes, the discrepancy in pressure loss between square and circular tubes is confined to a marginal variation of less than 5% [18]. Besides that, circular channels have well-established and straightforward equations for fluid dynamics, making it easier to calculate fluid flow pressure losses later.

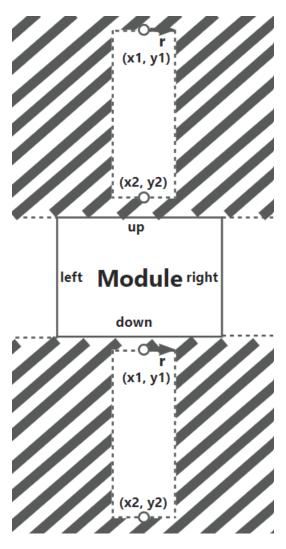

And in this thesis, channels have seven main parameters: the horizontal and vertical coordinates of the two end points of the circular tube, the radius of the circular tube, the

connection which the channel belongs to and the index number in the connection. The connection mentioned contains the connection information of a pair of pins, including the detailed information of all channels used to achieve the relationship between these two pins. And if a channel connects two different layers, it will have two additional parameters: information about two connected layers.

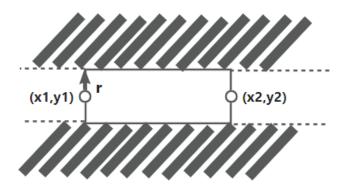

Figure 3.5: Schematic diagram of channel modeling on the same layer.

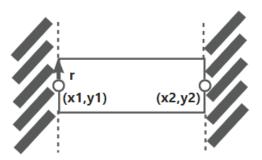

Figure 3.6: Schematic diagram of channel modeling on different layers.

## 3.2 Constraint modeling

This thesis mainly studies constraints related to channels, which include the primary constraints of a channel itself, the constraints of non-collision between channels and channels, channels and modules, the constraints of channels belonging to the same connection, and the pressure constraints of the liquid flowing in a channel.

#### 3.2.1 Basic constraints of a channel

The basic constraints of a channel can be divided into two situations according to the channel type: channels connecting pins on the same layer and channels connecting pins on different layers, which are discussed separately below.

#### Basic constraints of a channel connecting pins on the same layer

A channel connecting pins on the same layer can only be parallel to the x-axis or y-axis of the coordinate system and can not exceed the chip area. These constraints can be expressed by Equation 3.4, Equation 3.5, Equation 3.6, Equation 3.7 and Equation 3.8:

$$(y_1 = y_2) \lor (x_1 = x_2) \tag{3.3}$$

$$\begin{cases} y_1 \le y_2 + b_1 M \\ y_2 \le y_1 + b_1 M \end{cases}$$

(3.4)

$$\begin{cases} x_1 \le x_2 + b_2 M \\ x_2 \le x_1 + b_2 M \end{cases}$$

(3.5)

$$\begin{cases}

r \leq y_1 + b_1 M \\

y_1 \leq H - r + b_1 M \\

0 \leq x_1 + b_1 M \\

x_1 \leq W + b_1 M \\

0 \leq x_2 + b_1 M \\

x_2 \leq W + b_1 M

\end{cases}$$

(3.6)

$$\begin{cases} r \leq x_1 + b_2 M \\ x_1 \leq W - r + b_2 M \\ 0 \leq y_1 + b_2 M \\ y_1 \leq H + b_2 M \\ 0 \leq y_2 + b_2 M \\ y_2 \leq H + b_2 M \end{cases}$$

(3.7)

$$b_1 + b_2 = 1 (3.8)$$

where  $(x_1, y_1)$  and  $(x_2, y_2)$  represent the coordinates of the two endpoints of the channel,  $b_1$  and  $b_2$  are two auxiliary binary variables that determine whether the channel is parallel to the x-axis or the y-axis: if  $b_1$  is set to 0, it means that  $y_1$  must equal  $y_2$ , and the channel is parallel to the x-axis, and conversely if  $b_2$  is set to 0, it means that  $x_1$  must equal  $x_2$  and the channel is parallel to the y-axis, and M is a very large constant. In addition, r represents the channel's radius, and W and H represent the width and height of the chip, respectively.

#### Basic constraints of a channel connecting pins on different layers

A channel connecting pins on different layers must be perpendicular to the layers of the chip and can not exceed the area of the chip. These constraints can be expressed by Equation 3.9 and Equation 3.10:

$$\begin{cases} x_1 = x_2 \\ y_1 = y_2 \end{cases}$$

(3.9)

$$\begin{cases}

r \le x_1 \\

x_1 \le W - r \\

r \le y_1 \\

y_1 \le H - r

\end{cases}$$

(3.10)

where  $(x_1, y_1)$  and  $(x_2, y_2)$  represent the coordinates of the two endpoints of the channel, and W, H, and r represent the chip's width, height and the channel's radius, respectively.

#### 3.2.2 Constraints of non-collision

Constraints of non-collision require that channels and modules on the same layer do not overlap. The following is a detailed introduction to the two situations where channels and channels on the same layer do not overlap, and channels and modules on the same layer do not overlap.

#### Constraints of non-collision between channels on the same layer

Since the current discussion is about two channels, according to the previous formulas Equation 3.4 to Equation 3.8, it can be seen that the first and second channels each have two auxiliary binary variables, of which the first channel owns  $b_{1,1}$  and  $b_{1,2}$  and the second channel holds  $b_{2,1}$  and  $b_{2,2}$ . When  $b_{1,1}$  and  $b_{2,1}$  are set to 0, it means two channels are parallel to the x-axis, and when  $b_{1,2}$  and  $b_{2,2}$  are set to 0, it means two channels are parallel to the y-axis.

And Non-collision between channels on the same layer can be further divided into three situations:

- Two channels are parallel to the x-axis.

- Two channels are parallel to the y-axis.

- One channel is parallel to the x-axis, and the other is parallel to the y-axis.

In the following paragraphs, the constraint construction in these three cases will be detailed.

First, the constraints about two channels parallel to the x-axis will be introduced.

This thesis uses two sets of constraints to cover all the possibilities of relative positions between two channels parallel to the x-axis on the same layer. Figure 3.7, Equation 3.11 and Equation 3.12 describe the first set of constraints, and Figure 3.8, Equation 3.13 and Equation 3.14 represent the second:

Figure 3.7: First set of constraints(Top view of the chip layer). The shadow in the figure is the position the second channel can occupy using the first set of constraints.

$$r + r' \le |y_1 - y_1'| \tag{3.11}$$

$$\begin{cases}

r + r' \le y_1 - y_1' + b_1 M + b_{1,1} M + b_{2,1} M \\

y_1 - y_1' \le -r - r' + b_2 M + b_{1,1} M + b_{2,1} M

\end{cases}$$

(3.12)

Figure 3.8: Second set of constraints(Top view of the chip layer). The shadow in the figure is the position the second channel can occupy using the second set of constraints.

$$((x_{1}^{'} \leq x_{1}) \land (x_{2}^{'} \leq x_{1}) \land (x_{1}^{'} \leq x_{2}) \land (x_{2}^{'} \leq x_{2})) \lor ((x_{1} \leq x_{1}^{'}) \land (x_{2} \leq x_{1}^{'}) \land (x_{1} \leq x_{2}^{'}) \land (x_{2} \leq x_{2}^{'}))$$

$$(3.13)$$

$$\begin{cases} x_{1}^{'} \leq x_{1} + b_{3}M + b_{1,1}M + b_{2,1}M \\ x_{2}^{'} \leq x_{1} + b_{3}M + b_{1,1}M + b_{2,1}M \\ x_{1}^{'} \leq x_{2} + b_{3}M + b_{1,1}M + b_{2,1}M \\ x_{2}^{'} \leq x_{2} + b_{3}M + b_{1,1}M + b_{2,1}M \\ x_{1} \leq x_{1}^{'} + b_{4}M + b_{1,1}M + b_{2,1}M \\ x_{2} \leq x_{1}^{'} + b_{4}M + b_{1,1}M + b_{2,1}M \\ x_{1} \leq x_{2}^{'} + b_{4}M + b_{1,1}M + b_{2,1}M \\ x_{2} \leq x_{2}^{'} + b_{4}M + b_{1,1}M + b_{2,1}M \end{cases}$$

$$(3.14)$$

$$b_1 + b_2 + b_3 + b_4 = 3 (3.15)$$

where r and r' represent the first and second channels' radius, respectively.  $(x_1,y_1)$  and  $(x_2,y_2)$  represent the first channel's two endpoints' coordinates, and  $(x_1^{'},y_1^{'})$  and  $(x_2^{'},y_2^{'})$  represent the second one's. In addition,  $b_1$ ,  $b_2$ ,  $b_3$ , and  $b_4$  are four auxiliary binary variables to determine which kind of constraints work, and M is a huge constant. And the reason for adding  $b_{1,1}M + b_{2,1}M$  after each equation is that if two channels are not all parallel to the x-axis, which means  $b_{1,1}$  and  $b_{2,1}$  are not all equal to 0, the constraints will always be satisfied.

Second, the thesis will introduce the constraints of two channels all parallel to the y-axis. As with the case where both channels are parallel to the x-axis, the thesis also uses two alternative sets of constraints to cover all cases. Figure 3.9, Equation 3.16 and Equation 3.17 describe the first set of constraints, and Figure 3.10, Equation 3.18 and Equation 3.19 represent the second:

Figure 3.9: First set of constraints(Top view of the chip layer). The shadow in the figure is the position the second channel can occupy using the first set of constraints.

$$r + r' \le |x_1 - x_1'| \tag{3.16}$$

$$\begin{cases}

r + r' \le x_1 - x_1' + b_5 M + b_{1,2} M + b_{2,2} M \\

x_1 - x_1' \le -r - r' + b_6 M + b_{1,2} M + b_{2,2} M

\end{cases}$$

(3.17)

Figure 3.10: Second set of constraints(Top view of the chip layer). The shadow in the figure is the position the second channel can occupy using the second set of constraints.

$$((y_{1}^{'} \leq y_{1}) \land (y_{2}^{'} \leq y_{1}) \land (y_{1}^{'} \leq y_{2}) \land (y_{2}^{'} \leq y_{2})) \lor ((y_{1} \leq y_{1}^{'}) \land (y_{2} \leq y_{1}^{'}) \land (y_{1} \leq y_{2}^{'}) \land (y_{2} \leq y_{2}^{'}))$$

$$(3.18)$$

$$\begin{cases} y_{1}^{'} \leq y_{1} + b_{7}M + b_{1,2}M + b_{2,2}M \\ y_{2}^{'} \leq y_{1} + b_{7}M + b_{1,2}M + b_{2,2}M \\ y_{1}^{'} \leq y_{2} + b_{7}M + b_{1,2}M + b_{2,2}M \\ y_{2}^{'} \leq y_{2} + b_{7}M + b_{1,2}M + b_{2,2}M \\ y_{1} \leq y_{1}^{'} + b_{8}M + b_{1,2}M + b_{2,2}M \\ y_{2} \leq y_{1}^{'} + b_{8}M + b_{1,2}M + b_{2,2}M \\ y_{1} \leq y_{2}^{'} + b_{8}M + b_{1,2}M + b_{2,2}M \\ y_{2} \leq y_{2}^{'} + b_{8}M + b_{1,2}M + b_{2,2}M \\ y_{2} \leq y_{2}^{'} + b_{8}M + b_{1,2}M + b_{2,2}M \end{cases}$$

$$(3.19)$$

$$b_5 + b_6 + b_7 + b_8 = 3 ag{3.20}$$

where r and r' represent the first and second channels' radius, respectively.  $(x_1,y_1)$  and  $(x_2,y_2)$  represent the first channel's two endpoints' coordinates, and  $(x_1^{'},y_1^{'})$  and  $(x_2^{'},y_2^{'})$  represent the second one's. In addition,  $b_5$ ,  $b_6$ ,  $b_7$ , and  $b_8$  are four auxiliary binary variables to determine which kind of constraints work, and M is a huge constant. And the reason for adding  $b_{1,2}M + b_{2,2}M$  after each equation is that if two channels are not all parallel to the y-axis, which means  $b_{1,2}$  and  $b_{2,2}$  are not all equal to 0, the constraints will always be satisfied.

Last, the thesis will introduce the constraints when one channel is parallel to the x-axis and the other is parallel to the y-axis. This situation differs from the previous two situations, where the two channels are parallel. One prejudgment and two sets of constraints are used to cover all possibilities.

Before adding two sets of constraints on a pair of channels, check whether the two channels belong to the same connection and have adjacent index numbers, which means these two channels are connected. If the pair of channels meets this prerequisite, the two sets of constraints will not be added. The reason for adding this prejudgment condition is to consider the situation shown in Figure 3.11. If this prerequisite is not added, two mutually perpendicular channels will never be allowed to connect.

Figure 3.11: A situation where two channels are perpendicular and connected.

On the contrary, if this prerequisite is not satisfied, two sets of constraints will be added to these two channels. Figure 3.12, Equation 3.21 and Equation 3.22 describe the first set of constraint, and Figure 3.13, Equation 3.23 and Equation 3.24 describe the second set of constraints:

Figure 3.12: First set of constraints(Top view of the chip layer). The shadow in the figure is the position the second channel can occupy using the first set of constraints and dashed rectangles are examples of possible channel placements.

$$((x_{1}^{'}+r^{'} \leq x_{1}) \wedge (x_{1}^{'}+r^{'} \leq x_{2})) \vee ((x_{1}^{'}-r^{'} \geq x_{1}) \wedge (x_{1}^{'}-r^{'} \geq x_{2}))$$

(3.21)

$$\begin{cases} x_{1}^{'} + r^{'} \leq x_{1} + b_{9}M + b_{1,1}M + b_{2,2}M \\ x_{1}^{'} + r^{'} \leq x_{2} + b_{9}M + b_{1,1}M + b_{2,2}M \\ x_{1} \leq x_{1}^{'} - r^{'} + b_{10}M + b_{1,1}M + b_{2,2}M \\ x_{2} \leq x_{1}^{'} - r^{'} + b_{10}M + b_{1,1}M + b_{2,2}M \end{cases}$$

(3.22)

Figure 3.13: Second set of constraints(Top view of the chip layer). The shadow in the figure is the position the second channel can occupy using the second set of constraints and dashed rectangles are examples of possible channel placements.

$$((y_{1}^{'}+r\leq y_{1})\wedge(y_{2}^{'}+r\leq y_{1}))\vee((y_{1}^{'}-r\geq y_{1})\wedge(y_{2}^{'}-r\geq y_{1}))$$

(3.23)

$$\begin{cases} y'_{1} + r \leq y_{1} + b_{11}M + b_{1,1}M + b_{2,2}M \\ y'_{2} + r \leq y_{1} + b_{11}M + b_{1,1}M + b_{2,2}M \\ y_{1} \leq y'_{1} - r + b_{12}M + b_{1,1}M + b_{2,2}M \\ y_{1} \leq y'_{2} - r + b_{12}M + b_{1,1}M + b_{2,2}M \end{cases}$$

$$(3.24)$$

$$b_9 + b_{10} + b_{11} + b_{12} = 3 (3.25)$$

where r and r' represent the first and second channels' radius, respectively.  $(x_1,y_1)$  and  $(x_2,y_2)$  represent the first channel's two endpoints' coordinates, and  $(x_1^{'},y_1^{'})$  and  $(x_2^{'},y_2^{'})$  represent the second one's. In addition,  $b_9$ ,  $b_{10}$ ,  $b_{11}$ , and  $b_{12}$  are four auxiliary binary variables to determine which kind of constraints work, and M is a huge constant. And the reason for adding  $b_{1,1}M + b_{2,2}M$  after each equation is that if two channels are not perpendicular, which means  $b_{1,1}$  and  $b_{2,2}$  are not all equal to 0, the constraints will always be satisfied.

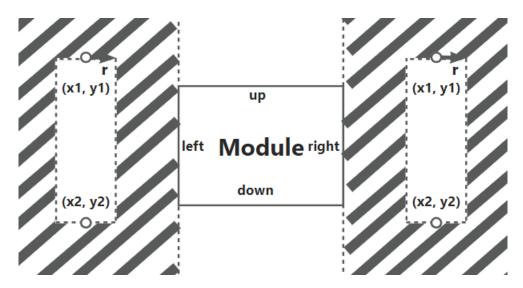

#### Constraints of non-collision between channels and modules on the same layer

Since the current discussion is about one channel, according to the previous formulas Equation 3.4 to Equation 3.8, it can be seen that the channel has two auxiliary binary variables, represented by  $b_{1,1}$  and  $b_{1,2}$ . When  $b_{1,1}$  is set to 0, the channel is parallel to the x-axis, and when  $b_{1,2}$  is set to 0, the channel is parallel to the y-axis. This thesis will discuss the situation according to whether the channel is parallel to the x-axis or the y-axis.

First, when the channel is parallel to the x-axis, two sets of constraints will be used to cover all the possible placements of the channel, which will not cause a collision with the module. These two sets of constraints define the space that can be occupied by the channel in the vertical (top and bottom) and horizontal (left and right) directions.

Figure 3.14, Equation 3.26 and Equation 3.27 describe the constraints on the space that can be occupied above and below the module, and Figure 3.15, Equation 3.28 and Equation 3.29 describe the constraints on the available space to the left and to the right of the module:

Figure 3.14: First set of constraints(Top view of the chip layer). The shadow in the figure is the position the channel can occupy using the first set of constraints and dashed rectangles are examples of possible channel placements.

$$(y_1 + r \le up) \lor (y_1 - r \ge down) \tag{3.26}$$

$$\begin{cases} y_1 + r \le up + b_{1,1}M + b_1M \\ down \le y_1 - r + b_{1,1}M + b_2M \end{cases}$$

(3.27)

Figure 3.15: Second set of constraints(Top view of the chip layer). The shadow in the figure is the position the channel can occupy using the second set of constraints and dashed rectangles are examples of possible channel placements.

$$((x_1 \le left) \land (x_2 \le left)) \lor ((x_1 \ge right) \land (x_2 \ge right))$$

(3.28)

$$\begin{cases} x_{1} \leq left + b_{1,1}M + b_{3}M \\ x_{2} \leq left + b_{1,1}M + b_{3}M \\ right \leq x_{1} + b_{1,1}M + b_{4}M \\ right \leq x_{2} + +b_{1,1}M + b_{4}M \end{cases}$$

(3.29)

$$b_1 + b_2 + b_3 + b_4 = 3 (3.30)$$

Where r represents the channel's radius, and  $(x_1,y_1)$  and  $(x_2,y_2)$  represent the two endpoints' coordinates of the channel. Besides that, left, right, up, and down refer to the values of the four boundaries of the module, respectively. And  $b_1$ ,  $b_2$ ,  $b_3$ , and  $b_4$  are four auxiliary binary variables that determine the channel will occupy which location relative to the module. For example, if  $b_1$  is set to 1, the channel is above the module. Last but not least, the reason for adding  $b_{1,1}M$  to each equation is to ensure the constraints only work when the channel is parallel to the x-axis, which means  $b_{1,1}$  equals 0.

Second, if the channel is parallel to the y-axis, which is the same as parallel to the x-axis, two sets of constraints are adequate to cover all the free space above, below, left, and right of the module.

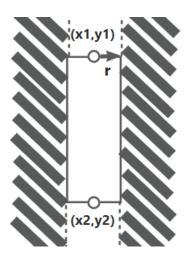

The first set of constraints is represented by Figure 3.16, Equation 3.31 and Equation 3.32, and Figure 3.17, Equation 3.33 and Equation 3.34 represents the situation where the second set of constraints considers:

Figure 3.16: First set of constraints(Top view of the chip layer). The shadow in the figure is the position the channel can occupy using the first set of constraints and dashed rectangles are examples of possible channel placements.

$$((y_1 \le up) \land (y_2 \le up)) \lor ((y_1 \ge down) \land (y_2 \ge down))$$

(3.31)

$$\begin{cases} y_1 \leq up + b_{1,2}M + b_5M \\ y_2 \leq up + b_{1,2}M + b_5M \\ down \leq y_1 + b_{1,2}M + b_6M \\ down \leq y_2 + b_{1,2}M + b_6M \end{cases}$$

(3.32)

Figure 3.17: Second set of constraints(Top view of the chip layer). The shadow in the figure is the position the channel can occupy using the second set of constraints and dashed rectangles are examples of possible channel placements.

$$(x_1 + r \le left) \lor (x_1 - r \ge right) \tag{3.33}$$

$$\begin{cases}

x_1 + r \le left + b_{1,2}M + b_7M \\

right \le x_1 - r + b_{1,2}M + b_8M

\end{cases}$$

(3.34)

$$b_5 + b_6 + b_7 + b_8 = 3 (3.35)$$

Where r represents the channel's radius, and  $(x_1,y_1)$  and  $(x_2,y_2)$  represent the two endpoints' coordinates of the channel. Besides that, left, right, up, and down refer to the values of the four boundaries of the module, respectively. And  $b_5$ ,  $b_6$ ,  $b_7$ , and  $b_8$  are four auxiliary binary variables that determine the channel will occupy which location relative to the module. For example, if  $b_5$  is set to 1, the channel is above the module. Last but not least, the reason for adding  $b_{1,2}M$  to each equation is to ensure the constraints only work when the channel is parallel to the y-axis, which means  $b_{1,2}$  equals 0.

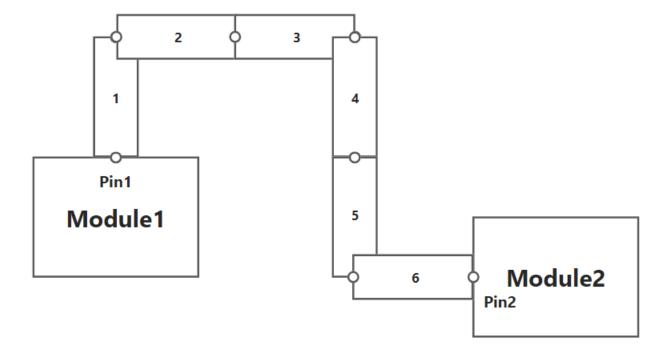

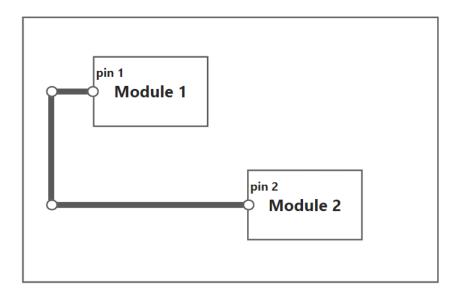

### 3.2.3 Constraints of channels belonging to the same connection

The connection mentioned here means a connection between two pins and a set of many channels is needed instead of just one channel to accomplish this connection. This subsection mainly focuses on constraints about channels within the same set.

It is required that the first endpoint of the first channel in a set of channels must coincide with the first pin, and the second endpoint of the last channel in the same set must coincide with the second pin. In addition, these channels in the same set must be guaranteed to be connected end to end. That is, the second endpoint of the previous channel must coincide with the first endpoint of the following channel.

The constraints are shown in Figure 3.18, Equation 3.36 and Equation 3.37:

Figure 3.18: A connection example where a set of six channels realizes the connection work of two pins.

$$\begin{cases} x_0 = pin_1 x \\ y_0 = pin_1 y \\ x'_{n-1} = pin_2 x \\ y'_{n-1} = pin_2 y \end{cases}$$

(3.36)

$$\begin{cases} x_{i}^{'} = x_{i+1} \\ y_{i}^{'} = y_{i+1} \end{cases} \qquad i = 0, 1, \dots, n-1$$

(3.37)

where n represents the the number of channels in a set, and  $(x_i, y_i)$  and  $(x_i', y_i')$  express the coordinates of the first endpoint and the second endpoint in the i-th channel, respectively. In addition, the coordinates of two pins are represented by  $(pin_1x, pin_1y)$  and  $(pin_2x, pin_2y)$ .

#### 3.2.4 Constraints on pressure losses in channels

The program described in this thesis can specifically design the wiring layout of channels based on the user's expectations for the fluid pressure at a particular output pin. The prerequisite is that users provide the input pressure for the channels, the expected steady flow rate, and the density and dynamic viscosity of the liquid flowing through the channels.

Figure 3.19: An example of constraints on pressure losses. The input fluid pressure is given, and now users make expectations on the liquid pressure at Pin3.

The idea of implementing this function is that the inlet pressure and the expected outlet pressure are already known. Therefore, the pressure that should be lost when the fluid flows in the channels can be calculated. Based on the pressure that should be lost in the channel flow, the total length of the liquid that should flow in the channel and how many right-angle turns it should make in the channel can be calculated. These lengths and the number of turns

can be used as constraints to generate the final channel layout.

First, the thesis will introduce the calculation method of pressure losses when liquid flows in a straight channel and when a channel turns 90 degrees.

#### Pressure losses when liquid flows in a straight channel

In the thesis, the pressure losses when fluid flows through straight channels are calculated by the Navier-Stokes equation.

And before using the Navier-Stokes equation, three assumptions are made. These three assumptions and their rationality are explained below.

The first assumption is that the fluid flowing in channels is an incompressible Newtonian fluid because microfluidic chips typically operate at small length scales, such as micrometers or nanometers. At these scales, the fluid's volume or density changes as it flows through the device are negligible. Therefore, the fluid can be approximated as incompressible, adhering to the assumption of constant density. Besides that, many microfluidic applications involve fluids with relatively low concentrations of solutes or particles, and the shear rates experienced in microfluidic channels are often within a range where the fluid behaves as a Newtonian fluid. The assumption of constant viscosity simplifies the mathematical modeling of fluid flow in microfluidic channels, making it easier to predict and analyze flow behavior.

The second assumption is that the fluid flowing in channels is laminar because, in microfluidic chips, the flow velocities and channel dimensions are small, resulting in low Reynolds numbers, and at low Reynolds numbers, the flow tends to be laminar and predictable, with viscous forces dominating over inertial forces. In addition, microfluidic channels have small cross-sectional dimensions, often in the micrometer range, and the small channel sizes constrain the fluid flow and inhibit the development of turbulent flow, promoting laminar behavior. Last but not least, flow rates in microfluidic chips are usually low, contributing to the development and maintenance of laminar flow. Low flow rates reduce the likelihood of turbulence and mixing between different fluid layers, resulting in well-defined, orderly flow patterns [19].

The last assumption is that no-slip condition takes effect, which means the velocity of the fluid at the channels' wall is 0. The reason why this assumption can be made is that in microfluidic devices, the channels are microscopic, typically in the range of micrometers or smaller, and the fluid molecules in contact with the solid surface experience a significant amount of interaction and friction due to their proximity to the solid material. At this scale, the effects of molecular interactions dominate and tend to cause the fluid to stick to the surface, adhering to a no-slip condition.

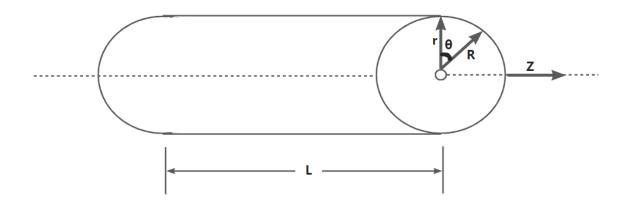

Based on these three assumptions, the Navier-Stokes equation is shown in Equation 3.38 and a schematic diagram of fluid flow in a channel is shown in Figure 3.20:

$$\rho(\frac{\partial \boldsymbol{u}}{\partial t} + \boldsymbol{u} \cdot \nabla \boldsymbol{u}) = -\nabla p + \eta \nabla^2 \boldsymbol{u} + \boldsymbol{f}$$

(3.38)

Figure 3.20: A schematic diagram of fluid flow in a microfluidic channel. R and L represent the channel's radius and length, respectively, and the z-axis direction represents the flow direction of the fluid. In addition,  $(z,r,\theta)$  forms a cylindrical coordinates.

where  $\rho$ ,  $\eta$  and p represent the density, the dynamic viscosity, and the pressure of the fluid, respectively. u represents the velocity of the fluid along the z-direction shown in Figure 3.20, and f represents densities of body force, such as gravity and electromagnetic force. In fact, the Navier-Stokes equation is a continuum representation of Newton's second law (F=ma) in terms of acceleration (a) per unit volume [19].  $\frac{\partial u}{\partial t}$  represents the unsteady term or the time derivative of the velocity field u. It describes how the velocity of a fluid particle changes with time.  $u \cdot \nabla u$  represents the convective acceleration or the advection of momentum. It is the change in velocity due to the motion of the fluid itself and is a nonlinear term.  $-\nabla p$  represents the gradient of pressure p. The negative sign indicates that fluid moves from regions of high pressure to regions of low pressure.  $\nabla^2 u$  is the Laplacian of the velocity field, which represents the diffusion of momentum due to viscosity. This term is responsible for the viscous dissipation of energy within the fluid flow.

And in microfluidic chips, inertial forces are so small compared to viscous forces that the non-linear term in the Navier-Stokes equation can be neglected. So, the Navier-Stokes equation can be simplified as Equation 3.39 when calculating microfluidics [19].

$$\rho \frac{\partial u}{\partial t} = -\nabla p + \eta \nabla^2 u + f \tag{3.39}$$

Now, put all the variables into the Navier-Stokes equation to get Equation 3.40:

$$\rho \frac{\partial v_z}{\partial t} = -\frac{\partial P}{\partial z} + \eta \left[ \frac{1}{r} \frac{\partial}{\partial r} (r \frac{\partial v_z}{\partial r}) + \frac{1}{r^2} \frac{\partial^2 v_z}{\partial \theta^2} + \frac{\partial^2 v_z}{\partial z^2} \right] + \rho g_z \tag{3.40}$$

Where  $v_z$  represents the velocity of the fluid flowing along the z-direction. Since the current consideration is the steady flow of fluid, the value of v only corresponds to the distance between the cross-section position of the fluid and the origin and has nothing to do with time, theta, and place along the z-direction, which means  $\frac{\partial v_z}{\partial t}$ ,  $\frac{\partial^2 v_z}{\partial \theta^2}$ , and  $\frac{\partial^2 v_z}{\partial z^2}$  always equal 0. Besides that, the thesis will first introduce how to calculate the losses of pressure in channels that connect two pins on the same layer, so the effect of gravity can also be ignored because it is perpendicular to the direction of the fluid flow, which means item  $\rho g_z$  can also be removed from Equation 3.40. So Equation 3.40 can be further simplified to Equation 3.41.

$$0 = -\frac{\partial P}{\partial z} + \eta \cdot \frac{1}{r} \frac{\partial}{\partial r} (r \frac{\partial v_z}{\partial r}) \tag{3.41}$$

Next, the thesis processes Equation 3.41 to make it easy to integrate and get Equation 3.42.

$$\int \frac{\partial}{\partial r} \left(r \frac{\partial v_z}{\partial r}\right) dr = \frac{1}{\eta} \frac{\partial P}{\partial z} \int r dr$$

(3.42)

After the first integration, the following equation can be obtained:

$$r\frac{\partial v_z}{\partial r} = \frac{1}{\eta} \frac{\partial P}{\partial z} \cdot \frac{1}{2} r^2 + C_1 \tag{3.43}$$

where  $C_1$  represents a constant resulting from the integration process. To calculate the value of  $C_1$ , divide both sides of Equation 3.43 by r and then get Equation 3.44.

$$\frac{\partial v_z}{\partial r} = \frac{1}{n} \frac{\partial P}{\partial z} \cdot \frac{1}{2} r + \frac{C_1}{r} \tag{3.44}$$

When r approaches 0, the first term on the right side of Equation 3.44  $(\frac{1}{\eta} \frac{\partial P}{\partial z} \cdot \frac{1}{2}r)$  comes 0, and the second term $(\frac{C_1}{r})$  approaches infinity if  $C_1$  does not equal 0, so it can be seen that the left side of the equation $(\frac{\partial v_z}{\partial r})$  should also approach infinity. However, it is known that there is

no infinite momentum at the center of channels. So,  $C_1$  must equal 0. Equation 3.44 can then be readjusted to Equation 3.45 to prepare for the second integration.

$$\int \frac{\partial v_z}{\partial r} dr = \frac{1}{2\eta} \frac{\partial P}{\partial z} \int r dr \tag{3.45}$$

After integration, the result is shown in Equation 3.46:

$$v_z(r) = \frac{1}{2\eta} \frac{\partial P}{\partial z} \cdot \frac{1}{2} r^2 + C_2 \tag{3.46}$$

where  $C_2$  represents a constant resulting from the integration process. The assumption about the no-slip condition is used to calculate the value of  $C_2$ , which means the velocity of the part of the fluid in contact with the channels' surface is 0. So  $v_z(R)$  should be 0, and therefore  $C_2$  should be  $-\frac{1}{4\eta}\frac{\partial P}{\partial z}R^2$ .

Now, the final expression for solving the pressure difference can be obtained through some sorting.

$$\triangle P = \frac{4\eta L \cdot v_z(r)}{R^2 \left(1 - \left(\frac{r}{R}\right)^2\right)} \tag{3.47}$$

In addition, the fluid flow rate mentioned in this thesis defaults to the velocity of the fluid at the center of the channel so that Equation 3.47 can be further simplified to Equation 3.48.

$$\triangle P = \frac{4\eta L \cdot v_z(R)}{R^2} \tag{3.48}$$

In the same way, this equation can be used for calculating the pressure losses in channels that connect two pins on different layers.

$$\triangle P = \eta L \left( \rho g_z - \frac{4v_z(R)}{R^2} \right) \tag{3.49}$$

#### Pressure losses when liquid flows in a channel that turns 90 degrees

In this thesis, the Darcy-Weisbach equation calculates the pressure losses when fluid turns 90 degrees in channels. The Darcy-Weisbach equation in fluid dynamics is an empirical formula connecting the loss of pressure caused by friction over a specific channel length to the mean velocity of incompressible fluid flow. Its basic form is as follows [20]:

$$\frac{\triangle P}{L} = f_D \cdot \frac{\rho}{2} \cdot \frac{\langle v \rangle^2}{D_H} \tag{3.50}$$

where  $\rho$  and v represent the density and the velocity of the fluid, respectively, and L represents the length of turn. Besides that,  $D_H$  represents the hydraulic diameter of the channel. For a channel with a circular cross-section, this value is equal to channel's diameter(in meters). For channels with non-circular cross-sections,  $D_H$  can be calculated as  $D_H = \frac{4A}{P}$ , where A represents the cross-sectional area and P is the perimeter (both in meters). Last but not least,  $f_D$  represents the Darcy friction factor, which is only related to the Reynolds number for laminar fluid [21].

#### The process of adding speed constraints

When receiving a requirement for the pressure difference between two pins, first find out how many connections and modules the path of the two pins contains. Then, count the channels' length of each connection and the number of turns and express them with a mathematical expression. Last, calculate the pressure losses according to the two methods of calculating pressure loss mentioned before and require it to be equal to the pressure difference given by the user.

Figure 3.21: An example of constraints about pressure losses of channels on the same layer. The user specifies the velocity of the fluid at pin p1 and makes requirements for the pressure difference between p1 and p4.

Here is an instance shown in Figure 3.21. First, the program will figure out that there are two connections and one module on the path between p1 and p4, and then, the program will

compute the total length of channels between p1 and p2 and between p3 and p4. Besides that, the program will also count the number of turns on the path, which is 2 in this figure. Last, the program will use the Navier-Stokes equation and the Darcy-Weisbach equation to calculate the total pressure losses and require it to equal the pressure difference users expected in Gurobi.

The equation used for counting turns and calculating the total length of connections is shown in Equation 3.51:

$$\begin{cases}

t_{i} = 1 - abs \left( \frac{x'_{i} - x_{i}}{x'_{i} - x_{i} + y'_{i} - y_{i}} \cdot \frac{x'_{i+1} - x_{i+1}}{x'_{i+1} - x_{i+1} + y'_{i+1} - y_{i+1}} + \frac{y'_{i} - y_{i}}{x'_{i} - x_{i} + y'_{i} - y_{i}} \cdot \frac{y'_{i+1} - y_{i+1}}{x'_{i+1} - x_{i+1} + y'_{i+1} - y_{i+1}} \right) \\

l_{i} = abs(x'_{i} - x_{i}) + abs(y'_{i} - y_{i}) \\

t = \sum_{i=0}^{n-2} t_{i} \\

l = \sum_{i=0}^{n-1} l_{i}

\end{cases}$$

(3.51)

where  $(x_i,y_i)$  and  $(x_i^{'},y_i^{'})$  represent two endpoints' coordinates of i-th channel in a connection, respectively. n represents the total number of channels in a connection. Besides that,  $t_i$  denotes the i-th channel in a connection whether it has a turn. When  $t_i$  equals 0, there is no turn; when  $t_i$  equals 1, there is a turn. And t represents the total number of turns in a connection. Last but not least,  $l_i$  expresses the length of the i-th channel in a connection, and l represents the total length of a connection.

## 4 Program performance optimization

By passing the mathematical modeling of the chip and chip internal constraints in chapter 3 as input to Gurobi, the program has the essential ability to automatically design channel connections based on chip information.

However, in actual applications, the program will often encounter channel connection design needs of large chips, which contain dozens of modules and dozens of connections and it takes a long time for these large-scale design projects to produce results, which cannot meet users' expectations. Therefore, in addition to realizing the basic functions of channel design, this thesis optimizes the program's performance in three aspects. These optimizations are introduced separately below.

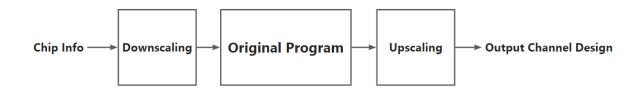

#### 4.1 Chip's downscaling and upscaling

Typically, most microfluidic chips are several thousand microns by several thousand microns in size. In Gurobi, each unit area, the square of a micrometer, is used to explore the possibility of a solution, which means that the number of unit squares that need to be explored will increase exponentially as the chip size increases, which will lead to the significant increase on the running time of the program.

On the contrary, if the chip area is reduced, the number of unit squares that the Gurobi optimizer needs to explore can be reduced, and the channel design results can be obtained quickly.

Based on this idea, a chip information preprocessing module is added before the chip data is input to the program, which is responsible for dividing the size parameter of the chip and the modules inside by a scaling factor to reduce the area of the chip.

Besides that, a reduction module is added before the program outputs. This reduction module will multiply the size data of the chip, the modules inside, and the channel design by the same scaling factor in the chip information preprocessing module to restore them to normal size.

The flow chart of the entire process of downscaling and upscaling is as follows:

Figure 4.1: Optimization flow chart of downscaling and upscaling.

The key to downscaling and upscaling optimization is selecting the scaling factor. The method of selecting the scaling factor will be introduced in detail below. The core target of selecting the scaling factor is to scale the chip and internal components as small as possible while ensuring no overlap between the edge of the chip and modules inside, modules and modules, and pins and pins.

To achieve this target, first, the minimum distances between the four boundaries of the chip and the module, between modules, and between pins should be calculated. In addition, a distance threshold will be preset in advance, representing the acceptable minimum value of the distance between modules and the surrounding boundaries of the chip, modules and modules, and pins after chip scaling. Subsequently, one only needs to use the threshold set in advance to remove the statistically calculated minimum distance in the chip to obtain the optimal scaling factor, as shown in Equation 4.1:

Figure 4.2: An example of counting the minimum distance between modules and the four boundaries of the chip, modules and modules, pins and pins.

$$\alpha = \frac{d_{min}}{threshold} \tag{4.1}$$

where  $\alpha$  represents the scaling factor,  $d_{min}$  denotes the minimum distance, and *threshold* refers to the minimum distance threshold predetermined by the user.

# 4.2 An advance estimate of the number of channels required in a connection

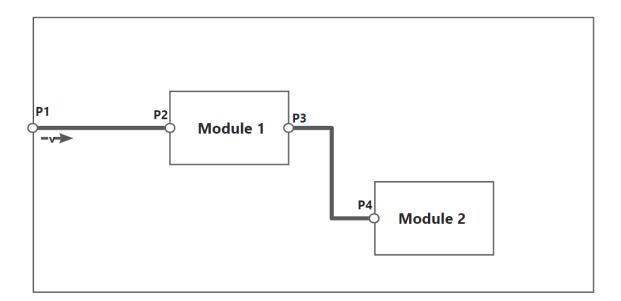

Before passing parameters to the Gurobi optimizer for a solution, it is necessary to determine how many channels each connection consists of. If the number of channels required for all connections is uniformly set to the default value, it will likely result in redundant parameters. Therefore, this thesis introduces a functional module that can estimate the number of channels required for each connection based on the relative positions of each module and pin in the chip in adavance. In other words, customize each connection's required number of channels according to its situation. The following describes how this functional module works.

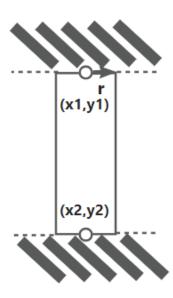

Since channels can only be horizontal or vertical, the number of channels required for a connection is related to the number of turns in the connection path because each turn requires converting channels to change the direction of travel. More precisely, the number of channels needed for a connection equals the minimum number of necessary turns plus 1. An example is shown in Figure 4.3. According to Figure 4.3, there are 2 turns; therefore, 3 channels are needed.

Figure 4.3: An example of calculating the number of channels needed in a connection.

And now, the core problem is estimating the minimum number of turns required for a connection. In this thesis,  $A^*$  algorithm is used to estimate the minimum turns of a connection.

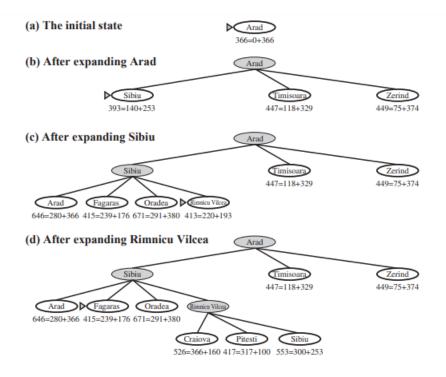

A\* is an informed search algorithm, categorized as a best-first search method, designed for solving problems in weighted graphs. It commences from a designated initial node within the graph and strives to identify the path to a specified goal node with the least cost, which can be defined as the minimal distance traveled or shortest time taken, among other factors. This approach involves the creation of a tree structure that branches out from the starting node, continuously expanding these paths by incrementally adding one edge at a time until certain termination conditions are met. During each cycle of its primary loop, A\* must decide which path to prolong [15].

This choice hinges on two key factors: the current cost of the path and an estimation of the cost needed to extend that path to reach the goal. In particular, A\* opts for the path that minimizes [15]:

$$f(n) = g(n) + h(n) \tag{4.2}$$

Here, n represents the next node in the path, g(n) signifies the cumulative cost from the start node to node n, and h(n) is a heuristic function providing an estimate of the most economical path cost from n to the goal. A\* concludes its operation when it either identifies a path extending from the starting point to the goal or encounters a situation where no eligible paths for extension remain. The appropriateness of the heuristic function is reliant on the specific problem at hand. If the heuristic function is deemed admissible, indicating it never overestimates the actual cost to reach the goal, A\* is assured to yield the least-cost path from the start to the goal [15].

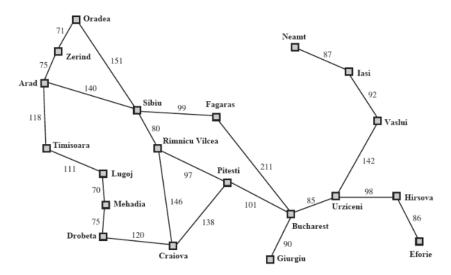

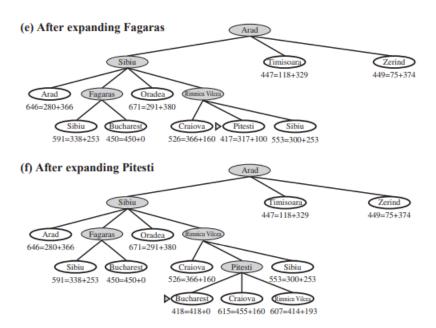

Below is an example of applying the A\* algorithm to solve a problem that aims to find the shortest distance from Arad to Bucharest. In this problem, h(n) equals the distance from the current place to Bucharest.

| Arad      | 366 | Mehadia        | 241 |

|-----------|-----|----------------|-----|

| Bucharest | 0   | Neamt          | 234 |

| Craiova   | 160 | Oradea         | 380 |

| Drobeta   | 242 | Pitesti        | 100 |

| Eforie    | 161 | Rimnicu Vilcea | 193 |

| Fagaras   | 176 | Sibiu          | 253 |

| Giurgiu   | 77  | Timisoara      | 329 |

| Hirsova   | 151 | Urziceni       | 80  |

| Iasi      | 226 | Vaslui         | 199 |

| Lugoj     | 244 | Zerind         | 374 |

Figure 4.4: The distance from each city to Bucharest [15].

Figure 4.5: A road map of part of Romania [15].

Figure 4.6: The stages in an  $A^*$  search for Bucharest. Nodes are labeled with f = g + h, where h values represent the straight-line distances to Bucharest as obtained from Figure 4.4 [15].

Figure 4.7: The stages in an  $A^*$  search for Bucharest. Nodes are labeled with f = g + h, where h values represent the straight-line distances to Bucharest as obtained from Figure 4.4 [15].

As mentioned above, the selection of h(n) varies depending on the type of problem. And the h(n) used in this thesis is shown in Equation 4.3 and Equation 4.4:

$$p = (x_n - x_{n-1}) \cdot (x_{n-1} - x_{n-2}) + (y_n - y_{n-1}) \cdot (y_{n-1} - y_{n-2})$$

$$\tag{4.3}$$

$$h(n) = \begin{cases} abs(x_n - x_{target}) + abs(y_n - y_{target}) & p = 0\\ abs(x_n - x_{target}) + abs(y_n - y_{target}) * 2 & p \neq 0 \end{cases}$$

$$(4.4)$$

where  $(x_{n-2}, y_{n-2})$  and  $(x_{n-1}, y_{n-1})$  represent the two endpoints' coordinates of the previous channel, and  $(x_{n-1}, y_{n-1})$  and  $(x_n, y_n)$  represent the coordinates of the two endpoints of the current channel. p represents the dot product of the current channel and the previous channel. From Equation 4.4, it is seen that the essential cost is the Manhattan Distance between the current node and the target node. Besides that, when the current channel is perpendicular to the previous channel, which means there is a turn, an additional cost equal to the Manhattan distance between the two points mentioned before will be added.

The reason for choosing the Manhattan Distance between the current node and the target node as the cost of turn is that when far away from the target, the extra cost is very high, and turning is discouraged. And when approaching the target, there may be some direction adjustments to make. If the cost of turning is still high, it is hard to find a feasible solution.

So when choosing the Manhattan Distance as the turn cost, the turn cost will decrease as it approaches the target, which makes it possible to find feasible solutions.

Through the above  $A^*$  algorithm, the program can set the required number of channels according to the situation of each connection, avoiding parameter redundancy and improving program operation efficiency.

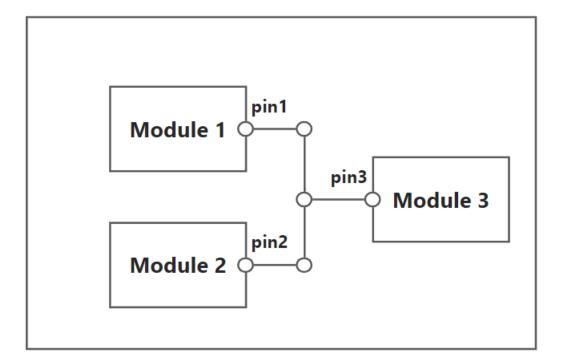

# 4.3 Merging part of channels of different connections that have the same pins

Suppose there are several connections with the same start pin or end pin. In that case, sharing the channel directly connected to the same pin is advisable because it will reduce the number of total channels, reducing the number of parameters that Gurobi should calculate. It will speed up the program processing time. Besides that, the chip will also be easier to fabricate because fewer channels need to be printed.

Figure 4.8: An example of a situation where fusion channels are required. pin<sub>1</sub> and pin<sub>2</sub> are both connected to pin<sub>3</sub>, so they share the last channel directly connected to pin<sub>3</sub>.

# 5 Calculation examples and analysis of experimental results

#### 5.1 Calculation case design and experimental equipment setup

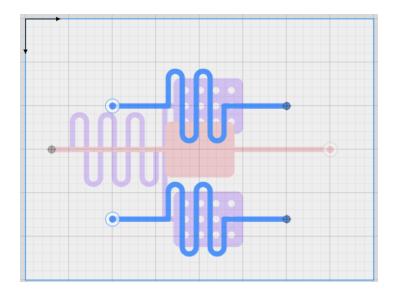

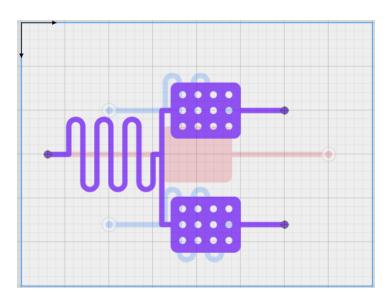

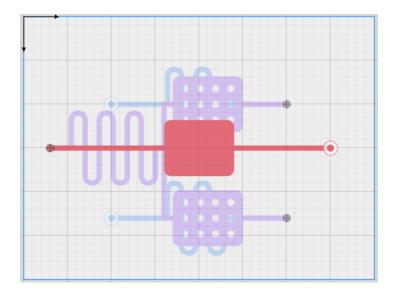

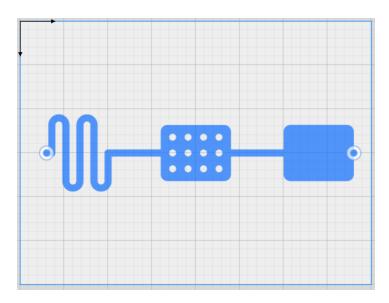

#### 5.1.1 Test case without a constraint of pressure losses

This thesis uses a three-layer chip containing six components with five connection relationships as a test case to verify whether the primary channel planning function of the program is practical. The following tables introduce the chip size and module size in the chip of the test case and the connection relationship between each pin port.

Table 5.1: Specifications of the chip in the test case.

|                      | chip  |

|----------------------|-------|

| Device length(µm)    | 20000 |

| Device width(µm)     | 15000 |

| Device thickness(µm) | 4000  |

| Channel width(µm)    | 400   |

| Module Height(µm)    | 100   |

| Number of layers     | 3     |

Table 5.2: Parameters of modules of the DelayChannel type in the chip.

| Module name                               | m1           | m2           | m3           |

|-------------------------------------------|--------------|--------------|--------------|

| Туре                                      | DelayChannel | DelayChannel | DelayChannel |

| Coordinate of the upper left endpoint(µm) | (5000,3000)  | (5000,9500)  | (1500,5500)  |

| Width(µm)                                 | 6000         | 6000         | 6000         |