# ТЛП

Technische Universität München TUM School of Computation, Information and Technology

# A Framework to Design and Synthesize Vehicle E/E Architecture

Hadi Askaripoor

Vollständiger Abdruck der von der TUM School of Computation, Information and Technology der Technischen Universität München zur Erlangung eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitz: Prof. Dr.-Ing. Jörg Ott

#### Prüfer der Dissertation:

- 1. Prof. Dr.-Ing. habil. Alois C. Knoll

- 2. Prof. Dr. Ali Mosleh

Die Dissertation wurde am 18.12.2023 bei der Technischen Universität München eingereicht und durch die TUM School of Computation, Information and Technology am 05.07.2024 angenommen.

#### Abstract

In recent years, the field of automotive electrical and electronic (E/E) architecture has undergone substantial evolution. The latest generation of road vehicles necessitates a substantial infusion of computational power to support the execution of a multitude of safety-critical applications and advanced driver assistance systems (ADAS) functionalities. Centralized architecture, enhanced by the incorporation of high-performance computing units, emerges as a pivotal approach to reinforce the capability of vehicles in handling these resource-intensive applications. The high number of sensors and actuators demands high-bandwidth communication protocols to facilitate a seamless data flow. In addition, to harmonize the integration of safety-critical and real-time applications, known as mixed-criticality systems, deterministic and redundancy protocols are necessary. However, configuring and integrating essential applications into a vehicle's E/E architecture, all while meeting various requirements, guaranteeing reliable communication, and considering optimization objectives, can be timeconsuming, complex, and error-prone tasks.

This thesis presents a novel model-based framework to facilitate the synthesis of car E/E architectures, which supports modeling for automotive embedded systems. The introduced tool automates mapping of software components to hardware elements and computes schedules for application threads. It establishes network message routing and schedules communication tasks within the car's topology while addressing safety requirements, including redundancy, homogeneous redundancy, and reliability. The proposed computer-aided tool also optimizes the system model, covering multiple optimization objectives. It supports multiple objective optimization and utilizes a single-step approach to solve mixed-integer programming (MIP) constraints, reducing solving time and considering the relationships among various constraints. Moreover, the proposed tool offers a web-based frontend that allows users to model their desired E/E systems and select various hardware and software requirements and properties, along with the boundary and optimization goals. The developed frontend also visualizes the solution of the designed system after it has been solved.

There are situations where a designed E/E architecture is not satisfiable, meaning that feasible solutions cannot be found by a MIP solver. Unlike simple models, navigating and correcting the unsatisfiability of complex E/E models is a complex and time-consuming task, leading to increased development costs. To tackle this issue, this thesis also introduces an approach to identify design errors when violations occur in a constraint set included in a system model after the solving step.

The performance of this model-based framework is assessed at three key stages. Designtime, where the solving and generation times of constraint sets in various scenarios are evaluated, including scalability analysis. Run-time, where the solution is deployed on an experimental setup, and finally, quantitative and qualitative evaluations. The results of the design-time experiments indicate that the formulations can scale to systems of reasonable size. During the run-time experiments, it is observed that there are no instances of timing deadline breaches following the deployment of the design-time solutions on an experimental setup.

#### Zusammenfassung

In den letzten Jahren hat sich der Bereich der elektrischen und elektronischen (E/E-) Architektur von Kraftfahrzeugen erheblich weiterentwickelt. Die neueste Generation von Straßenfahrzeugen erfordert eine erhebliche Steigerung der Rechenleistung, um die Ausführung einer Vielzahl von sicherheitskritischen Anwendungen und fortschrittlichen Fahrerassistenzsystemen (ADAS) zu unterstützen. Eine zentralisierte Architektur, die durch den Einbau von Hochleistungsrecheneinheiten verbessert wird, erweist sich als entscheidender Ansatz, um die Fähigkeit von Fahrzeugen zur Handhabung dieser ressourcenintensiven Anwendungen zu verbessern. Darüber hinaus erfordert die zunehmende Anzahl von Sensoren und Aktoren Kommunikationsprotokolle mit hoher Bandbreite, um einen nahtlosen Datenfluss zu ermöglichen. Zur Harmonisierung der Integration von sicherheitskritischen und Echtzeitanwendungen, die als Systeme mit gemischter Kritikalität bezeichnet werden, sind außerdem deterministische und redundante Protokolle unerlässlich. Die Konfiguration und Integration wichtiger Anwendungen in die E/E-Architektur eines Fahrzeugs unter Berücksichtigung der verschiedenen Anforderungen, der Gewährleistung einer zuverlässigen Kommunikation und der Optimierungsziele kann jedoch zeitaufwändig, komplex und fehleranfällig sein.

In dieser Arbeit wird ein neuartiges modellbasiertes Framework zur Erleichterung der Synthese der E/E-Architektur eines Fahrzeugs vorgestellt, das die Modellierung für eingebettete Systeme im Automobil unterstützt. Das vorgestellte Werkzeug automatisiert die Zuordnung von Softwarekomponenten zu Hardwareelementen und berechnet Zeitpläne für Anwendungsthreads. Es legt das Routing von Netzwerknachrichten fest und plant Kommunikationsaufgaben innerhalb der Fahrzeugtopologie unter Berücksichtigung von Sicherheitsanforderungen wie Redundanz, homogener Redundanz und Zuverlässigkeit. Das vorgeschlagene computergestützte Tool optimiert auch das Systemmodell und deckt mehrere Optimierungsziele ab. Es unterstützt die Mehrzieloptimierung und verwendet einen Ein-Schritt-Ansatz zur Lösung von MIP-Beschränkungen (Mixed-Integer Programming), wodurch die Lösungszeit reduziert und die Beziehungen zwischen den verschiedenen Beschränkungen berücksichtigt werden. Darüber hinaus bietet das vorgeschlagene Tool ein webbasiertes Frontend, mit dem Benutzer ihre gewünschten E/E-Systeme modellieren und verschiedene Hardware- und Softwareanforderungen und -eigenschaften sowie die Randbedingungen und Optimierungsziele auswählen können. Das entwickelte Frontend visualisiert auch die Lösung des entworfenen Systems, nachdem es gelöst wurde. Es gibt Situationen, in denen eine entworfene E/E-Architektur nicht zufriedenstellend ist, was bedeutet, dass der MIP-Löser keine machbaren Lösungen finden kann. Im Gegensatz zu einfachen Modellen ist das Navigieren und Korrigieren der Unerfüllbarkeit komplexer E/E-Modelle eine komplexe und zeitaufwändige Aufgabe, die zu erhöhten Entwicklungskosten führt. Um dieses Problem anzugehen, wird in dieser Arbeit auch ein Ansatz zur Identifizierung von Entwurfsfehlern vorgestellt, wenn nach dem Lösungsschritt Verletzungen in der im Systemmodell enthaltenen Constraintmenge auftreten.

Die Leistung dieses modellbasierten Rahmens wird in drei Schlüsselphasen bewertet: zur Entwurfszeit, in der die Lösungs- und Generierungszeiten von Constraint-Sets in verschiedenen Szenarien bewertet werden, einschließlich einer Skalierbarkeitsanalyse; zur Laufzeit, in der die Lösung in einem Versuchsaufbau eingesetzt wird, sowie durch quantitative und qualitative Bewertungen. Die Ergebnisse der Experimente zur Entwurfszeit zeigen, dass die Formulierungen auf Systeme angemessener Größe skaliert werden können. Bei den Laufzeitexperimenten wurde festgestellt, dass nach dem Einsatz der Lösungen aus der Entwurfszeit in einem Versuchsaufbau keine Verstöße gegen die Zeitvorgaben auftraten.

#### Acknowledgement

I extend my deepest gratitude to all those who have contributed to the realization of this Ph.D. thesis. First and foremost, I express my sincere appreciation to my supervisor, Professor Alois Knoll, for his unwavering support, mentorship, and invaluable guidance throughout this research journey and for giving me the chance to pursue my Ph.D. at his research group. His expertise and commitment have been instrumental in shaping the trajectory of my academic pursuits. I would also like to express my heartfelt thanks to Professor Ali Mosleh, my second examiner from University of California, Los Angeles (UCLA), for his valuable feedback and insightful comments on my research. His expertise has been instrumental in refining the quality of my work. Additionally, my sincere appreciation goes to Professor Jörg Ott, the chairman of my defense, for overseeing the defense process and for his time and support in ensuring everything runs smoothly.

A special acknowledgment is reserved for Dr. Morteza Hashemi Farzaneh as my mentor. His guidance and insightful hints provided in the early stages were pivotal in helping me find my research direction. I wish to express my gratitude to my colleagues at the Chair of Robotics, Artificial Intelligence, and Real-time Systems. In particular, I extend my special thanks to Amy Buecherl for her consistent help and kindness. A heartfelt thank you goes to Ute Lomp, the former member of the chair, for her unwavering support and care. Welcoming Janine Delle, a new member of the chair, deserves my appreciation for her kindness and contributions to the dissertation process. I also want to thank Marie-Luise Neitz for her valuable assistance. Dr. Alex Lenz merits special thanks for his unwavering support, help, and kindness throughout this journey. My sincere gratitude extends to Thilo Mueller, my student, for his contributions. I am indebted to my colleagues and friends, including Hossein Malmir, Walter Zimmer, and Soubarna Banik, for their proofreading of this thesis. A profound thank you goes to my best friend, Andreas Wieser, for his help and for being an exceptional companion and friend during this journey.

In conclusion, I express deep gratitude to my family, including my sister and brothers, for their continuous support, motivation, and assistance. To my parents, Fatemeh and Yousef, my heartfelt and special thanks for their unwavering love, motivation, and constant support throughout this challenging journey. Despite the long distance, my parents and family send their love and support. I am immensely grateful and love you all dearly. This work is dedicated to them.

Los Angeles, 14.12.2023

Hadi Askaripoor

## Contents

| 1 | Intr | oduction                                                                | 1  |

|---|------|-------------------------------------------------------------------------|----|

|   | 1.1  | Vehicle E/E Architecture and its Development                            | 1  |

|   |      | 1.1.1 The Main Bottlenecks of Current E/E Architecture                  | 3  |

|   |      | 1.1.2 The Main Technologies for Future's E/E Architecture               | 4  |

|   | 1.2  | Motivation and Research Questions                                       | 5  |

|   |      | 1.2.1 Motivation                                                        | 5  |

|   |      | 1.2.2 Research Questions                                                | 6  |

|   | 1.3  | Thesis Contributions                                                    | 7  |

|   | 1.4  | Thesis Structure                                                        | 9  |

| 2 | Basi | c Concepts and Terms                                                    | 11 |

|   | 2.1  | Task Mapping or Resource Allocation                                     | 11 |

|   | 2.2  | Time-triggered Scheduling                                               | 12 |

|   | 2.3  | Communication Message Routing                                           | 13 |

|   | 2.4  | Vehicle Communication Protocols                                         | 15 |

|   |      | 2.4.1 CAN and TTCAN Buses                                               | 15 |

|   |      | 2.4.2 FlexRay                                                           | 16 |

|   |      | 2.4.3 LIN Bus                                                           | 16 |

|   |      | 2.4.4 Automotive Ethernet and Ethernet TSN                              | 16 |

|   | 2.5  | Automotive Safety Standards                                             | 18 |

|   |      | 2.5.1 ISO 26262 (Functional Safety for Road Vehicles)                   | 18 |

|   |      | 2.5.2 SOTIF/ISO 21448                                                   | 19 |

|   | 2.6  | Safety Requirements                                                     | 19 |

|   |      | 2.6.1 Redundancy                                                        | 20 |

|   |      | 2.6.2 Freedom from Interference                                         | 20 |

|   |      | 2.6.3 ASIL                                                              | 20 |

|   |      | 2.6.4 Reliability                                                       | 21 |

|   | 2.7  | Design Space Exploration (DSE)                                          | 22 |

|   | 2.8  | Hypervisor                                                              | 22 |

| 3 | Stat | e of the Art                                                            | 25 |

|   | 3.1  | Communication Message Routing and Synthesis of Time-triggered Schedules |    |

|   |      | in Automotive Networks                                                  | 25 |

|   |      | 3.1.1 Communication Message Routing                                     | 25 |

|   |      | 3.1.2 Synthesis of Time-triggered Schedules in Automotive Domain        | 26 |

|   | 3.2  | Software Architecture Synthesis-related Studies                         | 27 |

|   |      | 3.2.1 Software Architecture Synthesis                                   | 27 |

|   |      | 3.2.2 E/E System Synthesis Considering Safety Requirements              | 27 |

|   | 3.3  | Task Mapping in Multi-Core Computing Units                              | 29 |

|   |      | 3.3.1 Mapping Techniques                                                | 29 |

|   | 3.4 |         | Optimization Parameters in Mapping                                  | 30 |

|---|-----|---------|---------------------------------------------------------------------|----|

|   |     |         | 38                                                                  | 31 |

|   |     | 3.4.1   | Non-commercial/Open-source Frameworks                               | 32 |

|   |     | 3.4.2   | Overview of Non-commercial Frameworks Analysis                      | 42 |

|   |     | 3.4.3   | Commercial Tools for E/E Architecture Configuration                 | 45 |

|   |     | 3.4.4   | Overview of Commercial Tools Analysis                               | 47 |

|   | 3.5 | Summ    | ary & Discussion                                                    | 48 |

| 4 | Met | hodolo  |                                                                     | 51 |

|   | 4.1 | Frame   | work Architecture                                                   | 51 |

|   |     | 4.1.1   | Model-Driven Development                                            | 54 |

|   |     | 4.1.2   | Object-oriented Metamodel                                           | 55 |

|   |     | 4.1.3   | Constraint Set                                                      | 55 |

|   |     | 4.1.4   | Optimization                                                        | 58 |

|   |     | 4.1.5   | Design Error Identifier                                             | 58 |

|   |     | 4.1.6   | An Overview of Framework Architecture                               | 59 |

|   | 4.2 | Frame   | work System Model                                                   | 60 |

|   |     | 4.2.1   | Application Thread                                                  | 60 |

|   |     | 4.2.2   | Communication Task                                                  | 60 |

|   |     | 4.2.3   | Mapping Action                                                      | 61 |

|   |     | 4.2.4   | Communication Message                                               | 61 |

|   |     | 4.2.5   | Application                                                         | 62 |

|   |     | 4.2.6   | Timing Limitations                                                  | 62 |

|   | 4.3 |         | raints MIP Formulation                                              | 65 |

|   | 1.0 | 4.3.1   | Automated Mapping                                                   | 65 |

|   |     | 4.3.2   | Automatic Message Routing                                           | 66 |

|   |     | 4.3.3   | Overlapping-Free Application Threads Considering Automated Map-     | 00 |

|   |     | т.5.5   | ping                                                                | 74 |

|   |     | 4.3.4   | Overlapping-Free Communication Tasks Considering Automatic Mes-     | 74 |

|   |     | т.Ј.т   | sage Routing                                                        | 75 |

|   |     | 4.3.5   | Path Dependency                                                     | 76 |

|   |     | 4.3.6   |                                                                     | 70 |

|   | 11  |         | Message Dependencylary Constraints & Optimization Objectives        | 77 |

|   | 4.4 | 4.4.1   |                                                                     |    |

|   |     |         | End-to-End Latency                                                  | 78 |

|   |     | 4.4.2   | Response Time                                                       | 79 |

|   |     | 4.4.3   | Resource Utilization (RU)                                           | 80 |

|   |     | 4.4.4   | Load Balancing in Vehicle Communication Network                     | 81 |

|   |     | 4.4.5   | Cost Reduction (CR)                                                 | 83 |

|   |     | 4.4.6   | Reliability                                                         | 83 |

|   |     | 4.4.7   | Hypervisor-related Constraints                                      | 87 |

|   | 4.5 |         | Objective Optimization                                              | 88 |

|   |     | 4.5.1   | Gurobi Multi-Objective Optimization                                 | 89 |

|   |     | 4.5.2   | Multi-Objective Optimization in the E/E Designer Framework          | 89 |

|   | 4.6 | -       | -Step Solving Algorithms                                            | 91 |

|   |     | 4.6.1   | CMR Algorithm                                                       | 91 |

|   |     | 4.6.2   | CSCT Algorithm                                                      | 91 |

|   |     | 4.6.3   | PD Algorithm                                                        | 93 |

|   | 4.7 |         | raint Formulation as Mixed Integer Programming for Gurobi Optimiza- |    |

|   |     | tion Se | olver                                                               | 94 |

|   |     | 4.7.1   | Big M Method                                                        | 94 |

|   |      | 4.7.2 Quadratic Expression                                                                                                                                          | 95                                                   |

|---|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|   | 4.8  | Discussion                                                                                                                                                          | 96                                                   |

| 5 | The  | Framework Frontend                                                                                                                                                  | 97                                                   |

| 0 |      | Modeling                                                                                                                                                            | 97                                                   |

|   | 0.1  | 5.1.1 Web-based Modeling Tool                                                                                                                                       | 97                                                   |

|   |      | 5.1.2 Drag and Drop Functionality                                                                                                                                   | 99                                                   |

|   |      | 5.1.3 Full-mesh Topology                                                                                                                                            | 99                                                   |

|   |      | 5.1.4 Automatic Creation of Software/Hardware Components                                                                                                            | 100                                                  |

|   | 5.2  | Requirements and Properties                                                                                                                                         | 100                                                  |

|   | 0.2  | 5.2.1 Hardware/Software Requirements and Properties                                                                                                                 | 100                                                  |

|   |      | 5.2.2 Optimization and Solving Properties                                                                                                                           | 101                                                  |

|   | 5.3  | Solving and Solutions                                                                                                                                               | 102                                                  |

|   |      | 5.3.1 Solving                                                                                                                                                       | 102                                                  |

|   |      | 5.3.2 Solutions                                                                                                                                                     | 103                                                  |

|   | 5.4  | Model Validation                                                                                                                                                    | 105                                                  |

|   | 5.5  | Implementation                                                                                                                                                      | 107                                                  |

|   |      | 5.5.1 Sirius Web                                                                                                                                                    | 107                                                  |

|   |      |                                                                                                                                                                     |                                                      |

| 6 |      | 0 5                                                                                                                                                                 | 109                                                  |

|   | 6.1  | Background                                                                                                                                                          | 109                                                  |

|   |      | 6.1.1 Conjunctive Normal Form                                                                                                                                       | 110                                                  |

|   |      | 6.1.2 Minimal Unsatisfiable Subset (MUS) or Unsatisfiable Core                                                                                                      | 111                                                  |

|   | 6.2  | Approach                                                                                                                                                            | 111                                                  |

|   |      | 6.2.1 Using Irreducible Inconsistent Subsystem (IIS)                                                                                                                | 112                                                  |

|   |      | 6.2.2 Using MARCO Algorithm                                                                                                                                         | 114                                                  |

|   | 6.3  | Evaluation                                                                                                                                                          | 116                                                  |

| 7 | Eval | uation                                                                                                                                                              | 119                                                  |

|   | 7.1  | Design-time Evaluation                                                                                                                                              | 119                                                  |

|   |      | 7.1.1 Evaluation of Communication Message Routing Generation                                                                                                        | 120                                                  |

|   |      | 7.1.2 Automated Mapping Approach and Application Threads' Scheduling<br>Evaluation                                                                                  | 122                                                  |

|   |      | 7.1.3 Evaluation of Full Capabilities of the E/E Designer Framework in a                                                                                            | 122                                                  |

|   |      | Single-Step Solving                                                                                                                                                 | 124                                                  |

|   |      | 7.1.4 Scalability Analysis                                                                                                                                          | 125                                                  |

|   |      | 7.1.5 Discussion                                                                                                                                                    | 126                                                  |

|   | 7.2  | Run-time Evaluation                                                                                                                                                 | 127                                                  |

|   | ,    | 7.2.1 Hardware Platform Analysis                                                                                                                                    | 127                                                  |

|   |      | 7.2.2 Experimental Setup                                                                                                                                            | 128                                                  |

|   | 7.3  | Quantitative and Qualitative Evaluation                                                                                                                             | 139                                                  |

|   |      |                                                                                                                                                                     |                                                      |

|   |      |                                                                                                                                                                     |                                                      |

|   |      |                                                                                                                                                                     | 139<br>142                                           |

| ~ | -    | <ul><li>7.3.1 Quantitative Analysis of Various Case Studies</li></ul>                                                                                               | 139<br>142                                           |

| 8 |      | <ul> <li>7.3.1 Quantitative Analysis of Various Case Studies</li></ul>                                                                                              | 139<br>142<br><b>143</b>                             |

| 8 | 8.1  | 7.3.1       Quantitative Analysis of Various Case Studies         7.3.2       Qualitative Analysis         clusion and Future Work         Summary                  | 139<br>142<br><b>143</b><br>143                      |

| 8 |      | 7.3.1       Quantitative Analysis of Various Case Studies         7.3.2       Qualitative Analysis         clusion and Future Work         Summary       Imitations | 139<br>142<br><b>143</b><br>143<br>145               |

| 8 | 8.1  | 7.3.1       Quantitative Analysis of Various Case Studies         7.3.2       Qualitative Analysis         clusion and Future Work         Summary                  | 139<br>142<br><b>143</b><br>143<br>145<br>145        |

| 8 | 8.1  | 7.3.1       Quantitative Analysis of Various Case Studies         7.3.2       Qualitative Analysis         clusion and Future Work         Summary                  | 139<br>142<br><b>143</b><br>143<br>145<br>145<br>145 |

| 8 | 8.1  | 7.3.1       Quantitative Analysis of Various Case Studies         7.3.2       Qualitative Analysis         clusion and Future Work         Summary                  | 139<br>142<br><b>143</b><br>143<br>145<br>145        |

|     | 8.3 Fut   | ture | Works                         | 146 |

|-----|-----------|------|-------------------------------|-----|

|     | 8.3       | .1   | New Requirements and Features | 146 |

|     | 8.3       | .2   | Run-time E/E Configurator     | 147 |

|     | 8.3       | .3   | Uncertain Optimization        | 147 |

|     | 8.3       | .4   | Run-time Simulation           | 147 |

| A   | Append    | ix 1 |                               | 149 |

| Bil | oliograph | ıy   |                               | 153 |

# List of Figures

| 1.1<br>1.2 | The figure presents the evolution of vehicle E/E architecture. Distributed E/E architectures were used until 2019, while domain-centralized architectures are used nowadays as vehicle architectures. The zonal architecture shows the future car E/E architecture [AHK22] | 2  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

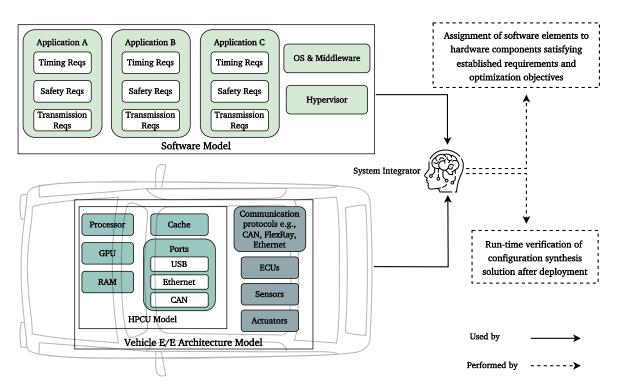

|            | configuration syntheses for automotive software components and the vehicle E/E architecture model                                                                                                                                                                          | 6  |

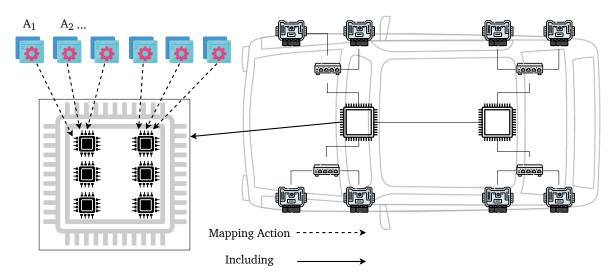

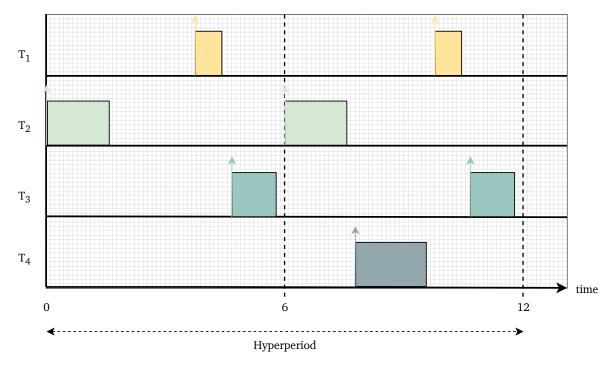

| 2.1<br>2.2 | Assignment of applications to an HPCU consisting of six cores. $\dots$ The time-triggered slots of four periodic tasks, namely $T_1$ , $T_2$ , $T_3$ , and $T_4$ . An                                                                                                      | 12 |

| 2.3        | arrow alongside each slot indicates the starting point of the respective task<br>Single and multicast routes within a car E/E topology for transferring com-<br>munication messages from senders to receivers. The communication messages                                  | 13 |

| 2.4        | are generated by applications executing on ECUs                                                                                                                                                                                                                            | 14 |

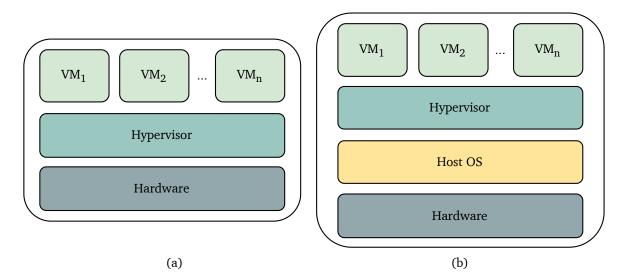

| 2.5        | (b) Type-2 or Hosted hypervisor                                                                                                                                                                                                                                            | 22 |

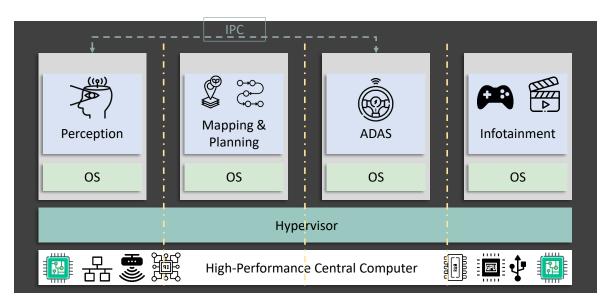

|            | 1 hypervisor consisting of four mixed-critical partitions. The yellow dash lines show the hard separations between partitions starting from the hardware level [AHK22].                                                                                                    | 23 |

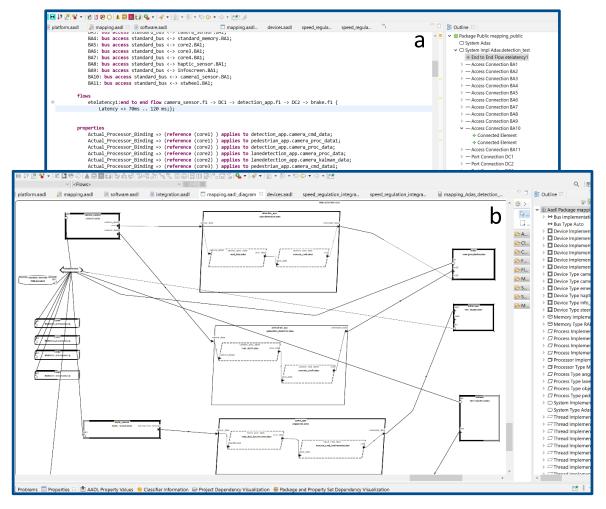

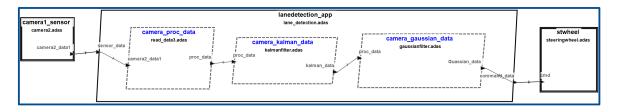

| 3.1        | The AADL text editor (a) to synchronized graphical editor (b) in OSATE frame-<br>work.                                                                                                                                                                                     | 32 |

| 3.2        | The AADL text editor for a lane detection application including flow analysis, processor and memory bindings in OSATE framework.                                                                                                                                           | 33 |

| 3.3        | The synchronized graphical editor for a lane detection application created based on the AADL text in the OSATE framework.                                                                                                                                                  | 33 |

| 3.4        | The report of end-to-end latency analysis for the specified flows in the OSATE tool.                                                                                                                                                                                       | 34 |

| 3.5        | Binpacking analysis and thread to processor bindings report in OSATE frame-<br>work.                                                                                                                                                                                       | 34 |

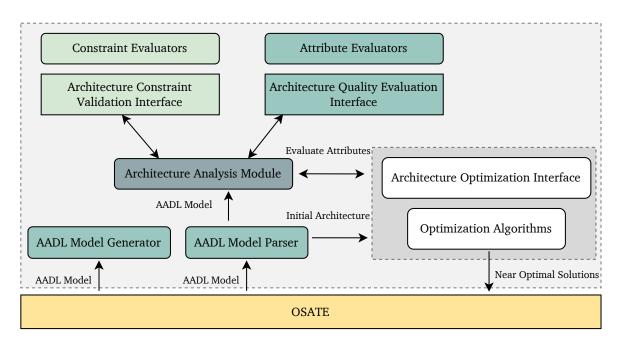

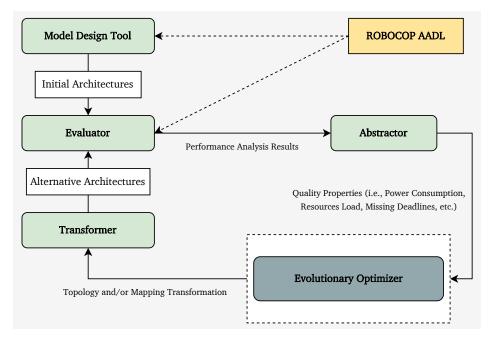

| 3.6        | The architecture of ArcheOpterix framework [AMK23]                                                                                                                                                                                                                         | 35 |

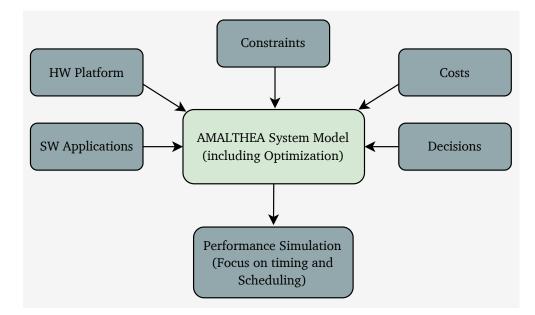

| 3.7        | The APP4MC architecture [AMK23]                                                                                                                                                                                                                                            | 37 |

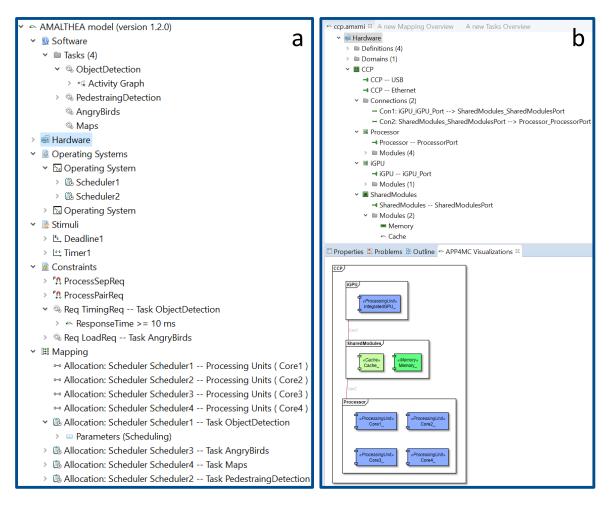

| 3.8        | A model of the hardware and software system in the automotive industry has<br>been developed using the APP4MC framework. This model encompasses tim-<br>ing and mapping constraints (a) and includes a visual representation of the                                        | 0, |

| _          | hardware model (b) [AHK22].                                                                                                                                                                                                                                                | 38 |

| 3.9        | The working scheme of the AQOSA toolkit [AHK22]                                                                                                                                                                                                                            | 41 |

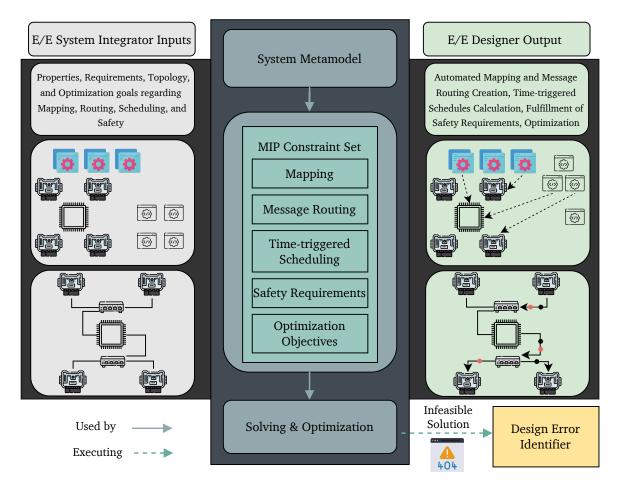

| 4.1                                           | The architecture of the proposed model-based framework. The left and right columns, representing E/E System Integrator Inputs and the E/E Designer Output, respectively, constitute the frontend. The middle box denotes the backend of the tool. In the framework's frontend, an E/E architecture is modeled by an E/E system architect. This modeling includes defining requirements, properties, and addressing various problems. The modeled E/E architecture is transformed into MIP formulations using the MDD approach. These formulations are then solved and optimized in the tool's backend. Finally, the optimal solution is visualized in the frontend of the framework.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 53       |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.2                                           | The overview of the framework, including modeling, synthesis, and design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

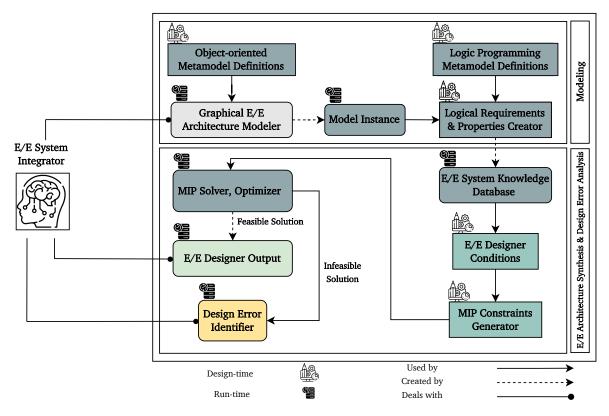

|                                               | error analysis parts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 59       |

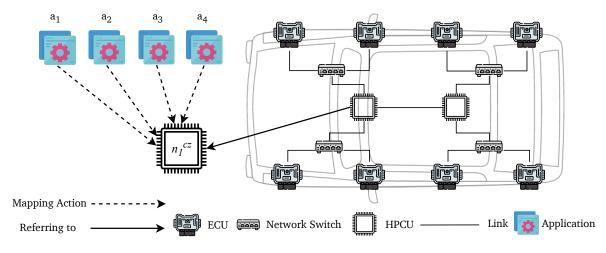

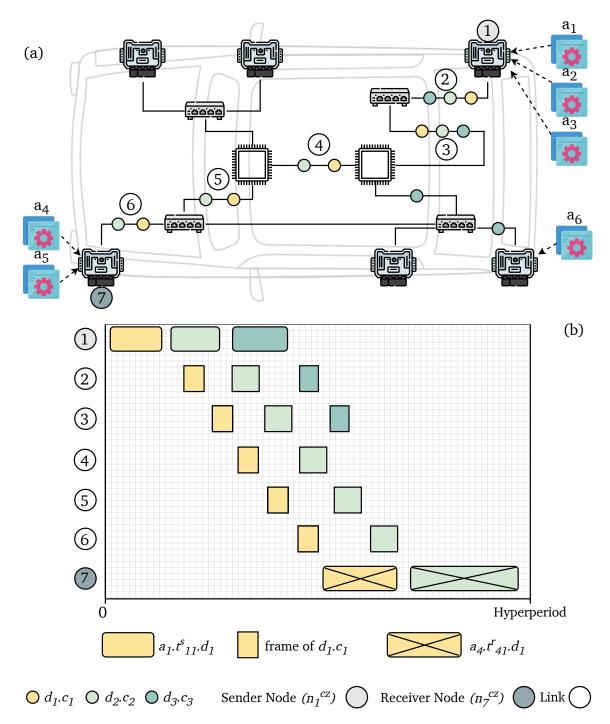

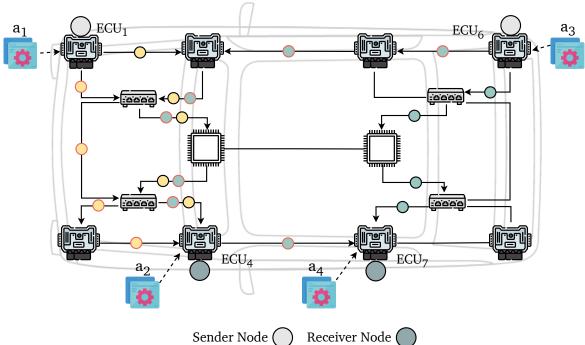

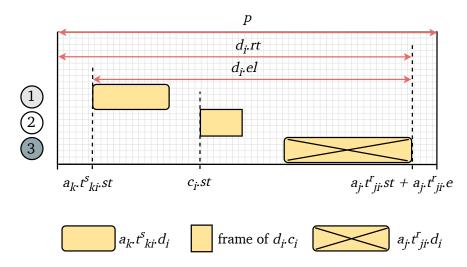

| <ul><li>4.3</li><li>4.4</li><li>4.5</li></ul> | A vehicle architecture including assignment of applications to an HPCU $(n_1^{cz})$ .<br>(a) A vehicle topology which shows generated paths for communication messages from senders to the receivers and mapped applications to the control nodes. Each colorful dot represents a communication task associated with a communication message. In this example, each application comprises a single application thread. (b) Calculated time-triggered schedules from the sender $(n_1^{cz})$ to the receiver $(n_7^{cz})$ . It includes schedules for the sender (number one, with thread slots that are not crossed) and the receiver application threads (number seven, with thread slots that are crossed). The schedules of communications tasks (yellow and light green frames of the tasks in numbers two to six) over the generated path (only the enumerated route in (a)) are also included. The path routing two communication messages $(d_1 \text{ and } d_2)$ is considered. As can be seen, message dependency for the sender and receiver and path dependency for communication tasks are fulfilled. The representations for light green frames are similar to the yellow ones [AMK23]. A vehicle architecture comprising intermediate and control nodes, links, and assigned applications to ECUs. A single (arrows with S) and a multicast (ar- | 61       |

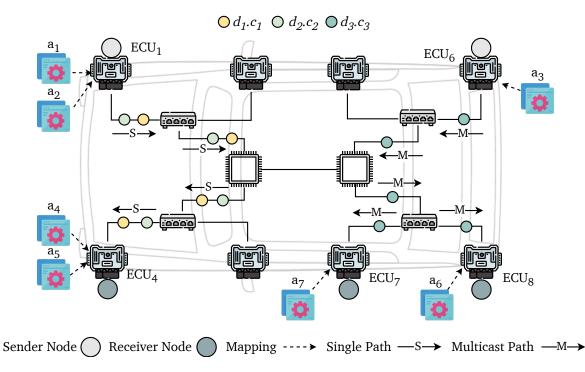

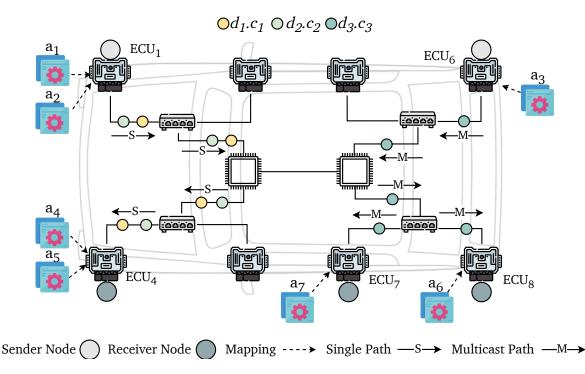

|                                               | rows with M) paths are generated in order to send communication messages (colored dots), created by applications, from sender nodes to receiver nodes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 67       |

| 4.6                                           | A modeled car architecture comprising intermediate and control nodes, links,<br>and assigned applications to ECUs. A redundant (yellow dot with red border<br>line) and a homogeneous redundant (green dot with red border line) routes<br>are created in order to send communication messages (colored dots), created                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| 4.7                                           | by applications, from sender nodes to receiver nodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 70<br>78 |

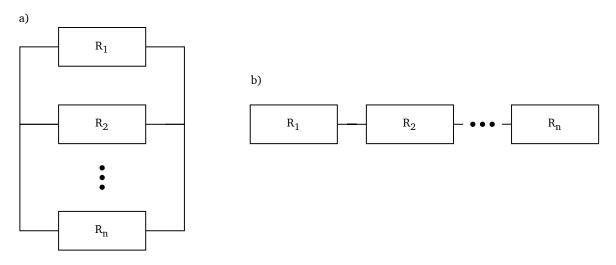

| 4.8                                           | a) A parallel system including multiple elements. b) A series system compris-<br>ing multiple elements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 84       |

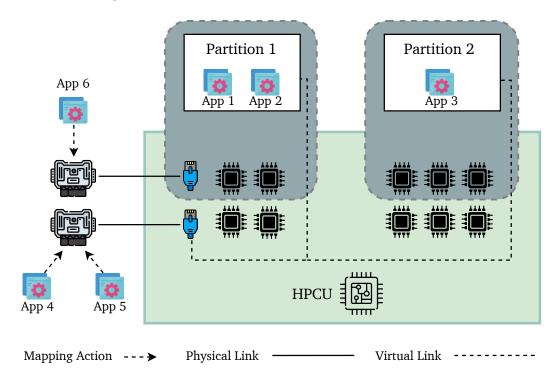

| 4.9                                           | Graphical representation of the functioning of the hypervisor constraints im-<br>plemented in the meta-model presented in Chapter 4, exemplified by the trans-<br>mission of communication messages. This exemplary scenario shows an HPCU<br>comprising 10 CPU cores and two communication interface devices running<br>two partitions. Partition 1 has exclusive control over two cores and one in-<br>terface device, while partition 2 controls three cores, as indicated by the dark<br>green boxes. The rest of the CPU cores and the other interface device are<br>shared among both partitions. Assume that communication messages are sent<br>between $a_1$ and $a_6$ , $a_2$ and $a_4$ , and $a_3$ and $a_5$ . The two concepts of exclusive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 04       |

|                                               | resource allocation and resource sharing are shown in this figure [MAK24]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 86       |

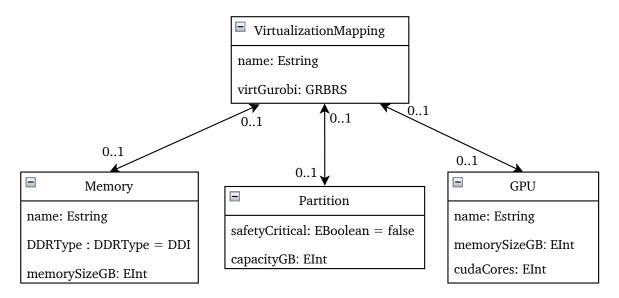

| 4.10 | The UML classes required for the hypervisor-related constraints                                                                                                                                                                                                                                                                                                                                                          | 87  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

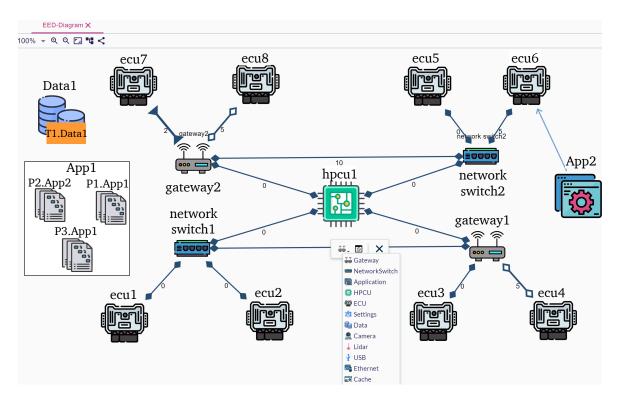

| 5.1  | An example of zonal E/E architecture model using the presented model-based framework [AMK23]                                                                                                                                                                                                                                                                                                                             | 98  |

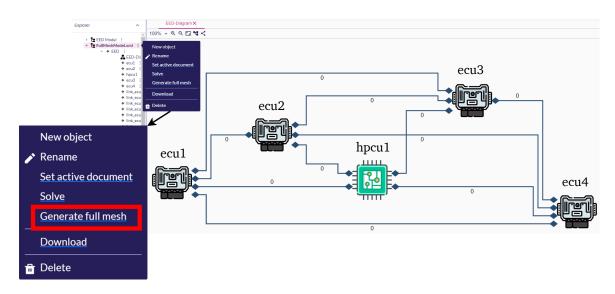

| 5.2  | A designed full-mesh E/E model including links and ECUs using the E/E De-<br>signer tool. By clicking on "Generate full-mesh", each hardware node is con-<br>nected to other nodes                                                                                                                                                                                                                                       | 99  |

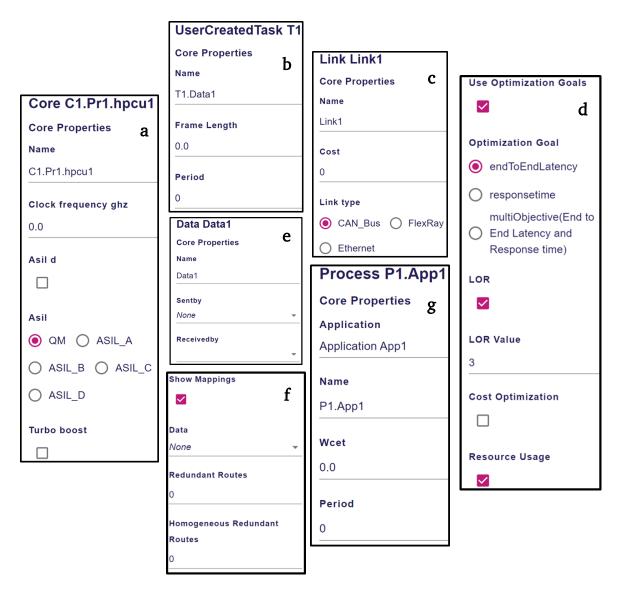

| 5.3  | Component properties (a), (b), (c), (e), (g), and optimization and solving settings (d) and (f) in the frontend of the presented framework [AMK23]                                                                                                                                                                                                                                                                       | 101 |

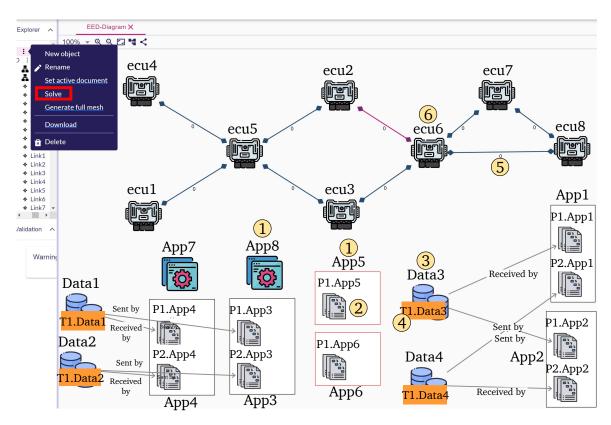

| 5.4  | A modeled E/E architecture by the presented tool including applications (No. one), application threads (No. two), communication messages (No. three), communication tasks (No. four), links (No. five), and ECUs (No. six). The model is solved and optimized by clicking on the <i>Solve</i> option (red rectangle) [AMK23]                                                                                             | 102 |

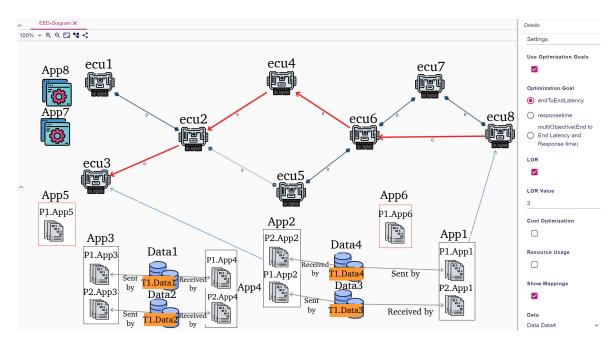

| 5.5  | A solution of the designed model in Figure 5.4 including mapping, message routing, and scheduling. Here, only the mappings for applications one and two related to the communication message four are displayed [AMK23]                                                                                                                                                                                                  | 103 |

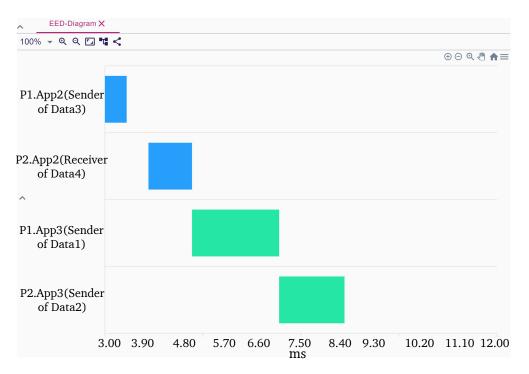

| 5.6  | Calculated time-triggered schedules by the introduced tool for running application threads on $ECU_3$ after mapping action as the solution for the model in Figure 5.5 [AMK23]                                                                                                                                                                                                                                           | 104 |

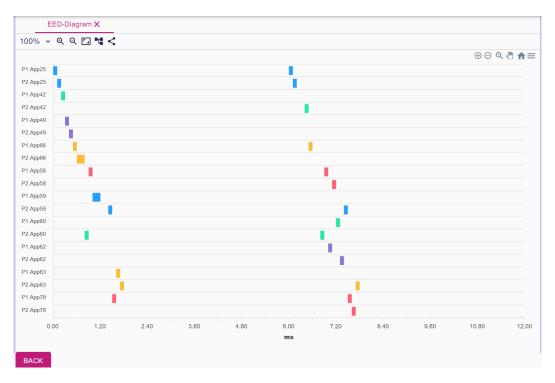

| 5.7  | Computed time-triggered schedules by the introduced tool for running 20 application threads belonging to 10 applications on an ECU after mapping action.                                                                                                                                                                                                                                                                 | 104 |

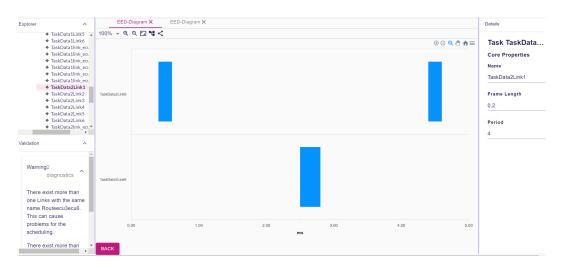

| 5.8  | Time-triggered schedules of two communication tasks over a link                                                                                                                                                                                                                                                                                                                                                          | 105 |

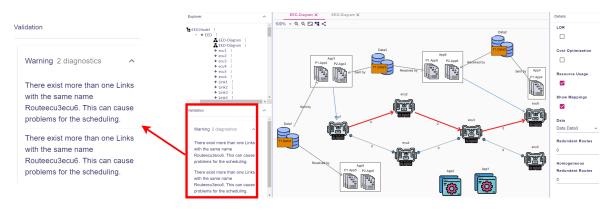

| 5.9  | A solution of a modeled E/E topology including mapping and message routing.<br>On the left side, several warnings are displayed regarding the validation of the<br>model.                                                                                                                                                                                                                                                | 106 |

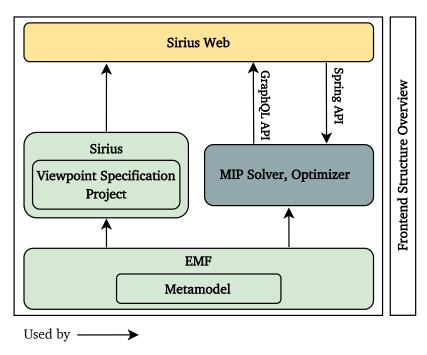

| 5.10 | An outline of the proposed framework's frontend describing the interaction of modified <i>Sirius Web</i> with other modules existing in the backend                                                                                                                                                                                                                                                                      | 107 |

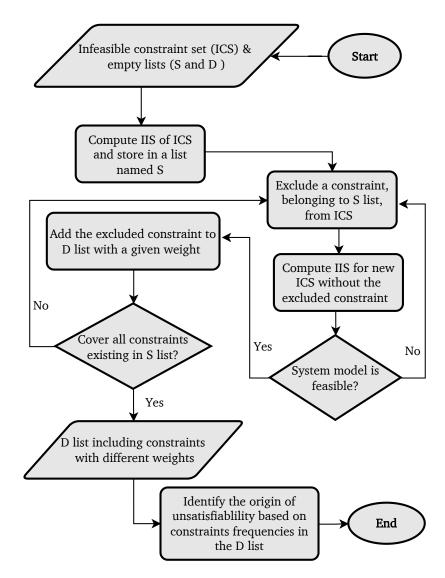

| 6.1  | The design error analysis flowchart using the IIS method                                                                                                                                                                                                                                                                                                                                                                 | 113 |

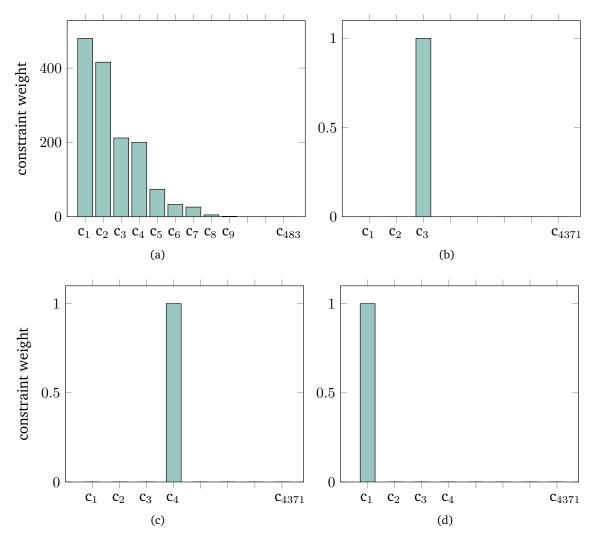

| 6.2  | The solutions of design error analysis approach created for various case studies using the IIS method.                                                                                                                                                                                                                                                                                                                   | 115 |

| 6.3  | The partial output of IIS computation for the case study presented in fig-<br>ure 6.2 (a)                                                                                                                                                                                                                                                                                                                                | 116 |

| 6.4  | The result of design error analysis approach using the IIS method for the use case described in figure 6.2 (a)                                                                                                                                                                                                                                                                                                           | 117 |

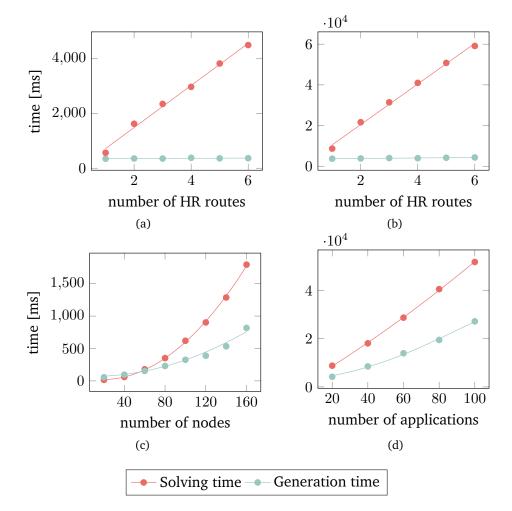

| 7.1  | The architectural synthesis times for the defined experimental scenarios in-<br>volving communication message routing integrated into the E/E Designer tool.<br>The constant variables for each scenario are established as follows: (a) Two<br>applications and one hundred nodes. (b) Twenty applications and one hun-<br>dred nodes. (c) Six HR paths and two applications. (d) One hundred nodes<br>and six HR paths | 121 |

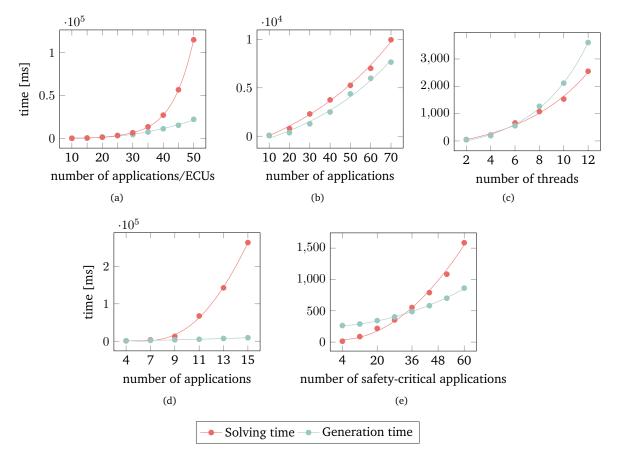

| 7.2  | Design-time performance evaluation of the introduced model-based frame-<br>work. The resource utilization constraint is applied to all use cases. (a) Each<br>application consists of two threads. (b) It is applied on a topology including                                                                                                                                                                                                                          |            |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|      | 8 ECUs, and each application has two threads. (c) The topology consists of 8 applications and 8 ECUs. (d) The topology comprises 8 ECUs, and each application consists of two threads with odd periods. (e) A zonal architecture including 15 ECUs is applied in this use case, and each safety-critical application has one thread. The boundary goals for resource utilization, maximum memory usage, and safety-critical mapping constraints are applied           | 123        |

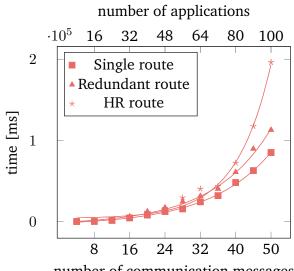

| 7.3  | The measurement of solving time in a case study includes the full capabilities of the proposed tool while considering different types of paths for transferring communication messages. The same architecture as in Figure 7.2 (e) is used in this experiment. This study incorporates the multi-objective optimization, which encompasses end-to-end latency, response time, and LOR, as well as the goals for resource utilization and maximum memory usage [AMK23] | 124        |

| 7.4  | Scalability analysis of the presented computer-aided tool. Generation and solv-<br>ing times for (a) a full-mesh architecture and (b) a zonal topology, each includ-<br>ing 15 ECUs [AMK23].                                                                                                                                                                                                                                                                          | 126        |

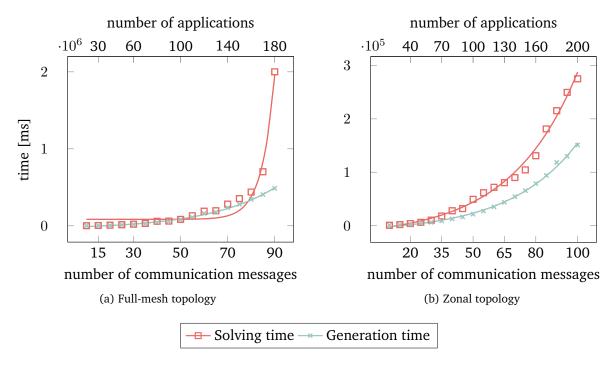

| 7.5  | The six relevant development kits serve as an HPCU including (1) Nvidia Drive AGX Xavier, (2) Nvidia Pegasus, (3) MPPA-DEV4 development platform, (4) R-Car H3 and M3 Starter Kits, (5) AVA 3501, (6) Nuvo 7208VTC.                                                                                                                                                                                                                                                   | 128        |

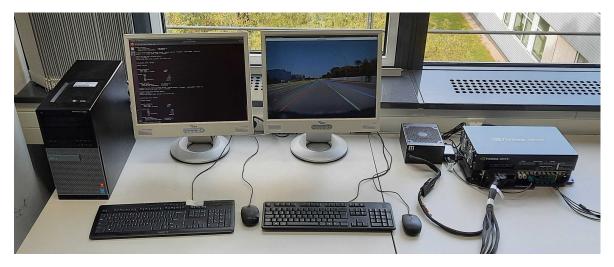

| 7.6  | The mapping experimental setup using the Nvidia Drive AGX. On the left is the host computer, and on the right is the Nvidia Drive AGX Xavier with the power adapter. Both are connected to a monitor and other peripherals                                                                                                                                                                                                                                            | 129        |

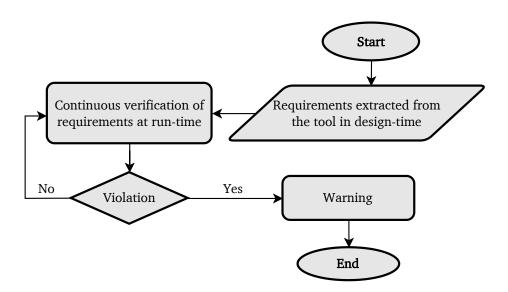

| 7.7  | The Monitoring mechanism flow chart.                                                                                                                                                                                                                                                                                                                                                                                                                                  | 130        |

| 7.8  | The Monitoring GUI. The threshold values for each specified requirement can<br>be chosen. For example, the threshold value of the CPU usage can be defined                                                                                                                                                                                                                                                                                                            | 101        |

| 7.9  | inside the red rectangle                                                                                                                                                                                                                                                                                                                                                                                                                                              | 131<br>131 |

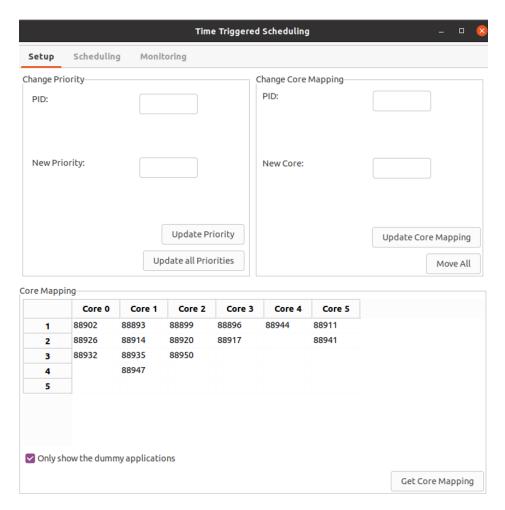

| 7.10 | The primary GUI including all features. Users can select the priority and as-<br>signment for each task on the window.                                                                                                                                                                                                                                                                                                                                                | 132        |

| 7.11 | The primary GUI including all features. The window visually represents the priority, period, and execution time associated with each task.                                                                                                                                                                                                                                                                                                                            | 133        |

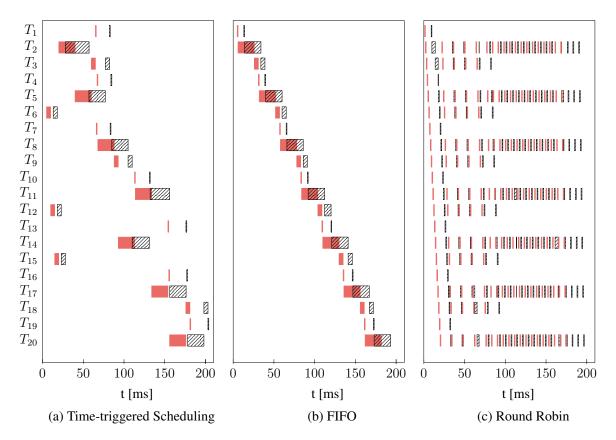

| 7.12 | Gantt charts of the different scheduling solutions for CPU 5. The red bars represent the planned execution, while the hatched bars stand for the actual execution [AMK23]                                                                                                                                                                                                                                                                                             | 134        |

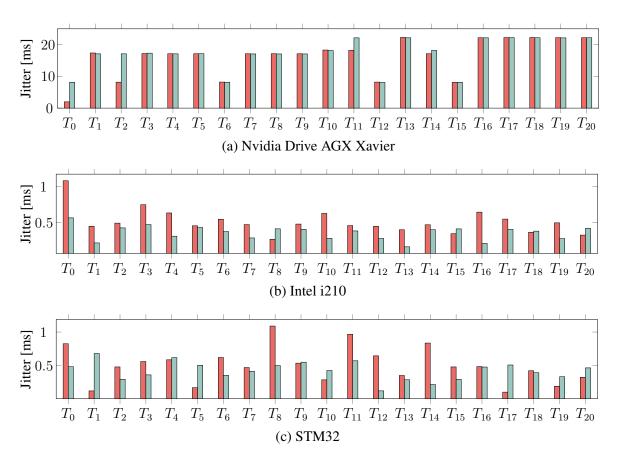

| 7.13 | Start and stop jitters of each thread measured for the time-triggered scheduling over one hyperperiod. These are the measurements on CPU core 5. Red bars represent the start jitter, and the green bars the stop jitter [AMK23]                                                                                                                                                                                                                                      | 135        |

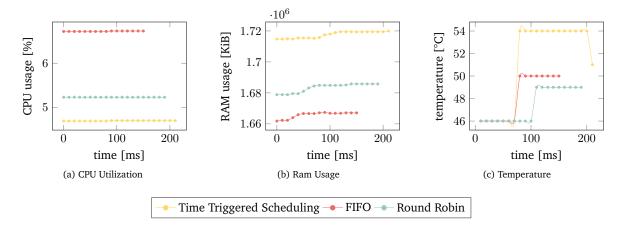

| 7.14 | Comparison of different metrics. Yellow is the time-triggered scheduling, red is FIFO scheduling, and green is Round Robin scheduling [AMK23]                                                                                                                                                                                                                                                                                                                         | 136        |

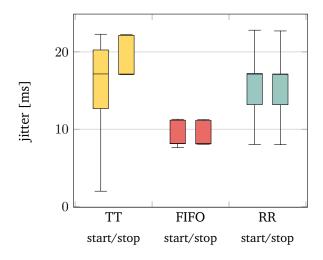

| 7.15 | Spread of start and stop jitter for the tested scheduling policies. The box plot shows the minimum and maximum values, the lower and upper quantiles,                                                                                                                                                                                                                                                                                                                 |            |

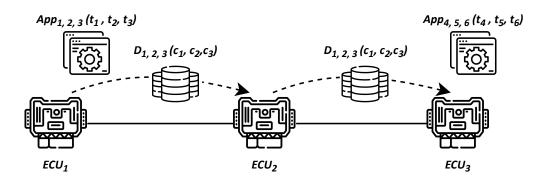

| 7.16 | and the mean. The yellow, red, and green boxes represent results for time-<br>triggered, FIFO, and Round Robin scheduling schemes, respectively Topology of the tested communication setup. Threads 1-3 on $ECU_1$ each send                                                                                                                                                                                                                                          | 136        |

|      | a communication packet to threads 4-6 on $ECU_3$ . All three packets $(c_1, c_2, c_3)$ are routed over $ECU_2$ [AMK23].                                                                                                                                                                                                                                                                                                                                               | 137        |

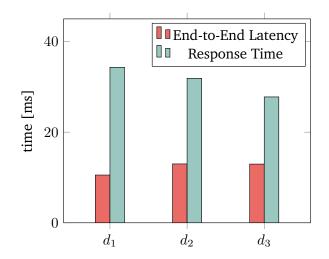

| Measured end-to-end latency and response times of the three communication messages using Nvidia Drive AGX, Nvidia TX2, and Intel i210 developer kits                                                                                        |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| as the setup                                                                                                                                                                                                                                | 138 |

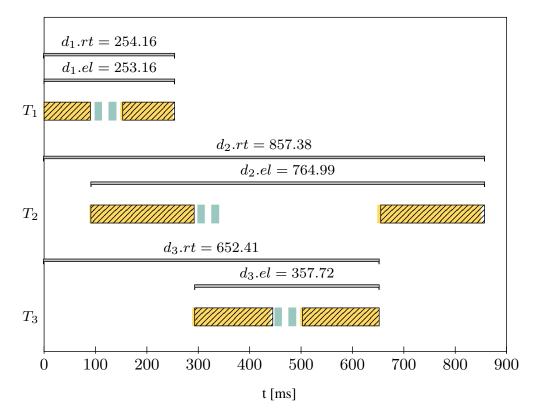

| Results of the communication evaluation experiment using STM development kits. The yellow bars represent the expected execution, while the hatched bars                                                                                     |     |

| represent the actual execution times of the sender and receiver applications.                                                                                                                                                               |     |

| The green bars indicate the planned schedule of the communication messages.                                                                                                                                                                 |     |

| The response time and end-to-end latency of each communication message are                                                                                                                                                                  |     |

| also shown [AMK23]                                                                                                                                                                                                                          | 138 |

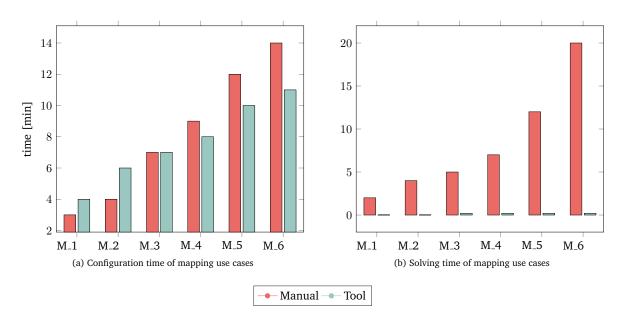

| Results of the quantitative evaluation for the mapping case studies using a manual approach and the E/E Designer tool. (a) The required setup time for                                                                                      |     |

| each use case. (b) The required solving time for each use case                                                                                                                                                                              | 140 |

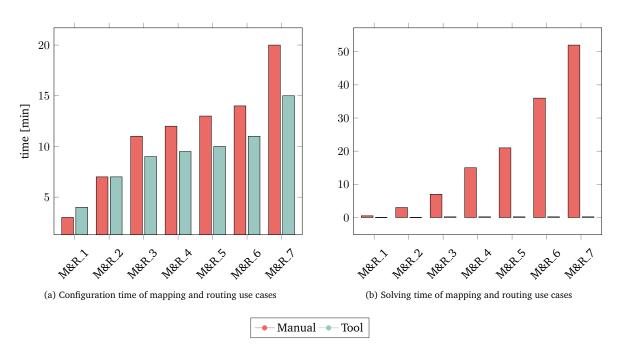

| Results of the quantitative evaluation for the mapping and routing case studies<br>using manual and tool-assisted approaches. (a) The required setup time for<br>each use case. (b) The required solving time for each use case. The manual |     |

| solving time does not include visualization and optimality of the solutions                                                                                                                                                                 | 142 |

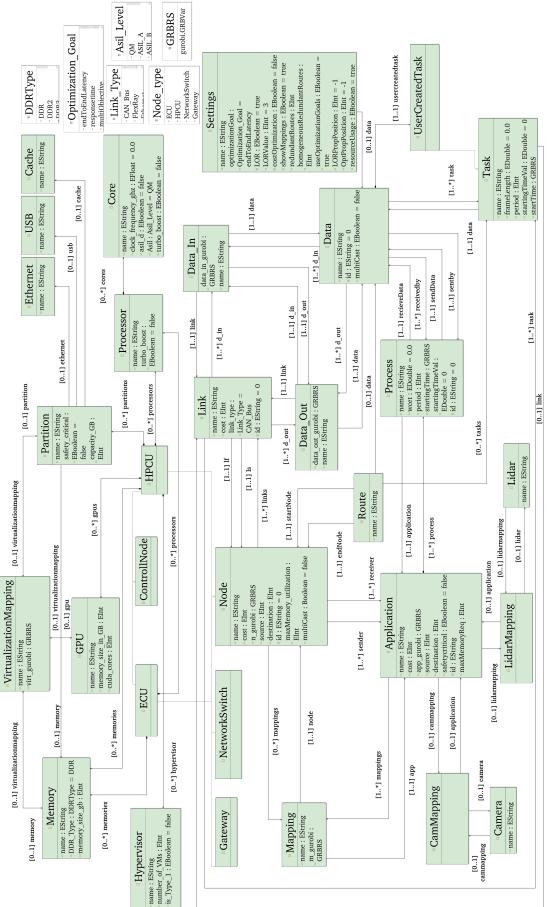

| Object-oriented metamodel for the E/E Designer framework. The green boxes indicate the classes, and the white boxes represent the types of data and ele-                                                                                    | 1   |

| ments used within the classes                                                                                                                                                                                                               | 151 |

## **List of Tables**

| 3.1  | Problem's type, problem's attributes, and DSE type of the above-mentioned  |     |

|------|----------------------------------------------------------------------------|-----|

|      | open-source frameworks.                                                    | 42  |

| 3.2  | The used optimization algorithms, and the covered optimization and safety- |     |

|      | relevant attributes in the above-explained open-source frameworks          | 43  |

| 3.3  | Features and DSE type of the above-presented commercial tools              | 47  |

| 7.1  | Periods and execution times of threads for each sample application         | 134 |

|      | Communication solution calculated by the presented framework.              |     |

| , .= |                                                                            | 207 |

| A.1  | Notation Reference.                                                        | 149 |

# List of Algorithms

| 1 | Cycle Breaker and Connection of Incoming & Outgoing Messages | 73  |

|---|--------------------------------------------------------------|-----|

| 2 | CMR                                                          | 90  |

| 3 | CSCT                                                         | 92  |

| 4 | PD                                                           | 93  |

| 5 | DVC                                                          | 114 |

# 1

### Introduction

#### 1.1 Vehicle E/E Architecture and its Development

The automotive industry is profoundly transforming, driven by technological advancements and a growing emphasis on safety, connectivity, and automation. Central to these changes is the concept of electrical and/or electronic (E/E) architecture, which refers to the organizational structure and integration of electrical and electronic systems within a vehicle. The development of E/E systems, including the technical approaches, requirements, design structure decisions, and methods, are heavily influenced by the vehicle's E/E architecture [AFK21a; AMK23].

The E/E architecture can be viewed from multiple perspectives. One is the physical aspect that shows the positioning and connections of elements in the car, such as electronic control units (ECUs), sensors, actuators, gateways, power supply, and switches. It also includes the placement of communication networks, wiring harnesses, and power distribution setups. Furthermore, the software used in the vehicle plays a crucial role in the E/E architecture, especially as the level of autonomy in cars has been advancing in recent years. Another perspective is that the E/E architecture can be seen as a logical representation, emphasizing the connection and interaction between the components and elements incorporated into the vehicle. In this context, the E/E architecture can be understood as pertaining to the transfer of data, the movement of signals, and the protocols for communication and interfaces [AHK22].

Recent advancements in driving automation have led to a significant increase in the number of companies investing in the development of autonomous vehicles. This effort has not only resulted in the inclusion of non-essential features, such as gaming using a vehicle's infotainment system, but also the implementation of advanced driver assistance systems (ADAS) to enhance safety and comfort for drivers. As a result, the E/E architecture of automobiles has undergone significant improvements, including the integration of various sensors, actuators, and powerful computing units to process the large amounts of data collected from the sensors for both critical and non-critical functions [AHK22].

Over the past few years, as the number of functionalities and features in vehicles has grown, the E/E architecture of cars has undergone significant changes [AFK20]. Initially, each ECU was responsible for managing a single function. As the number of functions increased, domain-specific ECUs emerged, responsible for controlling a set of functions related to a specific area or domain. These functional domains that require domain ECUs are usually compute-intensive and connect to many input/output (I/O) devices [AFK21b]. Each domain ECU is connected to multiple function-specific control units. A zonal ECU is responsible for distributing data and power throughout the vehicle, for example, by distributing the power

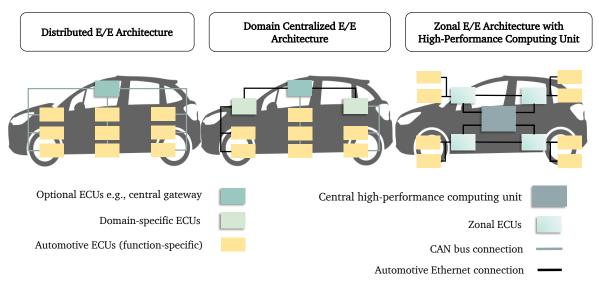

**Figure 1.1:** The figure presents the evolution of vehicle E/E architecture. Distributed E/E architectures were used until 2019, while domain-centralized architectures are used nowadays as vehicle architectures. The zonal architecture shows the future car E/E architecture [AHK22].

from the vehicle battery to various sensors and actuators using zonal controllers. Similarly, data is spread over the vehicle's network and transferred from sensors to other actuators/sensors and controllers using zonal ECUs. In addition, this type of ECU supports any feature available in the specific vehicle zone and acts as a gateway, switch, and smart junction box. Furthermore, it supports any interface for sensors, actuators, and displays [AMK23; AHK22].

Considering the ADAS and self-driving applications, using domain-specific ECUs increases the number of ECUs with substantial growth in the wiring harness, communication bandwidth, cost, software variants, and software complexity. Therefore, multi-core ECUs can be considered a solution to reduce the number of ECUs, cost, wiring harness, software complication, and variations. In addition, the multi-core technology has promptly been extending in different areas of embedded systems to deliver an appropriate performance for artificial intelligence (AI)-based applications and systems by giving scalable computing power [Bro06; AHK22]. A high-performance computing unit (HPCU) is a multi-core ECU that is composed of multiple system on chips (SoCs) that include several cores, a graphics processing unit (GPU), random access memory (RAM), and deep learning accelerators. These components work together to process high computational power-demand applications such as various object detection applications for ADAS functionalities [AFK21b]. The central computing unit is a fully scalable and upgradeable platform that connects to Edge and Cloud backend and uses cloud computing to process intensive vehicle functionalities. Additionally, it can act as the zonal gateway, meaning it serves as the master and core functionality of the vehicle [AHK22].

As shown in Figure 1.1, the development of E/E architectures has progressed through various stages. The initial stage referred to as distributed E/E architecture, involves using function-specific ECUs and a central gateway connected via a controller area network (CAN) bus. This architecture allows for stronger collaboration among ECUs and the ability to handle more complex functions, such as adaptive cruise control, as well as the potential for cross-functional connections. The next evolution in E/E architecture is known as domain centralized architecture, which utilizes domain-specific ECUs [AHK22]. As shown in Figure 1.1, function-specific control units are connected to domain-specific ECUs using both a CAN bus and an Ethernet connection. Moreover, this type of architecture also utilizes the central gateway ECU. This architecture is capable of handling even more complex functions and can also optimize cost through the consolidation of functions. For example, one domain-specific ECU