Technical University of Munich Department of Electrical and Computer Engineering Chair of Electronic Design Automation

# Fast RTL-based Fault Injection Framework for RISC-V Cores

Master's Thesis

Johannes Geier

Technical University of Munich Department of Electrical and Computer Engineering Chair of Electronic Design Automation

# Fast RTL-based Fault Injection Framework for RISC-V Cores

## Master's Thesis

Johannes Geier

Advisor: M.Sc. Uzair Sharif

Advising Professor: Prof. Dr.-Ing. habil. Daniel Müller-Gritschneder

Topic issued: 01.09.2019 Date of submission: 06.03.2020

Johannes Geier Hopfenstraße 29 85309 Pörnbach johannes.geier@tum.de

#### **Abstract**

The growing demand of processing power in an increasing number of embedded systems deployed in various circumstances has led to new challenges towards the development of such systems. One of these challenges is a digital system's resiliency against soft errors that can alter internal states and lead to unforeseen and sometimes critical behavior. Simulating such errors at a system's early design phases can help with integrating and evaluating countermeasures. This work introduces a fast Register Transfer Level (RTL)-based fault injection framework for soft-error evaluations of RISC-V processor cores. To enable injections, a tool was developed that transforms the RTL model and builds a specific injection Application Programming Interface (API) from the core's hardware description. The modified RTL and built API were put to test in a proof of concept framework evaluating an open-hardware RISC-V core's behavior towards random bit flips in its internal states. The framework is characterized by its utilization of automatically generated, however, core-specific sources which enable a high fault injection capability while maintaining low simulation overhead. The evaluation results were analyzed with respect to the probability of a certain error occurring after a random bit flip and the probability of a specific injection target being the cause for a certain error.

## Contents

| 1. | Intro      | oduction                                            |

|----|------------|-----------------------------------------------------|

|    | 1.1.       | Motivation                                          |

|    | 1.2.       | Contributions                                       |

|    | 1.3.       | Tasks                                               |

| 2. | Bac        | kground                                             |

|    | 2.1.       | Fault Model                                         |

|    |            | 2.1.1. Soft Errors                                  |

|    |            | 2.1.2. Injection Model                              |

|    |            | 2.1.3. Fault Effect Classification                  |

|    | 2.2.       | Verilator RTL                                       |

|    |            | 2.2.1. Verilator                                    |

|    |            | 2.2.2. Fault Injection                              |

|    |            | 2.2.3. RegPicker                                    |

|    | 2.3.       | Simulation Target: RI5CY                            |

|    |            | 2.3.1. Pipeline                                     |

|    |            | 2.3.2. Configuration                                |

|    |            | 2.3.3. Injection Targets                            |

|    | 2.4.       | LLVM                                                |

| 3. | Veri       | lator RTL Modification                              |

|    | 3.1.       | Verilator Evaluation                                |

|    |            | 3.1.1. Synthesis                                    |

|    |            | 3.1.2. Fault Injection                              |

|    | 3.2.       | Modification                                        |

|    |            | 3.2.1. Target Variables as Extended Data Structures |

|    |            | 3.2.2. Source Transformation                        |

|    | 3.3.       | Implementation                                      |

|    |            | 3.3.1. Injection API Builder                        |

|    |            | 3.3.2. Injection Rewriter                           |

| 4. | Sim        | ulation                                             |

|    | 4.1.       | Simulation Framework                                |

|    |            | 4.1.1. Modified VRTL Core                           |

|    |            | 4.1.2. Reduced Virtual System on Chip               |

|    |            | 4.1.3. Injection Scheduler                          |

|    |            | 4.1.4. User Interface                               |

|    | 4.2.       | Simulation Setup                                    |

|    | <b>-</b> - | 4.2.1. Target Software                              |

#### Contents

|     |        | 4.2.2. | Evaluation         |           |          |      | <br> | <br> |  | <br> | • | <br> |   | 49 |

|-----|--------|--------|--------------------|-----------|----------|------|------|------|--|------|---|------|---|----|

| 5.  | Eval   | uation |                    |           |          |      |      |      |  |      |   |      |   | 51 |

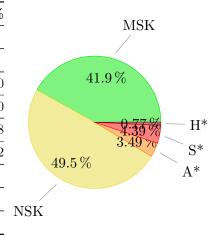

|     | 5.1.   | Error  | Classification     |           |          |      | <br> | <br> |  | <br> |   | <br> |   | 51 |

|     | 5.2.   | Result | s Analysis         |           |          |      | <br> | <br> |  | <br> |   | <br> |   | 53 |

|     |        | 5.2.1. | Statistical Fault  | Effect Pr | obabilit | ty . | <br> | <br> |  | <br> |   | <br> |   | 53 |

|     |        | 5.2.2. | Data Processing    | and Visu  | alizatio | n.   | <br> | <br> |  | <br> |   |      |   | 55 |

| 6.  | Resu   | ılts   |                    |           |          |      |      |      |  |      |   |      |   | 59 |

|     | 6.1.   | Fault  | Effect Probability |           |          |      | <br> | <br> |  | <br> |   | <br> |   | 59 |

|     | 6.2.   | Fault  | Effect Causation   |           |          |      | <br> | <br> |  | <br> |   |      |   | 64 |

|     |        | 6.2.1. | Hang-up Errors     |           |          |      | <br> | <br> |  | <br> |   | <br> |   | 64 |

|     |        | 6.2.2. | System Errors      |           |          |      | <br> | <br> |  | <br> |   |      |   | 67 |

|     |        | 6.2.3. | Application Erro   | rs        |          |      | <br> | <br> |  | <br> |   | <br> |   | 68 |

|     | 6.3.   | Concl  | usion              |           |          |      | <br> | <br> |  | <br> |   | <br> | • | 71 |

| 7.  | Sum    | mary   |                    |           |          |      |      |      |  |      |   |      |   | 73 |

| Α.  | Арр    | endix  |                    |           |          |      |      |      |  |      |   |      |   | 75 |

| Bil | oliogr | aphy   |                    |           |          |      |      |      |  |      |   |      |   | 85 |

# List of Figures

| 2.1. | Simple register stage                                | 19 |

|------|------------------------------------------------------|----|

| 2.2. | Single-bit target fault                              | 20 |

| 2.3. | Verilator flow                                       | 22 |

| 2.4. | Signal types and classification                      | 23 |

| 2.5. | RI5CY block diagram                                  | 24 |

| 2.6. |                                                      | 26 |

| 2.7. |                                                      | 27 |

| 3.1. | 1                                                    | 29 |

| 3.2. | $\mathbf{J}$                                         | 30 |

| 3.3. | Injection call with target dictionary                | 37 |

| 3.4. | API Builder process                                  | 38 |

| 3.5. | •                                                    | 38 |

| 3.6. | <b>3</b> 0                                           | 39 |

| 3.7. | 0                                                    | 40 |

| 3.8. | LLVM Tool - Finding sequential injection assignments | 41 |

| 4.1. | Simulation framework                                 | 43 |

| 4.2. | Simulation framework toolchain                       | 48 |

| 4.3. | Evaluation run                                       | 50 |

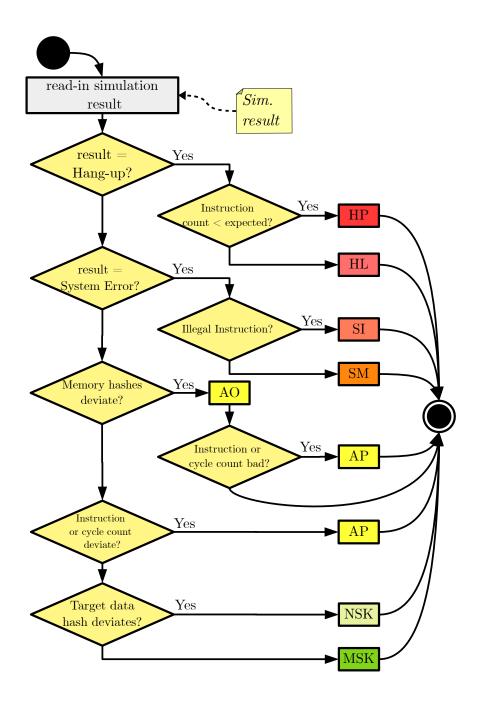

| 5.1. | Fault effect classification                          | 52 |

| 5.2. |                                                      | 54 |

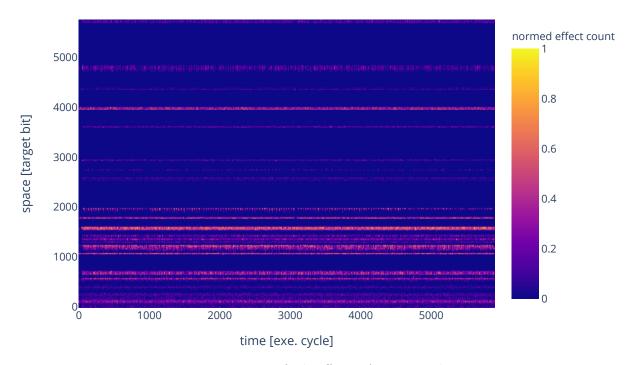

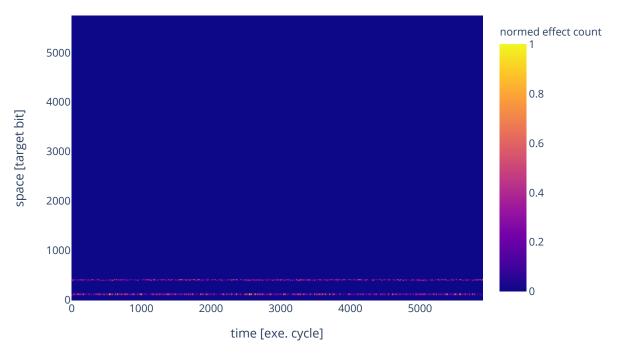

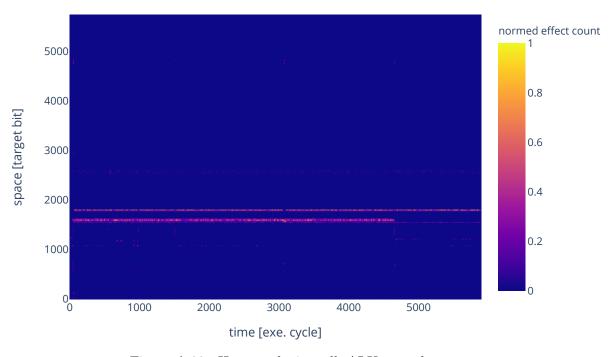

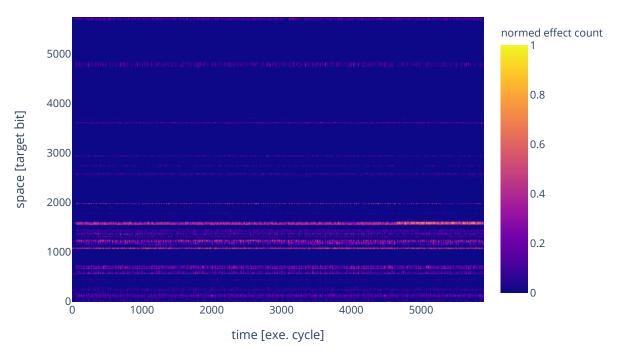

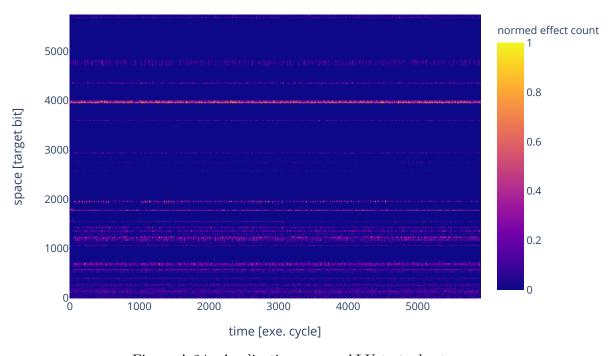

| 5.3. | Erroneous fault effects, ALU test - heat map         | 57 |

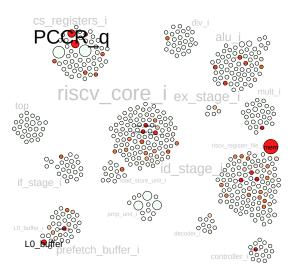

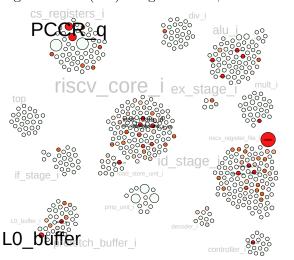

| 6.1. | Hang-up pipeline stall, ALU test - causation cluster | 64 |

| 6.2. | Hang-up logic stall, ALU test - causation cluster    | 66 |

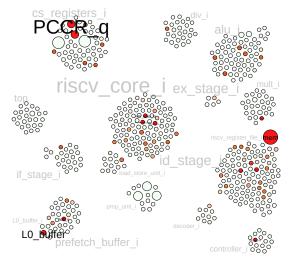

| 6.3. | System error, ALU test - causation cluster           | 67 |

| 6.4. | Application error, ALU test - causation cluster      | 69 |

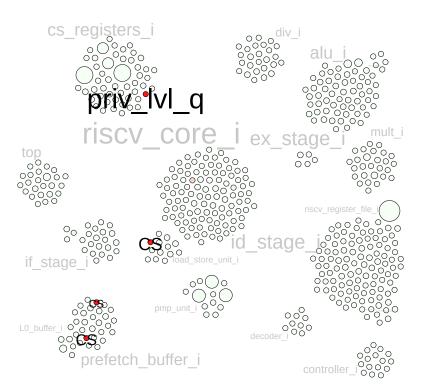

| A.1. | RI5CY injection target cluster                       | 75 |

| A.2. | RI5CY hierarchy - modules and cell instances         | 76 |

| A.3. | (HP) Pipeline stall, ALU test                        | 79 |

|      | ( ) ( )                                              | 79 |

| A.5. | (HP) Pipeline stall, MUL test                        | 79 |

| A.6. | (HL) Logic stall, MUL test                           | 79 |

|      | \                                                    | 79 |

| A.8. | (HL) Logic stall, AES test                           | 79 |

| A 9  | (SI) Illegal instruction ALU test                    | 80 |

## $List\ of\ Figures$

| A.10.(SM) Memory access, ALU test                | 80 |

|--------------------------------------------------|----|

| A.11.(SI) Illegal instruction, MUL test          | 80 |

| A.12.(SM) Memory access, MUL test                | 80 |

| A.13.(SI) Illegal instruction, AES test          | 80 |

| A.14.(SM) Memory access, AES test                | 80 |

|                                                  | 81 |

|                                                  | 81 |

|                                                  | 81 |

| A.18.(AP) Program Flow, MUL test                 | 81 |

|                                                  | 81 |

| A.20.(AP) Program flow, AES test                 | 81 |

| A.21.Hang-up pipeline stall, ALU test - heat map | 82 |

|                                                  | 82 |

|                                                  | 83 |

| A.24.Application errors, ALU test - heat map     | 83 |

## List of Tables

| 0 0                                              | 25<br>26                |

|--------------------------------------------------|-------------------------|

|                                                  | <b>3</b> 4              |

|                                                  | 34                      |

|                                                  |                         |

| Instruction transmission value                   | 36                      |

| User interface input table                       | 47                      |

| Target software test properties                  | 49                      |

| Fault effect priority levels                     | 51                      |

| 1 0                                              | 55                      |

|                                                  |                         |

| Fault effect probability, ALU test - all targets | 59                      |

| Fault effect probability, MUL test - all targets | 60                      |

| Fault effect probability, AES test - all targets | 60                      |

| Fault effect probability, ALU test - CSR targets | 61                      |

| Fault effect probability, ALU test - GPR targets | 62                      |

|                                                  | 63                      |

| Hang-up pipeline stall - influential targets     | 65                      |

| Hang-up logic stall - influential targets        | 66                      |

| System error causation - influential targets     | 68                      |

|                                                  | 70                      |

| Fault effect probability, MUL test - GPR targets | 77                      |

|                                                  | 77                      |

|                                                  | 77                      |

|                                                  | 78                      |

| • • • • • • • • • • • • • • • • • • • •          | 78                      |

| • • • • • • • • • • • • • • • • • • • •          | 78                      |

|                                                  | RISC-V privilege levels |

List of Tables

# Listings

| 2.1. | Example AST source                                 | 7 |

|------|----------------------------------------------------|---|

|      | Example AST dump                                   |   |

| 3.1. | Example SystemVerilog                              | 0 |

| 3.2. | Example Verilator sequential body                  | 0 |

| 3.3. | Pseudo-modified example Verilator sequential body  | 2 |

|      | Pseudo overloading class - extended data structure |   |

|      | Injection macro                                    |   |

| 4.1. | Virtual SoC clock-spin                             | 5 |

| 4.2. | Injection scheduler hook                           | 5 |

| 4.3. | Simulation run output                              | 0 |

Listings

### Acronyms

API Application Programming Interface

**AST** Abstract Syntax Tree

CPU Central Processing Unit

**CSR** Control and Status Register

**FSM** Finite and State Machine

GCC GNU Compiler Collection

**GNU** GNU Debugger

**GPR** General Purpose Register

**HDL** Hardware Description Language

IPS Instructions Per Second

ISA Instruction Set Arichitecture

ISS Instruction Set Simulation

**LSU** Load-Store Unit

MPU Memory Protection Unit

MSB Most Significant Bit

OS Operating System

PULP Parallel Ultra Low Power Platform

PRNG Pseudo Random Number Generator

RISC Reduced Instruction Set Computer

RTL Register Transfer Level

SET Single Event Transient

SoC System on Chip

Ul User Interface

VP Virtual Prototype

VRTL Verilator Register Transfer Level

VSoC Virtual System on Chip

XML eXtensible Markup Language

#### 1. Introduction

#### 1.1. Motivation

Most physical processes are controlled by information technology systems. Decentralization of control systems, access through large scale networks and more complex application software and inclusion of full-scale operating systems (OS) have lead to generally higher loads on embedded systems. This growing demand of processing power for a previously reasonably complex part of modern electronics has been met by the possibility to feature a much greater amount of components in an increasingly smaller form factor. At the same time, testing and even more so verification struggles to keep up with this growth. One way to encounter this development can be to utilize virtual prototypes (VPs) of such systems in early stages of design.

While designer's of application-level software use VP sockets to study and optimize properties of code and its means of employment, hardware developers might have to look into more than just the behavior of cross-compiled code. Since the deployed unit will manipulate our physical world, the same can be the case vice versa in an unintended way. A case of this are soft errors, where data storage elements inside the digital system are corrupted by unpredictable manipulators. These errors normally do not damage the system's hardware, however, might lead to erroneous behavior, thus, output of the system to the physical world. Soft errors can manifest themselves often by biased or unbiased bit-flips in sequential logic caused by radiation particles hitting such elements. Elaborating the impact of these errors on the system's application is a major concern on the design strategies which questions the coverage of simulating soft errors in virtual prototypes.

Current research tasked itself not only with investigating the impact of soft-errors but also how one should approach their modeling with respect to the level of abstraction. The most prominent idea is to do so on a functional or instruction level. There, instructions of the simulation target instruction set architecture (ISA) are translated just-in-time to equivalents of the host's ISA, where the simulation is performed. Prominent examples for this type of are QEMU and ETISS (TUM EI EDA n.d.). A more detailed approach is taken, when instructions are not only translated to the host ISA but interpreted. Here, the resulting traceable and instruction-wise execution emulates the ISA behavior (SiFive n.d.). Both ideas have in common that the smallest notion of time is one target instruction, therefore, can be summarized as instruction set simulation (ISS). A more fine-grained abstraction level is register transfer level (RTL). While ISS only mimics the system's behavior, an RTL simulation imitates the hardware itself. To clarify the dimensions of those levels, a gearbox simulation could be imagined. Depending on the observational goals, a simple equation describing how speed and momentum are translated from input to output could be enough. For processing systems, such equations would corre-

#### 1. Introduction

spond to the ISS level. This equation will not yield any information about the gearbox's inner workings that enable the translation nor how certain parts interact with each other. With the assumption of an unbreakable gearbox, an equation would be enough. However, problems arise when a designer wants to introduce faults, where no information about alterations to the gearbox's behavior is known, e.g. a gear's teeth breaks and there is no information about how this affects the translation. In contrast, simulating the gearbox more precisely would not depend on information about the system's changed behavior as the new behavior is described through the changes in the hardware itself. For processing systems, an executable model of the gearbox's hardware would correspond to RTL.

Since the smallest notion of data storing elements in ISS are general purpose registers (GPRs) and optionally control and status registers (CSRs), a large portion of possible soft error victims are left out from simulation. Research has shown that high-level error injection methodologies, i.e. only injecting in registers and memory, can lead to highly imprecise results (Cho et al. 2013). Therefore, RTL would be the obvious choice for the level of abstraction in soft error simulations. However, a more fine-grained simulation comes with costs. In this case, computational effort to simulate these additional hardware components. Minimizing this simulation effort by modifying highly optimized cycle-accurate RTL simulators for soft error evaluation is the focus of this work.

#### 1.2. Contributions

In this work, the generation of an executable RTL model for a Reduced Instruction Set Computer (RISC) that enables guaranteed fault injection is explored. The focus lays on;

- understanding Verilator as the main tool building the host-executable model from the hardware description language (HDL) sources,

- modifying the Verilator RTL model in order to enable cycle-accurate, and target-explicit injection of errors,

- proposing a proof-of-concept RTL fault injection toolchain that builds an injection framework from HDL sources and with minimal manual input,

- interpreting the results of a fault injection evaluation for a RISC example (RISC-V core).

#### 1.3. Tasks

First, the tool generating the executable model (VRTL), Verilator, has to be explored. This concludes understanding the VRTL to find ways to perform guaranteed fault injections on fault injection viable components, exclusively. Thus, injection targets have to be identified,

located and classified in order to optimize the overall simulation process by avoiding injections in model variables that do not correspond to real-world soft error victims.

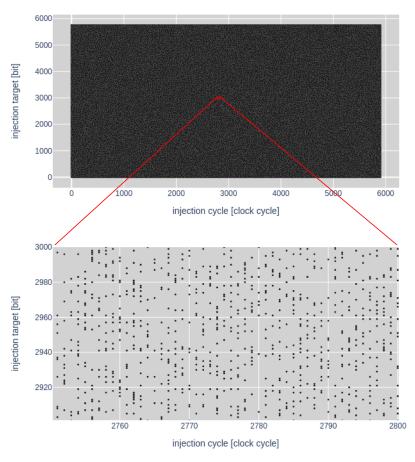

Next, an algorithm must be developed and implemented that modifies the VRTL sources to allow cycle-accurate injections. Then, the modified VRTL is incorporated in a simulation and fault injection framework for a RISC-V core enabling execution of cross-compiled application code and fault injection scheduling. At last, space (bit) and time (execution cycle) random faults are injected and their impact on the processor core analyzed.

## 1. Introduction

#### 2.1. Fault Model

#### 2.1.1. Soft Errors

As a type of transient errors in digital systems, soft errors can be mostly traced back to effects of neutron and alpha particle impacts on circuitry. The resulting fault can be modeled as a single event transient (SET) (Maniatakos et al. 2011) or sometimes also referred to as single event upsets (SEUs) (Baumann 2005). SEUs can affect combinational or sequential logic. However, sequential soft error victims, such as flip-flops and D-latches, have more impact on a system's behavior since their state is stored in-between system clock cycles and their state is only updated during a short latch-up phase. On the other side, combinational logic is continuously driven and converging to a stable state, thus, should have an inherent resiliency against SEUs where the transient impact is much smaller than the clock period. In designs with large propagation delays, thus, low clock frequencies, a SEU seldomly has an impact on combinational logic since the SEU has to happen during the relatively short latch-up phase. However, in high frequency designs a SEU might propagate more easily through the combinational logic, thus, increasing the chance of latching the error (Baumann 2005). Correct investigation of soft errors on combinational logic requires either a gate level model of the system or a RTL model with a modified net list. For this thesis, the following assumptions are made regarding the soft error model:

- i) SEUs in combinational logic are disregarded.

- ii) SEUs are modeled as bit flips in data storage elements.

- iii) Bit flips occur right after a correct latch-up.

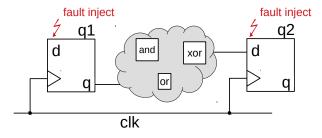

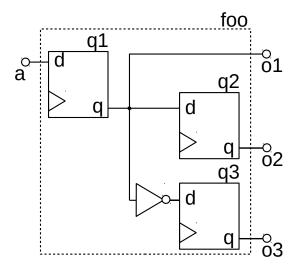

Figure 2.1.: Simple register stage

Fig. 2.1 shows a simple register stage. Register q2 is driven by combinational logic fed by q1. Both q1 and q2, are possible victims of a soft error modeled by a fault inject.

#### 2.1.2. Injection Model

Considering the RTL representation of a synthesized digital systems, thousands of nets and registers can be identified. Exploring a spatial and time explicit SEU, requires defining preliminary modeling rules for fault injections. In this thesis, an faulty model FI for one SEU is described by

$$FI = \{M, b, c, T\}$$

Variable b refers to a single-bit of a clocked data storage element in the bit-representation of a model M, e.g. a micro-architectural register, and c to a specific clock cycle in the observation period. The injection type T describes whether the target's value is flipped unbiased or biased towards a specific state, i.e. a logically high register injected with a high-biased injection, would not be affected, whereas a logically low one would flip to logic high. However, in this thesis, only unbiased flips are considered.

Figure 2.2.: Single-bit target fault

Fig. 2.2 shows a timing diagram for a single-bit fault injection. Equation v(M, b, t) describes the clean value of bit b of model M over a simulation time t. v(FI, t) refers to the value over simulation time with the faulty model. To guarantee an injection, the assumption is made, that at the moment of injection the target is stable, i.e. retaining the faulty state  $(T(v_c))$  at least until the next clock cycle.

#### 2.1.3. Fault Effect Classification

SEU do not necessarily produce errors in the affected system. Furthermore, if an error is generated, its observed impact during and after simulation time can vary. Based on the idea of basic fault effect classes described in (Cho et al. 2013), this work handles fault effects through the following after-simulation-time classification:

- Application Errors: The application finishes, however, output or program flow is unexpected and varies from an error-free reference run. Additionally, in-system hardware is not capable of detecting these errors.

- (AO) **Output**: The output memory differs from an expected, golden value. This includes peripherals' in a System on Chip (SoC) context.

- (AP) **Program Flow**: The program execution trace varies from an expected one. Considering these errors often is important for applications demanding a specific execution time, e.g. control applications, where the controller is designed with a worst case execution time in mind.

- System Errors: The system detects its erroneous behavior. Exceptions can be issued and could then be handled by dedicated processes in software.

- (SM) **Memory Access**: An invalid access to a protected memory region was detected by a dedicated hardware component, e.g. a Memory Protection Unit (MPU).

- (SI) Illegal Instruction: An invalid instruction in the pipeline has been caught.

- Application Finished Correctly: The program finishes as expected and no errors were detected.

- (MSK) **Soft Error Masked**: After execution no difference to the reference run can be identified. This means, output memory, execution cycles, and micro-architectural state of the model match the reference.

- (NSK) **Soft Error Not Masked**: After execution no difference to the reference run can be identified. However, the micro-architectural states differ from an expected one.

- Hang-up Error: The application does not finish and no system error is detected.

- (HL) Logic Stall: The pipeline is active, i.e. instructions still progress through the pipeline, however, no application progress can be made. Reason can be that the program is stuck in an endless loop because the loop's exit check continuously fails. Both software, e.g. an OS, and hardware, e.g. a watchdog, might be able to solve this issue.

- (HP) **Pipeline stall:** The pipeline is inactive, i.e. continuously stalled. This state can only be left by reset.

#### 2.2. Verilator RTL

#### 2.2.1. Verilator

The open-source tool Verilator synthesizes hardware descriptions, specified in Verilog and SystemVerilog hardware description language (HDL), to executable C++ or SystemC modules. The more general implementation as a source library enables a convenient integration of Verilator RTL (VRTL) in various applications.

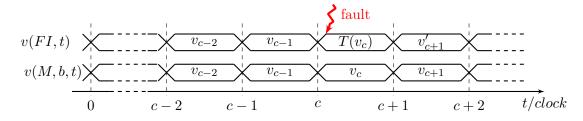

Figure 2.3.: Verilator flow (Geier 2019)

In contrast to simulators using HDL built-in simulation techniques, Verilator performs an actual synthesis process. The output is a cycle-accurate and efficient, i.e. fast, model (Veripool n.d.). However, due to the optimization during synthesis some issues arise:

- i) Flattened hierarchy: The output's hierarchy does not correspond the underlying hierarchical design in HDL. Verilator supports different ways to access internal variables, however, all require adding keywords in the input sources, i.e. non-functional modification to HDL sources.

- ii) Data types: In VRTL, there are no data types representing the bit length of a variable.

- iii) Omitting non-storing elements: Since Verilator performs a full synthesis, not all elements of combinational logic are required. Verilog nets, e.g. wires, that connect module instances in a hierarchical design are often left out. This saves execution time otherwise spent on updating signals in simulator delta-cycles.

- iv) **Legibility:** HDL sources are synthesized to thousands of lines of mostly incomprehensible C++ code. This makes debugging the VRTL near impossible resulting in a "black-box" situation.

Fig. 2.3 shows a basic Verilator use case utilizing VRTL and a C++ testbench to build an executable binary for a given SystemVerilog project. Outputs are updated by stimulating input

variables of the synthesized top module and calling its evaluation method. Those outputs can be handled in the hosting framework which, in this case, is a testbench instantiating the VRTL model.

#### 2.2.2. Fault Injection

The issues resulting from Verilator's optimizations described in 2.2.1 propagate to a possible fault injection application, nonetheless. Omitted nets make soft error simulation on combinational logic impossible. Code size and legibility aggravate any manual insertion of injection points for hardware projects at complexity levels of modern processor cores. Furthermore, flattened hierarchy and the indifference of data types, both in VRTL as in Verilog/SystemVerilog, hinders locating possible injection targets in the first place.

As fault injections into wires or variables that are actually constants in hardware, e.g. look-up tables or hard-wired signals, would be unnecessary, variables in the VRTL model require classification. SystemVerilog, unfortunately, does not specify whether a declared signal is going to be continuously, i.e. a wire, or sequentially, i.e. a register, assigned at declaration time. Although this SystemVerilog supports such explicit declarations, implicit signal declarations are resolved during synthesis (IEEE Computer Society 2001, IEEE Computer Society 2009). This results in many hardware descriptions using only the signal type keyword "logic" for all signal declarations.

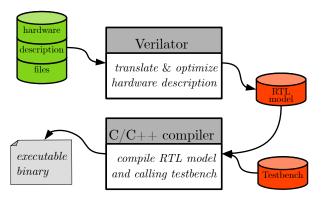

Figure 2.4.: Signal types and classification (Geier 2019)

A possible solution to this is proposed in (Weinzierl 2017); An algorithm categorizes VRTL variables based on their behavior inside the VRTL model, which is illustrated in Fig. 2.4. On the left, the difference between a signal declaration in HDL and its corresponding variable declaration in the C++ VRTL is shown, as well as the underlying behavior. On the right, the signal classification algorithm is shown. Each input signal x is classified as either a wire, a constant, or a registers.

#### 2.2.3. RegPicker

In (Geier 2019), the stand-alone tool RegPicker was developed which implements the classification algorithm described in sec. 2.2.2. Furthermore, the HDL's underlying hierarchy lost in the Verilator synthesis is reconstructed. Together with its classification, the signal's location is put out in an Extensible Markup Language file (XML). The XML constitutes a sufficient basis for a fault injection framework.

#### 2.3. Simulation Target: RI5CY

This work focuses on applying the fault model described in sec. 2.1 to RTL models of cores implementing the open-hardware RISC-V ISA. Recent developments, including adaptions in commercial products, established RISC-V as an interesting topic for research.

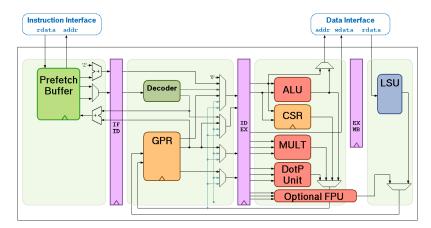

Figure 2.5.: RI5CY block diagram (Traber et al. 2019)

As a proof-of-concept simulation target, a 32-bit core executing cross-compiled RISC-V benchmark software is chosen. RI5CY is an open-source 32-bit RISC-V derivative developed by researchers at ETH Zürich and the University of Bologna, in context of the Parallel Ultra Low Power Platform (PULP) project (ETH Zürich n.d.a, ETH Zürich n.d.b).

#### 2.3.1. Pipeline

RI5CY has full support of RISC-V Base Integer Instruction Set, Standard Extension for Compressed Instructions, Integer Multiplication and Division Instruction Set Extension (RV32I, RV32C, RV32M), and PULP-specific ISA extensions, which are not surveyed in this work. Fig. 2.5 shows a block diagram of the 32-bit core and depicts its 4-stage pipeline:

- **IF** Instruction Fetch. Configured to start fetching from memory address 0x80 through a 128-Bit or 4-word cache line prefetcher.

- **ID** Instruction Decode: Interprets the fetched machine code including compressed instructions. Additionally, interrupts on illegal instructions.

- EX Execute: Takes decoded instructions and schedules execution on the respective unit.

- **WB** Write-Back: Manages storage to data memory through the Load-Store Unit (LSU) and an optional Physical Memory Protection (PMP).

#### 2.3.2. Configuration

The RI5CY project provides either a latch-based or flip-flop-based GPR file. In this work, the flip-flop-based implementation of the register file is used and instantiated inside the core's hierarchy. Furthermore, no floating point unit is added which means the GPR's memory is reduced to the RISC-V integer register specification shown in tab. 2.1. All simulations are performed on machine privilege level, however, the privilege functionality might be affected by soft errors. The levels and their respective encoding are shown in tab. 2.2.

| register | name                | description                       |

|----------|---------------------|-----------------------------------|

| x0       | zero                | Hard-wired zero                   |

| x1       | ra                  | Return address                    |

| x2       | $\operatorname{sp}$ | Stack pointer                     |

| x3       | gp                  | Global pointer                    |

| x4       | $\operatorname{tp}$ | Thread pointer                    |

| x5       | t0                  | Temporary/alternate link register |

| x6-7     | t1-2                | Temporaries                       |

| x8       | s0/fp               | Saved register/frame pointer      |

| x9       | s1                  | Saved register                    |

| x10-11   | a0-1                | Function arguments/return values  |

| x12-17   | a2-7                | Function arguments                |

| x18-27   | s2-11               | Saved registers                   |

| x28-31   | t3-6                | Temporaries                       |

Table 2.1.: RISC-V integer registers

from: (Krste Asanovic, Rimas Avizienis, Jacob Bachmeyer, Christopher F. Batten et al. 2017)

#### 2.3.3. Injection Targets

Feeding RI5CY's HDL description into RegPicker yields 327 VRTL variables as possible injection targets comprising 5753 single-bit targets.

| level | encoding | name               |

|-------|----------|--------------------|

| 0     | 00       | user / application |

| 1     | 01       | supervised         |

| 2     | 10       | reserved           |

| 3     | 11       | machine            |

Table 2.2.: RISC-V privilege levels from: (Waterman et al. 2014)

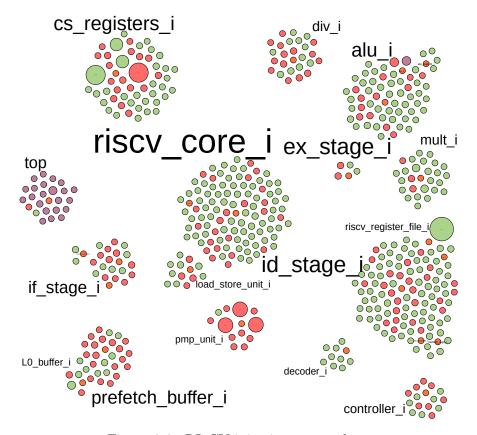

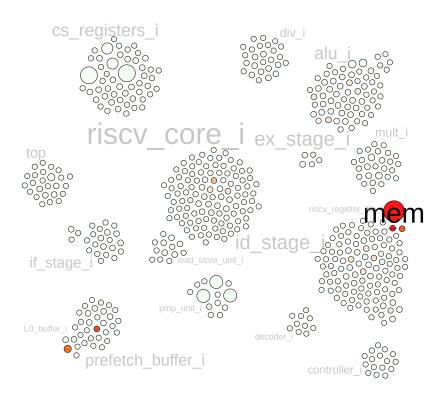

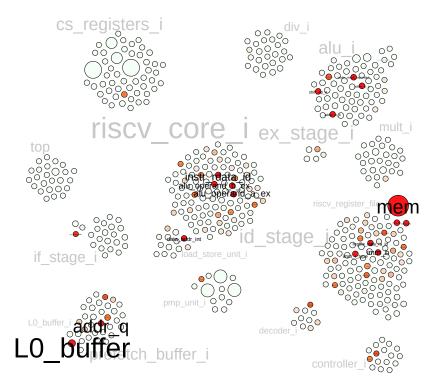

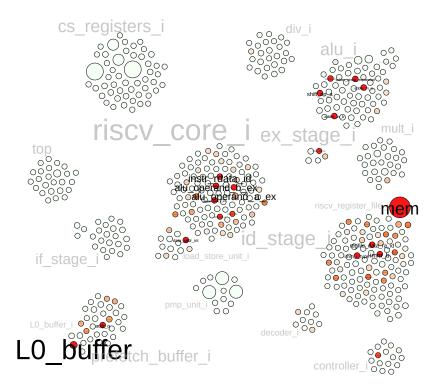

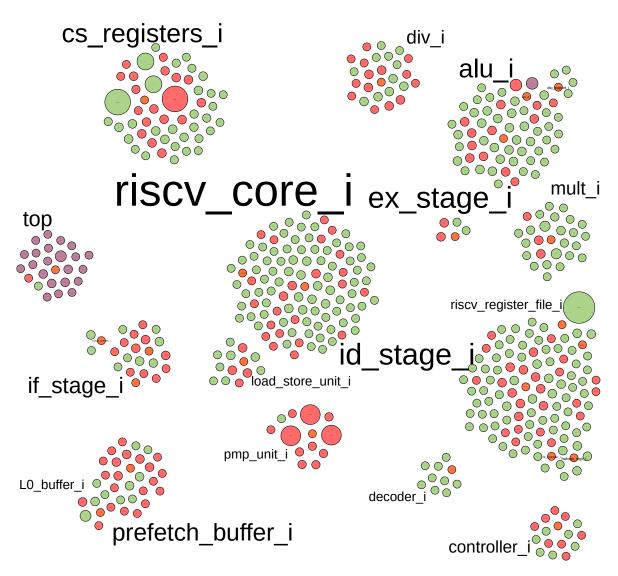

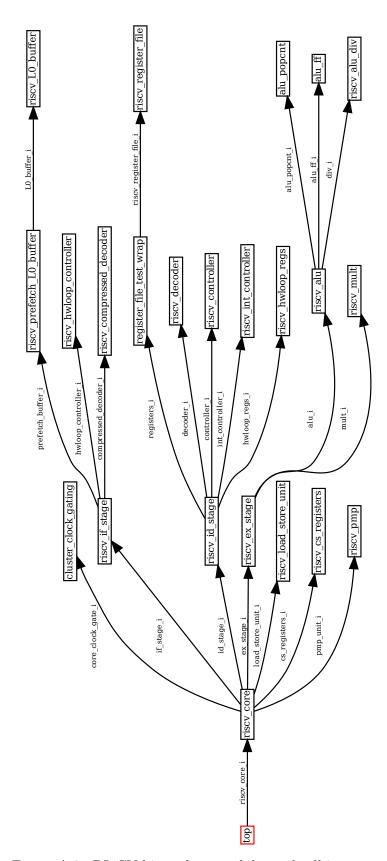

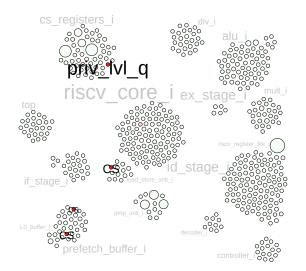

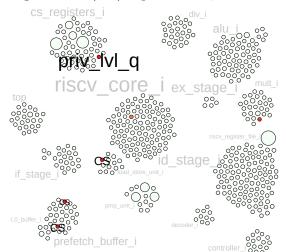

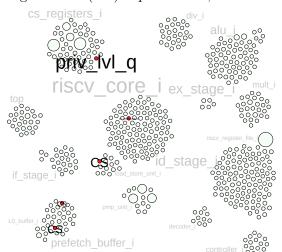

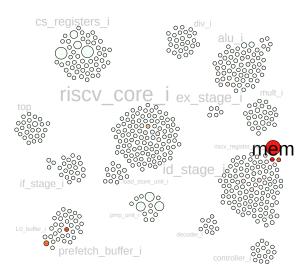

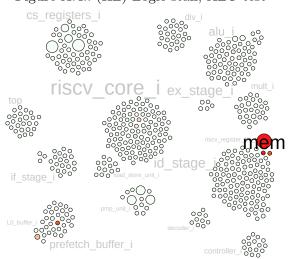

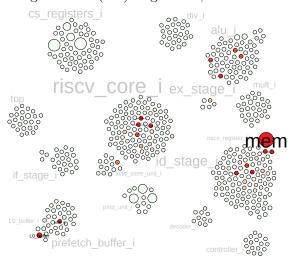

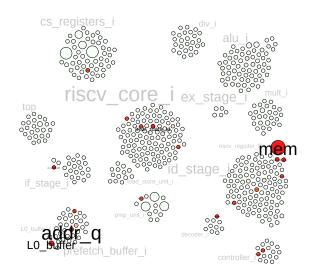

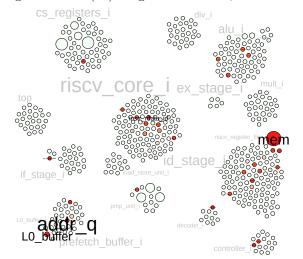

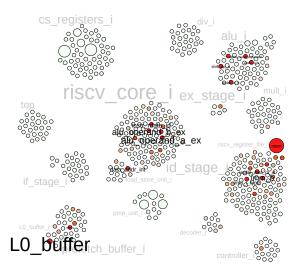

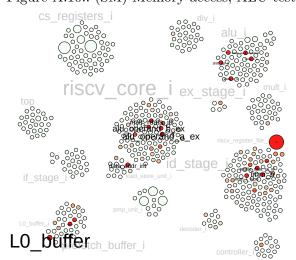

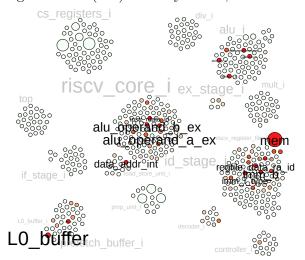

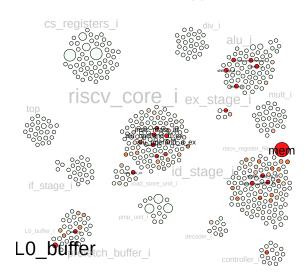

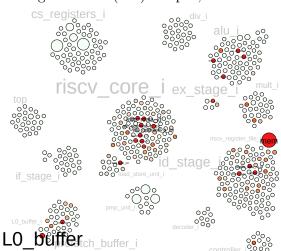

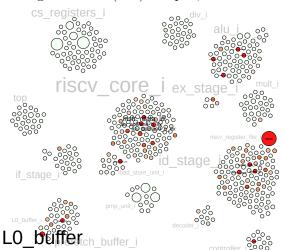

Fig. 2.6 shows the RI5CY fault injection target cluster. The cluster is generated from RegPicker analyzing the RI5CY HDL sources and transforming the output to a directed graph description. Nodes of the graph are variables of the VRTL model. Edges between nodes, although hidden, describe a weighted hierarchical relation between variables and their parent cell, where a cell is an instance of an HDL module. Each edge's weight corresponds to the bit-length of a variable. Registers, thus injection targets, are colored green, wires and constants, thus for fault injection of no concern, colored red and purple respectively. The coordinate of each node in the force-directed graph is calculated with a converging force-layout algorithm Force Atlas in the visualization tool Gephi (Gephi n.d.). For further clarification on RI5CY's hierarchy, i.e. cell relations, fig. A.2 in the appendix shows a graph of Verilator's own XML output.

Figure 2.6.: RI5CY injection target cluster

#### 2.4. LLVM

LLVM, formerly Low Level Virtual Machine, comprises a compartment of modular compiler and toolchain technologies (LLVM Foundation n.d.). The LLVM core libraries can be utilized to build custom tools for various applications. However, this work mostly utilizes tools revolving around LLVM's C/C++/Objective-C compiler (Clang) Abstract Syntax Tree (AST).

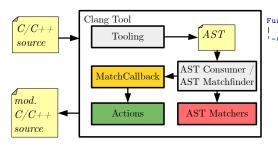

Figure 2.7.: Clang tooling

```

// clangASTexample.cpp

int main(void){

int x = 0;

int X[100] = { };

for (; x<100; ++x)

{

X[x] = x;

}

}</pre>

```

Listing 2.1: Example AST source

```

FunctionDecl 0x55d1792f94c0 <clangASTexample.cpp:1:1,

line:7:1> line:1:5 main 'intu()'

*CompoundStmt 0x55d1792f9a50 <col:15, line:7:1>

DeclStmt 0x55d1792f9670 eclStmt 0x55d1792f9670 <lie>2:2:2, col:12:

'-VarDecl 0x55d1792f95e8 <col:2, col:11> col:6 used x

cinit

| 'int' cinit

'-IntegerLiteral 0x55d1792f9650 <col:11> 'int' 0

DeclStmt 0x55d1792f9828 <line:3:2, col:18>

'-VarDecl 0x55d1792f9730 <col:2, col:17> col:6 used X

| 'intu[100]' cinit

-InitListExpr 0x55d1792f97d8 <col:15. col:17> 'intu[100]'

-array_filler: ImplicitValueInitExpr 0x55d1792f9818

<invalid sloc>> 'int'

ForStmt 0x55d1792f9a18 <line:4:2, line:6:2>

-BinaryOperator 0x55d1792f9898 <line:4:9, col:11> 'bool' '<'

|-ImplicitCastExpr 0x55d1792f9880 <col:9> 'int' <LValueToRValue>

-DeclRefExpr 0x55d1792f9840 <col:9> 'int

lvalue Var 0x55d1792f95e8 'x' 'int'

-IntegerLiteral 0x55d1792f9860 <col:11> 'int' 100

UnaryOperator 0x55d1792f98d8 <col:16, col:18> 'int'

lvalue prefix '++

'-DeclRefExpr 0x55d1792f98b8 <col:18> 'int

lvalue Var 0x55d1792f95e8 'x' 'int'

-CompoundStmt 0x55d1792f9a00 <col:20, line:6:2>

'-BinaryOperator 0x55d1792f99e0 <line:5:3, col:10> 'int' | lvalue '='

ArraySubscriptExpr 0x55d1792f9988 <col:3, col:6> 'int'

| lvalue

|-ImplicitCastExpr 0x55d1792f9958 <col:3> 'intu*'

| <ArrayToPointerDecay>

'-DeclRefExpr 0x55d1792f98f0 <col:3> 'intu[100]'

lvalue Var 0x55d1792f9730 'X' 'intu [100]'

ImplicitCastExpr 0x55d1792f9970 <col:5> 'int'

<I.ValueToRValue>

-DeclRefExpr 0x55d1792f9910 <col:5> 'int'

lvalue Var 0x55d1792f95e8 'x'

implicitCastExpr 0x55d1792f99c8 <col:10> 'int'

<LValueToRValue>

-DeclRefExpr 0x55d1792f99a8 <col:10> 'int'

lvalue Var 0x55d1792f95e8 'x' 'int'

```

Listing 2.2: Example AST dump

The AST is an intermediate representation of C/C++ source code. Listing 2.2 shows the AST for the brief example code (listing 2.1). An AST Matcher, e.g. FunctionDecl for declarations of functions or ArraySubscriptExpr for accesses to array elements, can be decorated further with more specific names to refine locating granularity. Together with Clang Tooling, the AST Matcher library enables callbacks to specific elements in the AST; Whenever the ClangTool traverses the AST and a previously defined condition is matched, a callback function is initiated with a reference to the matching AST element. This allows the user application (LLVM Frontend) to handle the code section in a desired way, e.g. analysis of transformation. In fig. 2.7 a simple Clang Tool is shown that modifies a given source file. The tooling library generates the AST which is then traversed in the AST Consumer. Actions can perform various transformations on the source file, while the AST Matchers and their respective callbacks locate the corresponding code sections.

#### 3. Verilator RTL Modification

#### 3.1. Verilator Evaluation

As described in Sec. 2.2.2, the VRTL model requires modifications to enable some form of fault injection methodolgy. Difficulties arising from flattened hierarchy and missing data type specifications can be handled by RegPicker (Sec. 2.2.3).

Legibility is more an indirect issue, since manually accessing variables and inserting injections inside the VRTL would not be feasible after all and the actual injections will be scheduled by an automated framework. The remaining problem is one of Verilator's greatest feats; Faster models through design optimization.

#### 3.1.1. Synthesis

At first glance, omitted nets seem to be of no concern, since no injections are performed on combinational logic. Thus, the smallest notion of time for this VP would be one clock cycle or rather half of a clock cycle, which would comply with the fault model proposed in Sec. 2.1. However, simply changing values of internal signals of the VRTL between calls to the evaluation method has occasionally shown no effect, i.e. auto-masking the fault. Inspecting the VRTL source has shown that read-after-write occurrences for registers one stage before a module output, i.e. sequential elements driving remaining wires. Reasons can be found with Verilator's optimization of these output assignments: Since a net normally takes on the value of its most dominant driver nearly immediately, Verilator simply inserts this continuous assignment right after the driver is updated in the sequential evaluation method. This saves costly evaluation time of combinational logic, however, results in the masking issue.

Figure 3.1.: VRTL example stimuli model

#### 3. Verilator RTL Modification

```

1 module foo(

2

input logic clk,

3

input logic a,

output logic o1, o2, o3

):

5

6

// declarations

logic q1, q2, q3;

// cont. body

9

10 assign o1 = q1;

11 \text{ assign } 02 = q2;

12

assign o3 = q3;

13

always_ff @(posedge clk)

14

// seq. body

15

16

else

q1 <= a;

17

q2 <= q1;

18

19

q3 <= !q1;

20

21

endmodule

```

Figure 3.2.: Fault injection example

Listing 3.1: Example SystemVerilog

Fig. 3.2 describes a simple SystemVerilog module foo, the left-hand side diagram illustrates the module as a conceptual implementation. Outputs o1, o2, and o3 are driven by q1, q2, and q3 respectively by the assign statement, thus, making them equivalent to nets or wires. In general SystemVerilog provides more than one always keyword type supporting latch, combinational or sequential procedures. The SystemVerilog keyword always\_ff enables procedural blocks modeling sequential logic behavior sensitive to the expression following the keyword. In this example, q1, q2, and q3, are sequentially updated by a non-blocking assignment (<=) in the clock (clk) -sensitive block. Non-blocking means that at sufficient sensitivity, the current state of each right-hand side non-blocking assignment is elaborated, however, the actual assignment is scheduled separately and updated at the end of the evaluation period. This means that, even though in line 17 of the listing 3.1, q1 is apparently updated before q2 in line 18, q2 will be updated with the value of q1 when the always\_ff is entered. SystemVerilog simulators, thus Verilator, too, have to conform to these and more specifications in (IEEE Computer Society 2009).

```

1 VL_INLINE_OPT void Vfoo::_sequent__TOP__1(Vfoo__Syms* __restrict vlSymsp) {

// Get internal variables from symbol table

2

Vfoo* __restrict v1TOPp VL_ATTR_UNUSED = v1Symsp->TOPp;

3

4

5

v1TOPp \rightarrow foo_DOT_q2 = v1TOPp \rightarrow foo_DOT_q1;

6

vlTOPp->foo__DOT__q3 = (1U & (~ (IData)(vlTOPp->foo__DOT__q1)));

v1TOPp->o2 = v1TOPp->foo__DOT__q2;

8

v1TOPp->o3 = v1TOPp->foo__DOT__q3;

9

10

vlTOPp \rightarrow foo_DOT_q1 = vlTOPp \rightarrow a);

vlTOPp \rightarrow o1 = vlTOPp \rightarrow foo_DOT_q1;

11

12 }

```

Listing 3.2: Example Verilator sequential body

Listing 3.2 shows foo's VRTL (Vfoo) sequential evaluation method. The method is called each time a positive clock edge is recognized by Vfoos's main evaluation function which is called by the simulation host. Furthermore, during one evaluation each register-like variable must not be assigned more than once, since only nets can be driven by multiple sources. Fig. 3.1 illustrates the example's stimulus, input a and clock signal together with a call to the main evaluation function, and outputs o1, o2, o3.

#### 3.1.2. Fault Injection

Considering a fault injection between clock cycles, e.g. by accessing Vfoo's variables through the VRTL symbol table vlSymsp the following observations can be made assuming no resets are done and clock-edges are triggered, thus, applying the fault model of sec. 2.1:

•  $FI = \{Vfoo, q1, c, flip\}$ :

c+1: Fault propagates to q2 and q3 through q1, thus outputs o2 and o3 are updated with a faulty state. Injection target q1 is updated by input a and o1 is assigned the new q1.

c+2: Fault has left the model.

**Problem:** o1 never sees the injected flip.

•  $FI = \{Vfoo, q2, c, flip\}$ :

c+1: q1 updates injection target q2, o2 is assigned the new value of q2. Fault has left the model.

**Problem:**  $\circ 2$  never sees the injected flip.

•  $FI = \{Vfoo, q3, c, flip\}$ :

c+1: q1 updates injection target q3, o3 is assigned the new value of q3. Fault has left the model.

**Problem:** o3 never sees the injected flip.

Consequence of this auto-masking of a section of possible injection targets is that injections between clock cycles, i.e. between evaluation calls, violates the fault model for VRTL.

#### 3.2. Modification

Injecting the fault right after the assignment statement, would also enable updating module outputs with faulty states. Listing 3.3 shows a pseudo-modified Vfoo that will always result in faulty outputs. However, manually inserting these injection points in VRTL is not feasible.

```

1 void pseudo_inject(CData& target){

#define c INJECTION_CLOCK

3

#define b INJECTION_BIT

// Check for injection clock cycle

5

if(clock_counter == c){

// flip target bit with bit-wise XOR

target = target ^ (0x1 << b);

8

10 }

11

12 VL_INLINE_OPT void Vfoo::_sequent__TOP__1(Vfoo__Syms* __restrict vlSymsp) {

// Get internal variables from symbol table

13

14

Vfoo* __restrict vlTOPp VL_ATTR_UNUSED = vlSymsp->TOPp;

15

// Body

16

17

vlTOPp->foo__DOT__q2 = vlTOPp->foo__DOT__q1;

pseudo_inject(vlTOPp->foo__DOT__q2);

18

vlTOPp->foo__DOT__q3 = (1U & (~ (IData)(vlTOPp->foo__DOT__q1)));

19

20

pseudo_inject(vlTOPp->foo__DOT__q3);

v1TOPp->o2 = v1TOPp->foo__DOT__q2;

21

vlTOPp->o3 = vlTOPp->foo__DOT__q3;

22

vlTOPp->foo__DOT__q1 = vlTOPp->a);

23

pseudo_inject(vlTOPp->foo__DOT__q1);

24

vlTOPp \rightarrow o1 = vlTOPp \rightarrow foo_DOT_q1;

26 }

```

Listing 3.3: Pseudo-modified example Verilator sequential body

#### 3.2.1. Target Variables as Extended Data Structures

#### Concept

One solution would be to extend each targets variable data type to return the correct or faulty value on demand. Originally, Verilator synthesizes bit vectors to the smallest possible trivial C/C++ data type, i.e. size-modified unsigned. Substitution of the targets data-type with a class-like data-type at declaration can enable more specific handling of the element during evaluation runtime. Overloading all possible arithmetic operators and conversions generates automatic call-back functionality for each extended variable. Additionally, this would only require changing the class definitions of the VRTL modules by modifying its member's declaration types to the overloading class type.

```

1 template <typename BaseType_t, unsigned int FIELDS>

2 class ExtendedData {

3 public:

bool inject;

BaseType_t mVar[FIELDS];

5

6 protected:

BaseType_t& read(int index = 0) {

8

if (inject){

9

... // return injected value

10

11

return (mVar[index]);

12

}

void write(BaseType_t newVal, int index = 0) {

13

mVar[index] = newVal;

14

15

16 public:

inline BaseType_t& operator[](unsigned int index) {

17

if (index > FIELDS) exit(0);

18

19

return read(index);

20

// ASSIGNMENT Overloading

21

inline ExtendedData& operator =(const BaseType_t &driver){...}

22

inline ExtendedData& operator =(ExtendedData &driver){...}

23

// ARITHMETIC Overloading

24

25

inline BaseType_t& operator +(const BaseType_t &driver){...}

inline BaseType_t& operator -(const BaseType_t &driver){...}

26

27

28

// CONVERSION Overloading

inline operator BaseType_t(){

29

return(read());

30

31

ExtendedData(void): inject(false), mVar(){}

32

33 };

```

Listing 3.4: Pseudo overloading class - extended data structure

Listing 3.4 shows a heavily shortened implementation of an extended data structure for VRTL variables. Since Verilator generates arrays of 32-bit elements for SystemVerilog variables longer than 64 bits, the actual data is stored in the mVar member, an array of the base or rather original data type in VRTL specified through a template argument during compilation. Besides arithmetic operators, implicit conversion (line 29) are overloaded to enable interaction with more trivial data types. The protected read method returns a clean or possibly faulty version of the data, while a write method handles correct assignment operations to the extended VRTL variable.

#### **Evaluation**

(Dittrich 2017) already utilized overloading C++ classes as extended data-types for variables in VRTL to support tracing in mixed-level simulations. While, this overloading approach allows a lot of flexibility and additional functionality, e.g. run-time tracing, simulation performance suffers.

Tab. 3.1 shows the results of a performance evaluation of the overloading approach. A VRTL model of a 32-bit RISC (OpenRisc1000) is set against a modified VRTL according to the

#### 3. Verilator RTL Modification

| host execution time | GCC opt            | GCC opt     |

|---------------------|--------------------|-------------|

| at 1M target cycles | -O3                | -O0         |

| VRTL                | $0.514~\mathrm{s}$ | $1.511 \ s$ |

| VRTL (modified)     | $8.106~\mathrm{s}$ | 17.861  s   |

| slowdown            | 15.77              | 11.82       |

Table 3.1.: Performance overloaded VRTL

previously introduced concept. The RTL model is run for one million cycles on a modern x86 host with Linux OS. The execution time is measured in user space yielding the actual time spent inside the process hosting the VRTL models. Although not important for execution times of eventually heavily optimized simulation frameworks, a look into how a compiler handles any further modifications to the VRTL sources is interesting; Without optimizations for the Gnu Compiler Collection (GCC) C++ compiler enabled, basic VRTL is about 12 times faster than the modified one. However, for a strong level of optimization (O3), non-modified VRTL is more than 15 times faster. The assumption can be made that operator overloading is not as easily handled by the compiler with respect to code optimization as the mainly arithmetic-intensive core of VRTL is.

The basic idea of using Verilator as a tool for RTL simulation is its speed compared to other available simulators. Slowing down the simulation for fault injection would eliminate the benefits of VRTL in the first place, thus, the usage.

#### 3.2.2. Source Transformation

#### Concept

While the previous approach in sec. 3.2.1 mostly relied on introducing additional functionality to VRTL variables, thus, modifying their declarations in VRTL classes, another option is to transform the VRTL's sources. The fundamental idea is to insert injection points in the model source code according to the concept introduced by listing 3.3.

| host execution time at 1M target cycles | GCC opt<br>-O3 | GCC opt  |

|-----------------------------------------|----------------|----------|

| VRTL                                    | 2.341 s        | 8.165 s  |

| VRTL (modified)                         | 2.622 s        | 10.057 s |

| slowdown                                | 1.12           | 1.23     |

Table 3.2.: Performance source-transformed VRTL

#### **Evaluation**

Tab. 3.2 shows the results of a performance evaluation of the source transformation concept. A VRTL model of a 32-bit RISC-V core (RI5CY) is set against source-transformed VRTL. Again, the RTL model is run for one million clock cycles on a x86 host and the simulation's execution time is measured as process user time. Without GCC optimization, original VRTL is 1.23 times faster than the modified VRTL. With optimization, the original is just 1.12 times faster. Although no injections are performed, checks for a injection at each possible injection point have to be performed which generates simulation overhead. Nonetheless, source-transformation seems to be more efficient, since most of the overhead can be resolved during compile time, where as overloading data types mostly influences the runtime.

#### **Performance**

Measuring execution time of the respective simulation process is a straight-forward way to compare the two solutions on a common host. Additionally, measuring instructions per second is commonly used and a somewhat meaningful benchmark. However, for a more independent, therefore, sophisticated, statement regarding a simulation's performance it is not sufficient. Reasons for this lay with the host. OS, implementation of the native libraries, and most of all the hardware itself can vary a lot between different simulation setups. These host-dependent influences can be reduced by comparing the number of instructions needed by the host to perform a certain number of target instructions in the simulation setup. This instruction transmission figure is still affected by the host's architecture, however, not so much by the host's other hardware, e.g. memory, cache, and CPU.

The instruction transmission measurement is setup up as followed: The simulation framework instantiates the VP. The VP executes a cross-compiled binary for a certain number of target clock cycles. In order to stimulate the VP, a clock spin is performed which is two consecutive VRTL evaluation cycles where one is with the input clock logically high and one logically low. For measuring the required host instructions, the whole setup is ran inside a GNU Debugger (GDB) process. The GDB is initiated with two breakpoints; The first where the initialization phase is done and clock spins start and the second where the program is finished. When the debugger reaches the first breakpoint, all further execution is performed step-wise, i.e. host instruction by host instruction, while the steps are counted. As an example target program a Arithmetic Logic Unit (ALU) test program is used which covers a good amount of general purpose computing in the target.

The transmission factor  $t_I$  can then be calculated with

$$i = \frac{I_{host}}{I_{target}}$$

#### 3. Verilator RTL Modification

Variable  $I_{host}$  refers to the number of host instructions and  $I_{target}$  to the number of instructions executed on the simulation target.

| ALU test on x86 $I_{target} = 4,662$ | $I_{host}$                     | $i_{ALU}$          |

|--------------------------------------|--------------------------------|--------------------|

| VRTL<br>modified VRTL                | 115, 656, 447<br>131, 660, 131 | 24, 808<br>28, 241 |

| slowdown                             |                                | 1.13               |

Table 3.3.: Instruction transmission VRTL

Tab. 3.3 lists the instruction transmission results for 1000 target clock cycles both on VRTL and source-modified VRTL with compiler optimization enabled. For the used target software an instruction transmission of 28, 241 was achieved. This means that on average, for every RISC-V instruction on the VP, about 28 thousand host instructions have to be executed. Additionally, the transmission factors should mirror the execution time slowdown effects of modified VRTL presented in tab. 3.2; the modified VRTL needs about 1.14 times more instructions than its unmodified counterpart for the same task. Additionally, since for both measurements the ALU test was used, an instructions per second (IPS) benchmark can be formulated. For example, while the host, an Intel I5 with 3.4 GHz, might yield 10 Giga-IPS, the simulation target, following  $i_{ALU}$  for modified VRTL, achieves only about 354 Kilo-IPS.

## 3.3. Implementation

The following sections of this chapter describes how the VRTL modifier was implemented as a stand-alone tool. For generating a RTL-custom injection framework, two major problems have to be solved by the modifier tool:

- 1. **API Builder:** Providing an API for managing injections in a project integrating the modified VRTL.

- 2. **Injection Rewriter:** Locating sequential assignments of targets in the AST and inserting injections

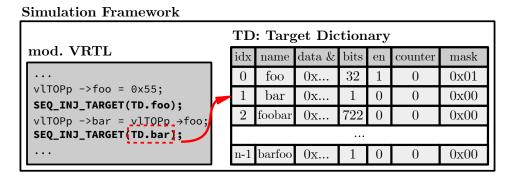

Both problems are basically decoupled. The only interaction happens, when an injection call accesses variables of the fault model set by the API. The API provides the user (framework) and injection call a common target dictionary holding information about each target's name, bit length, and reference to the original data element in the VRTL model. Furthermore, each target dictionary entry holds data for the injection purpose including a general injection enable, injection counter to avoid multiple injections per clock cycle, and a mask field specifying which bit of a multi-bit target has to be affected and which not.

Figure 3.3.: Injection call with target dictionary

Fig. 3.3 illustrates the interaction between modified VRTL and the target dictionary. The VRTL calls the injection macro SEQ\_INJ\_TARGET with the respective target dictionary entry. Both, location and arbitration of the injection call have to be managed by the Injection Rewriter (sec. 3.3.2) during the source transformation.

#### 3. Verilator RTL Modification

```

1 #define FI_UNLIKELY(x) __builtin_expect(!!(x), 0)

2

3 #define SEQ_INJ_TARGET(TDentry) {

4    if(FI_UNLIKELY((TDentry).enable)) {

5       if(((TDentry).counter <= 0) and (TDentry).mask) {

6       *((TDentry).data) = *((TDentry).data) ^ (TDentry).mask; \

7       (TDentry).counter++; \

8    } \

9   } \

10 }</pre>

```

Listing 3.5: Injection macro

Listing 3.5 contains the injection macro. Since most of the time and for the majority of all targets no injections are performed, an additional macro helps the compiler predict control flow for better simulation performance.

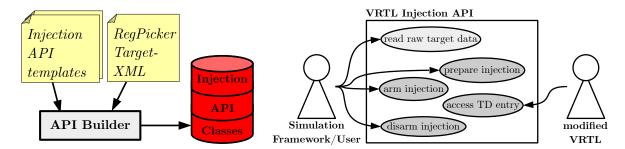

#### 3.3.1. Injection API Builder

The API Builder handles generating a corresponding injection API for a given VRTL model. The information provided by RegPicker (sec. 2.2.3) suffices as input, i.e. all targets/registers, their location and bit length, etc.

Figure 3.4.: API Builder process

Figure 3.5.: Injection API use case diagram

Fig. 3.5 shows the use cases for the injection API. On the one hand, modified VRTL accesses the API's underlying target dictionary. On the other hand, a simulation framework or API/VRTL user, instantiating both API and modified VRTL, configures and schedules the injections, thus accessing the target dictionary. Scheduling means arming or disarming an injection at the exact injection cycle, which has to be managed by the simulation framework.

Target information is taken from RegPicker's output XML and translated into corresponding C++ classes, the target dictionary entries (Fig. 3.4). Template files contain all RTL-invariant features, e.g. the target dictionary class, injection macros and a general injection API wrapper class. The templates get extended by the modifier program with RTL-variant, or rather specific, contents mostly related to the dictionary.

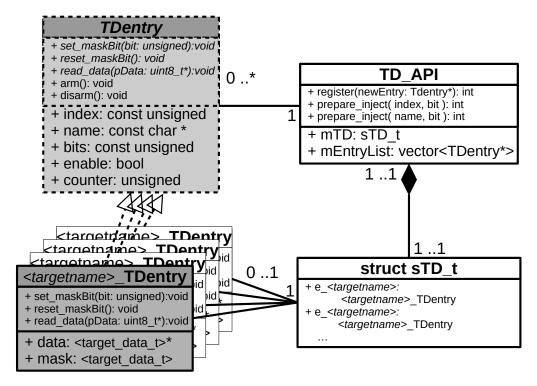

The simplified class diagram in fig. 3.6 describes the relations of the injection API's different classes. A common pure-abstract base class TDentry acts as an interface to each specific entry

Figure 3.6.: Injection API target dictionary class diagram

(<targetname>\_TDentry), e.g. for 100 targets, there will be 100 specific entry classes. Reason for this is that now the more specific entries can still be accessed generally even though their member data, corresponding to their unique VRTL counterparts, varies. This concludes strong-typed references/pointers to the VRTL data element and the equivalently typed mask. Each target dictionary entry implements a specific set\_maskBit method and a read\_data method that reads the entry's data byte-wise. The target dictionary API class TD\_API holds all entries as a vector of abstract TDentry pointers. The various entries get registered in this vector at the initialization phase of the simulator. The actual entry class instances are summed up in a target dictionary struct member of TD\_API, where as the vector enables preparing and resetting injections by target name or dictionary index without the knowledge of the specific entry class.

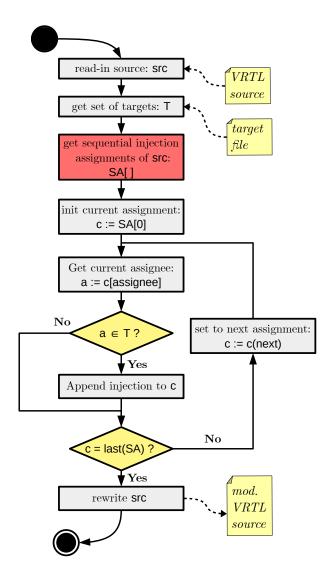

#### 3.3.2. Injection Rewriter

The modifier's scheme for rewriting the VRTL sources to support guaranteed injections is illustrated as an abstract control flow in fig. 3.7. The sequential injection assignments (SIA) have to be extracted from VRTL source file before they can be appended with their respective injection call.

The underlying nature of inserting or rather transforming size-wise unmanageable source files justifies the development of an LLVM-based tool for this VRTL modification.

### 3. Verilator RTL Modification

Figure 3.7.: VRTL source transformation algorithm

## **Extracting Sequential Injection Assignments**

Utilizing the AST Matchfinder to efficiently extract sequential assignments that are of interest for injection requires analyzing the properties of such assignments:

- i) The assignee is a target identified beforehand, e.g. by RegPicker,

- ii) the assignment is located inside a sequential evaluation method,

- iii) the assignment is the last inside one compound, i.e. basic block.

While i) and ii) are straight-forward essential properties, iii) traces back to the source's language boundaries. In C/C++ the largest possible bit-size of a variable is capped, e.g. 64 bit. However, in HDLs vectors of much larger bit-size can be specified. As described in sec. 3.2.1, Verilator handles this by specifying arrays where each field has up to 32-bit and essentially breaks up assignments into multiple field-individual ones executed one after another in the same compound. In addition, when variables have to be accessed bit-wise, i.e. not the full bit-vector is assigned a new value, Verilator synthesizes this similarly to multiple field access, however, for a single field in the same compound. Inserting the injection macro at the first occurrence of a target's assignment in the same compound could then lead to a self-masking process, i.e. an injection-following assignment might overwrite the injection. This issue is engaged by ensuring only the last, or rather, dominant, assignment for a single target in a compound statement has an injection point.

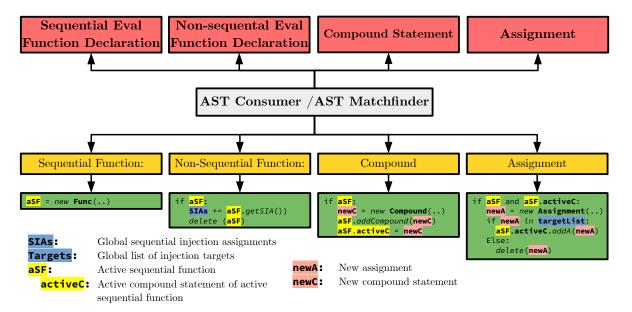

Figure 3.8.: LLVM Tool - Finding sequential injection assignments

Fig. 3.8 shows a simplified interpretation of the LLVM/Clang AST Matcher-Callback setup for SIAs in the VRTL sources. There are four concurrently running AST Matcher-Callback pairs in use:

- Sequential Eval Function Declaration: Matches function declarations that correspond to VRTL sequent function declarations. On callback, a new active sequential function (aSF) ob is generated.

- Compound: Matches all braced statements. If an active sequential function is found, the new compound object is added to the function object. The function objects saves the last found compound statement (active compound).

#### 3. Verilator RTL Modification

- Assignment: Matches all assignments. If the new assignment is found in the previously defined target list, it gets added to the active sequential function object's active compound statement.

- Non-Sequential Function: Matches all miscellaneous function declarations, i.e. non-sequential function. If a sequential function is active when this matcher is raised, the AST traversal left this aSF's declaration's body. Therefore, the aSF was fully analyzed and its SIAs can be extracted. The extraction iterates over all compounds returning only the dominant sequential assignments. Afterwards, the aSF gets discarded which avoids further assignments or compounds being added.

## 4. Simulation

### 4.1. Simulation Framework

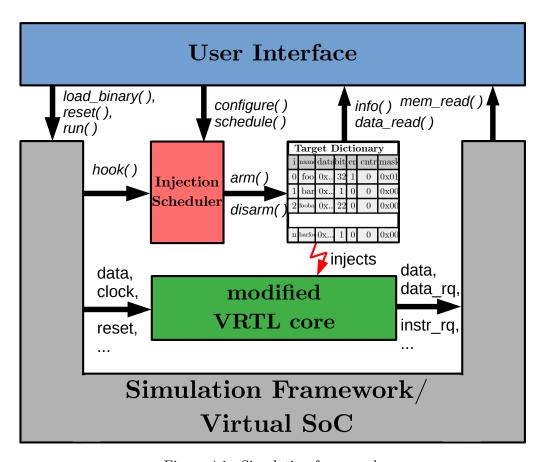

The simulation framework manages the modified VRTL core, an injection scheduler, and a user interface (UI). Additionally, a reduced virtual SoC (VSoC) is modeled. For better simulation performance, the framework is implemented in C++, which allows an efficient executable. Fig. 4.1 shows the framework's components and structure.

Figure 4.1.: Simulation framework

### 4. Simulation

#### 4.1.1. Modified VRTL Core

The modified VRTL core, as described in section 3.2, is integrated in the simulation as generated by the modification tool. Further modifications would break the abstraction layer generated by the automated design flow.

### 4.1.2. Reduced Virtual System on Chip

The simulation framework also mocks a reduced VSoC for the VRTL core. Although Verilator enables a SystemC model for better transaction-level modeling, the C++ output is used as the focus of this work is on the RISC cores and not on any additional peripherals. Therefore, the VSoC has to provide only the memory for the core to interface with. Since RI5CY has a data memory interface and an instruction memory interface, both have to be modeled by the VSoC and their transactions forwarded to the virtual memory.

#### Interface to VRTL

In short, the following functionality has to be provided by the virtual SoC component to the VRTL model:

- i) Clock spin: Stimulate with clock clock cycles.

- ii) Control: Set control outputs, e.g. enable instruction fetch, reset, ...

- iii) **Instruction memory:** Provide instruction fetch with instruction data in the virtual memory.

- iv) Data memory: Support load and store access to the virtual data memory.

#### Interface to Simulation Framework

Additionally, these tasks issued by the simulation framework have to be handled:

- i) **Boot:** Load a cross-compiled binary to the virtual instruction memory and initliaze control signals.

- ii) **Execute:** Run the model for a certain amount of clock cycles.

- iii) Reset: Set the model to a pre-defined state.

iv) **Injection hook:** Before evaluating a new clock cycle a possible injection scheduler hook function is called.

The simulation framework poses the first instance of manual input for each new RTL model in the proposed simulation toolchain. The reason is that it has an interface with the VRTL core, which is not standardized. For example, the examined RI5CY RISC-V core has a slim input/output profile assuming that more complex interfaces are implemented on top of it, e.g. connect the memory interfaces with a on-chip bus. On the other hand, cores like the OpenRisc1000 implement an on-chip wishbone-bus interface on the RTL's top module.

### 4.1.3. Injection Scheduler

The injection scheduler block acts as an interface to the target dictionary API generated by the modification stage. Additionally, a hook method can be called by the main clock-spin evaluation method in the framework, thus, allowing the scheduler to decide whether an injection should be performed in the current cycle. Injections can be scheduled by passing the target's index or name in the dictionary to the scheduler. Additionally, either the exact bit and clock cycle can be specified or both selected randomly. For random bit, a pseudo random number generator (PRNG) selects a bit within the bit-length of the target. For random clock cycle, the PRNG generates a random number within a configurable interval, e.g. before the faulty simulation, a reference run could be used to determine the actual program cycle count, thus, an injection-effective time interval.

```

void RV32_SoCFrame::

1 void TargetInjectScheduler::

2 clockspin(uint64_t cycles) {

2 hook(void){

3

for (; cycles; cycles--) {

//Call injection scheduler hook

if(mInjListSet.size() <= 0) return</pre>

4

4

TIS->hook();

5

6

6

if(mPU->mCvcles <

//Low clock evaluate

mInjListSet[0]->mInjectionCycle) return;

7

7

mCore -> clk_i = 0;

mInst_I -> update (mCore -> clk_i);

9

{

9

mData_I ->update(mCore ->clk_i);

if(PU->mCycles <=</pre>

10

10

mInjListSet[0]->mInjectionCycle)

mCore -> eval();

11

11

{

12

12

13

//High clock evaluate

13

mInjListSet[0]->arm();

mCore->clk_i = 1;

}

14

14

15

mInst_I -> update (mCore -> clk_i);

15

else

mData_I ->update(mCore ->clk_i);

16

16

{

mCore->eval();

17

mInjListSet[0]->disarm();

17

mInjListDone.push_back(mInjListSet[0]);

18

18

mInjListSet.erase(mInjListSet.begin());

19

//Increment cycle count

19

mPU->mCycles++;

20

}

20

21

}

^{21}

}

22 }

```

Listing 4.1: Virtual SoC clock-spin

Listing 4.2: Injection scheduler hook

For each simulation run multiple injections can be scheduled. Each injections in stored in a buffer sorted for earliest first, i.e. lowest clock cycle injection first. Listing 4.1 shows the

#### 4. Simulation

simulations clock-spin method calling the injection scheduler hook in line 5. Inside the hook, checks are performed whether any injections are scheduled (line 3) and the current clock cycle (mPU->mCycles) is an injection cycle (line 5, 6, 9 and 10). If an injection cycle is reached, the injection is armed meaning the enable flag in the respective target dictionary gets set. On the next call to the hook function the injection gets disarmed, deleted from the todo-list (mInjListSet) and appended to a done-list mInjListDone. Considering the hook method being called in every clock cycle, the sorted list ensures better performance, since no iterations over the injection list have to be performed.

#### 4.1.4. User Interface

For individual handling of the simulation framework, a UI provides dynamic configuration and execution. The GDB inspired command line interface supports the inputs listed in tab. 4.1. The inputs are grouped in *help*, *soc*, *mem*, and *inject*;

help displays interface help for all groups or a specific one,

soc includes commands controlling the simulation target,

mem lets the user read virtual memory content, and hash the virtual memory,

**inject** can return information regarding the target dictionary and scheduled injections. Additionally, the interval for random injections can be set. The load and store functions enable reproducing injection schedules, e.g. a previously stored configuration can be reloaded from configuration file. Injections can be added explicitly or randomly. Furthermore, a hash function performs a hash over all data elements registered in the target dictionary.

On soc run commands the UI returns the following:

- **Application finished:** The application finished its execution. This is detected by a return from the target software's main function

- Cycles done: The model was executed for the set amount of cycles without detecting any system errors.

- System level fault: The system detected an exception, e.g. an illegal instruction.

- Core hang-up: A maximum amount of clock cycles was reached without finishing the program or set amount of clock cycles.

| group  | command                                  | required                                                                       | options                          | example                                                                                                     |

|--------|------------------------------------------|--------------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------|

| help   |                                          |                                                                                |                                  | help                                                                                                        |

| soc    | run<br>load<br>reset<br>info             | <br><br><br><br><br>                                                           | [cycles: int]                    | soc run 100<br>soc load ./foo.bin<br>soc reset<br>soc info                                                  |

| mem    | read<br>hash                             | <address></address>                                                            | [bytes:=4]                       | mem read 0xFF 4<br>mem hash                                                                                 |

| inject | info                                     |                                                                                | [option:<br>{schedule, targets}] | inject info schedule                                                                                        |

|        | load<br>store<br>interval<br>hash<br>add | <pre><config file=""> <config file=""> <l>:<u></u></l></config></config></pre> | [target] [bit] [cycle]           | inject load ./config.txt<br>inject store ./config.txt<br>inject interval 0:100<br>inject hash<br>inject add |

Table 4.1.: User interface input table

#### 4. Simulation

## 4.2. Simulation Setup

The simulation setup can be partitioned in a simulation run and a classification of its results. Both are performed by individual Python scripts. To gather meaningful information about soft error effects on the core under test a large number of random injections have to be managed. The sum of all individual simulation runs is called an evaluation.

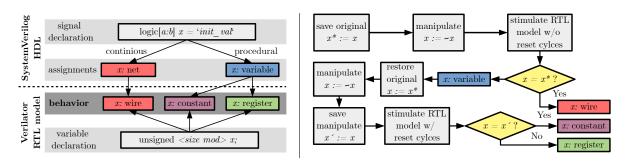

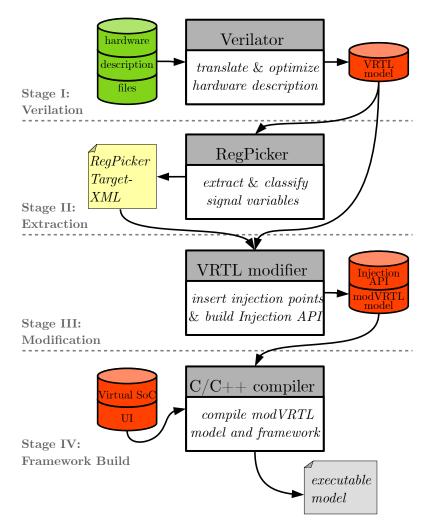

Figure 4.2.: Simulation framework toolchain

### 4.2.1. Target Software

An application program has to be generated. This is done by invoking the GNU RISC-V GCC for the target architecture (RISC-V n.d.). A custom linker script ensures correct linkage with the VSoCs memory space. Furthermore, a simple assembly startup file defines correct program boot behavior and exception handling. The resulting cross-compiled binary can then be passed

| eval. | req.        | executed instructions | data memory reads | data memory<br>writes | instruction fetches |

|-------|-------------|-----------------------|-------------------|-----------------------|---------------------|

| ALU   | 5,904       | 4,658                 | 1,823             | 383                   | 1,393               |

| MUL   | 16,528      | 11,706                | 4,813             | 1,610                 | 3,443               |

| AES   | $142,\!355$ | 106,101               | 34,737            | $12,\!205$            | 33,985              |

Table 4.2.: Target software test properties

through the UI to the simulation framework.

The bare-metal code is based on RISC-V test suits provided by the PULP project. The tests normally confirm whether a core implementing the RISC-V ISA operates as expected. Besides checking the basic functionality of the ISA, each test frequently accesses data memory, where its results are stored. Tab. 4.2 lists some properties, such as read and write accesses to memory, of the tests under normal circumstances, i.e. neither errors nor injections. Evaluation of the RI5CY core was done for an Arithmetic Logic Unit (ALU) test, a Multiplier (MUL) test, and an Advanced Encryption Standard (AES) test. In used prefetch buffer configuration, RI5CY reads 128-bit of instruction data per fetch from memory, which translates to four non-compressed instructions.

#### 4.2.2. Evaluation

To generate a multitude of simulation results as fast as possible, a cluster of linux host machines is used. Each host runs a Python script interacting with the simulation framework's UI by opening a pipelined sub-process. The individual result of a simulation run is appended to a host-unique result file in a simulation setup common directory on the server.

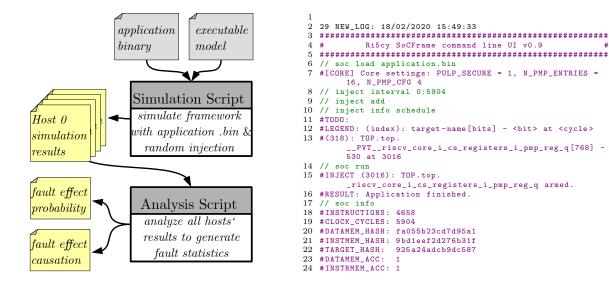

Fig. 4.3 shows the control flow and result for a complete evaluation. The simulation run is initialized with the executable model from the simulation framework toolchain's output and a cross-compiled application software. Listing 4.3 shows an example for a single simulation result returned by the framework's UI. For clarification, the UI commands invoked by the python script are inserted as green lines in the listing and output from the UI in purple. Each simulation run gets a simple header with an index and time stamp determining its start and identity. At first, the framework gets passed the cross-compiled binary's file-location which initiates the VSoC (line 5). Then, the injection interval is set to a significant value, e.g. the expected executing cycles, and a random injection is added and read back (lines 7-9). The simulation is now set up and a endless run invoked (line 13). When the scheduler hook injects the fault, the action is reported by the UI (line 14). In this example, the application software's main function returns to the startup files call to main(), which indicates its finishing state in line 15. Finally, internal information of the VSoC is read out (line 16). This includes the total number of clock cycles and instructions, a hash over the data and instruction memory, a hash over all target dictionary entries' data, and two memory access flags. The memory access flags indicate whether the load script-defined address spaces were violated, i.e. a write to the

#### 4. Simulation

Figure 4.3.: Evaluation run

Listing 4.3: Simulation run output

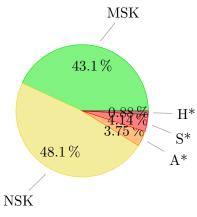

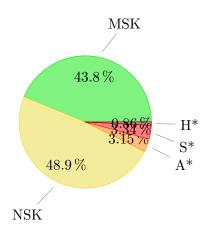

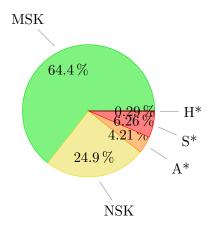

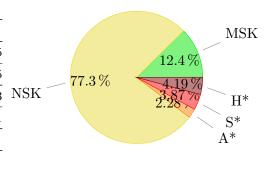

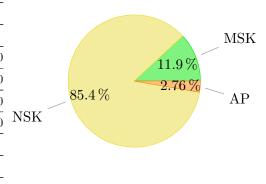

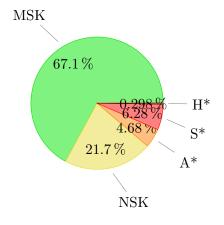

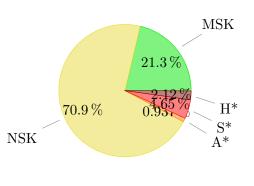

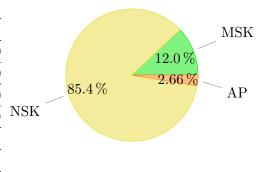

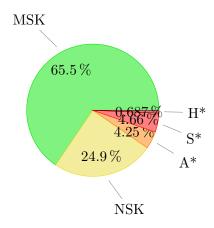

instruction ram was performed or a read from an invalid address.