Fakultät für Luftfahrt, Raumfahrt und Geodäsie

Lehrstuhl für Flugsystemdynamik

# Modular model-based development of safety-critical flight control software

#### Dipl.-Ing. Univ. Markus Tobias Hochstrasser

Vollständiger Abdruck der von der Fakultät für Luftfahrt, Raumfahrt und Geodäsie

der Technischen Universität München

zur Erlangung des akademischen Grades eines

Doktor-Ingenieurs (Dr.-Ing.) genehmigten Dissertation.

| Vorsitzender:            | Prof. DrIng. Oskar J. Haidn       |

|--------------------------|-----------------------------------|

| Prüfer der Dissertation: | 1. Prof. DrIng. Florian Holzapfel |

|                          | 2. Prof. DrIng. Stephan Myschik   |

Die Dissertation wurde am 12.06.2020 bei der Technischen Universität München eingereicht und durch die Fakultät für Luftfahrt, Raumfahrt und Geodäsie am 27.10.2020 angenommen.

#### Acknowledgments

Accomplishing the work for this thesis and writing it down would not have been possible without the support of many people throughout all the years.

The five years at the Institute of Flight Dynamics had become richer of experience than I expected the day, when I joined Prof. Holzapfel's team in 2013. In an enormous team effort, we brought various manned and unmanned aircraft into the sky, with complex and large, but also, and that is even more important, safe software, which did what it was intended to do.

I want to thank all the colleagues I worked with during these years. Our achievements, the long nights, our regular coffee breaks and the conferences spread all over the world, which we attended together, will remain a unique and unforgettable experience in my life.

My special acknowledgments go to Prof. Florian Holzapfel. He gave me the possibility to work with the Institute and organized the funding for this work. He allowed me finding my direction from mechanics to software. Throughout the years, he stood by my side with loyalty and was always available for questions and discussions. With his large network of contacts, he initiated discussions and workshops with software and aerospace experts around the world, which form the solid basis for this thesis.

I also want to sincerely thank Prof. Stephan Myschik. He was a valuable advisor over the years, both technically and psychologically. Without the encouraging and constructive meetings in his office, this thesis probably would have never been finished. Thank you for all the lunches at our Indian restaurant, which we will hopefully continue.

In addition, there were a lot of people from The MathWorks Inc., who supported me with their knowledge during this thesis. Thank you very much for your responsiveness and the opportunity to work together.

Last but not least, I want to thank my family. My wife, who accepted the countless hours in the office and the numerous weekends, which I spent in front of my computer. Thank you for bearing the gray hairs, that literally began to grow during this period of time. And my parents, who always supported me on the path I chose.

#### Kurzfassung

Die Entwicklung sicherheitskritischer Software befindet sich in einem stetig wachsenden Spannungsfeld. Auf der einen Seite wird eine aufwändige und akribische Nachweisführung gefordert, auf der anderen Seite wächst die Softwaregröße sowie die Komplexität der Software rasant. Hinzu kommen immer kürzer werdende Entwicklungszyklen. Für klein- und mittelständische Unternehmen ist ein Einstieg in die sicherheitskritische Softwareentwicklung mit enormem Ressourcenaufwand verbunden. Modellbasierte Softwareentwicklung bildet hier seit jeher eine gute Lösung, stößt aber hinsichtlich der Skalierungsanforderungen zunehmend an ihre Grenzen.

Diese Arbeit stellt einen neuen, durchgängigen Ansatz für modulare, hochautomatisierte modellbasierte Softwareentwicklung mit Simulink<sup>®</sup> und Stateflow<sup>®</sup> der Firma MathWorks vor. Er basiert auf aktuellen Luftfahrtstandards und bietet eine Lösung für die gegensätzlichen Anforderungen in der Softwareentwicklung.

Im Rahmen der Arbeit wurde ein modularer Entwicklungszyklus und -prozess entwickelt, der auf einem modularen Codegenerierungsansatz basiert und sich damit maßgeblich von existierenden Lösungen mit integraler Codegenerierung unterscheidet. Für den Prozess wurden neue Modellierungsrichtlinien definiert sowie eine Vielzahl an Artefakten implementiert, die beim Aufsetzten einer konsistenten Entwicklungs- und Simulationsumgebung, modularer Codegenerierung sowie einer weitgehend automatisierten Erstellung der Zertifizierungsnachweise unterstützen.

Das neu entwickelte Softwarewerkzeug *SimPol* unterstützt bei der Umsetzung der durch Standards geforderten bidirektionalen Nachverfolgbarkeitsanforderungen mit Siemens Polarion<sup>®</sup> REQUIREMENTS™. Das Softwarewerkzeug hebt sich in Bezug auf Datenmodell, Arbeitsablauf, und Konfigurationsmanagement von bestehenden Lösungen ab und eröffnet dadurch neue Möglichkeiten der automatisierten Verifikation, Reparatur und Bearbeitung von Verweisen.

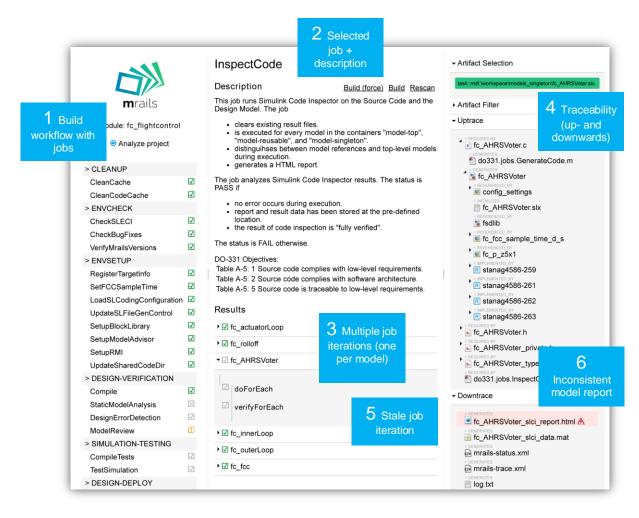

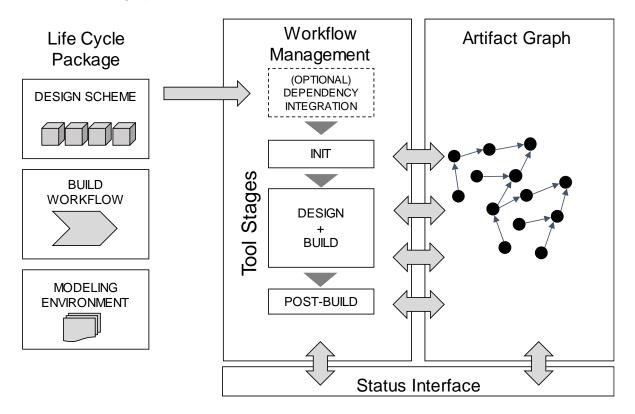

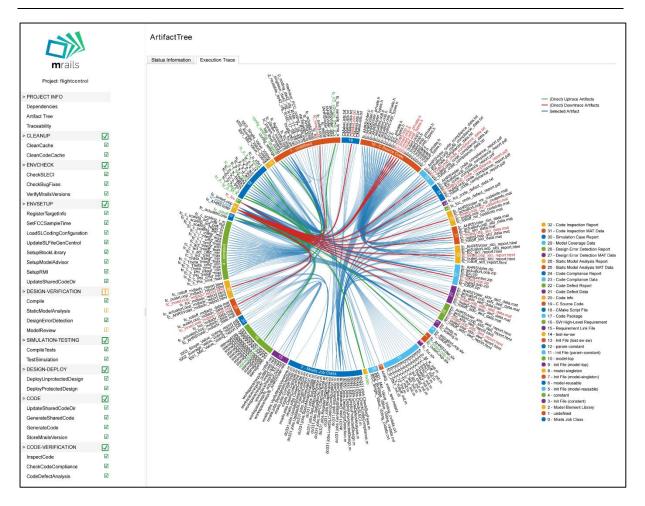

Das neuartige, auf Prozessaufgaben maßgeschneiderte Automatisierungswerkzeug *mrails* kombiniert Informationen aus der Automatisierung und statischen Nachverfolgbarkeitsverweisen und erlaubt dadurch die automatisierte Überprüfung der Aktualität, Konsistenz und Vollständigkeit von Entwicklungs- und Verifikationsartefakten. Zudem stellt es hochintegrierte Arbeitsabläufe für Review-Aufgaben bereit. Die Anwendbarkeit wird mit einer exemplarischen, weitgehend vollständigen Implementierung des modularen Entwicklungsprozesses demonstriert.

#### Abstract

Development of safety-critical software emerges in a field of tension between implementation rigor and extensive verification evidence on the one hand as well as steadily growing software complexity and size combined with shorter development cycles on the other hand. For small and medium size companies, entering the market of safety-critical software development is connected to enormous efforts. Model-based software development has been a viable solution to reduce adoption risks for years, but faces more and more scalability limitations.

This thesis presents a new, consistent approach for modular, highly automated model-based software development based on Simulink<sup>®</sup> and Stateflow<sup>®</sup> of The MathWorks. It respects the currently accepted software development standards for airborne software and has the objective to eliminate the opposing requirements of software development.

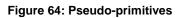

In the scope of this work, a modular development life cycle and process has been developed with generation of modular code at its core. Thereby, the approach significantly differentiates from existing solutions, which apply integral code generation. For this process, new modeling guidelines have been defined as well as a variety of artifacts been implemented, which support the setup of a consistent development and simulation environment, generation of modular code, and a broadly automated creation of certification evidence.

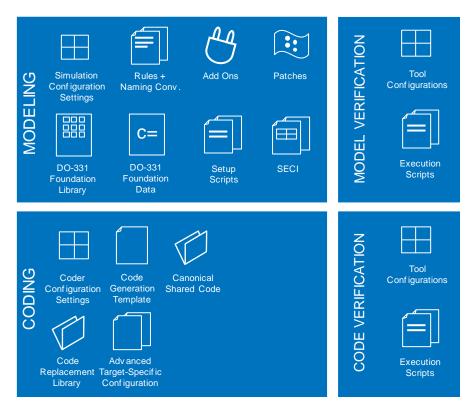

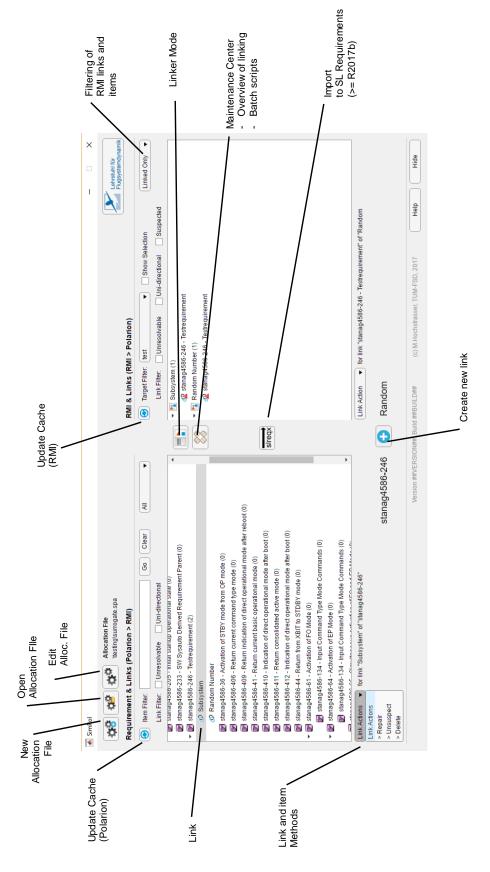

The novel software tool *SimPol* helps to implement standard-compliant, bidirectional traceability between Siemens Polarion<sup>®</sup> REQUIREMENTS<sup>™</sup> and artifacts from the model-based environment. The tool sets itself apart from existing solutions with respect to its data model, workflows, and configuration management capabilities. It allows automated verification, repair, and editing of traces.

The new, process-oriented build tool *mrails* combines data obtained from automation with static traceability and derives information about up-to-dateness, consistency, and completeness of development and verification artifacts. In addition, it provides deeply integrated workflows for review tasks. Its applicability is shown with an exemplarily, almost complete implementation of the modular development process.

## **Table of Contents**

| 1.1 Background    1.2 Objective and motivation              |

|-------------------------------------------------------------|

| -                                                           |

| 1.3 Scope                                                   |

|                                                             |

| 1.4 Structure of the thesis                                 |

| 1.5 Contributions                                           |

| 1.5.1 Modular development process (part 1)                  |

| 1.5.2 Modeling framework for safety-critical MBSwD in SL/SF |

| 1.5.3 Traceability rules and tooling10                      |

| 1.5.4 Process-oriented build tool and process automation10  |

| 1.5.5 Modular development process (part 2)1                 |

| 2 Fundamentals14                                            |

| 2.1 Certification basis15                                   |

| 2.2 ARP-4754A system development process15                  |

| 2.3 DO-178C                                                 |

| 2.4 DO-331                                                  |

| 2.5 DO-33324                                                |

| 2.6 DO-330 Tool qualification25                             |

| 2.7 Model-based design and software development26           |

| 3 Project context                                           |

| 3.1 MBSwD as embedded process27                             |

| 3.2 Hardware                                                |

| 3.3 Software components                                     |

| 3.4 Summary of assumptions                                  |

| 4 Modular development process (part 1)                      |

| 4.1 Objective                                               |

| 4.2 State-of-the-art                                        |

| 4.3 Structure                                               |

| 4.4 Software Life Cycle43                                   |

| 4.4.1 Model usage43                                         |

| 4.4.2 MBSwD process breakdown46                             |

| 4.4.3 Modular code49                                        |

| 4.5 Development Processes                                   |

| 4.5.1 Requirements Process (R)                       | 51  |

|------------------------------------------------------|-----|

| 4.5.2 Design Process (D)                             | 53  |

| 4.5.3 Coding Process (C)                             | 56  |

| 4.6 Verification Processes                           | 57  |

| 4.6.1 Review and analysis of Design Process          | 58  |

| 4.6.2 Review and analysis of Coding Process          | 60  |

| 4.6.3 Model simulation and testing                   | 61  |

| 4.6.4 Data coupling and control coupling analysis    | 71  |

| 4.6.5 Complete testing approach                      | 73  |

| 5 Modeling framework for safety-critical MBSwD in SL | 75  |

| 5.1 Objective                                        | 75  |

| 5.2 State-of-the-art                                 | 75  |

| 5.3 Structure                                        | 78  |

| 5.4 Design rules                                     | 81  |

| 5.4.1 Summary of rules                               | 81  |

| 5.4.2 Conformance                                    | 82  |

| 5.4.3 Compliance                                     | 82  |

| 5.4.4 High-level architectural design                | 86  |

| 5.4.5 Accuracy and consistency                       | 98  |

| 5.4.6 Algorithm aspects                              | 101 |

| 5.4.7 Traceability                                   | 101 |

| 5.4.8 Target compatibility                           | 102 |

| 5.4.9 Verifiability                                  | 103 |

| 5.5 Coding rules for code generation                 | 110 |

| 5.6 Module design rules                              | 111 |

| 5.6.1 Summary of rules                               | 111 |

| 5.6.2 Naming convention                              | 112 |

| 5.6.3 High-level architectural design                | 113 |

| 5.6.4 Detailed design                                | 128 |

| 5.6.5 Implementation of DO-178C concepts             | 175 |

| 5.7 Fundamental modeling rules                       | 184 |

| 5.8 Modeling environment                             | 185 |

| 5.9 Summary and outlook                              | 187 |

| 6 Traceability tooling and rules                     | 189 |

| 6.1 Objectives                                       | 189 |

| 6.2 State-of-the-art                                                  |     |

|-----------------------------------------------------------------------|-----|

| 6.3 Structure                                                         |     |

| 6.4 SimPol                                                            |     |

| 6.5 Traceability rules                                                | 200 |

| 6.5.1 Summary of rules                                                | 200 |

| 6.5.2 RMI settings                                                    | 200 |

| 6.5.3 Requirement allocation to modules                               | 201 |

| 6.5.4 Traceability to higher-level requirements                       | 202 |

| 6.5.5 Derived LLRs                                                    | 205 |

| 6.6 Summary and outlook                                               | 207 |

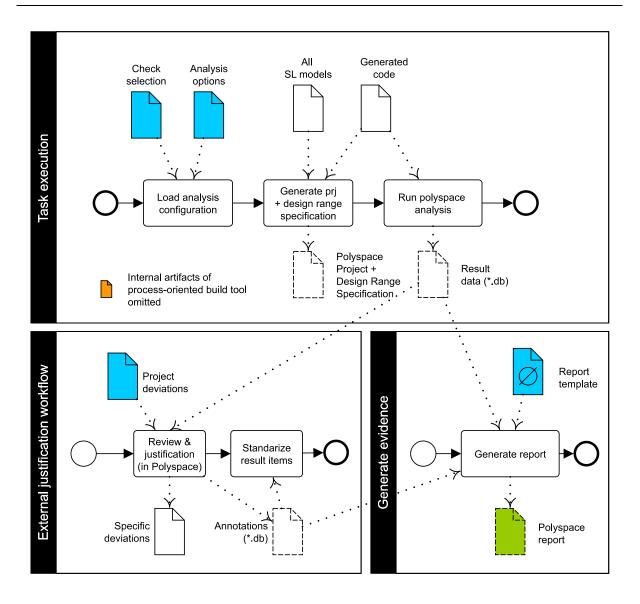

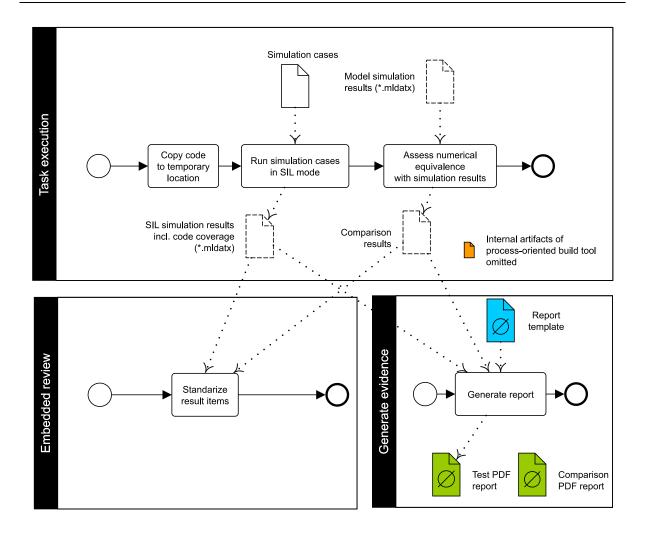

| 7 Process-oriented build tool and process automation                  | 208 |

| 7.1 Objective                                                         | 208 |

| 7.2 State-of-the-art                                                  | 208 |

| 7.3 Structure                                                         | 212 |

| 7.4 Process-oriented build tool                                       | 212 |

| 7.4.1 Application life cycle                                          | 212 |

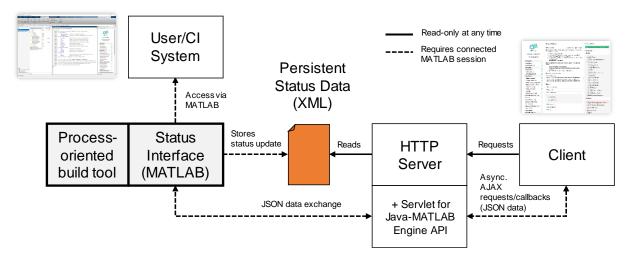

| 7.4.2 Implementation Overview                                         | 217 |

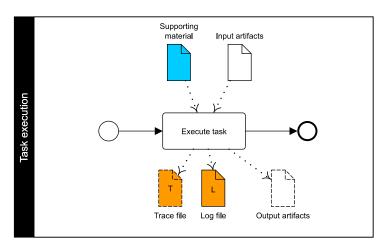

| 7.5 Standardized implementation of build jobs                         | 221 |

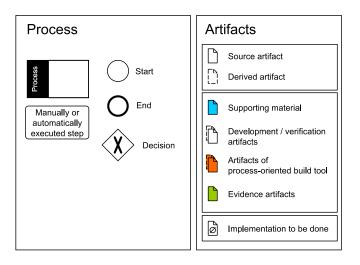

| 7.5.1 Process notation                                                | 221 |

| 7.5.2 Job execution standardization                                   | 222 |

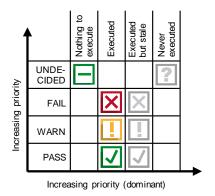

| 7.5.3 Job result standardization                                      | 224 |

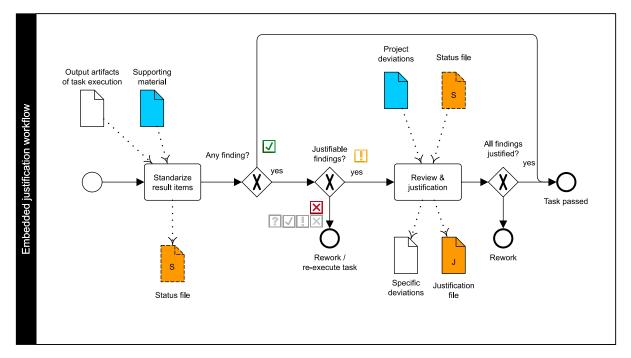

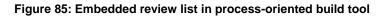

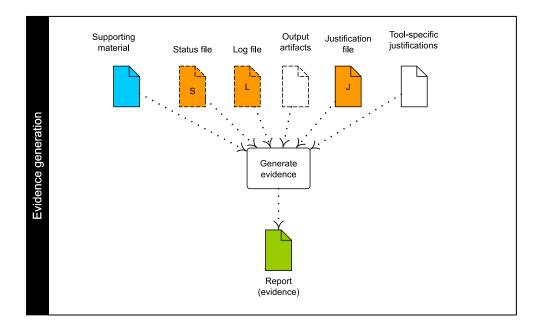

| 7.5.4 Justification workflows                                         | 225 |

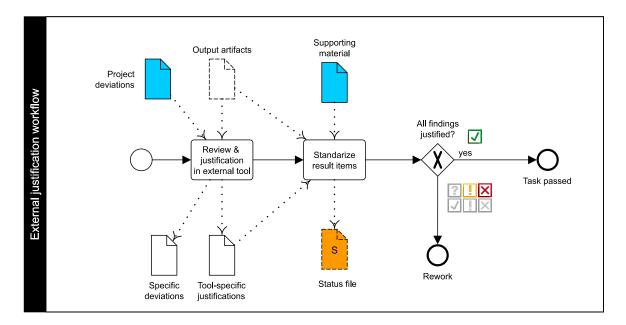

| 7.5.5 Evidence generation                                             | 227 |

| 7.6 Summary and outlook                                               | 229 |

| 8 Modular development process (part 2)                                | 230 |

| 8.1 Development tasks                                                 | 230 |

| 8.1.1 SwDP-DP-MB 6 – Assembly of Design Description                   | 230 |

| 8.1.2 SwDP-CP-MB 1 –Modular source code                               | 230 |

| 8.2 Verification tasks                                                | 242 |

| 8.2.1 SwVP-DP-MB 1 – Static model analysis                            | 242 |

| 8.2.2 SwVP-DP-MB 2 – Static module analysis                           | 247 |

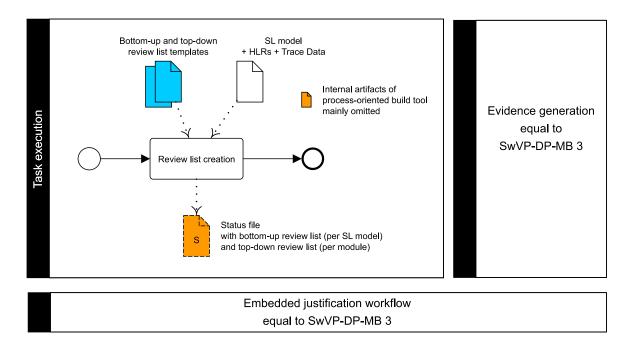

| 8.2.3 SwVP-DP-MB 3 – Model review                                     | 248 |

| 8.2.4 SwVP-DP-MB 4 – Traceability review and analysis                 | 251 |

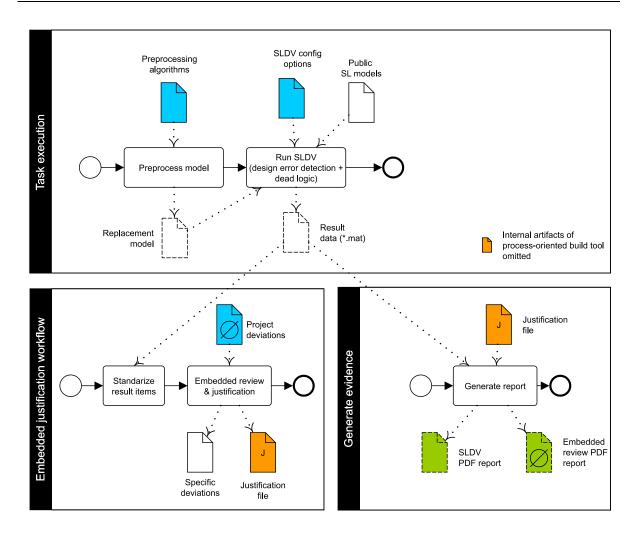

| 8.2.5 SwVP-DP-MB 5 – Design error detection                           | 253 |

| 8.2.6 SwVP-DP-MB 6 – Simulation / test procedure and case development | 261 |

| 8.2.7 SwV      | P-DP-MB 7 – Simulation / test case and procedure review   | 262    |

|----------------|-----------------------------------------------------------|--------|

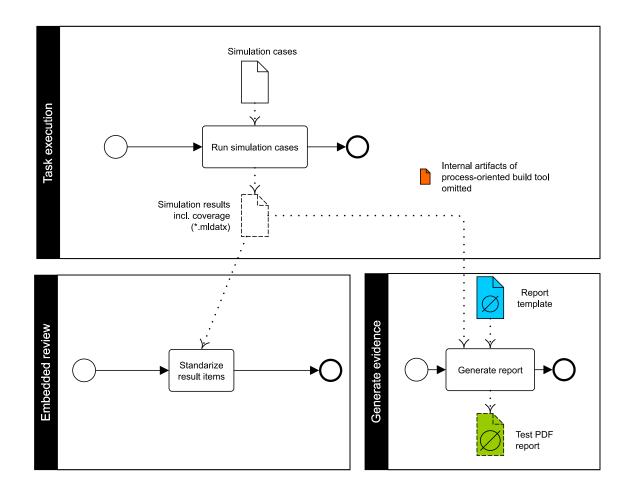

| 8.2.8 SwV      | P-DP-MB 8 – Simulation testing & result review            |        |

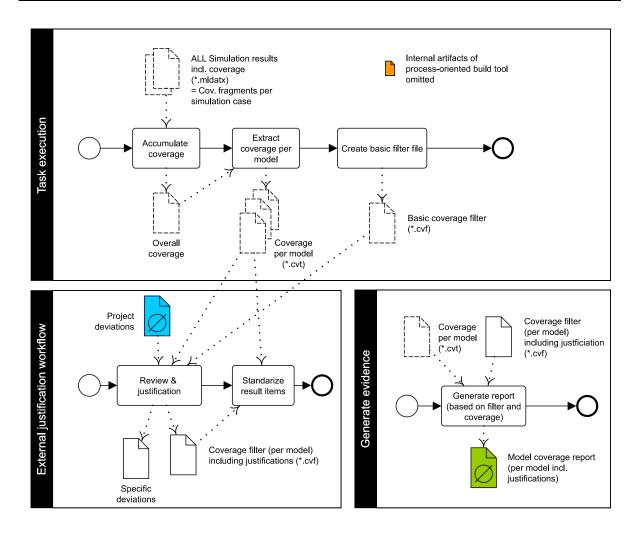

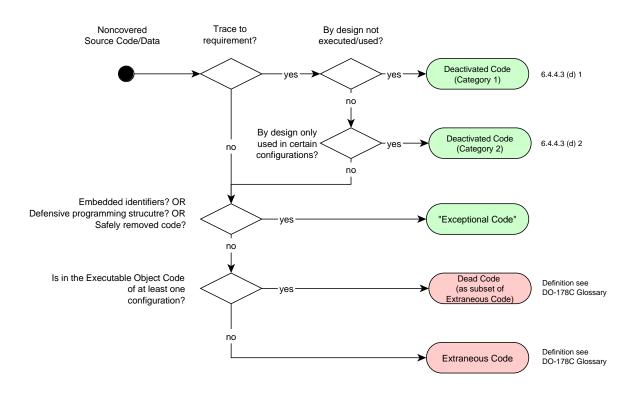

| 8.2.9 SwV      | P-DP-MB 9 – Model coverage assessment                     |        |

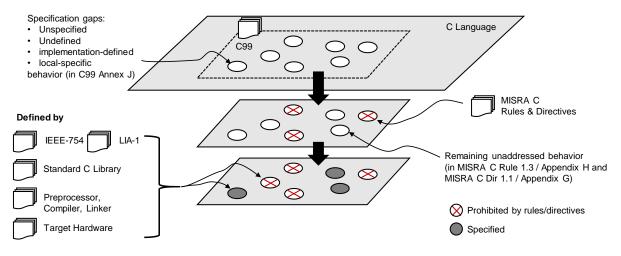

| 8.2.10 Sw      | /P-CP-MB 1 – Automatic code review                        | 273    |

| 8.2.11 Sw      | /P-CP-MB 2 – Static code analysis for standard compliance | 276    |

| 8.2.12 Sw      | /P-CP-MB 3 – Static code analysis for error detection     | 281    |

| 8.2.13 Sw      | /P-CP-MB 4 – Code review                                  |        |

| 8.2.14 Sw      | /P-CP-MB 5 – Code proving                                 |        |

| 8.2.15 Sw      | /P-CP-MB 6 – SIL testing & result review                  | 284    |

| 8.2.16 Sw      | /P-CP-MB 7 – SIL structural coverage assessment           |        |

| 8.3 Summary    | / and outlook                                             | 290    |

| 9 Conclusions. |                                                           | 292    |

| 10 References  |                                                           | 1      |

| Appendix A     | Review and analysis of data coupling and control coupling | XIII   |

| Appendix B     | Coding rules for code generation                          | XVI    |

| Appendix C     | Code generation examples                                  | XXVI   |

| Appendix D     | Comparison of Standard C Library integrations             | XXXII  |

| Appendix E     | Selected code generation settings                         | XXXIII |

| Appendix F     | Simulink Design Verifier model preprocessing              | XXXIV  |

| Appendix G     | Simulation case development rules                         | XXXVII |

| Appendix H     | List of artifacts                                         | XLII   |

## List of Figures

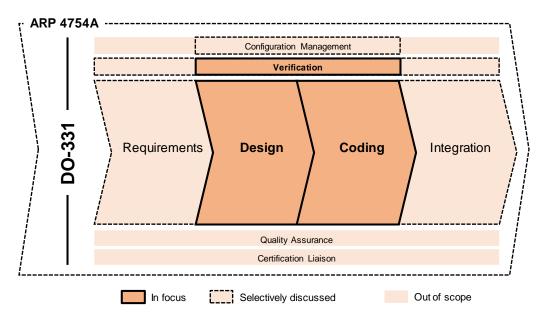

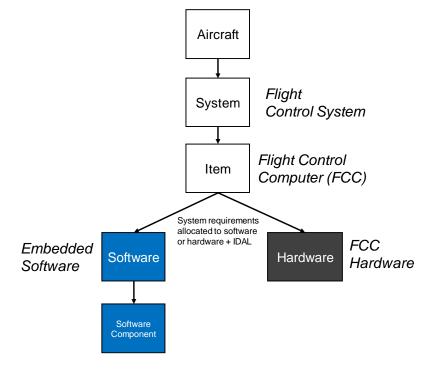

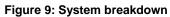

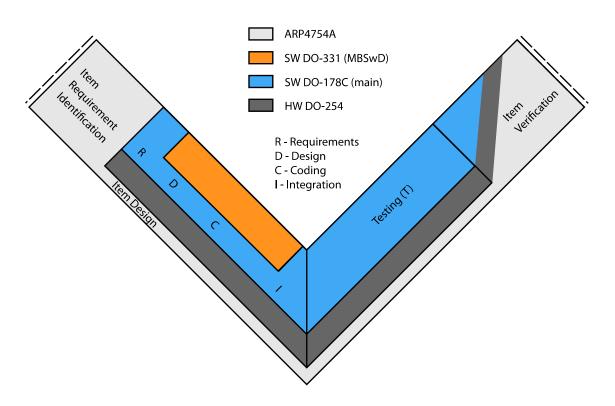

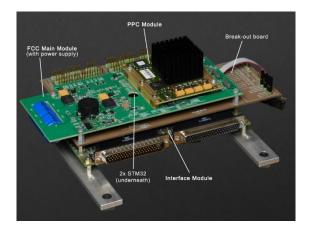

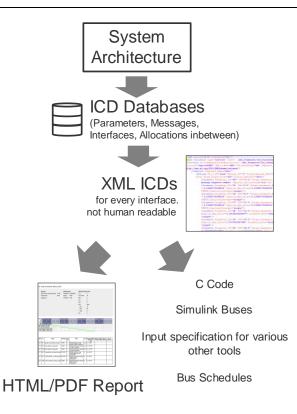

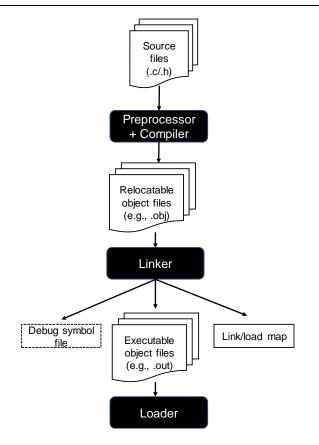

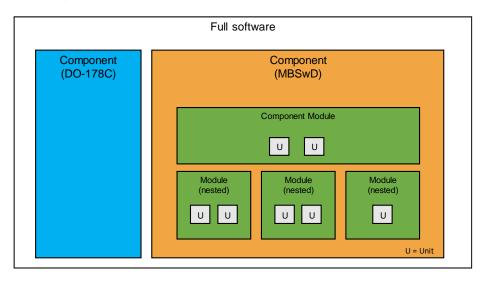

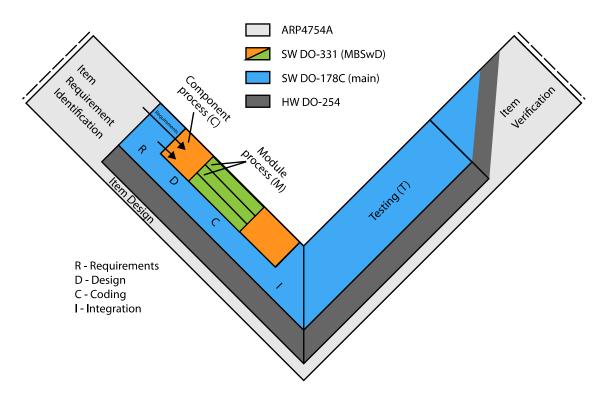

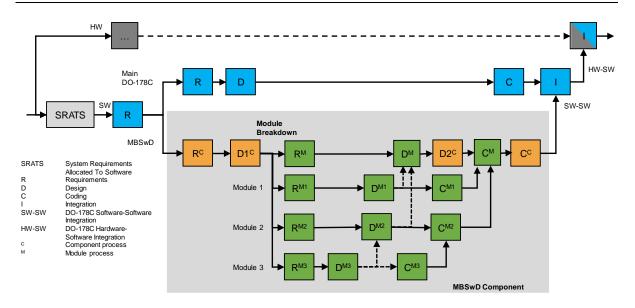

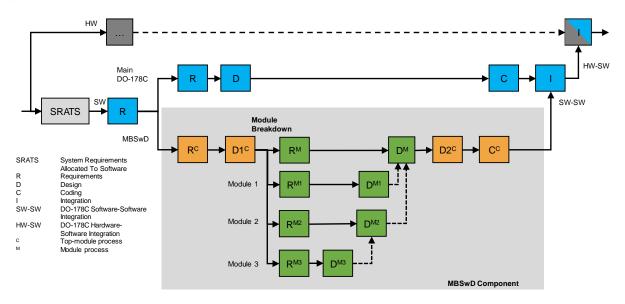

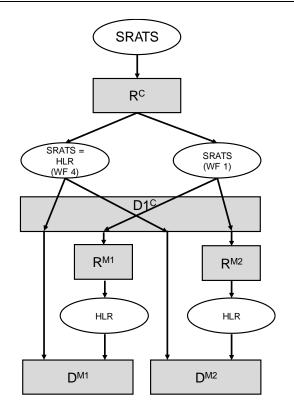

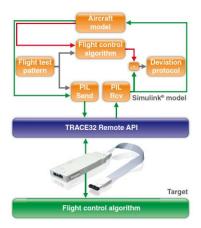

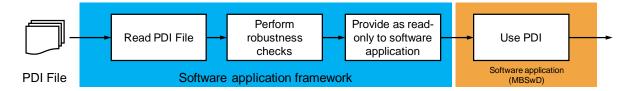

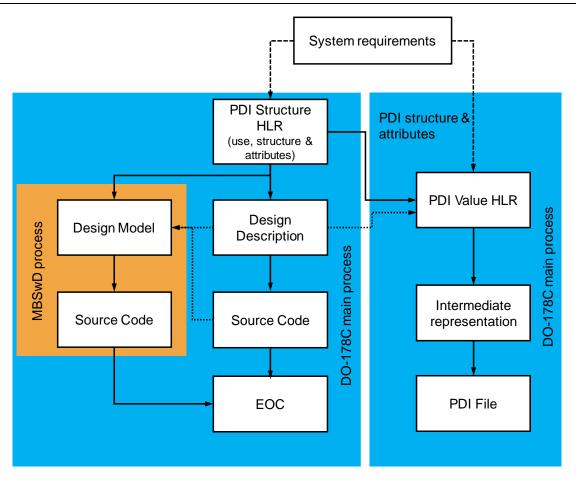

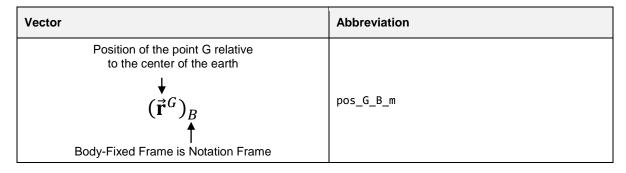

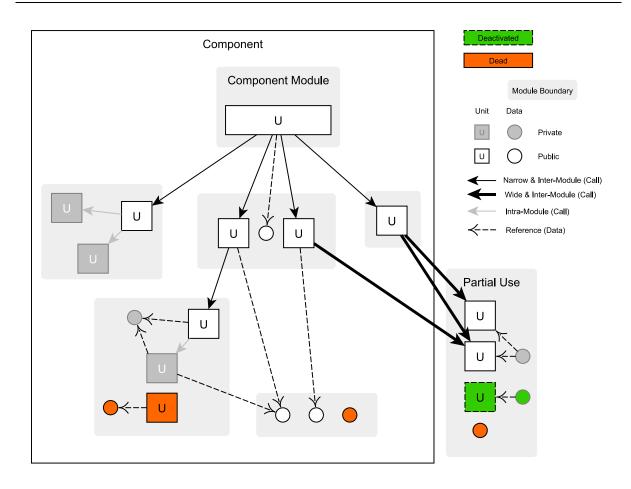

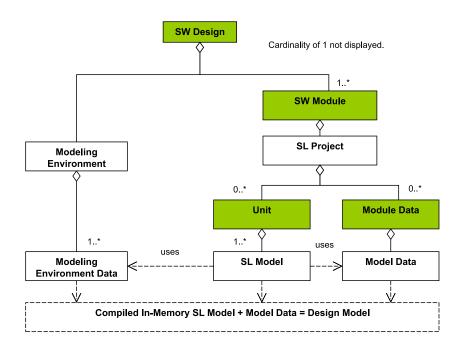

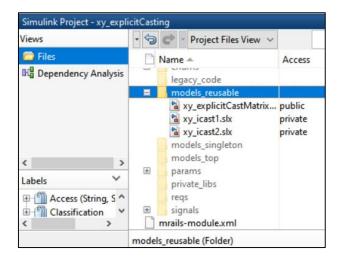

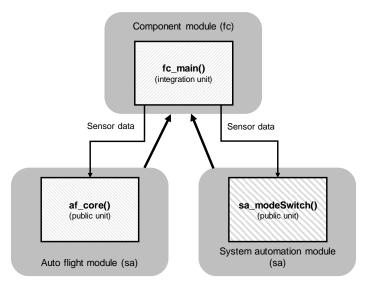

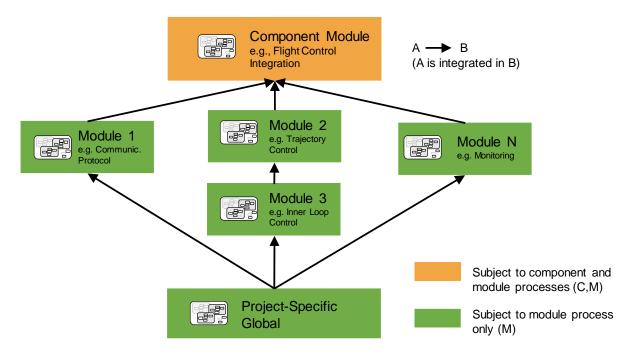

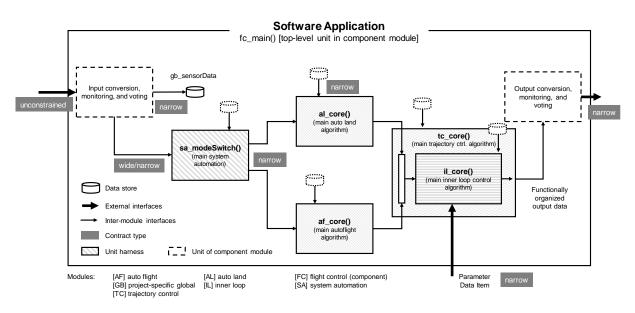

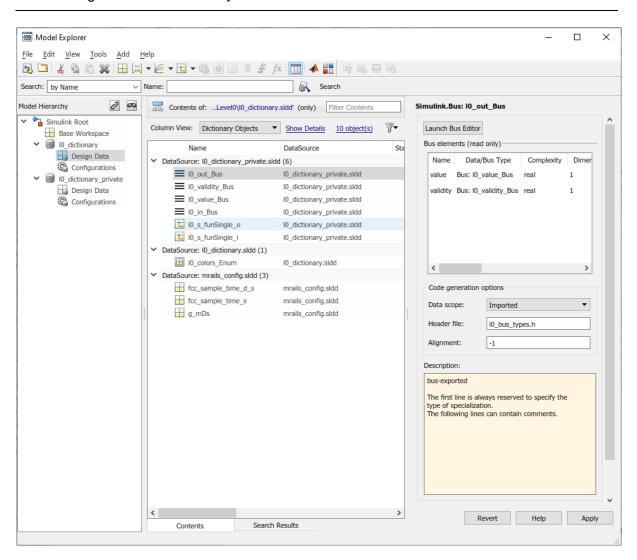

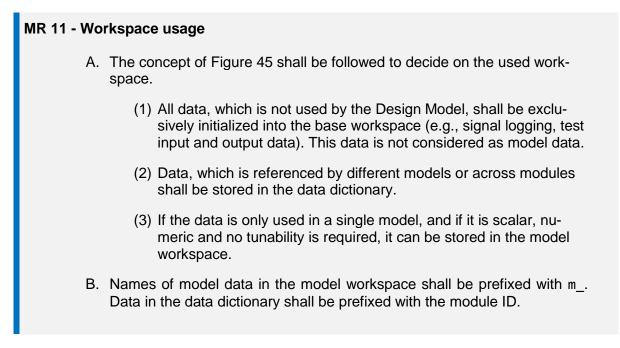

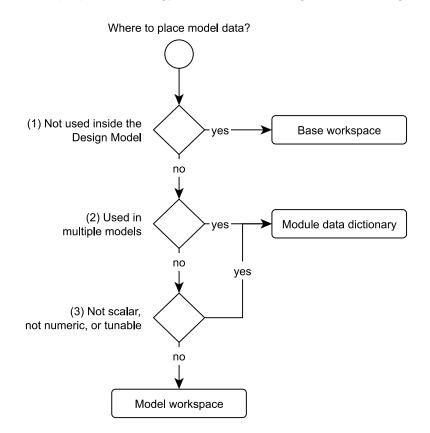

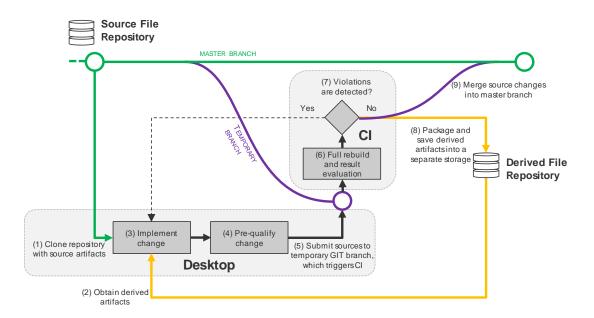

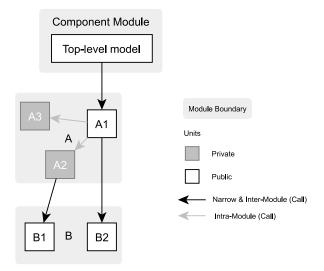

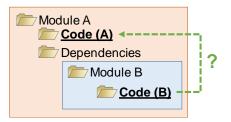

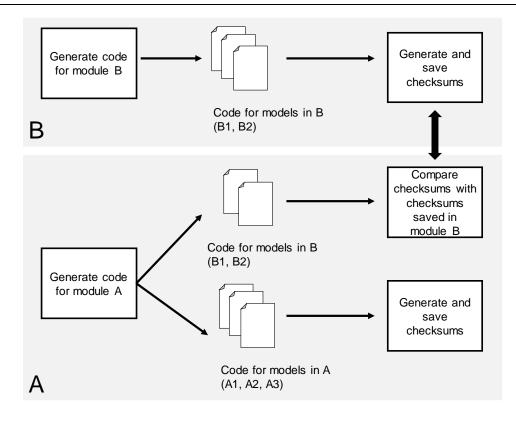

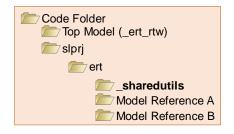

| Figure 3: Simplified ARP-4754A process       16         Figure 4: Processes and objectives summarized in DO-178C.       17         Figure 5: DO-178C process in a V-model software life cycle       19         Figure 6: Testing activities from DO-178C Figure 6-1       21         Figure 7: Development and verification traceability according to DO-178C.       23         Figure 8: Model simulation usage possibilities according to DO-311 MB.6.8       24         Figure 9: System breakdown       27         Figure 10: Integration of system, hardware, and software processes       29         Figure 11: FCC hardware       30         Figure 12: FCC hardware       30         Figure 13: FCC processor communication (from [37])       31         Figure 14: Software components on PowerPC based on considerations from [50] and [52]       32         Figure 15: Interface control and generation process       33         Figure 14: Software components on fow diagram with three exemplary sub-processes       47         Figure 22: MBSwD process breakdown as V-model       47         Figure 22: SRATS categorization and refinement       52         Figure 23: Traditional integral code generation approach       49         Figure 24: Duplication of low-level testing (DO-178C 6.4)       63         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#3)       66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Figure 2: Software component in context       14         Figure 3: Simplified ARP-4754A process       16         Figure 4: Processes and objectives summarized in DO-178C       17         Figure 5: DO-178C process in a V-model software life cycle       19         Figure 6: Testing activities from DO-178C Figure 6-1       21         Figure 7: Development and verification traceability according to DO-178C       23         Figure 9: System breakdown       27         Figure 10: Integration of system, hardware, and software processes       29         Figure 11: FCC hardware modules       30         Figure 12: FCC hardware modules       30         Figure 13: FCC sequence of tasks from [37]       31         Figure 14: Strökrare components on PowerPC based on considerations from [50] and [52]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 19: MBSwD process breakdown as V-model       47         Figure 20: MBSwD process breakdown as V-model       47         Figure 21: Contractural breakdown of software       48         Figure 22: SATS categorization and refinement       52         Figure 23: Traditional integral code generation approach       49         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)                                                                                                                                             | Figure 1: Considered development and integral processes in the scope of the thesis            | 5     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------|

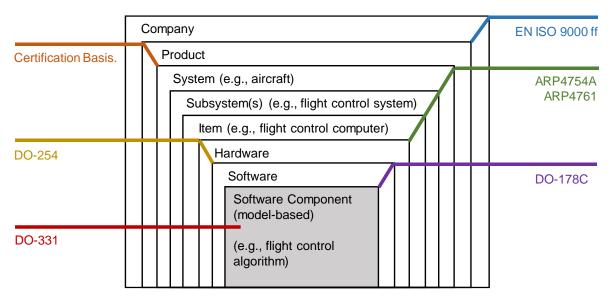

| Figure 4: Processes and objectives summarized in DO-178C.       17         Figure 5: DO-178C process in a V-model software life cycle       19         Figure 5: Exsting activities from DO-178C Figure 6-1       21         Figure 7: Development and verification traceability according to DO-178C.       23         Figure 9: System breakdown       27         Figure 10: Integration of system, hardware, and software processes       29         Figure 11: FCC hardware       30         Figure 12: FCC hardware modules       30         Figure 13: FCC processor communication (from [37])       31         Figure 13: FCC sequence of tasks from [37]       32         Figure 14: Storware components on PowerPC based on considerations from [50] and [52]       32         Figure 13: FCC sequence of tasks from [37]       32         Figure 13: FCC sequence of tasks from [37]       32         Figure 13: FCC sequence of tasks from [37]       32         Figure 13: Motivectural breakdown as V-model       47         Figure 12: CC bardware sequence       46         Figure 12: CC bardware sequence of tasks from [37]       32         Figure 21: Compilation, linking, and loading.       37         Figure 13: MoSWD process breakdown as V-model       47         Figure 22: Control and generation approach       48         Figure 23:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Figure 4: Processes and objectives summarized in DO-178C.       17         Figure 5: DO-178C process in a V-model software life cycle       19         Figure 6: Testing activities from DO-178C Figure 6-1       21         Figure 7: Development and verification traceability according to DO-178C.       23         Figure 8: Model simulation usage possibilities according to DO-331 MB.6.8       24         Figure 9: System breakdown       27         Figure 10: Integration of system, hardware, and software processes       29         Figure 11: FCC hardware modules       30         Figure 12: FCC hardware modules       30         Figure 13: FCC processor communication (from [37])       31         Figure 14: Software components on PowerPC based on considerations from [50] and [52]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 12: Compilation, linking, and loading       37         Figure 22: SMBS/D process breakdown as V-model       47         Figure 22: Start Scategorization and refinement       52         Figure 22: Start Scategorization and refinement       52         Figure 23: Purpose of structural coverage (according to DO-248C FAQ#43).       66         Figure 24: Duplication of low-level testing toral and Control Coupling (DO-178C D-107.       71                                                                                                              | Figure 2: Software component in context                                                       | 14    |

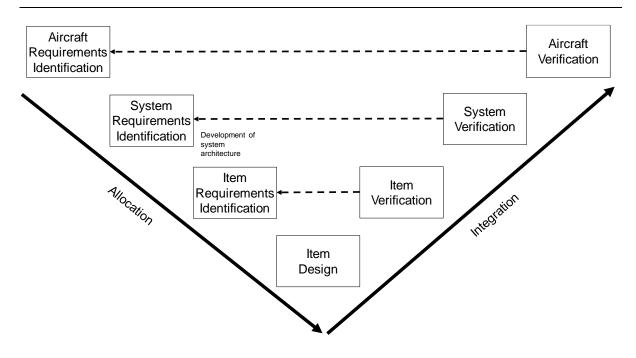

| Figure 5: DO-178C process in a V-model software life cycle       19         Figure 6: Testing activities from DO-178C Figure 6-1       21         Figure 9: Nodel simulation usage possibilities according to DO-331 MB.6.8       24         Figure 9: System breakdown       27         Figure 10: Integration of system, hardware, and software processes       29         Figure 11: CC hardware       30         Figure 12: FCC hardware modules       30         Figure 13: FCC processor communication (from [37])       31         Figure 13: FCC sequence of tasks from [37]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 12: COmpilation, linking, and loading.       37         Figure 12: Compilation, linking, and loading.       37         Figure 22: MBSwD process breakdown as V-model.       47         Figure 23: Test cases and test procedures (DO-178C f.4)       62         Figure 24: Duplication of low-level testing (DO-178C f.4)       63         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 25: Durpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 25: Durpose of structural coverage (according to DO-248C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 5: DO-178C process in a V-model software life cycle       19         Figure 6: Testing activities from DO-178C Figure 6-1       21         Figure 7: Development and verification traceability according to DO-178C.       23         Figure 9: System breakdown       27         Figure 10: Integration of system, hardware, and software processes       29         Figure 11: ECC hardware modules       30         Figure 12: FCC hardware modules       30         Figure 13: FCC processor communication (from [37])       31         Figure 13: FCC sequence of tasks from [37]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 17: Compilation, linking, and loading       37         Figure 20: MBSwD process breakdown as V-model       47         Figure 21: Traditional integral code generation approach       49         Figure 22: SRATS categorization and refinement       52         Figure 23: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 24: Duplication of low-level testing UD-178C 6.4)       63         Figure 25: Purpose of structural coverage (according to DO-178C P.110f)       <                                                                                                                                      |                                                                                               |       |

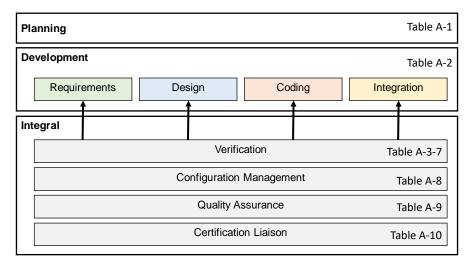

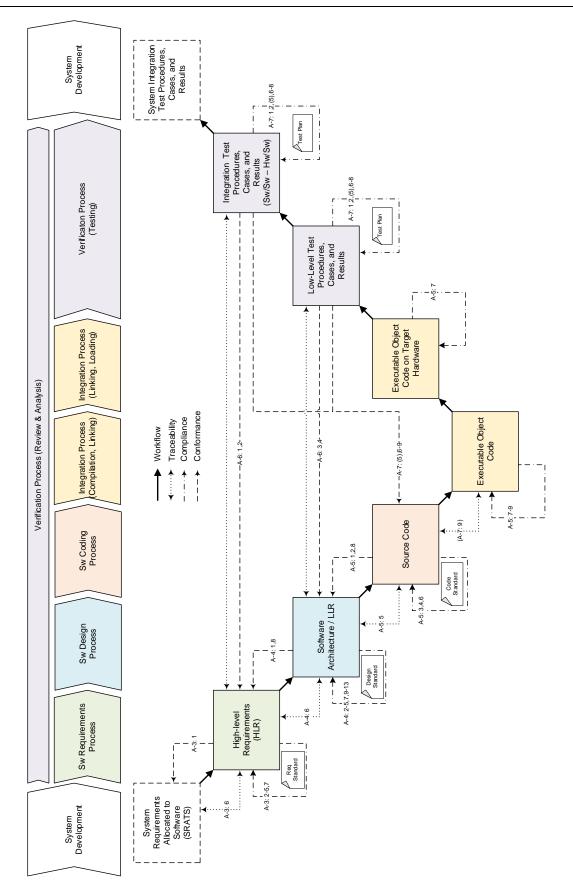

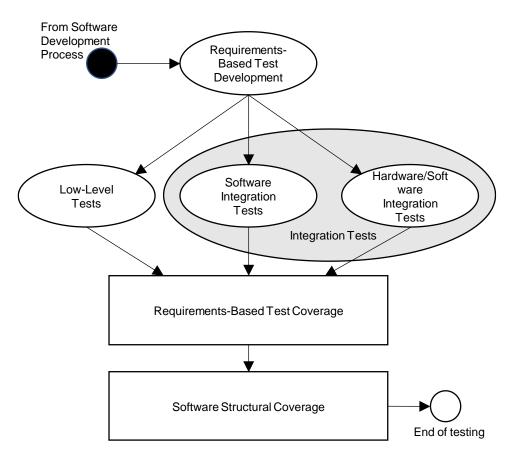

| Figure 6: Testing activities from DO-178C Figure 6-1       21         Figure 7: Development and verification traceability according to DO-178C       23         Figure 8: Model simulation usage possibilities according to DO-331 MB.6.8       24         Figure 9: System breakdown       27         Figure 10: Integration of system, hardware, and software processes       29         Figure 11: FCC hardware       30         Figure 12: FCC hardware modules       30         Figure 13: FCC processor communication (from [37])       31         Figure 14: Software components on PowerPC based on considerations from [50] and [52]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 19: MBSwD process breakdown as V-model       47         Figure 21: MSwD process breakdown as V-model       47         Figure 22: SRATS categorization and refinement       52         Figure 23: Test cases and test procedures (DO-178C C.4)       63         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 25: Durpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 25: Nodeling framework overview       79         Figure 26: PUL setup for software integration and low-level testing using Trace32 (from [97])       68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 6: Testing activities from DO-178C Figure 6-1       21         Figure 7: Development and verification traceability according to DO-178C.       23         Figure 8: Model simulation usage possibilities according to DO-331 MB.6.8       24         Figure 9: System breakdown       27         Figure 10: Integration of system, hardware, and software processes.       29         Figure 11: FCC hardware modules       30         Figure 12: FCC bardware components on PowerPC based on considerations from [50] and [52]       32         Figure 13: FCC sequence of tasks from [37]       32         Figure 14: Software components on PowerPC based on considerations from [50] and [52]       32         Figure 15: Interface control and generation process       33         Figure 16: Interface control and generation process       33         Figure 20: MBSvD process breakdown as V-model       47         Figure 21: Traditional integral code generation approach       49         Figure 22: SRATS categorization and refinement       52         Figure 23: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 24: Duplication of low-level testing 0D0-178C cA)       63         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure                                                                                               | Figure 4: Processes and objectives summarized in DO-178C                                      | 17    |

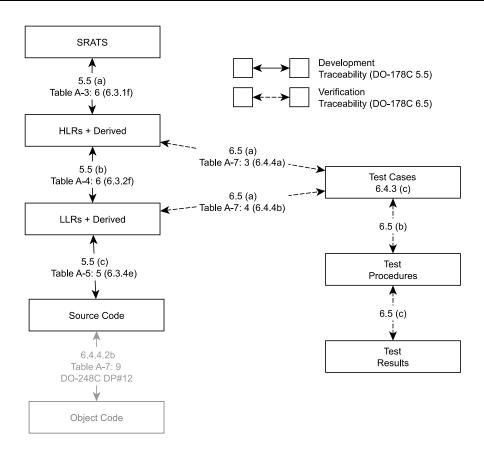

| Figure 7: Development and verification traceability according to DO-178C.       23         Figure 8: Model simulation usage possibilities according to DO-331 MB.6.8.       24         Figure 9: System breakdown.       27         Figure 10: Integration of system, hardware, and software processes.       29         Figure 11: FCC hardware       30         Figure 12: FCC hardware modules       30         Figure 13: FCC processor communication (from [37])       31         Figure 14: Software components on PowerPC based on considerations from [50] and [52]       32         Figure 16: Interface control and generation process       33         Figure 16: Interface control and generation process       33         Figure 13: Architectural breakdown of software       46         Figure 14: MBSwD process breakdown as 1-model.       47         Figure 22: SRATS categorization and refinement       52         Figure 23: Traditional integral code generation approach       49         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 26: PIL setup for software integration and low-level testing using using US-178C (100-178C 1.1.13)       68         Figure 25: Purpose                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 7: Development and verification traceability according to DO-178C.       23         Figure 8: Model simulation usage possibilities according to DO-331 MB.6.8       24         Figure 9: System breakdown       27         Figure 11: Ittegration of system, hardware, and software processes       29         Figure 12: FCC hardware modules       30         Figure 12: FCC hardware modules       30         Figure 13: FCC processor communication (from [37])       31         Figure 14: Software components on PowerPC based on considerations from [50] and [52]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 19: MBSwD process breakdown as flow diagram with three exemplary sub-processes       48         Figure 21: Traditional integral code generation approach       49         Figure 22: SRATS categorization and refinement       52         Figure 23: Test cases and test procedures (DO-178C 11.13)       62         Figure 24: Duplication of low-level testing (DO-178C 6.4)       63         Figure 25: Onlase dy definition of data and Control Coupling (DO-178C p.110f)       71         Figure 26: PIL setup for software integration and low-level testing using Trace32 (from [97])       68         Figure 27: DO-178C Glossary definition of data and Control Coupling (DO-178C p.110f)       71 <td>Figure 5: DO-178C process in a V-model software life cycle</td> <td> 19</td> | Figure 5: DO-178C process in a V-model software life cycle                                    | 19    |

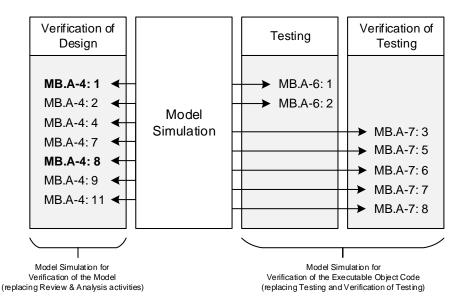

| Figure 8: Model simulation usage possibilities according to DO-331 MB.6.8.       24         Figure 9: System breakdown       27         Figure 10: Integration of system, hardware, and software processes.       29         Figure 11: FCC hardware       30         Figure 12: FCC hardware modules       30         Figure 13: FCC processor communication (from [37])       31         Figure 13: FCC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 17: Compilation, linking, and loading.       37         Figure 20: MBSwD process breakdown as V-model       46         Figure 21: Traditional integral code generation approach       49         Figure 22: SRATS categorization and refinement       52         Figure 23: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 26: PU setup for software integration and low-level testing using Trace32 (from [97])       68         Figure 27: Do-178C glossary definition of data and Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 8: Model simulation usage possibilities according to DO-331 MB.6.8.       24         Figure 9: System breakdown       27         Figure 10: Integration of system, hardware, and software processes.       29         Figure 11: FCC hardware       30         Figure 12: FCC hardware modules       30         Figure 13: FCC processor communication (from [37])       31         Figure 13: FCC processor communication process       33         Figure 14: Strokare components on PowerPC based on considerations from [50] and [52]       32         Figure 16: Interface control and generation process       33         Figure 16: Interface control and generation process       33         Figure 18: Architectural breakdown of software       46         Figure 21: Compilation, linking, and loading       47         Figure 22: MBSwD process breakdown as V-model       47         Figure 22: SRATS categorization and refinement       52         Figure 22: SRATS categorization and refinement       52         Figure 23: Test cases and test procedures (DO-178C 11.13)       62         Figure 24: Duplication of low-level testing (DO-178C 6.4)       63         Figure 25: Nodeling framework overview       79         Figure 26: PIL setup for software integration and low-level testing using Trace32 (from [97])       68         Figure 27: DO-178C glossary defin                                                                                                                                 |                                                                                               |       |

| Figure 9: System breakdown       27         Figure 10: Integration of system, hardware, and software processes.       29         Figure 11: FCC hardware       30         Figure 12: FCC chardware modules       30         Figure 13: FCC processor communication (from [37])       31         Figure 14: Software components on PowerPC based on considerations from [50] and [52]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 17: Compilation, linking, and loading       37         Figure 18: Architectural breakdown of software       46         Figure 20: MBSwD process breakdown as V-model       47         Figure 21: Traditional integral code generation approach       49         Figure 22: SRATS categorization and refinement       52         Figure 23: Test cases and test procedures (DO-178C 6.4)       63         Figure 24: Duplication of low-level testing (DO-178C 6.4)       63         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 27: DO-178C glossary definition of data and Control Coupling (DO-178C p.110f)       71         Figure 31: Module architecture example       88         Figure 32: Modeling framework overview       79         Figure 33: DD1 processing in software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 9: System breakdown       27         Figure 10: Integration of system, hardware, and software processes.       29         Figure 11: FCC hardware modules       30         Figure 12: FCC hardware modules       30         Figure 13: FCC processor communication (from [37])       31         Figure 13: FCC sequence of tasks from [37]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 18: Architectural breakdown of software       46         Figure 19: MBSwD process breakdown as V-model       47         Figure 21: Traditional integral code generation approach       49         Figure 22: SRATS categorization and refinement       52         Figure 22: UNBSwD process breakdown as flow diagram with three exemplary sub-processes       48         Figure 22: SNATS categorization and refinement       52         Figure 22: Duplication of low-level testing (DO-178C 1A)       66         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 26: Pll setup for software integration and low-level testing using Trace32 (from [97])       68         Figure 27: DO-178C Glossary definition of data and Control Coupling (DO-178C p.110f)       71         Figure 30: DO-178C Glossary definition of data and Control Coupling (DO-178C p.110f)                                                                                                      | Figure 7: Development and verification traceability according to DO-178C                      | 23    |

| Figure 10: Integration of system, hardware, and software processes       29         Figure 11: FCC hardware       30         Figure 12: FCC hardware modules       30         Figure 12: FCC processor communication (from [37])       31         Figure 14: Software components on PowerPC based on considerations from [50] and [52]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 17: Compilation, linking, and loading.       37         Figure 18: Architectural breakdown of software       46         Figure 20: MBSwD process breakdown as V-model.       47         Figure 21: Traditional integral code generation approach       49         Figure 22: SRATS categorization and refinement       52         Figure 23: Test cases and test procedures (DO-178C f.1.13)       62         Figure 24: Duplication of low-level testing (DO-178C f.4)       63         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 31: Module architecture example       79         Figure 32: Modeling framework overview       79         Figure 31: Module architecture example       83         Figure 32: Module interfaces       92         Figure 32: Module interfaces       92         Figure 32: Mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Figure 10:       Integration of system, hardware, and software processes       29         Figure 11:       FCC hardware       30         Figure 12:       FCC hardware modules       30         Figure 13:       FCC processor communication (from [37])       31         Figure 14:       Software components on PowerPC based on considerations from [50] and [52]       32         Figure 15:       FCC sequence of tasks from [37]       32         Figure 16:       Interface control and generation process       33         Figure 13:       Architectural breakdown of software       46         Figure 21:       Araditional integral code generation approach       47         Figure 22:       MBSwD process breakdown as V-model.       47         Figure 23:       Test cases and test procedures (DO-178C f1.13)       62         Figure 23:       Test cases and test procedures (DO-178C f1.13)       62         Figure 24:       Duplication of low-level testing (DO-178C fA)       63         Figure 25:       Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 26:       FIL setup for software integration and low-level testing using Trace32 (from [97])       68         Figure 28:       Types of test cases relevant for testing strategy (qualitative)       74         Figure 31: <t< td=""><td>Figure 8: Model simulation usage possibilities according to DO-331 MB.6.8</td><td> 24</td></t<>                                                                        | Figure 8: Model simulation usage possibilities according to DO-331 MB.6.8                     | 24    |

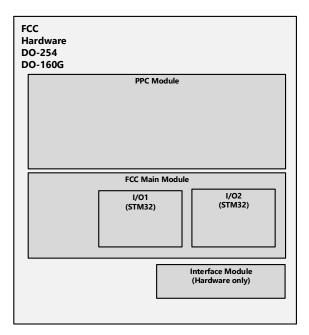

| Figure 11: FCC hardware       30         Figure 12: FCC hardware modules       30         Figure 13: FCC processor communication (from [37])       31         Figure 13: FCC sequence of tasks from [37]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 17: Compilation, linking, and loading.       37         Figure 18: Architectural breakdown of software       46         Figure 20: MBSwD process breakdown as V-model.       47         Figure 21: Traditional integral code generation approach       49         Figure 22: SRATS categorization and refinement       52         Figure 23: Test cases and test procedures (DO-178C 11.13)       66         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 27: DO-178C glossary definition of data and Control Coupling (DO-178C p.110f)       71         Figure 23: Modeling framework overview       79         Figure 31: Module architecture example       88         Figure 32: Modeling framework overview       79         Figure 32: Module interfaces       92         Figure 32: Module interfaces       92         Figure 32: Module architecture example       88         Figure 33: PDI processing in software       96 </td <td>Figure 11: FCC hardware modules       30         Figure 12: FCC hardware modules       30         Figure 13: FCC processor communication (from [37])       31         Figure 14: Software components on PowerPC based on considerations from [50] and [52]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 17: Compilation, linking, and loading.       37         Figure 20: MBSwD process breakdown as V-model       47         Figure 20: MBSwD process breakdown as V-model       47         Figure 21: Traditional integral code generation approach       49         Figure 22: SRATS categorization and refinement       52         Figure 23: Test cases and test procedures (Do-178C 1A.13)       62         Figure 23: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 25: Do-178C glossary definition of data and Control Coupling (DO-178C p.110f)       71         Figure 32: Modeling framework overview       79         Figure 32: Module inchreacture example       83         Figure 32: Module interfaces       92         Figure 33: PDI processing in software       96         Figure 33: DO-178C glossary - Derived requirements</td> <td>• ,</td> <td></td>                                                                                                                                           | Figure 11: FCC hardware modules       30         Figure 12: FCC hardware modules       30         Figure 13: FCC processor communication (from [37])       31         Figure 14: Software components on PowerPC based on considerations from [50] and [52]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 17: Compilation, linking, and loading.       37         Figure 20: MBSwD process breakdown as V-model       47         Figure 20: MBSwD process breakdown as V-model       47         Figure 21: Traditional integral code generation approach       49         Figure 22: SRATS categorization and refinement       52         Figure 23: Test cases and test procedures (Do-178C 1A.13)       62         Figure 23: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 25: Do-178C glossary definition of data and Control Coupling (DO-178C p.110f)       71         Figure 32: Modeling framework overview       79         Figure 32: Module inchreacture example       83         Figure 32: Module interfaces       92         Figure 33: PDI processing in software       96         Figure 33: DO-178C glossary - Derived requirements                                                                                                                                         | • ,                                                                                           |       |

| Figure 12: FCC hardware modules       30         Figure 13: FCC processor communication (from [37])       31         Figure 14: Software components on PowerPC based on considerations from [50] and [52]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 17: Compilation, linking, and loading       37         Figure 18: Architectural breakdown of software       46         Figure 19: MBSwD process breakdown as V-model       47         Figure 20: MBSwD process breakdown as flow diagram with three exemplary sub-processes       48         Figure 21: Traditional integral code generation approach       49         Figure 23: SRATS categorization and refinement       52         Figure 23: Test cases and test procedures (DO-178C 11.13)       62         Figure 24: Duplication of low-level testing (DO-178C 6.4)       63         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 26: PIL setup for software integration and low-level testing using Trace32 (from [97])       68         Figure 29: Modeling framework overview       79         Figure 31: Module architecture example       83         Figure 32: Module interfaces       92         Figure 33: PDI processing in software       96         Figure 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 12: FCC hardware modules       30         Figure 13: FCC processor communication (from [37])       31         Figure 14: Software components on PowerPC based on considerations from [50] and [52]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 16: Interface control and generation process       33         Figure 18: Architectural breakdown of software       46         Figure 19: MBSwD process breakdown as V-model       47         Figure 21: Traditional integral code generation approach       49         Figure 22: SRATS categorization and refinement       52         Figure 23: Test cases and test procedures (DO-178C 11.13)       62         Figure 24: Duplication of low-level testing (DO-178C 6.4)       63         Figure 25: PLI setup for software integration and low-level testing using Trace32 (from [97])       68         Figure 27: DO-178C glossary definition of data and Control Coupling (DO-178C p.110f)       71         Figure 31: Module architecture example       83         Figure 32: Module interfaces       92         Figure 32: Module interfaces       92         Figure 32: Module interfaces       92         Figure 32: Module architecture example       83         Figure 33: PDI processing in software       97                                                                                                                                          | Figure 10: Integration of system, hardware, and software processes                            | 29    |

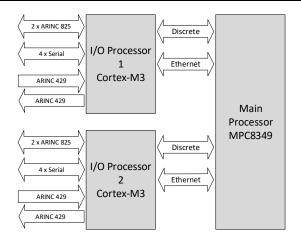

| Figure 13: FCC processor communication (from [37])       31         Figure 14: Software components on PowerPC based on considerations from [50] and [52]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 15: CCD sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 17: Compilation, linking, and loading.       37         Figure 19: MBSwD process breakdown of software       46         Figure 20: MBSwD process breakdown as V-model.       47         Figure 21: Traditional integral code generation approach       49         Figure 22: MBSwD process breakdown as flow diagram with three exemplary sub-processes       48         Figure 23: Test cases and test procedures (DO-178C 11.13)       62         Figure 24: Duplication of low-level testing (DO-178C 6.4)       63         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 26: PIL setup for software integration and low-level testing using Trace32 (from [97])       68         Figure 28: Types of test cases relevant for testing strategy (qualitative)       74         Figure 29: Modeling framework overview       79         Figure 31: Module architecture example       83         Figure 32: Module interfaces       92         Figure 33: DO processing in software       96 <td>Figure 13: FCC processor communication (from [37])       31         Figure 14: Software components on PowerPC based on considerations from [50] and [52]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 15: CC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 17: Compilation, linking, and loading.       37         Figure 18: Architectural breakdown of software       46         Figure 20: MBSwD process breakdown as V-model.       47         Figure 21: Traditional integral code generation approach       49         Figure 22: SRATS categorization and refinement.       52         Figure 23: Test cases and test procedures (DO-178C 11.13)       62         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 26: PIL setup for software integration and low-level testing using Trace32 (from [97])       68         Figure 27: DO-178C Glossary definition of data and Control Coupling (DO-178C p.110f)       71         Figure 31: Module architecture example       83         Figure 32: Modeling framework overview       79         Figure 33: PDI processing in software.       96         Figure 34: PDI view based on DO-248C Figure 4-4</td> <td>•</td> <td></td>                                                   | Figure 13: FCC processor communication (from [37])       31         Figure 14: Software components on PowerPC based on considerations from [50] and [52]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 15: CC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 17: Compilation, linking, and loading.       37         Figure 18: Architectural breakdown of software       46         Figure 20: MBSwD process breakdown as V-model.       47         Figure 21: Traditional integral code generation approach       49         Figure 22: SRATS categorization and refinement.       52         Figure 23: Test cases and test procedures (DO-178C 11.13)       62         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 26: PIL setup for software integration and low-level testing using Trace32 (from [97])       68         Figure 27: DO-178C Glossary definition of data and Control Coupling (DO-178C p.110f)       71         Figure 31: Module architecture example       83         Figure 32: Modeling framework overview       79         Figure 33: PDI processing in software.       96         Figure 34: PDI view based on DO-248C Figure 4-4                                                                                                              | •                                                                                             |       |

| Figure 14: Software components on PowerPC based on considerations from [50] and [52]       32         Figure 15: FCC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 17: Compilation, linking, and loading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Figure 14: Software components on PowerPC based on considerations from [50] and [52]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                               |       |

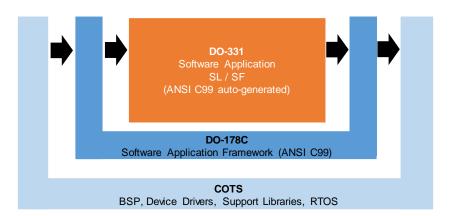

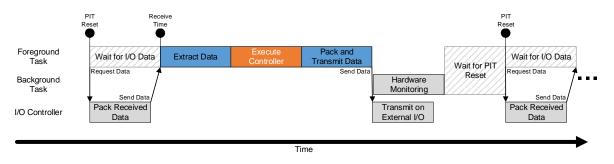

| Figure 15: FCC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 17: Compilation, linking, and loading.       37         Figure 18: Architectural breakdown of software       46         Figure 19: MBSwD process breakdown as V-model       47         Figure 21: MBSwD process breakdown as flow diagram with three exemplary sub-processes       48         Figure 22: SRATS categorization and refinement.       52         Figure 23: Test cases and test procedures (DO-178C 14.13)       62         Figure 24: Duplication of low-level testing (DO-178C 6.4)       63         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43)       66         Figure 26: PIL setup for software integration and low-level testing using Trace32 (from [97])       68         Figure 27: DO-178C glossary definition of data and Control Coupling (DO-178C p.110f)       71         Figure 28: Types of test cases relevant for testing strategy (qualitative)       74         Figure 31: Modeling framework overview       79         Figure 32: Modeling framework overview       79         Figure 32: Module interfaces       92         Figure 33: PDI processing in software.       96         Figure 34: DI view based on DO-248C Figure 4-4       97         Figure 35: Covered and noncovered design (qualitative)       108 <td>Figure 15: FCC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 17: Compilation, linking, and loading.       37         Figure 18: Architectural breakdown of software       46         Figure 21: MBSwD process breakdown as How diagram with three exemplary sub-processes       48         Figure 22: MBSwD process breakdown as flow diagram with three exemplary sub-processes       48         Figure 22: SRATS categorization and refinement.       52         Figure 23: Test cases and test procedures (DO-178C 11.13).       62         Figure 24: Duplication of low-level testing (DO-178C 6.4)       63         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43).       66         Figure 26: PIL setup for software integration and low-level testing using Trace32 (from [97]).       68         Figure 29: Modeling framework overview.       79         Figure 30: DO-178C Glossary - Derived requirements.       83         Figure 31: Module architecture example       88         Figure 32: Module interfaces       92         Figure 33: PDI processing in software.       96         Figure 34: DU view based on DO-248C Figure 4-4       97         Figure 35: Covered and noncovered design (qualitative).       106         Figure 36: DO-331 MB.B.18.9 - Partial Use of Libraries.       108</td> <td>Figure 13: FCC processor communication (from [37])</td> <td> 31</td> | Figure 15: FCC sequence of tasks from [37]       32         Figure 16: Interface control and generation process       33         Figure 17: Compilation, linking, and loading.       37         Figure 18: Architectural breakdown of software       46         Figure 21: MBSwD process breakdown as How diagram with three exemplary sub-processes       48         Figure 22: MBSwD process breakdown as flow diagram with three exemplary sub-processes       48         Figure 22: SRATS categorization and refinement.       52         Figure 23: Test cases and test procedures (DO-178C 11.13).       62         Figure 24: Duplication of low-level testing (DO-178C 6.4)       63         Figure 25: Purpose of structural coverage (according to DO-248C FAQ#43).       66         Figure 26: PIL setup for software integration and low-level testing using Trace32 (from [97]).       68         Figure 29: Modeling framework overview.       79         Figure 30: DO-178C Glossary - Derived requirements.       83         Figure 31: Module architecture example       88         Figure 32: Module interfaces       92         Figure 33: PDI processing in software.       96         Figure 34: DU view based on DO-248C Figure 4-4       97         Figure 35: Covered and noncovered design (qualitative).       106         Figure 36: DO-331 MB.B.18.9 - Partial Use of Libraries.       108                                                                                                                 | Figure 13: FCC processor communication (from [37])                                            | 31    |