## **TECHNISCHE UNIVERSITÄT MÜNCHEN**

Fakultät für Maschinenwesen

Professur für Sichere Eingebettete Systeme

## Advances in Model-Based Testing of Programmable Controllers: Automatic Test Generation using Design-to-Test and Plant Features

Canlong Ma, M.Sc.

Vollständiger Abdruck der von der Fakultät für Maschinenwesen der Technische Universität München zur Erlangung des akademischen Grades eines

#### Doktor-Ingenieurs (Dr.-Ing.)

genehmigten Dissertation.

Vorsitzender: Prof. Dr.-Ing. Boris Lohmann

Prüfer der Dissertation:

- 1. Prof. Dr. Julien Provost

- 2. Prof. Dr.-Ing. Georg Frey

Die Dissertation wurde am 06.12.2018 bei der Technische Universität München eingereicht und durch die Fakultät für Maschinenwesen am 05.07.2019 angenommen.

## Anhang I

## Eidesstattliche Erklärung

Ich erkläre an Eides statt, dass ich bei der **Fakultät für Maschinenwesen** der TUM zur Promotionsprüfung vorgelegte Arbeit mit dem Titel: **Advances in Model-Based Testing of Programmable Controllers: Automatic Test Generation using Design-to-Test and Plant Features**, in **Professur für Sichere Eingebettete Systeme** unter der Anleitung und Betreuung durch **Prof. Dr. Julien Provost** ohne sonstige Hilfe erstellt und bei der Abfassung nur die gemäß § 6 Ab. 6 und 7 Satz 2 angebotenen Hilfsmittel benutzt habe.

- □ Ich habe keine Organisation eingeschaltet, die gegen Entgelt Betreuerinnen und Betreuer für die Anfertigung von Dissertationen sucht, oder die mir obliegenden Pflichten hinsichtlich der Prüfungsleistungen für mich ganz oder teilweise erledigt.

- □ Ich habe die Dissertation in dieser oder ähnlicher Form in keinem anderen Prüfungsverfahren als Prüfungsleistung vorgelegt.

- □ Die vollständige Dissertation wurde in **mediaTUM** veröffenlicht. Die **Fakultät für Maschinenwesen** hat der Veröffentlichung zugestimmt.

- Ich habe den angestrebten Doktorgrad noch nicht erworben und bin nicht in einem früheren

Promotionsverfahren für den angestrebten Doktorgrad endgültig gescheitert.

- □ Ich habe bereits am \_\_\_\_\_\_ bei der Fakultät für \_\_\_\_\_

\_\_\_\_\_ der Hochschule \_\_\_

unter Vorlage einer Dissertation mit dem Thema

die Zulassung zur Promotion beantragt mit dem Ergebnis:

Die öffentlich zugängliche Promotionsordnung der TUM ist mir bekannt, insbesondere habe ich die Bedeutung von § 28 (Nichtigkeit der Promotion) und § 29 (Entzug des Doktorgrades) zur Kenntnis genommen. Ich bin mir der Konsequenzen einer falschen Eidesstattlichen Erklärung bewusst.

Mit der Aufnahme meiner personenbezogenen Daten in die Alumni-Datei bei der TUM bin ich

□ einverstanden

$\Box$  nicht einverstanden

# Acknowledgment

I would like to express my acknowledgments to many people throughout the whole research journey during my PhD.

First, I would like to thank my supervisor, Prof. Dr. Julien Provost, a great mentor not only for my research but also for my personal development. He always took the time to discuss with me, answer my questions, and give me advices. During these years, I have learned a lot from him, not only the knowledge and technologies, but also the passion, enthusiasm, and patience for research and work.

I would also like to thank my second reviewer, Prof. Dr.-Ing. Georg Frey, for giving me great feedback and suggestions, as well as to thank Prof. Dr.-Ing. Boris Lohmann for serving as my committee chair.

I thank my dear SES colleagues Claudius Jordan, Laurin Prenzel, and Nancy Elhady, for supporting me and providing me with great suggestions for any issue I ever had, in work and life. I wish you great success in your research and life. During my PhD, I also thank my friends Minjie Zou, Wei Zhu, Jiejia Hu, and all my other friends for always encouraging me and giving me valuable advices whenever I needed.

I want to deliver special thanks to my parents, sister and family for understanding, supporting and encouraging me in my whole life, even though we lived physically far away most of the time during my PhD. Finally, most thanks to Congying, my wife, you are the light of my life.

Canlong Ma November 28th, 2018, Munich

## Abstract

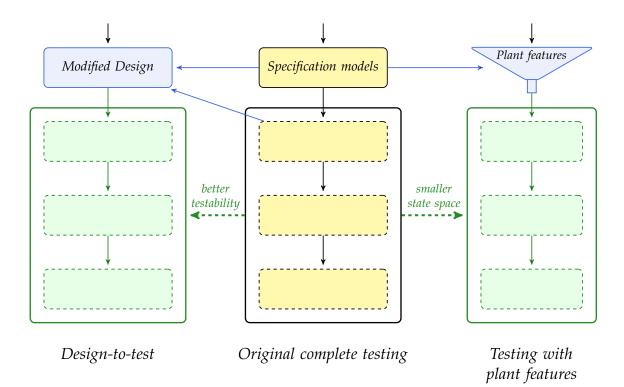

In this thesis, two novel approaches aiming at increasing the effectiveness and efficiency during the model-based testing of programmable controllers in automation systems are presented: **design-to-test (DTT)** and **plant features (PFs)**.

These two approaches deal with black-box conformance testing, where the specifications and implementations can be modeled as finite state machines (FSMs). Given an automation system, the testing objective is to validate whether the implemented controller conforms to expected input-output behavior with regard to their specification models. However, existing testing methods suffer from various issues and are therefore not well applicable for current industrial applications.

On the one hand, the DTT approach aims to improve the *effectiveness* of complete testing, which is indispensable for critical systems. The specification models are automatically checked and modified with limited design overhead in order to improve the testability of their physical implementation, namely its controllability, observability, and single-input-change testability. This approach also guarantees, by design, that the behavior of the implementation remains unchanged during its normal execution, i.e., when disconnected from a test bench.

On the other hand, the PF approach attempts to enhance the *efficiency* of testing for large scale systems where complete testing is hardly realistic. Plant features are manually modeled using simple templates (which also limits the modeling overhead), and then automatically fed into test generation. As a result, the input space of a system under test and the number of *meaningful* test cases can be significantly reduced, and consequently, the length of an executable test sequence can also be significantly shortened. It is worth mentioning that the obtained shortened test sequence guarantees full coverage of the whole *nominal* behavior of a system under test.

Based on case studies, these two approaches outperform the current methods and advance the model-based testing of programmable controllers.

## Zusammenfassung

In dieser Arbeit werden zwei innovative Ansätze vorgestellt, die die Effektivität und Effizienz modellbasierten Testens für programmierbare Steuergeräte in Automatisierungssystemen erhöhen sollen: Design-to-Test (DTT, dt. Entwurf-für-Testen) und Plant Features (PFs, dt. Anlageneigenschaften).

Die beiden Ansätze befassen sich mit Black-Box-Konformitätstests für programmierbare Steuergeräte, wobei die Spezifikationen und Implementierungen als endliche Automaten modelliert werden können. Bei einem Automatisierungssystem besteht das Testziel darin, zu validieren, ob das implementierte Steuergerät dem erwarteten Eingabe-Ausgabe-Verhalten hinsichtlich seiner Spezifikationsmodelle entspricht. Bestehende Testmethoden leiden jedoch unter verschiedenen Problemen und sind daher für derzeitige industrielle Anwendungen nicht gut anwendbar.

Zum einen zielt der DTT-Ansatz darauf ab, die *Effektivität* vollständiger Tests zu verbessern, die für kritische Systeme unverzichtbar sind. Die Spezifikationsmodelle werden automatisch mit begrenztem zusätzlichen Entwurfsaufwand überprüft und modifiziert, um die Testbarkeit der physikalischen Implementierung zu verbessern, d.h. die Steuerbarkeit, die Beobachtbarkeit und die s.g. single-input-change testability (dt. Testbarkeit mittels einzelner Eingangsgrößenwechsel). Dieser Ansatz garantiert, dass das Verhalten der Implementierung während ihrer normalen Ausführung unverändert bleibt, d.h. wenn sie nicht mit einem Prüfstand verbunden ist.

Zum anderen zielt der PF-Ansatz darauf ab, die *Effizienz* von Tests für große Systeme zu verbessern, bei denen vollständige Tests kaum realistisch sind. Anlageneigenschaften werden manuell mit einfachen Vorlagen modelliert (was auch den Modellierungsaufwand begrenzt) und dann automatisch in die Testgenerierung einbezogen. Dadurch können der Eingangsraum eines zu testenden Systems und damit die Anzahl

der *aussagekräftigen* Testfälle deutlich reduziert und die Länge einer ausführbaren Testsequenz auch deutlich verkürzt werden. Es ist wichtig zu erwähnen, dass die erhaltene verkürzte Testsequenz eine vollständige Abdeckung des gesamten *Nennverhaltens* eines getesteten Systems garantiert.

Auf der Grundlage von Fallstudien übertreffen diese beiden Ansätze die derzeitigen Methoden und fördern das modellbasierte Testen für programmierbare Steuergeräte.

## Contents

| Ał | ostrac  | t                                             | iii |

|----|---------|-----------------------------------------------|-----|

| Ζı | Isamr   | nenfassung                                    | v   |

| Li | st of l | Figures                                       | xi  |

| Li | st of [ | Tables x                                      | iii |

| Li | st of A | Acronyms                                      | κv  |

| 1  | Intro   | oduction                                      | 1   |

|    | 1.1     | Motivation                                    | 1   |

|    | 1.2     | Problem statement of testing                  | 3   |

|    | 1.3     | Contributions                                 | 5   |

|    | 1.4     | Outline                                       | 6   |

| 2  | Back    | kground knowledge                             | 9   |

|    | 2.1     | Programmable controller                       | 9   |

|    |         | 2.1.1 Programing languages                    | 9   |

|    |         | 2.1.2 Model-based development of applications | 10  |

|    |         | 2.1.3 Cyclic execution                        | 11  |

|    | 2.2     | Error, fault, failure                         | 12  |

|    | 2.3     | Verification & validation                     | 12  |

| 3  | State   | e of the art                                  | 15  |

|    | 3.1     | Introduction                                  | 15  |

|    | 3.2     | Informal methods                              | 15  |

|    | 3.3     | Formal verification                           | 16  |

|    |         | 3.3.1 Theorem proving                         | 16  |

| 3.3.4       Runtime verification         3.3.5       Brief discussions of formal verification techniques         3.4       Validation through testing         3.4.1       Spontaneous, manual testing vs. systematic, automatic testing         3.4.2       White-box, black-box, gray-box testing         3.4.3       Open-loop / closed-loop testing         3.5.1       X-in-the-loop testing         3.5.2       Conformance testing         3.6       Test-driven development         3.7       Concept of design-to-test         3.8       Plant models in verification and validation         4.1       Mathematical notation         4.1.1       Specification model         4.1.2       Plant feature model         4.2.1       Conformance testing of programmable controller         4.2.1       Conformance testing of programmable controller         4.2.2       Black-box conformance testing of programmable controller         4.2.2       Black-box testing of a programmable controller: a testing unit         4.2.3       Test generation of complete conformance testing         5.1       Introduction         5.2       Core idea         5.3.1       Black-box conformance testing on programmable controllers         5.3.2       SIC-Testability & T-guar                                                                   |   |      | 3.3.2    | Model checking                                                   | 17 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|----------|------------------------------------------------------------------|----|

| <ul> <li>3.3.5 Brief discussions of formal verification techniques</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |      | 3.3.3    | Static analysis                                                  | 18 |

| <ul> <li>3.4 Validation through testing</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      | 3.3.4    | Runtime verification                                             | 20 |

| <ul> <li>3.4.1 Spontaneous, manual testing vs. systematic, automatic testing</li> <li>3.4.2 White-box, black-box, gray-box testing</li> <li>3.4.3 Open-loop / closed-loop testing</li> <li>3.5 Model-based testing</li> <li>3.5.1 X-in-the-loop testing</li> <li>3.5.2 Conformance testing</li> <li>3.5.2 Conformance testing</li> <li>3.6 Test-driven development</li> <li>3.7 Concept of design-to-test</li> <li>3.8 Plant models in verification and validation</li> <li>4 Testing framework</li> <li>4.1 Mathematical notation</li> <li>4.1.1 Specification model</li> <li>4.1.2 Plant feature model</li> <li>4.2 Model-based black-box conformance testing of programmable controller</li> <li>4.2.1 Conformance testing of programmable controller: objective and process</li> <li>4.2.2 Black-box testing of a programmable controller: a testing unit</li> <li>4.2.3 Test generation of complete conformance testing</li> <li>5 Design-to-test approach</li> <li>5.1 Introduction</li> <li>5.2 Core idea</li> <li>5.3 Testing issues &amp; DTT methods</li> <li>5.3.1 Black-box conformance testing on programmable controllers</li> <li>5.3.2 SIC-Testability &amp; T-guard method</li> <li>5.3.4 Controllability &amp; C-guard method</li> <li>5.3.4 Controllability &amp; C-guard method</li> <li>5.3.4 Test cost through design</li> </ul> |   |      | 3.3.5    | Brief discussions of formal verification techniques              | 21 |

| <ul> <li>3.4.2 White-box, black-box, gray-box testing</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 3.4  | Valida   | tion through testing                                             | 22 |

| <ul> <li>3.4.3 Open-loop / closed-loop testing</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      | 3.4.1    | Spontaneous, manual testing vs. systematic, automatic testing .  | 22 |

| <ul> <li>3.5 Model-based testing</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |      | 3.4.2    | White-box, black-box, gray-box testing                           | 23 |

| <ul> <li>3.5.1 X-in-the-loop testing</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |      | 3.4.3    | Open-loop / closed-loop testing                                  | 24 |

| <ul> <li>3.5.2 Conformance testing</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 3.5  | Model    | l-based testing                                                  | 25 |

| <ul> <li>3.6 Test-driven development.</li> <li>3.7 Concept of design-to-test.</li> <li>3.8 Plant models in verification and validation</li> <li>4 Testing framework</li> <li>4.1 Mathematical notation .</li> <li>4.1.1 Specification model .</li> <li>4.1.2 Plant feature model .</li> <li>4.2 Model-based black-box conformance testing of programmable controlle</li> <li>4.2.1 Conformance testing of programmable controller: objective and process .</li> <li>4.2.2 Black-box testing of a programmable controller: a testing unit</li> <li>4.2.3 Test generation of complete conformance testing .</li> <li>5 Design-to-test approach</li> <li>5.1 Introduction .</li> <li>5.2 Core idea .</li> <li>5.3.1 Black-box conformance testing on programmable controllers .</li> <li>5.3.2 SIC-Testability &amp; T-guard method .</li> <li>5.3.3 Observability &amp; C-guard method .</li> <li>5.4.1 Test cost through design .</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                            |   |      | 3.5.1    | X-in-the-loop testing                                            | 26 |

| <ul> <li>3.7 Concept of design-to-test.</li> <li>3.8 Plant models in verification and validation</li> <li>4 Testing framework</li> <li>4.1 Mathematical notation</li> <li>4.1.1 Specification model</li> <li>4.1.2 Plant feature model</li> <li>4.2 Model-based black-box conformance testing of programmable controller</li> <li>4.2.1 Conformance testing of programmable controller: objective and process</li> <li>4.2.2 Black-box testing of a programmable controller: a testing unit</li> <li>4.2.3 Test generation of complete conformance testing</li> <li>5 Design-to-test approach</li> <li>5.1 Introduction</li> <li>5.3 Testing issues &amp; DTT methods</li> <li>5.3.1 Black-box conformance testing on programmable controllers</li> <li>5.3.2 SIC-Testability &amp; T-guard method</li> <li>5.3.4 Controllability &amp; C-guard method</li> <li>5.4.1 Test cost through design</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |      | 3.5.2    | Conformance testing                                              | 27 |

| <ul> <li>3.8 Plant models in verification and validation</li> <li>4 Testing framework</li> <li>4.1 Mathematical notation</li> <li>4.1.1 Specification model</li> <li>4.1.2 Plant feature model</li> <li>4.2 Model-based black-box conformance testing of programmable controller</li> <li>4.2.1 Conformance testing of programmable controller: objective and process</li> <li>4.2.2 Black-box testing of a programmable controller: a testing unit</li> <li>4.2.3 Test generation of complete conformance testing</li> <li>5 Design-to-test approach</li> <li>5.1 Introduction</li> <li>5.2 Core idea</li> <li>5.3.1 Black-box conformance testing on programmable controllers</li> <li>5.3.2 SIC-Testability &amp; T-guard method</li> <li>5.3.4 Controllability &amp; C-guard method</li> <li>5.4.1 Test cost through design</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 3.6  | Test-d   | riven development                                                | 29 |

| <ul> <li>4 Testing framework</li> <li>4.1 Mathematical notation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 3.7  | Conce    | pt of design-to-test                                             | 30 |

| <ul> <li>4.1 Mathematical notation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 3.8  | Plant    | models in verification and validation                            | 31 |

| <ul> <li>4.1.1 Specification model</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4 | Test | ing fra  | mework                                                           | 33 |

| <ul> <li>4.1.2 Plant feature model</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 4.1  | Mathe    | matical notation                                                 | 33 |

| <ul> <li>4.2 Model-based black-box conformance testing of programmable controller<br/>4.2.1 Conformance testing of programmable controller: objective and<br/>process</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |      | 4.1.1    | Specification model                                              | 33 |

| <ul> <li>4.2.1 Conformance testing of programmable controller: objective and process</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |      | 4.1.2    | Plant feature model                                              | 36 |

| process       4.2.2       Black-box testing of a programmable controller: a testing unit         4.2.3       Test generation of complete conformance testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 4.2  | Model    | -based black-box conformance testing of programmable controllers | 37 |

| <ul> <li>4.2.2 Black-box testing of a programmable controller: a testing unit</li> <li>4.2.3 Test generation of complete conformance testing</li> <li>5 Design-to-test approach</li> <li>5.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      | 4.2.1    | Conformance testing of programmable controller: objective and    |    |

| <ul> <li>4.2.3 Test generation of complete conformance testing</li> <li>5 Design-to-test approach</li> <li>5.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |      |          | process                                                          | 37 |

| <ul> <li>5 Design-to-test approach</li> <li>5.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |      | 4.2.2    | Black-box testing of a programmable controller: a testing unit . | 39 |

| <ul> <li>5.1 Introduction</li> <li>5.2 Core idea</li> <li>5.3 Testing issues &amp; DTT methods</li> <li>5.3.1 Black-box conformance testing on programmable controllers</li> <li>5.3.2 SIC-Testability &amp; T-guard method</li> <li>5.3.3 Observability &amp; O-action method</li> <li>5.3.4 Controllability &amp; C-guard method</li> <li>5.4 Design, testing &amp; normal execution</li> <li>5.4.1 Test cost through design</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |      | 4.2.3    | Test generation of complete conformance testing                  | 41 |

| <ul> <li>5.2 Core idea</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5 | Des  | ign-to-t | test approach                                                    | 43 |

| <ul> <li>5.3 Testing issues &amp; DTT methods</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 5.1  | Introd   | uction                                                           | 43 |

| <ul> <li>5.3.1 Black-box conformance testing on programmable controllers</li> <li>5.3.2 SIC-Testability &amp; T-guard method</li> <li>5.3.3 Observability &amp; O-action method</li> <li>5.3.4 Controllability &amp; C-guard method</li> <li>5.4 Design, testing &amp; normal execution</li> <li>5.4.1 Test cost through design</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 5.2  | Core i   | dea                                                              | 43 |

| <ul> <li>5.3.2 SIC-Testability &amp; T-guard method</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | 5.3  | Testing  | g issues & DTT methods                                           | 45 |

| <ul> <li>5.3.3 Observability &amp; O-action method</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |      | 5.3.1    | Black-box conformance testing on programmable controllers        | 45 |

| <ul> <li>5.3.4 Controllability &amp; C-guard method</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |      | 5.3.2    | SIC-Testability & T-guard method                                 | 46 |

| 5.4 Design, testing & normal execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |      | 5.3.3    | Observability & O-action method                                  | 51 |

| 5.4.1 Test cost through design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |      | 5.3.4    | Controllability & C-guard method                                 | 53 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 5.4  | Desig    | n, testing & normal execution                                    | 58 |

| 5.4.2 Influence of added guards and actions on state-space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |      | 5.4.1    | Test cost through design                                         | 58 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |      | 5.4.2    | Influence of added guards and actions on state-space             | 59 |

|   |      | 5.4.3                                   | Settings of added guards and actions in testing          | 59  |

|---|------|-----------------------------------------|----------------------------------------------------------|-----|

|   |      | 5.4.4                                   | Settings of added guards and actions in normal execution | 60  |

|   | 5.5  | DTT-N                                   | MAT: MATLAB Toolbox for the DTT approach                 | 60  |

|   |      | 5.5.1                                   | Workflow of DTT-MAT                                      | 60  |

|   |      | 5.5.2                                   | Limitations for applicable Stateflow models              | 62  |

|   | 5.6  | Case S                                  | Studies                                                  | 62  |

|   |      | 5.6.1                                   | A cooling water system                                   | 62  |

|   |      | 5.6.2                                   | A manufacturing cell                                     | 68  |

|   | 5.7  | Summ                                    | nary of the DTT approach                                 | 73  |

| 6 | Test | ing wi                                  | th plant features                                        | 75  |

|   | 6.1  | Introd                                  | luction                                                  | 75  |

|   | 6.2  | Core i                                  | dea                                                      | 75  |

|   | 6.3  | Descri                                  | iption of signal relations                               | 76  |

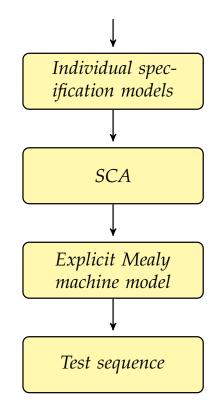

|   | 6.4  | Frame                                   | ework of test generation with plant features             | 78  |

|   | 6.5  | Test ca                                 | ase generation with utilization of plant models          | 80  |

|   |      | 6.5.1                                   | Level 1: Signal relations among sensors                  | 81  |

|   |      | 6.5.2                                   | Level 2: Signal relations among sensors and actuators    | 83  |

|   |      | 6.5.3                                   | Test case generation with fault injection                | 85  |

|   |      | 6.5.4                                   | Applying plant features in the generation of SCA         | 85  |

|   | 6.6  | Case s                                  | studies                                                  | 87  |

|   |      | 6.6.1                                   | A logistics system                                       | 87  |

|   |      | 6.6.2                                   | A flexible manufacturing system                          | 93  |

|   | 6.7  | Summ                                    | nary of the PF approach                                  | 99  |

| 7 | Con  | clusior                                 | 1 and outlook                                            | 101 |

|   | 7.1  | Concl                                   | usion                                                    | 101 |

|   | 7.2  | Limita                                  | ations and outlook                                       | 103 |

|   |      | 7.2.1                                   | Extension of signals in models                           | 103 |

|   |      | 7.2.2                                   | Extension of plant features                              | 104 |

|   |      | 7.2.3                                   | Reuse of plant features in diagnosis                     | 104 |

|   |      | 7.2.4                                   | Modular approach                                         | 105 |

|   |      | 7.2.5                                   | Extended application on hybrid systems                   | 106 |

| 8 | List | of pub                                  | lications                                                | 107 |

|   | 8.1  | Peer-r                                  | eviewed journal publications                             | 107 |

|   | 8.2  | 2 Peer-reviewed conference publications |                                                          |     |

8.3 Other peer-reviewed publications (not directly relevant to this thesis) . 108

### Bibliography

109

# **List of Figures**

| 1  | V-model in the system development: design, verification, validation and     |    |  |

|----|-----------------------------------------------------------------------------|----|--|

|    | diagnosis                                                                   | 2  |  |

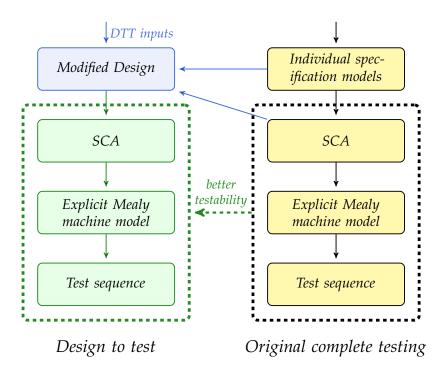

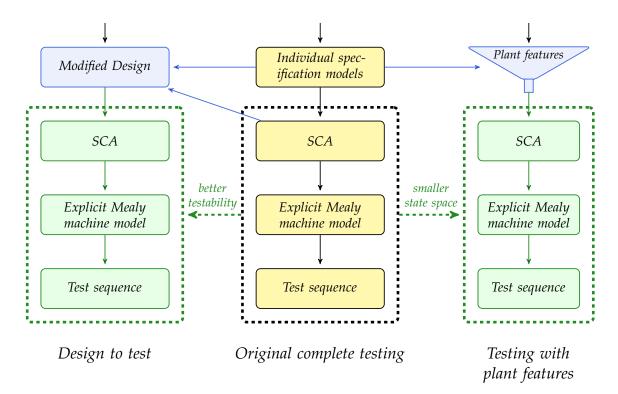

| 2  | Simplified frameworks of complete testing, design-to-test, and test gen-    |    |  |

|    | eration with plant features                                                 | 5  |  |

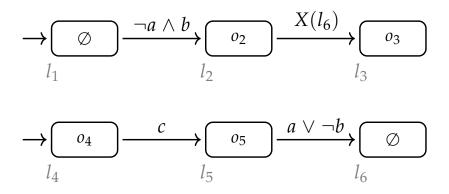

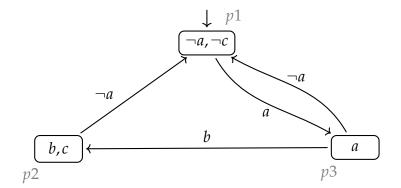

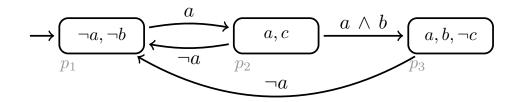

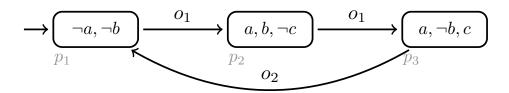

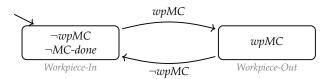

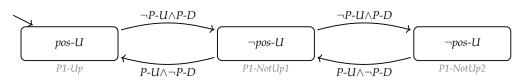

| 3  | A simple Moore machine model example with Boolean signals                   | 35 |  |

| 4  | A simple Moore machine plant model with Boolean signals                     | 37 |  |

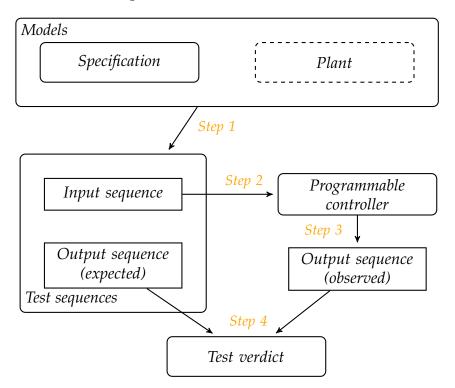

| 5  | Workflow of testing a programmable controller                               | 38 |  |

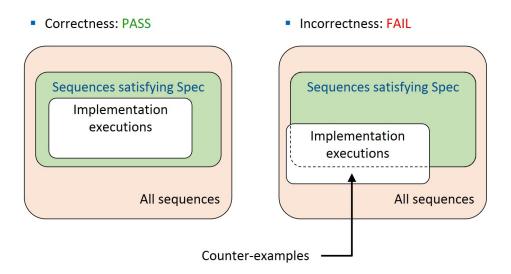

| 6  | Test verdict of an implementation against its specifications                | 39 |  |

| 7  | A simple specification example                                              | 41 |  |

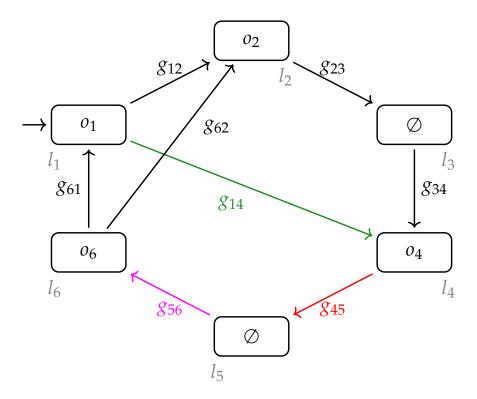

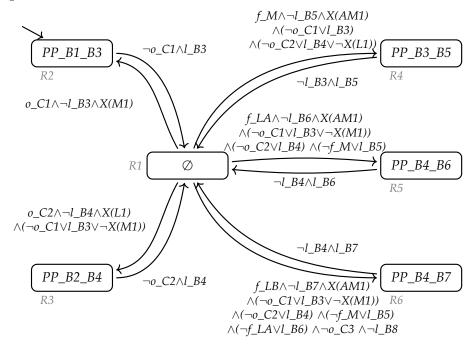

| 8  | Process of complete conformance testing                                     | 42 |  |

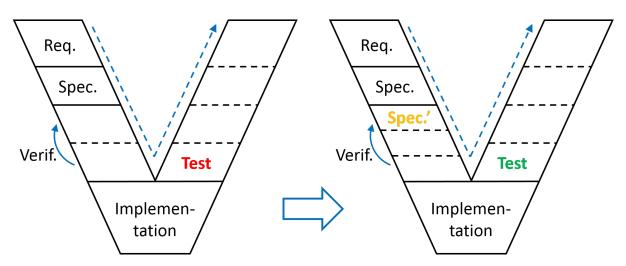

| 9  | V-models of the system engineering process: classic and with the DTT        |    |  |

|    | approach                                                                    | 44 |  |

| 10 | Process of complete conformance testing modified with the design-to-        |    |  |

|    | test (DTT) approach                                                         | 46 |  |

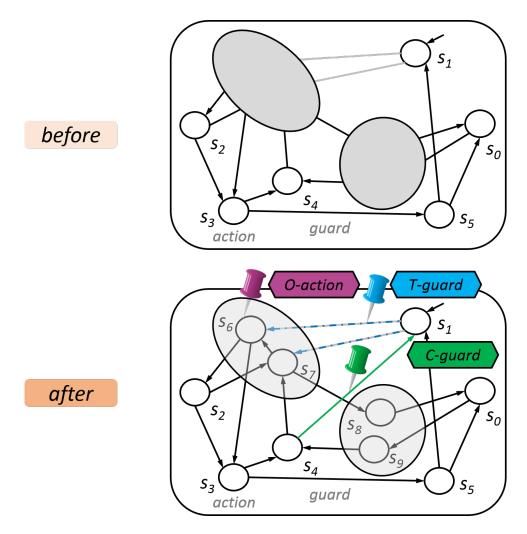

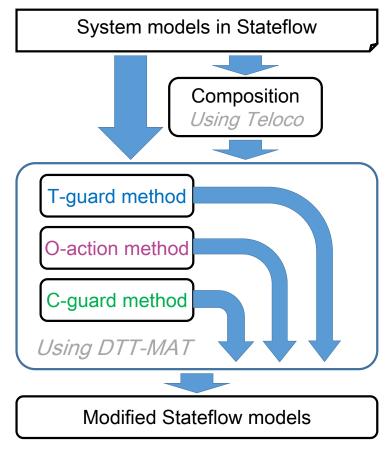

| 11 | Basic idea of the DTT approach: adding T-guards, O-actions and C-           |    |  |

|    | guards to modify the initial specification model, so that the model will    |    |  |

|    | fulfill the SIC-testability, observability and controllability requirements | 47 |  |

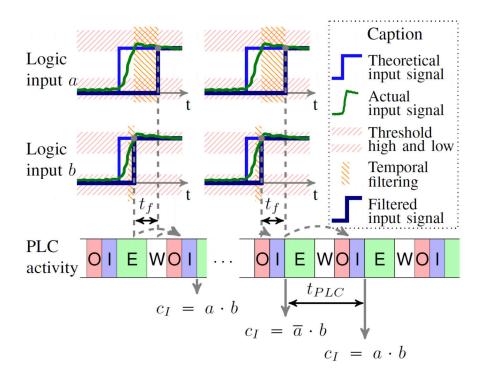

| 12 | Physical causes of single-input-change (SIC)-testability issue in pro-      |    |  |

|    | grammable controllers                                                       | 48 |  |

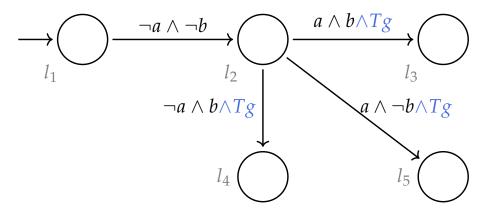

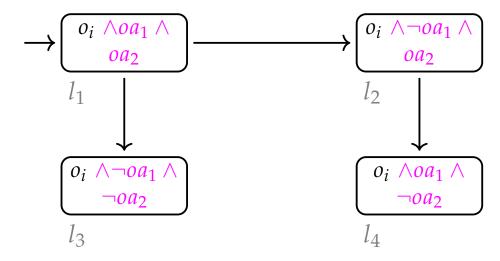

| 13 | A simple Moore machine model updated with T-guards                          | 49 |  |

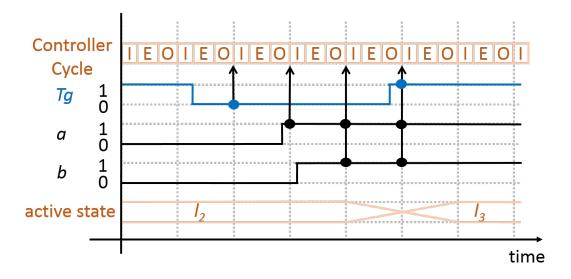

| 14 | Status changes of signals and locations after adding T-guards               | 49 |  |

| 15 | A simple Moore machine example updated with O-actions                       | 52 |  |

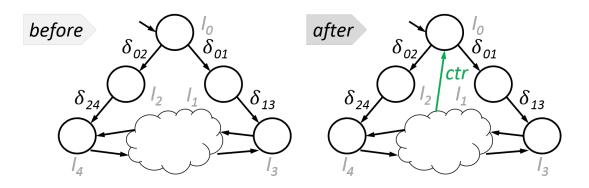

| 16 | C-guard in testing transitions between unreachable locations                | 54 |  |

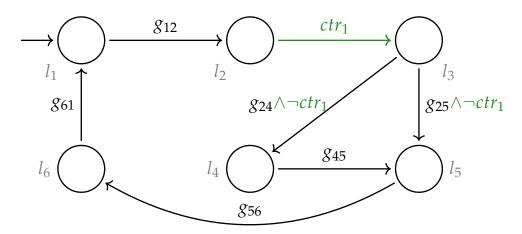

| 17 | A simple Moore machine example updated with C-guards                        | 54 |  |

| 18 | Workflow of DTT-MAT                                                         | 61 |  |

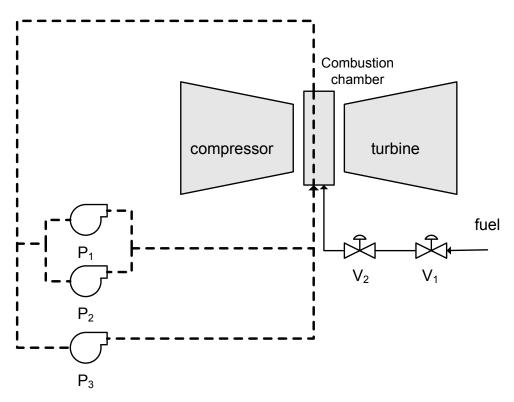

| 19 | Case study: a cooling-water system                                          | 63 |  |

|    |                                                                             |    |  |

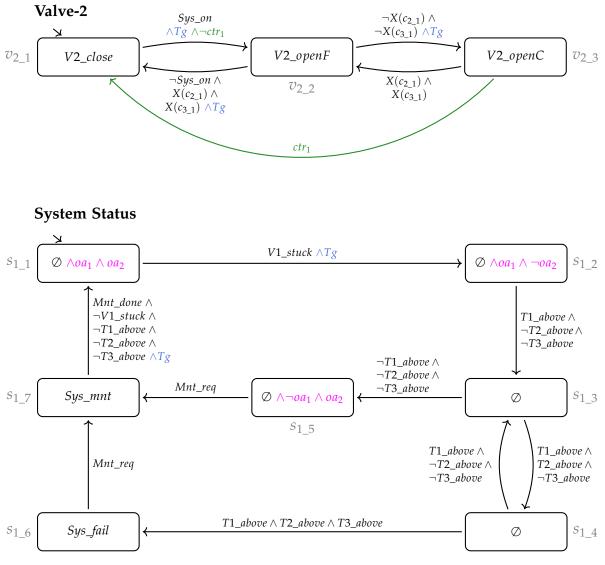

| 20 | Specification model of $V_2$ and <i>System Status</i>                          | 65  |  |

|----|--------------------------------------------------------------------------------|-----|--|

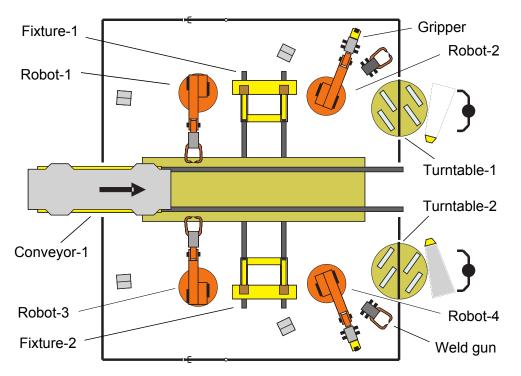

| 21 | Case study: a welding and material handling cell                               | 69  |  |

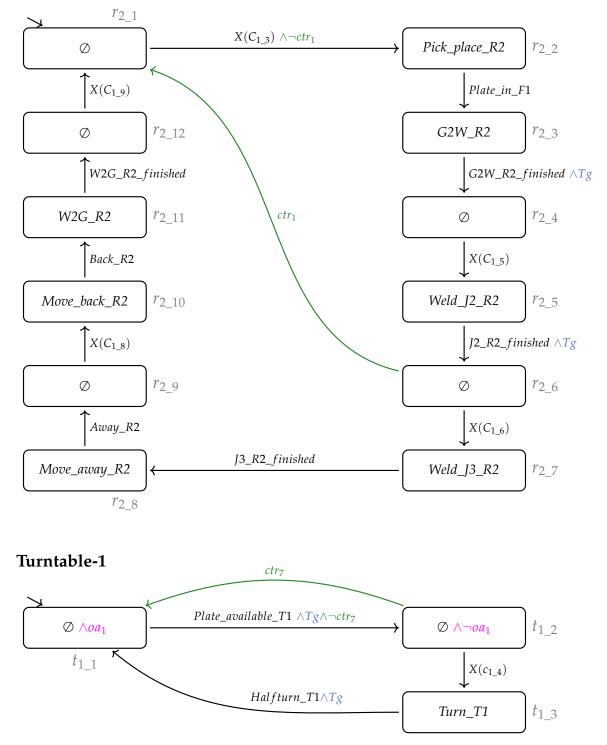

| 22 | A Moore machine model for Robot-2 and Turntable-1                              |     |  |

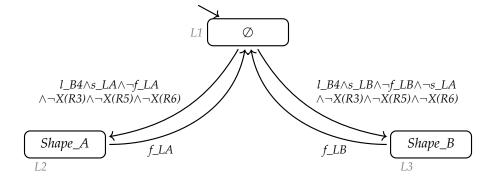

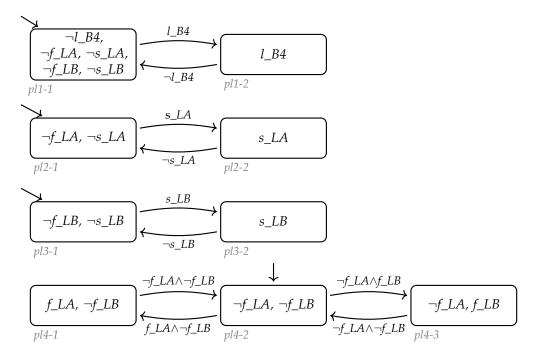

| 23 | Two basic types of signal relations                                            | 76  |  |

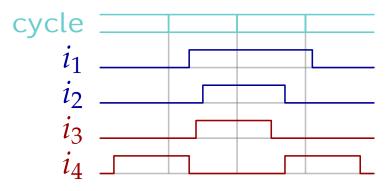

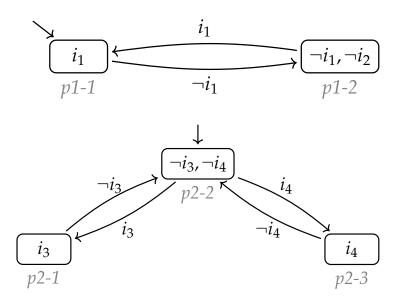

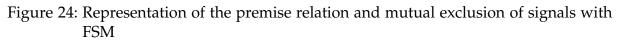

| 24 | Representation of the premise relation and mutual exclusion of signals         |     |  |

|    | with FSM                                                                       | 77  |  |

| 25 | A simple example of multiple signal relations                                  | 78  |  |

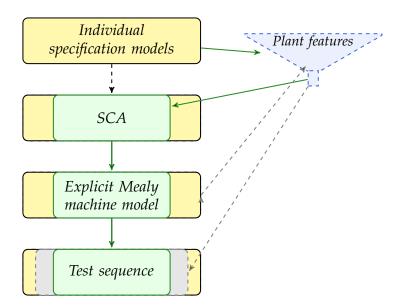

| 26 | Framework of involving plant features in the test generation.                  |     |  |

|    | low blocks: generation of complete testing; Gray block and arrows:             |     |  |

|    | earlier version of test generation with plant features ([1], [2]); Green       |     |  |

|    | blocks and arrows: current version of test generation with plant features.     | 79  |  |

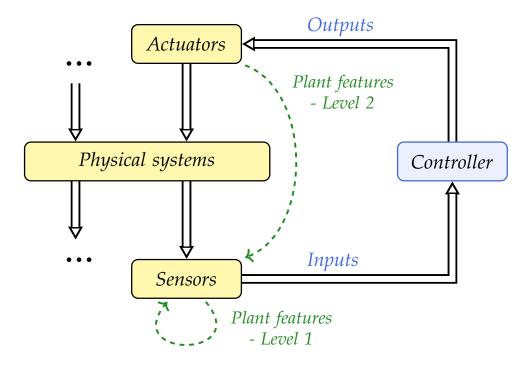

| 27 | Specification and plant in an automation system                                | 81  |  |

| 28 | Example: plant model of level 1                                                | 81  |  |

| 29 | Example: plant model of level 2                                                | 83  |  |

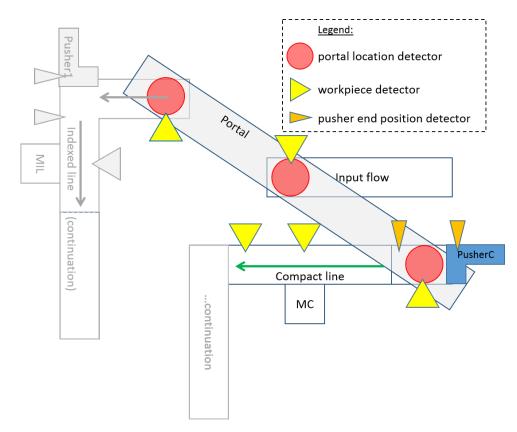

| 30 | Case study: a logistics system containing a portal and two subsequent          |     |  |

|    | lines (top view)                                                               | 87  |  |

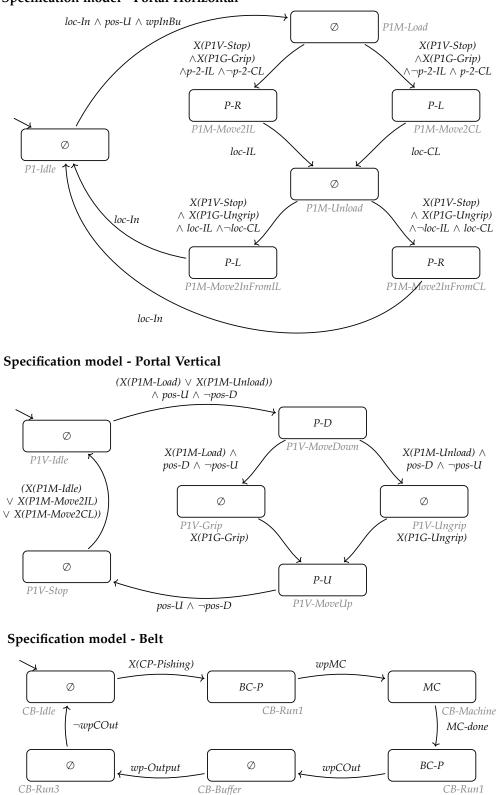

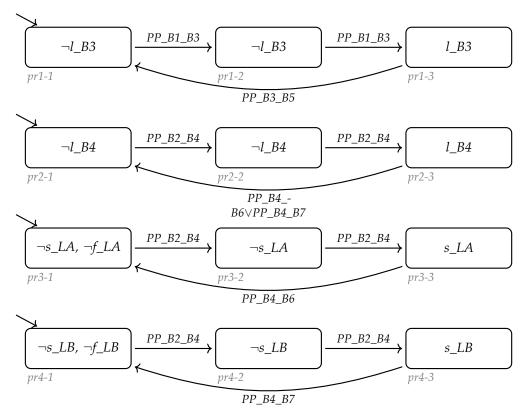

| 31 | Specification models for the horizontal portal movement, the vertical          |     |  |

|    | portal movement and the belt of the compact line                               | 90  |  |

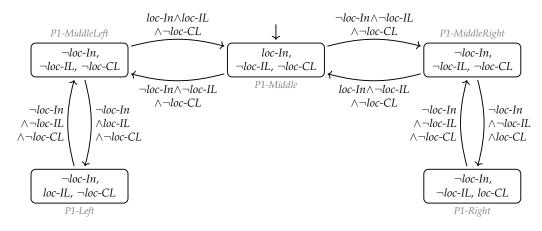

| 32 | Plant models for the nominal behavior of the vertical and horizontal           |     |  |

|    | portal movement and the machine on the compact line                            | 91  |  |

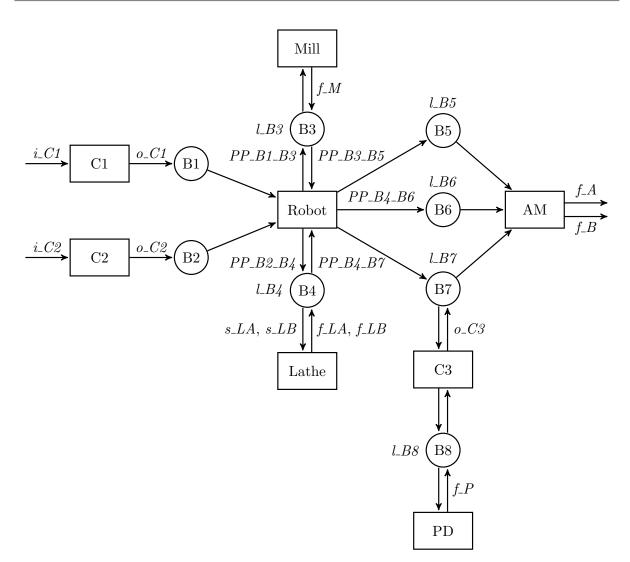

| 33 | Case study: a flexible manufacturing system                                    | 95  |  |

| 34 | Specification models for two subsystems: <i>Lathe-Buffer4</i> and <i>Robot</i> | 96  |  |

| 35 | Plant models for two subsystems: <i>Lathe-Buffer4</i> and <i>Robot</i>         | 98  |  |

| 36 | Frameworks of complete testing, design-to-test, and test generation with       |     |  |

|    | plant features                                                                 | 101 |  |

# List of Tables

| 1 | Verification and validation                                               | 13 |

|---|---------------------------------------------------------------------------|----|

| 2 | Path cost matrix for the system in Fig. 17                                | 55 |

| 3 | Inputs & outputs of the cooling-water system                              | 64 |

| 4 | Inputs & outputs for the models <i>Robot-2</i> and <i>Turntable-1</i>     | 71 |

| 5 | Table of inputs & outputs for the portal, belt and machine on the compact |    |

|   | line                                                                      | 89 |

| 6 | Results and comparison of test generation methods on the case study of    |    |

|   | compact line                                                              | 93 |

| 7 | Inputs & outputs of the flexible manufacturing system                     | 94 |

| 8 | Results and comparison of test generation methods on the case study of    |    |

|   | flexible manufacturing system                                             | 99 |

# List of Acronyms

| BIST    | built-in-self-test                                |

|---------|---------------------------------------------------|

| ССТ     | complete conformance testing                      |

| CTL     | computational tree logic                          |

| DFT     | design-for-test                                   |

| DTT     | design-to-test                                    |

| DTT-MAT | design-to-test MATLAB tool box                    |

| FBD     | function block diagram                            |

| FSM     | finite state machine                              |

| HIL     | hardware-in-the-loop                              |

| IC      | integrated circuit                                |

| IEC     | International Electrotechnical Commission         |

| IEEE    | Institute of Electrical and Electronics Engineers |

| IL      | instruction list                                  |

| IM      | intermediate model                                |

| IUT     | implementation under test                         |

| LD      | ladder diagram                                    |

| T 777   |                                                   |

LTL linear temporal logic

- MBT model-based testing

- MIC multiple-input-change

- MIL software-in-the-loop

- PF plant feature

- PIL processor-in-the-loop

- PLC programmable logical controller

- SCA stabilized composed automaton

- SFC sequential function chart

- SIC single-input-change

- SIL model-in-the-loop

- ST structured text

- SUT system under test

- SysML systems modeling language

- UML unified modeling language

- VLSI very-large-scale integration

## 1 Introduction

### 1.1 Motivation

Nowadays, automation engineering is facing challenges in designing and testing. It involves knowledge and technology from multiple fields such as mechanical and electrical engineering as well as computer science. Besides, automation systems are often composed of multiple subsystems that are distributed and interact with each other.

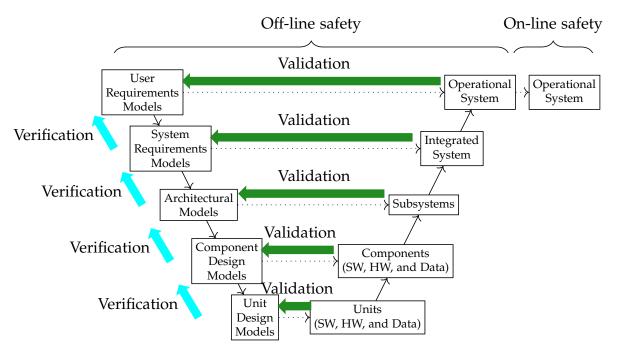

Fig. 1 presents the classic V-model of system development. The left wing of the 'V' represents the design phase. The first step is to collect requirements from users, which are usually informal, e.g., descriptions in the form of natural language. Then, engineers consolidate all the requirements and create formal specification models. During the design phase, the models are refined and detailed step by step, from the most abstract system level (on the top) throughout subsystem, architecture, component levels until the most detailed unit level (on the bottom).

Meanwhile, each time models are created or detailed, they are always checked against the models/requirements one level higher. This procedure is called verification, including formal and informal techniques. Formal verification is a type of popular verification techniques aiming at proving the correctness and consistency of formal models with respect to certain formal specifications or properties. Recent research and development of formal verification techniques can be found in [3] [4] [5].

The right wing of the 'V' represents the integration of implemented parts, i.e., from unit level (on the bottom) back to system level (on the top). Each time after the integration for one level is done, the obtained implementations will be validated whether they

conform to the initial specifications/requirements.

Figure 1: V-model in the system development: design, verification, validation and diagnosis

Verification and validation are both important off-line safety measures to ensure the correctness of a product or process [6]. They are not the same thing, although they are often confused. Succinctly, the difference can be understood as follows [7]:

- Verification: "Are we building the product right?"

- Validation: "Are we building the right product?"

After the steps of the both wings have been finished, the system will be put into use and enters the so-called 'on-line mode' (the most right block in Fig. 1). In this phase, some other measures such as diagnosis, reconfiguration, maintenance and repair are used to ensure the on-line safety of a system [8].

## 1.2 Problem statement of testing

Testing, as "an activity in which a system or component is executed under specified conditions, the results are observed or recorded, and an evaluation is made of some aspect of the system or component" ([9], page 368), is considered as an important validation means.

Automation systems are comprised of hardware and software components, which interact with each other through various communication protocols, and often also interact with the physical environment with peripherals such as sensors and actuators.

On one hand, in many applications especially critical fields such as railway, power production and medical devices, the functionality of automation systems are becoming more and more complicated [10]. Verification techniques can verify the models, but they cannot guarantee the correctness of the final implemented system which is also strongly influenced by the hardware and environmental factors. For example, a single-input-change (SIC) issue that can lead to undetected behavioral difference between initial design and final implementation is resulted from hardware execution characteristics [11], which can not be discovered by verification techniques. To cope with these issues, testing is strongly recommended and even compulsorily required by many industrial standards such as IEC 61508 [12], IEC 61511 [13] and ISO 26262 [14] as a validation technique on top of verification methods.

On the other hand, in many fields such as manufacturing, the life cycles of industrial products/processes are also constantly shortening. As a consequence, the introduction of new processes and modification of existing designs are carried out more frequently, which causes frequent changes in system specifications [15]. This also requires efficient system engineering approaches including not only useful designing tools but also powerful testing techniques.

Referring to Fig. 1, usually, testing is not considered until the design and implementation steps are finished. Besides, research work has shown that in current practice, most testing activities are still conducted manually while design tasks have been supported by abundant tools to be done automatically [16] [17]. Manual testing methods are mostly straightforward, expert-based, and have been proven useful in practice decades-long [18], [19], etc. Nevertheless, their disadvantages are obvious: individually customized, time-consuming, and error-prone. The short-comings have become big obstacles which are hardly bearable for the testing demands of modern automation systems, especially for safety-critical and large scale systems.

Among all applications, safety-critical automation systems have in particular following characteristics: intensive interaction with sensors and actuators; strict requirements on real-time performance; and high demands on dependability and safety [20]. Therefore, safety-critical systems, or safety-critical parts of a system, need to be tested completely. To be specific, the testings should cover all possible behavior of a system/part under all situations it could have.

As for large scale systems (which are usually not completely critical), the largest testing challenge is to overcome the so-called 'state space explosion' issue. Briefly, when the number of inputs of a system grows linearly, the total state space in test generation grows exponentially, and the obtained test sequence grows also exponentially. Consequently, complete testing is neither convenient to generate nor realistic to execute for large scale systems.

In this thesis, the tested targets are programmable controllers, which play a key role in many automation systems such as manufacturing and power plant. Compared to general computers, programmable controllers are dedicated to a limited set of specific tasks. They receive a variety of input signals from sensors, internal buses and external networks, make decisions according to the implemented specifications from users, and send commands to actuators. Owing to user demands of complex functions, high individualization, and frequent modifications, the development and application of programmable controllers are also becoming highly complex. This fact raises challenges not only to design tasks but also to verification and validation methods [21].