### Dissertation

# Studies of Read-Out Electronics and Trigger for Muon Drift Tube Detectors at High Luminosities

von Sebastian Nowak

eingereicht an der

Fakultät für Physik

der

Technischen Universität München

erstellt am

Max-Planck-Institut für Physik

(Werner-Heisenberg-Institut)

München Juni 2015

# TECHNISCHE UNIVERSITÄT MÜNCHEN

Max-Planck-Institut für Physik (Werner-Heisenberg-Institut)

# Studies of Read-Out Electronics and Trigger for Muon Drift Tube Detectors at High Luminosities

#### Sebastian Nowak

Vollständiger Abdruck der von der Fakultät für Physik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr. A. Ibarra

Prüfer der Dissertation:

Priv.-Doz. Dr. H. Kroha

Univ.-Prof. Dr. L. Oberauer

Die Dissertation wurde am 22.06.2015 bei der Technischen Universität München eingereicht und durch die Fakultät für Physik am 24.06.2015 angenommen.

Wer immer strebend sich bemüht, den können wir erlösen.

(Faust. Der Tragödie zweiter Teil)

# **Abstract**

The Large Hadron Collider (LHC) at the European Centre for Particle Physics, CERN, collides protons with an unprecedentedly high centre-of-mass energy and luminosity. The collision products are recorded and analysed by four big experiments, one of which is the ATLAS detector. For precise measurements of the properties of the Higgs-Boson and searches for new phenomena beyond the Standard Model, the LHC luminosity of  $L = 10^{34} \rm cm^{-2} s^{-1}$  is planned to be increased by a factor of ten leading to the High Luminosity LHC (HL-LHC). In order to cope with the higher background and data rates, the LHC experiments need to be upgraded.

In this thesis, studies for the upgrade of the ATLAS Muon Spectrometer are presented with respect to the read-out electronics of the Monitored Drift Tube (MDT) and the small-diameter Muon Drift Tube (sMDT) chambers and the Level-1 muon trigger. Due to the reduced tube diameter of sMDT chambers, background occupancy and space charge effects are suppressed by an order of magnitude compared to the MDT chambers.

The rate capability of the sMDT chambers is limited by signal pile-up effects of the MDT read-out electronics using bipolar signal shaping. In order to profit from the full potential of sMDT chambers, prototype read-out electronics with improved signal shaping and baseline restoration has been developed. Measurement and simulation of the sMDT drift-tubes with the new read-out electronics show that the high-rate performance of the sMDT chambers is substantially increased.

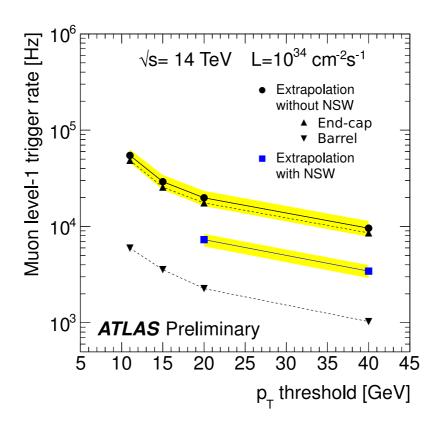

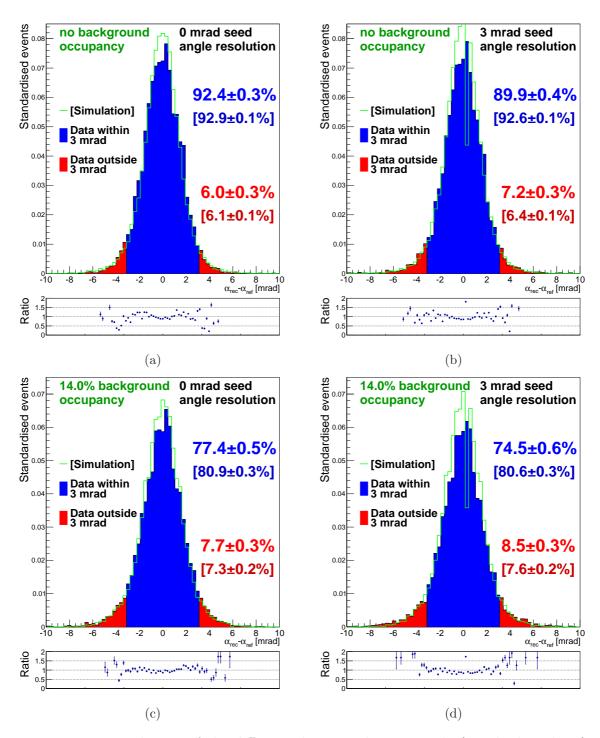

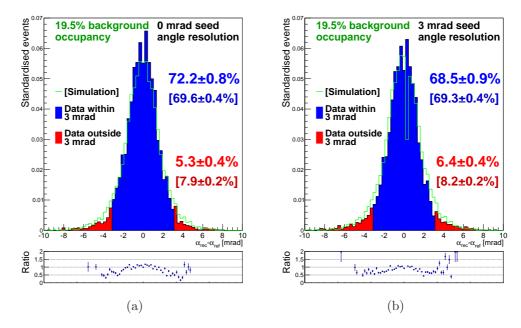

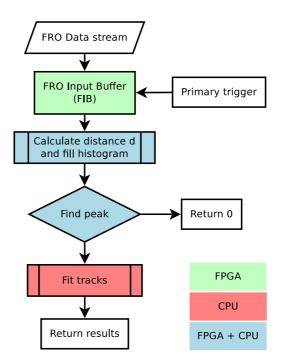

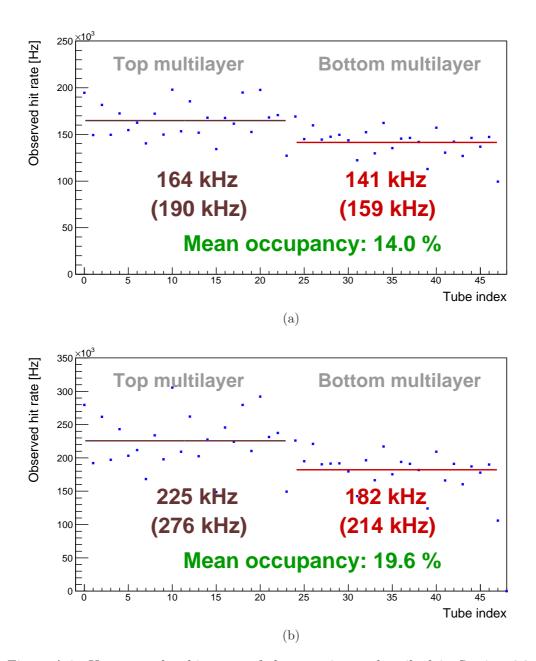

At HL-LHC, muon trigger rates are expected to be about 10 times higher than at the LHC design luminosity. In order to fully exploit the physics potential of the HL-LHC, the selectivity of the ATLAS Muon Trigger system has to be improved. This is achieved by using the MDT chambers of the ATLAS Muon Spectrometer in the muon trigger to obtain the optimum achievable muon momentum resolution in the trigger. Simulations and measurements with a demonstrator of the MDT based trigger at the CERN Gamma Irradiation Facility demonstrate the feasibility of this concept.

# Contents

| Αb | strac | ct care and a second care a second care | 5  |

|----|-------|-----------------------------------------------------------------------------------------------------------------|----|

| 1. | Mot   | ivation and Outline                                                                                             | 9  |

| 2. | The   | Large Hadron Collider                                                                                           | 11 |

| 3. | The   | ATLAS Muon Spectrometer                                                                                         | 13 |

|    | 3.1.  | The Muon Detectors                                                                                              | 13 |

|    | 3.2.  | 1 2                                                                                                             |    |

|    |       | 3.2.1. The Level-1 Trigger                                                                                      |    |

|    |       | 3.2.2. The High-Level Trigger                                                                                   | 15 |

|    | 3.3.  | <u>.</u>                                                                                                        | 16 |

|    | 3.4.  | 10                                                                                                              | 17 |

|    |       | 3.4.1. Upgrade of the Trigger and Data Acquisition System                                                       | 18 |

| 4. | Muo   | on Drift-Tube Chambers                                                                                          | 19 |

|    | 4.1.  | Monitored Drift Tube Chambers                                                                                   | 19 |

|    |       | 4.1.1. MDT Chamber Read-out Electronics                                                                         | 21 |

|    | 4.2.  | Small-Diameter Muon Drift Tube Chambers                                                                         | 23 |

|    |       | 4.2.1. Spatial Resolution and Muon Efficiency                                                                   | 24 |

|    | 4.3.  | 9                                                                                                               | 25 |

|    |       | 1 0                                                                                                             | 25 |

|    |       | 4.3.2. Read-Out Electronics Effects                                                                             | 26 |

| 5. | Opti  | imisation of Drift-Tube Read-Out Electronics for High Counting Rates                                            | 31 |

|    | 5.1.  | Signal Shaping                                                                                                  | 31 |

|    |       | 5.1.1. Unipolar and Bipolar Signal Shaping                                                                      | 31 |

|    |       | 5.1.2. Baseline Restoration                                                                                     | 32 |

|    | 5.2.  | The ASD Chip                                                                                                    | 33 |

|    | 5.3.  | A Discrete Pulse Shaper for sMDT Tubes (ASBC)                                                                   | 36 |

|    |       | 5.3.1. The ASBC Circuit                                                                                         | 37 |

|    |       | 1                                                                                                               | 43 |

|    |       | 1                                                                                                               | 44 |

|    |       | 5.3.4. Response Simulation                                                                                      |    |

|    |       |                                                                                                                 | 49 |

|    |       | 5.3.6 Noise Considerations                                                                                      | 50 |

#### Contents

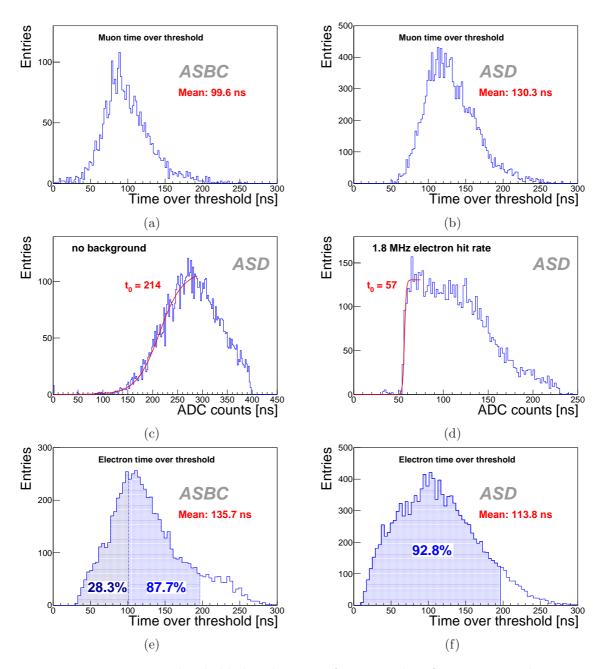

|     |       | 5.3.7. Muon, Electron and $\gamma$ Analog Response                    | . 54                |

|-----|-------|-----------------------------------------------------------------------|---------------------|

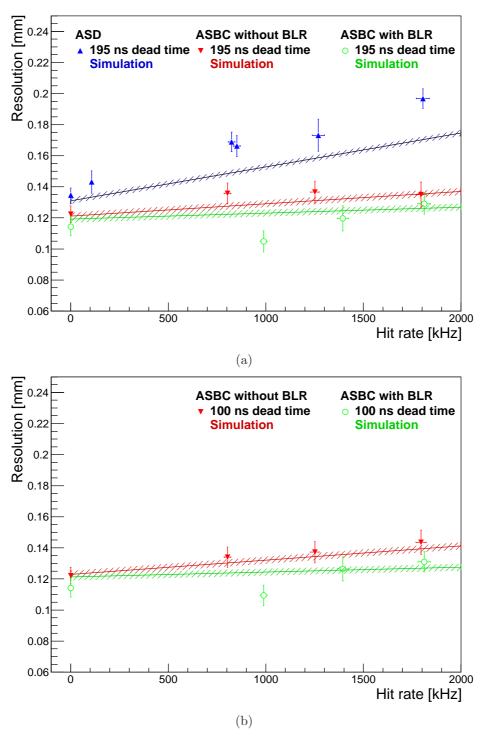

|     | 5.4.  | Performance of the ASBC Electronics at High Counting Rates            |                     |

|     |       | 5.4.1. Experimental Setup                                             |                     |

|     |       | 5.4.2. Data Analysis                                                  |                     |

|     |       | 5.4.3. Simulation of the Performance of the sMDT Read-Out Electronics |                     |

|     |       | 5.4.4. Results                                                        |                     |

|     |       | 5.4.5. Performance under Irradiation with <sup>137</sup> Cs           |                     |

|     |       | 5.4.6. Conclusion and Outlook                                         |                     |

| 6   | Drift | t-Tube Based First-Level Muon Trigger for ATLAS at HL-LHC             | 77                  |

| ٠.  | 6.1.  |                                                                       |                     |

|     | 6.2.  |                                                                       |                     |

|     | 6.3.  |                                                                       |                     |

|     | 0.0.  | 6.3.1. Initial Considerations                                         |                     |

|     |       | 6.3.2. Fast Track Reconstruction Algorithm                            |                     |

|     |       | 6.3.3. Monte-Carlo Simulation Studies                                 |                     |

|     |       | 6.3.4. Performance of the Fast Read-out with Experimental Data        |                     |

|     |       | 6.3.5. Timing Performance Estimation                                  |                     |

|     | 6.4.  | Further Considerations                                                |                     |

|     |       | 6.4.1. Bunch Crossing Identification                                  |                     |

|     |       | 6.4.2. Hough transform based pattern recognition                      |                     |

|     | 6.5.  | Conclusion and Outlook                                                |                     |

| Su  | mma   | ry                                                                    | 123                 |

| Α.  | App   | endix                                                                 | 125                 |

|     |       | Parametrisation of the Space-Drift-Time Relationship                  | _                   |

|     |       | Read-Out Electronics for Drift-Tubes                                  |                     |

|     |       | A.2.1. Unipolar and Bipolar Shaping Scheme                            |                     |

|     |       | A.2.2. The RC-Circuit                                                 |                     |

|     |       | A.2.3. Operational Amplifier Based Differentiator                     | . 128               |

|     |       | A.2.4. The ASBC                                                       | . 131               |

|     |       | A.2.5. Stage 1                                                        | . 135               |

|     |       | A.2.6. Stage 2                                                        | . 135               |

|     |       | A.2.7. Diode Model Determination (SPICE)                              | . 136               |

|     |       | A.2.8. Simulation                                                     |                     |

|     |       | Performance of the Trigger Demonstrator Set-up                        |                     |

|     |       |                                                                       |                     |

|     | A.4.  | ARM Cortex-M4F Implementation of the Track Finding Algorithm          | . 141               |

| Bil |       | aphy                                                                  | . 141<br><b>149</b> |

## 1. Motivation and Outline

The Organization shall provide for collaboration among European States in nuclear research of a pure scientific and fundamental character, and in research essentially related thereto. The Organization shall have no concern with work for military requirements and the results of its experimental and theoretical work shall be published or otherwise made generally available.

(CERN Convention, Article 2 [1])

Since the foundation of CERN<sup>1</sup> in 1953 many important discoveries in particle physics have been made. In 1983 the W- and Z-Bosons were discovered by the UA1 and UA2 experiments using proton-antiproton collisions in the Super-Proton Synchrotron (SPS) which started operation in 1976. Between 1989 and 2000 Large Electron-Positron Collider (LEP) was operated at CERN with four experiments which performed precision measurements of the electroweak interaction.

With the start of the Large Hadron Collider (LHC) a new era for particle physics has begun. The first highlight was the discovery of the Higgs-Boson in 2012 [2,3]. For precise measurements of the Higgs-Boson properties and searches for new phenomena beyond the Standard Model the centre-of-mass energy of the LHC will be raised to 13 TeV in 2015 and the luminosity will be increased in several steps over the next ten years (see Section 2). The luminosity increase necessities upgrades of LHC experiments.

In this thesis, studies for the upgrade of the ATLAS Muon Spectrometer are presented, in particular of the Level-1 muon trigger and of the read-out electronics of the Monitored Drift Tubes (MDT) chambers and small-diameter Muon Drift Tube (sMDT) chambers.

After a short introduction about the LHC, the ATLAS Experiment and the planned luminosity upgrades, the principles of the MDT and sMDT chambers are discussed in Chapter 4. In Chapter 5, improvements of their read-out electronics for operation at high luminosities are presented. Chapter 6 is devised to studies of using the MDT chambers in the ATLAS Level-1 muon trigger.

<sup>&</sup>lt;sup>1</sup>Conseil Européen pour la Recherche Nuclaire

#### 1. Motivation and Outline

# 2. The Large Hadron Collider

The Large Hadron Collider (LHC) [4], colliding protons in a circular storage ring of 27 km circumference since end of 2009, is the largest scientific instrument ever build. The accelerated protons of the LHC circle the ring in bunches with a design separation in time of 25 ns corresponding to a bunch crossing rate of 40 MHz. In addition to the proton beams, the LHC can also accelerate and collide heavy ion beams, in particular lead ions. The LHC is designed for a nominal instantaneous luminosity of  $L_0 = 10^{34} cm^{-2} s^{-1}$  of proton-proton collisions at a centre-of-mass energy of 14 TeV with 2808 bunches of protons [5].

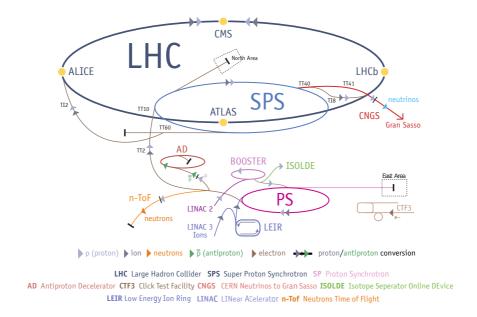

The LHC has been built in the already existing accelerator tunnel of the Large Electron Positron Collider (LEP) which has been shut down at the end of 2000. The already existing pre-accelerators are being reused, namely the LINAC2, the BOOSTER, the Proton Synchrotron (PS) and the Super Proton Synchrotron (SPS). An overview of the CERN accelerator complex is given in Fig. 2.1.

The LHC started at a center-of-mass energy of 900 GeV end of 2009 and 7 TeV in 2010. In 2012, the center-of-mass energy was raised to 8 TeV. A peak luminosity of about  $L=8\cdot 10^{33}cm^{-1}s^{-1}$  was also reached in 2012.

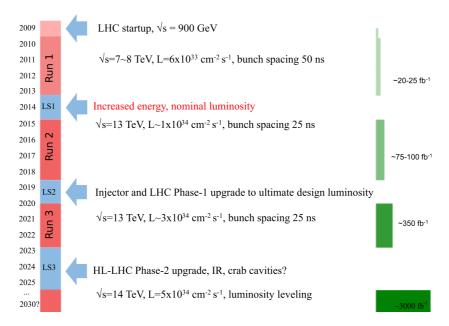

Without an additional LHC luminosity increase the running time necessary to half the statistical error in the measurements will be more than a decade. Therefore, the LHC luminosity has to be increased [7], the planned time-line (2014) is shown in Fig. 2.2. It is planned to upgrade the LHC in several steps. In Run 2 the LHC is going to be operated slightly below its design energy. During the one year LS 2 the Phase-1 upgrade is going to take place, leading afterwards to a luminosity increase of a factor of 3. Finally, between 2023 and 2025 the Phase-2 upgrade is going to lead to the so-called High-Luminosity LHC (HL-LHC). The main objective of the HL-LHC is to reach a peak luminosity of  $L = 5 \cdot 10^{34} cm^{-2} s^{-1}$  with levelling, leading to a integrated luminosity of  $250 fb^{-1}$  per year and to  $3000 fb^{-1}$  over 12 years [7].

Due to the luminosity increase after the upgrades, the LHC experiments have to be adapted to cope with the changed conditions. Therefore, LS1 and LS2 are also used to upgrade the experiments and conduct the necessary maintenance.

The implications of the Phase-2 upgrade for the ATLAS Muon Spectrometer and the development of new detector components to operate under the changed conditions are discussed in the following.

#### 2. The Large Hadron Collider

Figure 2.1.: Overview of the CERN accelerator complex [6]. Starting with LINAC2 and the BOOSTER and after pre-acceleration in the PS and SPS, the protons are injected into the LHC ring.

Figure 2.2.: Planned time schedule of the LHC high luminosity upgrades [8]. Upgrades to Phase-1 and Phase-2 (HL-LHC) take place during the Long shutdowns LS2 amd LS3, respectively. The green boxes represent the accumulated integrated luminosity of the accelerator.

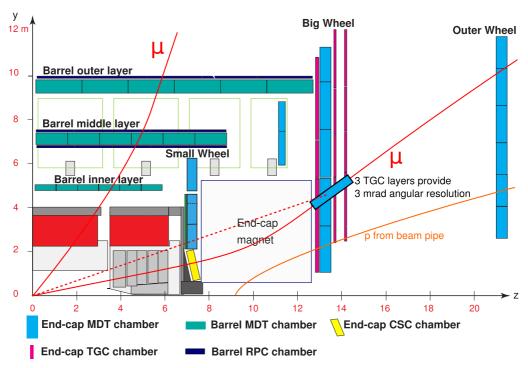

# 3. The ATLAS Muon Spectrometer

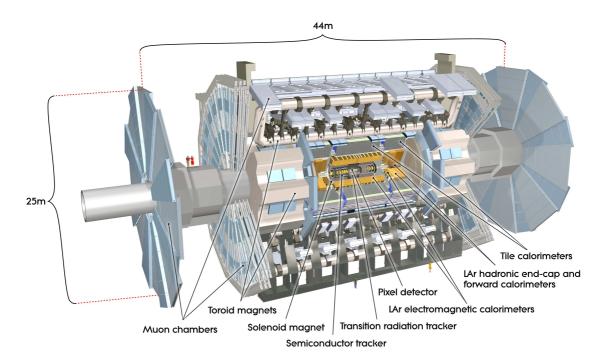

The goals of the ATLAS<sup>1</sup> experiment [9] (see Fig. 3.1) are to measure Standard Model processes indicating Higgs boson production and decays with high precision and to discover new physics beyond. With a length of 44 m, a diameter of 25 m and a weight of 7000 tons, the ATLAS detector is the largest experiment at the LHC. Its construction took place between May 2003 and end of 2008.

#### 3.1. The Muon Detectors

The Muon Spectrometer [10] is the outer-most and largest part of the ATLAS detector (see Fig. 3.1 and Fig. 3.3). It provides precise muon track and momentum reconstruction with a momentum resolution of

$$\frac{\Delta p_T}{p_T} < 10^{-4} \frac{p}{GeV} \tag{3.1}$$

for  $p_T > 300 \text{ GeV}$  and

$$\frac{\Delta p_T}{p_T} < 3\% \tag{3.2}$$

for  $p_T < 300 \text{ GeV}$  [10]. The resolution in the lower momentum range is limited by multiple scattering in the detector structures and by energy loss fluctuations in the calorimeters.

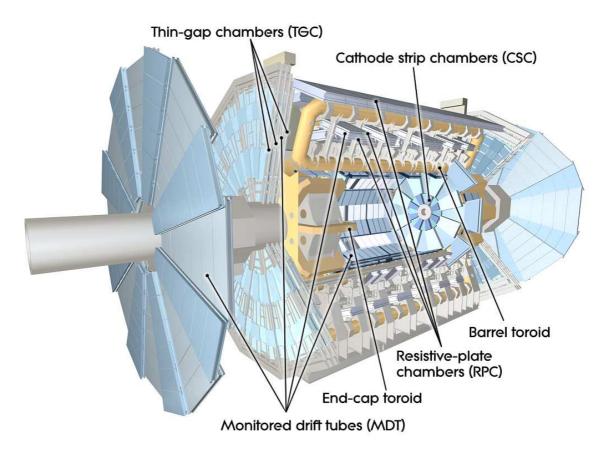

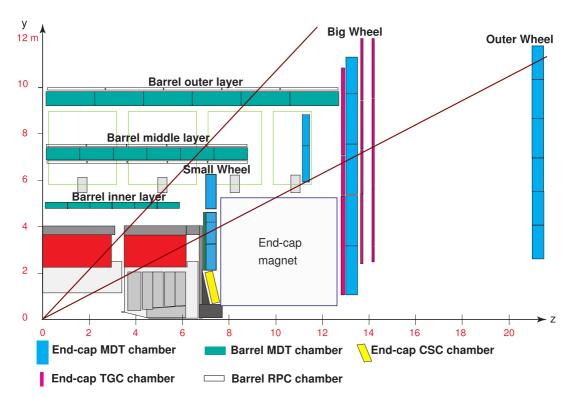

The Muon Spectrometer is split into the barrel and two end-cap regions (see Fig. 3.3), each with three layers of precision tracking detectors. The barrel consists of inner, middle and outer layers, each end-cap of a Small Wheel, Big Wheel and the Outer Wheel. With the exception of the very forward regions of the Small Wheels where cathode strip chambers (CSC) are used, the muon tracking detectors are Monitored Drift Tube (MDT) chambers (see Section 4).

To achieve the required muon momentum resolution in the toroidal magnetic field of the Muon Spectrometer, the track points in each layer have to be measured with an accuracy of better than 50  $\mu$ m. This sets the requirements on the intrinsic resolution and the mechanical precision of the MDT chambers [10] (see Section 4.1). In addition, the operating parameters, the relative alignment of the chambers and the magnetic field strength have to be monitored with high precision to be taken into account in muon track reconstruction.

<sup>&</sup>lt;sup>1</sup>ATLAS - A Toroidal LHC AparatuS

Figure 3.1.: Cut-away view of the ATLAS detector [9]. The inner tracking detector and the calorimeters for particle and jet energy measurements are surrounded by the Muon Spectrometer consisting of three layers of muon chambers in a toroidal magnetic field of superconducting air-core magnets.

Special, fast trigger chambers are used for the Level-1 muon trigger, Resistive Plate Chambers (RPC) in the middle and outer layers of the barrel and Thin Gap Chambers (TGC) in the end-caps. They also measure the track coordinates along the MDT drift-tubes with reduced resolution.

# 3.2. The Trigger and Data Acquisition System

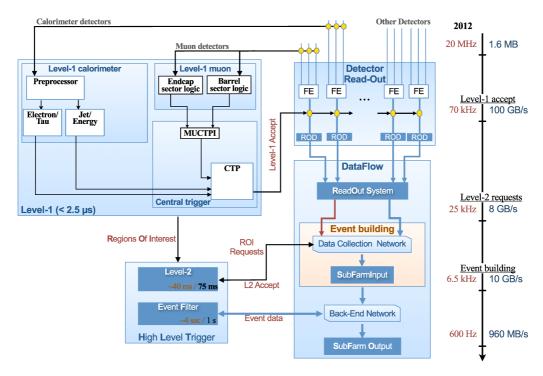

The ATLAS trigger system consists of three levels. A simplified overview of the trigger and DAQ system is given in Fig. 3.4.

#### 3.2.1. The Level-1 Trigger

The Level-1 (L1) trigger decision is based on reduced-granularity information from the calorimeter and muon trigger chambers (see Section 3.1). As shown in Fig. 3.4, the decisions of calorimeter and muon trigger are combined in the Central Trigger Processor. In addition, the L1 trigger provides Regions of Interest (RoI) which are passed on to the next trigger level. During the L1 trigger latency of 2.5  $\mu$ s, the information of all detector

Figure 3.2.: Cut-away view of the ATLAS Muon Spectrometer. RPCs and TGCs are used as trigger chambers, CSCs and MDTs are used for precision measurement [9].

read-out channels is kept in buffers of the front-end electronics (FE). The front-end system was originally designed for a maximal Level-1 trigger rate of 75 kHz. It has been upgraded to a maximal rate of 100 kHz in 2014 [11].

Finally, the event data selected by the Level-1 trigger is read-out from the FE buffers into the read-out buffers (ROBs) via the readout drivers (RODs). The Level-1 trigger decision is based on combinations of calorimeter and muon detector informations [12]. The trigger implementation is programmable to adjust to varying luminosities and background conditions.

#### 3.2.2. The High-Level Trigger

The High-Level Trigger consists of two parts: The Level-2 trigger and the Event Filter (EF).

The Level-2 trigger uses the RoI information provided by the Level-1 trigger which includes the position  $(\eta, \phi)$ , the transverse momentum  $(p_T)$  range and the energy sums of

#### 3. The ATLAS Muon Spectrometer

Figure 3.3.: Schematic view of one quadrant of the ATLAS muon spectrometer. The red lines indicate tracks of muons with infinite momentum. They typically traverse three detector layers allowing for a track sagitta measurement.

calorimeter cells belonging to candidate objects. While the RoI information is transmitted for all events selected by the Level-1 trigger over a dedicated data path, the data required in order to make the Level-2 trigger decision is accessed selectively. The Level-2 trigger has access to the complete event data with the full granularity, but typically needs only data from a small fraction of the detector.

The ROBs keep the complete data of the selected bunch crossing until the event is rejected or accepted by the Level-2 Trigger. The Event Filter (EF) applies the full offline reconstruction algorithms to the complete event data. Events selected by the EF are sent to mass storage while rejected trigger events are deleted.

## 3.3. Background Radiation in the Muon Spectrometer

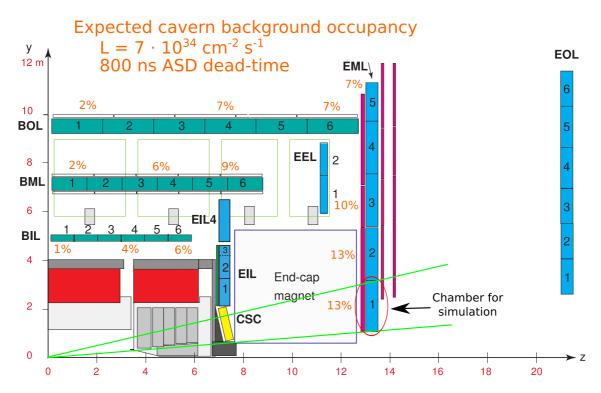

The ATLAS muon detectors are exposed to unprecedentedly high background radiation of photons and of neutrons with typical energies of 1 MeV which originate from interactions of the collision products in the detector and the shielding of the beams and is uncorrelated in time with the bunch-crossings and fills the whole detector cavern [13].

Figure 3.4.: Schematic overview of the trigger and DAQ system for collision data taking operations [12] (see text).

In the Muon Spectrometer the highest background rates occur in the innermost detector layers of the end-cap regions. The impact of the background radiation on the operation of the Monitored Drift Tube chambers is discussed in Section 4.3. This uncorrelated background radiation increases proportionally with the luminosity.

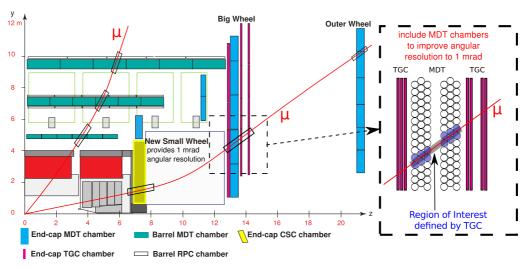

# 3.4. Upgrade of the ATLAS Detector at High Luminosity

Due to the the increased luminosity at the HL-LHC (see Section 2), the ATLAS detector has to be upgraded to cope with the increasing event rates and background radiation. The main limitations of the currently installed detectors are the lifetimes of the components, the increasing background, the increasing event and background rates and the radiation damage to detectors and electronic components.

Besides the inner tracking detector, which will be completely replaced for Phase-II because of radiation damage and increasing particle rates, the calorimeter and muon detector electronics as well as the trigger and data acquisition supplies have to be upgraded [14]. Developments for the MDT chamber read-out electronic and the new MDT-based Level-1 muon trigger are discussed in this thesis.

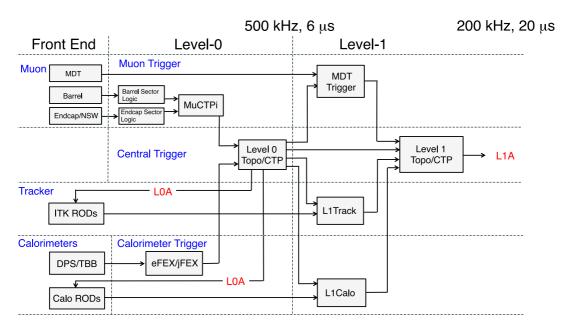

Figure 3.5.: Block diagram of the split Level-0/Level-1 trigger proposed for ATLAS Phase-II operation [14]. The MDT trigger may also be implemented already at Level-0.

#### 3.4.1. Upgrade of the Trigger and Data Acquisition System

In order to cope with HL-LHC luminosities, it is planned to upgrade the ATLAS trigger system for Phase-II operation with splitting of the current Level-1 trigger into Level-0 and Level-1 [14].

The following properties are envisaged [14]:

- The Level-0 trigger provides the functionality of the current Level-1 trigger with an output rate of 500 kHz after a latency of 6  $\mu$ s.

- The Level-1 trigger reduces the event rate to at least 200 kHz within an additional latency of at least 20  $\mu$ s<sup>2</sup>. The rate reduction is accomplished by new track trigger in the inner detector within a RoI provided by the Level-0 trigger.

- The High-Level trigger uses offline-reconstruction algorithms to reduce the final readout rate to 5-10 kHz.

A block diagram of the architecture of the ATLAS Level-0 and Level-1 trigger system for the Phase-2 operation is shown in Fig. 3.5. The Level-1 Calorimeter trigger will have access to the full calorimeter granularity. The Level-1 Muon trigger will use the MDT precision tracking chambers to sharpen the trigger threshold as a function of  $p_{\rm T}$  of the muons. The Level-1 Central Trigger Processor finally combines the results of the individual Level-1 trigger systems.

<sup>&</sup>lt;sup>2</sup>A latency of 60  $\mu$ s is in discussion (begin 2014).

# 4. Muon Drift-Tube Chambers

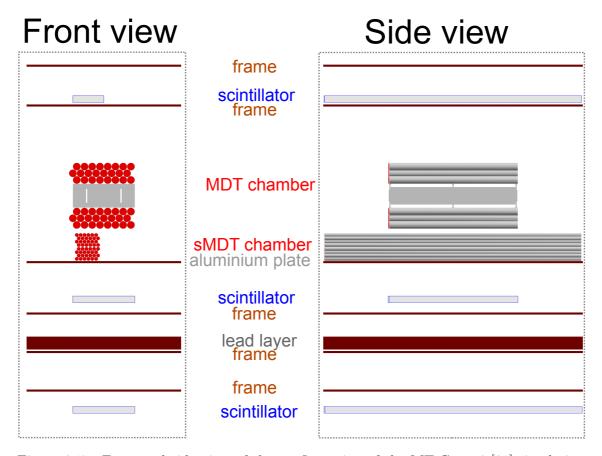

The majority of the precision tracking chambers in the ATLAS Muon Spectrometer are Monitored Drift Tube (MDT) chambers [10]. These kind of particle tracking detectors, which are high accuracy wire chambers and, therefore, commonly used in high-energy particle physics [15], provide high tracking efficiency and spatial resolution, but their performance suffers at high counting rates. Hence, drift-tube chambers with reduced tube diameter for the operation at high background rates have been developed. The first two of this small-diameter Muon Drift tube (sMDT) chambers have been installed in the ATLAS detector in 2014 [16]. More sMDT chambers are currently under construction for installation in 2017 and 2018/19 [17,18]. Functionality and performance of MDT and sMDT chambers are discussed in the following.

#### 4.1. Monitored Drift Tube Chambers

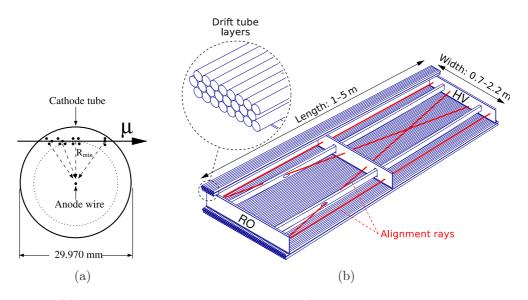

MDT chambers consists of aluminium drift-tubes assembled into two multi-layers with 3 or 4 layers each (see Fig. 4.1b). The tungsten-rhenium anode wire in the centre is set to a potential of 3080 V with respective to the tube wall. The main MDT parameters are listed in Tab. 4.1.

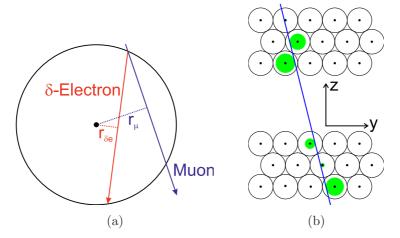

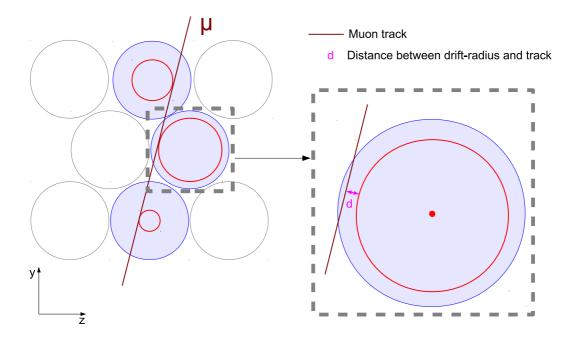

When a muon passes through an MDT tube, the Argon atoms are ionised along the path of the particle. A 100 GeV muon creates on average about 100 clusters separated typically by 100  $\mu$ m per cm of typically 3 electrons in it [19]. The ionisation electrons drift towards the wire in the electric field, the ions to the tube wall (see Fig. 4.1a). The electric field strength increases with  $\frac{1}{r}$  towards the wire. In the vicinity of the wire, the field is strong enough for the drifting ionisation electrons to gain enough energy to ionise the Ar gas atoms, leading to an avalanche of secondary electrons and amplification of the primary ionisation charge. For a potential of 3080 V between tube wall and anode wire of the MDT tubes, the gas gain is 20000. The passing muon can also knock out an electron from an atom of the tube wall, a so called  $\delta$ -electron, which frequently passes the tube at a shorter distance to the wire than the muon (see Fig. 4.2a) masking the muon hit and leading to wrong drift-time measurement.

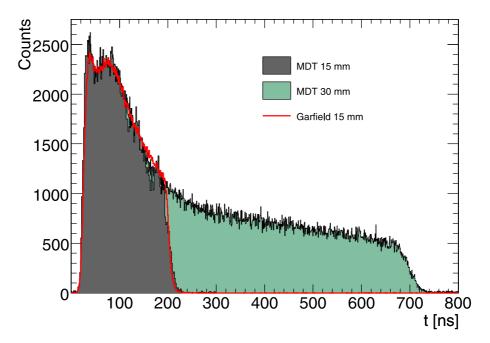

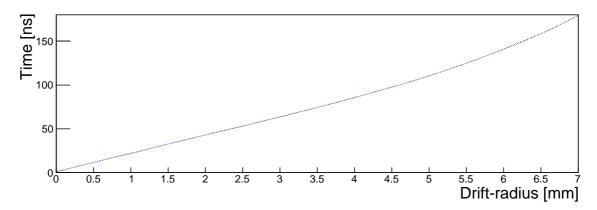

The minimal distance between muon track and wire can be determined by measuring the time between the muon passing and the ionised signal arriving at the wire (see Fig. 4.1a) and using a calibrated space-to-drift-time relation. In Fig. 4.6 the drift-time spectrum recorded with a uniformly irradiated MDT tube is shown. The drift velocity of the electrons depends on the drift gas. Therefore, the purity of the gas is important for the precise drift distance measurement.

#### 4. Muon Drift-Tube Chambers

Figure 4.1.: (a) Cross section of an MDT tube and (b schematic view of an ATLAS MDT chamber in the barrel region) [9].

| Parameter                     | MDT design value                       | sMDT design value     |  |

|-------------------------------|----------------------------------------|-----------------------|--|

| Tube material                 | Aluminium                              |                       |  |

| Outer tube diameter           | 29.970  mm                             | 15.0  mm              |  |

| Tube wall thickness           | $0.4 \mathrm{\ mm}$                    |                       |  |

| Wire material                 | gold-plated W/Re $(97/3)$              |                       |  |

| Wire diameter                 | $50~\mu\mathrm{m}$                     |                       |  |

| Gas mixture                   | $Ar/CO_2/H_2O$ (93/7/ $\leq$ 1000 ppm) |                       |  |

| Gas pressure                  | 3 bar (absolute)                       |                       |  |

| Gas gain                      | 20000                                  |                       |  |

| Wire potential                | +3080  V                               | +2730  V              |  |

| Maximum drift-time            | $\sim 700 \text{ ns}$                  | $\sim 185 \text{ ns}$ |  |

| Average drift-tube resolution | $80~\mu\mathrm{m}$                     | $105~\mu\mathrm{m}$   |  |

Table 4.1.: Parameters of the MDT and sMDT chambers [9].

Figure 4.2.: (a) Illustration of the effect of  $\delta$ -electrons [20]. A muon knocks an electron out of the tube wall which may cross the tube closer to the wire than the muon and, therefore, masks the real muon hit leading to a wrong drift-time measurement.

(b) Principle of track reconstruction in the drift-tube chambers. The track is fitted to the measured drift-radii [20].

Fig. 4.2b illustrates the muon track reconstruction by minimising the distances between track and measured drift-circles (see also Section 6.3.5.5).

#### 4.1.1. MDT Chamber Read-out Electronics

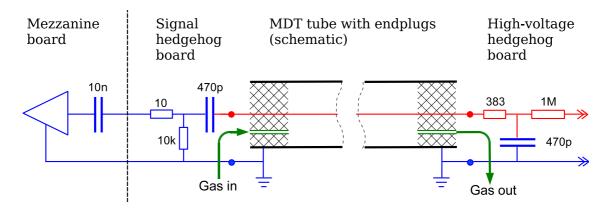

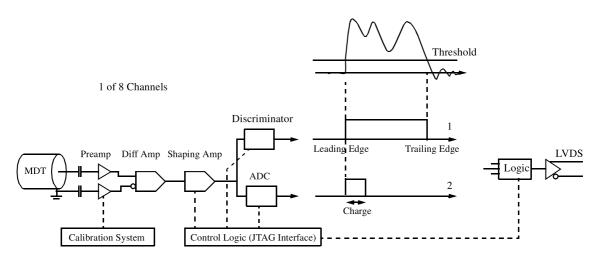

Fig. 4.3 gives an overview of the electronics circuits connected to the drift-tubes. The electrical connections are implemented on so-called hedgehog boards which supply 24 tubes each. One end of the tube is used for high-voltage supply and is terminated with the drift-tube impedance of 383  $\Omega$  to avoid signal reflections. Noise is suppressed with a low-pass filter. At the other end of the tube, the signal is capacitively decoupled from the high-voltage and further processed by active read-out electronics circuits on the so-called Mezzanine boards [21], which each contains three 8-channel ASD<sup>1</sup> chips which amplify and shape the signal (see Section 5) and send the digital signal to a Time-to-Digital converter (TDC) if the analogue pulse is above a predefined threshold. In order to minimise noise, the ASD circuits are differential. A block diagram of one channel is shown in Fig. 4.4.

Parameters of the chip can be set using the JTAG<sup>2</sup> protocol. Besides the discriminator threshold, the most important parameter is the artificial (programmed) dead time after a pulse exceeding the threshold which can be set between a minimum of 220 ns and a maximum of 820 ns and is discussed in Section 4.3.2.1. For a detailed description of all ASD parameters see [22].

<sup>&</sup>lt;sup>1</sup>Amplifier Shaper Discriminator

<sup>&</sup>lt;sup>2</sup> Joint Test Action Group, IEEE 1149.1 Standard Test Access Port and Boundary-Scan Architecture

Figure 4.3.: Electrical connections to an ATLAS MDT tube [21]. One end of the tube is used for high-voltage supply and terminated with the drift-tube impedance of 383  $\Omega$  to avoid signal reflections. The other end of the tube, the signal is capacitively decoupled from the high voltage and processed by preamplifier and shaper circuits on the so-called Mezzanine boards.

The ASD chip provides two options to determine the input charge from the shaped signal. The first one is to measure the time interval during which the signal is above the threshold and the second one is to measure the pulse charge using a Wilkinson ADC [22] at the first threshold crossing time of the signal.

The digital output pulses of the ASD are sent to a 24-channel Time-to-Digital-Converter (TDC) on the Mezzanine card, which measures the threshold crossing time corresponding to the arrival time of the ionisation signal of the wire with respect to the trigger signal. The ATLAS Muon Spectrometer uses the AMT-3 chip [23] as TDC.

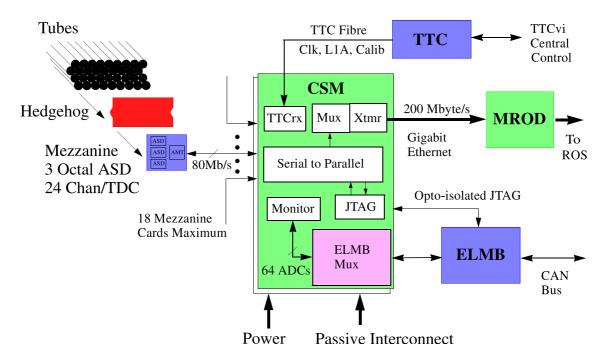

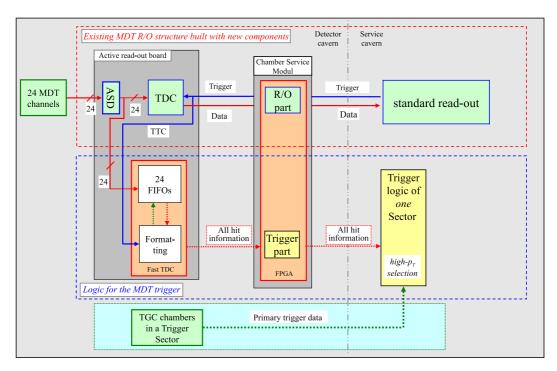

Up to 18 AMT chips, corresponding to 432 MDT channels (the maximum number of channels of an MDT chamber in ATLAS), are read out by a so-called Chamber Service Module (CSM) on the chamber. The CSM transmits the LHC clock and trigger signals (TTC<sup>3</sup>) and JTAG code to the ASD-chips and the temperature sensor measurements on the Mezzanine cards to the detector control system (DCS) via the ELMB<sup>4</sup>. The data of the TDCs are sent via an optical fibre from the CSM to a read-out driver (MROD<sup>5</sup>) module for further processing [21]. An overview of the whole read-out chain is shown in Fig. 4.5. For further details on the ATLAS MDT read-out system and its performance see [21,24].

<sup>&</sup>lt;sup>3</sup>Timing Trigger and Control

<sup>&</sup>lt;sup>4</sup>Embedded Local Monitor Board

<sup>&</sup>lt;sup>5</sup>MDT Readout Driver

Figure 4.4.: Block diagram of one ASD channel [21]. The incoming signal is amplified, bipolar shaped (see Section 5) and digitised. The ASD chip can be operated in (1) time over threshold or (2) charge measurement mode. The ASD can be configured using the JTAG protocoll. The digital output of threshold crossing time is LVDS.

#### 4.2. Small-Diameter Muon Drift Tube Chambers

The MDT chambers installed in the ATLAS Detector show a very good efficiency and resolution up to the highest background counting rates expected at the LHC design luminosity. But at much higher background rates as expected at the high-luminosity upgrade of the LHC (HL-LHC) they suffer from a degradation of the spatial resolution and muon detection efficiency (see Section 4.3). Therefore, drift-tube chambers with reduced tube diameter of 15 mm, so-called small-Diameter Muon Drift Tube (sMDT) chambers have been developed. For compatibility reasons, all other drift-tube parameters, especially gas mixture and pressure and the gas gain, are kept the same (see Tab. 4.1). Due to the smaller diameter, the wire potential has to be decreased to 2730 V in order to obtain the gas amplification of 20000.

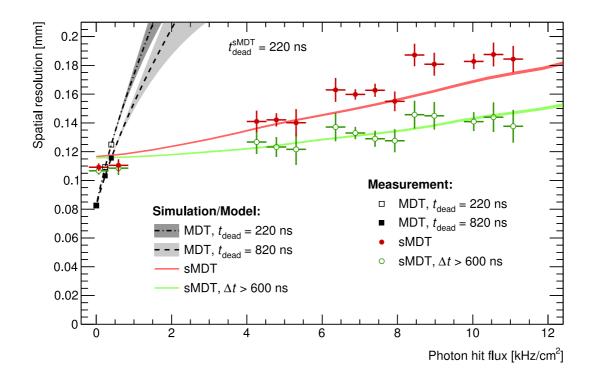

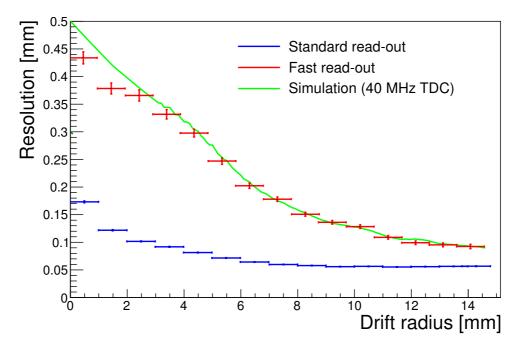

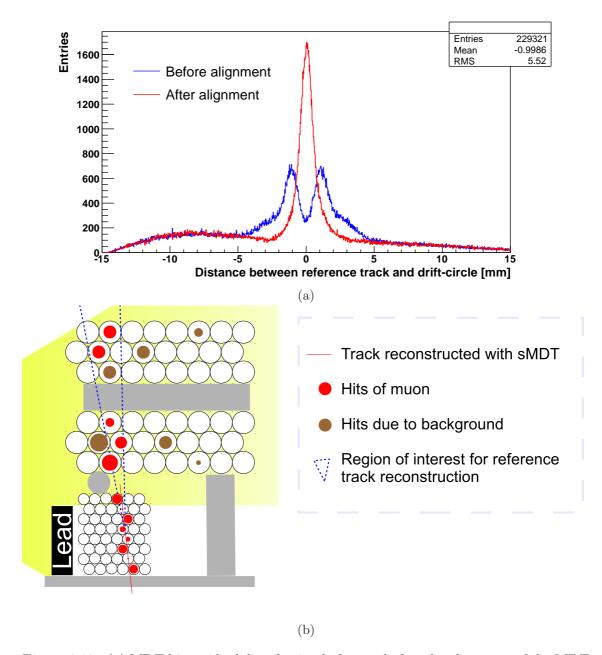

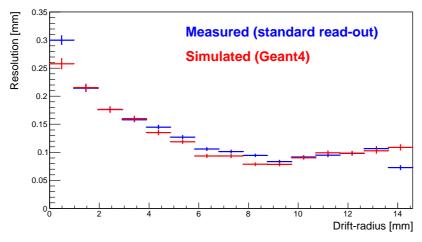

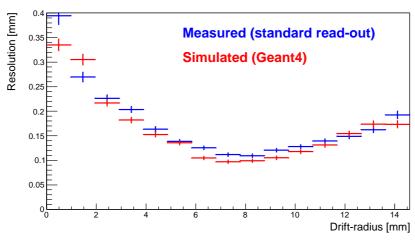

The drift-tubes with the two times smaller diameter are expected to two times lower hit rate at the same background flux. The maximum drift-time of sMDT tubes is only about 185 ns [27], a factor of  $\sim 3.8$  smaller than for MDT tubes. Altogether, the drift-tube occupancy is reduced by a factor of  $2 \cdot 3.8 = 7.6$ . In addition, the reduced tube diameter leads to strong suppression of space-charge effects [25] deteriorating the spatial resolution (see Section 4.3) and allows for higher redundancy and efficiency in track segment reconstruction due to the up to two times larger number of tube layers fitting into the same volume. The average spatial resolution without background irradiation is slightly worse by about 20  $\mu$ m compared to MDT tubes (see Fig. 4.7) due to the shorter average drift distances (see Fig. 4.9).

#### 4. Muon Drift-Tube Chambers

Figure 4.5.: Block diagram of the on-chamber data processing with Mezzanine boards, CSM, ELMB, TTC, and MROD [21]. While the TTC trigger signals and the data transmissions are to the MROD, the connections to the CSM are through the passive interconnect.

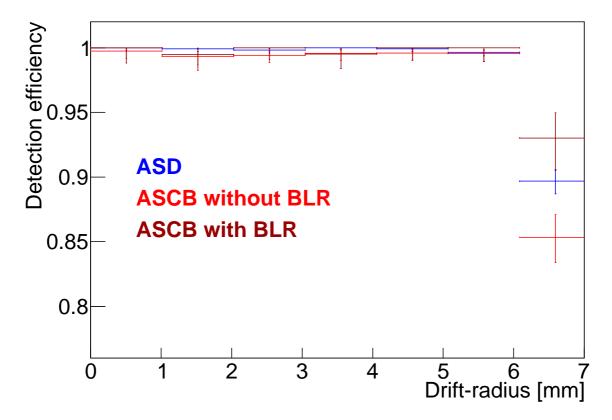

#### 4.2.1. Spatial Resolution and Muon Efficiency

The performance of the sMDT tubes has already been studied extensively using the standard MDT read-out electronics [28–30].

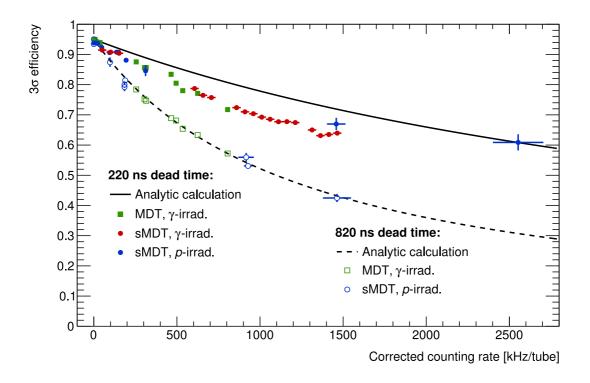

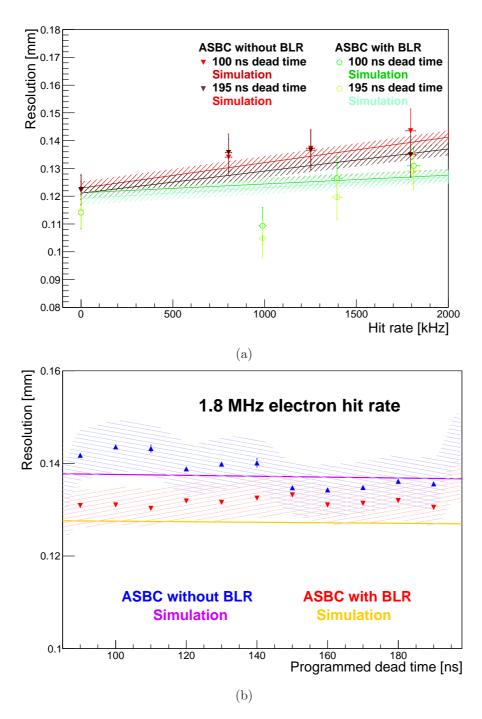

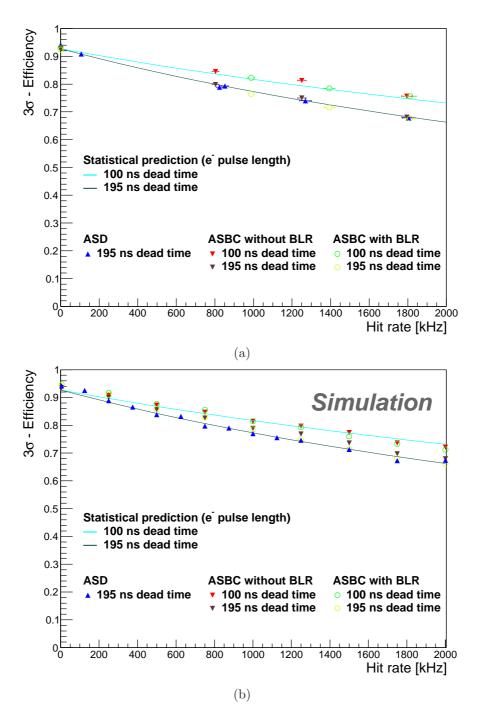

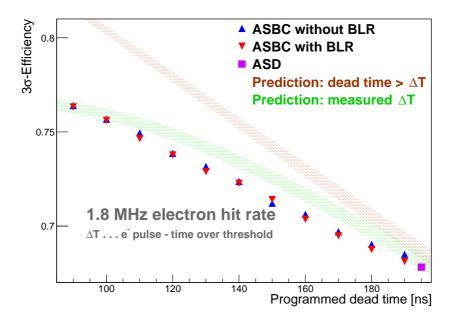

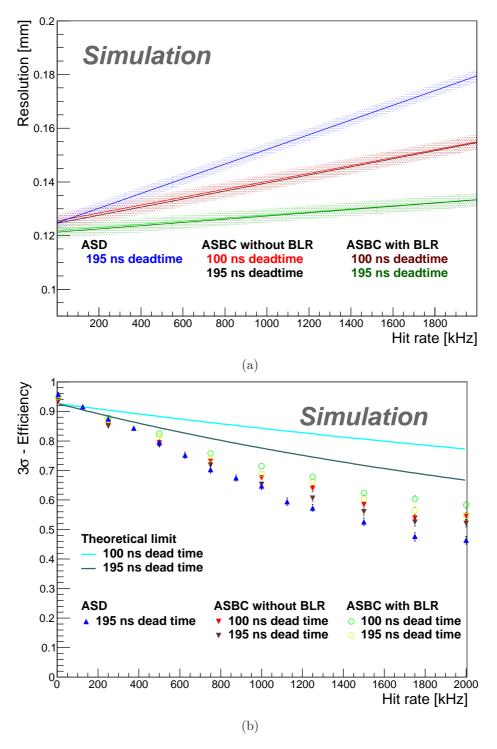

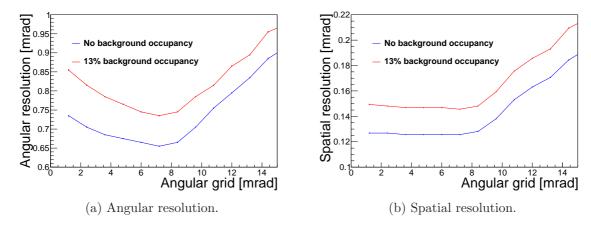

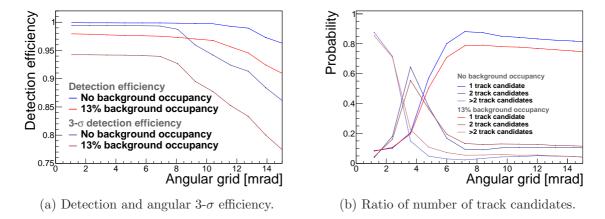

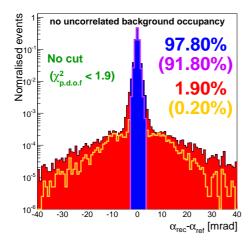

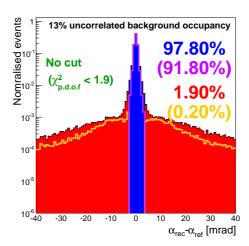

Fig. 4.7 and Fig. 4.8 show the average MDT and sMDT single-tube spatial resolution and  $3\sigma$  muon detection efficiency<sup>6</sup> depending on the flux and counting rate of photon conversions, respectively. In addition, the sMDT resolution is shown with the requirement  $\Delta t > 600$  ns on the time interval between two successive hits, which is equivalent to operation with a dead time of 600 ns.

The read-out electronics behaviour has a strong impact on the resolution and  $3\sigma$ -efficiency of the sMDT tubes at very high background rates. The sMDT resolution and efficiency depend strongly on the electronics dead time and the signal shaping. By optimisation of signal shaping the resolution and efficiency at high background rates of the sMDT tubes operated with short dead time settings can be improved significantly (see Section 5).

<sup>&</sup>lt;sup>6</sup>The probability for a hit to be measured on the extrpolated muon trajectory within three times the drift-tube spatial resolution as a function of the drift-radius.

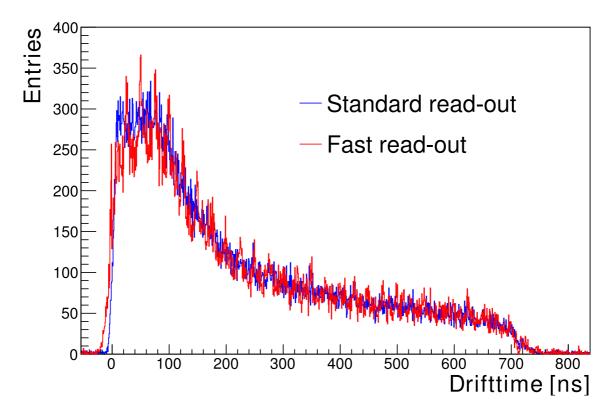

Figure 4.6.: Drift-time spectra of MDT and sMDT tubes operated with Ar:CO2 (93:7) gas mixture at 3 bar absolute pressure and a gas gain of 20000 [25]. The measurement with cosmic ray muons is compared with simulation (Garfield [26]) for the 15 mm diameter tubes.

#### 4.3. High-Rate Phenomena

Most of the hits in the MDT chambers are caused by the  $\gamma$  and neutron background radiation in the ATLAS cavern (see Section 3.3), which cause space charge of slow drifting ions in the tubes and mask muon hits due to the dead time of the read-out electronics.

#### 4.3.1. Space Charge Effects

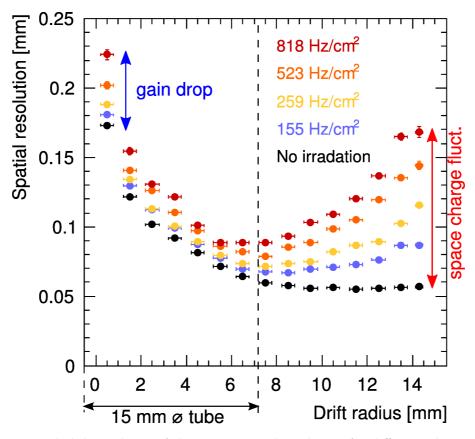

The ion space charge in the drift-tubes caused by the background hits modifies the electric field and, hence, the drift-velocity and the gas amplification. Due to the stochastic nature of the background hits, the space charge and, therefore, the drift velocity vary in time, leading to a degradation of the spatial resolution increasing with the drift-distance. This effect of space charge fluctuations, which cannot be taken into account in calibration of the space to drift-time relationship, is shown in Fig. 4.9.

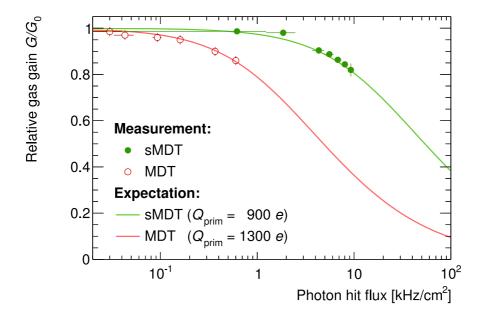

The shielding of the wire potential by the ion space charge leads to loss in gas gain (see Fig. 4.10), smaller signals and, therefore, degradation of the time resolution. This effect dominates for muon tracks passing the tube close to the wire.

Close to the tube wall, the effect of space charge and, consequently, of the electric field and of the drift-velocity on the spatial resolution dominates [32].

Figure 4.7.: Average spatial resolution of 1 m long sMDT and MDT drift-tube depending on the flux of background photon conversions for different electronics dead time settings of the read-out electronics [27]. In addition, the sMDT resolution is shown for the requirement  $\Delta t > 600$  ns on the time interval between two successive hits is shown, which is equivalent to operation with a dead time of 600 ns. Solid coloured lines show the simulated sMDT resolution for different dead time settings.

#### 4.3.2. Read-Out Electronics Effects

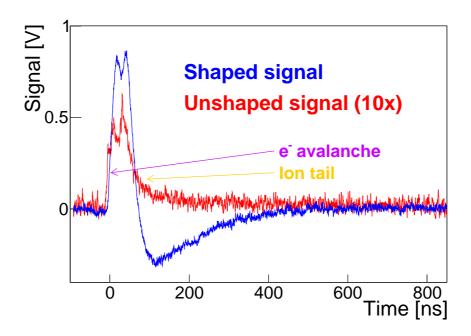

In Fig. 4.11 a typical amplified signal from an sMDT tube muon is shown. The fast rising leading edge is caused by the electron avalanche, while the slowly drifting ions cause the long trailing edge of the unshaped pulse.

Due to the different arrival times of the ionisation electron clusters along the muon path, the signals can show several peaks which may result in several discriminator threshold crossings while only the first threshold crossing time is of interest for the drift-time measurement. In order to suppress these secondary discriminator threshold crossings, electronics dead time programmable between a minimum of 220 ns and a maximum of 820 ns which covers the maximum drift-time of the MDT tubes during which electron clusters may arrive, is used in the ASD chip (see Section 5.2).

Figure 4.8.:  $3\sigma$ -efficiency of MDT and sMDT tubes depending on the dead time-corrected background  $\gamma$  counting rate (see Section 4.3.2.1) for minimum and maximum electronics dead time settings of the ASD chip [27]. The analytic calculation is based on Eq. 4.4.

Without additional signal shaping, the tails cause a shift of the baseline at high counting rates. From different signal shaping options (see Section 5.1), the ASD uses bipolar shaping (see the blue curve in Fig. 4.11). Bipolar shaping differentiates the signal suppressing low frequencies. It provides baseline stability up to high rates, but causes an undershoot with a length corresponding to the length of the ion tail.

#### 4.3.2.1. Dead Time Effects

During the electronics dead time  $\tau$ , the read-out electronics is insensitive to any further hits arriving. Therefore, the muon detection efficiency decreases with increasing background rate depending on the dead time. When m is the true counting rate and k counts are registered in a read-out time window T, a total dead time  $k\tau$  is accumulated, since each detected hit triggers the electronics dead time. During the total dead time,  $mk\tau$  counts are lost. The true number of hits in the time window is (see [33])

$$mT = k + mk\tau (4.1)$$

#### 4. Muon Drift-Tube Chambers

Figure 4.9.: Radial dependence of the MDT spatial resolution for different photon irradiation rates [31]. The degradation of the resolution with increasing background flux due to fluctuations of the space charge and, therefore, of the drift-field is limited to the region r>6 mm and increases with the drift distance. Loss of gas gain due to shielding of the wire potential decreases the signal amplitude which leads to a worsening of the resolution in particular near the wire.

leading to

$$m = \frac{\frac{k}{T}}{1 - \frac{k}{T}\tau} . \tag{4.2}$$

Taking into account the linear dependence of the muon efficiency on the observed counting rate  $r = \frac{k}{T}$

$$\epsilon(r) = \epsilon_0 \cdot (1 - r \cdot \tau) , \qquad (4.3)$$

where  $\epsilon_0$  is the muon efficiency in the case of negligible hit rate, one obtains

$$\epsilon(m) = \frac{\epsilon_0}{1 + m\tau} . \tag{4.4}$$

The observed and the true counting rate differ because also background hits are masked by preceding hits. In order to obtain maximum efficiency, the dead time has to be as short as possible while minimising the probability for secondary threshold crossings.

Figure 4.10.: Dependence of the relative gas gain G/G0 in MDT and sMDT tubes on the flux of photon conversions ( $G_0 = 2 \cdot 10^4$ ) [27]. The expectation is based on primary ionisation charges  $Q_{prim}$  of the converted photons.

For the sMDT tubes, the electronics dead time can be reduced to at least the maximum drift-time of 185 ns, about 3.8 times shorter than for the MDT tubes. The ASD chip, of the moment, only allows for a minimum dead time of  $\sim 200$  ns determined by the time needed by the Wilkinson ADC for the signal charge measurement.

#### 4.3.2.2. Signal Pile-Up Effects

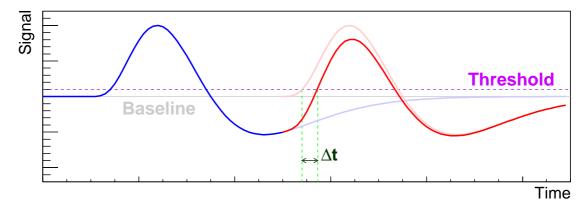

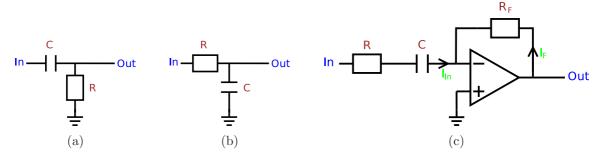

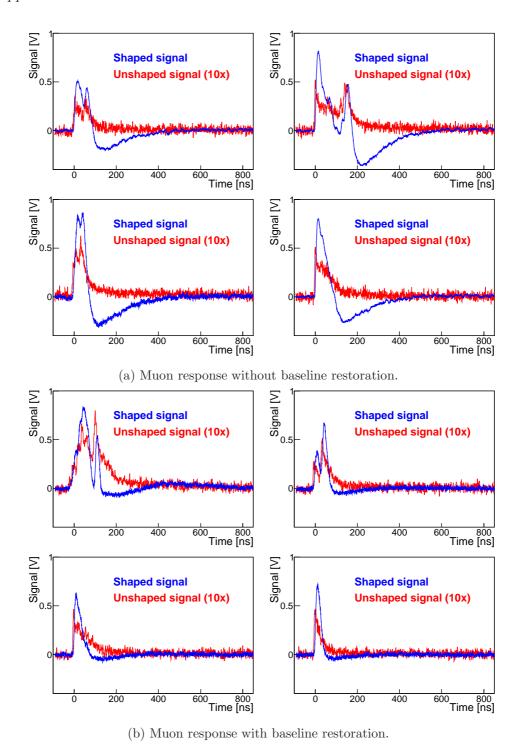

With bipolar shaping and short electronics dead times scheme, muon signal pulses may be overlaid at high counting rates on top of the undershoot of preceding photon or neutron background pulse leading to a reduction of amplitude and rise time of the secondary muon pulse at the baseline and the discriminator threshold and to a shift of the threshold crossing time (see Fig. 4.12).

These signal pile-up effects lead to hit efficiency loss and degrade the time resolution. The time slewing corrections (see Section 5.4.2.1) based on the signal charge measurement using the Wilkinson ADC implemented on the ASD chip recover only very little of the pile-up degradation (see [27]).

The pile-up effects can be effectively suppressed by optimisation of the shaping or baseline restoration (see Section 5).

Figure 4.11.: Typical signal of a muon in an sMDT tube amplified with a 10 k $\Omega$  transimpedance amplifier before (red line) and after (blue line) bipolar shaping. While the electron avalanche causes the steeply rising leading edge of the signal pulse, the slow drifting ions lead to the long trailing edge of the unshaped pulse which is removed by signal shaping (Measurement bandwidth: 200 MHz).

Figure 4.12.: Illustration of signal pile-up effect with bipolar shaping. Due to the signal undershoot, the threshold crossing time of the successive pulse is shifted by  $\Delta t$  and the amplitude is reduced.

# 5. Optimisation of Drift-Tube Read-Out Electronics for High Counting Rates

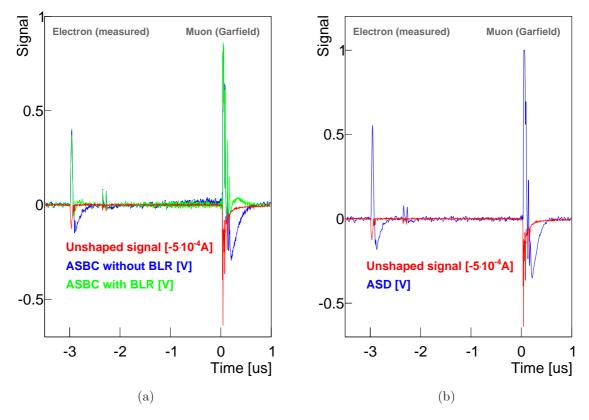

At high counting rates, the read-out electronics has strong impact on the performance of sMDT tubes. Bipolar shaping as used in the present version of the read-out electronics provides baseline stability, but its performance is limited by signal pile-up. In order to reach a higher rate capability, baseline restoration can be used.

In the following, the application of baseline restoration for the sMDT tube read-out electronics is discussed. Parts of this chapter are also presented in [34–36].

#### 5.1. Signal Shaping

In order to minimise the effect of noise and baseline shifts due to slowly decreasing trailing pulses edges, analogue detector signals need to be processed. This processing is called signal shaping.

Two commonly used signal shaping concepts are the so-called unipolar and bipolar shaping [32].

#### 5.1.1. Unipolar and Bipolar Signal Shaping

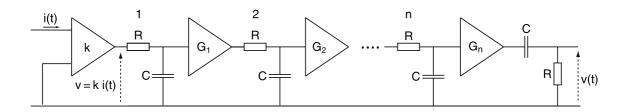

If linear<sup>1</sup> filters with negligible differentiation behaviour are used for signal shaping, the pulse processing is called unipolar shaping (an overview about different kind of unipolar shaping is given in [37]). Besides the simple CR high-pass and RC low-pass filter, also more complex filter types can be used. Details on signal shaping are discussed in Appendix A.2.1.

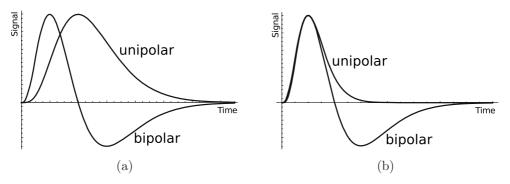

Signals with slow decreasing falling edges processed with unipolar shaping can cause a shift of the baseline (see Section 4.3.2). Hence, the differentiation of the shaped signal has been proposed in [38], leading to the so-called bipolar shaping. Due to the differentiation slow changing edges are set to the baseline, so even in case of a sequence of pulses the baseline stays stable. The differentiation of the trailing edge causes a response with contrary polarity, this effect is the undershoot of the bipolar shaping, see Fig. 5.1 (the corresponding circuits and calculation are presented in Appendix A.2.1). Due to charge conservation, the area below the pulse is zero (the area of overshoot and undershoot are equal). When the bandwidth of the differentiator is limited, this argument is not valid any more and the total area below the pulse may not be zero (see Appendix A.2.3).

<sup>&</sup>lt;sup>1</sup>A given input pulse  $I_{in}(t)$  results in an output pulse  $V_{out}(t)$ , where  $V_{out}[c \cdot I_{in}(t)] = c \cdot V_{out}[I_{in}(t)]$ .

#### 5. Optimisation of Drift-Tube Read-Out Electronics for High Counting Rates

Figure 5.1.: δ-response illustration of unipolar and bipolar shapings [32]. (a) shows shapings with identical parameters, hence the bipolar shaped response is the derivative of the unipolar shaped response. In (b), the shaping parameters of the bipolar shaper are chosen in order to the gain the same peaking time.

In Fig. 5.1a-5.1b the  $\delta$ -responses for unipolar and bipolar shaping are illustrated. If the shaping parameters are identical (see Fig. 5.1a), bipolar shaping shows a smaller peaking time<sup>2</sup> with respect to unipolar shaping due to the derivative of the signal (see Fig. 5.1b). In order to gain the same peaking time, the parameters of the bipolar shaper needs to be modified, leading to a longer signal response. Hence, the advantage of baseline stability of the bipolar shaping trades off against pulse length.

A more detailed description of unipolar and bipolar shaping and its application for MDT read-out electronics is given in [32,39]. Electrical circuits for differentiation are discussed in Appendix A.2.3.

#### 5.1.2. Baseline Restoration

In order to minimise the pile-up effect of bipolar shaping at high counting rates (see Section 4.3.2.2), the undershoot of the signal response needs to be minimised. This minimisation is called baseline restoration (BLR).

If all input pulses have similar pulse height and length, baseline restoration can be realised by the use of additional filters (see [40]). Otherwise, a non-linear solution have to be chosen, where the decision depends on the application.

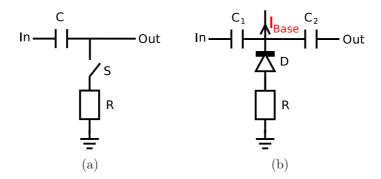

The principle of the simplest one is shown in Fig. 5.2a. During the undershoot the switch S is closed, leading to signal suppression (CR filter). The switch can be implemented using passive components (diode with capacities and resistors) as shown in Fig. 5.2b. Due to its switching time and its non-linear voltage-current characteristic curve, it may be useful to set a working point for the diode using the current  $I_{Base}$ . In case of a fixed current, the concept is called passive BLR (see [41]). By setting the current depending on the input signal, this concept can be further improved, leading to the so-called active baseline restoration, see [42,43].

<sup>&</sup>lt;sup>2</sup>Time when the  $\delta$ -response reaches the maximum.

Figure 5.2.: (a) Basic principle of passive, active and gated baseline restoration. During the undershoot the switch S is closed, leading to signal suppression (CR filter). (b) Possible implementation of passive (Current  $I_{Base}$  is zero or fixed) and active (Current  $I_{Base}$  depends on signal on In) baseline restoration.

If an additional circuit for undershoot detection controlling the switch S is used, the concept is called gated BLR, for further information see [44, 45]. Alternatively, it is also possible to restore the baseline by adding the inverted signal to input signal, this concept is discussed in [45, 46].

#### 5.2. The ASD Chip

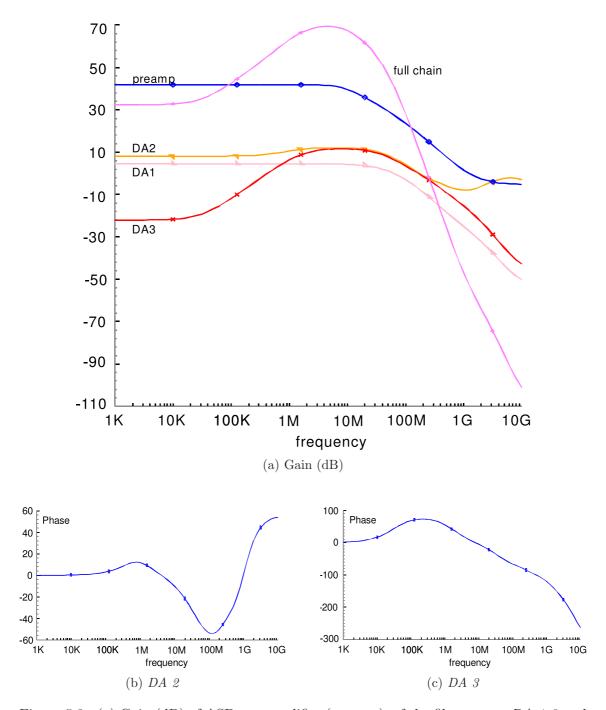

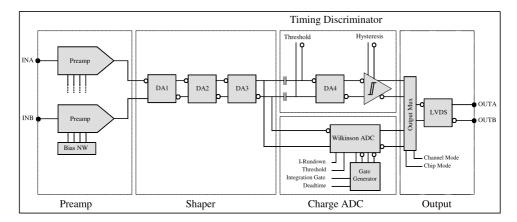

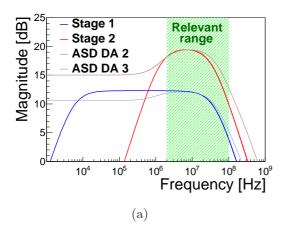

The ASD chip [22] is an octal CMOS Amplifier/Shaper/Discriminator using bipolar shaping optimised for the ATLAS MDT chambers (see Section 4.1). In Fig. 5.4 one channel is shown as block diagram. The circuit is fully differential and consists of four stages.

**Pre-Amplifier** The pre-amplifier (preamp) consists of an "active" and an associated "dummy" amplifier. While the active amplifier is capacitively coupled to the drift-tube, the dummy amplifier is left floating providing DC balance to the subsequent stages as well as some degree of noise suppression. The gain of the pre-amplifier is shown in Fig. 5.3a as a function of the frequency. It has a 3dB-bandwidth<sup>3</sup> of 11.94 MHz.

**Shaper** The shaper consists of three stages:

- **DA** 1 is a simple amplifier with a 3dB-bandwidth of 45 MHz. Its main purpose is to ensure the differential signal being completely complementary.

- **DA** 2 implements a pole/zero network (see Appendix A.2) in order to cancel the very long time constant component of the positive ion MDT pulse.

<sup>&</sup>lt;sup>3</sup>Frequency where the gain is reduced by 3 dB with respect to the maximum gain.

#### 5. Optimisation of Drift-Tube Read-Out Electronics for High Counting Rates

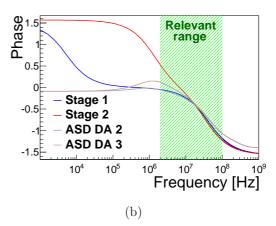

Figure 5.3.: (a) Gain (dB) of ASD pre-amplifier (preamp), of the filter stages DA 1-3 and full chain of theses stages depending on the frequency [22]. Frequency dependent phase of (b) the DA 2 stage (pole/zero filter) and (c) the DA 3 stage (RC network) [22].

Figure 5.4.: Block diagram of one channel of the ASD chip consisting of four stages [22] (see text).

• *DA 3* uses a simple series RC network with a RC product of approximately 50 ns to effect a bipolar shaping stage. In contrary to the preamp and *DA 1-2*, *DA 3* is non-linear for signals larger than one third of the maximum signal range.

The gain depending on the frequency of DA 1-3 is plotted in Fig. 5.3a.

**Discriminator** The discriminator consists of a timing discriminator and a Wilkinson  $ADC^4$  operated in parallel. The timing discriminator applies the threshold voltages and amplifies the signals with an additional amplifier  $(DA\ 4)$  with a gain of 16 dB and a 3dB-bandwidth of 85.7 MHz.

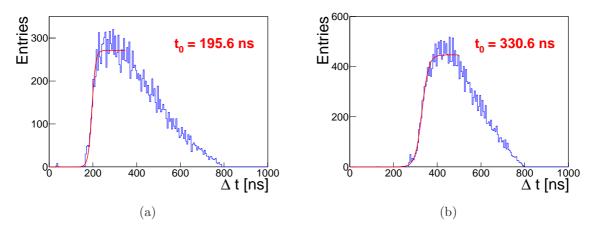

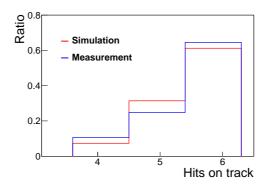

The ADC measures the leading edge pulse charge in order to perform time slew correction in offline analysis to enhance timing resolution. Due to measurement time of the Wilkinson ADC, a programmable dead time between 200 and 800 ns for the discriminator is implemented differing between unique ASD chips. The actual dead time can be measured in operation by plotting the time difference between two proceeding hits and determine the minimum of the distribution. In Fig. 5.5 this distribution for the two different ASD chips is shown. For the measurement results presented in this thesis, the ASD chip of Fig. 5.5a has been used.

Besides in the ADC mode, the ASD chip can also operated in time-over-threshold mode which provides information about the pulse length above the threshold.

The final output information consists of the threshold carrying signal of the leading edge pulse and either of threshold carrying signal of the falling edge in time-over-threshold mode or of the digitised input pulse charge in ADC mode. These signals are converted by a LVDS driver into low-level output signals.

<sup>&</sup>lt;sup>4</sup>The Wilkinson ADC integrates the signal charge onto a holding capacitor and measure its value by running it down at constant current.

#### 5. Optimisation of Drift-Tube Read-Out Electronics for High Counting Rates

Figure 5.5.: Time difference between two successive hits measured with two different ASD chips. The onset  $t_0$  of the distribution, which is determined by fitting a Fermi function, corresponds to the effective dead time.

Besides the shaper stages DA 2-3, the preamp and DA 1 are also essential for the shaping due to their limited bandwidth. Fig. 5.3a shows clearly that the magnitude of the preamp and DA 2/3 3dB-bandwidth is the same.

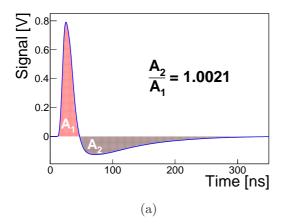

In order to set a starting point for a successor of the ASD chip, a LTSpice<sup>5</sup> simulation has been set up (see [47]). The  $\delta$ -response for two different signal amplitudes obtained with this simulation is shown together with the ratio of the area below over- and undershoot in Fig. 5.6. Due to the bipolar shaping scheme (see Appendix A.2.1), the ratio is approximately one. In the following, the results obtained with this simulation are used for comparison.

# 5.3. A Discrete Pulse Shaper for sMDT Tubes (ASBC)

In order to test and understand the application of baseline restoration for the sMDT readout, a shaping circuit with properties similar to the ASD has been designed. It is called ASBC - Amplifier, Shaper, Baseline-Restorer, Comparator.

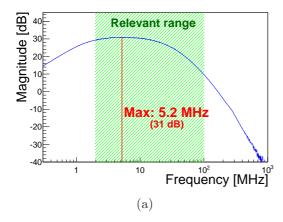

The design was carried out according to the gain of the ASD shaper stages DA 2 and DA 3, the gain of preamp and DA 1 were approximated to be constant. The relevant frequency range has been defined with 2 MHz to 100 MHz, according to the parameters of a typical muon pulse ( $\sim$ 10 ns rise time and  $\sim$ 500 ns fall time, see Fig. 4.11).

Figure 5.6.: ASD  $\delta$ -response (8 ns rise time, shaped on 1.2 pF) for (a) 50 mV and (b) 100 mV amplitude obtained from [47]. Due to the bipolar shaping scheme, the area below over- and undershoot are approximately equal. The signal amplitudes indicate the non-linearity of DA 3 (twice the input does not lead to twice the output).

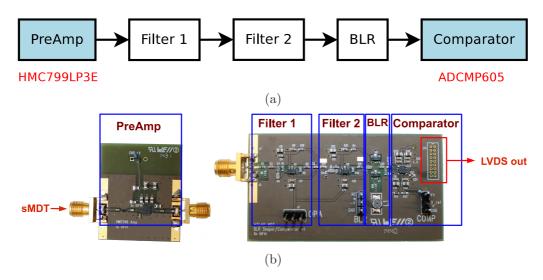

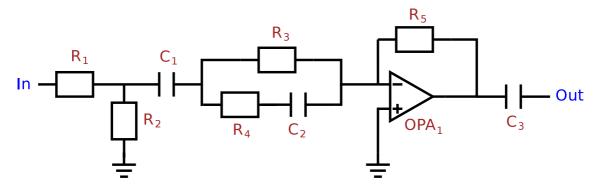

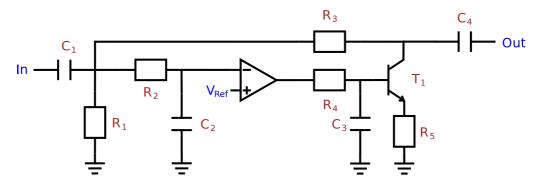

#### 5.3.1. The ASBC Circuit

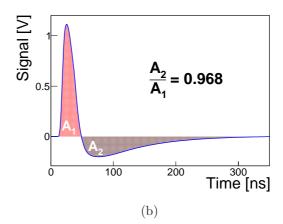

The structure and a photograph of the ASBC are shown in Fig. 5.7a and 5.7b. For the sMDT signal amplification, a transimpedance amplifier<sup>6</sup> with 10 k $\Omega$  transimpedance<sup>7</sup> and 700 MHz bandwidth is used, corresponding to the combination of the pre-amplifier and DA 1 of the ASD. The signal shaping is conducted in three stages, where the first one does ion tail cancellation, the second one additionally shapes and differentiate the signal and the third one restores the baseline. The resulting amplified and shaped signal is then digitised, using a comparator<sup>8</sup> with 1.6 ns propagation delay with 1 ps rms random jitter. The voltage on the second input of the comparator can be modified to gain an adjustable signal threshold.

#### 5.3.1.1. Filter Stage 1

The schematic of the filter stage 1 (purpose ion tail cancellation, corresponding to DA 2 of ASD) is shown in Fig. 5.8. The circuit consists of a voltage divider, which is also used for cable termination, and an AC-coupled inverting amplifier, where a pole-zero network is used as input resistor of the inverter.

<sup>&</sup>lt;sup>5</sup>SPICE (Simulation Program with Integrated Circuit Emphasis) implementation of Linear Technology. <sup>6</sup>HMC799LP3E, Hittite Microwave Corporation (*PreAmp*), see [48].

<sup>&</sup>lt;sup>7</sup>A transimpedance amplifier is a current-to-voltage converter (inverted). Therefore, the gain g is described with  $g = \frac{U}{I} = [\Omega]$ .

<sup>&</sup>lt;sup>8</sup>ADCMP605, Analog Devices, see [49].

Figure 5.7.: (a) Structure and (b) photograph of the ASBC (Amplifier, Shaper, Baseline-Restorer, Comparator) electronics. For sMDT signal amplification (*PreAmp*) a transimpedance amplifier (HMC799LP3E, see [48]) and for digitisation a comparator (ADCMP605, see [49]) is used. The pulse shaping is conducted in three stages, where the third one also restores the baseline.

The complex resistance  $Z_{pz}$  of the pole-zero network is<sup>9</sup>

$$Z_{pz}(\omega) = R_3 \| (R_4 + \frac{1}{i\omega C_2})$$

(5.1)

In case of an ideal operational amplifier<sup>10</sup> ( $OPA_1$ ), a large resistance of the pole-zero network with respect to  $R_2$  and a big capacity of  $C_1^{11}$ , the complex gain  $G_1$  is calculated with

$$G_1(\omega) = -\frac{R_2}{R_1 + R_2} \cdot \frac{R_5}{Z_{pz}(\omega)} = -\frac{R_2 \cdot R_5}{R_1 + R_2} \cdot \frac{(R_3 + R_4) \cdot \omega C_2 - i}{R_3 \cdot (R_4 \cdot \omega C_2 - i)} . \tag{5.2}$$

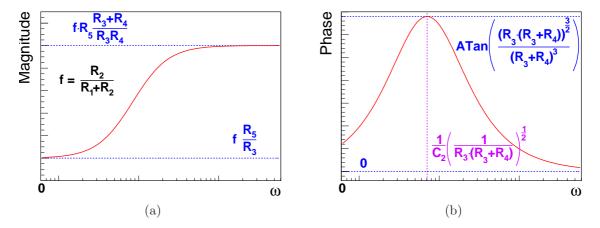

The magnitude and phase of Eq. 5.2 are shown in Fig. 5.9a and Fig. 5.9b. While the magnitude is bounded between the limits defined by the pole-zero network, the phase show a maximum for a certain frequency (see Section A.2.5).

Eq. 5.2 describes the high-pass behaviour of the circuit, indeed, it is necessary to include the low-pass features the ASD DA2 (see Fig. 5.3a). Thus, the limited bandwidth of a real operational amplifier<sup>12</sup> is used and the value of the feedback resistor  $R_5$  is chosen to gain the necessary bandwidth. The values of the parts shown in Fig. 5.8 are listed in Tab. A.2. The resulting gain<sup>13</sup> is shown Fig. 5.12. The magnitude and phase are in accordance with the corresponding ASD parameters.

<sup>&</sup>lt;sup>9</sup> || indicates parallel arrangement.

<sup>&</sup>lt;sup>10</sup>Infinite input resistance, infinite gain, infinite bandwidth

<sup>&</sup>lt;sup>11</sup>The capacity has to be big enough to provide AC-coupling without signal shaping.

<sup>&</sup>lt;sup>12</sup>For this application, THS4304 [50] is used.

<sup>&</sup>lt;sup>13</sup>Calculation based on the gain-bandwidth-product GBW=870 MHz (see [50]).

Figure 5.8.: Schematic of filter stage 1, see Fig. 5.7a. It consists of an AC-coupled inverting amplifier, where a pole-zero network is used as input resistor of the inverter. Filter stage 1 is a high-pass for sMDT signal ion tail cancellation.

Figure 5.9.: Filter stage 1 magnitude (a) and phase (b) (see Eq. 5.2) depending of the frequency. The determination of the bounds is discussed in Section A.2.5.

# 5.3.1.2. Filter Stage 2

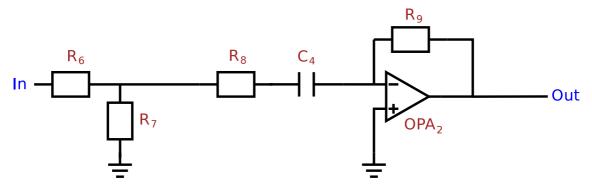

The schematic of the filter stage 2, which consists of a voltage divider and an inverting amplifier with an RC-circuit as input resistance, is shown in Fig. 5.10. The circuit corresponds the differentiator shown in Fig. A.2c, its purpose is signal shaping and signal differentiation (see Eq. A.17) and its functionality corresponds to DA 3 of the ASD.

The complex resistance  $\mathbb{Z}_{RC}$  of the RC-circuit is

$$Z_{RC} = R_8 + \frac{1}{i\omega C_4} , \qquad (5.3)$$

leading to a complex gain  $G_2(\omega)$  of the circuit under the assumption of an ideal operational amplifier and a large resistance of the RC-circuit with respect to  $R_7$

$$G_2(\omega) = -\frac{R_7}{R_6 + R_7} \cdot \frac{R_9}{Z_{RC}} = -\frac{R_7 \cdot R_9}{R_6 + R_7} \cdot \frac{\omega C_4}{\omega R_8 C_4 - i} . \tag{5.4}$$

Figure 5.10.: Schematic of filter stage 2 (see Fig. 5.7a). It consists of an inverting amplifier, where an RC-circuit is used as input resistor of the inverter. Filter stage 2 is used as differentiator.

Figure 5.11.: Filter stage 2 magnitude (a) and phase (b) (see Eq. 5.2) versus frequency. The determination of the bounds is discussed in Section A.2.6.

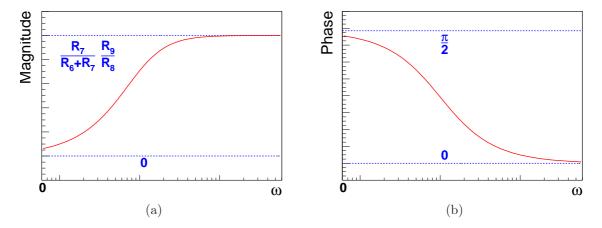

The magnitude and phase of Eq. 5.4 are shown in Fig. 5.11a and Fig. 5.11b. The circuit behaves as filter stage 1 with  $R_3 \to \infty$  in Eq. 5.2. Fig. 5.11a is Fig. 5.9a shifted and Fig. 5.11b shows the falling edge of Fig. 5.9b. In order to obtain the same gain as DA3 of the ASD (see Fig. 5.3a), low pass behaviour has to be added to filter stage 2. Thus, the amplifier bandwidth is adjusted with the feedback resistor  $R_9$ . The resulting gain is illustrated in Fig. 5.12. The magnitude shows a small difference for high frequencies of the relevant range and the phase for lower frequencies, respectively.

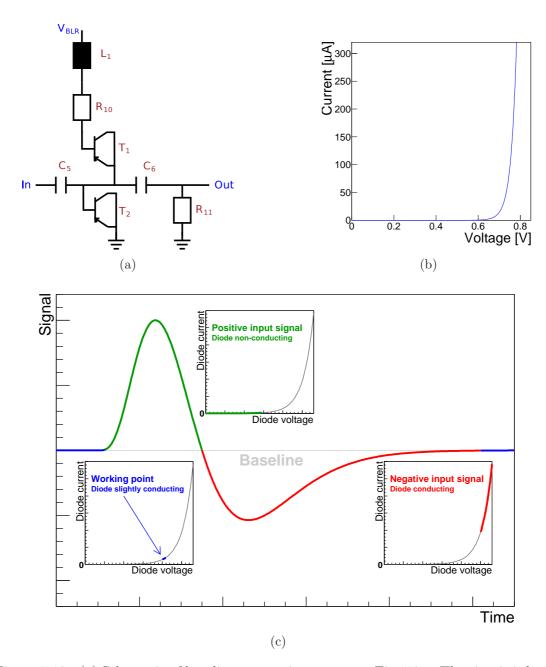

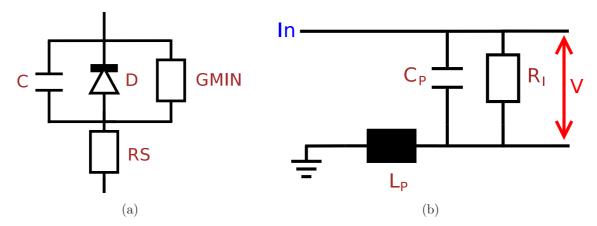

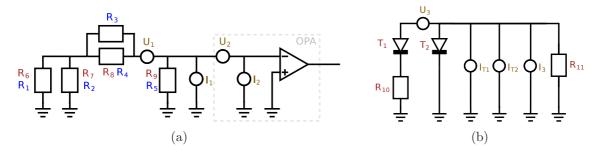

# 5.3.1.3. BLR Stage

The schematic of the BLR stage is shown in Fig. 5.13a. It uses a passive baseline restoration concept and corresponds to the circuit shown in Fig. 5.2b, where the resistor  $R_{10}$  and the inductance  $L_1$  are used together as current source and the transistor  $T_2$  is connected in a

Figure 5.12.: (a) Gain magnitude and (b) phase of stage 1 and stage 2 including the frequency behaviour (gain-bandwidth-product) of the operation amplifiers in comparison with ASD *DA 2* and *DA 3*, where the ASD magnitude is multiplied and the phase is shifted to reach the ASBC level.

way to act as diode. The second transistor  $T_2$  defines the current pointer and compensates the impact of small temperature changes, the capacitor  $C_6$  provides AC-coupling and  $R_{11}$  is a pull-down resistor defining the baseline.

The reason for using a transistor<sup>14</sup> as diode is caused by its low capacity in comparison to commonly used diodes. Its characteristic line is shown in Fig. 5.13b. Together with  $C_5$  the transistor capacity acts as voltage divider and together with the diode as RC-circuit, so the transistor capacity should be small and  $C_5$  should be large. On the other hand,  $C_5$  affects the timing behaviour of the transistor and should be as small as possible<sup>15</sup>.

Due to the interaction of all parts, the non-linear behaviour of the diode and, hence, the shaping behaviour of the BLR stage, the parameter selection is a trade-off and the optimal values according to simulation and tests are shown in Tab. A.2.

The voltage at  $V_{BLR}$  defines the current over  $T_1$  and  $T_2$  and sets, consequently, the working point. The operating principle is shown in Fig. 5.13c, the three different operating states are

- Baseline input: Due to the current flowing over  $R_{10}$  the diode is slightly conducting, so the potential between the diodes is stable, causing the baseline at Out.

- Positive input: The positive input voltages compensates the current over  $R_{10}$  and shifts the diode into the non-conducting mode. If the BLR-current is small with respect to the signal current over  $C_5$ , the signal at Out is the same as at In.

- **Negative input:** The negative input voltage shifts the diode into the full conducting mode, causing a short-circuit of the signal to ground and, therefore, restoring the baseline.

<sup>&</sup>lt;sup>14</sup>The used transistor (PNP) is a BFT92, see [51].

<sup>&</sup>lt;sup>15</sup>For details on the timing behaviour of semi-conductors see [52].

Figure 5.13.: (a) Schematic of baseline restoration stage, see Fig. 5.7a. The circuit is based on the passive BLR concept, where a transistor is used as diode due to its low capacity. The working point is defined by the voltage at  $V_{BLR}$ ,  $R_{10}$  and  $L_1$ , which together act as current source.

- (b) Characteristic line of BFT92 used as diode (wiring corresponding to (a)).

- (c) Operating principle of the baseline-restorer shown in (a). On the working point (baseline input), the diode is slightly conducting, for positive input signals it become non-conducting and negative signals are drained to ground.

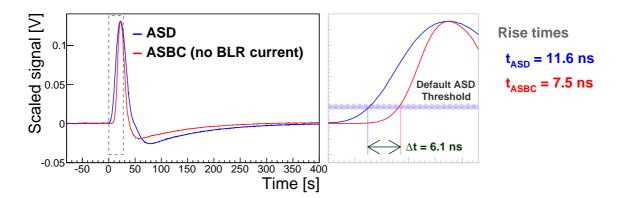

Figure 5.14.:  $\delta$ -response of ASD and ASBC (scaled to fit the amplitude of the ASD response). The  $\delta$ -signal was obtained by shaping a square pulse of 800 mV amplitude with 1.2 pF capacity. The right plot indicates the difference of the rise times for an ASD threshold of 38 mV.

If the working point is too low, the diode does not shift into conducting mode, if, however, it is too high, the diode never becomes non-conducting. So the working point has to be chosen with care, and the behaviour of the ASBC depending of  $V_{BLR}$  has to be measured.

In this thesis, the following definitions are used:

- ASBC without BLR: The diode current is zero.

- ASBC with BLR: The diode is operated at the working point.

# 5.3.2. Comparison of ASD and ASBC $\delta$ -Response

In Fig. 5.14 the  $\delta$ -response of ASD and ASBC without BLR measured in front of the discriminator is shown. The input pulse is obtained from an AC-coupled (1.2 pF) square signal.

There are two major differences between ASD and ASBC

- $\bullet$  The rise time<sup>16</sup> of the ASBC is smaller.

- The bipolar undershoot is smaller and faster.

The smaller rise time which is caused by higher bandwidth of the ASBC electronics PreAmp (the ASD chip Preamp and DA 1 are part of the signal shaper, see Section 5.2) is expected to have a positive impact on resolution and efficiency, because the faster rising edge minimises the time-slewing effect. Likewise, the signal pile-up effect for high counting rates is expected to be suppressed.

In addition, further pile-up suppression by the smaller bipolar undershoot is expected.

$<sup>^{16}</sup>$ Time between 10% and 90% of the signal amplitude.

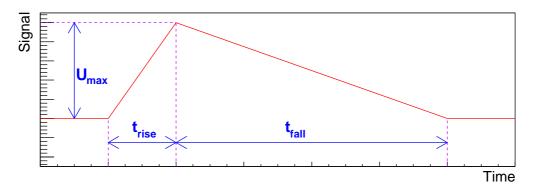

Figure 5.15.: Parametrisation of input pulse with rise time  $(t_{rise})$ , fall time  $(t_{fall})$  and amplitude  $(U_{max})$ . Due to AC-coupling of the shaping circuit, the absolute level of the baseline does not matter and the difference between baseline and peak is the relevant parameter.

# 5.3.3. ASBC Response for a Parametrised Pulse

The first approach to evaluate the behaviour of baseline restoration implementation is the ASBC response measured in front of the comparator for a simplified pulse representing the actual muon and background caused pulses.

In Fig. 5.15 the pulse shape, which is a  $\delta$ -pulse with different rise and fall time, used for the following measurements is shown. The three pulse parameters are the amplitude  $U_{max}$ , the rise time  $t_{rise}$  and the fall time  $t_{fall}$ . Due to AC-coupling of the shaping circuit, the absolute level of the baseline does not matter and the difference between baseline and peak is the relevant parameter.

Due to its high bandwidth with respect to the shaper, the ASBC pre-amplifier has no shaping effect on the signals. Hence, the following measurements were obtained from the ASBC without pre-amplifier.

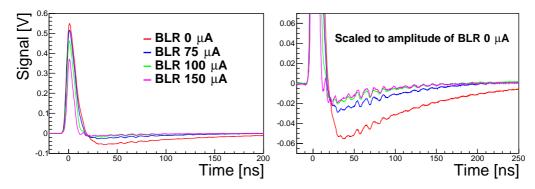

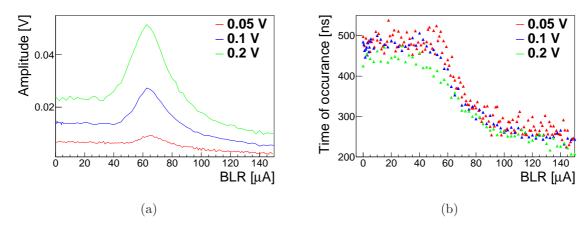

In Fig. 5.16 the response for different BLR currents is shown. The BLR current has impact on the amplitude as well as on the undershoot. Following the diode characteristic line shown in Fig. 5.13b, the undershoot suppression increases with the BLR working point until a certain current value. The value is the optimal working point. As soon the working point is set in the linear range of the diode, further suppression of the bipolar undershoot with respect to the response amplitude is not possible.

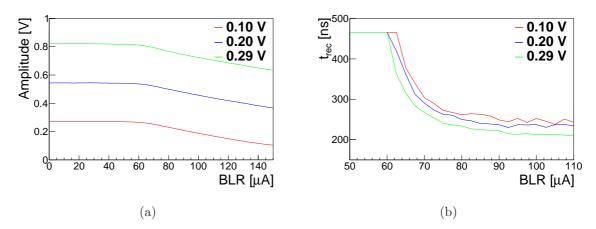

In Fig. 5.17a the amplitude and in Fig. 5.17b the recovery time<sup>17</sup> of the ASBC response depending on the working point for different input pulse amplitudes are shown. These measured functions can be explained with the diode threshold and characteristic line. As soon the working point is above the diode threshold, the BLR impact increases until a certain value. Fig. 5.17b shows that the optimal working point is approximately 90  $\mu$ A.

<sup>&</sup>lt;sup>17</sup>Definition: The time after the input signal when the mean of the next 30 ns has the same value as 30 ns of the baseline.

Figure 5.16.:  $\delta$ -response (5 ns rise time, 5 ns fall time, 0.2 V amplitude) of ASBC (without PreAmp) for different baseline restoration (BLR) currents. Besides a faster baseline recovery, an increasing BLR current causes a reduction of the signal amplitude. Therefore the graphs of the left plots are scaled to the same amplitude. The signal fluctuations of the undershoot are caused by reflections on the signals lines.

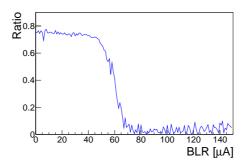

The ratio of the areas below the  $\delta$ -response undershoot and overshoot is expected to be one for bipolar shaping (assuming infinite bandwidth, see Appendix A.2.1). Fig. 5.18 shows this ratio for the ASBC depending on the BLR current. Without baseline restoration the ratio is smaller than one, due to the bandwidth of filter stage 2 (see Section 5.3.1.2). With increasing BLR current, the ratio stays constant until the diode threshold and then decreases very fast until it saturates slightly above zero.

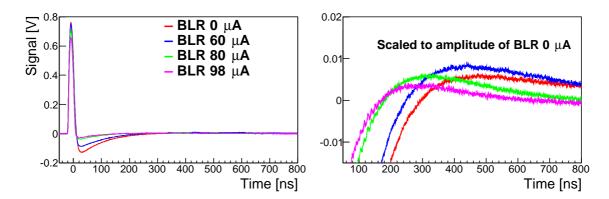

Due to the additional shaping behaviour of the dynamic diode capacity (see Section 5.3.4), it is expected to obtain an additional overshoot after the bipolar undershoot. This overshoot occurs for slowly decreasing pulses, it is shown in Fig. 5.19. In order to avoid additional comparator threshold crossings caused by noise increasing the signal height of the undershoot, it has to be as low as possible.

In Fig. 5.20a the amplitude of this second overshoot and in Fig. 5.20b its time of occurrence with respect to the input pulse depending on the working point is shown. The second overshoot shows a maximum for working points in vicinity of the diode threshold, then it decreases with increasing working point. For the 90  $\mu$ A working point, the amplitude of the overshoot is smaller than in case of no BLR current.

The functions of Fig. 5.20b<sup>18</sup> shows a similar shape as the recovery time of Fig. 5.17b. At the 90  $\mu$ A working point, the overshoot time is approximately halved.

Figure 5.17.: Amplitude (a) and recovery time (b) of the ASBC (without PreAmp)  $\delta$ response depending on the BLR current for different input amplitudes (5 ns

rise time, 5 ns fall time, see text.

Figure 5.18.: Ratio of the areas below successive undershoot and first overshoot of the  $\delta$ -response (5 ns rise time, 5 ns fall time, 0.05 V amplitude) depending on the BLR current for the ASBC (without PreAmp).

# 5.3.4. Response Simulation

The pulse shaping of the ASBC (without the PreAmp<sup>19</sup>) for arbitrary input pulses can be described with a two-tiered simulation, where the result of the first simulation is used as feed for the second one.

#### • Tier 1

Using scattering parameters, Tier 1 simulates the linear parts of the shaper (filter stages 1 and 2). The impact of the PCB is included because the scattering parameters are measured<sup>20</sup>. The magnitude and phase of the forward transmission coefficient are shown in Fig. 5.21.

<sup>&</sup>lt;sup>18</sup>Noise and reflections on the signals have a strong impact on the time measurements.

<sup>&</sup>lt;sup>19</sup>The PreAmp can be approximated by multiplying the input current signal with a factor of 10000.

$<sup>^{20}\</sup>mathrm{Due}$  to its layer structure, the PCB acts as capacitor.

Figure 5.19.: ASBC (without PreAmp)  $\delta$ -response (5 ns rise time, 20 ns fall time, 0.1 V amplitude) for different BLR currents. The right plot illustrates the impact of the BLR current on the second overshoot.

The Fourier transformed response  $\tilde{X}(\mu)$  of the shaping stages can be determined using the relation

$$\tilde{X}(\mu) = X(\mu) \cdot s(f) , \qquad (5.5)$$

where  $X(\mu)$  is the Fourier transform of the input pulse, s(f) is the forward transmission coefficient (complex scattering parameter  $S_{21}$ ) for the frequency corresponding to the integer index  $\mu^{21}$ .  $X(\mu)$  can be described by the discrete Fourier transform<sup>22</sup>

$$X(\mu) = \frac{1}{N} \sum_{n=0}^{N-1} x(n)e^{-\frac{2i\pi\mu n}{N}}$$

(5.6)

with the inversion

$$x(n) = \sum_{\mu=0}^{N-1} X(\mu) e^{\frac{2i\pi\mu n}{N}} , \qquad (5.7)$$

where N is the total number of data points and the integer index n in time domain. The following simulation results are obtained using the discrete Fourier transform library FFTW3 [54].

#### • Tier 2

Based on the SPICE library ngspice (see [55]) the BLR stage is simulated. This simulation includes non-linear effects, because SPICE is based on solving differential equations. In order to describe the diode behaviour of BFR92A<sup>23</sup>, a diode model had to be established.

Figure 5.20.: Amplitude (a) and time (b) of the late overshoot of ASBC shaped  $\delta$ -pulses (without PreAmp) depending of the BLR current for different input signal amplitudes (in Volt).

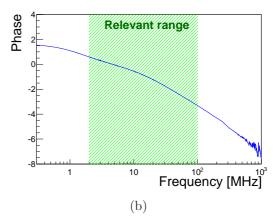

#### 5.3.4.1. The Diode Model

The schematic of the SPICE diode model [56] is shown in Fig. 5.22a. Here the behaviour of the diode is described with additional serial (GMIN) and parallel (RS) resistors and a parallel capacitance (C). The static diode forward<sup>24</sup> voltage and current (so-called DC large-signal model) can be calculated iteratively with

$$V = V_D + I_D \cdot RS \tag{5.8a}$$

$$I_D = I_S \cdot \left( e^{\frac{V_D}{N \cdot V_t}} - 1 \right) + V_D \cdot GMIN , \qquad (5.8b)$$

where V is the voltage on the circuit,  $V_D$  the voltage on the diode,  $I_D$  the current on the diode,  $I_S$  the diode saturation current, N the ideality factor of the diode and  $V_T = 25 \ mV$  the thermal voltage.

The so-called AC small-signal model approximates the dynamic diode forward behaviour with an parallel capacitance, which includes junction and diffusion effects.

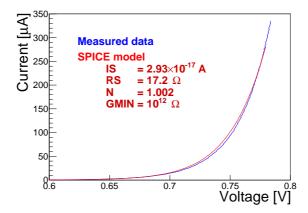

The parameters of the diode SPICE model (see Section A.2.7) are obtained using the minimisation with MINUIT2 [57] of the results obtained with measurement and simulation of

- the static diode model,

- Tier 1 and Tier 2, where the values of the static model are used as basis.

The fit of the characteristic line of the diode (the parallel resistance GMIN is fixed at the default value of  $10^{12} \Omega$ ) is shown in Fig. 5.23. The diode shows nearly ideal behaviour

<sup>&</sup>lt;sup>21</sup>Index of the discrete data table.

<sup>&</sup>lt;sup>22</sup>Definition according to [53].

<sup>&</sup>lt;sup>23</sup>NXP does not provide any simulation model for BFR92A used as diode.

<sup>&</sup>lt;sup>24</sup>Forward refers to the diode conducting polarity.

Figure 5.21.: (a) Magnitude and (b) phase of the measured forward transmission coefficient of ASBC filter stage 1 and 2.

(ideality factor<sup>25</sup>  $N \approx 1$ ) and its saturation current of  $2.93 \cdot 10^{-17}$  A is small with respect to standard diodes<sup>26</sup>. Due to the basis resistance of the transistor, the serial resistor RS=17.2  $\Omega$  is huge.

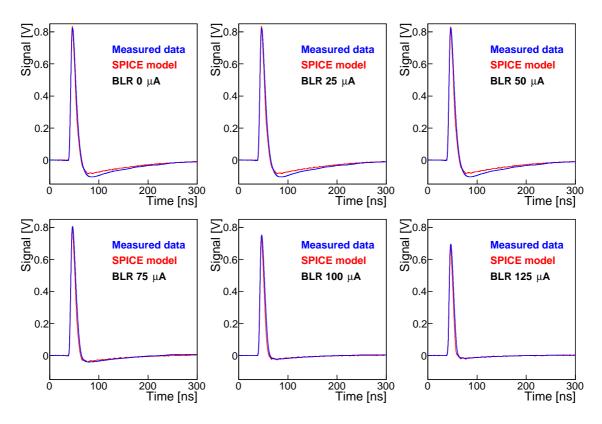

In Fig. 5.24 the results of the full simulation (Tier 0 and 1) based on the SPICE model fit for  $\delta$ -responses with different working points is shown. Measured data and fit show a minor discrepancy which may be caused by the SPICE model approximations and parasitic effects of the baseline restorer PCB area. Furthermore, the fit converges for a probe<sup>27</sup> inductance of 30 nH and a probe capacitance of 3.8 pF (see Fig. 5.22b). These values correspond to the expectation [58].

Overall, the simulation describes the BLR behaviour well which proves that the transistor circuit discussed above can be used as a diode.

#### 5.3.5. Threshold Determination

Due to the signal suppression caused by the BLR stage, the comparator threshold with and without baseline restoration differs. In order to obtain the values corresponding to the ASD default value of -39 mV (see [22]), two different methods were used.

#### 5.3.5.1. ASBC Without Baseline Restoration

The ASD and ASBC discriminator levels in response to a  $\delta$ -pulse have been compared. The  $\delta$ -signal was obtained by shaping a square pulse with an 1.2 pF capacitor.

<sup>&</sup>lt;sup>25</sup>The ideality factor of a diode is a measure of how closely the diode follows the ideal diode equation.

$<sup>^{26}</sup>$ 1N4148: IS = 3.5 · 10<sup>-11</sup> A, N = 1.24, RS = 0.064 Ω

$<sup>^{27} \</sup>mathrm{Inner}$  resistance according to data sheet: 1 M $\Omega$ .

Figure 5.22.: (a) Schematic of the SPICE diode model. The static behaviour of the diode is approximate with a serial and parallel resistor, the dynamic behaviour with a parallel capacitance, respectively.

(b) Description of the measurement probe. The ground connection is approximated with an inductance, the conductance of the probe and the inner resistance are included.

#### 5.3.5.2. ASBC With Baseline Restoration

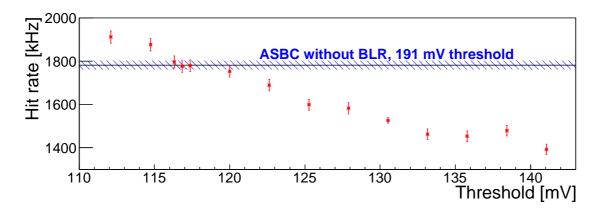

Due to the switching time of the diode, the shaping differs for very small (level of the threshold) and big signals (level of actual muon responses). Therefore, the default threshold was determined by comparing the measured hit rate (see Section 5.4.2.5) of a radiated sMDT tube read out with the ASBC with and without baseline restoration.

In Fig. 5.25 this measurement is shown, leading to a threshold of 116 mV.

#### 5.3.6. Noise Considerations

The voltage noise  $N_{tot}$  of a system consisting of l amplifiers can be described with its root mean square and, therefore, can be calculated by summing up the squares of the single noise sources and taking into account the gain of the amplifiers:

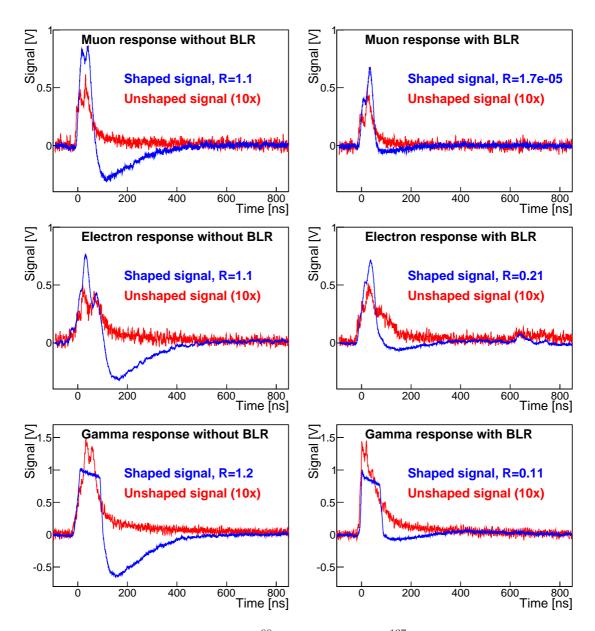

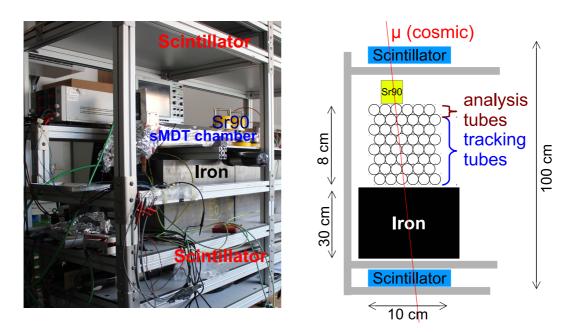

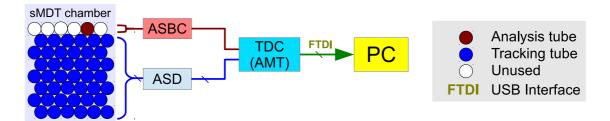

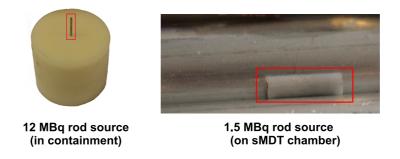

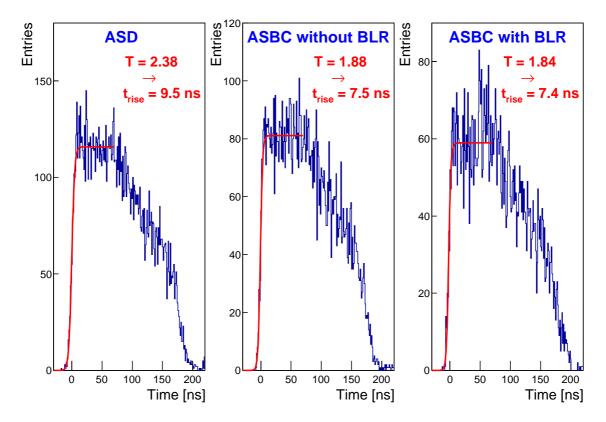

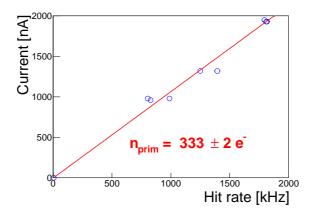

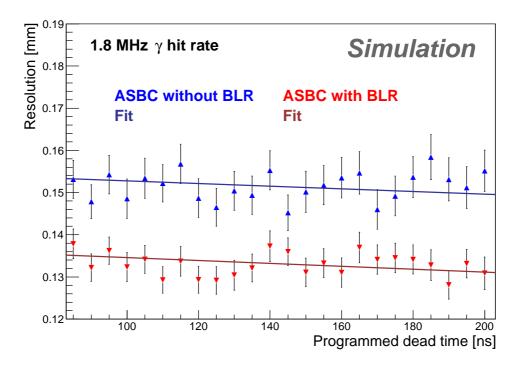

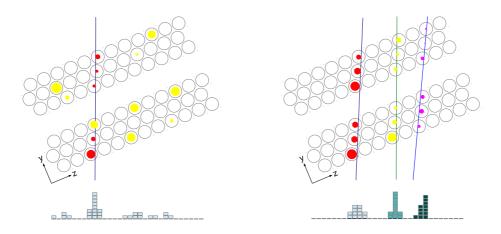

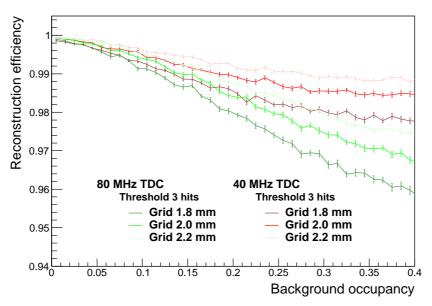

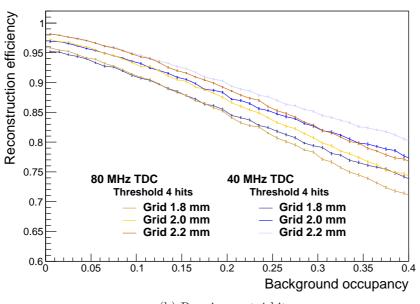

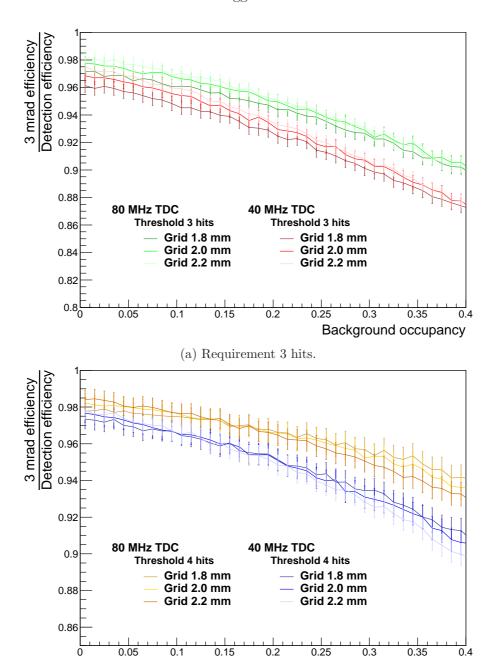

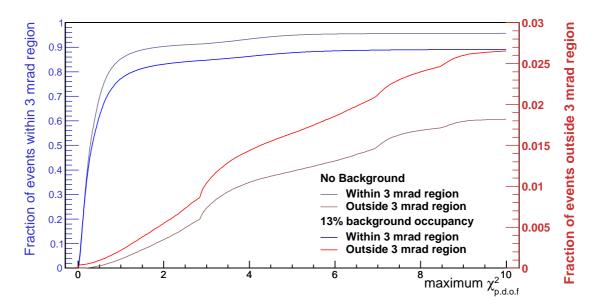

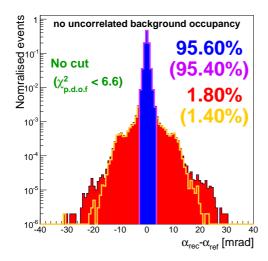

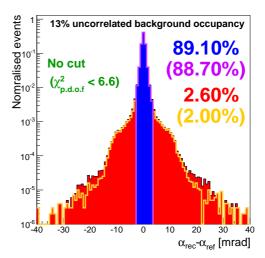

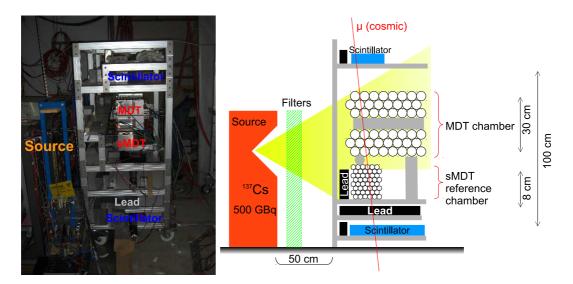

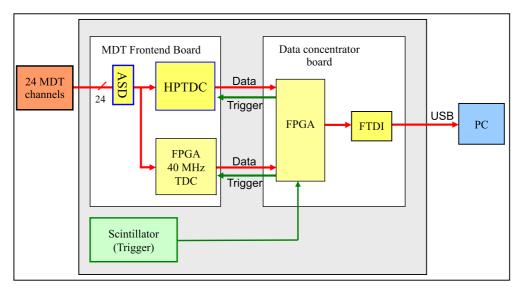

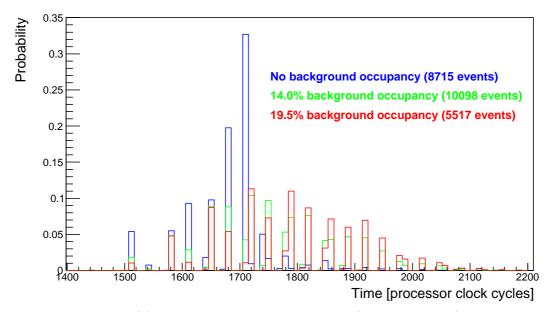

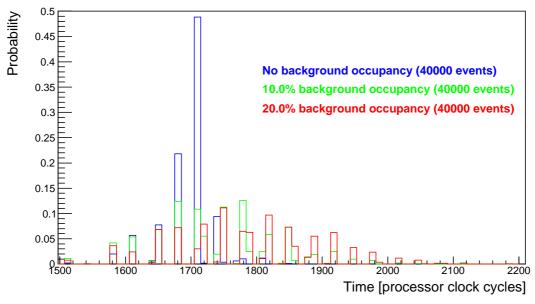

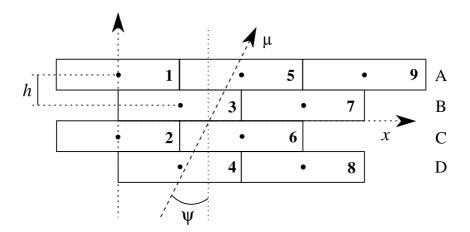

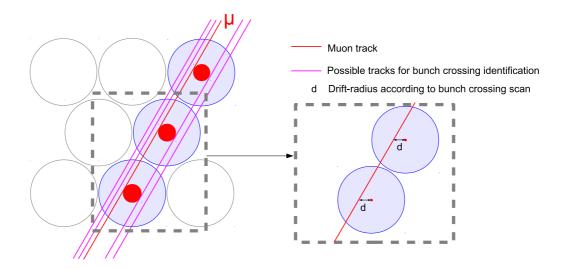

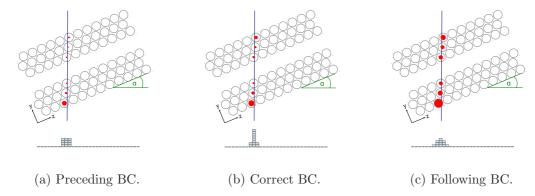

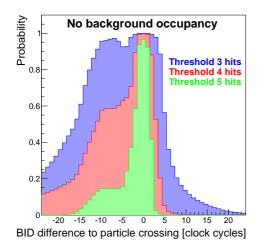

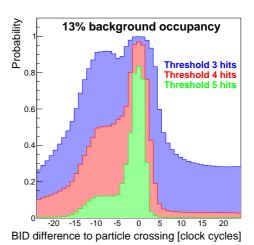

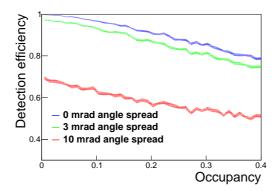

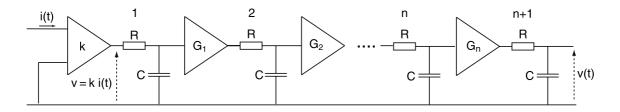

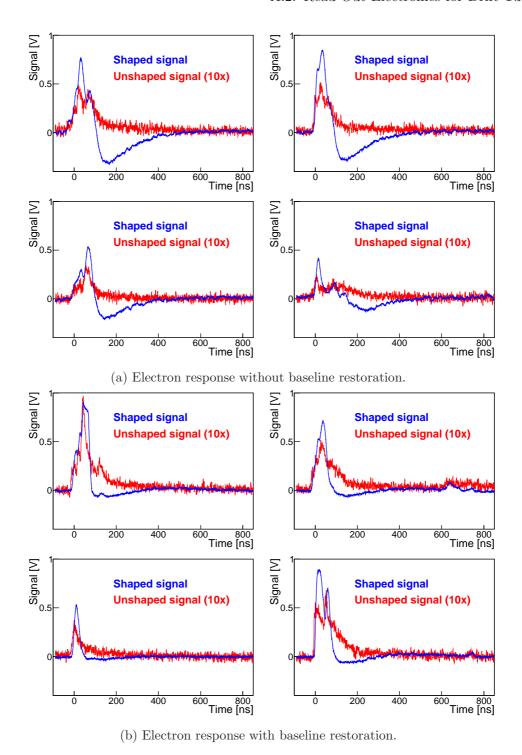

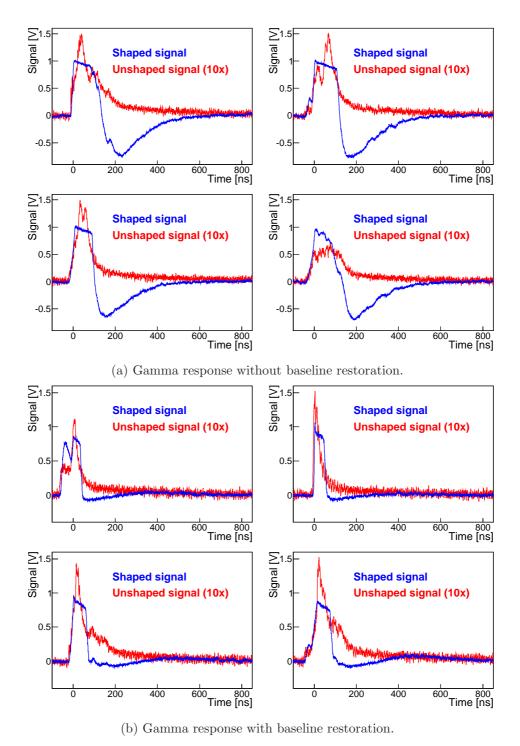

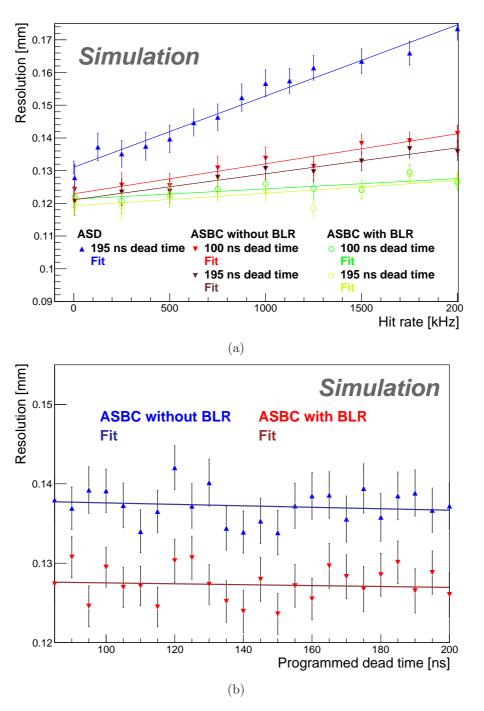

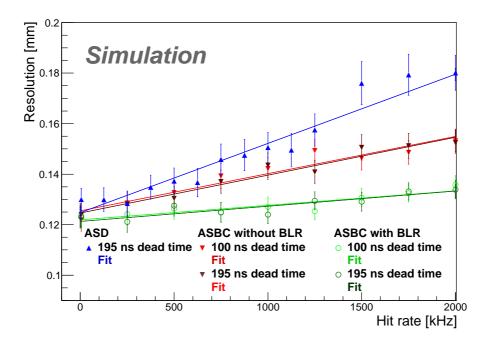

$$N_{tot} = \sqrt{\sum_{i=0}^{l} \left( U_i^2 \prod_{j=i+1}^{l} g_j \right)} , \qquad (5.9)$$