# Reduktion von Integrationsproblemen für Software im Automobil durch frühzeitige Erkennung und Vermeidung von Architekturfehlern

Herbert Reiter

# Institut für Informatik der Technischen Universität München

# Reduktion von Integrationsproblemen für Software im Automobil durch frühzeitige Erkennung und Vermeidung von Architekturfehlern

#### Herbert Reiter

Vollständiger Abdruck der von der Fakultät für Informatik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr. Uwe Baumgarten

Prüfer der Dissertation:

1. Univ.-Prof. Dr. h.c. Manfred Broy

2. Univ.-Prof. Dr. Jochen Ludewig,

Universität Stuttgart

Die Dissertation wurde am 12.07.2010 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 12.11.2010 angenommen.

# Kurzfassung

Ein wesentlicher Anteil der Funktionalität eines Automobils wird mittlerweile über den Einsatz von Elektrik, Elektronik und der sie steuernden Software realisiert. Vor der Integration müssen die einzelnen Komponenten umfangreiche Modultests bestanden haben. Dennoch zeigen sich im Verbund Fehler, die auf Schwächen in der Architekturbeschreibung und der Integration hindeuten.

Diese Arbeit definiert zunächst die Integrationsproblematik sowie zentrale Begriffe formal. Anschließend werden die Ergebnisse der im Rahmen dieser Arbeit durchgeführten empirischen Untersuchung bei der Robert Bosch GmbH vorgestellt. Zur praxistauglichen Erkennung und Vermeidung der Integrationsproblematik werden analytische sowie konstruktive Qualitätssicherungsmaßnahmen vorgeschlagen und bewertet.

### **Abstract**

In recent years many key functions in automobiles have come to be performed by electrical and electronic components and by the software on which they operate. Before integration phase each component has to pass comprehensive module tests. However, interconnected components lead to errors that indicate an insufficient architecture description and integration.

This thesis offers formal definitions of key terms and of the problems connected with integration and then presents results obtained from an empirical investigation at Robert Bosch GmbH. In order to detect and avoid the integration problem in practice, analytical as well as constructive quality assurance methods are suggested and evaluated.

# **Danksagung**

Mein herzlicher Dank gilt meinem Doktorvater Prof. Broy für die stets konstruktive Rückmeldung und zahlreiche wertvolle Anregungen und Denkanstöße sowie seinen Lehrstuhlmitarbeitern für die vielseitigen Diskussionen. Ebenso möchte ich mich bei Prof. Ludewig für die Übernahme des Zweitgutachtens und seine hilfreichen Anmerkungen bedanken.

Ganz besonders bedanke ich mich bei der Robert Bosch GmbH, die es mir ermöglicht hat, diese Dissertation im industriellen Umfeld anzufertigen, und insbesondere bei Andreas Thums für die Betreuung.

Des Weiteren bedanke ich mich bei meinen Korrekturlesern Iris Reiter, Ingeborg Rentsch und Torsten Schütze, bei letzterem auch für die vielen Tipps im Umgang mit LATEX.

# Inhaltsverzeichnis

| 1 | Einl | eitung                                       |                  |           |      |     |      |    |  |  |  | 13 |

|---|------|----------------------------------------------|------------------|-----------|------|-----|------|----|--|--|--|----|

|   | 1.1  | Motivation                                   |                  |           |      |     |      |    |  |  |  | 13 |

|   | 1.2  | Eigener Lösungsans                           | atz im Überbli   | ck        |      |     |      | •  |  |  |  | 14 |

| 2 | Syst | emintegration im A                           | utomobil         |           |      |     |      |    |  |  |  | 17 |

|   | 2.1  | $\operatorname{Umfeld} \ldots \ldots \ldots$ |                  |           |      |     |      |    |  |  |  | 17 |

|   |      | 2.1.1 Eingebettete                           | Systeme und      | deren Zus | samn | nen | spie | el |  |  |  | 17 |

|   |      | 2.1.2 Softwarebed                            | ingte Fehler .   |           |      |     |      |    |  |  |  | 20 |

|   |      | 2.1.3 Frühe Entwi                            | cklungsphasen    |           |      |     |      |    |  |  |  | 20 |

|   | 2.2  | Der Fehler-Begriff .                         |                  |           |      |     |      |    |  |  |  | 21 |

|   | 2.3  | Grundidee der Integ                          | gration          |           |      |     |      |    |  |  |  | 23 |

|   |      | 2.3.1 Modulare En                            | ntwicklung       |           |      |     |      |    |  |  |  | 23 |

|   |      | 2.3.2 Architektur-                           | und Integratio   | onsfehler |      |     |      |    |  |  |  | 25 |

|   | 2.4  | Fehlerlokalisierung                          | im Entwicklung   | gsprozess |      |     |      |    |  |  |  | 26 |

|   |      | 2.4.1 Tatsächliche                           | und ideale Ar    | tefakte . |      |     |      |    |  |  |  | 26 |

|   |      | 2.4.2 Mentale Art                            | efakte           |           |      |     |      |    |  |  |  | 27 |

| 3 | Gru  | ndlagen: Formales S                          | ystemmodell      |           |      |     |      |    |  |  |  | 29 |

|   | 3.1  |                                              |                  |           |      |     |      |    |  |  |  | 29 |

|   | 3.2  | Datenströme und O                            | peratoren auf    | Strömen   |      |     |      |    |  |  |  | 30 |

|   |      |                                              | stellung von S   |           |      |     |      |    |  |  |  | 30 |

|   |      |                                              | der Zeit         |           |      |     |      |    |  |  |  | 31 |

|   |      |                                              | auf Strömen .    |           |      |     |      |    |  |  |  | 31 |

|   | 3.3  | Verhaltensbeschreib                          |                  |           |      |     |      |    |  |  |  | 34 |

|   |      |                                              | lten             |           |      |     |      |    |  |  |  | 34 |

|   |      | 3.3.2 Black-Box- u                           | and Glass-Box-   | Sicht .   |      |     |      |    |  |  |  | 37 |

|   |      | 3.3.3 Realisierbark                          | keit eines Syste | ems       |      |     |      |    |  |  |  | 38 |

|   |      |                                              | erfeinerung      |           |      |     |      |    |  |  |  | 40 |

|   | 3.4  | Komposition von Sy                           |                  |           |      |     |      |    |  |  |  | 41 |

|   | 3.5  | Granzan das System                           |                  |           |      |     |      |    |  |  |  | 12 |

| 4 | Inte | gration                                    | aus formaler Sicht                                            | 43 |

|---|------|--------------------------------------------|---------------------------------------------------------------|----|

|   | 4.1  | Phase                                      | n der modularen Entwicklung                                   | 43 |

|   | 4.2  |                                            | disierung wichtiger Begriffe                                  | 44 |

|   |      | 4.2.1                                      | Fehler-Begriffe                                               | 44 |

|   |      | 4.2.2                                      | Architektur- und Integrationsfehler                           | 46 |

|   |      | 4.2.3                                      | Verbundfehler                                                 | 47 |

|   | 4.3  | Klassi                                     | fikation von Architekturfehlern                               | 48 |

|   |      | 4.3.1                                      | Abstraktionsebenen der Informationsdarstellung                | 48 |

|   |      | 4.3.2                                      | Interaktionseigenschaften                                     | 52 |

| 5 | Star | nd der                                     | Praxis                                                        | 55 |

|   | 5.1  | Archit                                     | ekturbeschreibung                                             | 55 |

|   |      | 5.1.1                                      | Typische Bestandteile der Architekturbeschreibung             | 56 |

|   |      | 5.1.2                                      | Bewertung der Architekturbeschreibungen                       | 59 |

|   | 5.2  | Softwa                                     | are-Entwicklungsprozesse                                      | 59 |

|   |      | 5.2.1                                      | Integrationslastige Entwicklung                               | 60 |

|   |      | 5.2.2                                      | Entwicklung durch Änderung – das Altmeisterprinzip            | 61 |

|   |      | 5.2.3                                      | Durchgängigkeit der Entwicklung                               | 62 |

|   |      | 5.2.4                                      | Abbildung der Organisationsstruktur auf die Systemarchitektur | 63 |

|   | 5.3  | rische Untersuchung von Architekturfehlern | 63                                                            |    |

|   |      | 5.3.1                                      | Erläuterung und Klassifizierung der ermittelten Fehlerdaten   | 64 |

|   |      | 5.3.2                                      | Ursachen für die Entstehung von Architekturfehlern            | 67 |

|   |      | 5.3.3                                      | Erkenntnisse aus den empirischen Fehlerdaten                  | 68 |

|   | 5.4  | Zusan                                      | nmenfassung                                                   | 69 |

| 6 | Anfo | orderun                                    | ngen an den Entwicklungsprozess zur Vermeidung von Architek-  |    |

|   | turf | ehlern                                     |                                                               | 71 |

|   | 6.1  | Durch                                      | gängigkeit des Entwicklungsprozesses                          | 71 |

|   |      | 6.1.1                                      | Hinreichende Architekturbeschreibung                          | 72 |

|   |      | 6.1.2                                      | Konsistente Schnittstellen in der Architekturbeschreibung     | 72 |

|   |      | 6.1.3                                      | Korrekte Verfeinerungsschritte über den Entwicklungsprozess   |    |

|   |      |                                            | hinweg                                                        | 73 |

|   | 6.2  | Konsis                                     | stenzsicherung bei Änderung eines bestehenden Systems         | 73 |

|   |      | 6.2.1                                      | Feingranulare Änderungserfassung                              | 74 |

|   |      | 6.2.2                                      | Propagieren von Änderungen                                    | 74 |

| 7 |      |                                            | tierte Maßnahmen zur Erkennung und Vermeidung von Archi-      |    |

|   |      | urfehle                                    |                                                               | 77 |

|   | 7.1  |                                            | von Maßnahmen                                                 | 77 |

|   | 7.2  | Analy                                      | tische Maßnahmen                                              | 78 |

|   |      | 7.2.1                                      | Reviews                                                       | 78 |

| В | Voll                 | ständig                          | es Listing zum AADL-Beispiel                                                                      | 117                  |

|---|----------------------|----------------------------------|---------------------------------------------------------------------------------------------------|----------------------|

| Α | Vorl                 | age zui                          | r Schnittstellenspezifikation                                                                     | 115                  |

| 9 | 9.1<br>9.2           | Zusam                            | nmenfassung                                                                                       |                      |

|   | 8.4                  |                                  | tung für die Entwicklung von Subsystemen                                                          |                      |

|   |                      | 8.3.4<br>8.3.5<br>8.3.6          | Externe Fehlerkosten                                                                              | . 107<br>. 109       |

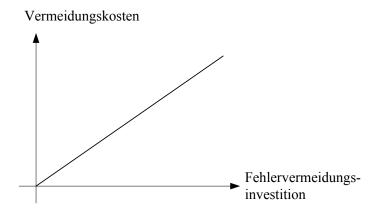

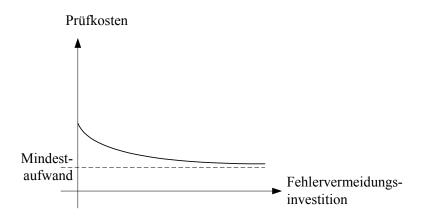

|   |                      | 8.3.1<br>8.3.2<br>8.3.3          | Vermeidungskosten                                                                                 | . 103<br>. 104       |

|   | 8.3                  | 8.2.1<br>8.2.2<br>Quant          | Vorteile von Fehlervermeidungsmaßnahmen                                                           | . 102                |

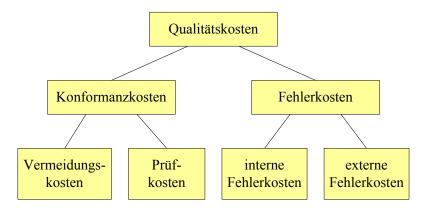

| 8 | <b>Kos</b> t 8.1 8.2 | Qualit<br>Qualit                 | maler Einsatz von Qualitätssicherungsmaßnahmen ät, Preis und Kosten                               | . 101                |

|   | 7.7                  | 7.6.2<br>Zusam                   | Erweiterung des Schnittstellen-Begriffs                                                           |                      |

|   | 7.6                  | 7.5.2                            | Wiederverwenden konsistenter Systemkonfigurationen re Unterstützung durch den Entwicklungsprozess | . 94<br>. 95         |

|   | 7.5                  | 7.4.1<br>7.4.2<br>Wiede<br>7.5.1 | Architekturbeschreibungssprachen (ADL) Spezifikationssprachen zur Schnittstellenbeschreibung      | . 89<br>. 93         |

|   | 7.4                  | 7.3.2<br>7.3.3<br>Umfas          | Statisches Scheduling                                                                             | . 82<br>. 83<br>. 83 |

|   | 7.3                  | 7.2.2<br>7.2.3<br>Verme<br>7.3.1 | Architekturverifikation                                                                           | . 80<br>. 81         |

# 1 Einleitung

#### 1.1 Motivation

Mit fortschreitender Technologie werden an das Automobil immer höhere Anforderungen gestellt. Bis 2010 soll die Zahl der Verkehrstoten in der EU halbiert $^1$  werden, die CO<sub>2</sub>-Diskussion fordert umweltschonendere Technologie und nicht zuletzt verlangt der Markt nach Innovation.

Um die ständig wachsenden Anforderungen erfüllen zu können, wird die technische Ausstattung der Automobile stetig verbessert: Das Antiblockiersystem (ABS) und das Elektronische Stabilitäts-Programm (ESP) sorgen für die größtmögliche Stabilität in schwierigen Fahrsituationen; Luftmassenmesser und Lambdasonden, welche die Zusammensetzung der Ansaug- bzw. Abgasluft messen, sorgen für eine präzise Regelung des Luft-Kraftstoff-Gemisches und erlauben so die Einhaltung der Abgasnormen; Komfortsysteme wie Adaptive Cruise Control (ACC), Klimaanlage und Multimediasysteme helfen, den Fahrer zu entlasten und den Insassen eine möglichst angenehme Fahrt zu bereiten.

Der intensive Einsatz von Elektrik und Elektronik im Automobil hat dazu geführt, dass in einem Kleinwagen mittlerweile ca. 20 Steuergeräte verbaut sind und in der Oberklasse bis zu 70. Der Mehrwert neuer Funktionalitäten liegt zunehmend im intelligenten Zusammenspiel, also der Vernetzung elektronischer Komponenten. Laut einer Studie der Boston Consulting Group [ZH04] werden 70% der künftigen Innovationen allein durch Software realisiert. Eine Mercer-Studie [Mer06] schätzt den Wert der elektrischen und elektronischen Bauteile samt Software weltweit betrachtet bereits auf einen Anteil von 20% am Gesamtwert eines Automobils. Bis 2015 soll dieser Anteil auf über 30% steigen. Die stark ansteigende Zahl an Funktionalitäten im Automobil sorgt für eine zunehmende Komplexität, selbst wenn die Anzahl der Steuergeräte künftig gleichbleibend oder gar rückläufig sein sollte.

Die starke Vernetzung der Steuergeräte birgt auch Risiken. Kleine Änderungen oder lokale Fehler können sich dadurch systemweit auswirken und eigentlich unabhängige Funktionen sich gegenseitig beeinflussen (Feature Interaction). Gerade Zeitanforderungen werden hier oft zum Problem.

<sup>&</sup>lt;sup>1</sup>Die Europäische Kommission hat eine Empfehlung an die EU herausgegeben, in den Jahren 2001 bis 2010 eine Halbierung der Zahl der Verkehrstoten zu erreichen. Im Jahr 2005 gab es 44900 Verkehrstote in der EU, davon 5361 in Deutschland (Quelle: Eurostat).

Das Handelsblatt [Han03] berichtete schon vor einigen Jahren, dass Fehler in der Elektronik für  $55\,\%$  der Ausfälle im Automobil verantwortlich sind. Die Hauptursache wird im mangelnden Zusammenspiel der Subsysteme verschiedener Zulieferer gesehen. Zudem ist in einem undurchschaubaren Systemverbund extrem schwer festzustellen, wo der Fehler liegt, und am Einzelgerät oft kein Fehler zu entdecken. Laut Boston Consulting Group [ZH04] sind  $50\,\%$  aller Fahrzeugrückrufe allein auf Softwarefehler zurückzuführen.

Bei der mittlerweile erreichten Vielzahl an Funktionalität im Automobil stoßen die bisherigen Qualitätssicherungsverfahren, die im Wesentlichen auf Reviews und intensiven Tests beruhen, an ihre Grenzen. Durch die gemeinsam genutzten Ressourcen genügt es nicht mehr, die Funktionen einzeln zu testen. Die Fehlersuche wird zusätzlich durch die Nebenläufigkeit der Subsysteme im verteilten System erschwert, da zeitlich bedingte Fehler meist nur schwer reproduzierbar sind. Ein unzureichendes Design macht die Integration der einzelnen Steuergeräte zu einem vernetzten Steuergeräteverbund zu einer zeit- und kostenintensiven Aufgabe [Bro06]. Noch verstärkt wird dies durch die im Automobilbereich auftretende Vielzahl an Funktions- und Ausstattungsvarianten.

Fehlerhaftes Zusammenspiel kann vielfältige Ursache haben und reicht von inkonsistenter Datendarstellung über unterschiedliche Zeitabstimmung bis hin zu unberücksichtigten Störeinflüssen zwischen zwei oder mehreren Subsystemen.

Bei heute eingesetzten Entwicklungsprozessen werden viele dieser Fehler erst bei der Integration des Systems entdeckt. Dabei sind die Fehler größtenteils nicht erst bei der Integration, d. h. in späten Entwicklungsphasen, entstanden. Auch die Überprüfung der einzelnen Steuergeräte gegenüber ihrer Spezifikation wird in der Regel ohne nennenswerten Fehlerbefund abgeschlossen. Dies lässt den Schluss zu, dass die Fehlerursachen schon in früheren Entwicklungsphasen zu suchen sind. Neuartige Vorgehensweisen sind notwendig, um das erfolgreiche Zusammenspiel der Komponenten von Anfang an sicherzustellen und damit die steigende Komplexität im Automobil zu beherrschen.

# 1.2 Eigener Lösungsansatz im Überblick

Diese Arbeit zeigt auf, welche typischen Integrationsprobleme aktuell in der Praxis vorkommen und schlägt entsprechende Abhilfemaßnahmen vor, die eine Erkennung bzw. Vermeidung der Fehlerursachen schon in frühen Entwicklungsphasen ermöglichen.

Der Aufbau der Arbeit ist zweigeteilt. Im theoretischen Teil wird die Systemintegration auf formaler Basis untersucht. Zwei Integrationsebenen stehen dabei im Vordergrund:

• Der Steuergeräteverbund als Integration mehrerer, nebenläufiger Steuergeräte, die über einen Datenbus kommunizieren.

• Ein Steuergerät als Integration von Softwaretasks, Betriebssystem und Steuergeräte-Hardware. Die Tasks sind wiederum (weitgehend) nebenläufig und kommunizieren über den gemeinsamen Arbeitsspeicher.

Im empirischen Teil der Arbeit wird der Stand der Praxis in der Entwicklung eingebetteter Systeme im Automobilbereich untersucht. Speziell werden Software-Entwicklungsprozesse und die Beschreibung von Architekturen im Hinblick auf integrationsrelevante Aspekte hin betrachtet.

Nach einer Einführung in die Thematik der Systemintegration (Kapitel 2) wird als Grundlage für die weitere Arbeit ein formales Systemmodell eingeführt (Kapitel 3). Mit dessen Hilfe lassen sich das Problem der Integration und zentrale Begriffe in dieser Arbeit formal charakterisieren sowie in wichtige Fehlerklassen unterteilen (Kapitel 4).

Eine Analyse empirischer Fehlerdaten zeigt, welche Integrationsprobleme aktuell in der Praxis auftreten und greift die zuvor eingeführte Fehlerklassifikation auf, um die große Spannweite der Fehlerursachen darzustellen (Kapitel 5).

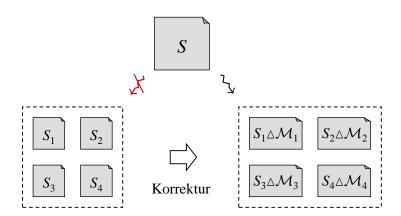

Im Hinblick auf die Erkennung und Vermeidung von Integrationsproblemen werden im nächsten Schritt Anforderungen an den Entwicklungsprozess aufgestellt, die hinreichend für die Erstellung integrierbarer Systeme sind. Dabei wird neben der Neuentwicklung von Systemen auch die im Automobilbereich dominierende, änderungsgetriebene Entwicklung berücksichtigt, bei der wichtig ist, dass nach jeder Änderung wieder ein integrierbarer Systemzustand erreicht wird (Kapitel 6).

Zur Erfüllung dieser Prozessanforderungen in der Praxis werden ausgewählte Maßnahmen aus den Bereichen Prozesse, Spezifikationssprachen und Werkzeuge untersucht. Neben dem Nutzen, also der potenziellen Erkennung oder Vermeidung von Integrationsproblemen, ist auch der damit einhergehende Aufwand für den praxistauglichen Einsatz einer Maßnahme von entscheidender Bedeutung (Kapitel 7).

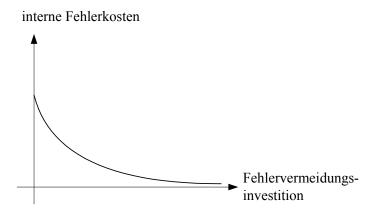

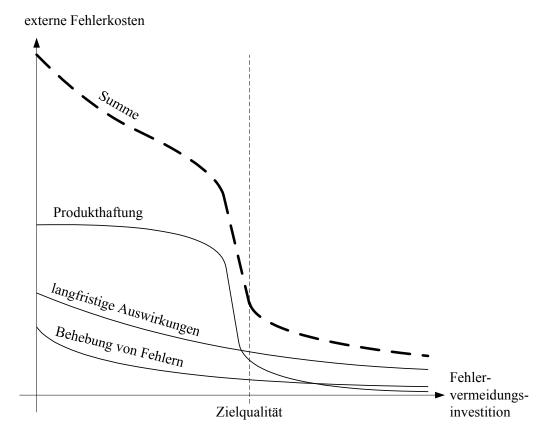

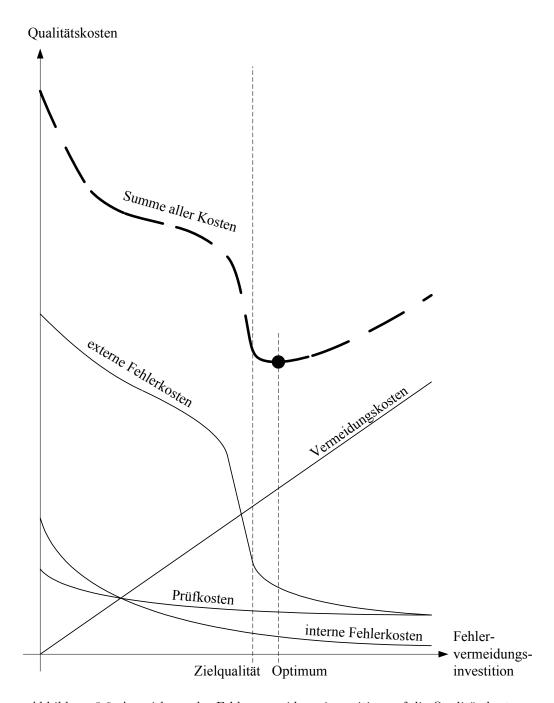

Das Vorgehen, Integrationsprobleme schon in frühen Entwicklungsphasen zu erkennen und zu vermeiden, verspricht eine hohe Produktqualität per Konstruktion. Doch nicht immer ist dieser Ansatz dem herkömmlichen Vorgehen, intensiv zu testen und gefundene Fehler zu beseitigen, überlegen. Letztlich entscheiden ökonomische Aspekte, welche Investition in Fehlervermeidungsmaßnahmen langfristig optimal ist (Kapitel 8).

# 2 Systemintegration im Automobil

#### 2.1 Umfeld

Viele Faktoren sind dafür verantwortlich, dass Subsysteme später problemlos integriert werden können und das dadurch entstehende System einwandfrei funktioniert. Neben technischen Faktoren wie richtig gesetzten Bohrlöchern, niedrigem Schwingungsverhalten und passenden Schraubengewinde sind auch elektrische und elektronische Faktoren wie geringe Schwankungen der Versorgungsspannung, richtige Polung der Anschlüsse und ein passendes Kommunikationsprotokoll von entscheidender Bedeutung. Eine Schlüsselrolle spielt dabei die Software, in der immer mehr Teile der Systemfunktionalität realisiert sind. Für die Untersuchung von Fehlern bezüglich funktionaler Anforderungen in der Systemintegration sind vor allem eingebettete Systeme und die darin enthaltene Software zu betrachten. Im Hinblick auf die Vermeidung von Integrationsproblemen kommt den frühen Entwicklungsphasen eine besondere Bedeutung zu. Dieser Abschnitt erläutert das Umfeld dieser Arbeit.

## 2.1.1 Eingebettete Systeme und deren Zusammenspiel

#### Definition 2.1 (Eingebettete Systeme)

Eingebettete Systeme sind Software-/Hardwaresysteme, die als Teil eines größeren Systems für den Benutzer verborgen arbeiten, aber für die Funktions- und Leistungsfähigkeit des Gesamtsystems entscheidend sind. Ihre Aufgabe besteht darin, eine Anzahl technischer Geräte und physikalischer Prozesse der Umgebung zu überwachen und/oder gemäß einer definierten Funktionalität über Sensoren und Aktoren zu steuern und zu regeln [FGP04]. □

Die im Automobil eingesetzten eingebetteten Systeme werden auch als *Electronic Control Unit* (ECU) oder *Steuergerät* bezeichnet. Sie zeichnen sich durch folgende Eigenschaften aus (in Anlehnung an [Jaz98]):

echtzeitfähig Für die korrekte Funktionalität ist nicht nur die Ausgabe des korrekten Ergebnisses erforderlich, sondern zusätzlich muss die Reaktion innerhalb vorgegebener Zeitschranken erfolgen. Gerade bei Regelungsaufgaben wie dem Antiblockiersystem (ABS) ist diese Eigenschaft essenziell.

- **nebenläufig** Jedes Steuergerät besitzt einen eigenen Prozessor und hat einen eigenen, internen Rechentakt. Die eingebetteten Systeme arbeiten daher nebenläufig, die Kommunikation untereinander erfolgt asynchron.

- Massenprodukt Automobile werden in der Regel in hoher Stückzahl hergestellt. Daher sind geringer Produktionsaufwand und niedrige Materialkosten sehr wichtig. Für die eingebetteten Systeme bedeutet das, dass sie möglichst geringe Stückkosten haben müssen.

- beschränkte Ressourcen Aufgrund möglichst niedriger Stückkosten sind die durch die Hardware bereitgestellten Ressourcen sehr beschränkt. Das bedeutet insbesondere einen kleinen Arbeitsspeicher, wenig Rechenleistung und eine geringe Bandbreite zur Kommunikation zwischen Steuergeräten.

- wartungsfrei Die eingebetteten Systeme im Automobil sind auf wartungsfreien<sup>1</sup> Betrieb ausgelegt. Nur in Ausnahmefällen bedarf es eines manuellen Eingriffs.

- Funktionalität in Software Die wesentliche Verhaltenslogik eines eingebetteten Systems ist in Software implementiert. Sie wird im Flash- oder ROM-Speicher abgelegt. Software ist leicht austauschbar und verursacht aufgrund ihres immateriellen Charakters praktisch keine Vervielfältigungskosten.

- vorab festgelegte Funktionalität und Umgebung Die Funktionalität des eingebetteten Systems und die Umgebung, in die es eingebettet ist, sind bereits zur Entwurfszeit festgelegt. Nur in Ausnahmefällen wird die technische Architektur eines Fahrzeugs im Feld nachträglich verändert. Selbst der nachträglich Einbau von Zubehör ist bereits zur Entwurfszeit eingeplant. Darüber hinausgehende Eingriffe sind von Herstellerseite nicht erwünscht und können zum Erlöschen der Betriebserlaubnis und des Gewährleistungsanspruchs führen.

- einfache Datenstrukturen und Kommunikationsabläufe Die Kommunikation zwischen eingebetteten Systemen erfolgt typischerweise mittels relativ einfacher Datenstrukturen. Diese bestehen aus primitiven Datentypen (z.B. uint8, int16, bool) und zusammengesetzten Datentypen. Komplexe Datenstrukturen wie Ströme oder serialisierte Objekte, die sich über mehrere Nachrichtenpakete erstrecken, treten typischerweise nur im Multimediaverbund auf. Die Kommunikation zwischen eingebetteten Systemen verwendet schlanke Protokolle, auf Verbindungsorientierung und Sessions wird verzichtet. Die Komplexität liegt v.a. in der Algorithmik der eingebetteten Systeme.

<sup>&</sup>lt;sup>1</sup>Anmerkung zum Begriff *Wartung*: Die Norm VDI 2896 [VDI94] definiert Wartung als "Maßnahmen zur Bewahrung des Sollzustandes von technischen Mitteln eines Systems". Hierbei wird davon ausgegangen, dass das System bereits vor der Wartung korrekt funktioniert hat. Im Unterschied dazu wird bei Software unter Wartung die Änderung der Software zur Korrektur von Fehlern, Funktionserweiterung oder Anpassung verstanden (ISO/IEC 12207 [ISO95]).

Die Realisierung vieler Funktionen mittels elektronischer Steuergeräte ermöglicht es, diese auf einfache Weise untereinander zu vernetzen. Dadurch wird ein Potential geschaffen, das ganz neue, bisher unbekannte Funktionalitäten erlaubt. Dies wird in der Praxis immer häufiger genutzt. Der Mehrwert neuer Funktionalitäten liegt zunehmend im intelligenten Zusammenspiel mehrerer Subsysteme. Eine Vernetzung findet dabei sowohl zwischen den Steuergeräten als auch zwischen den Softwaremodulen und Tasks innerhalb eines Steuergeräts statt.

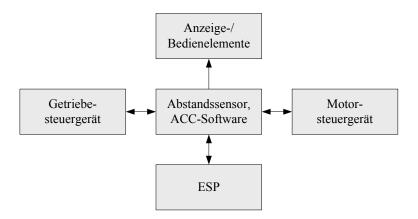

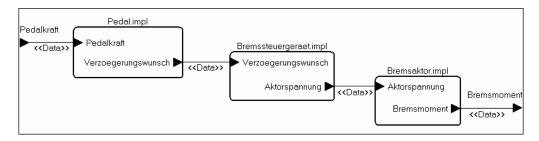

Ein typisches Beispiel für eine Verbundfunktionalität ist Adaptive Cruise Control (ACC) – ein Tempomat mit Abstandsregelung zum vorausfahrenden Fahrzeug. Es verbindet einen Abstandssensor mit dem Bremssystem (üblicherweise angesteuert durch das Elektronische Stabilitäts-Programm (ESP)), der Motorsteuerung, der Getriebesteuerung und den Anzeige- und Bedienelementen. Die Beschleunigung des Fahrzeugs erfolgt über eine Erhöhung des Motormoments, die Verzögerung des Fahrzeugs über das Schleppmoment des Motors und bei Bedarf zusätzlich über einen Bremseingriff. Das Getriebesteuergerät gibt Aufschluss über das momentane Übersetzungsverhältnis zwischen Motor- und Raddrehzahl und damit über die Beschleunigungswirkung einer Motormomentveränderung. Abbildung 2.1 zeigt den ACC-Verbund schematisch. Weitere Informationen sind in [Bos02, Bos07] zu finden.

Abbildung 2.1: ACC als Verbund mehrerer Subsysteme. Die Pfeile geben den Informationsfluss bei einem aktiven ACC-System an.

Aber nicht nur Funktionen werden gemeinsam genutzt, sondern auch Ressourcen wie Rechenzeit, Arbeitsspeicher und Kommunikationsverbindungen. Heutige Bussysteme ersetzen eine Vielzahl an Verbindungskabeln und helfen so, den Kabelbaum im Automobil in Volumen und Gewicht enorm zu reduzieren.

#### 2.1.2 Softwarebedingte Fehler

Der Großteil der Funktionalität eines Steuergeräts ist in Software implementiert. Tritt ein Fehler auf, ist die Ursache daher meistens auch in der Software zu suchen bzw. kann durch Änderung der Software behoben werden. In dieser Arbeit werden daher vorwiegend softwarebedingte Fehler untersucht, d. h.

- Fehler in einer Software-Komponente,

- Interaktionsfehler zwischen Software-Komponenten,

- Interaktionsfehler zwischen Software und Hardware sowie

- Verhaltensfehler in der Hardware, soweit sie das Verhalten des eingebetteten Systems beeinflussen.

Der Begriff des Fehlers wird in Abschnitt 2.2 genauer beschrieben.

#### 2.1.3 Frühe Entwicklungsphasen

Um Fehler aus der Sicht des Entwicklungsprozesses zu behandeln, zu beheben oder zu vermeiden, kommen grundsätzlich folgende Möglichkeiten in Betracht.

- Fehlervermeidung während der Entwicklung Während der Entwicklung werden Vorkehrungen getroffen, so dass Fehler gar nicht erst entstehen können.

- Fehlerbehebung während der Entwicklung Im Entwicklungsprozess wird darauf geachtet, dass entstandene Fehler möglichst schnell gefunden und behoben werden.

- Autonome Fehlerbehandlung zur Laufzeit Die zur Laufzeit unvermeidlichen physikalischen Störeinflüsse auf das System (beispielsweise elektromagnetische Einstrahlung, Erschütterung und Wärme) können auch bei einem funktional fehlerfreien System zu einem falschen Systemverhalten führen. Mittels Fehlertoleranzmechanismen (siehe [TS03, Ech90]) lassen sich solche Fehler abmildern und manchmal sogar vollständig kompensieren. Neben physikalischen Störeinflüssen können damit teilweise auch Fehler, die trotz sorgfältiger Entwicklung im Produkt vorhanden sind, behandelt werden.

- **Fehlerbehebung zur Laufzeit** Hier wird ein System durch Eingriff von außen (z. B. durch die Werkstatt) verändert. Damit lassen sich während der Laufzeit defekt gewordene Subsysteme und auch solche, die bereits seit der Entwicklung fehlerhaft sind, durch fehlerfreie ersetzen oder reparieren.

Bezüglich der Erkennung und Vermeidung von Fehlern ergibt sich daraus eine Vielzahl an methodischen Ansatzpunkten. Häufig sind Produktfehler auf ein unzureichendes Design zurückzuführen, das die Architektur und die Interaktion zwischen den Subsystemen nicht ausreichend präzise beschreibt. Diese Fehler hätten also schon in frühen Entwicklungsphasen, d. h. bei der Erstellung der Systemspezifikation und des Designs, gefunden oder gar vermieden werden können. Daher untersucht diese Arbeit bezüglich der Erkennung und Vermeidung von Fehlern speziell die frühen Entwicklungsphasen. Der Schwerpunkt liegt dabei auf der Fehlervermeidung während der Entwicklung. Prinzipiell gehört dazu auch die autonome Fehlerbehandlung zur Laufzeit, da es sich hierbei um Mechanismen im Produkt handelt, die ebenfalls schon in frühen Entwicklungsphasen zu berücksichtigen sind. Auf physikalische Störeinflüsse und deren Beherrschung wird in dieser Arbeit ebenfalls eingegangen, sie spielen aber nur eine untergeordnete Rolle und werden wie die Fehlertoleranzmechanismen nur am Rande behandelt.

## 2.2 Der Fehler-Begriff

Da in dieser Arbeit häufig von Fehlern gesprochen wird, soll der Begriff zunächst genauer definiert werden. Eine formale Definition wird später in Abschnitt 4.2.1 gegeben.

In der Literatur ist der Begriff des Fehlers nicht einheitlich festgelegt und wird in unterschiedlichen Bedeutungen verwendet. In deutschen Texten findet man Begriffe wie Fehler, Ausfall, Versagen und Fehlerursache, während in der englischsprachigen Literatur Begriffe wie error, fault, bug und failure zu lesen sind. Diese Begriffe lassen sich nicht unmittelbar einander zuordnen. Beispielsweise werden error und bug meist als Fehler übersetzt, wohingegen failure im Deutschen in Ausfall und Versagen unterschieden wird [Lap92, IEE90]. Der Fehler-Begriff in dieser Arbeit richtet sich nach [Lap92].

Allen im Folgenden verwendeten Fehler-Begriffen liegt folgende Definition des Begriffs Fehler zu Grunde:

#### Definition 2.2 (Fehler)

Ein Fehler ist eine Abweichung zwischen Soll und Ist.

Wesentlich ist dabei, dass ein Fehler nur dann festgestellt werden kann, wenn es eine – als richtig angesehene – Soll-Vorgabe gibt. Nur wenn Soll und Ist nicht übereinstimmen, liegt ein Fehler vor. Eine Soll-Vorgabe muss nicht notwendigerweise schriftlich vorliegen. Es kann auch mehrere Soll-Vorgaben geben, wobei dann klar sein muss, auf welche sich der Fehler-Begriff bezieht. Abschnitt 2.4 vertieft diesen Aspekt.

#### Fehlerursache und -wirkung

Im Folgenden wird der Fehler-Begriff weiter differenziert in Fehlerursache, Fehlzustand und Versagen. Dadurch lässt sich besser verdeutlichen, auf welche Eigenschaft eines Systems man sich konkret bezieht.

#### Definition 2.3 (Fehlerursache (engl. fault))

Eine Fehlerursache ist eine Abweichung des tatsächlichen vom beabsichtigten Aufbau eines Produkts.

#### Definition 2.4 (Fehlzustand (engl. error))

Ein Fehlzustand oder auch  $fehlerhafter\ Zustand$  liegt vor, wenn ein Produkt in einen nicht beabsichtigten internen Zustand übergeht.

#### Definition 2.5 (Versagen (engl. failure))

Ein Versagen oder auch fehlerhaftes Verhalten ist ein von der Spezifikation abweichendes, nach außen sichtbares Verhalten eines Produkts.

Ein Versagen bezieht sich auf das Eingabe-Ausgabe-Verhalten eines Produkts. Verhält sich das Produkt nicht gemäß einer bestimmten Spezifikation, so liegt ein Versagen vor. Eine *Spezifikation* eines Produkts ist dabei eine Beschreibung der erwarteten Funktionen und/oder Leistungen und die Bedingungen, unter denen sie zu erbringen sind [Lap92].

Damit ein Versagen auftreten kann, muss ein Fehlzustand vorliegen, d. h. das Produkt befindet sich in einem nicht beabsichtigten internen Zustand. Führt der Fehlzustand zu einer falschen Ausgabe und wird so für die Umgebung des Produkts sichtbar, so spricht man von einem Versagen. Das Vorliegen eines Fehlzustands muss aber nicht in jedem Fall zu einem Versagen führen. Durch den Einsatz von Fehlertoleranzverfahren wird versucht, einen Fehlzustand rechtzeitig zu erkennen und in einen beabsichtigten internen Zustand überzuführen, um dadurch ein Versagen zu vermeiden.

Ebenso verhält es sich zwischen Fehlerursache und Fehlzustand. Damit ein Fehlzustand auftreten kann, muss eine Fehlerursache, also eine Abweichung im Aufbau des Produkts, vorliegen. Führt eine Fehlerursache zu einem Fehlzustand, spricht man von einer aktivierten Fehlerursache. Das Vorhandensein einer Fehlerursache muss aber nicht in jedem Fall zu einem Fehlzustand führen.

Beispiel 2.1 Betrachtet man ein Softwaremodul, so wäre eine Codezeile, in der ein Operator + mit - vertauscht wurde, eine Fehlerursache. Kommt das Modul zur Ausführung, kann diese Codezeile zu einem falschen Zwischenergebnis führen, also einer falschen Variablenbelegung, einem Fehlzustand. Wenn das falsche Zwischenergebnis zur Ausgabe eines Ergebnisses verwendet wird und so als falsche Antwort an die Umgebung des Moduls sichtbar wird, liegt ein Versagen des Moduls vor.

Fehlerursache, Fehlzustand und Versagen beschreiben eine nach beiden Seiten offene Fehlerfortpflanzungskette [Lap92, ALRL04]. Jede Fehlerursache kann als Auswirkung und damit Versagen einer zeitlich davor liegenden Ursache aufgefasst werden. Ebenso kann jedes Versagen die Ursache für ein weiteres Versagen (also eines Folgefehlers) sein. Beispielsweise kann das Versagen einer Komponente als Ursache für das Versagen des gesamten Systems gesehen werden.

```

\begin{array}{c} \cdots \to \text{Fehlerursache} \xrightarrow{\text{erzeugt}} \text{Fehlzustand} \xrightarrow{\text{wird sichtbar als}} \text{Versagen} \xrightarrow{\text{fungiert als}} \\ \to \text{Fehlerursache} \to \cdots \end{array}

```

Häufig unterscheidet man zusätzlich zwischen Versagen und Ausfall, siehe [Gra07]. Dabei ist Ausfall ein Spezialfall von Versagen: Von einem Ausfall eines Produkts spricht man, wenn es (vorübergehend) die Fähigkeit verliert, eine vorgegebene Funktionalität zu erbringen. Der Ausfall geht also immer mit einer Veränderung des Produkts einher, die entweder temporär (z. B. durch Überhitzung) oder permanent (z. B. durch Kabelbruch) vorliegt. Im Zusammenhang mit Software spricht man nur von Versagen, weil Software ein logisches Konstrukt ist und keinen physikalischen Einflüssen unterliegt, also insbesondere sich nicht abnutzt.

Weiter gehende Unterteilungen des Fehler-Begriffs finden sich beispielsweise in [Lap92, ALRL04, Mar03]. Der Begriff Fehler selbst wird künftig als Oberbegriff oder stellvertretend für eine der genannten Fehlerarten verwendet, wenn die Bedeutung aus dem Zusammenhang klar hervorgeht.

# 2.3 Grundidee der Integration

Dieser Abschnitt erläutert die Grundidee der Integration und definiert Fehler, die in diesem Zusammenhang auftreten können. Eine entsprechende formale Darstellung dazu wird später in den Abschnitten 4.1 und 4.2.2 angegeben.

#### 2.3.1 Modulare Entwicklung

Das Automobil ist ein klassisches Beispiel für eine modulare Entwicklung. Die Systemspezifikation wird zunächst zerlegt in viele einzelne Module, die von verschiedenen Zulieferern entwickelt, gefertigt und geliefert werden. Bei der Integration werden die Module vom OEM schließlich zum Gesamtsystem zusammengebaut, d. h. integriert.

Dazu einige Begriffsdefinitionen:

#### Definition 2.6 (System)

Ein System ist eine Einheit, die mit ihrer Umgebung, d. h. anderen Systemen, kommuniziert. Ein System kann z. B. ein Stück Software, Hardware, eine Person oder die

physikalische Welt sein. Die gemeinsame Grenze zwischen einem System und seiner Umgebung wird Systemqrenze genannt.<sup>2</sup>

In dieser Arbeit wird nicht zwischen System, Modul, Komponente und Produkt unterschieden. Der Begriff System dient hier als gemeinsamer Oberbegriff.

#### Definition 2.7 (Subsystem)

Ein Subsystem ist ein System, welches Bestandteil eines (übergeordneten) Systems ist. Der Begriff Subsystem wird verwendet, um auf eine ist-Teil-von-Beziehung zwischen einem System und seinem übergeordneten System hinzuweisen.

Ein Subsystem kann entweder wiederum hierarchisch zusammengesetzt sein oder eine nicht mehr sinnvoll weiter zerlegbare Einheit darstellen.

#### Definition 2.8 (Architektur)

Eine Architektur eines Systems ist gegeben durch eine Menge von Subsystemen zusammen mit den Kommunikationsverbindungen zwischen den Subsystemen.

#### Definition 2.9 (Integration)

Integration (oder Systemintegration) ist das Zusammenfügen mehrerer realisierter Subsysteme zu einem System.  $\Box$

Wendet man die Idee der Integration auf Spezifikationen an und vereint die Subsystemspezifikationen, um damit beispielsweise Eigenschaften des gesamten Systems vorherzusagen, so spricht man von *virtueller Integration*. Dieses Vorgehen findet bei der modellbasierten Entwicklung Anwendung.

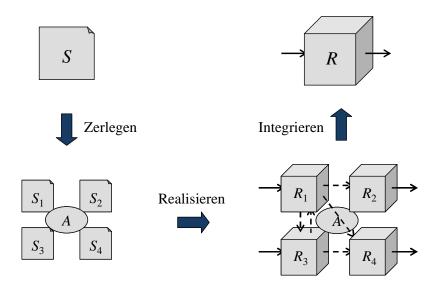

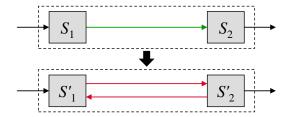

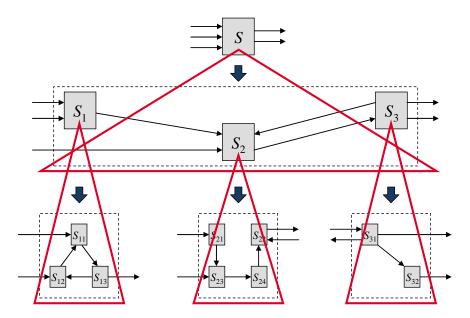

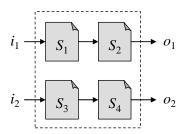

Abbildung 2.2 stellt die modulare Entwicklung eines Systems schematisch dar. Ausgangspunkt ist eine Systemspezifikation S. Diese wird zerlegt in mehrere Subsystemspezifikationen  $S_i$  zusammen mit einer Architekturbeschreibung A, die das Zusammenspiel der Subsysteme beschreibt. Die einzelnen Subsysteme werden dann unabhängig voneinander erstellt und es entsteht jeweils eine Realisierung  $R_i$ . Anschließend werden die Subsysteme gemäß Architekturbeschreibung A zum System R integriert.

Die modulare Entwicklung wird in der Regel dazu genutzt, ein komplexes System in mehrere weniger komplexe Subsysteme – hier Module genannt – zu zerlegen und diese arbeitsteilig zu entwickeln und zu produzieren.

Ist ein zu realisierendes Subsystem  $S_i$  recht komplex, kann die Idee der modularen Entwicklung selbstverständlich erneut angewendet und  $S_i$  in weitere Subsysteme zerlegt werden.

<sup>&</sup>lt;sup>2</sup>Der hier verwendete Systembegriff entspricht dem in [ALRL04].

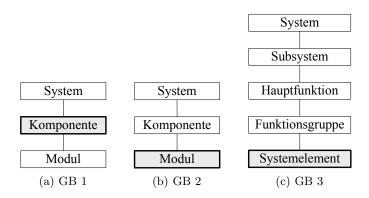

Abbildung 2.2: Schematische Darstellung der modularen Entwicklung

#### 2.3.2 Architektur- und Integrationsfehler

Das Ziel der Integration ist, das fehlerfreie Zusammenspiel der Subsysteme zu gewährleisten. Im Vordergrund steht dabei ein fehlerfreies Zusammenspiel aus Architektursicht und weniger aufgrund der Korrektheit der einzelnen, beteiligten Subsysteme. Unter einem Integrationsproblem wird allgemein ein Fehler, der beim Zusammenspiel der Subsysteme beobachtet wird, verstanden (siehe Kapitel 1). Im Hinblick auf die Fehlerursache sollen im Folgenden die Begriffe Architekturfehler und Integrationsfehler unterschieden werden.

#### Definition 2.10 (Architekturfehler)

Ein Architekturfehler ist eine fehlerhafte Zerlegung einer Systemspezifikation, d. h. die durch die Zerlegung entstandene Architektur stimmt nicht mit der Systemspezifikation überein.

#### Definition 2.11 (Integrationsfehler)

Ein *Integrationsfehler* ist eine fehlerhafte Integration eines Systems, d. h. das durch die Integration entstandene System stimmt nicht mit der Architekturbeschreibung überein.

Gemäß Abbildung 2.2 liegt ein Architekturfehler vor, wenn beim Zerlegen der Systemspezifikation ein Fehler entsteht, und ein Integrationsfehler, wenn beim Integrieren der Subsystemrealisierungen zum System ein Fehler entsteht.

Der Grundstein für die Integration wird bereits zu dem Zeitpunkt gelegt, zu dem die Subsysteme des Systems identifiziert werden. Teilweise sind einige Subsysteme

bereits in den Anforderungen festgelegt, andere entstehen erst mit den Architekturentscheidungen in der Designphase und später. Ein typisches Beispiel für einen Architekturfehler ist ein Kommunikationsproblem zwischen zwei Subsystemen aufgrund unterschiedlicher Bitdarstellung der ausgetauschten Information.

Auch während der Integration, also des Zusammensetzens des Systems aus seinen Einzelbestandteilen, können Fehler entstehen. Beispielsweise können Subsysteme vergessen, falsche Subsystemversionen verwendet oder Verbindungskabel zwischen Subsystemen falsch angeschlossen werden.

Nicht betrachtet werden Fehler bei der Realisierung einzelner Subsysteme, da diese nicht explizit die Architektur betreffen.

Diese Arbeit konzentriert sich auf die Erkennung und Vermeidung von Architekturfehlern, da bereits in frühen Entwicklungsphasen ein großer Einfluss auf die spätere Integration besteht und hier gemachte Fehler in nachfolgenden Entwicklungsphasen nur noch schwer auszugleichen sind.

## 2.4 Fehlerlokalisierung im Entwicklungsprozess

Im zeitlichen Verlauf des Entwicklungsprozesses können Fehler in verschiedenen Entwicklungsphasen entstehen. Abhängig von der Sicht des Betrachters kann ein Fehler unterschiedlich ausgelegt werden, wenn der zugehörige Referenzpunkt, d. h. das Soll gemäß Definition 2.2 des Fehlerbegriffs, nicht einheitlich ist. Dieser Abschnitt erklärt, woher Fehler kommen, welche Fehler es in den unterschiedlichen Entwicklungsphasen geben kann und wie man mit unvollständigen Spezifikationen umgehen kann.

#### 2.4.1 Tatsächliche und ideale Artefakte

Während der Entwicklung eines Produkts werden mehrere Zwischenprodukte, hier als tatsächliche Artefakte bezeichnet, erstellt und weiter verwendet. Betrachtet am Modell der modularen Entwicklung gehören dazu die tatsächliche Spezifikation, die tatsächliche Architektur, die tatsächliche Realisierung der einzelnen Subsysteme und das tatsächliche System.

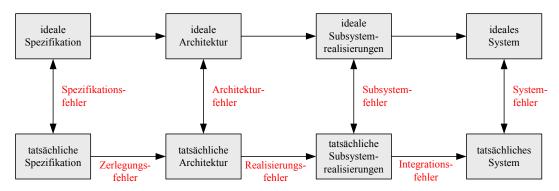

Die Feststellung, ob ein Artefakt fehlerfrei ist, erfordert einen Vergleich zwischen einem tatsächlichen Artefakt und einem Referenzartefakt, hier als *ideales Artefakt* bezeichnet. Ideale Artefakte sind die ideale Spezifikation, die ideale Architektur, ideale Subsystemrealisierungen und das ideale System. Ein Fehler liegt vor, wenn ein tatsächliches Artefakt von einem als korrekt angesehenen idealen Artefakt abweicht, d. h. die Verfeinerungsbeziehung nicht gilt. Konkret spricht man von einem *Spezifikationsfehler*, wenn die tatsächliche Spezifikation von der idealen abweicht. Analoges gilt für *Architekturfehler*, *Subsystemfehler* und *Systemfehler*.

Die idealen Artefakte sind in der Regel nicht eindeutig vorgegeben, sondern müssen ausgewählt werden, um eine Abweichung zwischen einem konkreten Produkt und der entsprechenden Idealvorstellung ausdrücken zu können. Zwischen den idealen Artefakten, die man in einem konkreten Fall ausgewählt hat, wird man sinnvollerweise eine gewisse Kompatibilität verlangen, insbesondere die Korrektheitsbeziehungen gemäß der modularen Entwicklung aus Abschnitt 4.1. Somit ist die Wahlfreiheit der idealen Artefakte auf die möglichen Verfeinerungsbeziehungen, ausgehend von der idealen Spezifikation, eingeschränkt. Die idealen Artefakte sollen im Folgenden automatisch alle geforderten Eigenschaften erfüllen, was durch das Adjektiv *ideal* bereits suggeriert wird.

Neben der Abweichung von den idealen Artefakten können auch die Übergänge zwischen den tatsächlichen Artefakten fehlerbehaftet sein. Die entsprechenden Fehlerbegriffe sind Zerlegungsfehler, Realisierungsfehler und Integrationsfehler. Abbildung 2.3 zeigt eine Übersicht über die genannten Artefakte und die zugehörigen Fehlerbegriffe. Entsprechend dem üblichen Sprachgebrauch wird im Folgenden nicht unterschieden zwischen Architekturfehler und Zerlegungsfehler. Falls für das Verständnis erforderlich, wird im Einzelfall angegeben, welchem Artefakt die tatsächliche Architektur gegenübergestellt wird.

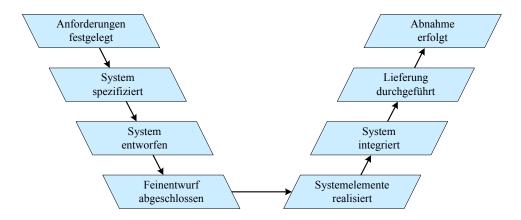

Abbildung 2.3: Ideale und tatsächliche Artefakte im Entwicklungsprozess mit Einordnung der Fehlerbegriffe

#### 2.4.2 Mentale Artefakte

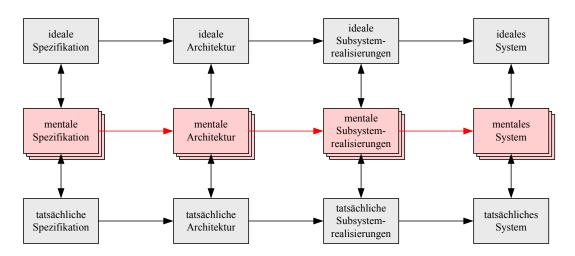

Obwohl die idealen Artefakte oft nicht explizit bekannt sind, glauben die Entwickler mehr oder weniger genau zu wissen, was zu entwickeln ist und wie das Ergebnis am Schluss auszusehen hat. Der Grund dafür sind gedankliche Modelle in den Köpfen der Entwickler, sog. mentale Artefakte. Sie treten an die Stelle der idealen Artefakte und bilden für die Entwickler die Grundlage für die Feststellung, ob ein Fehler vorliegt oder nicht (Abbildung 2.4).

Jeder Entwickler verfügt über ein eigenes mentales Modell. Die mentalen Artefakte stimmen in der Praxis nie exakt mit den fiktiven idealen Artefakten überein, sie

Abbildung 2.4: Einfluss der mentalen Artefakte der Entwickler

spiegeln eher die subjektive Einschätzung des Entwicklers wider. Diese ist geprägt von persönlicher Erfahrung, eigener Intuition und implizit getroffenen Annahmen ("nach bestem Wissen und Gewissen"). Eine Gefahr ist dabei, dass mehrere Entwickler, die häufig noch dazu in ganz unterschiedlichen Domänen mit unterschiedlichem Begriffsverständnis arbeiten, zu deutlich von einander abweichenden Vorstellungen über das ideale System kommen können, d. h. sich deren mentale Artefakte stark unterscheiden. Nach arbeitsteiliger Entwicklung der Subsysteme stellt man dann bei der Integration fest, dass die realisierten Subsysteme gar nicht zusammenpassen. Aber auch wenn die mentalen Artefakte mehrerer Entwickler weitgehend gleich sein sollten, lässt sich daraus nichts über die Übereinstimmung mit den idealen Artefakten ableiten.

Die mentalen Artefakte bilden sich oft auf der Grundlage der vorhandenen Spezifikationen. Die Gefahr für große Abweichungen zwischen den mentalen Artefakten ist besonders dann recht hoch, wenn die Spezifikationen unvollständig sind, denn in diesem Fall gibt es einen größeren Interpretationsspielraum. Abhilfe schaffen kann nur eine präzisere Spezifikation oder zumindest eine Abstimmung unter den Entwicklern.

Die mentalen Artefakte können das Ergebnis eines Entwicklungsprozesses in der Praxis sehr stark beeinflussen. Für die objektive Bestimmung von Fehlern ist jedoch immer das jeweilige ideale Artefakt entscheidend. Daher wird bei der Fehlerklassifizierung in dieser Arbeit versucht, das ideale Artefakt zu schätzen.

# 3 Grundlagen: Formales Systemmodell

In diesem Kapitel wird ein formales Systemmodell vorgestellt, mit dessen Hilfe sich die Struktur und das Verhalten von Netzwerken eingebetteter Systeme beschreiben lassen. Es stellt die Grundlage für die nachfolgenden Kapitel dar und ermöglicht insbesondere eine formale Definition des Fehlerbegriffs sowie die Formulierung formaler Korrektheitseigenschaften von Entwicklungsprozessen.

## 3.1 Überblick

Das im Folgenden betrachtete Systemmodell basiert auf der Methodik Focus [BS01]. Es weicht nur an wenigen Stellen davon ab, was dann jeweils im Detail beschrieben wird. Dieses Kapitel geht im Wesentlichen nur auf die in dieser Arbeit verwendeten Bestandteile des Systemmodells ein.

Focus wurde als Ansatz gewählt, weil es die folgenden Merkmale zur Beschreibung von Systemen besonders gut unterstützt:

- Vollständige, funktionale Beschreibung von digitalen Systemen,

- Darstellung des Zeitverhaltens, insbesondere der Nebenläufigkeit,

- modulare Entwicklung,

- klare Semantik von Systemen,

- zustandslose Beschreibung von Systemen (Black-Box-Sicht) sowie

- Nichtdeterminismus.

Nach einer Einführung in die Repräsentation von Daten und Zeit mittels Strömen im folgenden Abschnitt stellt Abschnitt 3.3 die Verhaltensbeschreibung mittels Relationen zwischen Ein- und Ausgabeströmen vor. In Abschnitt 3.4 wird die Komposition mehrerer Subsysteme zu einem System beschrieben. Abschnitt 3.5 geht schließlich auf die Grenzen des Systemmodells ein.

## 3.2 Datenströme und Operatoren auf Strömen

Die Kommunikation auf einem Kanal zwischen zwei Kommunikationspartnern erfolgt unidirektional über eine Folge von Zeichen aus einem bestimmten Zeichenvorrat. Diese Zeichenfolge wird Strom genannt. Ein Strom stellt die gesamte Kommunikationshistorie zwischen zwei Kommunikationspartnern dar und kann endlich oder unendlich lang sein. Darüber hinaus erlaubt es Focus, über das spezielle Symbol  $\sqrt{}$  explizit Zeitticks zu modellieren.

#### 3.2.1 Formale Darstellung von Strömen

Sei  $\mathbb{N}_+ \stackrel{\mathsf{def}}{=} \mathbb{N} \setminus \{0\}$  die Menge aller positiven natürlichen Zahlen.  $[1 \dots n]$  sei die Menge aller natürlichen Zahlen zwischen 1 und n für  $n \geq 1$  und die leere Menge für n = 0.

#### Definition 3.1 (Strom)

Sei M eine beliebige, nichtleere Menge (Alphabet). Ein endlicher Strom über M ist eine Abbildung  $[1 \dots n] \to M$ , d. h. eine endliche Folge in M. Ein unendlicher Strom über M ist eine Abbildung  $\mathbb{N}_+ \to M$ , d. h. eine unendliche Folge in M. Für die Darstellung eines Stroms s wird folgende Notation verwendet:

$$s = \langle m_1, m_2, m_3, \dots \rangle$$

Der leere Strom wird mit  $\langle \rangle$  dargestellt.

$s(1) = m_1$  ist das erste Element,  $s(2) = m_2$  das zweite Element und  $s(i) = m_i$  das *i*-te Element des Stroms. Alle Elemente  $m_i$  werden auch als *Nachrichten* bezeichnet und sind aus dem Alphabet M des Stroms.

#### Definition 3.2 (Menge aller Ströme)

Sei M eine beliebige, nichtleere Menge. Die Menge  $M^*$  aller endlichen Ströme, die Menge  $M^\infty$  aller unendlichen Ströme und die Menge  $M^\omega$  aller Ströme werden definiert als

$$M^{\,*} \ \stackrel{\mathsf{def}}{=} \ \bigcup_{n \in \mathbb{N}} \left\{ s \mid s : \left[ \, 1 \ldots n \, \right] \to M \right\},$$

$$M^{\,\infty} \stackrel{\mathsf{def}}{=} \mathbb{N}_+ \to M,$$

$$M^{\omega} \stackrel{\mathsf{def}}{=} M^* \cup M^{\infty}.$$

#### 3.2.2 Darstellung der Zeit

Die eingebetteten Systeme eines Automobils bilden ein verteiltes, nebenläufiges System. Da allein aus dem Inhalt und der Position der ausgetauschten Nachrichten in den Strömen noch kein Schluss auf die zeitliche Beziehung zweier Nachrichten in verschiedenen Strömen möglich ist, wird ein systemweiter Zeittakt eingeführt. FOCUS bietet hierzu zeitbehaftete Ströme (engl. timed streams) an.

#### Definition 3.3 (Zeitbehafteter Strom)

Sei M eine beliebige, nichtleere Menge. Sei  $\sqrt{\not} \in M$  das Symbol, das einen Zeittick repräsentiert. Die Menge  $M^*$  aller endlichen, zeitbehafteten Ströme über M, die Menge  $M^{\infty}$  aller unendlichen, zeitbehafteten Ströme über M und die Menge  $M^{\omega}$  aller zeitbehafteten Ströme über M werden definiert als

$$\begin{split} M^{\,*} &\stackrel{\mathsf{def}}{=} \;\; \bigcup_{n \in \mathbb{N}} \left\{ s \mid s : [1 \dots n] \to M \cup \left\{ \sqrt{\right\}} \right\}, \\ M^{\,\boxtimes} &\stackrel{\mathsf{def}}{=} \;\; \left\{ s \mid s : \mathbb{N}_{+} \to M \cup \left\{ \sqrt{\right\}} \; \text{und} \;\; \forall \, j \in \mathbb{N}_{+} \;\; \exists \, k \in \mathbb{N}_{+} : k \geq j \wedge s(k) = \sqrt{\right\}}, \\ M^{\,\boxtimes} &\stackrel{\mathsf{def}}{=} \;\; M^{\,*} \cup M^{\,\boxtimes}. \end{split}$$

Jeder Strom aus  $M^{\infty}$  enthält unendlich viele Zeitticks. Zwischen jeweils zwei benachbarten Zeitticks im Strom befinden sich höchstens endlich viele Zeichen aus M. Die Zeitticks unterteilen den Strom also in eine unendliche Folge von endlichen Teilströmen. Die Teilströme können auch leer sein.

Beispiel 3.1 Beispiel für einen endlichen, zeitbehafteten Strom:

$$s = \langle m_1, \sqrt{m_2, m_3, \sqrt{m_4}} \rangle$$

Im Folgenden wird Strom als Oberbegriff sowohl für einen zeitlosen als auch für einen zeitbehafteten Strom verwendet. Wenn nichts anderes angegeben ist, sei M stets eine beliebige, nichtleere Menge.

## 3.2.3 Operatoren auf Strömen

Viele Stromoperatoren sind sowohl auf zeitlose als auch auf zeitbehaftete Ströme anwendbar. Es genügt, diese nur auf zeitlosen Strömen zu definieren, da sie damit automatisch auch auf zeitbehaftete Ströme anwendbar sind: Jeder zeitbehaftete Strom ist auch ein zeitloser Strom, wenn man das Symbol  $\sqrt{}$  in das Alphabet des zeitlosen Stroms aufnimmt, d. h.  $M \stackrel{\omega}{=} (M \cup {\{\sqrt\}})^{\omega}$ .

#### Definition 3.4 (Länge eines Stroms)

#s bezeichnet die Länge des Stroms s. Es gilt:

$$\#: M^{\omega} \to \mathbb{N}_{\infty}$$

$$\#s \stackrel{\mathsf{def}}{=} \begin{cases} n & \mathsf{falls}\ s : [1\dots n] \to M \ \mathsf{für}\ \mathsf{ein}\ n \in \mathbb{N} \\ \infty & \mathsf{falls}\ s \in M^\infty \end{cases}$$

#### Definition 3.5 (Konkatenation von Strömen)

$r \cap s$  bezeichnet die Konkatenation der Ströme r und s. Es gilt:

$$\frown : M^{\omega} \times M^{\omega} \rightarrow M^{\omega}$$

und für alle  $i \in \mathbb{N}_+$  ist

$$(r \cap s)(i) \stackrel{\mathsf{def}}{=} \begin{cases} r(i) & \text{falls } 1 \leq i \leq \#r \\ s(i - \#r) & \text{falls } \#r < i \leq \#r + \#s \end{cases}$$

Wichtige Eigenschaften der Konkatenation sind:

- $\#r = \infty \Rightarrow r \cap s = r$

- $\#(r \cap s) = \#r + \#s$

- $\langle \rangle$  ist neutrales Element:  $s \cap \langle \rangle = s$ ,  $\langle \rangle \cap s = s$

- Assoziativität:  $(r \cap s) \cap t = r \cap (s \cap t)$

#### Definition 3.6 (Potenzierung eines Stroms)

$s^n$  bezeichnet den Strom, welcher durch n-malige Konkatenation von s entsteht. Es gilt:

$\hat{} : M^{\omega} \times \mathbb{N}_{\infty} \to M^{\omega}$ , wobei anstatt  $\hat{s} n$  immer  $\hat{s} n$  geschrieben wird

$$s^n \stackrel{\mathsf{def}}{=} \begin{cases} \langle \rangle & \text{falls } n = 0 \\ s \frown s^{(n-1)} & \text{falls } n \ge 1 \end{cases}$$

Beispiel 3.2  $\langle m, \sqrt{\rangle}^4 = \langle m, \sqrt{m}, \sqrt{$

#### Definition 3.7 (Präfix, Anfangsstrom)

Ein Strom r ist ein Präfix (Anfangsstrom) eines Stroms s, kurz  $r \sqsubseteq s$ , wenn r zu s verlängert werden kann. Für alle  $r, s \in M^{\omega}$  gilt:

$$r \sqsubseteq s \iff_{\mathsf{def}} \exists t \in M^{\omega} : r \cap t = s$$

**Beispiel 3.3**

$$\langle m_1, m_2 \rangle \sqsubseteq \langle m_1, m_2, m_3, m_4 \rangle$$

Die Präfixrelation  $\sqsubseteq$  ist eine Halbordnung auf  $M^{\omega}$ , d. h. eine reflexive, antisymmetrische und transitive Relation.

#### Definition 3.8 (Filter)

$D \otimes s$  bezeichnet einen Teilstrom (substream) von s, welcher entsteht, wenn alle Nachrichten aus s entfernt werden, die nicht in D enthalten sind.  $\otimes$  wird als Filter-Operator bezeichnet. Es gilt:

$$\mathbb{S}: \mathcal{P}(M) \times M^{\omega} \to M^{\omega}$$

$$D \circledast s \overset{\mathsf{def}}{=} \begin{cases} \langle \rangle & \text{falls } s = \langle \rangle \\ \langle m \rangle \smallfrown (D \circledast r) & \text{falls } s = \langle m \rangle \smallfrown r \text{ und } m \in D \\ D \circledast r & \text{falls } s = \langle m \rangle \smallfrown r \text{ und } m \not\in D \end{cases}$$

#### Definition 3.9 (Abschneiden eines Stroms)

$s|_i$  bezeichnet einen Strom, welcher nach dem i-ten Eintrag abgeschnitten ist. Es gilt:

$$|: M^{\omega} \times \mathbb{N}_{\infty} \to M^{\omega}$$

$$s|_i \overset{\mathsf{def}}{=} \begin{cases} r & \text{falls } i \leq \#s, \text{ wobei } r \sqsubseteq s \text{ mit } \#r = i \\ s & \text{falls } i > \#s \end{cases}$$

#### Definition 3.10 (Zeitbehaftetes Abschneiden eines Stroms)

$s\downarrow_i$  bezeichnet einen zeitbehafteten Strom, welcher direkt nach dem i-ten Zeittick abgeschnitten ist. Es gilt:

$$\downarrow : M^{\underline{\omega}} \times \mathbb{N}_{\infty} \to M^{\underline{\omega}}$$

$$s{\downarrow}_i \stackrel{\mathsf{def}}{=} \begin{cases} \langle \rangle & \text{falls } i = 0 \\ s & \text{falls } i > \#(\{\sqrt\} \, \circledS \, s) \text{ oder } i = \infty \\ r & \text{sonst, wobei } r \sqsubseteq s \text{ mit } \#(\{\sqrt\} \, \circledS \, r) = i \text{ und } r(\#r) = \sqrt{s} \end{cases}$$

Die ursprüngliche Definition des ↓-Operators in Focus erstreckt sich nur auf unendliche Ströme. Die hier vorgestellte Definition erweitert den Definitionsbereich des Operators auf endliche Ströme.

Beispiel 3.4 Vergleich der Operatoren zum zeitlosen bzw. zeitbehafteten Abschneiden von Strömen:

$$\langle m_1, \sqrt{m_2, \sqrt{m_3, \sqrt{m_4}}} \rangle = \langle m_1, \sqrt{m_2} \rangle$$

$\langle m_1, \sqrt{m_2, \sqrt{m_3, \sqrt{m_4}}} \rangle = \langle m_1, \sqrt{m_2, \sqrt{m_3, \sqrt{m_4}}} \rangle$

#### Definition 3.11 (Zeitabstraktion)

$\overline{s}$  bezeichnet einen zeitlosen Strom, welcher durch Entfernen aller Zeitticks aus dem zeitbehafteten Strom s entsteht. Es gilt:

П

$$\overline{s} \stackrel{\text{def}}{=} M \otimes s$$

**Beispiel 3.5**

$$\overline{\langle m_1, m_2, \sqrt{, m_3, \sqrt{, m_4} \rangle}} = \langle m_1, m_2, m_3, m_4 \rangle$$

# 3.3 Verhaltensbeschreibung mittels Stromrelationen

Aus Informationsverarbeitungssicht ist ein Systemverhalten eine Zuordnung von Eingaben zu Ausgaben. FOCUS verwendet ebenfalls diese Sicht und beschreibt das Verhalten eines Systems als Relation zwischen Eingabeströmen und Ausgabeströmen. Bei deterministischen Systemen ist diese Relation eine stromverarbeitende Funktion.

#### 3.3.1 Systemverhalten

#### Definition 3.12 (Kanal)

Ein Kanal ist ein expliziter Kommunikationsweg, den ein System zur Kommunikation mit seiner Umgebung bereitstellt. Jeder Kanal hat einen Namen, ein Alphabet und ist unidirektional. Man unterscheidet zwischen Ein- und Ausgabekanälen.

Damit zwei Systeme miteinander kommunizieren können, muss ein Ausgabekanal des einen Systems mit einem Eingabekanal des anderen Systems verbunden sein und die beiden Alphabete müssen gleich sein.

#### Definition 3.13 (Schnittstelle)

Die Schnittstelle eines Systems ist die Menge aller Kanäle des System. Die Namen der Kanäle eines Systems müssen dabei paarweise verschieden sein.

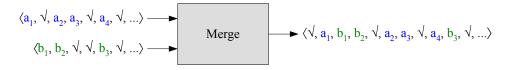

Beispiel 3.6 Betrachtet werden soll ein System Merge, das zwei Eingabeströme zu einem Ausgabestrom verarbeitet, indem die Nachrichten zwischen jeweils zwei Zeitticks in den Eingabeströmen konkateniert und einen Zeittakt später ausgegeben werden. Merge hat die Eingabekanäle  $i_1$  und  $i_2$  sowie den Ausgabekanal o. Die Alphabete der Eingabekanäle sind zwei beliebige, nichtleere Mengen  $M_1$  und  $M_2$ , das Alphabet des Ausgabekanals ist  $M_1 \cup M_2$ . Abbildung 3.1 stellt die Schnittstelle grafisch dar.

Abbildung 3.1: Schnittstelle des Systems Merge

#### Definition 3.14 (Verhaltensrelation, Systemverhalten)

Seien  $I_1, \ldots, I_n$  die Alphabete der Eingabekanäle und  $O_1, \ldots, O_m$  die Alphabete der Ausgabekanäle eines Systems S. Zur Abkürzung werden

$$I_S^{\omega} \stackrel{\mathsf{def}}{=} I_1^{\omega} \times \cdots \times I_n^{\omega}$$

$$O_S^{\omega} \stackrel{\mathsf{def}}{=} O_1^{\omega} \times \cdots \times O_m^{\omega}$$

eingeführt. Das Verhalten des Systems S ist eine Relation

$$\mathcal{R}_S \subseteq I_S^{\ \omega} \times O_S^{\ \omega}$$

$\mathcal{R}_S$  nennt man auch Verhaltensrelation oder Systemverhalten.

Im Folgenden werden häufig zeitbehaftete Systeme mit unendlichen Strömen betrachtet. Die Verhaltensrelation hat dann die Eigenschaft

$$\mathcal{R}_S \subseteq I_S \stackrel{\infty}{=} \times O_S \stackrel{\infty}{=}$$

**Beispiel 3.7** Die formale Verhaltensbeschreibung von *Merge* sieht in FOCUS-Notation wie folgt aus.

Im oberen Teil der Spezifikation werden die Ein- und Ausgabekanäle  $i_1$ ,  $i_2$  und o definiert. Dabei wird nur das Alphabet des Kanals angegeben. Da es sich um ein zeitbehaftetes System handelt – festgelegt durch das Schlüsselwort timed rechts oben –, ergeben sich die Mengen aller möglichen Ströme der Kanäle zu  $M_1^{\infty}$ ,  $M_2^{\infty}$  bzw.  $(M_1 \cup M_2)^{\infty}$ .

Man beachte, dass bei einem zeitbehafteten System die Ströme stets unendlich lang sind. Das liegt daran, dass die Zeit niemals endet, unabhängig davon, ob das System Ausgaben produziert oder nicht. Das Systemmodell ordnet auch einem System, das von Anfang an ausgefallen ist und deshalb keinerlei Ausgabe produziert, einen definierten Ausgabestrom zu, nämlich den Strom  $\langle \sqrt{\rangle}^{\infty}$ , bestehend nur aus Zeitticks.

Die Modellierung mittels zeitbehafteter Ströme erweist sich bei eingebetteten Systemen im Automobil als gut geeignet. Mit Hilfe der Zeitticks kann trotz Nebenläufigkeit ein zeitlicher Bezug zwischen Strömen verschiedener Kanäle hergestellt werden. Eingebettete Systeme im Automobil sehen ebenfalls kein zeitliches Ende ihrer Funktionalität vor (abgesehen von technischen Einschränkungen wie Materialermüdung oder die Verschrottung des Automobils) und sind daher mit unendlichen Strömen zu modellieren.

In Abbildung 3.2 ist anhand Beispielströmen dargestellt, wie das System Merge arbeitet.

Abbildung 3.2: Verhalten von Merge mit Beispielströmen

#### 3.3.2 Black-Box- und Glass-Box-Sicht

Die Verhaltensbeschreibung eines Systems mittels einer Verhaltensrelation benötigt keinerlei Wissen über die internen Vorgänge des Systems. Man spricht deshalb von Black-Box-Sicht oder auch Schnittstellenverhalten. Da die Berechnung der Ausgabe möglicherweise von der gesamten bisherigen Eingabehistorie abhängt, setzt die Verhaltensrelation  $\mathcal{R}_S$  nicht nur einzelne Eingabenachrichten mit einzelnen Ausgabenachrichten in Beziehung, sondern ganze Eingabeströme mit Ausgabeströmen.

Die Glass-Box-Sicht (auch White-Box-Sicht) hingegen führt einen Systemzustand ein, der die gesamte bisherige Eingabehistorie repräsentiert. Für die Berechnung der nächsten Ausgabe wird nur die aktuelle Eingabe und der Systemzustand benötigt. Explizites Wissen über die gesamte Eingabehistorie ist nicht mehr erforderlich.

Beispiel 3.8 Das System Merge sieht aus Glass-Box-Sicht folgendermaßen aus:

In dieser Darstellung liest Merge sukzessive immer nur eine Nachricht aus einem Eingabestrom ein. Zur Zwischenspeicherung der Nachrichten werden zwei interne Puffer verwendet:  $b_1$  puffert die Nachrichten aus Eingabestrom  $i_1$  und  $b_2$  die Nachrichten aus  $i_2$ . Sobald der nächste Zeittick an beiden Eingängen anliegt, werden der konkatenierte Pufferinhalt  $b_1 \cap b_2$  ausgegeben und die Puffer geleert. Die beiden Puffer bilden zusammen den Systemzustand. Die Glass-Box-Darstellung mit der schrittweisen Verarbeitung der Eingabe ist näher an einer möglichen Implementierung, da sie bereits den konkreten Berechnungsalgorithmus verdeutlicht.

Im Folgenden wird ausschließlich die Black-Box-Sicht verwendet, weil bei der Systembeschreibung möglichst auf Implementierungsdetails verzichtet werden soll.

# 3.3.3 Realisierbarkeit eines Systems

Die oben vorgestellte Verhaltensbeschreibung von Systemen erfolgt mittels einer Verhaltensrelation. Dabei lassen sich prinzipiell auch Systeme beschreiben, die keine Entsprechung in der Praxis haben. Ein Beispiel dafür wäre ein System, das in die Zukunft sehen kann, indem es stets Nachrichten ausgibt, die erst einige Zeitticks später auf einem Eingabekanal empfangen werden.

Daher fordert das Systemmodell von einem System zusätzlich, dass es *kausal* ist, d. h. die Ausgabe darf nur von den bereits empfangenen Eingaben abhängen. Dabei wird unterschieden zwischen schwacher und starker Kausalität. Im Gegensatz zur starken Kausalität darf bei der schwachen Kausalität zusätzlich noch die Eingabe im aktuellen Zeitintervall für die Ausgabe berücksichtigt werden.

#### Definition 3.15 (x-Schnitt einer Relation)

Seien A und B beliebige Mengen und  $R \subseteq A \times B$  eine Relation. Der x-Schnitt von R, kurz R(x), für ein  $x \in A$  ist definiert als

$$R(x) \stackrel{\mathsf{def}}{=} \{ y \mid (x, y) \in R \}.$$

### Definition 3.16 (Schwache und starke Kausalität)

Ein System S mit Verhaltensrelation  $\mathcal{R}_S \subseteq I_S \stackrel{\infty}{=} \times O_S \stackrel{\infty}{=}$  ist schwach bzw. stark kausal, wenn gilt:

$$\forall r, s \in I_S \stackrel{\infty}{=} \forall i \in \mathbb{N} : r \downarrow_i = s \downarrow_i \implies \mathcal{R}_S(r) \downarrow_i = \mathcal{R}_S(s) \downarrow_i \quad \text{bzw.}$$

$$\forall r, s \in I_S \stackrel{\infty}{=} \forall i \in \mathbb{N} : r \downarrow_i = s \downarrow_i \implies \mathcal{R}_S(r) \downarrow_{i+1} = \mathcal{R}_S(s) \downarrow_{i+1}$$

Dabei bedeutet das zeitbehaftete Abschneiden  $A \downarrow i$  einer Menge A an Strömen, dass jeder Strom einzeln abgeschnitten wird, d. h.  $A \downarrow i = \{s \downarrow i \mid s \in A\}$ .

Bei einem stark kausalen System darf jede Ausgabe nur von Eingaben abhängen, die mindestens ein Zeitintervall früher empfangen wurden. Dadurch wird die unweigerlich anfallende Verarbeitungszeit zum Berechnen der Ausgabe ausgedrückt. Bei einem schwach kausalen System hingegen darf zusätzlich die Eingabe im selben Zeitintervall wie die Ausgabe in die Berechnung der Ausgabe einfließen. Beschreibt man eingebettete Systeme in ausreichend kleinen Zeitintervallen, erhält man stets ein stark kausales System (siehe [Bro04]).

Eine Systemspezifikation beschreibt im Allgemeinen, mit welchen möglichen Ausgaben ein System auf bestimmte Eingaben reagieren darf und mit welchen nicht. Sie beschreibt also Einschränkungen des Systemverhaltens. Zum besseren Verständnis sollen folgende Extremfälle betrachtet werden.

Stark unterspezifiziertes System Enthält die Systemspezifikation keine Angaben zum Verhalten, d. h. gibt sie keinerlei Einschränkungen des Systemverhaltens vor, so liegt ein stark unterspezifiziertes System vor. Zu einem stark unterspezifizierten System gibt es stets viele verschiedene Realisierungen, die allesamt der Spezifikation genügen.

Deterministisches System Gibt es zu jeder Eingabe genau eine eindeutige, richtige Ausgabe, so handelt es sich um ein deterministisches System. Es gibt nur eine mögliche Realisierung, die sich im Sinne der Spezifikation korrekt verhält.

Widersprüchliche Spezifikation Wenn die Systemspezifikation zu mindestens einer Eingabe eine widersprüchliche Aussage bezüglich der zugehörigen Ausgabe macht, ist sie widersprüchlich. Es gibt dann kein realisiertes System, das sich bezüglich dieser Spezifikation stets korrekt verhalten kann, weil die Spezifikation bei mindestens einer Eingabe durch den Widerspruch keine korrekte Ausgabe zulässt.

Betrachtet man im ersten Fall die zugehörige Verhaltensrelation  $\mathcal{R}_S$ , so stellt man fest, dass es sich um die totale Relation handelt, also  $\mathcal{R}_S = I_S \cong \times O_S \cong$ . Jedem Eingabestrom werden alle möglichen Ausgabeströme zugeordnet, es handelt sich um eine hochgradig *nichtdeterministische* Systembeschreibung. Systemspezifikationen sind typischerweise immer nichtdeterministisch und bieten so Freiheit bei der Erstellung der Realisierung.

Bei einem deterministischen System ist die zugehörige Verhaltensrelation eine Funktion, d. h. für jeden Eingabestrom  $i \in I_S^{\infty}$  ist der x-Schnitt einelementig, also  $|\mathcal{R}_S(i)| = 1$ . Jedes eingebettete System ist deterministisch und stellt eine Funktion dar.<sup>1</sup>

Eine widersprüchliche Spezifikation beschreibt im Unterschied zu den beiden vorhergehenden Punkten ein nicht realisierbares System. Dies ist für die Praxis kein brauchbarer Ausgangspunkt für eine Systementwicklung, daher wird folgende Systemeigenschaft eingeführt.

#### Definition 3.17 (Realisierbarkeit)

Ein System S ist schwach realisierbar bzw. stark realisierbar, wenn S schwach kausal bzw. stark kausal ist und es eine Funktion f gibt mit  $f \subseteq \mathcal{R}_S$ . Ein System wird als realisierbar bezeichnet, wenn es zumindest schwach realisierbar ist.

Jedes stark realisierbare System ist auch schwach realisierbar. Eine realisierbare Spezifikation garantiert, dass es zu jedem Eingabestrom mindestens einen gültigen Ausgabestrom gibt. Sie ist damit widerspruchsfrei.

<sup>&</sup>lt;sup>1</sup>Hierin geht ein, dass es in eingebetteten Systemen keinen echten Zufall gibt, sondern das Zustande-kommen jeder Ausgabe theoretisch nachvollziehbar und reproduzierbar ist.

Aus der Definition folgt unmittelbar, dass jedes existierende, eingebettete System realisierbar ist. Das trifft selbst auf ein ausgefallenes System zu, welches nicht mehr reagiert, siehe Abschnitt 3.3.1.

Bei Systemspezifikationen soll ausgeschlossen sein, dass sie widersprüchlich oder nicht kausal sind. Daher wird im Folgenden stets gefordert, dass Systemspezifikationen realisierbar sind.

# 3.3.4 Verhaltensverfeinerung

Bei der Entwicklung eines Systems tritt eine Folge an Spezifikationsständen auf und mündet schließlich in eine Realisierung. Am Beispiel der modularen Entwicklung sind dies die Systemspezifikation, die Architekturbeschreibung, alle Subsystemrealisierungen zusammen und das System. Zur Beschreibung des korrekten Übergangs von einem Spezifikationsstand zum nächsten bzw. zur Realisierung wird der Begriff der Verhaltensverfeinerung eingeführt.

#### Definition 3.18 (Verhaltensverfeinerung)

Seien  $S_1$  und  $S_2$  beliebige Systeme.  $S_2$  ist eine Verhaltensverfeinerung von  $S_1$ , kurz  $S_1 \rightsquigarrow S_2$ , wenn beide Systeme die gleiche Schnittstelle haben und jedes Verhalten von  $S_2$  auch ein Verhalten von  $S_1$  ist. Formal:

$$(S_1 \leadsto S_2) \Leftrightarrow (\mathcal{R}_{S_1} \supseteq \mathcal{R}_{S_2})$$

# Definition 3.19 (Verhaltensäquivalenz)

Seien  $S_1$  und  $S_2$  beliebige Systeme.  $S_1$  und  $S_2$  sind verhaltensäquivalent, kurz  $S_1 \iff S_2$ , wenn  $S_1 \rightsquigarrow S_2$  und  $S_2 \rightsquigarrow S_1$ .

Bei realisierbaren Systemen bedeutet eine Verhaltensverfeinerung lediglich die Reduzierung des Nichtdeterminismus. Man kann also die Verhaltensverfeinerung verwenden, um Spezifikationsfreiräume zu nutzen.

Sind S, S', S'' aufeinander folgende Spezifikationsstände eines Systems und R die Realisierung am Ende der Entwicklung, dann sollte gelten:

$$S \leadsto S' \leadsto S'' \leadsto R$$

Da  $\leadsto$  transitiv ist, wird dadurch sichergestellt, dass R ein korrektes Verhalten im Sinne der Spezifikation S aufweist, also  $S \leadsto R$ .

FOCUS kennt auch die Konzepte der Schnittstellenverfeinerung und bedingten Verhaltens- bzw. Schnittstellenverfeinerung, die jedoch in dieser Arbeit nicht benötigt und daher nicht weiter vorgestellt werden.

# 3.4 Komposition von Systemen

# Definition 3.20 (Komposition von Systemen)

Seien  $S_1$  und  $S_2$  beliebige Systeme. Dann bezeichnet  $S_1 \otimes S_2$  die Komposition von  $S_1$  und  $S_2$  und ist selbst wiederum ein System. Gleichnamige Aus- und Eingabekanäle werden durch lokale Kanten miteinander verbunden. Dabei wird vorausgesetzt, dass die Namen aller Ausgabekanäle beider Systeme verschieden und die Alphabete der verbundenen Kanäle gleich sind. Die Systemschnittstelle der Komposition besteht aus den nicht-gebundenen Kanälen beider Systeme.

Der Kompositionsoperator  $\otimes$  ist kommutativ. Sind die Namen aller Eingabekanäle verschieden, ist der Operator auch assoziativ. Bei der Komposition mehrerer Systeme kann dann auf die Klammerung verzichtet werden. Eine formale Definition der Komposition ist in Focus zu finden.

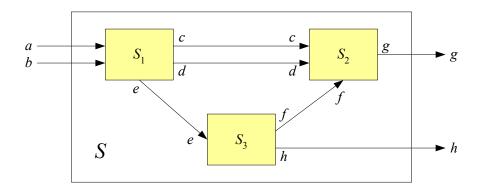

**Beispiel 3.9** Abbildung 3.3 zeigt die Komposition dreier Subsysteme  $S_1$ ,  $S_2$  und  $S_3$ . Das dadurch entstehende System S hat die Eingabekanäle a und b sowie die Ausgabekanäle g und h. Alle anderen Kanäle der Subsysteme werden lokal gebunden und sind nicht nach außen sichtbar.

Abbildung 3.3: Komposition von drei Subsystemen

#### Definition 3.21 (Verhalten einer Komposition)

Seien  $S_1$  und  $S_2$  beliebige Systeme. Das Verhalten der Komposition  $S = S_1 \otimes S_2$  wird definiert durch

$$\mathcal{R}_{S} \stackrel{\text{def}}{=} \{(i, o) \in I_{S} \stackrel{\infty}{=} \times O_{S} \stackrel{\infty}{=} | \exists l \in L^{\infty} : ((\Pi_{i_{S_{1}}}.i, \Pi_{i_{S_{1}}}.l), (\Pi_{o_{S_{1}}}.o, \Pi_{o_{S_{1}}}.l)) \in \mathcal{R}_{S_{1}}$$

$$\wedge ((\Pi_{i_{S_{2}}}.i, \Pi_{i_{S_{2}}}.l), (\Pi_{o_{S_{2}}}.o, \Pi_{o_{S_{2}}}.l)) \in \mathcal{R}_{S_{2}} \}$$

wobei  $i_{S_1}$ ,  $o_{S_1}$ ,  $i_{S_2}$ ,  $o_{S_2}$  die Namen der Ein- bzw. Ausgabekanäle von  $S_1$  bzw.  $S_2$  sind und  $\Pi_A.t$  die Projektion auf die Einträge mit Namen A des Tupels t. Der Bezeichner

l steht für die Ströme der lokalen Kanten und  $L^{\infty}$  ist die Menge aller Ströme der lokalen Kanten.

**Beispiel 3.10** Seien  $M_a$ ,  $M_b$ ,  $M_c$ ,  $M_d$ ,  $M_e$ ,  $M_f$ ,  $M_g$  und  $M_h$  die Alphabete der Kanäle aus obigem Beispiel. Dann ergibt sich:

$$\begin{split} I_S &\stackrel{\infty}{=} = M_a \stackrel{\infty}{=} \times M_b \stackrel{\infty}{=} \\ O_S &\stackrel{\infty}{=} = M_g \stackrel{\infty}{=} \times M_h \stackrel{\infty}{=} \\ L^{\infty} &= M_c \stackrel{\infty}{=} \times M_d \stackrel{\infty}{=} \times M_f \stackrel{\infty}{=} \\ \mathcal{R}_S &= \left\{ \; ((a,b),(g,h)) \in I_S \stackrel{\infty}{=} \times O_S \stackrel{\infty}{=} \; \mid \; \exists (c,d,e,f) \in L^{\infty} : (a,b,c,d,e) \in \mathcal{R}_{S_1} \\ & \wedge \; (c,d,f,g) \in \mathcal{R}_{S_2} \; \wedge \; (e,f,h) \in \mathcal{R}_{S_3} \; \right\} \end{split}$$

Der Kompositionsoperator  $\otimes$  ist außerdem monoton bezüglich der Verhaltensverfeinerung:

$$S_1 \rightsquigarrow S_1' \land S_2 \rightsquigarrow S_2' \Rightarrow (S_1 \otimes S_2) \rightsquigarrow (S_1' \otimes S_2')$$

Die Komposition definiert ein System bottom-up, d. h. das Verhalten der Komposition ist vollständig durch das Verhalten ihrer Subsysteme festgelegt.

# 3.5 Grenzen des Systemmodells

Das in diesem Kapitel vorgestellte Systemmodell beschränkt sich auf eine rein funktionale Beschreibung von Systemen. Nicht darstellbar sind hingegen nicht-funktionale Anforderungen wie Bedienbarkeit oder Zuverlässigkeit. Zur Beschreibung der Zuverlässigkeit fehlen dem Systemmodell beispielsweise die Angabe eines Operationsprofils, d. h. die relativen Aufrufhäufigkeiten der einzelnen Systemfunktionen sowie die Versagenswahrscheinlichkeiten der Systemfunktionen.

Ein weiterer Punkt ist die Zeitdarstellung in Focus. Die Beschreibung der zeitlichen Abläufe erfolgt anhand diskreter Zeittakte, die den kontinuierlichen Zeitverlauf in Intervallabschnitte zerlegen. Mit dieser Zeitabstraktion ist es in Focus nicht direkt möglich, beliebige reelle Zeitabstände zu messen. Eine Erweiterung auf zeitkontinuierliche Ströme sowie diskrete Ströme auf Basis einer kontinuierlichen Zeit ist in [Bro01] beschrieben. Damit lässt sich auch der Bezug zur realen Zeit herstellen, um beispielsweise einen Timeout von 100 ms zu modellieren.

Für das in dieser Arbeit benötigte Systemmodell ist Focus aber eine ideale Basis und hat sich als ausreichend mächtig und äußerst kompakt erwiesen.

# 4 Integration aus formaler Sicht

In diesem Kapitel wird die Integration aus formaler Sicht beschrieben. Wichtige Eigenschaften und Begriffe werden mit Hilfe des eingeführten Systemmodells charakterisiert.

# 4.1 Phasen der modularen Entwicklung

Gemäß Abschnitt 2.3.1 besteht die modulare Entwicklung im Wesentlichen aus drei Phasen: Zerlegen in Subsysteme, Realisieren der Subsysteme, Integrieren zum System. Formal stellen sich diese drei Phasen wie folgt dar.

Phase 1: Zerlegen in Subsysteme Eine gegebene Systemspezifikation S wird zerlegt in mehrere Subsystemspezifikationen  $S_1, \ldots, S_n$ . Die Zerlegung ist korrekt, wenn die Subsystemspezifikationen zusammen ein Systemverhalten beschreiben, das der ursprünglichen Systemspezifikation entspricht, also

$$S \leadsto (S_1 \otimes \cdots \otimes S_n) \tag{4.1}$$

Fehler in dieser Phase werden als Zerlegungsfehler bezeichnet.

Phase 2: Realisieren der Subsysteme Die einzelnen Subsysteme werden in dieser Phase unabhängig voneinander realisiert, und aus jeder Subsystemspezifikation  $S_i$  entsteht eine Realisierung  $R_i$ . Die Realisierungen sind korrekt, wenn jedes einzelne realisierte Subsystem seiner Spezifikation entspricht, also

$$\forall i \in [1 \dots n] : S_i \leadsto R_i \tag{4.2}$$

Fehler in dieser Phase werden als Realisierungsfehler bezeichnet.