## TECHNISCHE UNIVERSITÄT MÜNCHEN Lehrstuhl für Entwurfsautomatisierung

# Hierarchical Statistical Static Timing Analysis Considering Process Variations

#### Bing Li

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs**

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr.-Ing. Jörg Eberspächer

Prüfer der Dissertation: 1. Univ.-Prof. Dr.-Ing. Ulf Schlichtmann

2. Univ.-Prof. Dr. sc. Samarjit Chakraborty

Die Dissertation wurde am 27.01.2010 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 15.07.2010 angenommen.

#### **Acknowledgments**

This thesis is the result of my working at the Institute for Electronic Design Automation, Technische Universität München as a research and teaching assistant.

First of all, I thank Professor Ulf Schlichtmann for admitting me to his research group. He has patiently guided me to enter the research field of statistical timing analysis and given me constructive advices on my specific topics since the beginning. He carefully reviewed all my papers and his insightful suggestions helped me not only improve my academic writing but also form a professional research style. Additionally, he also spent much time to help me overcome all other problems during my PhD studying. Moreover, I thank him for giving me the chance to establish the VLSI design lab. For me this is a precious experience in teaching and communication with students.

Many thanks are due to the committee members Professor Samarjit Chakraborty and Professor Jörg Eberspächer for their interest in my thesis.

From PD Dr. Helmut Gräb I gained much after each of our talks. I thank him for his generous help and advices. I thank Walter Schneider and Dr. Manuel Schmidt for our fruitful discussions. I give my thanks to Ning Chen for the numerous talks and the collaboration in writing papers. Christoph Knoth gave me lots of help in writing; Xin Pan gave me invaluable suggestions as I prepared my presentations; Qingqing Chen worked with me in teaching the VLSI design lab and took over it finally. I am grateful to all of them. I thank all the other PhD students in the institute for maintaining such a creative atmosphere, which is important for me to finish my thesis.

Since I joined the institute, Dr. Bernd Finkbein, Hans Ranke, Werner Tolle, Jürgen Zenz, Susanne Werner and Gertraude Kallweit have given me all sorts of support and I thank them gratefully.

Last but not the least, I give my deepest gratitude to my wife Xue Zhao. Without her patient support and encouragement I could not finish this thesis.

Munich, January 2010

Bing Li

## **Contents**

| 1 | Intro | oductio | on and the second of the secon | 1  |

|---|-------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1   | Challe  | enges in SoC Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3  |

|   | 1.2   | Contr   | ributions of This Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6  |

|   | 1.3   | Organ   | nization of This Dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7  |

|   | 1.4   | Sumn    | nary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8  |

| 2 | Stat  | ic Timi | ng Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9  |

|   | 2.1   |         | ential Circuits and Timing Graphs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9  |

|   | 2.2   | Timin   | ng of Flip-flop Based Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12 |

|   | 2.3   | Timin   | ng of Latch Based Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13 |

|   | 2.4   | Static  | Timing Analysis of Combinational Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15 |

|   | 2.5   | Static  | Timing Analysis of Flip-flop Based Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19 |

|   | 2.6   | Static  | Timing Analysis of Latch Based Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20 |

|   | 2.7   | Sumn    | nary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21 |

| 3 | Prol  | blem D  | escription                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23 |

|   | 3.1   | Variat  | tions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23 |

|   |       | 3.1.1   | Sources of Variations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25 |

|   |       | 3.1.2   | Decomposition of Process Variations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25 |

|   |       | 3.1.3   | Correlation Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27 |

|   |       | 3.1.4   | Process Variation Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 29 |

|   | 3.2   | Statis  | tical Timing Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30 |

|   |       | 3.2.1   | Process Parameter Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30 |

|   |       | 3.2.2   | Gate Delay Representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31 |

|   |       | 3.2.3   | Statistical Timing Analysis of Combinational Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34 |

|   |       | 3.2.4   | Statistical Timing Analysis of Sequential Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39 |

|   | 3.3   | Timin   | ng Model Extraction for Static Timing Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 42 |

|   |       | 3.3.1   | Static Timing Model for Combinational Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 42 |

|   |       | 3.3.2   | Static Timing Model for Sequential Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 46 |

|   |       | 3.3.3   | Timing Verification with Static Timing Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 48 |

|   | 3.4   | Hiera   | rchical Statistical Timing Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 49 |

|   |       | 3.4.1   | State of the Art in Statistical Timing Model Extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50 |

|   |       | 3.4.2   | State of the Art in Hierarchical Statistical Timing Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 53 |

|   | 3.5   | Sumn    | nary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 55 |

| 4  | Stat                   | tistical Timing Model Extraction                                     | 57  |  |  |  |

|----|------------------------|----------------------------------------------------------------------|-----|--|--|--|

|    | 4.1                    | Timing Model Extraction for Combinational Circuits                   | 57  |  |  |  |

|    |                        | 4.1.1 Concept of Noncritical Edge Removal for Static Timing Analysis | 58  |  |  |  |

|    |                        | 4.1.2 Noncritical Edge Removal in Statistical Timing Analysis        | 60  |  |  |  |

|    |                        | 4.1.3 Timing Model Extraction with Noncritical Edge Removal          | 63  |  |  |  |

|    | 4.2                    | Timing Model Extraction for Flip-flop Based Circuits                 | 65  |  |  |  |

|    | 4.3                    | Timing Model Extraction for Latch Based Circuits                     | 68  |  |  |  |

|    |                        | 4.3.1 Timing Specification with Inputs for Latch Based Circuits      | 69  |  |  |  |

|    |                        | 4.3.2 Timing Constraint Restructuring for Latch Based Circuits       | 70  |  |  |  |

|    |                        | 4.3.3 Path Traversal and Clock Scheme                                | 73  |  |  |  |

|    |                        | 4.3.4 Timing Constraint Extraction from Enabling Clock Edges         | 75  |  |  |  |

|    |                        | 4.3.5 Timing Constraint Extraction from Inputs                       | 78  |  |  |  |

|    |                        | 4.3.6 Nonpositive Loop Constraint Extraction                         | 79  |  |  |  |

|    |                        | 4.3.7 Summary of Timing Model Extraction for Latch Based Circuits    | 80  |  |  |  |

|    | 4.4                    | Summary                                                              | 81  |  |  |  |

|    |                        |                                                                      |     |  |  |  |

| 5  |                        | relation Handling in Hierarchical Statistical Timing Analysis        | 83  |  |  |  |

|    | 5.1                    | Correlation Handling with Variable Substitution                      | 84  |  |  |  |

|    | 5.2                    | Discussion                                                           | 86  |  |  |  |

|    | 5.3                    | Summary                                                              | 88  |  |  |  |

| 6  | Ехр                    | perimental Results                                                   | 89  |  |  |  |

|    | 6.1                    | Experiment Setup                                                     | 89  |  |  |  |

|    | 6.2                    | Results of Timing Models for Combinational Circuits                  | 92  |  |  |  |

|    | 6.3                    | Results of Timing Models for Sequential Circuits                     | 97  |  |  |  |

|    | 6.4                    | Results of Hierarchical Statistical Timing Analysis                  | 100 |  |  |  |

|    | 6.5                    | Summary                                                              | 102 |  |  |  |

| 7  | Con                    | nclusion                                                             | 103 |  |  |  |

| Bi | bliog                  | raphy                                                                | 107 |  |  |  |

| Al | Abstract in German 115 |                                                                      |     |  |  |  |

## **List of Figures**

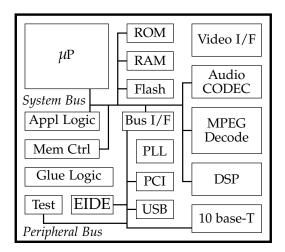

| 1.1  | System on Chip Example [KCJ <sup>+</sup> 00]                  |

|------|---------------------------------------------------------------|

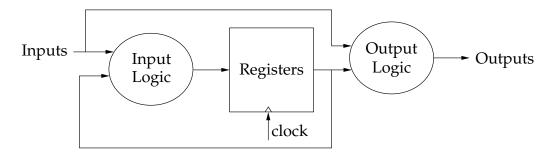

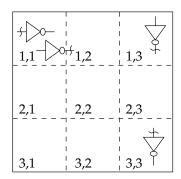

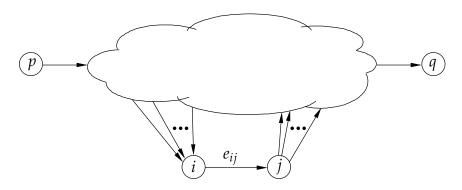

| 2.1  | Sequential Circuit Structure                                  |

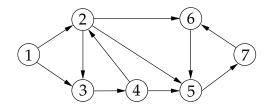

| 2.2  | Example of Reduced Timing Graph                               |

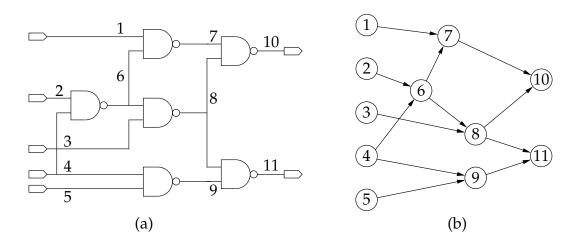

| 2.3  | c17 Benchmark and Timing Graph                                |

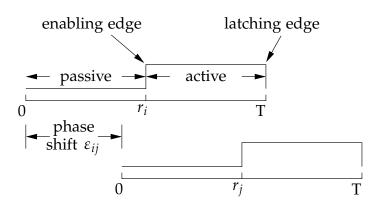

| 2.4  | Local Time Zone and Clock Phase Shift                         |

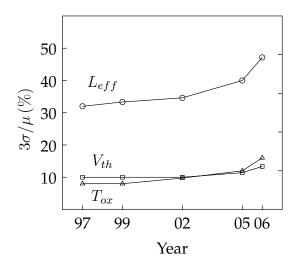

| 3.1  | Relative Variation Increase, data from [Nas01]                |

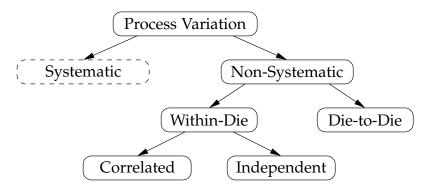

| 3.2  | Variation Classification [BCSS08]                             |

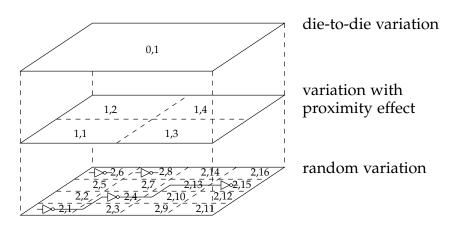

| 3.3  | Quadtree Correlation Model [ABZ <sup>+</sup> 03b, ABZ03a]     |

| 3.4  | Uniform Grid Correlation Model [CS03]                         |

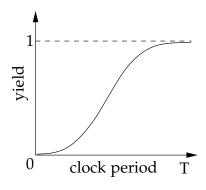

| 3.5  | Graphic Representation of Yield Computation                   |

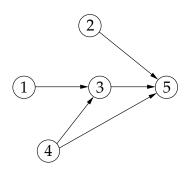

| 3.6  | Correlation Example in Statistical Arrival Time Propagation 3 |

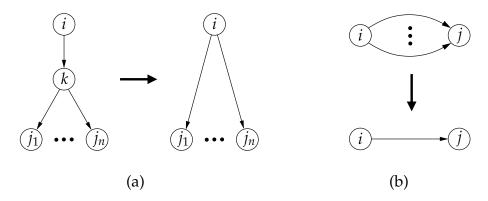

| 3.7  | Basic Merge Operations [KM97, MKB02]                          |

| 3.8  | Example of Basic Merge Operations                             |

| 3.9  | Butterfly- $\alpha$ Transformation [KM97]                     |

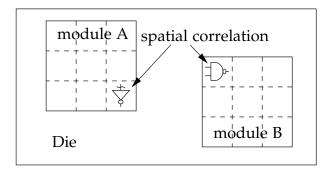

| 3.10 | Correlation Between Modules                                   |

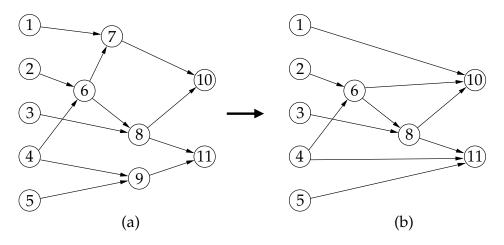

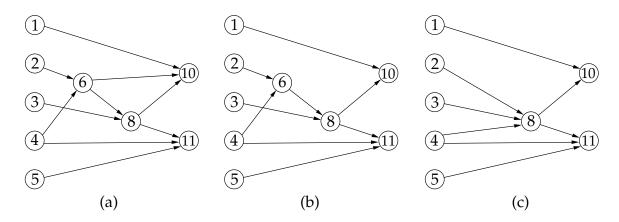

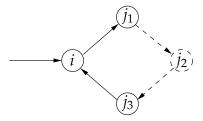

| 4.1  | Example of Noncritical Edge Removal                           |

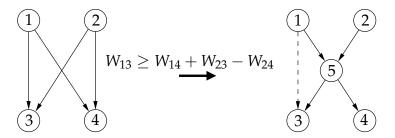

| 4.2  | Path Partition according to an Edge                           |

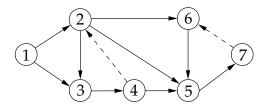

| 4.3  | Loop Example in Reduced Timing Graph                          |

| 4.4  | Reduced Timing Graph Example with Feedback Edge Removal 74    |

| 5.1  | Heterogeneous Grid                                            |

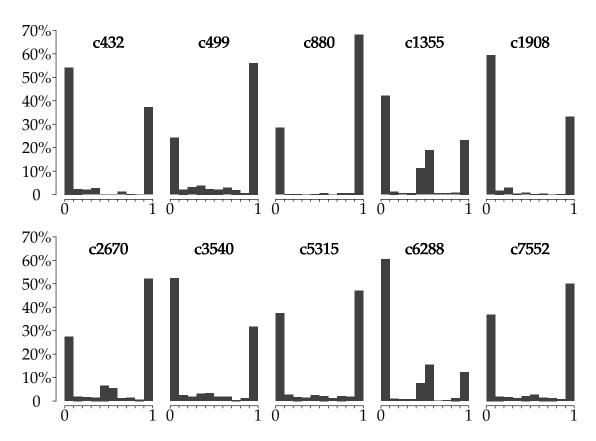

| 6.1  | Criticality Distributions of ISCAS85 Benchmarks               |

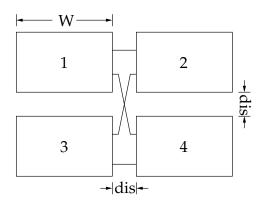

| 6.2  | Layout of the Hierarchical Circuit                            |

## **List of Tables**

| 2.1 | Notation Definition for Timing Analysis                            | 12  |

|-----|--------------------------------------------------------------------|-----|

| 2.2 | Arrival Time Propagation of c17                                    | 17  |

| 2.3 | Arrival Time Propagation from $n_3$ in c17 Timing Graph            | 19  |

| 6.1 | ISCAS85 Benchmarks                                                 | 90  |

| 6.2 | ISCAS89 Benchmarks                                                 | 91  |

| 6.3 | Results of Black-Box Timing Models for Combinational Circuits      | 93  |

| 6.4 | Accuracy of Statistical Criticality Computation, $\delta_c = 0.05$ | 95  |

| 6.5 | Results of Gray-Box Timing Models for Combinational Circuits       | 96  |

| 6.6 | Results of Timing Model Extraction for Flip-flop Based Circuits    | 98  |

| 6.7 | Results of Timing Model Extraction for Latch Based Circuits        | 99  |

| 6.8 | Results of Hierarchical Statistical Timing Analysis                | 101 |

## **List of Algorithms**

| 1 | Maximum Delay Computation from All Inputs               | 16 |

|---|---------------------------------------------------------|----|

| 2 | Maximum Delay Computation from Primary Input $n_p$      | 18 |

| 3 | Timing Analysis of Flip-flop Based Circuits             | 20 |

| 4 | Minimum Clock Period of Latch Based Circuits            | 20 |

| 5 | Minimum Clock Period with Constraint Relaxation         | 21 |

| 6 | Critical Edge Identification in Static Timing Analysis  | 60 |

| 7 | Statistical Model Extraction for Combinational Circuits | 64 |

### **Chapter 1**

#### Introduction

With ubiquitous presence, Integrated Circuits (IC) have become an essential part of life and economy. As a fundamental implementation method, IC design as well as manufacturing has affected most industry branches and has been involved in nearly every innovation of the present era. Meanwhile, IC design methodology and manufacturing technology are compelled to innovate themselves to meet the increasing technical and economic requirements of the rapidly advancing industry.

In the past 40 years, the IC industry has met the requirements from different application areas by keeping the pace of device scaling of Moore's law [Moo65, Moo03]. With smaller devices, more functions are integrated into a chip without increasing the die size. This integration enables the trend of System-on-Chip (SoC) design, where a chip provides the functionality of a complete system. For example, such integration happens continuously in the field of consumer electronics [Lee05], where more and more functions are integrated in each new product generation. With more devices in a chip, design complexity of an SoC chip increases drastically. Facing the pressure of more Non-Recurring Engineering (NRE) expenses and shorter time to market, new design methodologies, such as Electronic System Level (ESL) design and Intellectual Property (IP) integration, are considered as the keys to solve design issues in managing the exploding number of transistors and functions in a design [CK08, MP03, Hen03].

The Electronic Design Automation (EDA) companies assume the role to provide methodologies and tools for IC design and verification. With these commercial tools, different design flows for digital circuits are constructed. These design flows share some common steps: circuit descriptions in Hardware Design Language (HDL) are translated into netlists at synthesis step; logic gates included in the netlists are distributed on the die at layout step and interconnects between them are routed thereafter; before sign-off, designs are verified against functionality, timing and power specifications.

Standing at the center of these design flows, a widely used development model is data abstraction. From high level abstraction, e.g., ESL, to low level parasitic extraction, details are considered gradually in the design flow. In this way, tasks of design and verification become manageable at each step. Consequently, this abstraction reduces the complexity not only for designers but also for design flow engineers. As examples of such abstraction, preverified modules are considered as black boxes in the SoC design flow; geometries instead of internal transistor structures of digital gates are used during the layout step.