## Institut für Informatik der Technischen Universität München

Lehrstuhl für Informatik mit Schwerpunkt Wissenschaftliches Rechnen

## **Hierarchical Pattern Matching in VLSI**

## Marko Milošević

Vollständiger Abdruck der von der Fakultät für Informatik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender:

Univ.-Prof. Tobias Nipkow Ph.D.

Prüfer der Dissertation: 1. Univ.-Prof. Dr. Hans-Joachim Bungartz

2. Univ.-Prof. Dr. Erich Barke, Leibniz Universität Hannover

3. Univ.-Prof. Dr. Thomas Huckle

Die Dissertation wurde am 25.03.2009 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 06.07.2009 angenomen.

## Abstract

Structural pattern matching is an important part of the microchip design verification process. It is necessary to isolate semantic structural contexts in a given design netlist in order to be able to perform flexible and intelligent checks like, for example LVS (Layout Versus Schematics), ERC (Electrical Rule Checks), gate level netlist timing analysis and others. Because of that, many different algorithms were devised to support this particular segment of chip verification. The theoretical basis for these algorithms is pattern matching in graphs, i.e. subgraph isomorphism. Algorithms developed so far are working with flat input netlists. This is not efficient and limits the application of the mentioned algorithms due to the flat netlist's extensive size. Making the pattern matching hierarchical can improve the processes of chip design verification and simulation.

We provide the solution for the problem of the structural pattern matching in hierarchical netlists by defining the new methodology which employs the concept of Layered Views to present the hierarchical layout of a given netlist in a "friendly" way to an arbitrary application domain (user) algorithm. This general framework solves typical problems that algorithms working with hierarchical netlists are facing. Particularly, we propose the Virtually Flattened View (VFV), a sophisticated concept that prepares the hierarchical data for the user algorithms and allows them to see that data as if they were flat. We achieve this by materializing (creating a proxy copy) a small data portion which is kept consistent with the source hierarchical netlist by specific algorithms and data structures. The view offers the possibility to emboss the materialized data portion into the primary design's hierarchy, as a separate instance, altering the primary hierarchy. The outcome of this process is again a valid hierarchical netlist. We, further, apply the defined concepts to Incremental Pattern Matching, originally developed for flat input netlists only. In this way we obtain the methodology to solve the problem of pattern matching in hierarchical netlists.

For several reference scenarios, quantitative and qualitative improvements of our approach are demonstrated. The quantitative improvement is discussed through runtime and memory requirement tests. The qualitative improvement comes from the fact that the new methodology allows full-chip analysis and concise, hierarchical result reports.

## Zusammenfassung

Der Verifikationsprozess integrierter Schaltungen beinhaltet eine ganze Reihe wichtiger Prüfungen wie LVS (Layout vs. Schematics), ERC (Electrical Rule Check), Statische Timinganalyse und andere, die flexibler und effizienter durchgeführt werden können, wenn der funktionale Aufbau der Schaltung der Prüfung zugänglich ist (und nicht nur eine rein transistorbasierte Netzliste ohne weitere Struktur vorliegt).

Aus diesem Grund ist eine strukturbasierte Mustererkennung, die es erlaubt, die für den Verifikationsprozess wichtigen Kontexte aus der Schaltung zu isolieren, ein wesentlicher Differentiator für die Qualität der eingesetzten Verifikationsprogramme hinsichtlich Performanz und Fehlerabdeckung. Dies hat in der Vergangenheit zu etlichen Aktivitäten in diesem Gebiet geführt, so dass eine Vielzahl unterschiedlicher Algorithmen und Implementierungen zur Mustererkennung vorliegt. Gemeinsam ist ihnen die Identifizierung von Mustern in Graphen, also die Erkennung von Teilgraphisomorphismen.

Die bisher entwickelten Algorithmen setzen flache Netzlisten ohne innere Struktur (Hierarchie) voraus. Das ist bei grossen Datenmengen nicht effizient und limitiert das Anwendungsgebiet. Gelingt es also, die Strukturerkennung auf hierarchischen Daten zu ermöglichen, so kann eine sehr grosse Verbesserung der Verifikationsperformanz erzielt werden.

In dieser Arbeit stellen wir eine Lösung für die hierarchische Erkennung von Mustern in hierarchischen Netzlisten vor, die auf der Einführung der neuen Technik sogenannter "Layered Views" beruht. Mit ihrer Hilfe werden die hierarchischen Daten den Applikationen auf eine sehr benutzerfreundliche und einfach zu nutzende Weise präsentiert. Insbesondere schlagen wir an dieser Stelle "Virtually Flattened Views" (VFV) vor. Diese präsentieren die hierarchischen Daten in einer Weise, die der Applikation erlaubt, sie zu interpretieren, als kämen sie von einer flachen Datenbasis. Typische Probleme, die beim Arbeiten mit hierarchischen Daten gelöst werden müssen, lassen sich auf diesem Weg einmal lösen, die Applikationen können in weiten Teilen unverändert von einer flachen Implementierung auf eine hierarchische Implementierung portiert werden, nur durch die Umstellung auf die Nutzung des VFV als Beispiel eines "Layered Views". Der VFV wird durch eine sehr lokale Ausflachung der hierarchischen Datenbasis implementiert, die dynamisch den Anforderungen der flachen Applikation entsprechend aktualisiert wird.

Auf diesem Weg können wir aber nicht nur die hierarchischen Daten lokal flach zur Verfügung stellen, wir können auch die Ergebnisse der Mustererkennung, die nun ja flach entstehen, ohne weiteres in die hierarchische Datenbasis unter Modifikation der existierenden Hierarchie zurückschreiben. Das Ergebnis der Mustererkennung ist also wieder eine hierarchische Netzliste. Weiter gehend wenden wir die neuen Techniken auf die inkrementelle Mustererkennung an, die ursprünglich nur für flache Daten implementiert wurde. Insgesamt gesehen haben wir damit das Problem der Mustererkennung in hierarchischen Netzlisten vollständig gelöst.

Für einige Referenzszenarios, die aus realen Industrieapplikationen stammen, demonstrieren wir die quantitativen und qualitativen Verbesserungen, die mit unserem Ansatz erzielt werden können. Die quantitativen Aspekte werden anhand von Laufzeit und Speicherverbrauchsvergleichen diskutiert. Die qualitativen Verbesserungen erzielen wir zum einen durch sehr kompakte (hierarchische) Ergebnisse, zum anderen können nun erstmals Netzlisten für das komplette Design bearbeitet werden, während vorher nur Teilausschnitte geprüft werden konnten.

## Acknowledgemens

I thank my professor, Prof. Dr. Hans-Joachim Bungartz for leading me through this project methodologically and giving me self-confidence in crucial moments. I want to thank Dr. Martin Frerichs, Dr. Tilman Neunhöffer, Hannes Armruster and the rest of the ATS department of Qimonda AG for the substantial support of my work. I am especially grateful to Dr. Alexander Seidl for having the organisational side of my project in a perfect grip. In the end, I want to thank my family and friends for understanding and believing in me.

Marko Milošević

# Contents

| 1 | INT   | RODUCTION                                                                      | 13  |

|---|-------|--------------------------------------------------------------------------------|-----|

|   | 1.1   | MOTIVATION                                                                     | 13  |

|   | 1.2   | OBJECTIVES AND SCOPE                                                           |     |

|   | 1.3   | OUTLINE                                                                        |     |

| 2 | GRA   | PH MATCHING CONCEPTS IN VLSI                                                   | 19  |

|   | 2.1   | BASICS OF GRAPH NOTATION                                                       | 19  |

|   | 2.2   | GRAPH MATCHING                                                                 |     |

|   | 2.3   | SUBCIRCUIT RECOGNITION, THE APPLICATION OF SUBGRAPH MATCHING                   |     |

|   | 2.4   | INCREMENTAL PATTERN MATCHING                                                   |     |

|   | 2.5   | CLASSIFY PROJECT – CLARULA DESCRIPTIVE LANGUAGE                                |     |

|   | 2.6   | TREATING BIG NETS IN THE INCREMENTAL PATTERN MATCHING ALGORITHM                |     |

|   | 2.7   | INEXACT PATTERN MATCHING APPLIED TO SUBCIRCUIT RECOGNITION                     |     |

|   | 2.8   | ADDRESSING DESIGNS WITH EXTENSIVE SIZE BY EMPLOYING HIERARCHY                  |     |

| 3 | HIF   | RARCHY                                                                         |     |

| 5 |       |                                                                                |     |

|   | 3.1   | HIERARCHICAL ABSTRACTION IN VLSI                                               |     |

|   |       | Introduction                                                                   |     |

|   |       | Folded hierarchical model                                                      |     |

|   | 3.2   | EDA DATABASES                                                                  |     |

|   |       | History                                                                        |     |

|   |       | Standardization                                                                |     |

|   |       | OpenAccess                                                                     |     |

|   | 3.3   | NLDB                                                                           |     |

|   |       | <i>Hierarchical concepts in NLDB</i>                                           |     |

|   | 3.4   | Personalization                                                                |     |

|   | 3.5   | POLYMORPHIC HIERARCHY                                                          |     |

|   |       |                                                                                |     |

| 4 | HIE   | RARCHICAL MULTILAYER VIEWS                                                     |     |

|   | 4.1   | INTRODUCTION                                                                   |     |

|   | 4.2   | ACCESS LAYER – PURE ABSTRACT INTERFACE                                         |     |

|   | 4.3   | STATIC BASE                                                                    |     |

|   | 4.4   | LAYERED VIEWS AND THEIR OBJECT-ORIENTED ARCHITECTURE                           |     |

|   | 4.5   | EXAMPLES OF VIEWS                                                              | 70  |

| 5 | VIR   | TUALLY FLATTENED VIEW                                                          | 73  |

|   | 5.1   | INTRODUCTION                                                                   |     |

|   | 5.2   | VIRTUALLY FLATTENED VIEW - HIGH-LEVEL ARCHITECTURE                             | 75  |

|   | 5.3   | VIRTUALLY FLATTENED VIEW CLASS REPRESENTATION                                  |     |

|   | 5.4   | DEVICEFLATCONTAINER - ITERATOR                                                 |     |

|   | 5.5   | VIRTUAL ELEMENT BUILDER                                                        |     |

|   |       | Objects with roles                                                             | 85  |

|   |       | Consistency of the virtually flat view data portion objects with NLDB database |     |

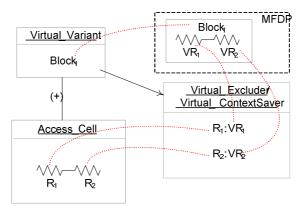

|   |       | ual_ContextSaver)                                                              |     |

|   | 5.7   | CONTEXT-SWITCHING / MULTI-CONTEXT NODES                                        |     |

|   | 5.8   | MULTI-CONTEXT (OVERLAPPED) FLAT DATA PORTION                                   |     |

|   | 5.9   | COMMITTING OF THE MFDP (AND IT'S REPETITIVE USE)                               |     |

|   | 5.10  | DISTRIBUTED VARIANTS.                                                          |     |

|   |       | 1 Technique for the topology adaptation                                        |     |

|   | 5.10. | 2 Dynamic variant creation                                                     | 109 |

|    |       | 0.3 Virtual variant tree                                               |     |

|----|-------|------------------------------------------------------------------------|-----|

|    | 5.10  | 0.4 Layered nodes                                                      | 112 |

| 5  | 5.11  | SUMMARY                                                                | 114 |

| 6  | API   | PLICATION OF THE VFV TO SEARCH ORIENTED PATTERN MATCHING               |     |

| ME | THO   | DS                                                                     | 117 |

| 6  | 5.1   | INTRODUCTION                                                           | 117 |

| 6  | 5.2   | HYBRID LAYER                                                           | 117 |

|    | 6.2.  | 1 Positioning of the Hybrid layer                                      | 118 |

|    |       | 2 Cir_VirtualBuilder, the concretisation of the Virtual_ElementBuilder |     |

| 6  | 5.3   | ADAPTATIONS OF THE FLAT ALGORITHM.                                     |     |

| 6  | 5.4   | HIERARCHICAL RESULT REPORTS                                            | 122 |

| 6  | 5.5   | EXAMPLE OF THE MATCHING PROCESS BY INCREMENTAL HIERARCHICAL STRUCTURAL |     |

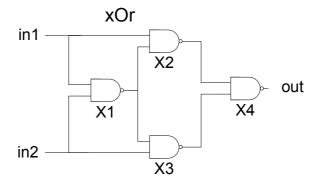

| Р  | ATTEF | N MATCHING                                                             | 124 |

|    | 5.6   | CASE STUDY                                                             |     |

| 7  | CO    | NCLUSION                                                               | 133 |

# Appendix

| APENDIX A (PERSONALISATION BY VARIANTS)         | 137 |

|-------------------------------------------------|-----|

| APPENDIX B (FINGERPRINT VERIFICATION PRINCIPLE) | 143 |

| APPENDIX C (HIERARCHICAL MATCHING EXAMPLE)      | 144 |

# Table of figures

| FIGURE 1 1-1 - | TYPICAL TOOL EVOLUTION CURVE                                           | 14   |

|----------------|------------------------------------------------------------------------|------|

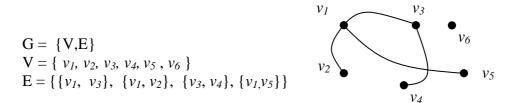

|                | EXAMPLE OF THE GRAPH NOTATION.                                         |      |

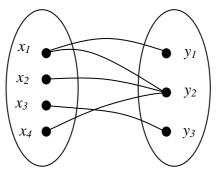

|                | BIPARTITE GRAPH                                                        |      |

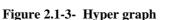

|                | HYPER GRAPH                                                            |      |

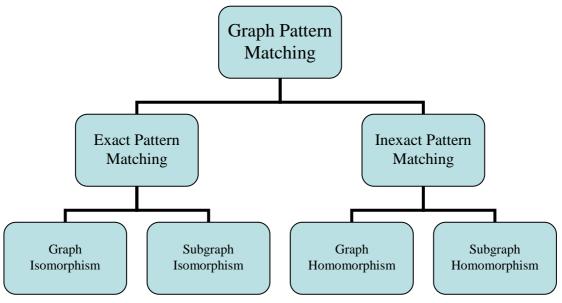

|                | CLASSIFICATION OF THE PATTERN MATCHING IN GRAPHS.                      |      |

|                | A) STANDARD GRAPH WITH ONE CLASS OF VERTICES. B) BIPARTITE GRAPH.      |      |

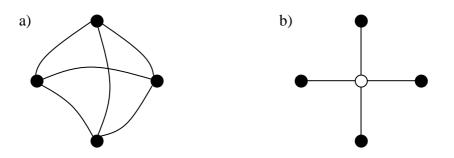

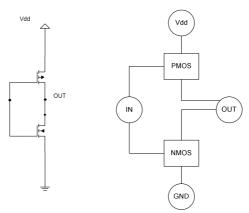

|                | BIPARTITE GRAPH REPRESENTATION OF AN INVERTER CIRCUIT                  |      |

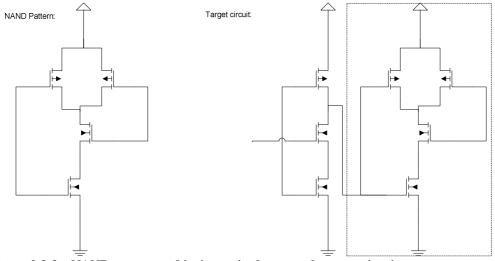

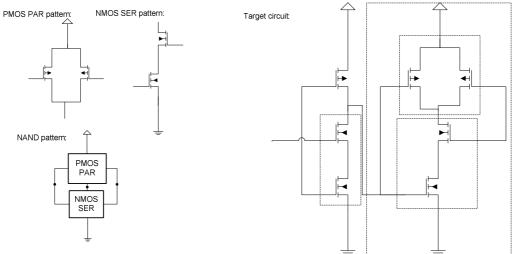

|                | NAND PATTERN AND ITS IMAGE IN THE EXAMPLE TARGET CIRCUIT               |      |

|                | INAND PATTERN AND ITS IMAGE IN THE EXAMPLE TARGET CIRCUIT              |      |

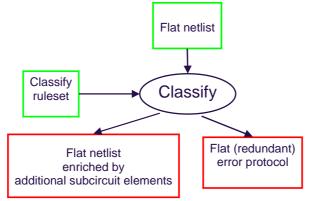

|                | PATTERN MATCHING TOOL CCLASSIFY – EXECUTION FLOW                       |      |

|                |                                                                        |      |

|                | CLARULA LANGUAGE STRUCTURE                                             |      |

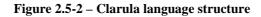

|                | OPTIONAL PORT USAGE EXAMPLES.                                          |      |

|                | EXAMPLE OF THE MATCHING PROCESS                                        |      |

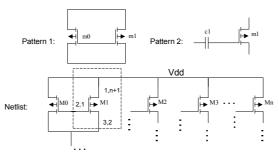

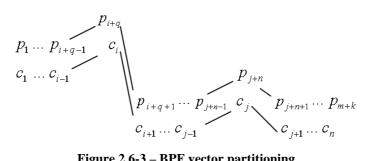

|                | BPF VECTOR PARTITIONING.                                               |      |

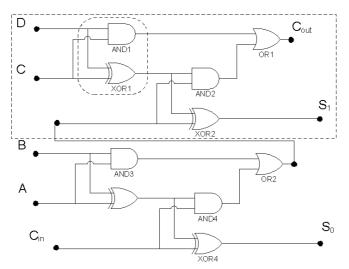

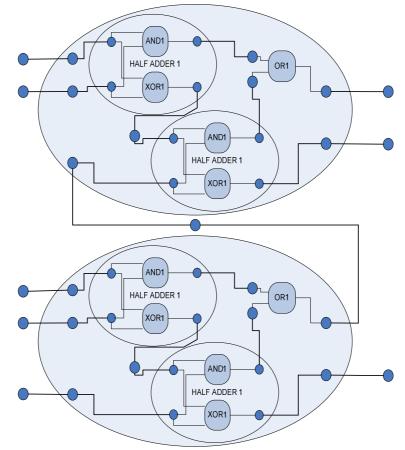

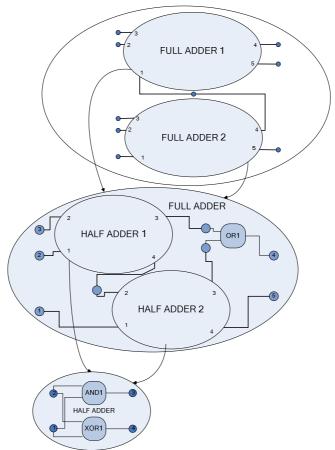

|                | FLAT REPRESENTATION OF THE 2-BIT ADDER.                                |      |

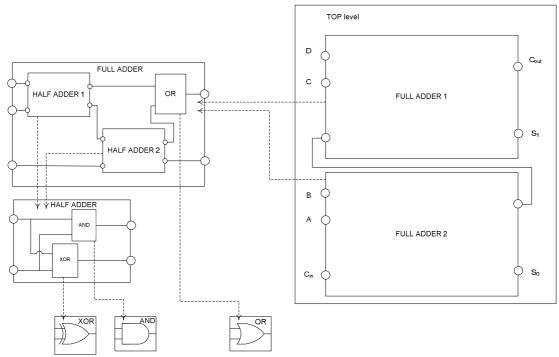

|                | HIERARCHICAL REPRESENTATION OF THE 2-BIT FULL ADDER.                   |      |

|                | ENCAPSULATED HIERARCHICAL GRAPH EXAMPLE.                               |      |

|                | FOLDED ENCAPSULATED HIERARCHICAL GRAPH EXAMPLE.                        |      |

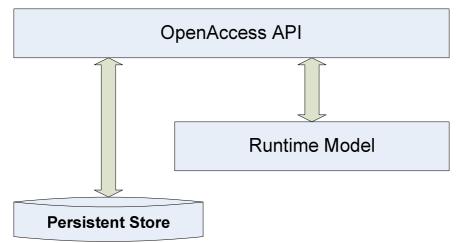

|                | THE CONCEPTUAL DIAGRAM OF THE OPEN ACCESS DATABASE                     |      |

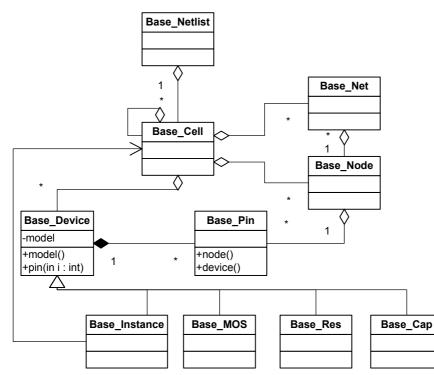

|                | UML MODEL OF THE NLDB DATABASE.                                        |      |

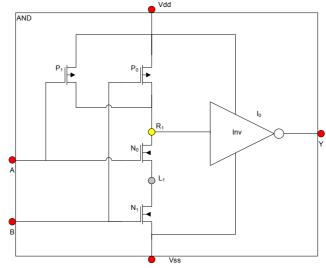

|                | LOGICAL AND GATE CELL                                                  |      |

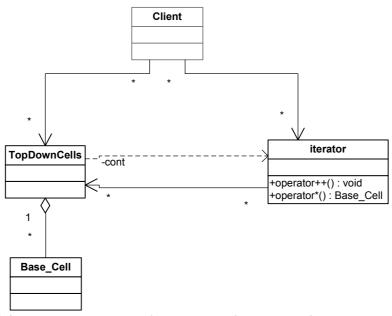

|                | TOP-DOWN CELLS CONTAINER.                                              |      |

|                | AN INDIAN OR AN ESKIMO?                                                | . 59 |

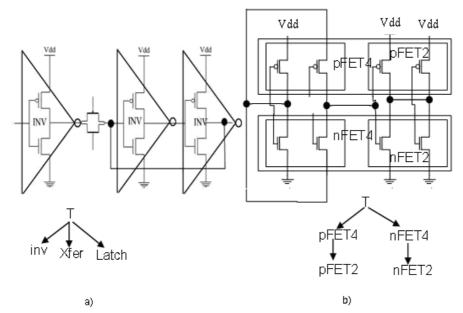

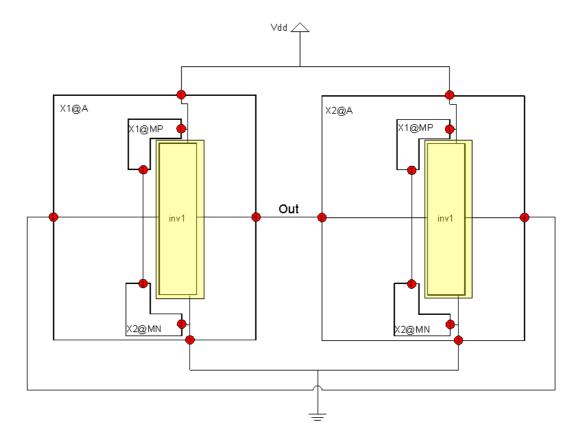

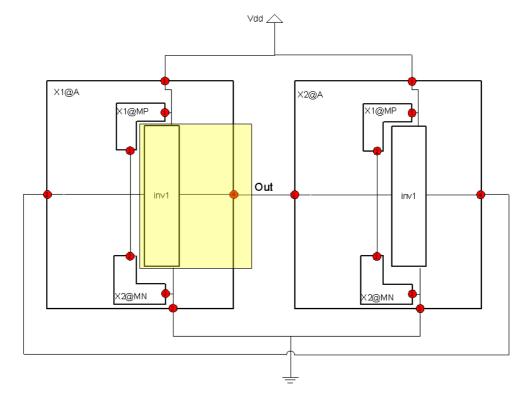

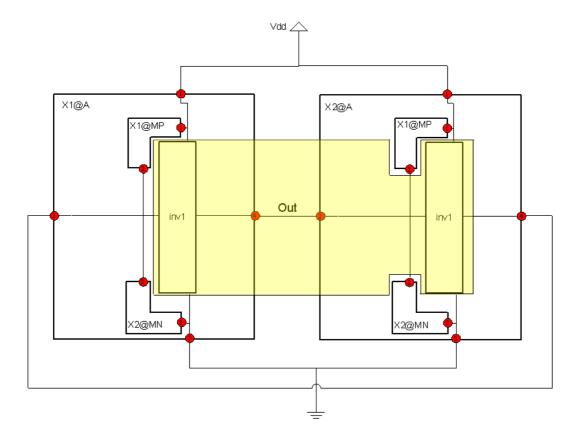

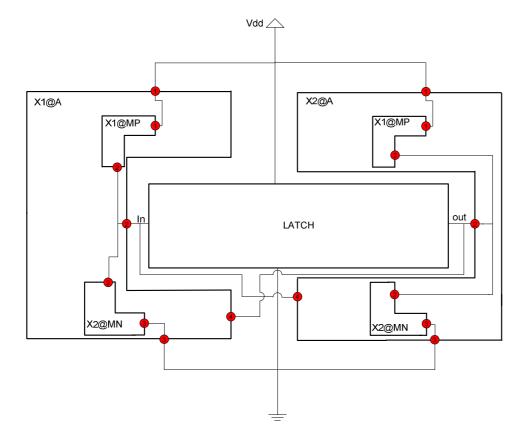

|                | IDENTICAL DRIVER AND LATCH CIRCUIT THAT HAS TWO DIFFERENT HIERARCHICAL |      |

|                | 5                                                                      |      |

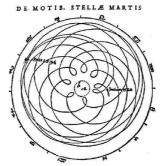

|                | THE PATH OF PLANET MARS IN THE GEOCENTRIC SYSTEM - THE ANALOGY         |      |

|                | CHAINING THE TRANSFORMATIONS OF THE HIERARCHY                          |      |

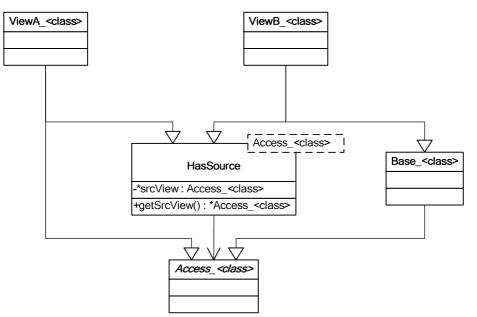

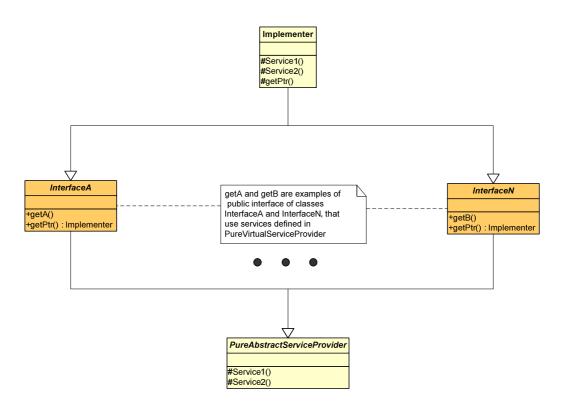

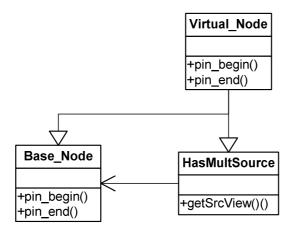

|                | ACCESS LAYER CLASS DIAGRAM                                             |      |

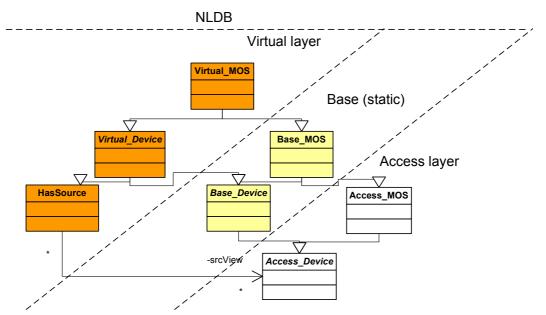

|                | STATIC BASE VS. ACCESS LAYER                                           |      |

|                | TEMPLATED HASSOURCE CLASS DEFINES THE LAYERING PROPERTY                |      |

|                | VIEW POSITIONING RELATIVE TO AL LAYER, STATIC BASE AND OTHER VIEWS.    |      |

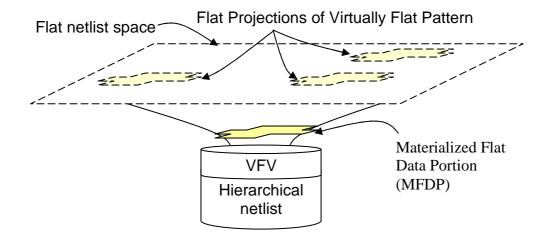

|                | THE CONCEPTUAL DIAGRAM OF THE VIRTUALLY FLATTENED VIEW.                |      |

|                | HIGH LEVEL ARCHITECTURE OF THE VIRTUALLY FLATTENED VIEW.               |      |

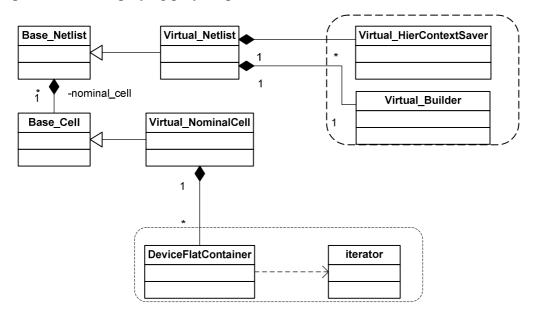

|                | VIRTUALLY FLATTENED VIEW LAYER PLACEMENT INSIDE NLDB CLASS HIERARCHY   |      |

|                | SPECIFIC_PIN FUNCTION CODE                                             |      |

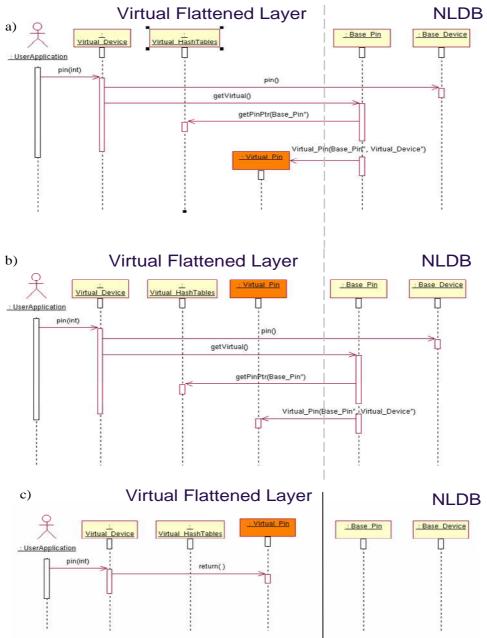

|                | SEQUENCE DIAGRAM OF VIRTUAL_PIN OBJECT AQUISITION                      |      |

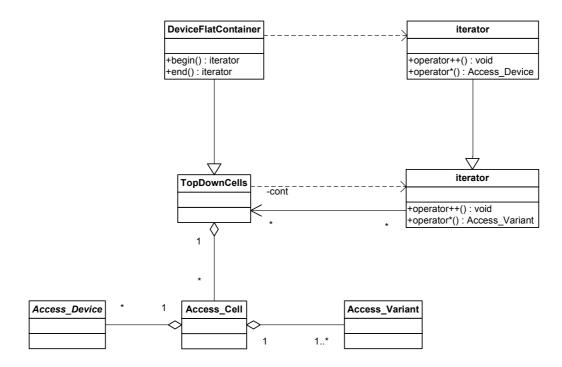

|                | CLASS DIAGRAM OF DEVICEFLATCONTAINER                                   |      |

|                | EXAMPLE OF DYNAMIC DEVICEFLATCONTAINER CONTENT                         |      |

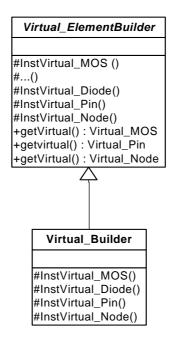

|                | VIRTUAL_ELEMENTBUILDER ARCHITECTURE                                    |      |

|                | EXAMPLE METHOD OF THE GETVIRTUAL() FAMILY                              |      |

|                | OBJECT WITH ROLES – DESIGN PATTERN PROPOSAL                            |      |

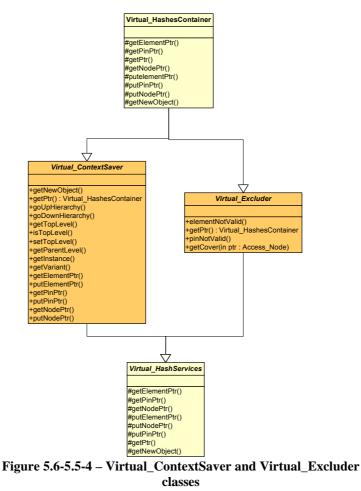

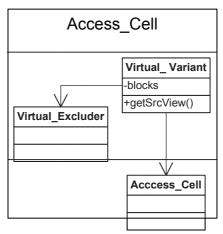

|                | 5-4 – VIRTUAL_CONTEXTSAVER AND VIRTUAL_EXCLUDER CLASSES                |      |

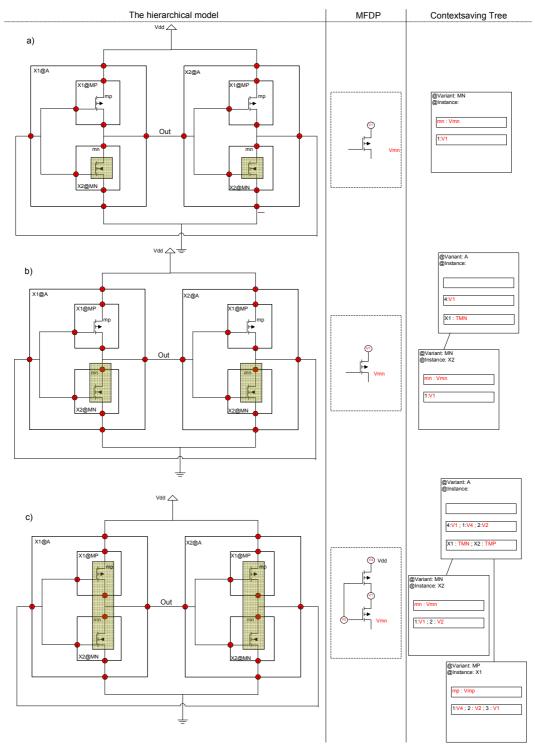

|                | THE EXAMPLE OF THE DEVELOPMENT OF THE CONTEXT SAVING TREE              |      |

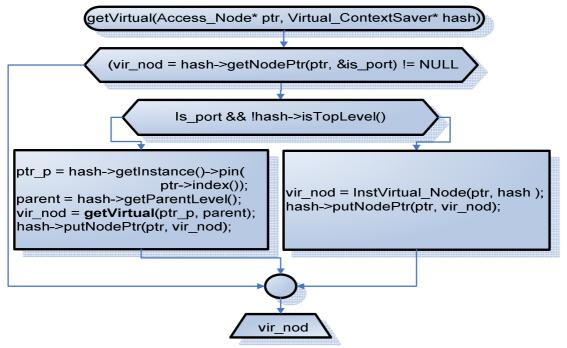

|                | ALGORITHM OF THE FUNCTION GETVIRTUAL(ACCESS_NODE* PTR)                 |      |

| FIGURE 5.7-1 - | RELATION BETWEEN VIRTUAL_NODE CLASS AND BASE_NODE CLASS.               | .95  |

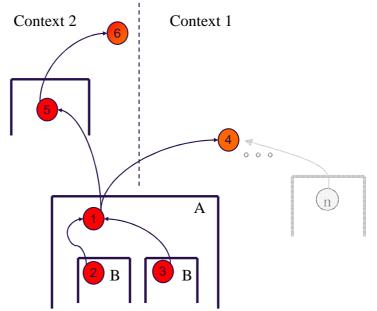

|                | EXAMPLE OF A MULTI-CONTEXT NODE.                                       |      |

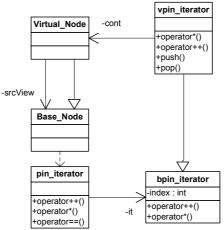

|                | POSITIONING OF THE VPIN_ITERATOR CLASS IN THE CSI                      |      |

|                | ARCHITECTURE OF VPIN_ITERATOR AND IT'S RELATION TO VIRTUAL_NODE        |      |

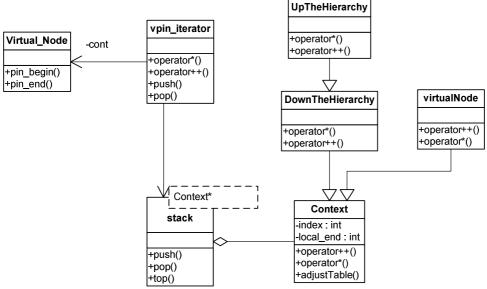

|                | OPERATOR++() METHOD OF THE VPIN_ITERATOR CLASS                         |      |

|                | OPERATOR++() OF THE CLASS DOWNTHEHIERARCHY                             |      |

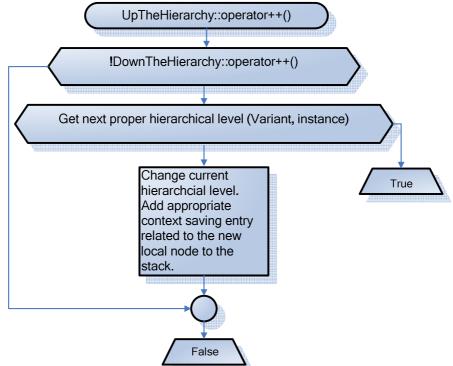

| FIGURE 5.7-7 - | BLOCK DIAGRAM OF THE OPERATOR++() METHOD FROM UPTHEHIERARCHY CLASS 1   | 100  |

|                | MULTI-CONTEXT TOPOLOGY EXAMPLE                                         |      |

| FIGURE 5.8-2 - | MOTIVATION FORT HE INTRODUCTION OF MEMENTO.                            | 103  |

|                | EMBOSSING STEP                                                         |      |

|                | EXAMPLE OF PORT CREATION                                               |      |

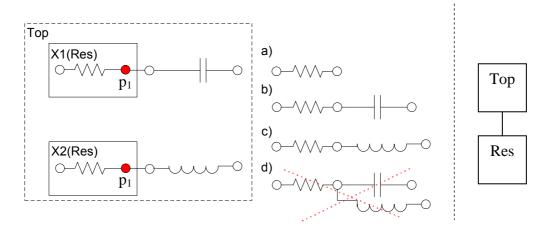

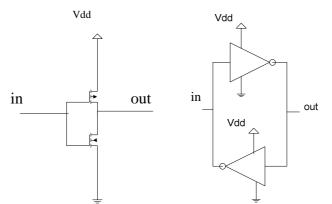

| FIGURE 5.10-1  | - TOPOLOGY ADAPTATION PRINCIPLE EXAMPLE                                | 107  |

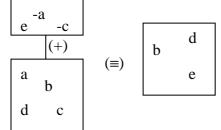

| FIGURE 5.10-2 - RECOURSIVE REPRESENTATION OF THE ABSTRACT INTERFACE OF THE CLASS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Access_Variant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 108     |

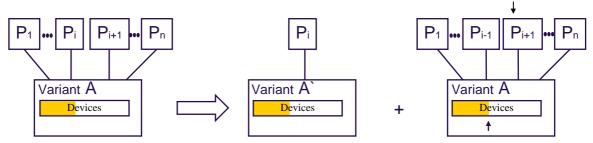

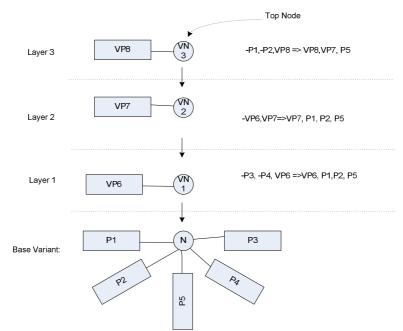

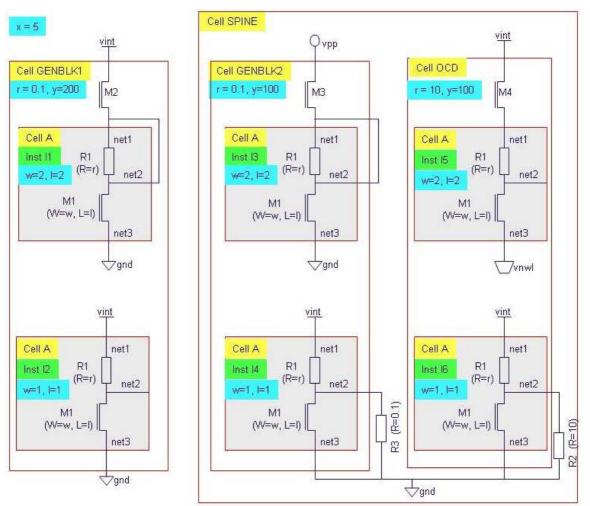

| FIGURE 5.10-3 – THE EXAMPLE OF THE TECHNIQUE OF TOPOLOGY ADAPTATION.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 109     |

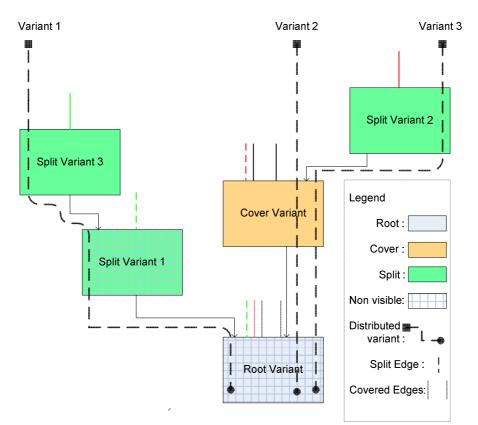

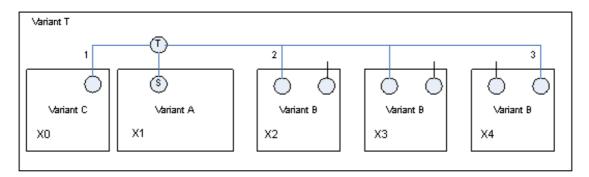

| FIGURE 5.10-4 – DISTRIBUTED VARIANT TREE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 111     |

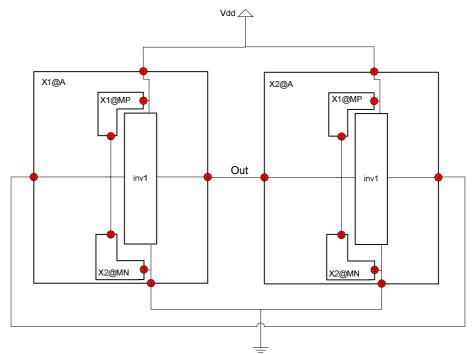

| FIGURE 5.10-5 – EXAMPLE OF THE DISTRIBUTED NODE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 113     |

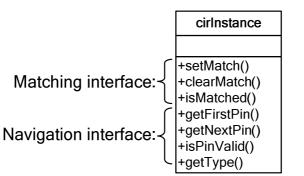

| FIGURE 6.2-1 – INTERFACE OF THE CIRINSTANCE CLASS OF THE CLASSIFY PROJECT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 118     |

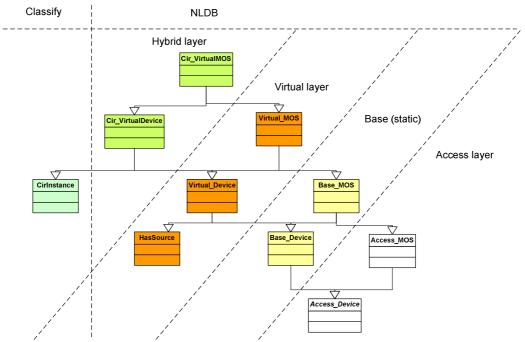

| FIGURE 6.2-2 – PLACEMENT OF THE HYBRID LAYER CLASSES IN THE ACCESS_DEVICE INHERITANC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Έ       |

| DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 119     |

| $FIGURE\ 6.6-1-STRUCTURAL\ PATTERN\ MATCHING\ TOOL-CLASSIFY\ -\ ALGORITHM\ EVOLUTION\ AND ADDID ADDID$ | JD      |

| AVAILABLE VERSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 125     |

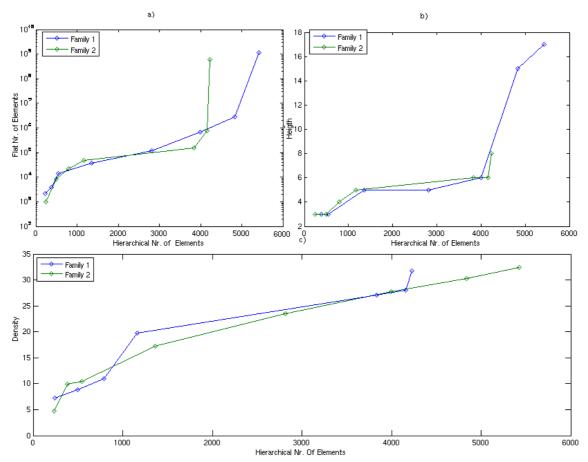

| FIGURE 6.6-2 – QUANTITIES OF THE EXAMPLE HIERARCHICAL NETLIST FAMILIES.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 126     |

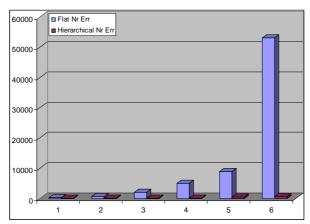

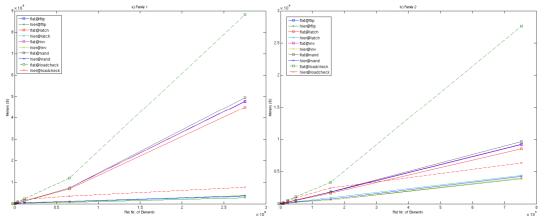

| FIGURE 6.6-3 - NR. HIER. AND FLAT MATCHES FOR DIFFERENT HIERARCHICAL NETLISTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 128     |

| FIGURE $6.6-4 - L$ inear distribution of the ratio between the number of flat reports an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D THE   |

| HIERARCHICAL REPORTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 128     |

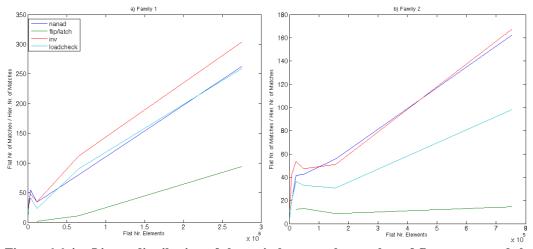

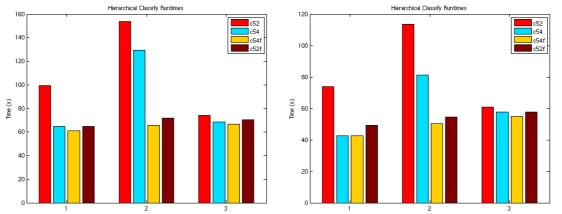

| FIGURE 6.6-5 – TIME COMPLEXITY OF DIFFERENT ALGORITHM VERSIONS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 129     |

| FIGURE 6.6-6 – MEMORY CONSUMPTION OF THE DIFFERENT CLASSIFY VERSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 130     |

| FIGURE 6.6-7 – RUNTIME REQUIREMENTS FOR THE EXAMPLES IN THE DOMAIN WHERE NO FLATTEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | JING IS |

| POSSIBLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |

| FIGURE A-1 – VARIANT CRITERIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 138     |

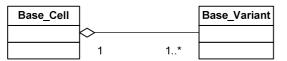

| FIGURE A-2 - RELATION BETWEEN BASE_CELL AND BASE_VARIANT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 139     |

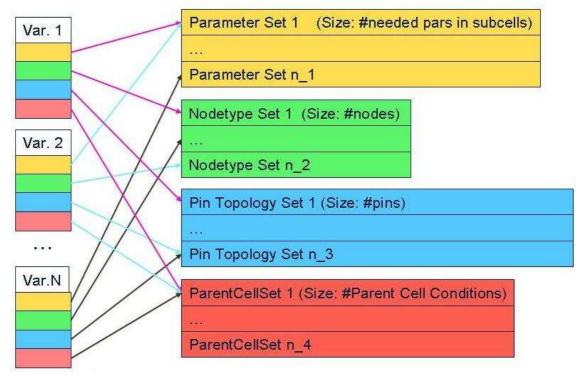

| FIGURE A-3- VARIANT CRITERIA STORING DATA STRUCTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 140     |

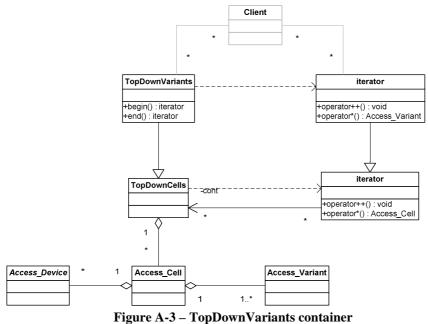

| FIGURE A-3 – TOPDOWNVARIANTS CONTAINER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 141     |

## 1 Introduction

### 1.1 Motivation

The number of transistors that can be placed inexpensively in an integrated circuit has been increasing exponentially for more than four decades, confirming the observations and predictions of Moore's Law [1]. In fact, it has been doubling approximately every two years. For dynamic memory (DRAM) chips the growth in complexity has been even faster, as their capacity doubles about every one and a half years. Integrated circuit design must keep step with the increasing complexity. The fabrication setup process of VLSI designs is very expensive, as well. Each mask set that is necessary to be printed prior to massive production of micro-chips costs several millions of dollars. Further, the time needed for the development of a modern semiconductor product is critical. "Time to market" is typically given in very narrow windows. If one misses the optimal time to ship a new product, one also leaves the most of the revenue to the competitors. In memory production business, avoiding mentioned cost penalties is even more crucial as the margin in that business is very low. For given reasons no trial and error approach is allowed in order to prove the correctness of a design that is to be produced. Thus, verifying and proving that the design architecture is correct and feasible to manufacture in the given realistic technology prior to actual fabrication (achieving "first time write" principle) is utterly important.

The above stated requirements have coined numerous methodologies to model and check the IC designs. One of the central methods to fight the design complexity is employment of the concept of hierarchical abstraction. The overall development of electronic designs is colored by hierarchical approach, both from designing and building the schematics to the verification process. Different tools were introduced over time to support the verification process, thus to check the designs from various aspects. Depending on actual technologies the set of tools employed to perform the verification adapts and evolves. As the technology develops and inevitably shrinks to smaller scales different new problems related to the physical effects that could be neglected in the past emerge. In order to treat these new issues we have often new tools that get integrated into the design and verification methodology.

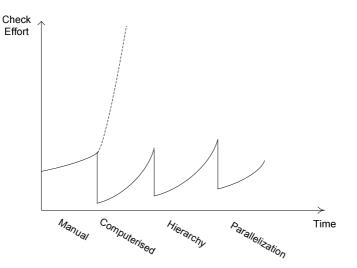

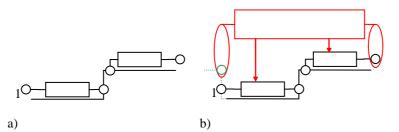

The fact that the designs are hierarchical shapes EDA tools. The tools can greatly benefit from the hierarchy as it offers completely irredundant view on a design, but to achieve that "oasis" an often big price mirrored in the required solution algorithm complexity has to be paid. In some cases this complexity is moderate and there are even tools that naturally benefit from the hierarchical representation, on the other hand there are tools for which the years of development are necessary in order to reach the stage where they can successfully employ the hierarchical concept. Making tools hierarchical can be seen also as one step in the tool evolution process. The typical development of the tool is driven by the importance of the check it performs and the complexity of the data that is verified. As the data which is the point of analysis constantly gets more complex and thus cumbersome, new and new solutions have to be integrated into the tool methodology to keep the effort spent to manage the data in acceptable range. The graph given in Figure 1.1-1 is showing the typical effort "waves" [2] that the tool/check experiences during its evolution. In the example we see that the check was at first performed manually, that was possible e.g. in the times

Figure 1.1-1 – Typical tool evolution curve

and cases when the designs were not having more than 100 transistors. As the data complexity has grown (exponentially), to prevent the exponential growth of check effort (given as a dotted line) a computer tool gets introduced. The tool in the moment when it is introduced brings amazing enhancement and we can notice the drop of effort to the values that are even smaller than the effort employed at the beginning of the evolution. Cycles like this repeat after each (revolutionary) improvement forming the wavy shape.

Depending on the evolutive stage, at the given current state of the art we have two kinds of tools: first that have reached the development stage to work directly on the hierarchical designs and the second which consists of the tools whose algorithmic implementations work exclusively on the designs that were previously flattened, thus simplified. The flattening process collapses all hierarchical levels and makes the model of the IC design whose layout is identical to that of a chip which is being printed into silicon. An additional class of tools (filtering tools) that enable flattening and other helpful transformations of the hierarchical designs have emerged, as well.

Today, to the first group typically belong important physical (design) rule checks (DRC) and layout vs. schematics (LVS) methods. Accordingly, in Electrical Rule Check (ERC) domain, where one checks the electrical correctness of the design, we have a lot of methods that are implemented so that they can benefit from the hierarchy, e.g. ESD checks, floating nodes check and device high voltage checks (where one checks if the given device in the design gets exposed to voltages it can't withstand). As another example device reliability checks can be considered, where one adapts the device robustness to its duty cycle (the frequency of exposing the device to the stressed, non-conducting, mode). In all of these checks one does not need to have the broad information about the environment in which a given device is defined.

In cases where this is needed, the environment typically crosses hierarchical boundaries and is orthogonal to them. In these cases introducing the algorithm that works directly on the hierarchical data is far from trivial. In some cases the solutions for these problems were found, like in mentioned DRC checks, but still, as we have pointed out, in most of the cases we perform the algorithm on flattened netlists. One of the examples is the parasitic extraction problem. The dependencies between parasitic nets are typically cross-hierarchical and instance dependent.

Another, for the motivation of this thesis the most important, example of the tools that work on flattened schematic data are those that employ structural pattern

matching in electronic designs. These tools are frequently used in ERC, but also can enhance different other areas of EDA. In some sense structural pattern matching makes the schematic design processing more intelligent. By employing the matching one can become aware of the context in which a given design device is used and thus gain additional power to optimize the given device or to analyze its configuration with greater precision finding unwanted incorrectness.

One important realistic application of this process is the ERC check where one sets the proper dimension of the drivers of the latches in the electronic circuits. The ratio of the parameters of the transistors that are members of the given driver circuit have to be adjusted to the driven circuit load. This is a task suitable for pattern matching. One can identify all latches in the electronic circuit and than find their corresponding drivers. After this step one can compare the parameters of the transistors identified as driver building elements to the requirements that are imposed to them and adjust them. As this adjustment is highly specific to the given instantiation place and the designers that employ hierarchy and build different contexts out of generic parts (predefined subcircuits) can't be aware of all quantitative aspects easily, the benefit of a tool that pin points incorrect configurations is vital.

As we have mentioned one of the prerequisites (a pre-processing step) for today's state of the art structural pattern matching for IC circuits is assuring that input schematic designs are flat. This is present throughout the community for, to our knowledge, all available solutions.

This approach introduces several disadvantages. First, the size of the flat design can't be even compared to the hierarchical and it overwhelms the typical resources of today's computers. If the analysis is still possible the memory requirements are then typically so high that more expensive 64-bit machines are required and the corresponding runtime becomes an issue, too. One of the most challenging problems that comes as a consequence of the fact that the transformed (flattened) design is used is back-annotating the results to the original schematics. This can be difficult as, by working on the flat netlist, we obtain redundant results that are over-bloated and hard to compare (and find out that they are actually coming from different occurrences of the identical subcirucit of the hierarchical designs). The described problem creates additional time demanding analysis activity (man power) of the tool user and disables the automatization of the process and its integration to modern hierarchical design development environments.

For that reason, there is a need to enhance the structural pattern matching process and solve the algorithmically very demanding problem in order to allow performing of that task directly on the hierarchical schematic designs. Similar problems to those that we have pointed out in the above text are present in all of the tools that are, at the common state of the art, performing checks on the flattened netlists.

### 1.2 Objectives and scope

Our main goal is to achieve the algorithmic solution for the problem of structural pattern matching in hierarchical designs. Since the complete proven solution(s) for pattern matching problem in flat IC designs already exist and also other tools that were written to work on flat data share some similar obstacles which disable them from running hierarchically, we want to try to find a common solution that could be applied to any flat algorithm. For this reason, we have decided to search for our solution directly in the database which prepares and exposes the design data to the client application. We want to upgrade the standard database presenting abilities by allowing views which make the hierarchical organization of the given design relative.

The fact that the modern, standardized EDA databases are typically objectoriented gives us a beautiful chance to include advanced and very useful concepts that the object orientation brings in our solution. Hence, for reading and understanding of this thesis one needs to be familiar with advanced object-oriented concepts and UML notation language, which is the most suitable and in the same time the most general way to describe different aspects of the object oriented concepts. Furthermore, our solutions will include different design patterns that make the solution more robust.

The expected results are at first, the functional correctness of the model that needs to present the data to the user algorithm in a (friendly) flat way and keep it consistent with the original hierarchical data. We further expect that the upgraded originally flat structural pattern matching tool run generates irredundant results after, by our contribution possible, precise calculations directly in the place where a given topological context has been defined (relative to the specific subcircuit). Additionally, we expect better runtime of the pattern matching application and more economic memory consumption. This is challenging as the problem of structural pattern matching to which we want to apply the model that presents the hierarchical data in a flat fashion is NP complete. Taming these two parameters should push the border of the size of the designs that are manageable towards today's full chip sizes. That fact puts one into position to run the corresponding checks in realistic application cases in sublinear times (sublinear concerning the flat netlist size). We expect that the algorithm complexity depends rather on the hierarchical than on flat design quantities.

One additional important quality that we want to achieve is to use the existing successful pattern matching industrial project completely transparently with the upgraded database and that the solution we propose is possible to be used with no or small corrections with other tools that favour flat to hierarchical netlist representation. Note that possible corrections of the solution that would be applied to other tools would also be a continuation of this research and would contribute to the evolution of the hierarchy transforming (hiding) data presenter.

We will apply the proposed solution to an industrial project, the pattern matching tool - "classify", which implements the incremental structural pattern matching principle (studied by several groups) and experimentally check our expectations and value the benefits that the proposed approach brings. In order to do that we will employ real-life industrial test cases that are thoroughly quantified, so that we can gain confidence and better understand the performed tests' outcome.

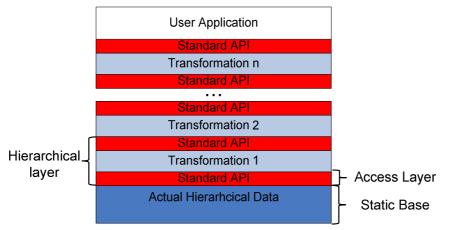

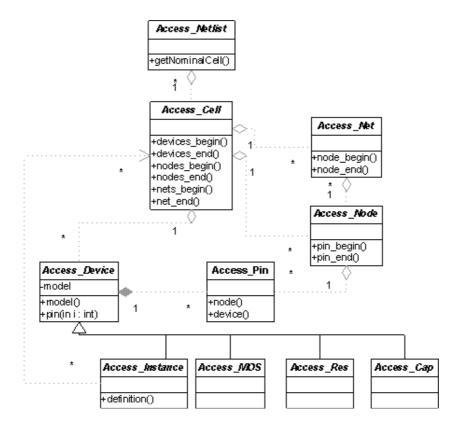

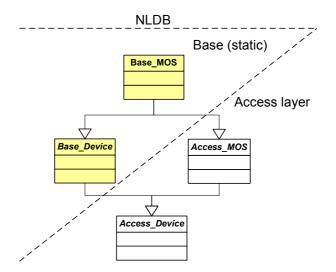

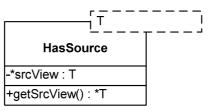

#### 1.3 Outline