### LEHRSTUHL FÜR INTEGRIERTE SCHALTUNGEN Univ.-Prof. Dr.-Ing. I. Ruge, em.

### PERFORMANCE ESTIMATION FOR THE DESIGN SPACE EXPLORATION OF SYSTEM-ON-CHIP SOLUTIONS

#### Nuria Pazos Escudero

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktor-Ingenieurs (Dr.-Ing.)

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr.-Ing. Georg Färber

Prüfer der Dissertation:

- 1. Univ.-Prof. Dr.-Ing. Ingolf Ruge, em.

- 2. Univ.-Prof. Dr. rer. nat. Wolfgang Rosenstiel,

Eberhard-Karls-Universität Tübingen

Die Dissertation wurde am 30.04.2003 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 29.07.2003 angenommen.

## Acknowledgements

First of all, I want to thank Prof. Ingolf Ruge who encouraged and enabled me to pursue this Ph.D. thesis at his institute. Furthermore, I want to thank the members of the dissertation committee, Prof. Wolfgang Rosenstiel and Prof. Georg Färber for the time and effort they gave to this cause.

Specially, I thank my tutor and leader of the networking group at the institute Thomas Wild for motivating me and for his patience. The technical discussions with him have contributed significantly to my scientific work. It has been a pleasure and an honour to work with him. At the same time, I greatly thank Dr. Walter Stechele his daily trust on me.

My very special thanks are directed to Nabil Ouerhani. Without his substantial and daily technical as well as private support and encouragement I would not have been able to reach this goal.

To those individuals who spent their time proof-reading my papers and the manuscript of this work, I am particularly grateful. Their suggestions and corrections were very helpful in clarifying various points that might otherwise have been mistreated or omitted. A special thank goes again to Thomas Wild and to Paul Zuber, to my colleagues Axel Hof, Hubert Mooshofer and Jürgen Foag, to my friends Dr. Magdalena Rafecas, Dr. Javier Bracamonte, Markus Kuhn, Raymond Korhon and, finally, to Ilka Nahmmacher, who read carefully the final version.

I would also like to thank other colleagues I had the pleasure to interact with: Stephan Herrmann, Torsten Mahnke, Raul Medina, Ulrich Niedermeier and Armin Windschiegl. This also includes my former Master's students Susana Martin and Jorge Juan Ramos and the internship student Amit Chaudhari, whose contributions have been particularly valuable.

Concerning my industrial experience, I would like to thank our project partners from Siemens ICN, Karl Schrodi and Dr. Thomas Theimer, for showing me the huge amount of industrial applications the world of networking comprises. I owe many thanks to the system administrators at the institute Wolfgang Kothz and Stephan Herrmann, who always provided quick help for my infinite computer problems. I also want to express my thanks to Verena Draga, Gabi Spöhrle and Doris Zeller for their administrative help.

A particular acknowledgement is directed to the persons who pushed the start of my adventure in Germany, Dr. Teresa Riesgo, Dr. Yago Torroja, Dr. Eduardo de la Torre and Prof. Javier Uceda from the Universidad Politecnica de Madrid.

Last but not least, I cannot forget to thank my dear family their unconditional support and encouragement and my friends all over the world for being there. It is not easy to be far away from home, but they have made it possible that I feel close to them during the last years. I owe special thanks to my parents, Francisco and Aurora, and my sister Montse and my brother Francisco for everything they have done for me and for their blind support. This work is dedicated to my father, who injected me the feeling for engineering.

#### Kurzfassung

Die steigende Komplexität aktueller VLSI–Systeme und die Erhöhung des Marktdrucks für diese Produkte zwingen die Entwickler, sich zu höheren Abstraktionsebenen zu bewegen und den Entwurfsablauf mit ausführbaren Spezifikationen zu beginnen. Auf der System–Ebene wird sowohl der Ablauf zur Auswahl der optimalen Architektur als auch die Partitionierung der Funktionalitäten beträchtlich beschleunigt.

Die Entwurfsraum-Untersuchung ist eine der wichtigsten Aufgaben innerhalb des Entwurfs auf System-Ebene. Sie versucht, die beste Architektur-Partitionierungsalternative zu finden, d.h. die optimale Partitionierung der Systemfunktionalitäten zwischen Hardware und Software und gleichzeitig die richtigen Architektur-Ressourcen, welche die Anforderungen der Spezifikation erfüllen. Die Performance-Abschätzung spielt eine wichtige Rolle innerhalb der Entwurfsraum-Untersuchung, um die Entwurfsalternativen einzuordnen. Performance-Abschätzung wird mit der Bestimmung der Auslastung und des Durchsatzes der Ressourcen gekennzeichnet.

Die vorliegende Arbeit stellt eine neuartige Methode für die Performance–Abschätzung auf der Systemebene vor, die auf der Beschreibungssprache SystemC beruht. Wesentlich bei diesem Ansatz ist, dass kein aufwendiger Umbau des Strukturmodells erforderlich ist, um verschiedene Partitionierungsalternativen zwischen Hardware und Software zu untersuchen. Folglich ist der Modellierungsaufwand bei der Verwendung der vorgeschlagenen Methode wesentlich niedriger, als wenn ein Strukturmodell der Zielarchitektur auf einer niedrigeren Abstraktionsebene verwendet würde. Gleichzeitig beschleunigt diese Methode die Simulation und verbessert die Genauigkeit der Ergebnisse bisheriger Ansätze. Diese Eigenschaften ermöglichen eine schnelle und einfache Exploration von mehreren Alternativen bei einer Entwurfsraum–Untersuchung.

Die vorgeschlagene Performance–Abschätzungsmethode ist dafür gedacht, innerhalb eines Hardware–Software Co–Design Ablaufs integriert zu werden, bei dem mehrere Zielarchitekturen untersucht werden und eine einfache Zuordnung der Funktionen zur Zielarchitektur möglich sein sollte.

Der Industriestandard SystemC wurde als Beschreibungssprache für die Implementierung der Methode gewählt. Es handelt sich dabei um eine neue Verwendung dieser Sprache, wobei die Systemfunktionalitäten und die Eigenschaften der Zielarchitektur in Form eines Graphen funktional beschrieben sind. Frühere Ansätze haben SystemC angewendet, um die Systemfunktionalitäten und die Zielarchitektur strukturell zu beschreiben. Die Methode beruht auf drei Modellen, dem funktionalen, dem architekturalen und dem Kommunikationsmodell, die aufeinander aufbauen. Die Spezifikationsfunktionen sind in Form eines Prozessgraphen beschrieben, der mit den Eigenschaften der Zielarchitektur weiter gekennzeichnet ist. Diese Annotierungsinformation bezieht sich auf die Abbildung und das Scheduling der Funktionen zu Prozessierungseinheiten und auf die Betrachtung der Systemkommunikation und der Lösung von Zugriffskonflikten. Der Implementierungsablauf für die Erzeugung der drei Modelle ist anhand entsprechender Konfigurationsdateien automatisiert.

Für die Verifikation der vorgeschlagenen Methode wurde eine flexible Co–Simulationsplattform entwickelt, die ein strukturelles Modell der Zielarchitektur darstellt. Ein Zyklen–genaues Modell der Plattform wurde implementiert. Es dient als Referenz für die Bewertung der Ergebnisse der vorgeschlagenen Methode. Auf Basis der Ergebnisse der Plattform wurden die Simulationszeit und der Ausgangsdurchsatz der neuen Methode verifiziert.

Die Methode wurde auf ein Hardware–Software System für die Bearbeitung von Netzwerk–Protokollen erfolgreich angewendet. Eine System–on–Chip Architektur, die mehrere eingebettete Prozessoren, die ihrerseits Multi-Threading unterstützen, und dedizierte Hardware-Beschleuniger beinhaltet, wurde als Zielarchitektur für die Zuordnung der Funktionen ausgewählt. Es wurde gezeigt, dass die neue Methode eine um rund 70% schnellere Simulation als eine Zyklen–genaue Simulation erreicht, während die Genauigkeit der Ergebnisse innerhalb einer akzeptablen Toleranz bleibt (etwa 1,5% Abweichung). Wesentlich dabei ist, dass die Untersuchung von mehreren Partitionierungsalternativen beschleunigt wird. Dies ist durch die Verwendung eines funktionalen Graphenmodells, das zusammen mit Architekturdaten das Verhalten des Systems nachbildet, ermöglicht. Jedes Mal, wenn eine neue Zuordnungsalternative untersucht wird, ist es lediglich nötig, die Konfigurationsinformation für die neue Alternative zu ändern. Auf diese Weise kann das Verfahren zur automatischen Untersuchung einer grossen Anzahl an Architekturalternativen eingesetzt werden.

#### Abstract

The increasing complexity of current VLSI systems and the increase of time-tomarket pressure for these products are forcing the developers to move to higher levels of abstraction and to design products from executable specifications. At the system level, the process towards the selection of the optimal target architecture as well as the partitioning of the functionalities can be considerably accelerated.

Design space exploration is one of the most important tasks of system level design. It tries to find the best architecture–partition alternative, meaning the optimal partition of the system functionalities between hardware and software and, at the same time, the right architecture resources, which meet the requirements of the specification. Performance estimation plays a decisive role inside the design space exploration for ranking the design alternatives. Performance estimation is characterised by measuring utilisation and throughput of the resources.

The present thesis introduces a novel system level performance estimation methodology based on the system level language SystemC. Especially significant is that no costly rebuilding of the structure of the model is necessary in order to explore different hardware–software partition alternatives. Consequently, the modelling effort when applying the proposed method is considerably lower compared to building up a structural model of the target architecture at a lower level of abstraction. At the same time, this methodology speeds up the simulation and enhances the accuracy of the results of existing approaches. All of these characteristics allow for fast and easy exploration of several alternatives during design space exploration.

The performance estimation methodology proposed is intended to be integrated in a hardware–software co-design procedure, where several target architectures have to be explored and an easy re-mapping of the functions onto the target architecture should be possible.

The industry standard language SystemC has been chosen as the description language for the implementation of the methodology. It is noteworthy that this is a new application of this language, where the system functionalities and the characteristics of the target architecture are described functionally in terms of a graph. Existing approaches have applied SystemC to describe the system functionalities and the target architecture in a structural way.

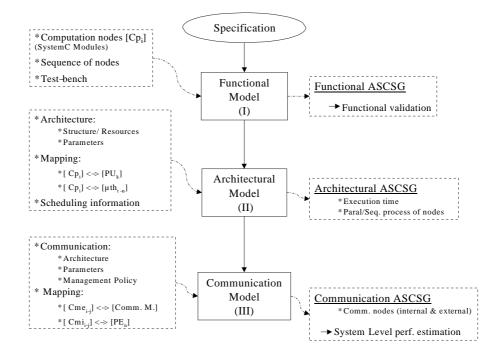

The method is based on three models, the Functional, Architectural and Communication model, each of which is built on top of the previous one. The functions of the specification are described in terms of a process graph, which is further annotated with the characteristics of the target architecture. This annotation information is related to the mapping and scheduling of the functions to the processing units and to the consideration of the system communication and the solution of access conflicts. The implementation procedure towards the creation of these three models has been automated by means of corresponding configuration files.

For the verification of the proposed method, a flexible hardware–software co-simulation platform is developed, which represents a structural model of the target architecture. A cycle accurate model of this platform is implemented, which serves as a reference for the evaluation of the results of the proposed methodology. Taking the results of the platform as a basis for the comparison, the simulation runtime and the output throughput of the new methodology are verified.

The methodology has been successfully applied to a hardware–software system for networking protocol processing. A System-on-Chip architecture, which comprises multiple embedded processors, each of it with multi-threading support and dedicated hardware accelerators, is taken as target architecture for the mapping of the functionalities. It is demonstrated that the new methodology achieves about 70% faster simulations than a cycle accurate simulation, while maintaining the accuracy within an acceptable tolerance (around 1.5%). Significantly by the proposed methodology is that it considerably accelerates the exploration of several partition alternatives by applying a functional graph model, which, together with architecture information, reproduces the behaviour of the system. Each time a new partition alternative is explored, it is only necessary to change the configuration information for the new alternative to be tested. In this manner the procedure can be employed for an automatic exploration of a large amount of architecture alternatives.

# Contents

| A             | cknov                 | wledgements                                      | ii   |

|---------------|-----------------------|--------------------------------------------------|------|

| K۱            | urzfa                 | ssung                                            | iii  |

| Al            | bstra                 | $\mathbf{ct}$                                    | v    |

| In            | dex o                 | of Contents                                      | vii  |

| $\mathbf{Li}$ | st of                 | Tables                                           | xiii |

| $\mathbf{Li}$ | st of                 | Figures                                          | xv   |

| Li            | st of                 | Acronyms                                         | xix  |

| 1             | $\operatorname{Intr}$ | oduction                                         | 1    |

|               | 1.1                   | Motivation                                       | 2    |

|               | 1.2                   | Novelty Aspects                                  | 3    |

|               | 1.3                   | Procedure                                        | 4    |

|               | 1.4                   | Structure of the Work                            | 5    |

| <b>2</b>      | Stat                  | te of the Art                                    | 7    |

|               | 2.1                   | Chapter Introduction                             | 7    |

|               | 2.2                   | System Level Design. Languages and Methodologies | 8    |

|     | 2.2.1  | Classical Hard    | dware–Software Co-Design Procedure       | 8  |

|-----|--------|-------------------|------------------------------------------|----|

|     | 2.2.2  | System Level      | Design Procedure                         | 11 |

|     | 2.2.3  | System Level      | Languages                                | 13 |

|     |        | 2.2.3.1 C/C       | ++-Based Languages                       | 15 |

|     |        | 2.2.3.2 Dom       | nain-Specific System Level Languages     | 17 |

|     |        | 2.2.3.3 Exte      | ensions to Hardware Design Languages     | 17 |

|     | 2.2.4  | Computer-Aid      | ded Co-Design Methods and Tools          | 18 |

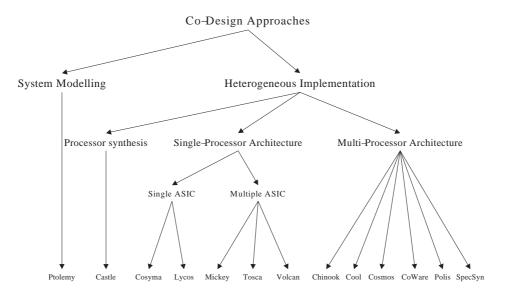

|     |        | 2.2.4.1 Clas      | sification of Co-Design Approaches       | 19 |

| 2.3 | Perfor | mance Estimat     | tion Approaches                          | 25 |

|     | 2.3.1  | Block Level P     | Performance Estimation                   | 25 |

|     |        | 2.3.1.1 Softw     | ware Performance Estimation Techniques   | 25 |

|     |        | 2.3.1.1.          | .1 Cycle-Accurate Performance Model      | 26 |

|     |        | 2.3.1.1.          | 0 1                                      | 26 |

|     |        | 2.3.1.1.          | .3 Original C-Code Annotation            | 26 |

|     |        | 2.3.1.1.          | <i>v</i> 1                               | 27 |

|     |        | 2.3.1.2 Hard      | dware Performance Estimation Techniques  | 27 |

|     |        | 2.3.1.2.          | .1 Local Scheduling Methods              | 28 |

|     |        | 2.3.1.2.          | .2 Global Scheduling Methods             | 28 |

|     | 2.3.2  | System Level      | Performance Estimation                   | 29 |

|     |        | 2.3.2.1 Simu      | ulation-Based Approaches                 | 29 |

|     |        | 2.3.2.2 Trac      | ee-Based Performance Analysis Strategies | 30 |

|     |        | 2.3.2.3 Stat      | ic Performance Estimation Methods        | 31 |

|     |        | 2.3.2.4 Anal      | lytical Performance Estimation Methods   | 32 |

| 2.4 | VLSI   | Architectures for | or Networking Applications               | 34 |

|     | 2.4.1  | Network Infra     | structure                                | 34 |

|   |     |        | 2.4.1.1   | Comput     | er Networks                                   | 34 |

|---|-----|--------|-----------|------------|-----------------------------------------------|----|

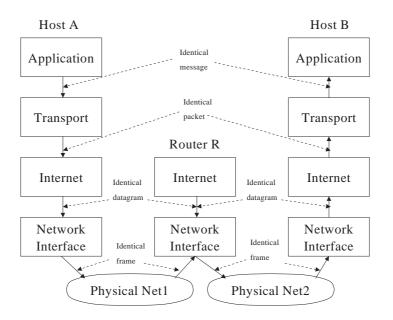

|   |     |        | 2         | .4.1.1.1   | Communication Layers in a TCP/IP Network.     | 35 |

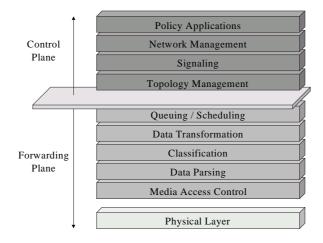

|   |     |        | 2         | .4.1.1.2   | Communication Processing Tasks                | 36 |

|   |     |        | 2         | .4.1.1.3   | Classification of Computer Networks           | 38 |

|   |     |        | 2.4.1.2   | Network    | c Equipment                                   | 38 |

|   |     | 2.4.2  | VLSI N    | etworking  | Architectures Design                          | 39 |

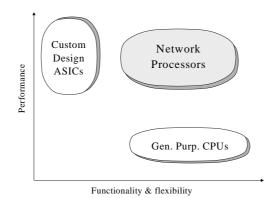

|   |     |        | 2.4.2.1   | Evolutio   | on of VLSI Networking Architectures           | 39 |

|   |     |        | 2.4.2.2   | Design '   | Trade-Offs                                    | 41 |

|   |     | 2.4.3  | Network   | x Processo | Drs                                           | 41 |

|   |     |        | 2.4.3.1   | Commo      | n Characteristics                             | 41 |

|   |     |        | 2.4.3.2   | Main A     | ttributes                                     | 42 |

| 3 | Per | formai | nce Estir | nation f   | or Design Space Exploration                   | 45 |

| Ū | 3.1 |        |           |            | · · · · · · · · · · · · · · · · · · ·         | 45 |

|   | 3.2 | -      |           |            | n                                             | 46 |

|   | 3.3 |        |           |            |                                               | 49 |

|   |     | 3.3.1  |           |            | mation Requirements                           | 50 |

|   |     | 3.3.2  |           |            | Performance Estimation Approaches             | 51 |

|   |     |        | 3.3.2.1   |            | cal Modelling and Evaluation                  | 52 |

|   |     |        | 3.3.2.2   |            | cal Modelling and Evaluation by Means of Sim- | 52 |

|   |     |        | 3.3.2.3   | Instruct   | ion Level Models                              | 53 |

|   |     |        | 3.3.2.4   | Cycle-A    | ccurate Models                                | 53 |

|   |     |        | 3.3.2.5   | RTL an     | d Logic Level Models                          | 53 |

|   | 3.4 | Comp   | arison of | Performa   | nce Estimation Approaches                     | 54 |

|   |     | 3.4.1  | Advanta   | ages and I | Disadvantages                                 | 54 |

|   |     | 3.4.2  | Support   | of Co-De   | esign Procedures                              | 55 |

|   |     | 3.4.3   | Need for Improvements                                                                        | 56 |

|---|-----|---------|----------------------------------------------------------------------------------------------|----|

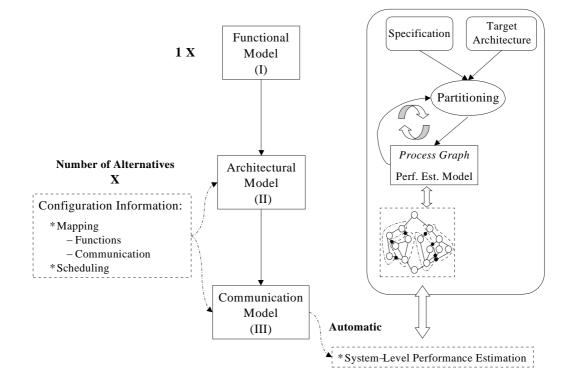

|   | 3.5 | Integra | ation in the Design Flow                                                                     | 57 |

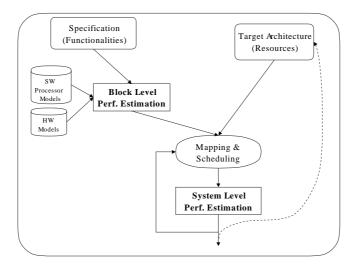

|   |     | 3.5.1   | Inputs Required by the Performance Estimation                                                | 58 |

|   |     | 3.5.2   | Boundary Conditions                                                                          | 59 |

| 4 |     |         | evel Performance Estimation for Multi-Processing, Multi-<br>SoC Architectures                | 63 |

|   | 4.1 | Chapt   | er Introduction                                                                              | 63 |

|   | 4.2 | Funda   | mentals of the Methodology                                                                   | 63 |

|   | 4.3 | Model   | ling Approach                                                                                | 65 |

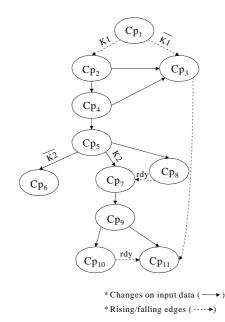

|   |     | 4.3.1   | Functional Annotated SystemC Conditional Synchronisation Graph<br>(Functional ASCSG)         | 66 |

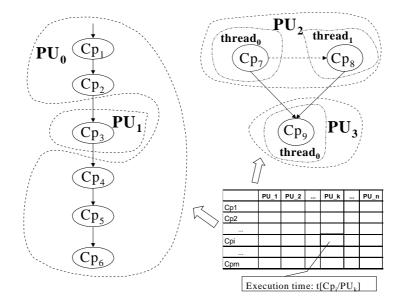

|   |     | 4.3.2   | Architectural Annotated SystemC Conditional Synchronisation<br>Graph (Architectural ASCSG)   | 67 |

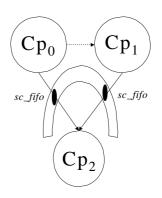

|   |     | 4.3.3   | Communication Annotated SystemC Conditional Synchronisa-<br>tion Graph (Communication ASCSG) | 68 |

|   | 4.4 | Evalua  | ation Approach                                                                               | 70 |

|   | 4.5 | System  | n Performance Estimation Scheme                                                              | 71 |

|   |     | 4.5.1   | Inputs for the Modelling of the ASCSG                                                        | 71 |

|   |     |         | 4.5.1.1 Sequence of Nodes                                                                    | 73 |

|   |     |         | 4.5.1.2 Convergence of Paths                                                                 | 73 |

|   |     |         | 4.5.1.3 Flexible Mapping                                                                     | 74 |

|   |     |         | 4.5.1.4 Multiple Instances of <i>Computation Nodes</i>                                       | 74 |

|   |     | 4.5.2   | Outputs of the Evaluation of the ASCSG                                                       | 75 |

|   |     |         | 4.5.2.1 Functional Validation                                                                | 75 |

|   |     |         | 4.5.2.2 Processing of Nodes                                                                  | 75 |

|   |     |         | 4.5.2.3 Tracking and Monitoring                                                              | 76 |

|   |     |         |                                                                                              |    |

5 Implementation

|   | 5.1                  | Chapt   | er Introd  | uction                             | 77  |

|---|----------------------|---------|------------|------------------------------------|-----|

|   | 5.2                  | Impler  | mentation  | n of the ASCSG                     | 77  |

|   |                      | 5.2.1   | Creation   | of the Functional Model            | 78  |

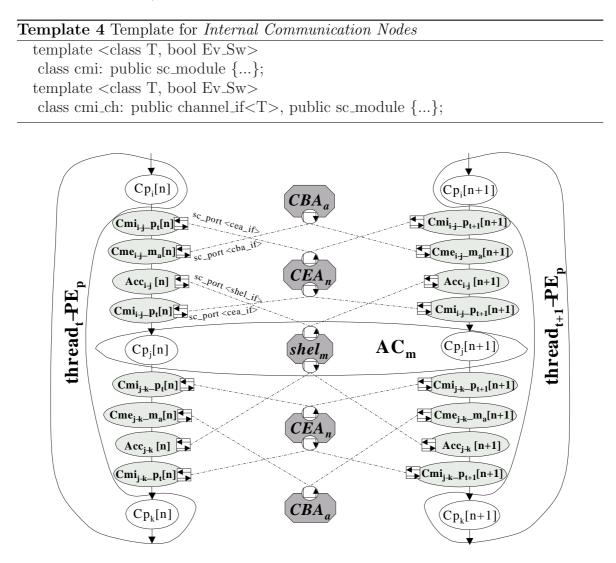

|   |                      | 5.2.2   | Creation   | of the Architectural Model         | 79  |

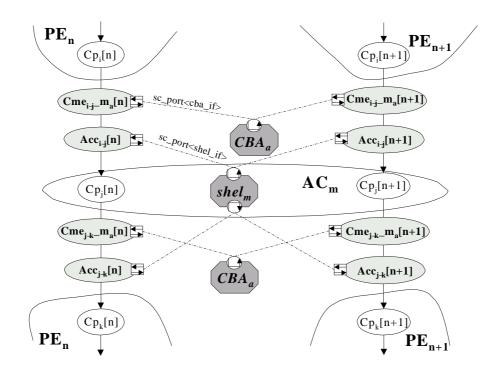

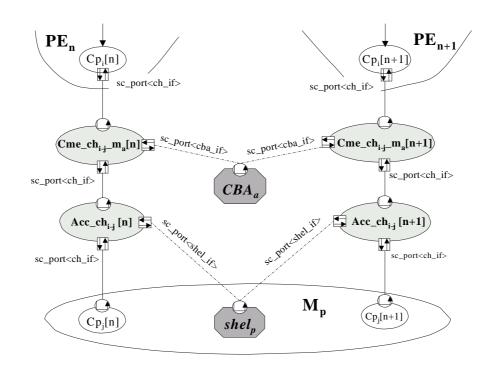

|   |                      | 5.2.3   | Creation   | of the Communication Model         | 81  |

|   | 5.3                  | Autom   | nation Ap  | proach                             | 85  |

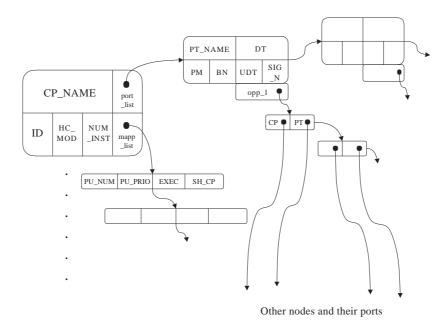

|   |                      | 5.3.1   | Data St    | ructure for the Implementation     | 85  |

|   |                      | 5.3.2   | Configur   | ration Files                       | 88  |

| 6 | Met                  | hodol   | ogy Veri   | fication                           | 93  |

|   | 6.1                  | Chapt   | er Introd  | uction                             | 93  |

|   | 6.2                  | Hardw   | vare–Softv | ware Co-Simulation Techniques      | 94  |

|   |                      | 6.2.1   | Techniq    | ues Requiring Processor Models     | 95  |

|   |                      | 6.2.2   | Techniq    | ues not Requiring Processor Models | 96  |

|   | 6.3                  | Target  | Platforn   | n Architecture                     | 97  |

|   | 6.4                  | Model   | ling Appi  | roach                              | 98  |

|   |                      | 6.4.1   | Skeleton   | of the Co-Simulation Platform      | 99  |

|   |                      | 6.4.2   | Function   | nal Units                          | 101 |

|   |                      |         | 6.4.2.1    | Embedded RISC Processor            | 101 |

|   |                      |         | 6.4.2.2    | Hardware Blocks – Accelerators     | 104 |

|   |                      |         | 6.4.2.3    | Shared Memories                    | 104 |

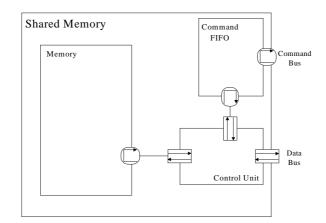

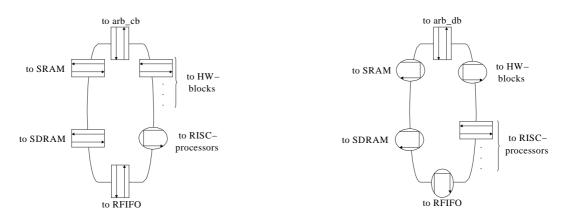

|   |                      | 6.4.3   | Commu      | nication Structure                 | 105 |

|   |                      |         | 6.4.3.1    | Command Bus                        | 106 |

|   |                      |         | 6.4.3.2    | Data Bus                           | 107 |

| 7 | $\operatorname{Res}$ | ults ar | nd Evalu   | ation                              | 109 |

|   | 7.1                  | Chapt   | er Introd  | uction                             | 109 |

|   | 7.2                  | Case S  | Study .    |                                    | 109 |

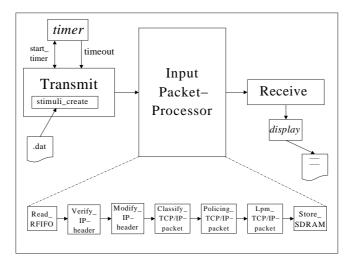

|    |       | 7.2.1  | Packet Processor Functionalities                 | 110 |

|----|-------|--------|--------------------------------------------------|-----|

|    |       | 7.2.2  | TCP/IP Packet Processing Data Flow               | 111 |

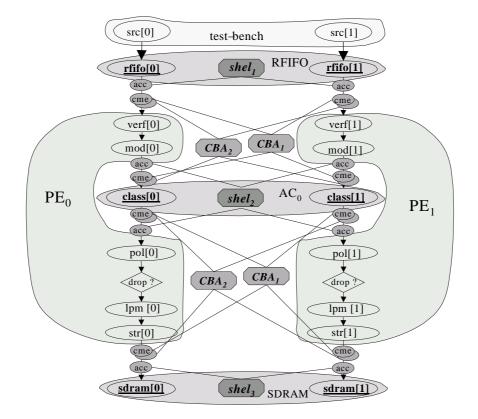

|    | 7.3   | Model  | ling of Architecture–Partition Alternatives      | 112 |

|    | 7.4   | Simula | tion Results                                     | 117 |

|    |       | 7.4.1  | Simulation Environment                           | 117 |

|    |       | 7.4.2  | Simulation Predefinitions                        | 119 |

|    |       | 7.4.3  | Output Throughput                                | 120 |

|    |       | 7.4.4  | Performance Values                               | 120 |

|    | 7.5   | Simula | tion Speed of the ASCSG                          | 124 |

|    | 7.6   | Accura | acy of the ASCSG                                 | 127 |

|    | 7.7   | Model  | ling Effort of the ASCSG                         | 127 |

|    | 7.8   | Compa  | arison with Other Performance Estimation Methods | 130 |

| 8  | Sum   | nmary  | and Conclusions                                  | 133 |

| Bi | bliog | raphy  |                                                  | 145 |

# List of Tables

| 2.1 | Comparison of Hardware–Software Co-Design Approaches | 23  |

|-----|------------------------------------------------------|-----|

| 3.1 | Stirling Numbers of the Second Kind                  | 49  |

| 3.2 | Comparison of Architecture Simulators                | 54  |

| 5.1 | Possible Mapping Execution Times                     | 79  |

| 7.1 | Architecture–Partition Alternatives Explored         | 119 |

| 7.2 | Parameter Processing Units                           | 119 |

| 7.3 | Parameter Communication Media                        | 120 |

| 7.4 | Values Block Level Performance Estimation            | 120 |

| 7.5 | Output Throughput (packets/s)                        | 121 |

| 7.6 | Simulation Speed                                     | 126 |

| 7.7 | Simulation Accuracy                                  | 128 |

| 7.8 | Comparison Performance Estimation Approaches         | 131 |

# List of Figures

| 2.1 | Classical Hardware–Software Co-Design Procedure                          | 9  |

|-----|--------------------------------------------------------------------------|----|

| 2.2 | System Level Design Flow                                                 | 12 |

| 2.3 | Classification of Co-Design Approaches                                   | 20 |

| 2.4 | TCP/IP Conceptual Layers                                                 | 36 |

| 2.5 | Communication Processing Tasks                                           | 37 |

| 2.6 | VLSI Networking Architectures                                            | 40 |

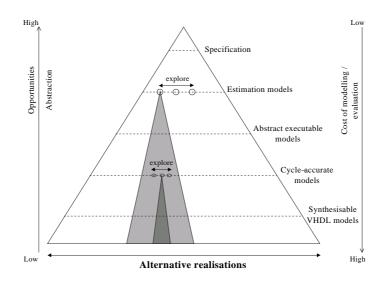

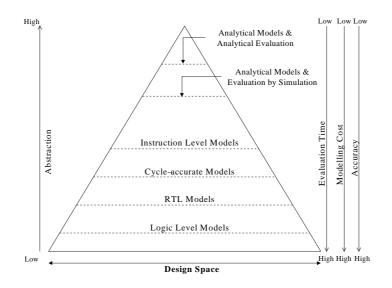

| 3.1 | Abstraction Levels for Models                                            | 46 |

| 3.2 | Design Space Exploration                                                 | 48 |

| 3.3 | Performance Estimation Abstraction Levels                                | 52 |

| 3.4 | Integration Performance Estimation Process in the Design Flow $\ldots$ . | 57 |

| 3.5 | Target Architecture                                                      | 61 |

| 4.1 | Estimation of Performance                                                | 64 |

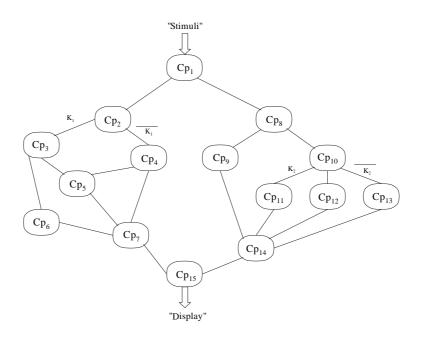

| 4.2 | Functional ASCSG                                                         | 66 |

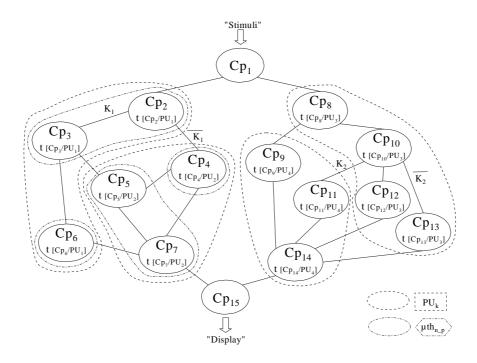

| 4.3 | Architectural ASCSG                                                      | 67 |

| 4.4 | Shared Computation Node                                                  | 68 |

| 4.5 | Communication ASCSG                                                      | 69 |

| 4.6 | System Performance Estimation Scheme                                     | 72 |

| 4.7 | Sequence of Nodes                                                        | 73 |

| 4.8  | Convergence of Nodes                                                            | 73  |

|------|---------------------------------------------------------------------------------|-----|

| 4.9  | Mapping onto PE/Thread–AC                                                       | 74  |

| 4.10 | Multiple Instances of <i>Computation Nodes</i>                                  | 75  |

| 4.11 | Functional Validation                                                           | 76  |

| 5.1  | ASCSG Implementation Procedure                                                  | 78  |

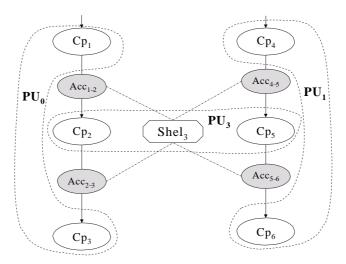

| 5.2  | Access to a Shared Computation Node                                             | 81  |

| 5.3  | Access to a Shared Communication Medium                                         | 82  |

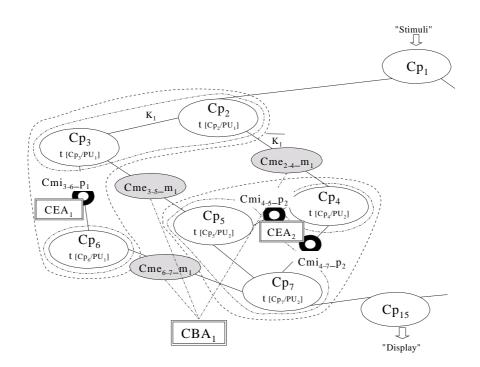

| 5.4  | Access to a Shared Communication Medium from/to a Hierarchical Channel          | 83  |

| 5.5  | Context Switch and Context Event Notification in a Multi-Threading<br>Processor | 84  |

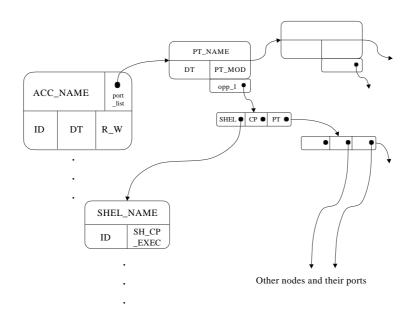

| 5.6  | Computation Node Data Structure                                                 | 86  |

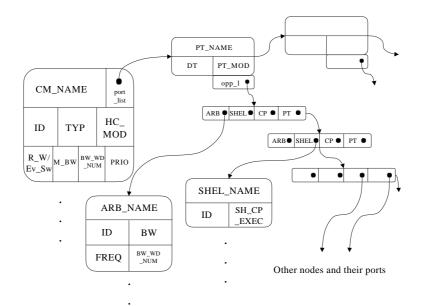

| 5.7  | Access Node / Shared Element Data Structure                                     | 87  |

| 5.8  | Communication Node / Arbiter Data Structure                                     | 88  |

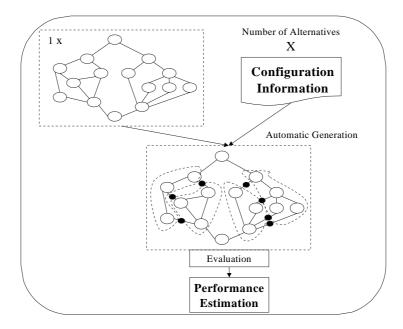

| 5.9  | Performance Estimation by Means of Configuration Information $\ . \ . \ .$      | 91  |

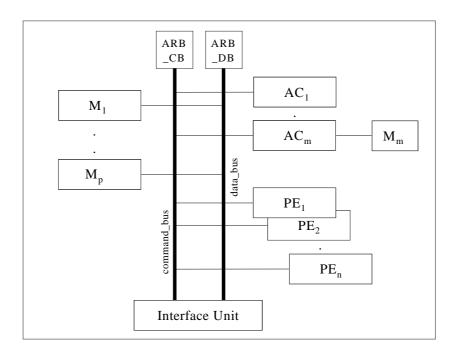

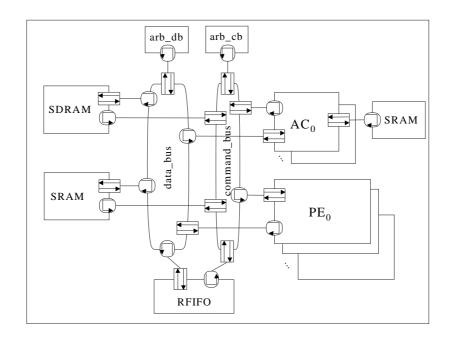

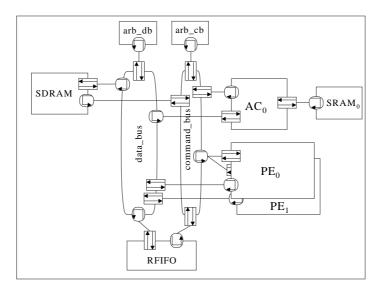

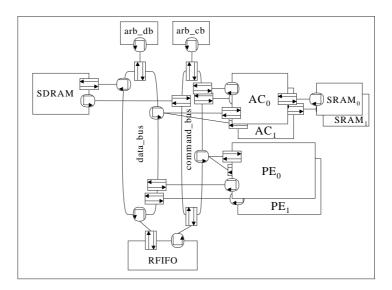

| 6.1  | Target Platform Architecture                                                    | 98  |

| 6.2  | Bus-Based Co-Simulation Platform                                                | 100 |

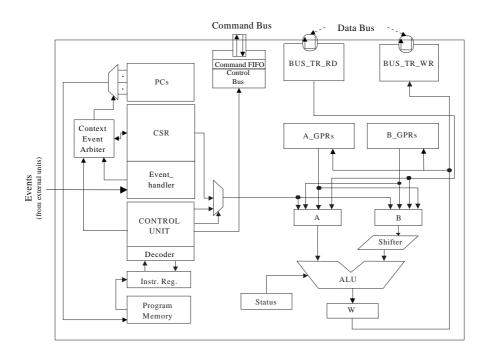

| 6.3  | Embedded RISC Processor                                                         | 102 |

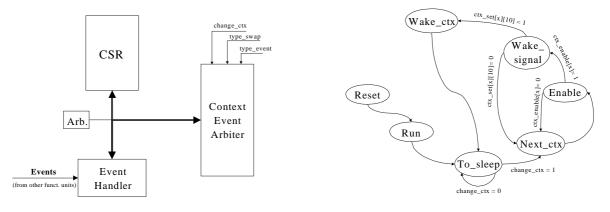

| 6.4  | Multi-Threading Modelling                                                       | 103 |

| 6.5  | FSM of Context Event Arbiter                                                    | 103 |

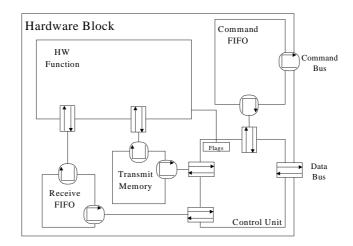

| 6.6  | Internal Architecture of a Hardware Block                                       | 105 |

| 6.7  | Internal Architecture of a Shared Memory                                        | 106 |

| 6.8  | Command Bus                                                                     | 106 |

| 6.9  | Data Bus                                                                        | 106 |

| 7.1  | Case Study: Input Packet Processing                                             | 111 |

| 7.2  | Case Study: Functional ASCSG                                                    | 113 |

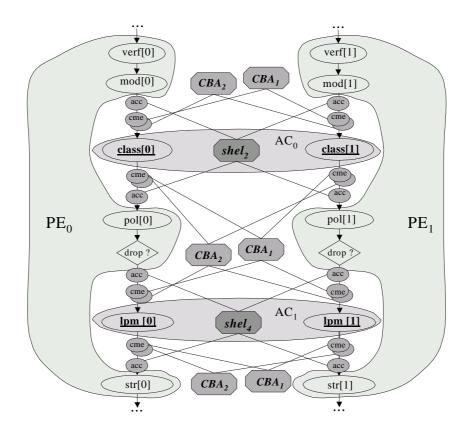

| 7.3  | First Alternative: Two PEs and One AC                | 114 |

|------|------------------------------------------------------|-----|

| 7.4  | Target Architecture First Alternative                | 115 |

| 7.5  | Second Alternative: Two PEs and Two ACs              | 116 |

| 7.6  | Target Architecture Second Alternative               | 117 |

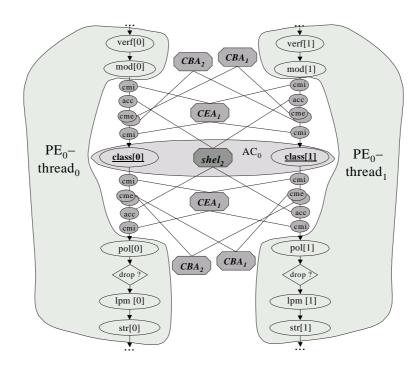

| 7.7  | Third Alternative: One Multi-Threading PE and One AC | 118 |

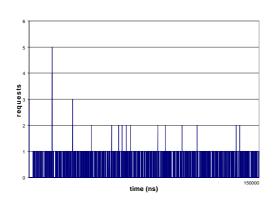

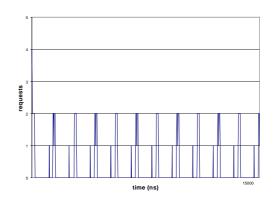

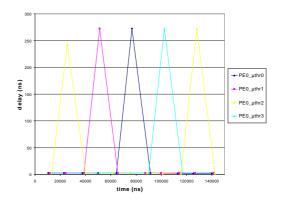

| 7.8  | Queue Command Bus                                    | 122 |

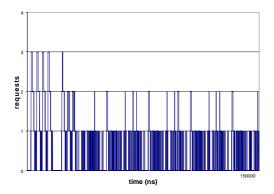

| 7.9  | Queue Data Bus                                       | 122 |

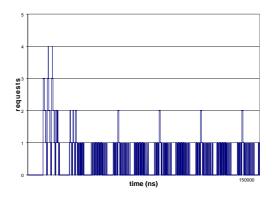

| 7.10 | Queue Classify Accelerator                           | 122 |

| 7.11 | Queue LPM Accelerator                                | 122 |

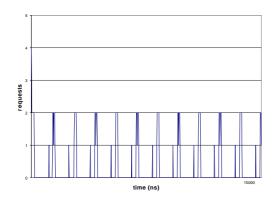

| 7.12 | Queue Events PE_0                                    | 123 |

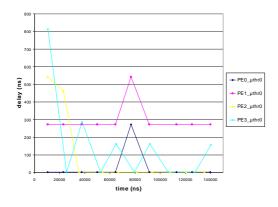

| 7.13 | Queue Events $PE_1$                                  | 123 |

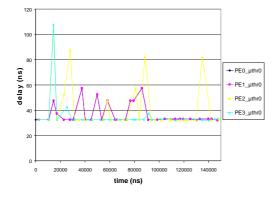

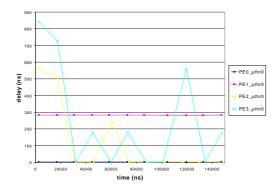

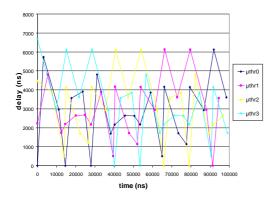

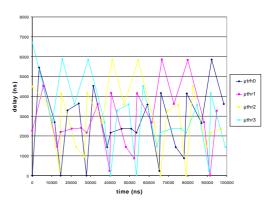

| 7.14 | Delay Write Request Command Bus; PEs                 | 123 |

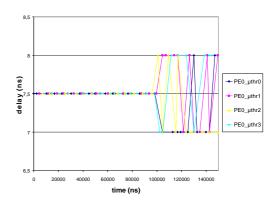

| 7.15 | Delay Write Request Command Bus; Threads             | 123 |

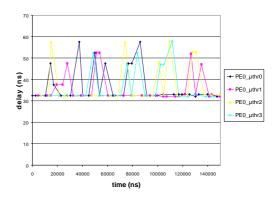

| 7.16 | Delay Write Request Data Bus; PEs                    | 124 |

| 7.17 | Delay Write Request Data Bus; Threads                | 124 |

| 7.18 | Delay Write Request Classify; PEs                    | 124 |

| 7.19 | Delay Write Request Classify; Threads                | 124 |

| 7.20 | Delay Write Request LPM; PEs                         | 125 |

| 7.21 | Delay Write Request LPM; Threads                     | 125 |

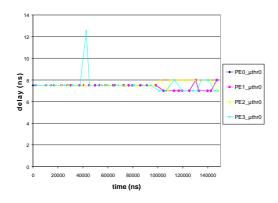

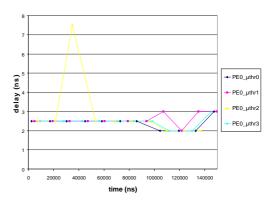

| 7.22 | Delay Wait Event $PE_0$                              | 125 |

| 7.23 | Delay Wait Event $PE_1$                              | 125 |

| 7.24 | Modelling Effort                                     | 129 |

# List of Acronyms

- AC: Accelerator

- ALU: Arithmetic Logic Unit

- ANSI: American National Standards Institute

- ARPANET: Advanced Research Project Agency NETwork

- AS: Autonomous System

- ASAP: As Soon As Possible scheduling algorithm

- ASCSG: Annotated SystemC Control-Synchronisation Graph

- ASIC: Application Specific Integrated Circuit

- ASSP: Application Specific Standard Products

- BFM: Bus Functional Model

- CAD: Computer-Aided Design

- CAG: Communication Analysis Graph

- CBA: Command Bus Arbiter

- CDFG: Control Data Flow Graph

- CEA: Context Event Arbiter

- CFG: Control Flow Graph

- CFSM: Co-design Finite State Machine

- Cme: external Communication node

- Cmi: internal Communication node

- COSYMA: COSYnthesis of eMbedded microArchitectures

- CPG: Conditional Process Graph

- CPI: Communications Programming Interfaces

- CP: ComPutation node

- CPU: Central Processing Unit

- CSR: Control and Status Registers

- DiffServ: Differentiated Services

- DSP: Digital Signal Processor

- EDA: Electronic Design Automation

- ESC: Extended SystemC library

- FDDI: Fiber Distributed Data Interface

- FPGA: Field Programmable Gate Array

- FSM: Finite State Machine

- FTP: File Transport Protocol

- GNU: GNU's Not Unix

- GPR: General Purpose Register

- HDL: Hardware Description Language

- HDLC: High level Data Link Protocol

- HTTP: Hyper Text Transfer Protocol

- IP: Intellectual Property

- IP v.6: Internet Protocol version 6

- ISO: International Organisation for Standardisation

- ISP: Internet Service Provider

- ISS: Instruction Set Simulator

- ITRS: International Technology Roadmap for Semiconductors

- LAN: Local Area Network

- MAC: Medium Access Control

- MAN: Metropolitan Area Network

- MIPS: Million Instructions Per Second

- M: Memory unit

- OC: Optical Carrier

- ODETTE: Object-oriented co-DEsign and functional Test TEchniques

- OSI: Open Systems Interconnection

- PE: Processing Element

- POOSL: Parallel Object-Oriented Specification Language

- PNI: Programmable microprocessors on Network Interfaces

- PU: Processing Unit

- QoS: Quality of Service

- RFIFO: Receive First In First Out

- RISC: Reduced Instruction Set Computer

- RTL: Register Transfer Level

- RTOS: Real Time Operative System

- SDL: Specification and Description Language

- SDRAM: Synchronous Dynamic Random Access Memory

- SIA: Semiconductor Industry Association

- SIR: System Intermediate Representation

- SLA: Service Level Agreement

- SLDL: System Level Design Language

- SoC: System-on-Chip

- SONET: Synchronous Optical Network

- SPADE: System level Performance Analysis and Design Space Exploration

- SPI: System Property Intervals

- SRAM: Static Random Access Memory

- TCP: Transport Control Protocol

- UML: Unified Modelling Language

- VC: Virtual Component

- VHDL: VHSIC Hardware Description Language

- VHSIC: Very High Speed Integrated Circuits

- VLSI: Very Large System Integration

- WAN: Wide Area Network

## Chapter 1

# Introduction

At present, the complexity of VLSI integrated systems is growing exponentially. This is partially supported by the advances in silicon processing technology, which enable integration of ever more complex functions on a single chip. These so-called Systems-on-Chip (SoC) contain dedicated hardware components, programmable processors, memories, etc., requiring not only the design of digital and analogue hardware but also the design of embedded software. Nevertheless, the well known chart published by the Semiconductor Industry Association (SIA) [1] predicts an increase in design complexity of about 58% per year while designer productivity increase stays at 21% per year. These predictions demand new methodologies and tools that will allow significant productivity improvements beyond the present trend.

Moreover, increasingly more complex circuits have to be designed in less time and with greater guarantees of success in order to compete in a market that is becoming more and more aggressive. This demanding environment is forcing fundamental changes in the way VLSI systems are designed. The use of predefined Intellectual Property (IP) blocks for System-on-Chip (SoC) design has become essential in order to build the required complexity in a short time-to-market. The designers see current design tools and methodologies as inadequate for developing million gate ASICs from scratch. Tools are not providing the productivity gains required to keep pace with the increasing gate counts available from deep submicron technology. Design reuse, i.e. the use of pre-designed and pre-verified cores, is the most promising opportunity to bridge the gap between available gate count and designer productivity.

A further interesting consequence of this increase of design complexity and increase of time-to-market pressure is that they are forcing companies to move to higher and higher levels of abstractions and to design products from executable system specifications. In the International Technology Roadmap for Semiconductors (ITRS) [2] 2001 is written

that "the cost of design is the greatest threat to the continuation of the semiconductor roadmap". Although design reuse and implementation tools contribute to decrease the design cost, in the future the ITRS claims for "intelligent test-benches" and "embedded system level methodologies".

The design of network equipment constitutes a good example of complex systems with an enormous growing perspective. Nowadays, the network equipment vendors are racing to provide the new converged voice–video–data communication infrastructure. Furthermore, conservative estimates for aggregate bandwidth on the Internet backbone indicate a doubling each year for the past ten years. One consequence of this growth is the demand for greater performance, flexibility, reliability and cost effectiveness in the routers and switches which control the flow of data through the network.

### 1.1 Motivation

The new challenges concerning speed and flexibility pursued by emerging networking architectures introduce in their design a scenario of multiple alternatives. The selection of the optimal target architecture as well as the partitioning of the functionalities that fulfills the constraints should start at a high-level of abstraction, i.e. at system level, where different trade-offs can be fixed. Moreover, from the user's point of view of a certain architecture, the best mapping of the functionalities onto the fixed architecture can be facilitated if a model of the system at a high level of abstraction is provided.

In a traditional design methodology, hardware and software design takes place in isolation with the hardware being integrated with the software after the hardware is fabricated. At system level, engineers are reconsidering how designs are specified, partitioned and verified. In the actual complex systems, the software is programmed in C/C++ and the corresponding hardware is developed in description languages such as VHDL and Verilog. Thus, it is becoming common that problems arise from the use of different design languages and incompatible tools. Errors that cannot be fixed in software lead to costly re-fabrication and adversely affect time-to-market. To avoid costly silicon re-spins and improve time-to-market, the design methodology has to change, so that the hardware and the software are integrated earlier in the design cycle that leads to the so-called system level design.

At system level, a huger scenario of possible alternatives have to be explored and, therefore, the new embedded system level methodologies have to improve the support of fast and flexible design space exploration procedures. This can be achieved by applying fast and flexible performance estimation methods together with exploration strategies, in order to rank the design alternatives. Performance estimation is characterised by measuring utilisation and throughput of the resources.

In traditional system design methodologies the target architecture is predefined. The designer holds the design choices in terms of hardware–software partitioning, which opens a huge space for exploration. During the partitioning phase, the functionality captured by the specification is distributed among the allocated system components. If the designer additionally wants to explore various architecture choices, the design space becomes more dense. This creates the need for a fast exploration process, where the performance evaluation of a potential solution plays a decisive role for reducing the design alternatives. If the exploration is performed at a higher level of abstraction, a huger scenario of low level alternatives is covered. Afterwards, at lower levels of abstraction, only the best alternatives will be further evaluated.

It can be summarised that the acceleration of the exploration process requires a fast performance estimation of the functionalities without losing accuracy. A compromise between accuracy and computation time determines the feasibility of the estimation techniques. Moreover, the time consumption of the whole design process could be drastically reduced if high level estimation methodologies would be performed before taking major design decisions.

A further related issue to be supported by the new system level methodologies is the description language. If a design consists of hardware and software, the modelling language should be C/C++ since standard processors come only with C/C++ compilers. Unfortunately, the C/C++ language was developed for describing software and not hardware. It is missing basic constructs for expressing hardware concurrency and communication among components. Therefore, a language is needed that can be compiled with standard compilers and that is capable of modelling hardware and software on different levels of abstraction.

### **1.2** Novelty Aspects

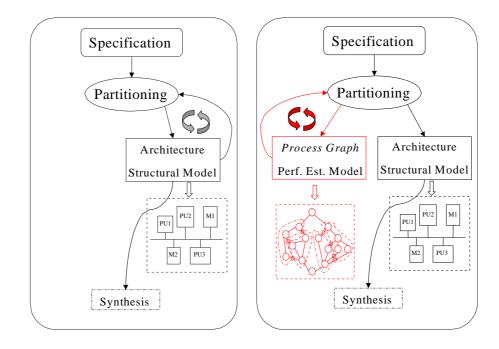

The present work introduces a novel system level performance estimation methodology based on the system level language SystemC. The rebuilding effort is considerably lower when applying the proposed methodology compared to building up a structural model of the target architecture at a lower level of abstraction. It accelerates the exploration of several partitioning alternatives of a system specification onto a target architecture. This is achieved by applying a graph, whose structure does not have to be re-constructed each time a new alternative is explored. Only the information concerning the new architecture–partition configuration to be tested has to be provided.

The performance estimation methodology proposed is intended to be integrated in a

hardware–software co-design procedure, where several target architectures have to be explored and an easy re-mapping of the functions onto the target architecture should be possible. The current methodology achieves a fast simulation runtime while maintaining the accuracy within an acceptable tolerance. The latter is achieved by taking into account the communication loads among components when the partitioning decision is taken.

The goals pursued by the new methodology are achieved by means of a two-step procedure. First, the system is modelled in terms of a graph, where the relevant information concerning the target architecture is annotated and a mechanism to solve resource contentions is added. This functional modelling accelerates the exploration of further alternatives without requiring a re-building of the structure of the graph if the hardware structure is changed. Second, the evaluation is performed by means of simulation at system level. It allows a more detailed analysis than analytical evaluation. And, at the same time, the simulation runs faster than a simulation at a lower level of abstraction.

For the modelling of the graph, the industry standard system level language SystemC has been chosen. It is noteworthy that this is a new application of this language, which supports the implementation of the whole methodology. SystemC characteristics such as the modelling of time, reactivity and concurrency, and the assistance it provides in evaluating resource contentions, make this language especially suitable for the implementation of the methodology. Existing approaches have applied SystemC to describe the system functionalities and the target architecture in a structural way.

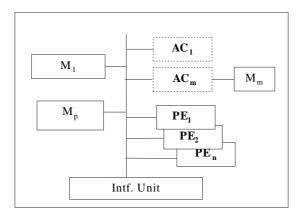

The proposed method is oriented to support the design of multi-processing and multi-threading architectures for networking applications. These architectures contain, mainly, multiple RISC embedded processors, powerful co-processors to accelerate some costly functions and memory and interface blocks. Different communication resources connect all building blocks with each other. Very often a bus-based communication is found. An important characteristic of RISC embedded processors is its multi-threading hardware support to avoid idle times when waiting on results from other resources. The modelling and evaluation support of this characteristic also constitutes a novelty aspect of the proposed method, which has not been previously covered by other performance estimation approaches.

### 1.3 Procedure

An introduction to the problems behind design space exploration of the most recent systems is needed for understanding the requirements imposed on the performance estimation methods. This theoretic study, together with an exploration of the existing techniques, will show the shortcomings and need for improvement in this area. In particular, the current work concentrates on the reduction of the re-building effort, which is quite high in previous approaches based on a structural model of the system target architecture.

As input for the work, a graph representation for modelling the system functionalities is selected. This graph is further annotated with information concerning the target architecture and the selected partitioning of the functionalities onto the available resources. Furthermore, the required mechanisms to solve resource contentions are added to the graph. Then, the evaluation of the graph by means of simulation delivers the performance estimation values. In order to verify the new approach in terms of simulation time and accuracy, a comparison of the simulation results with a cycleaccurate model is made for a specific example from the networking world. Finally, the results achieved by the proposed system level performance estimation methodology are compared with the results of other approaches. Especially attention is paid to the abstraction level, modelling effort, simulation time and accuracy.

### 1.4 Structure of the Work

The remainder of this work is organised as follows: Chapter 2 presents the state of the art in the related areas of system level design, performance estimation techniques as well as in the main application scenario, VLSI networking architectures. In Chapter 3 the role of performance estimation within design space exploration is presented and the problems are explained. Furthermore, the disadvantages and shortcomings of the previous approaches are shown, which constitute the main motivations for the development of the proposed method. Then, the integration of the proposed performance estimation method into the hardware-software design flow is depicted and the boundary conditions and assumptions taken are explained. Chapter 4 describes the modelling approach. This encompasses the Functional, Architectural and Communication models. Moreover, the system performance estimation scheme is illustrated by means of selective examples from the networking world. The steps towards the implementation of the methodology are explained in Chapter 5. Chapter 6 depicts the configurable cycle-accurate hardware-software co-simulation platform built for verification purposes. Chapter 7 compares the performance results achieved by the proposed methodology to the outcomes of the cycle-accurate platform. The results are evaluated and, further on, the procedure of the new method is compared with other performance estimation techniques. The work ends with a summary and the conclusions.

\_\_\_\_\_

# Chapter 2

# State of the Art

### 2.1 Chapter Introduction

In order to position the topic of this thesis, system performance estimation, as part of the system level design, a comparison between the classical hardware–software codesign procedure and the system level design is performed first. Later on, the most recent and relevant system level languages are classified and briefly explained. Subsequently, some well known computer aided co-design methods and tools developed at different universities and companies are introduced.

The estimation of the performance achieved by the architecture–partition alternative under study plays an important role in this system level design paradigm. Several approaches dealing with this issue at different abstraction levels are then shown and their advantages and disadvantages discussed.

An introduction to the application scenario, VLSI networking architectures, is finally carried out. An overview of the evolution of such architectures will show the requirements when pursuing the design of such complex systems. It demands the exploration of different trade-offs at system level, where the designer has more freedom to achieve a reasonable compromise.

### 2.2 System Level Design. Languages and Methodologies

Nowadays, the increase in complexity of the current VLSI designs has forced an evolution in the nature of the systems under design. The definition of a system has moved from the system-on-board to the System-on-Chip (SoC). In the past, the systems were composed of discrete parts such as microprocessors, memory chips, analogue devices and application-specific integrated circuits (ASICs). In contrast, the modern Systemon-Chip may well contain one or more processors including both microcontrollers and digital signal processors (DSPs) or specialised processors. Moreover, it includes on-chip memory and peripheral control devices, linked together by an on-chip communication network.

System design of embedded systems is often perceived as a process going from a functional specification of a system, through a number of refinement or transformation steps to an architecture, and from there, to a final implementation ([3]).

The increase in complexity and reduction of time-to-market requirements for current embedded systems has resulted in the fact that the first phases in the design process, i.e. design specification, allocation of the architecture and mapping of the functions onto the target architecture, are no longer carried out from scratch, but rather with the help of abstract models. This Section firstly depicts the classical hardware–software co-design procedure and, later on, demonstrates why this does not meet the design requirements introduced by today's complex systems. The whole procedure has thus to start at a higher level of abstraction, i.e. at system level, where the designer has more freedom to explore the trade-offs and detect the bottlenecks. System level design is mainly characterised by both, high-level of abstraction and exploration, where the latter attribute is a consequence of the former one.

#### 2.2.1 Classical Hardware–Software Co-Design Procedure

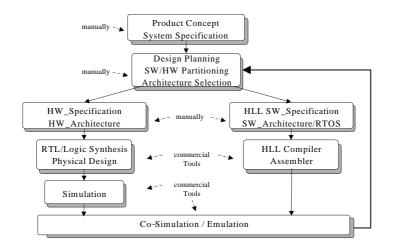

Hardware–software co-design can be defined as the cooperative design of hardware and software. The flexibility offered by software allows late design changes and simplifies debugging. Furthermore, the reuse of software by porting it to other processors reduces the time-to-market and the design effort. Finally, in most cases, the use of processors is very cheap compared to the development costs of ASICs. However, hardware is always used by the designer when the processors are not able to meet the required performance. This trade-off between hardware and software illustrates the optimisation aspect of the co-design problem. A typical electronic system development project is divided into four basic phases ([4]): Product concept; design planning; hardware–software design phase; and integration and test phase (co-simulation/emulation), as can be seen in Figure 2.1.

Figure 2.1: Classical Hardware–Software Co-Design Procedure

- 1. Product Concept. During this phase, the entity being designed is viewed as an overall system rather than as distinct hardware and software components. This phase delivers the specifications for the system behaviour. Additionally, functional requirements and budgets for both hardware and software components of the system are created. These include constraining costs, size, performance, and physical attributes. The system engineer writes a C or C++ model of the system to verify the concepts and algorithms at system level.

- 2. Design Planning, Hardware–Software Partitioning. Starting from the specification, the design is partitioned into hardware and software parts. This step has to done in a manner by which the system function is preserved. This phase also takes into account the underlying architecture and the resources on which the system is being implemented. Partitioning involves the following major subtasks:

- Target Architecture Constraints Description: It includes the available resources and their interconnections;

- Allocation and Binding: The designer schedules certain operations in hardware and others in software and then estimates whether the constraints are satisfied;

- Cost/Performance Estimation: In order to estimate the overall performance of the system, accurate estimates of the performance of the functions on various resources are required.

- 3. Hardware–Software Design Phase. During this phase, different teams for the hardware and software part solve their respective problems. The hardware and software design and implementation efforts typically start at the same time and ideally end at the same time. But in practice, the beginning of the software development has to wait until the hardware is finished. The software part is developed using compilers and debugger tools, while for the hardware part, the functionality is described using a hardware design language (HDL). For the parts of the original model to be implemented in software, the model has to be re-written with calls to an RTOS. The conversion of the C/C++ model to be implemented in hardware into the HDL occurs manually. This process is very tedious and error prone. After the conversion took place, the HDL model becomes the focus of development. The C model quickly goes out-of-date as changes are made. Changes are typically made only to the HDL model and will not implemented in the C model.

- 4. Integration and Test Phase. In theory, integration and test are the final steps where the correctness of the system is checked. In practice, it is the first time that the completed hardware and independently developed software come together as a system. At this time numerous errors appear, as for example, the effects of misinterpretations of interface definitions, out-of-date specifications, poorly communicated changes of the specification between the teams, and ineffective performance modelling. Consequently, one third or more of the total development time is spent in this phase ([5]). As the tools progress and become more friendly to both the hardware and software developers, the overlap between the test phase and the design and implementation phases will increase. Tests that are created to validate the C model functionality cannot be run against the HDL model without conversion. The test suite has to be converted to the HDL environment.

Developers are often forced to redesign and/or reduce product objectives when integration problems are found. Given the long fabrication cycles and costs associated with re-designing and re-spinning ASICs, the adaptation of the work is frequently performed in software. This is not always the best solution for the end product. But integration and test leads back to the design and implementation phase, and can take about the same amount of time to complete as the original design and implementation. Also in some cases, the first product release will not contain all of the intended software functionality because it has not been possible to start the integration effort earlier in the design.

Furthermore, two things are necessary before virtual integration and test can be accomplished. The first is the ability to simulate the hardware at speeds sufficient to make software execution a reality. In most cases, this means that the overall simulation performance must be increased by a factor of at least 1000 over the current execution speeds for hardware-oriented simulation products. The model is simulated and verified with an RTOS emulator. Some parts of the original code can be reused, but the change in abstraction from the original model to an RTOS-based model requires significant manual re-coding and verification of changes becomes a problem. The second is the need to bring the debug and development environments for the hardware and software closer together. Simulation waveforms do not provide a natural way for a software engineer to debug highlevel languages. The original source form for both the software and hardware must be maintained within a single unified debugging environment.

As depicted in Figure 2.1, in a classical hardware–software co-design procedure the first two phases are performed manually, while the last two are partially supported by commercial tools. Moreover, the decision concerning the partition of the functionalities in hardware and software is reached empirically and no exploration takes place. Firstly at the end of the co-design procedure, i.e. in the integration and test phase, come the hardware and software together and, in case the predefined constraints are not met, a new partitioning alternative is tried. This procedure becomes then very tedious in case the test of several alternatives is required.

It can be concluded that the classical co-design approach is no longer feasible for the design of large heterogeneous Systems-on-Chip because quantitative architectural considerations are not taken into account prior to the implementation phase. A move to a level of abstraction beyond the RT level is therefore required — a move to what has been termed system level design.

#### 2.2.2 System Level Design Procedure

One of the most challenging tasks in System-on-Chip design is to map a complex application onto a heterogeneous architecture, assuring that the specified performance and cost requirements are preserved. The required flexibility and performance is best delivered by a heterogeneous system architecture. As a result, the designer faces a huge design space and has to compose a system architecture from various kinds of building blocks in order to meet the constraints of the specific application.

A solution for dealing with this complexity is to exploit hierarchy and to move to higher levels of abstraction ([7]). The level of abstraction is a trade-off with the level of accuracy. A high abstraction level implies low accuracy and vice versa. Nevertheless, a complex embedded system is easier to deal with at the abstract system level than at the detailed gate or transistor level.

The term System Level Design refers to the abstraction level increase in the design

of embedded systems, i.e., from the architecture level to the system level. This is an earlier stage in the design process which was previously carried out manually. Thus, the design process of a new system starts from a highly abstract specification model and ends with a highly accurate implementation model. The advantage of such a topdown approach is that all necessary design decisions can be made at an abstraction level where the irrelevant details are left out of the model. At system level, the designer has more freedom.

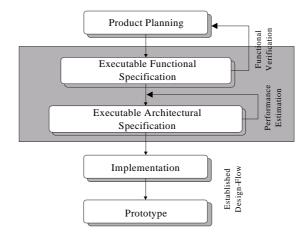

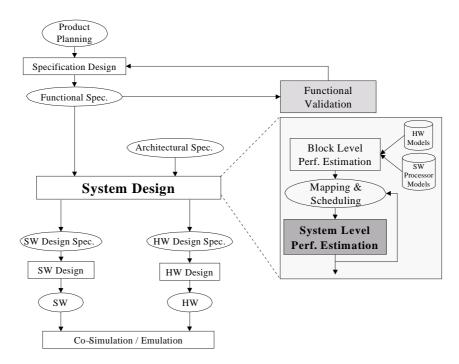

Figure 2.2 illustrates the system level design flow. Further on, the different phases are explained in detail.

Figure 2.2: System Level Design Flow

The system level design process begins with the product planning, where there is still a close interaction between the customer and the designer. They both reach an agreement concerning the system functionalities, which is written in terms of a specification model that can be simulated (executable functional specification). It forms the input to architecture exploration and therefore defines the basis for all exploration and synthesis. The specification model is purely functional, that is, it is free of any implementation details and of any notion of time. The model executes in zero simulation time.

The specification model describes the required behaviour. There are different flavours of models, characterised by the abstraction level and the semantics. Some systems are described using finite state machines, either graphically (e.g., Statecharts) or by means of textual languages (e.g., SDL or Esterel), whereas hardware components are often specified using a hardware description language (e.g., VHDL or Verilog). Developing a single language (textual or graphical) that can express all desired features is a difficult task because of the heterogeneity of the system components. Specification and design frameworks that support multiple and extensible design front-ends is the foreseeable solution. Such frameworks should then support a variety of tools for validation and synthesis of the hardware and software component. The SPI (System Property Intervals) model ([8]) represents a good example of such frameworks. SPI is an internal high-level representation that facilitates global, system level analysis, optimisation and synthesis of heterogeneously specified embedded systems.

Once the functional description has been verified and there are no changes in the description and in the product specification needed, the process enters into the architecture exploration phase. The purpose of this phase is to map the system functionalities represented by the specification model onto the components of the target architecture, which has been previously defined. The steps involved in this phase are as follows: First of all, a target architecture (composed of processing elements and memory units) for the implementation is allocated. Secondly, the partitioning of the functionalities onto the processing elements takes place. This step comprises the mapping of the functionalities.

This partitioning of the functionalities onto the target architecture opens a large scenario of alternatives, the scope of which grows with the complexity of the system. This architecture exploration phase is supported by an executable architectural specification, which delivers an estimation of the performance achieved by the partition alternative under study. This architecture exploration phase is today partially supported by some tools and methodologies.

The search of the optimal solution that meets the predefined cost constraints is a NP-complete problem ([9]). If a problem is known to be NP-complete, then it is unlikely that a polynomial time algorithm exists for that problem. However, in the design automation field there is an urgent need to solve the problem even if it cannot be solved optimally. As soon as the specified cost constraints are met, the implementation phase starts. From this point on, an established standard design flow follows.

#### 2.2.3 System Level Languages

Fundamentally, a system design language is a notation that embodies semantics for describing a system prior to mapping it onto an architecture. Components must be able to be described without making assumptions about the implementation. The system level design language must have a way to describe the behaviour of the components in the system irrespective of whether they will be mapped to software running on a microprocessor or to application-specific hardware.

It should be possible to use the language to construct a performance model. Such a

model allows exploration of the architecture of the system without exactly specifying what microprocessor or bus specification will be used in the implementation. The decisions can be made later, after the entire system is described and simulated at a very high-level.

The language must also include the ability to incorporate the description of constraints, such as event ordering, timing, dependencies and concurrency, with granularity and scheduling mechanisms.

Understanding what system level design means is crucial for defining the requirements of a system level language. System level languages might provide support for integrating domain-specific descriptions, for more abstract modelling and for verification. There are four major reasons why a system level design language becomes necessary ([3]):

- SoC designs combine hardware and software, not only hardware as in traditional ASIC design. Therefore, there is a need for a language that describes the functionality of both the software and hardware. It is essential that the system is defined first, and the exact implementation (hardware or software) is established later on in the design process;

- SoC designs are increasingly incorporating hardware and software intellectual property (IP) from various sources. All of these sources need to use a common system level design language so that the entire system can be modelled;

- Even hardware-only designs are becoming too complex to simulate in RTL. Simulating the entire design at a higher level provides much faster simulation times and lets the designer test the behaviour of the entire chip before it is produced;

- System level design is also required to develop a virtual prototype of the hardware that the software designers can use to begin software development. The old model of waiting until the hardware is finished to begin software development is not applicable any more.

Currently, many different languages in the area of system design are available. They can be broadly classified with regard to the design phase they support and the application scenario they are focused on. Under the first criterion, the existing design languages can be divided into three classes. The first group contains the system specification and modelling languages for the description of functionality, properties and constraints. Secondly, there are architecture languages for the modelling of an architecture and system IP (Intellectual Property) and VC reuse (Virtual Component). And finally, the last group comprises design command languages for estimation and validation purposes. A language covering more than one such task is also possible. An important boundary condition when developing a system level language is the fact that there are many different kinds of systems (i.e., different domains with different models of computation). Moreover, within a system, the heterogeneity also has to be taken into account.

In the past, there have been a few attempts at the standardisation in the area of system level languages, but they were not very successful. ACCELLERA ([10]) constitutes a new attempt at standardisation. It was formed in 2000 through the unification of Open Verilog International and VHDL International to focus on identifying new standards, development of standards and formats, and to foster the adoption of new methodologies. ACCELLERA has promoted the development of *Rosetta* ([11]). *Rosetta* is a System Level Design Language (SLDL) developed to address requirement specifications for SoC designs. The mission of the SLDL is to bring together heterogeneous information in a language environment. Specifically, *Rosetta* allows designers to develop and integrate specifications written in multiple semantic models to provide language and semantic support for concurrent engineering of electronic systems. Some current activities around *Rosetta* subsets for SystemVerilog, SystemC and other Hardware Design Languages (HDL). The standardisation process is scheduled to be concluded in December 2004.

A first rough classification of the system level design languages can be carried out by differentiating between C/C++ approaches, domain-specific languages and extensions of hardware design languages. Moreover, most of them support the system specification and modelling of functionalities, while only few provide a means of architecture modelling and a support for estimation and validation. A further distinctive criterion is the necessity of no language translation in the further refinement of the specification.

### 2.2.3.1 C/C++-Based Languages

The C based system level languages offer two main advantages. First of all, they are known worldwide and, secondly, there is no translation necessary for the software part. For the hardware part, methods and automated tools have been appearing in the meantime that will support the translation. The current two big players in the area of C/C++ based approaches are SystemC and SpecC:

• SystemC is a new modelling language based on C++ that is intended to enable system level design and IP exchange at multiple abstraction levels for systems containing both hardware and software components ([12]). The SystemC standard is controlled by a steering group composed of a broad range of companies

from the Electronic Design Automation (EDA, [13]) and electronics industries. SystemC consists of a set of C++ class libraries plus a simulation kernel that supports hardware modelling concepts at system level, behavioural level and register transfer level. It provides a robust software environment for hardware–software co-design. Nowadays, very few tools exist that act as a bridge between the system architect modelling and verifying SoC designs in C/C++ and hardware designers implementing those designs in silicon. Moreover, until now they support only a small subset of SystemC constructs and they do not provide an optimised code yet. Two examples would be the CoCentric SystemC Compiler ([14]), which synthesises hardware from SystemC source code, and the Forter Design System's Cynthesizer ([15]), which can transform the SystemC design (using the Extended SystemC Library (ESC)) into Verilog or VHDL suitable for input into a wide variety of ASIC and FPGA logic synthesis tools;

Further work in this direction is being done within the framework of the ODETTE project ([16]). The prime deliverable of the Object-oriented co-DEsign and functional Test TEchniques project is a system for object-oriented hardware–software co-design, which provides a migration path from object-oriented system specifications to efficient hardware and software implementations. The design flow that will be supported within ODETTE is based on SystemC-plus. SystemC-plus ([17]) describes a synthesisable SystemC/C++ subset, adds object-oriented constructs to this subset, adds another class library on top of SystemC and brings post-synthesis and pre-synthesis behaviour together;

- SpecC is an example of a system level design language based on C. It is defined as an extension of the ANSI-C programming language. The first version of the SpecC language ([18]) was developed in 1997 at the University of California Irvine under the supervision of Prof. Gajski. The SpecC language is a formal notation intended for the specification and design of digital embedded systems including hardware and software. Built on top of the ANSI-C programming language, the SpecC language supports concepts essential for embedded systems design. It includes behavioural and structural hierarchy, concurrency, communication, synchronisation, state transitions, exception handling and timing ([19]). A methodology for the refinement process within the system level design flow as well as the required tools have also been developed in the meantime. Recently, a new version of the language, SpecC 2.0, has been announced which enables the migration from system level to RTL level and further implementation;

- $C_x$  is a minimum extension of the C programming language by a process statement allowing parallel processes. This language is used for the input description of the system functions in the co-design workbench COSYMA ([28]).

# 2.2.3.2 Domain-Specific System Level Languages

Several system level languages have been developed in the meantime with an application domain in mind. While they are broadly used, they nevertheless comprise different restrictions depending on the domain.

- SDL: The Specification and Description Language (SDL) is an object-oriented, formal language used for the specification of complex, event driven and real time applications ([20]). The language is able to describe the structure, behaviour, and data of real time and distributed communicating systems. The great strength of SDL lies in describing large real time systems. SDL is a design and implementation language dedicated to advanced technical systems (i.e., real time systems, distributed systems, and generic event driven systems where parallel activities and communication are involved). Typical application areas are high and low-level telecom systems, aerospace systems, and distributed or highly complex mission critical systems;

- Esterel: This is both a programming language, dedicated to programming reactive systems, and a compiler which translates Esterel programs into finite state machines. It is a member of a family of synchronous languages, which is particularly well suited to programming reactive systems, including real time systems and control automata ([21]). It can generate C code to be embedded as a reactive kernel in a larger program that handles the interface and data manipulations. It can also generate hardware in the form of netlists of gates, which can then be embedded into a larger system. Esterel has been chosen by the Polis group as one of their input languages for their hardware–software co-design system;

- UML: The Unified Modelling Language ([22]) helps to specify, visualise and document models of software systems, including their structure and design. There are many UML tools available on the market for analysing the application's requirements and designing a solution that meets them. Any type of application running on any type and combination of hardware, operating system, programming language and network can be modelled in UML.

## 2.2.3.3 Extensions to Hardware Design Languages

Hardware description languages, for instance VHDL and Verilog, are known and used worldwide but are restricted to describing hardware. Besides design, today's language requirements comprise verification, system and software interfaces. Therefore, the classical hardware design languages might evolve to cover these other facets. One attempt in this direction is SystemVerilog ([23]). SystemVerilog 3.0 evolves Verilog rather than substituting it. These additions extend Verilog into the system space and the verification space. It was built on top of the work of the IEEE Verilog 2001 committee. SystemVerilog improves the productivity, readability and reusability of Verilog-based code.

# 2.2.4 Computer-Aided Co-Design Methods and Tools

When a design team conceives a digital system, it has to perform an implementation that satisfies the system level specification within a short period of time. Furthermore, it has to maximise the system value while reducing the cost. The value of an implementation depends, for instance, on the performance and the power consumption. The cost is a function of the following parameters: number of hardware parts; size of the silicon dies (packaging costs); and software development. The value and cost are also related to the ease of debugging, testing and extending the system, as well as to the reliability and maintenance ([24]).

Computer-aided co-design tools require as input a formal system level specification in the form of system level languages or charts. It will lead to a structured design methodology, will facilitate hardware and software reuse and will permit the support of analysis and validation tools. All of these factors contribute to decreasing the design time. Furthermore, a CAD tool should be able to support the exploration of different design alternatives rapidly and should automatically generate a detailed low-level description of the implementation.

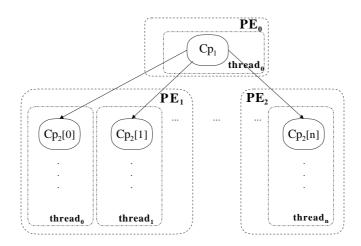

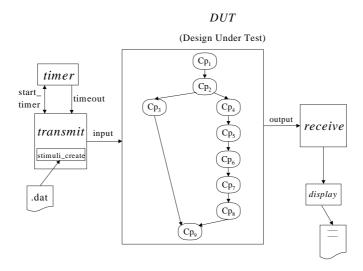

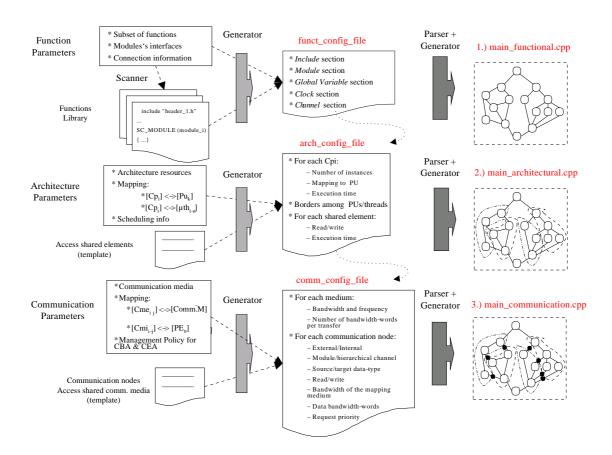

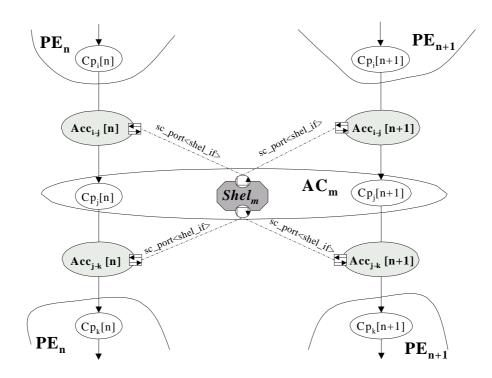

The overall objective in co-design tool research and development is providing integrated environments for concurrent specification, validation and synthesis of both hardware and software. A description of these three phases is provided below.