### Lehrstuhl für Realzeit-Computersysteme

### SDL-based Design of Application Specific Hardware for Hard Real-Time Systems

Annette Muth

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktor-Ingenieurs (Dr.-Ing.)

genehmigten Dissertation.

| Vorsitzender:            | UnivProf. DrIng. J. Eberspächer                                                  |

|--------------------------|----------------------------------------------------------------------------------|

| Prüfer der Dissertation: | 1. UnivProf. DrIng. G. Färber                                                    |

|                          | 2. UnivProf. Dr. rer. nat. W. Rosenstiel,<br>Eberhard-Karls-Universität Tübingen |

Die Dissertation wurde am 17.01.2002 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 02.05.2002 angenommen.

Meinen Eltern

# Abstract

Specification languages and automated design methods are increasingly being used to master the growing complexity in the development of embedded electronic systems. The work presented here uses the "Specification and Description Language" SDL as basis of an automated design process targeting application specific hardware particularly for hard real-time systems.

The SDL specification is annotated with deadlines, event streams and event dependencies which capture the timing requirements and properties of the embedding system. The next step towards an electronic circuit is a VHDL description of the required behaviour. Different principles for the transformation of SDL into VHDL, the implementation models, are presented. The server model maps each SDL process to its own VHDL entity with its own message queue. The activity thread implementation in contrast executes all transitions, which are triggered in the SDL processes by one external signal or timer output, directly one after the other, abolishing the internal communication between the processes. In the presented design process, a SDL-Compiler generates VHDL from textual SDL. The statemachine part is linked with so called run-time components, which implement reusable functions like message queues, timers, and communication channels. Commercial synthesis tools create the electronic circuit from the VHDL design. The complete design flow was integrated with a HW/SW rapid prototyping environment.

Hard real-time systems require the beforehand proof that all deadlines will be met. A real-time analysis is presented which calculates the worst case response times to external events, considering the timing constraints, different implementation models and run-time components. An upper bound on the necessary length of the message queues is derived as well. The consideration of event dependencies during real-time analysis brings a relaxation of a possibly too pessimistic worst case scenario. The presented methods have been tested in the rapid prototyping environment on a FPGA-based target architecture with the help of several application examples. The results from these experiences allow an evaluation of both the resource requirements and real-time properties of the hardware automatically generated from SDL. ii

# Contents

| 1        | Inti | roduction                                            | 1                     |

|----------|------|------------------------------------------------------|-----------------------|

|          | 1.1  | Background                                           | 1                     |

|          | 1.2  | Scope                                                | 3                     |

|          | 1.3  | Overview                                             | 4                     |

| <b>2</b> | Rel  | ated Work                                            | 7                     |

| 3        | Spe  | ecification with SDL                                 | 15                    |

|          | 3.1  | Functional Specification with SDL                    | 15                    |

|          |      | 3.1.1 Background                                     | 15                    |

|          |      | 3.1.2 Language Elements of SDL-92                    | 16                    |

|          |      | 3.1.3 Model of Computation                           | 19                    |

|          |      | 3.1.4 Discussion $\ldots$                            | 20                    |

|          | 3.2  | Timing Constraints                                   | 21                    |

|          | 3.3  | Predefined Components                                | 26                    |

| 4        | Imp  | plementation of SDL in Hardware                      | <b>27</b>             |

|          | 4.1  | Hardware Design with VHDL                            | 28                    |

|          | 4.2  | Implementation of a Single SDL Process               | 29                    |

|          |      | 4.2.1 Component view                                 | 29                    |

|          |      | 4.2.2 Finite State Machine Implementation in VHDL    | 32                    |

|          | 4.3  | Server Implementation Model                          | 35                    |

|          | 4.4  | Activity Thread Implementation Model                 | 36                    |

|          | 4.5  | Combination of Implementation Models                 | 40                    |

|          | 4.0  |                                                      | 10                    |

| <b>5</b> | -    | -                                                    | 43                    |

| 5        | -    | al-Time Analysis                                     | -                     |

| 5        | Rea  | a <b>l-Time Analysis</b><br>Real-Time Analysis Model | 43                    |

| 5        | Rea  | <b>d-Time Analysis</b><br>Real-Time Analysis Model   | <b>43</b><br>44       |

| 5        | Rea  | <b>al-Time Analysis</b><br>Real-Time Analysis Model  | <b>43</b><br>44<br>44 |

|   |     | 5.2.2 Event Dependencies                      | . 52 |

|---|-----|-----------------------------------------------|------|

|   |     | 5.2.3 Output Event Stream                     | . 56 |

|   |     | 5.2.4 Derived Event Dependencies              | . 61 |

|   | 5.3 | Serialized Activity Thread                    | . 63 |

|   | 5.4 | Parallel Activity Thread                      | . 64 |

|   |     | 5.4.1 Waiting Time                            | . 66 |

|   |     | 5.4.2 Event Dependencies                      | . 68 |

|   | 5.5 | SDL System Analysis                           | . 70 |

|   |     | 5.5.1 Overall Reaction Time                   |      |

|   |     | 5.5.2 Derivation of Internal Event Streams    | . 71 |

|   |     | 5.5.3 Inclusion of Additional Information     | . 72 |

|   | 5.6 | Message Queue Depth                           | . 72 |

|   |     | 5.6.1 Required Message Queue Depth            |      |

|   |     | 5.6.2 Event Dependencies                      | . 75 |

|   |     | 5.6.3 Undersized Queues                       | . 77 |

| 6 | Au  | tomated Design Process                        | 79   |

|   | 6.1 | Design Tasks                                  | . 79 |

|   | 6.2 |                                               |      |

|   |     | 6.2.1 Target Architecture                     |      |

|   |     | 6.2.2 Rapid Prototyping Design Process        |      |

| 7 | Ext | perimental Results and Evaluation             | 89   |

|   | 7.1 | -                                             |      |

|   |     | 7.1.1 CAN-bus physical layer                  |      |

|   |     | 7.1.2 Servo Motor Controller                  |      |

|   |     | 7.1.3 Assembly Line                           |      |

|   | 7.2 | Resource Usage of the Implementation          |      |

|   |     | 7.2.1 Resource Estimations                    |      |

|   |     | 7.2.2 CAN-bus physical layer                  |      |

|   |     | 7.2.3 Servo motor controller                  |      |

|   |     | 7.2.4 Assembly line                           |      |

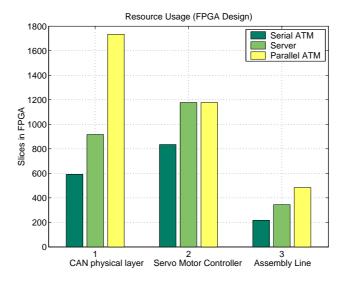

|   |     | 7.2.5 FPGA Resource Usage                     |      |

|   | 7.3 | Real-Time Analysis Results                    |      |

|   |     | 7.3.1 Timing Requirements and Operation Modes |      |

|   |     | 7.3.2 Server Model                            |      |

|   |     | 7.3.3 Serial Activity Thread Model            |      |

|   |     | 7.3.4 Parallel Activity Thread Model          |      |

|   | 7.4 | Evaluation                                    |      |

| 8 | Cor | nclusions and Future Work                     | 123  |

|   |     |                                               |      |

iv

| CONTENTS                   | V   |

|----------------------------|-----|

| Bibliography               | 129 |

| A Application Examples     | 135 |

| A.1 CAN Bus Physical Layer | 135 |

| A.2 Servo Motor Controller |     |

| A.3 Assembly Line          | 152 |

| B Generated VHDL Code      | 159 |

| C SDL Run-Time Components  | 181 |

CONTENTS

vi

# List of Figures

| 3.1  | Example SDL System Structure                                                                                                                | 16 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2  | SDL-92 EFSM Elements                                                                                                                        | 17 |

| 3.3  | Finite event sequence                                                                                                                       | 22 |

| 3.4  | Periodic event sequence                                                                                                                     | 23 |

| 3.5  | Contribution to the event function by one event tuple                                                                                       | 24 |

| 3.6  | Event stream example                                                                                                                        | 25 |

| 4.1  | Hardware design flow targeting FPGA                                                                                                         | 29 |

| 4.2  | Basic hardware architecture implementing one SDL process                                                                                    | 30 |

| 4.3  | VHDL frame for one SDL process                                                                                                              | 34 |

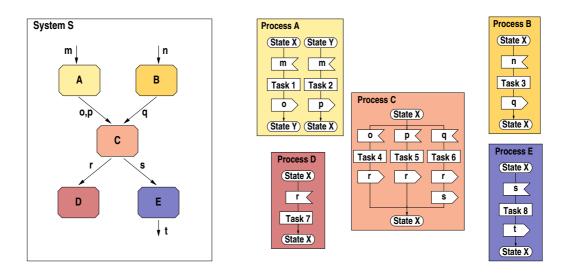

| 4.4  | SDL specification example                                                                                                                   | 36 |

| 4.5  | Server model implementation                                                                                                                 | 37 |

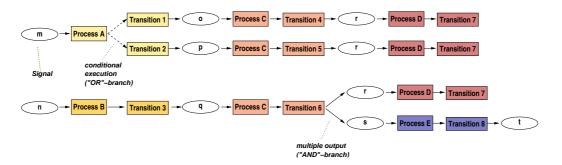

| 4.6  | Task precedence graph of the SDL system from figure 4.4                                                                                     | 38 |

| 4.7  | VHDL frame for one activity thread                                                                                                          | 39 |

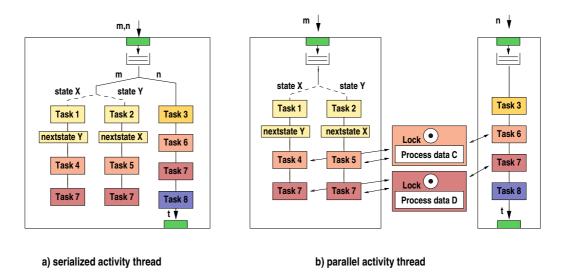

| 4.8  | Activity thread model alternatives                                                                                                          | 40 |

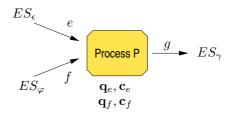

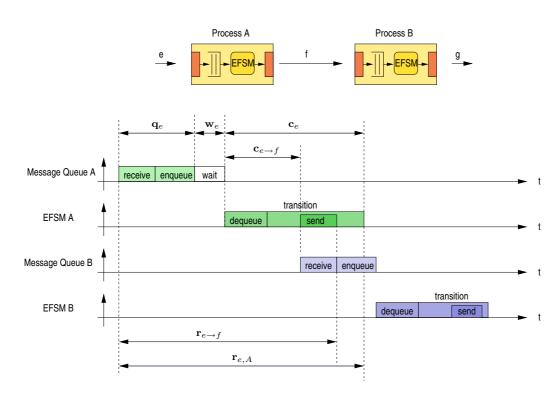

| 5.1  | Top-level view of an implementation process $P$                                                                                             | 44 |

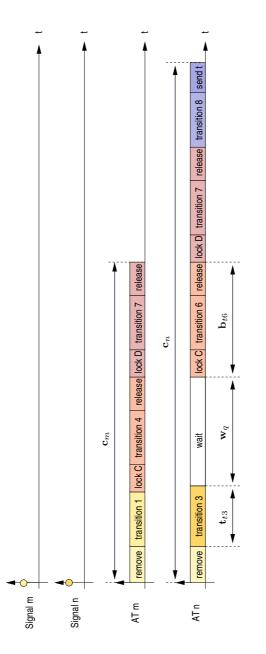

| 5.2  | Timing relationship in a precedence system                                                                                                  | 45 |

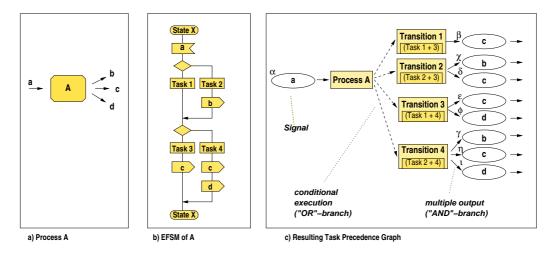

| 5.3  | Derivation of the task precedence graph                                                                                                     | 46 |

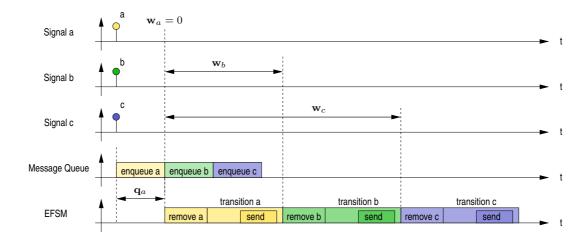

| 5.4  | Variables used during real-time analysis                                                                                                    | 48 |

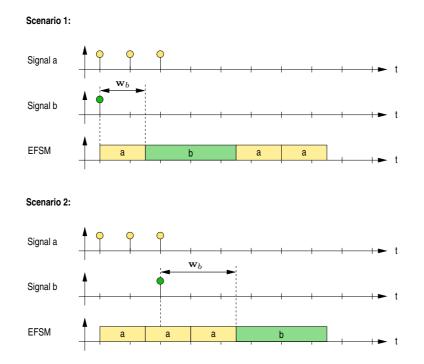

| 5.5  | Detailed view of the waiting time                                                                                                           | 50 |

| 5.6  | First-come-first-serve computation with different event se-                                                                                 |    |

|      | quences                                                                                                                                     | 51 |

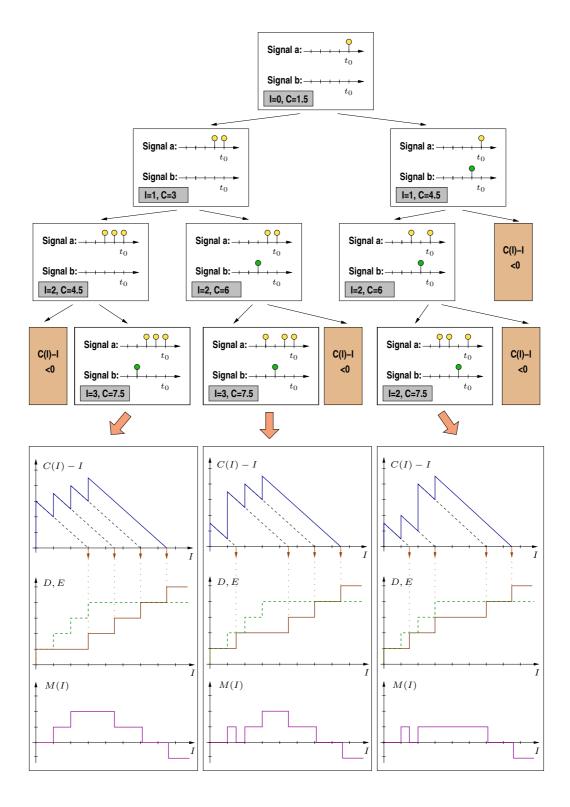

| 5.7  | Determination of $\mathbf{w}$ for the example from figure 5.6                                                                               | 53 |

| 5.8  | Possible event sequences preceding an occurrence of signal 2 at $t_0$                                                                       | 54 |

| 5.9  | Search tree example                                                                                                                         | 55 |

| 5.10 | Example for internal signal $d$                                                                                                             | 56 |

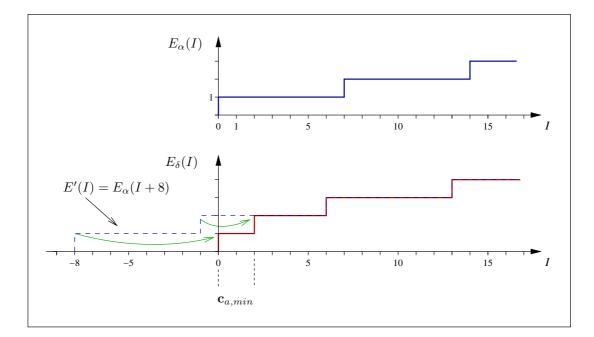

| 5.11 | Derivation of $ES_{\delta}$ from $ES_{\alpha}$ for general $J$                                                                              | 59 |

| 5.12 | Graphical and algorithmical derivation of $E_{\delta}(I)$ for the exam-                                                                     |    |

|      | ple from figure 5.10 $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                       | 60 |

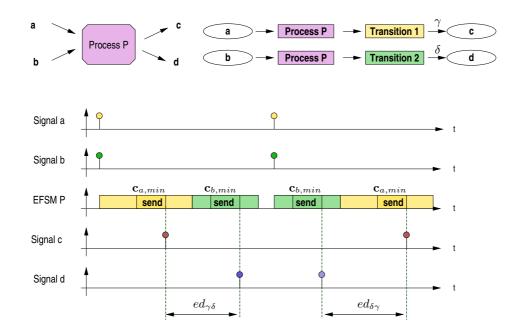

| 5.13 | Event dependencies between signals from one SDL process                                                                                     |    |

|      | $(different transitions) \dots \dots$ | 61 |

|      |                                                                                                                                             |    |

| 5.14 | Event dependency between signals from one SDL process (one                                                                                                |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      |                                                                                                                                                           | 62 |

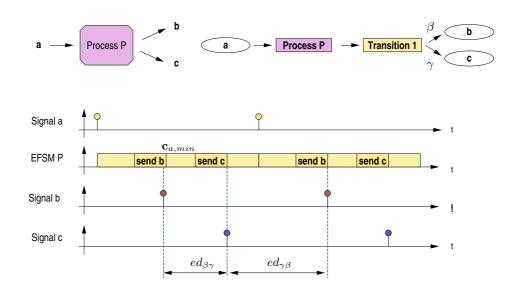

| 5.15 | Propagation of event dependencies between SDL processes                                                                                                   | 63 |

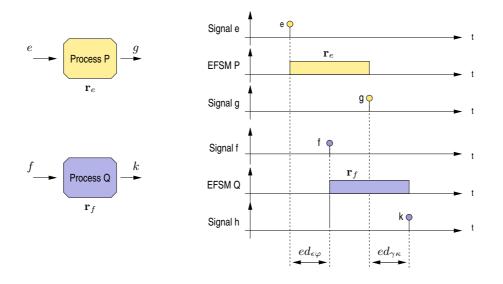

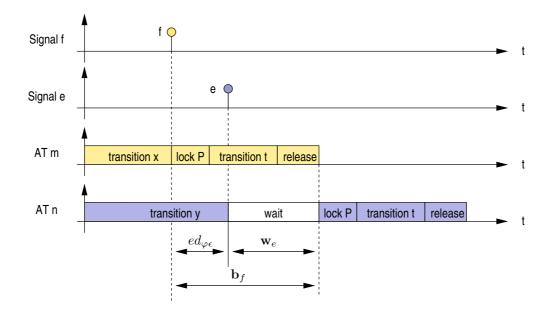

| 5.16 | Parallel execution of activity threads from figure 4.8                                                                                                    | 65 |

| 5.17 | Blocking time influenced by event dependency $ed_{\varphi\epsilon}$                                                                                       | 68 |

| 5.18 | Partial view of Search Tree                                                                                                                               | 70 |

| 5.19 | Cyclic dependency between $ES_{\gamma}$ and $ES_{\beta}$                                                                                                  | 72 |

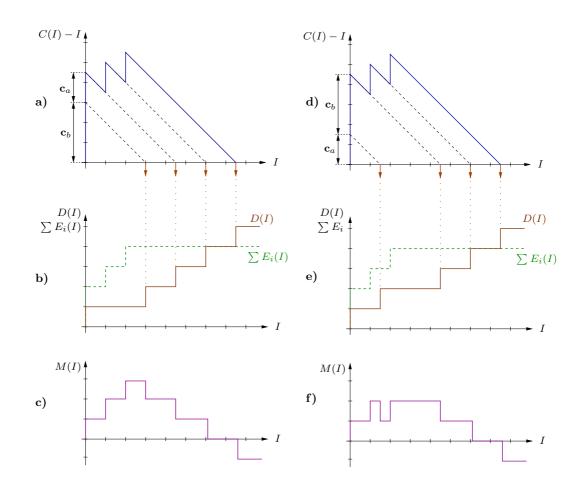

| 5.20 | Derivation of queue depth for example from figure 5.7                                                                                                     | 74 |

| 5.21 | Derivation of queue depth for example from figure 5.7 with                                                                                                |    |

|      | additional event dependency $ed_{\alpha\beta} = ed_{\beta\alpha} = 1$                                                                                     | 76 |

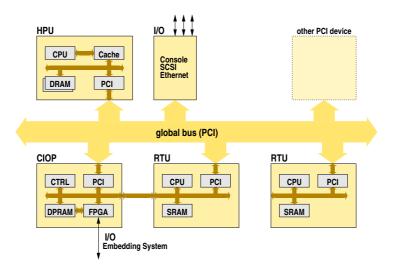

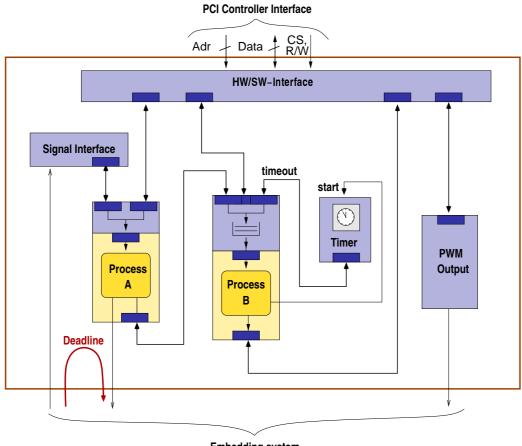

| 6.1  | Rapid prototyping target architecture – block diagram                                                                                                     | 81 |

| 6.2  | Photo of the rapid prototyping target architecture                                                                                                        | 82 |

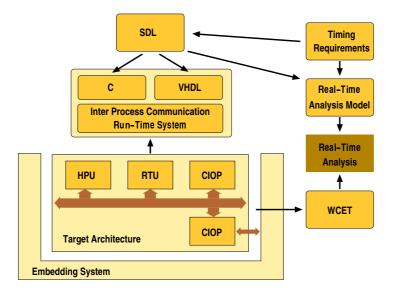

| 6.3  | Rapid prototyping design process – overview                                                                                                               | 83 |

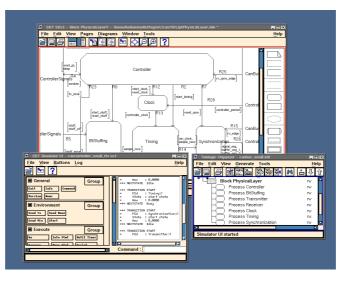

| 6.4  | CASE-tool SDT – screenshot                                                                                                                                | 84 |

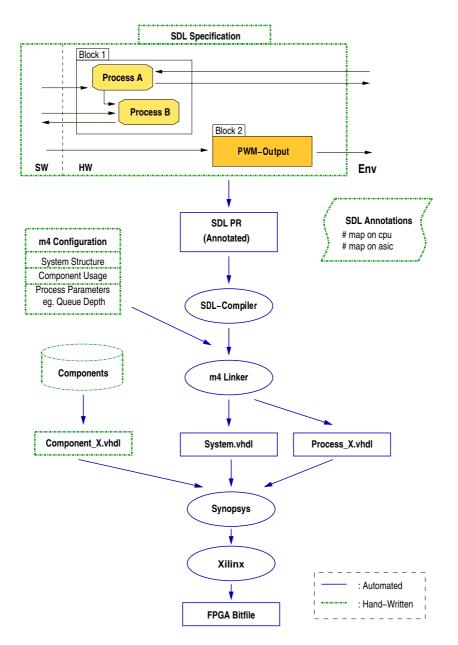

| 6.5  | Rapid prototyping hardware design process                                                                                                                 | 85 |

| 6.6  | Hardware system architecture for SDL example from figure 6.5                                                                                              | 87 |

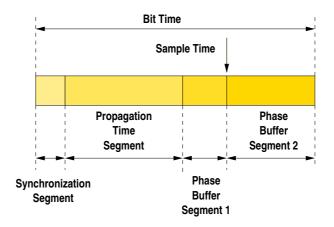

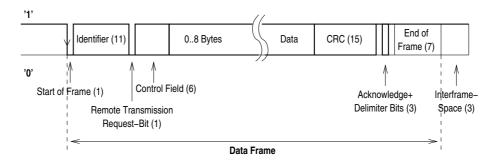

| 7.1  | Internal bit timing in CAN                                                                                                                                | 90 |

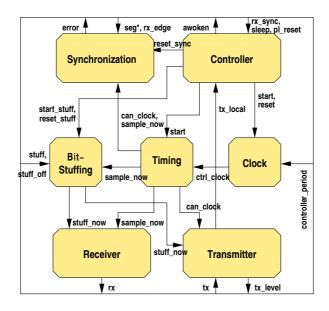

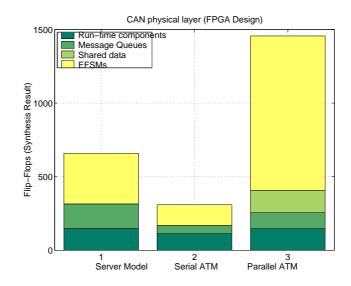

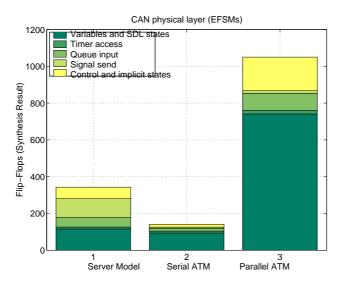

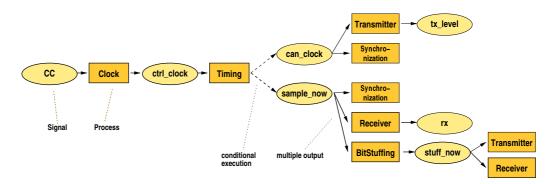

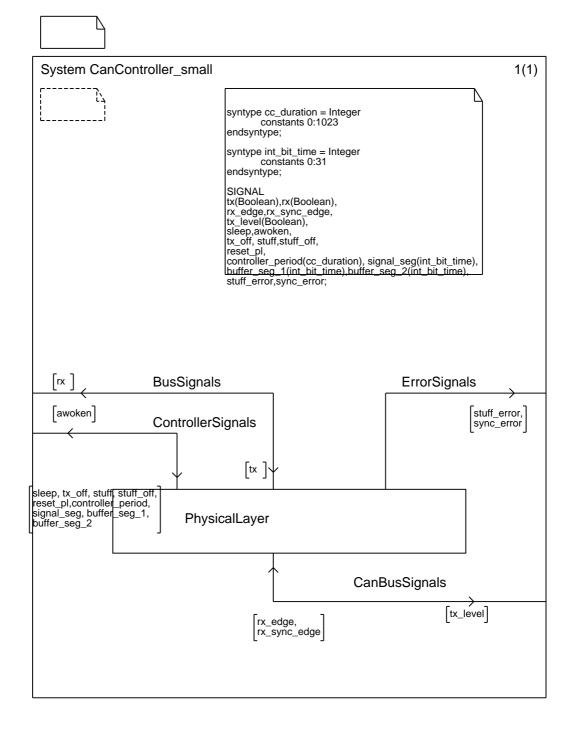

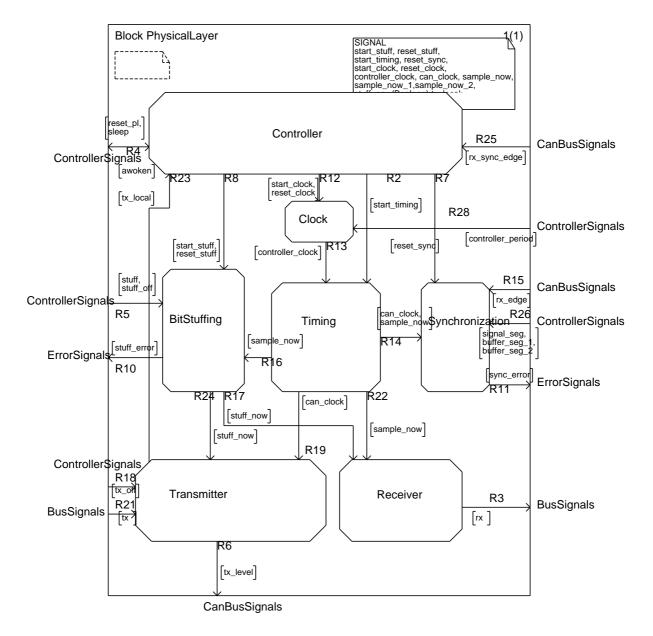

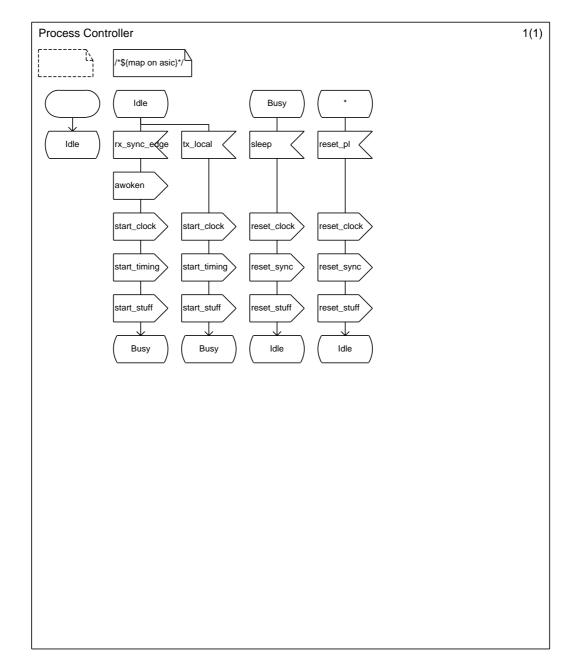

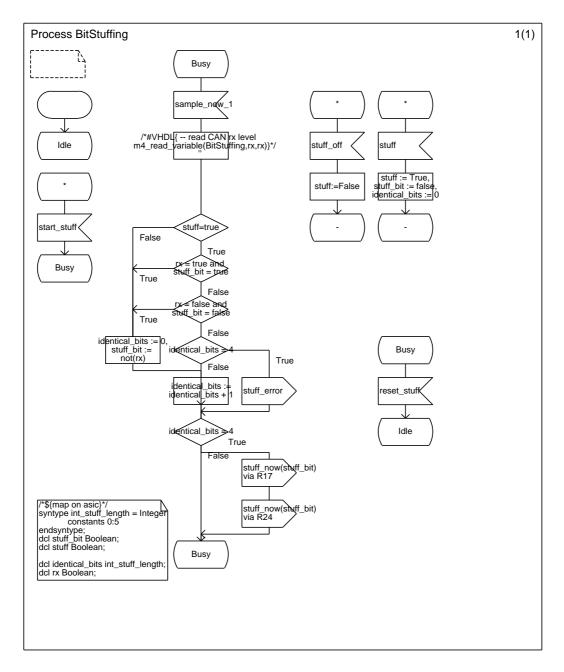

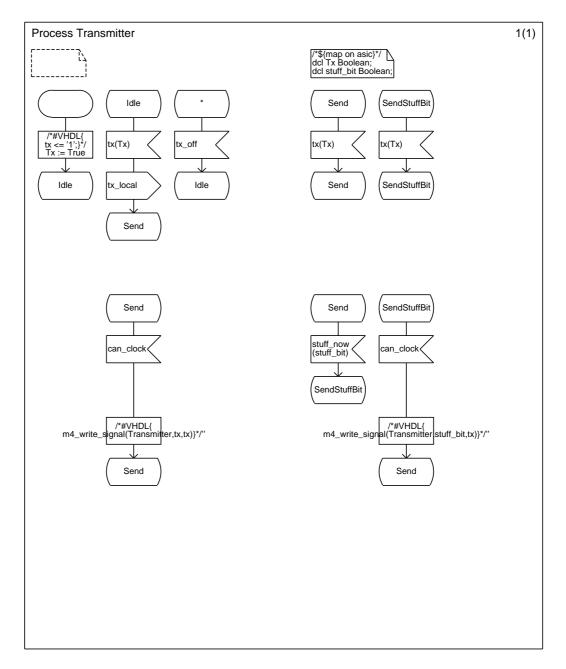

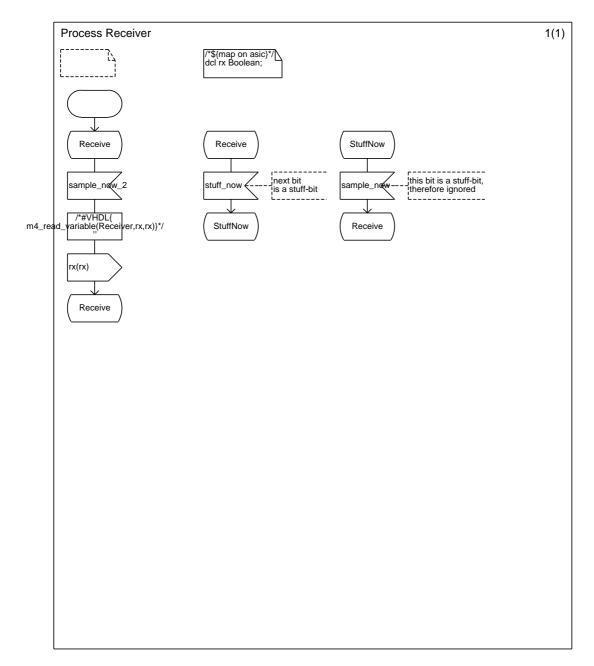

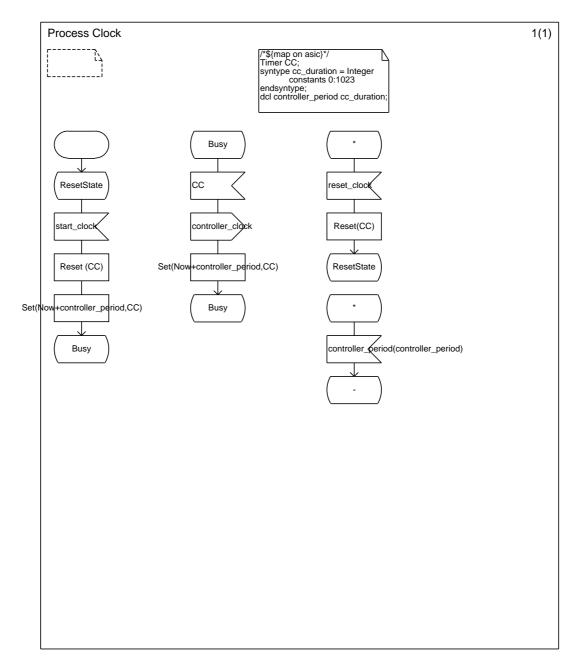

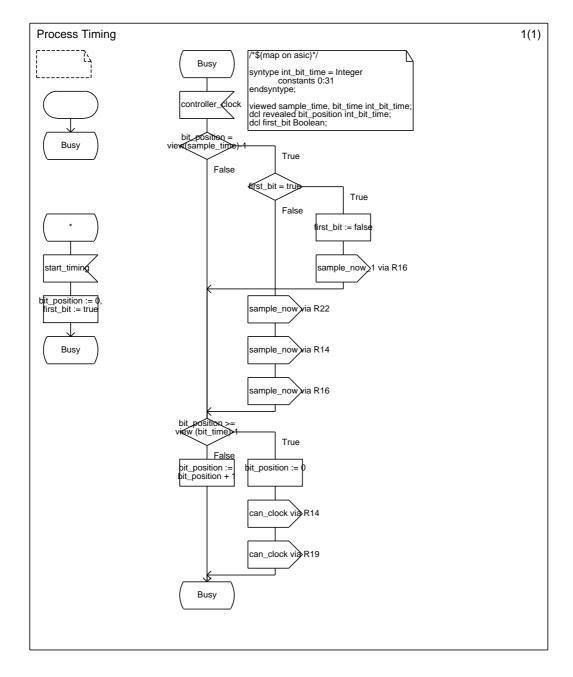

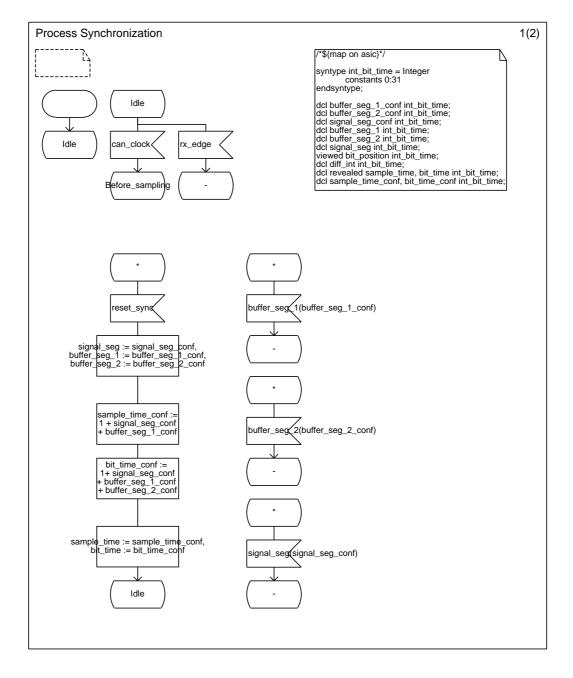

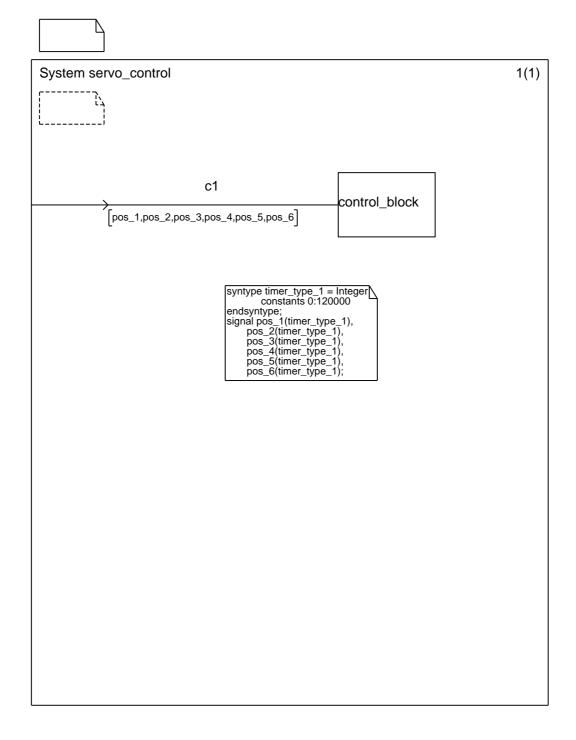

| 7.2  | SDL specification of the CAN physical layer (SDL processes) .                                                                                             | 91 |

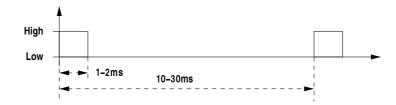

| 7.3  | Timing of the servo motor control signal                                                                                                                  | 92 |

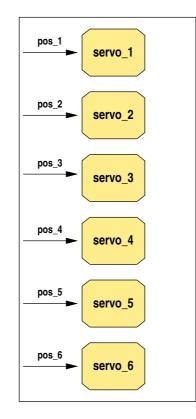

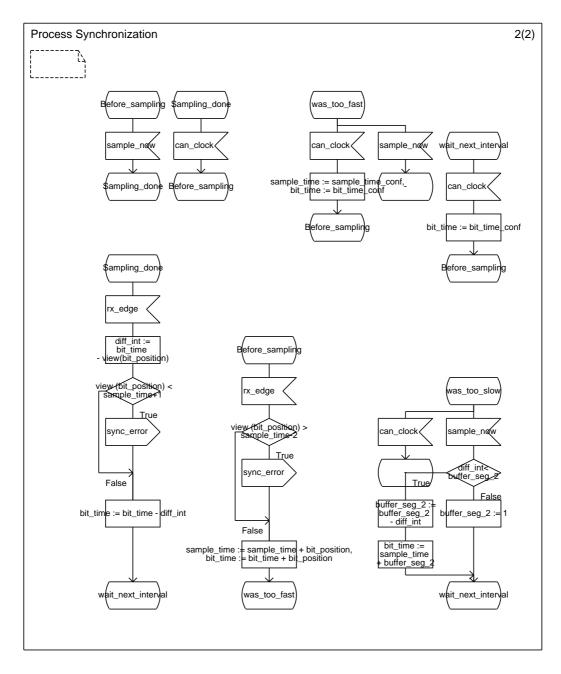

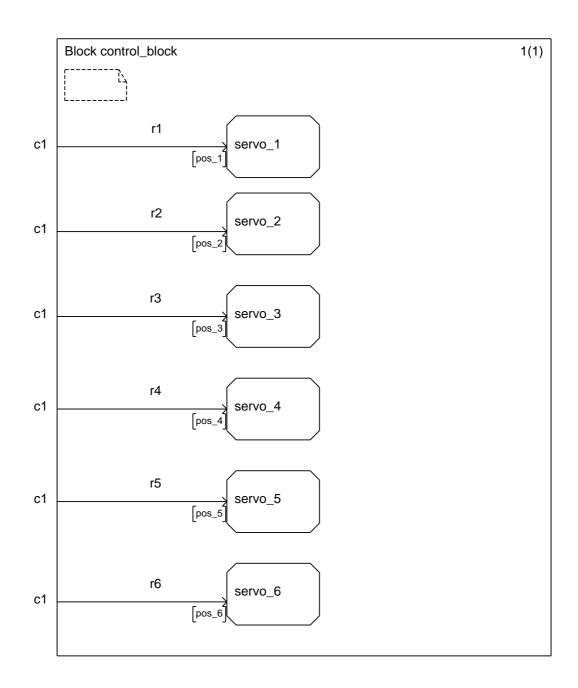

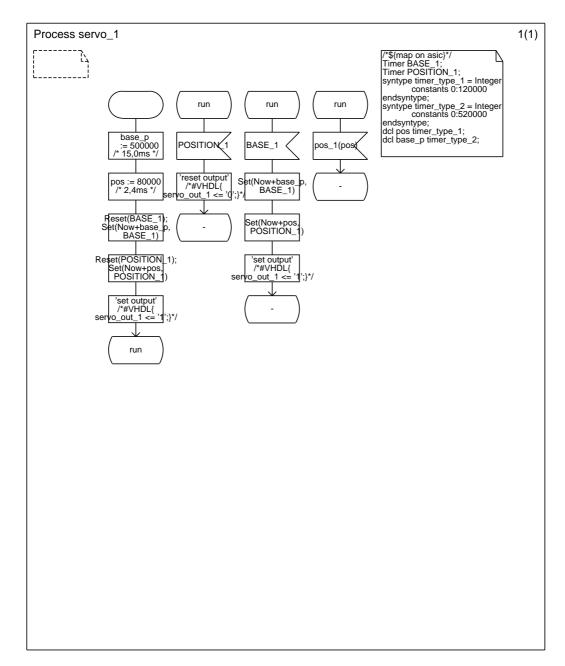

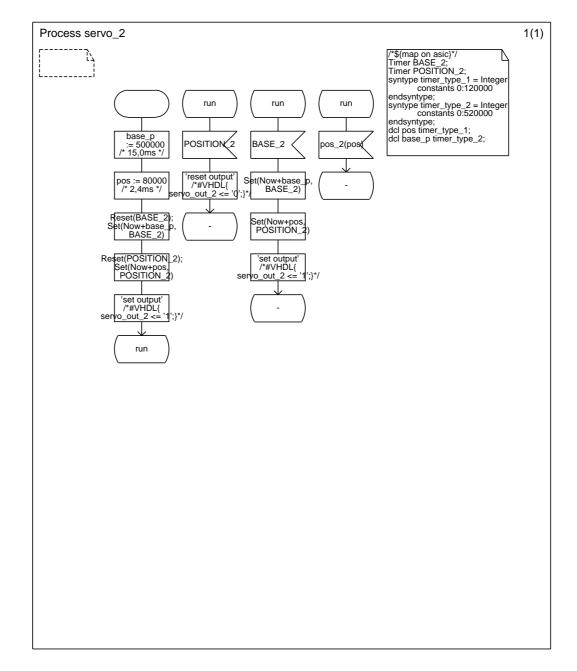

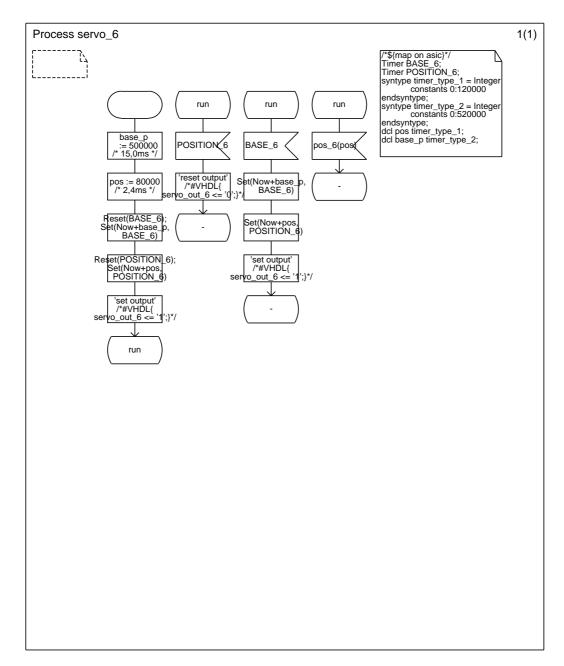

| 7.4  | SDL specification of the servo motor controller                                                                                                           | 93 |

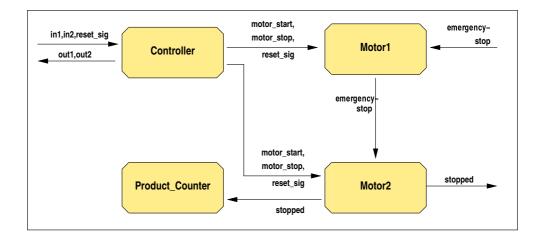

| 7.5  | SDL specification of the assembly line example                                                                                                            | 94 |

| 7.6  | Variables determining resource usage                                                                                                                      | 95 |

| 7.7  | CAN bus: memory elements of the entire FPGA design                                                                                                        | 98 |

| 7.8  | CAN bus: memory elements of the EFSM implementation 9                                                                                                     | 99 |

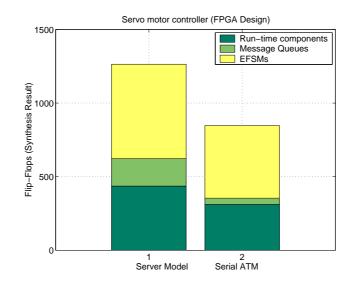

| 7.9  | Servo controller: memory elements of the entire FPGA design 10                                                                                            | 00 |

| 7.10 | Servo controller: memory elements of the EFSM implementation 10                                                                                           | 01 |

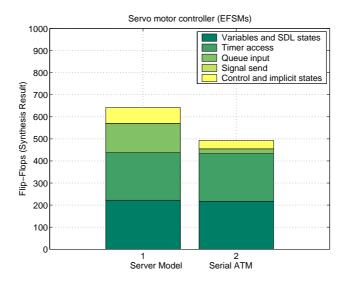

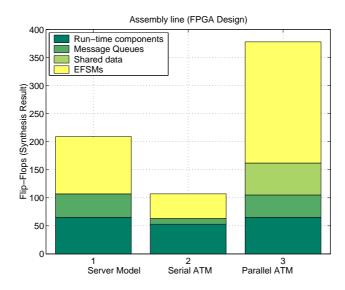

| 7.11 | Assembly line: memory elements of the entire FPGA design . 10                                                                                             | 02 |

|      | Assembly line: memory elements of the EFSM implementation 10                                                                                              |    |

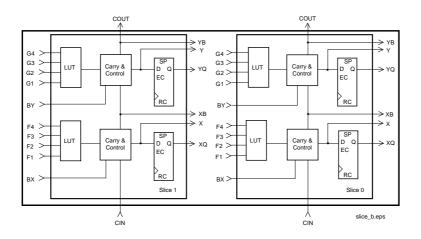

|      | Xilinx Virtex configurable logic block consisting of two slices . 10                                                                                      |    |

|      | CAN message frame                                                                                                                                         |    |

|      | Task precedence system triggered by signal CC 1                                                                                                           |    |

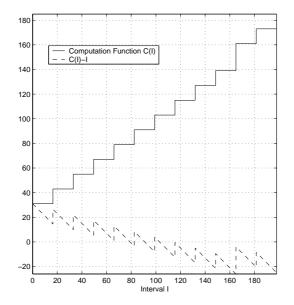

| 7.16 | $C(I) - I$ for $P_{bit} = 14.5  cycles \dots \dots$ | 17 |

|      | Resource usage overview of the application examples 12                                                                                                    |    |

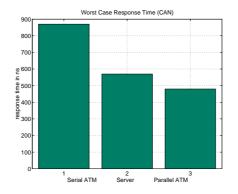

| 7.18 | Maximum response time for the CAN bus example 12                                                                                                          | 21 |

| A.1  | SDL specification of the CAN physical layer                                                                                                               |    |

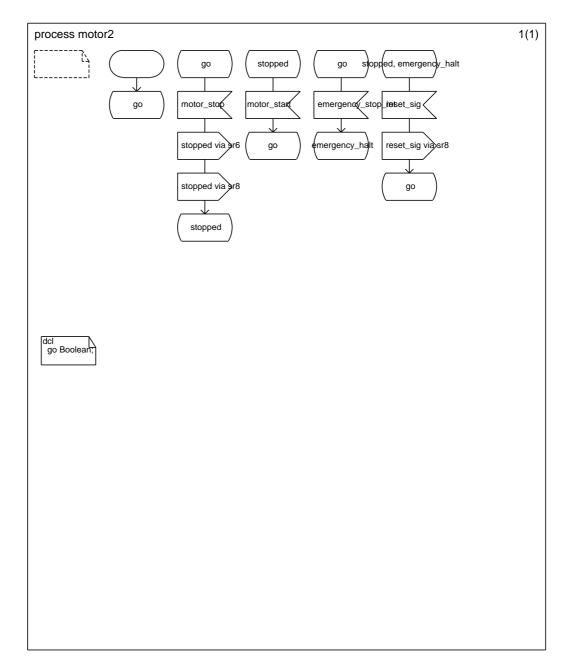

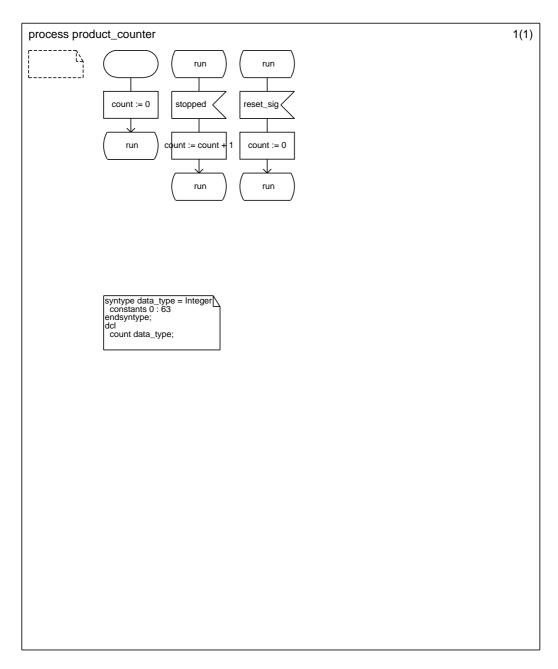

| A.2  | SDL specification of the servo motor controller                                                                                                           |    |

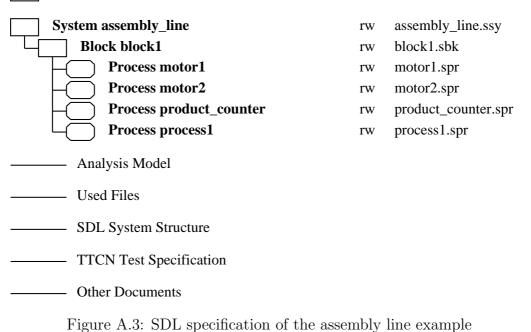

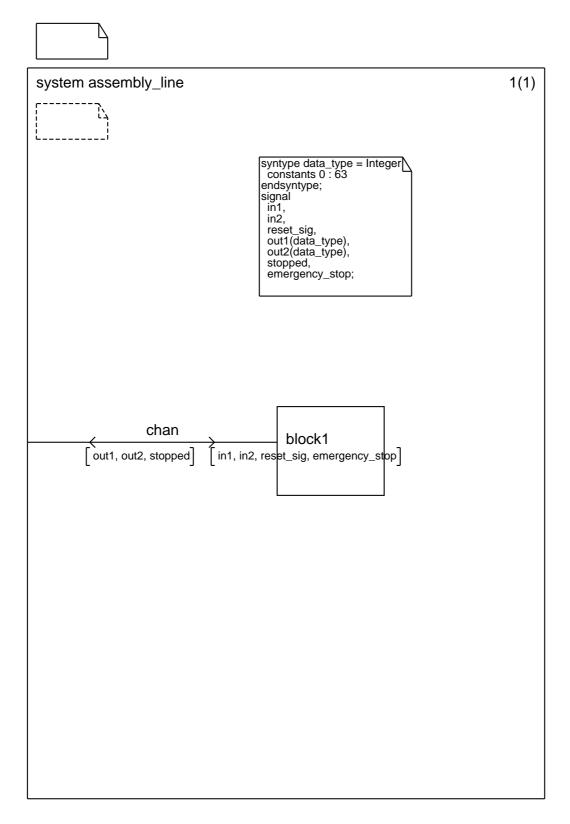

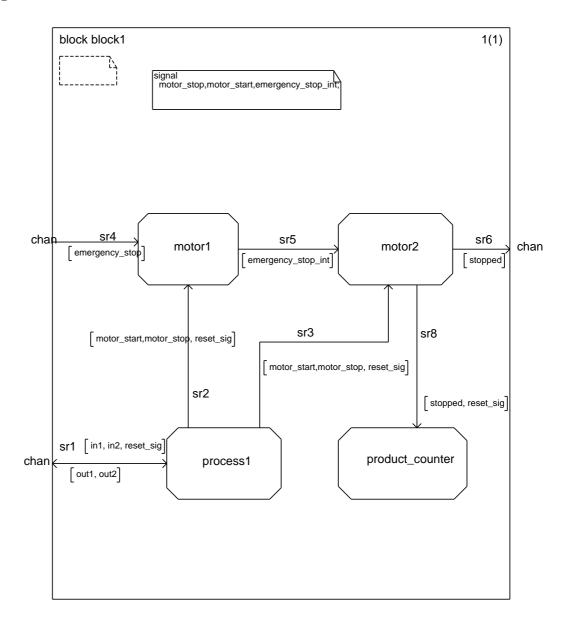

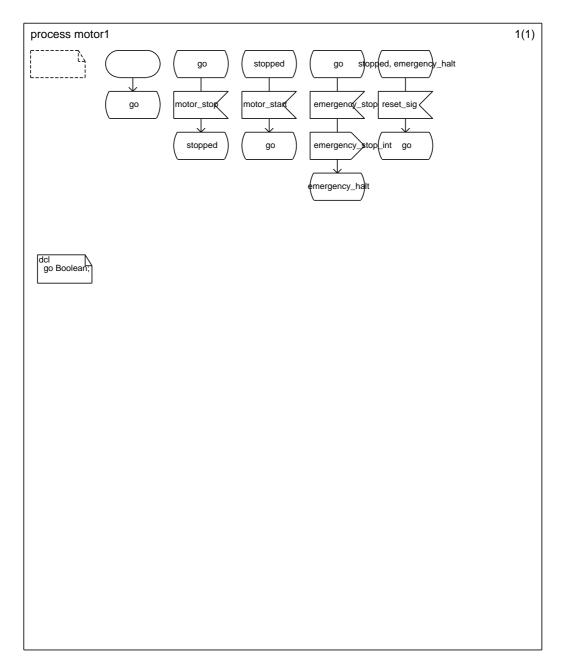

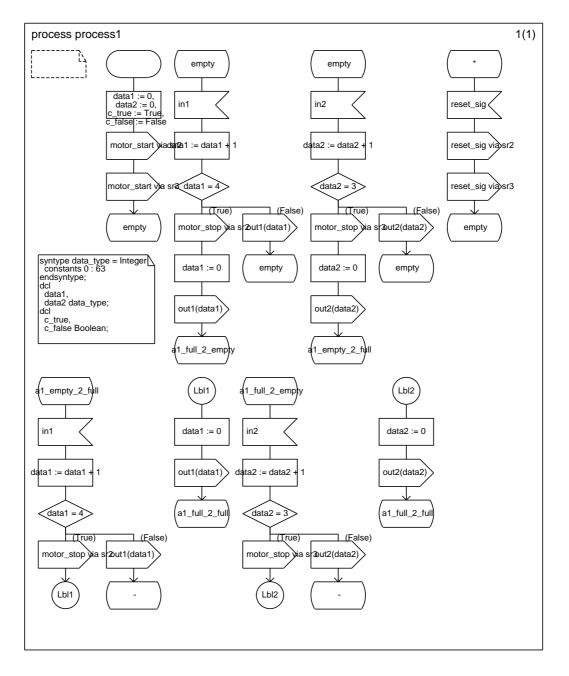

| A.3  | SDL specification of the assembly line example                                                                                                            | 52 |

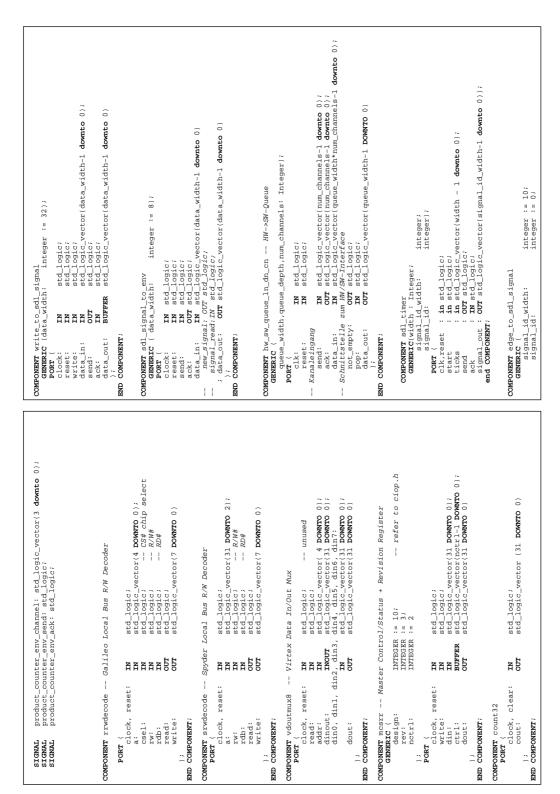

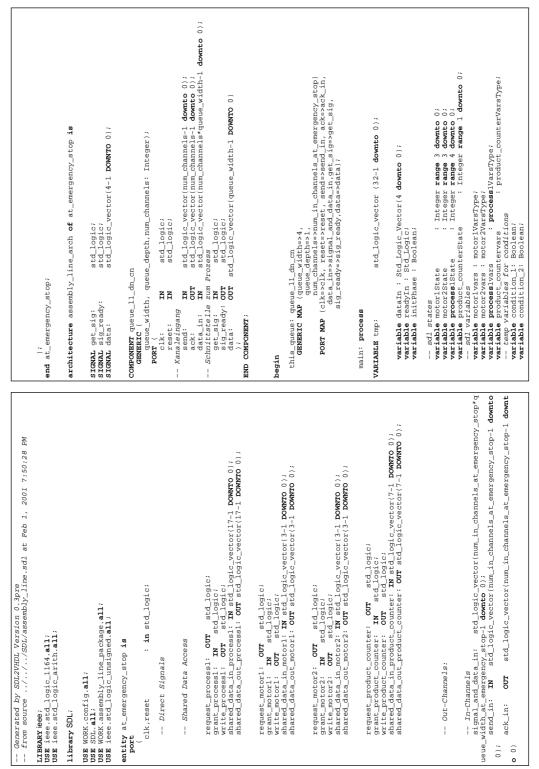

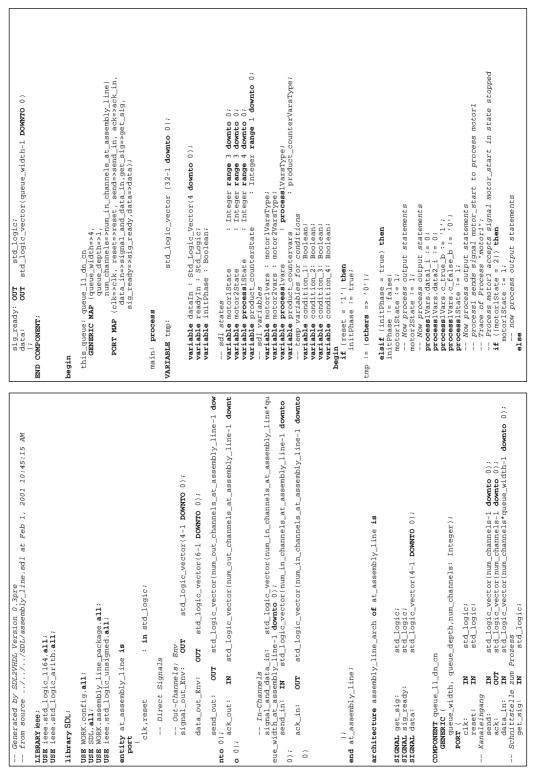

| B.1  | Top-level VHDL file of application example assembly line 10                                                                                               | 60 |

viii

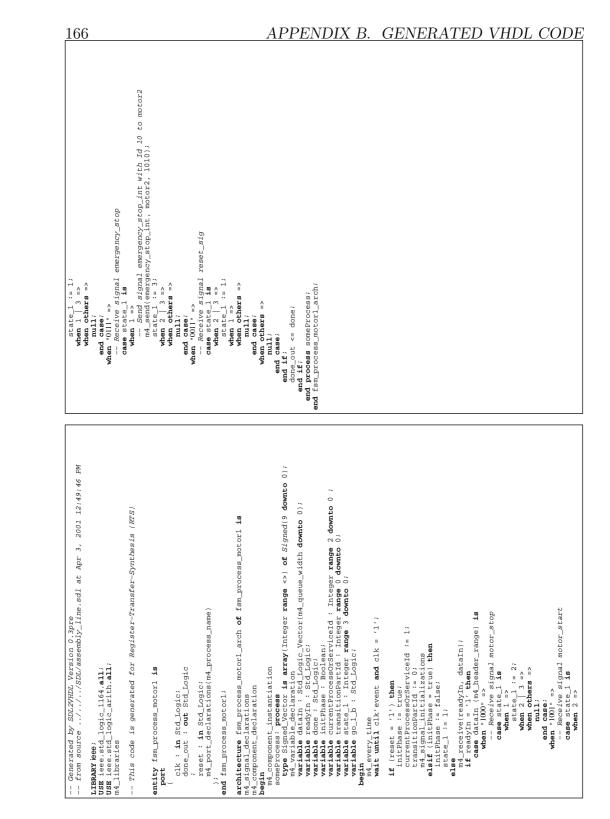

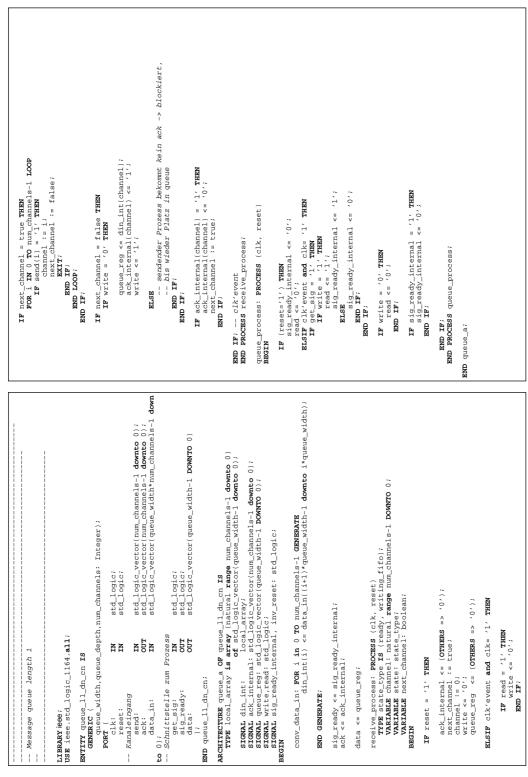

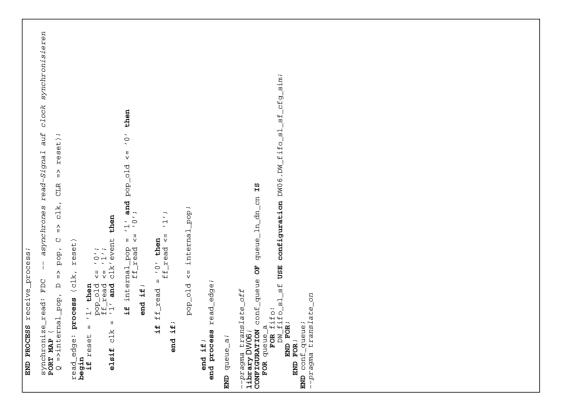

| B.2 | 2 Server implementation SDL process motor1 (before m4 macro                                                                           |  |  |  |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|     | replacement)                                                                                                                          |  |  |  |  |

| B.3 | Server implementation SDL process motor2                                                                                              |  |  |  |  |

| B.4 | Server implementation SDL process process1                                                                                            |  |  |  |  |

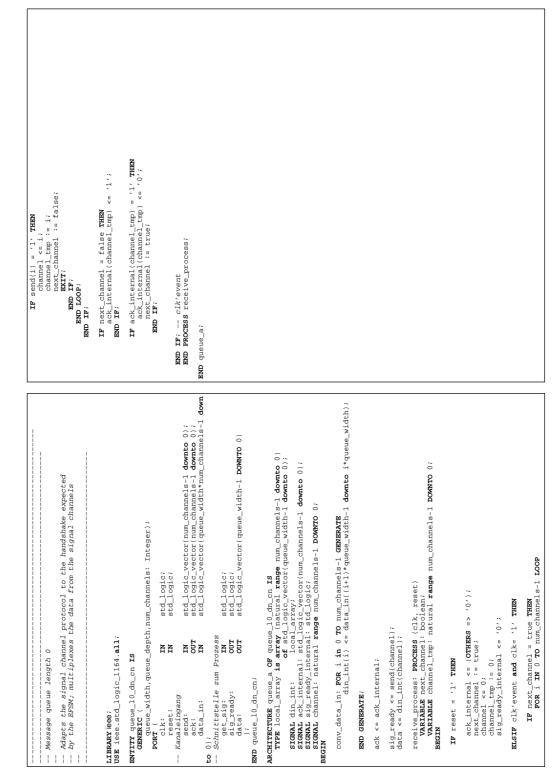

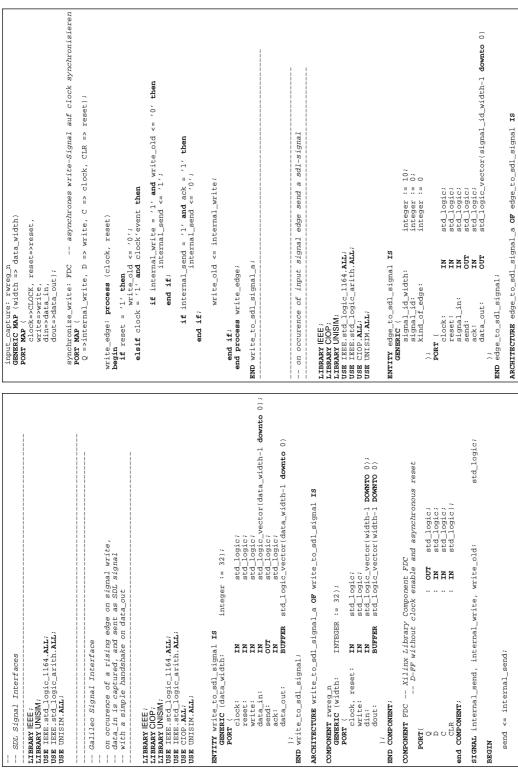

| B.5 | Parallel activity thread implementation of AT emergency_stop 172                                                                      |  |  |  |  |

| B.6 | Serial activity thread implementation (EFSM)                                                                                          |  |  |  |  |

|     |                                                                                                                                       |  |  |  |  |

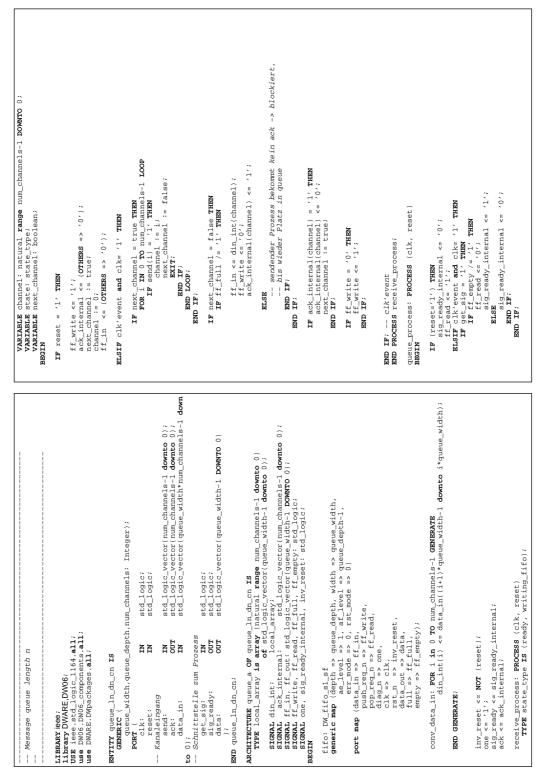

| C.1 | Message queue length $0 \dots $ |  |  |  |  |

| C.2 | Message queue length 1                                                                                                                |  |  |  |  |

| C.3 | Message queue length n                                                                                                                |  |  |  |  |

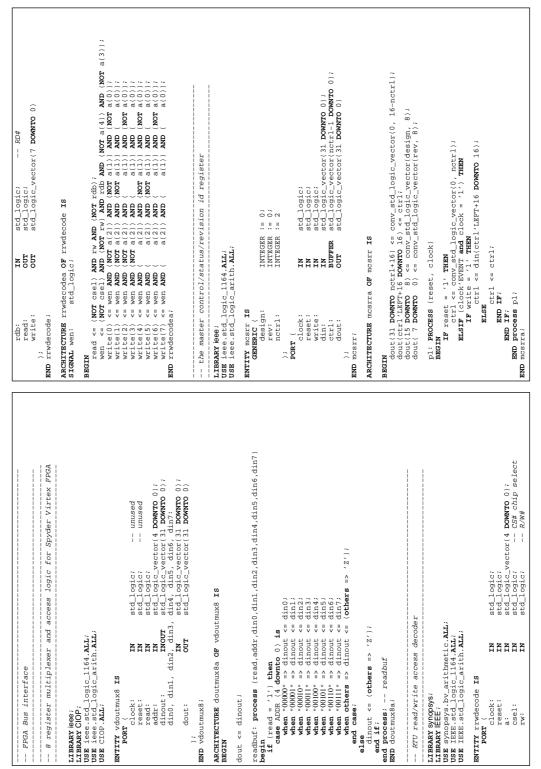

| C.4 | FPGA bus interface                                                                                                                    |  |  |  |  |

| C.5 | Signal input components                                                                                                               |  |  |  |  |

| C.6 | Signal output                                                                                                                         |  |  |  |  |

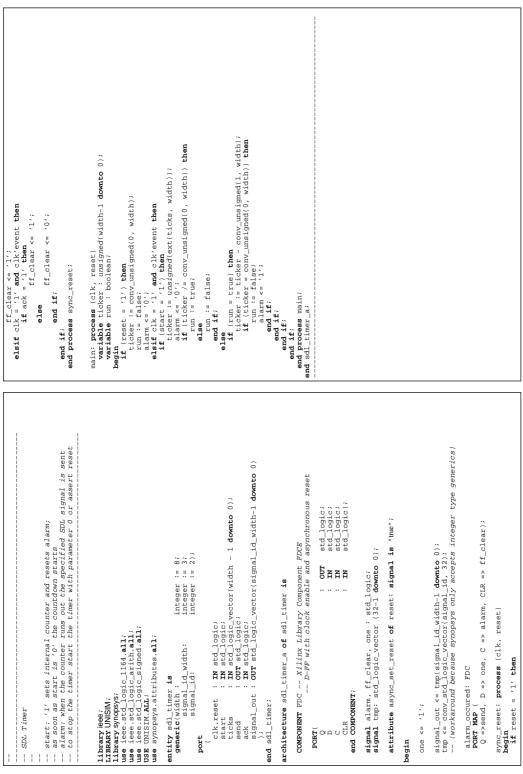

| C.7 | SDL timer                                                                                                                             |  |  |  |  |

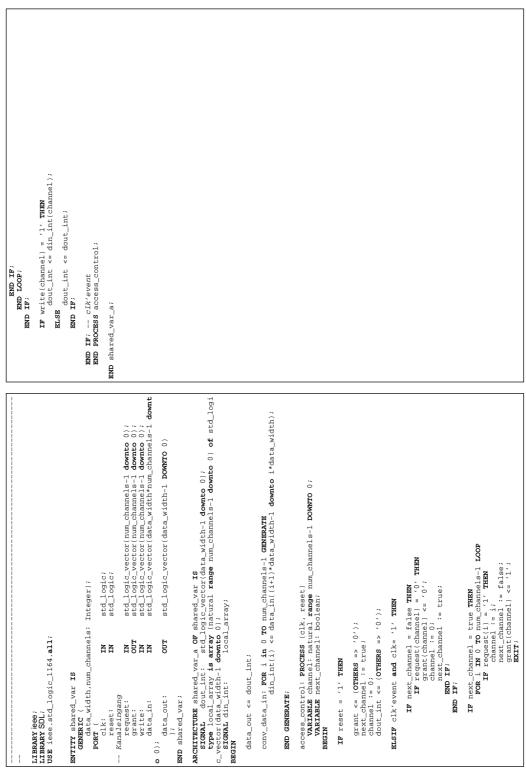

| C.8 | Shared data component                                                                                                                 |  |  |  |  |

# List of Tables

| 2.1                      | Specification Language Overview                                                                                                                                                                                                                                                           | • | • | • | • | • | • | •           | 8                        |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|-------------|--------------------------|

| 3.1                      | SDL Annotations                                                                                                                                                                                                                                                                           |   | • |   | • | • |   | •           | 25                       |

| 5.1                      | Derivation of $ES_{\delta}$ from $ES_{\alpha}$ for $J \leq a_2 - c_{a,min}$ .                                                                                                                                                                                                             | • | • |   |   | • | • | •           | 58                       |

| 6.1                      | Supported SDL Language Features                                                                                                                                                                                                                                                           | • | • | • | • | • | • | •           | 86                       |

| 7.2<br>7.3<br>7.4<br>7.5 | Xilinx resource usage CAN-bus physical layer<br>Xilinx resource usage servo motor controller<br>Xilinx resource usage assembly line<br>Assignment of SDL signals to operation modes<br>Execution times required by run-time components<br>Execution times required by run-time components |   |   |   |   |   |   | •<br>•<br>• | 105<br>105<br>109<br>111 |

|                          | ······································                                                                                                                                                                                                                                                    |   |   |   |   |   |   |             |                          |

### LIST OF TABLES

xii

# Chapter 1

# Introduction

### 1.1 Background

The development of embedded electronic systems presents an increasing challenge for industry and academia: Most new features in many domains, e.g. in automotive and telecommunications, depend on electronics. The increasing density and speed of electronic circuits correspond with an increasing complexity to be mastered during the design process. Sharp competition leads to shortening design cycles and pressure on the development costs, while engineering manpower is turning into a scarce resource. At the same time, embedded systems have to meet stringent requirements, among others functionality, reliability, size and power consumption. Very central among these rank soft and hard *real-time requirements*. These express the embedded system's ability to respond not only correctly but also within a given time.

Modern design methodologies, realized in HW/SW–codesign environments like [EHB<sup>+</sup>96], [COH<sup>+</sup>99], [BCG<sup>+</sup>97] (see also [GVNG94], [Wol94]), aim to meet these challenges by introducing systematic, formal design methods and increasing the degree of automation in the design process. They start with a model of the system under development in one or several specification languages. The use of a system model in a formal specification language has several advantages. Firstly, its defined semantics allow a concise description and avoid the ambiguities of a natural language. Secondly, validation with the help of simulation, formal verification or real–time analysis is possible. Thirdly, a formally defined language makes it possible to write compilers which translate it into a different language. This opens the path to an automated design process, which ensures that an implementation is reached in shorter time, is hopefully error free and consistent with the specification.

Embedded systems typically consist of microprocessors respectively pro-

cessor cores executing software, and application specific hardware. During the automated design process, a suitable architecture of processors, buses and custom hardware is determined and the specification is partitioned and mapped to the available execution units. The next steps towards implementation are communication refinement, automated code generation and synthesis of hardware and software.

Rapid prototyping has been proposed as a method to find errors and flaws in the embedded system's requirements at a very early stage of development. To make this possible, the specification is executed in the real environment in form of a working prototype. In order to rapidly obtain such a prototype, an automated design process like outlined above is used, targeting a rapid prototyping platform. In a rapid prototyping application, the execution of the specification in software means high flexibility, short design cycles and good debug facilities. *Application specific hardware* on the other hand is very often necessary as a link to the embedding process, i.e. for glue logic or a custom bus protocol, and as execution unit for processes with short deadlines. Here, too, it is possible to reach a high degree of flexibility by using reprogrammable FPGAs.

In many application areas, the focus of rapid prototyping lies only on the functional correctness of the embedded system. For *hard real-time systems* however, it is also necessary to include the real-time aspects already at the prototyping stage: In the design of a system that has to meet hard dead-lines, the timing requirements of the embedding system have to be modeled correctly. This is a non-trivial, error-prone task. A real-time analysis in the prototyping stage and the real-time execution of the prototype show if the timing situation has been understood correctly. In contrast to simulation, the idea of a prototype is to be executed in the real world with real data. If the application to be designed has to meet hard timing requirements, they generally will have to be met by a prototype executing in the same environment, too. A schedulability analysis must give the proof that it is safe to execute the prototype.

A multitude of *specification languages* and methods are used in embedded systems design, i.e. C, C++, VHDL, Esterel, Statecharts, Matlab and SDL. Several properties of the "Specification and Description Language" SDL make it well suited for a design methodology like outlined above. SDL allows implementation independent system modeling at a high level of abstraction, in graphical and textual form. Its formal semantics form a solid basis for validation and simulation. Due to SDL's asynchronous execution and communication scheme, dividing and joining models is easy, which allows for more flexibility in architectural synthesis, and efficient implementations on distributed systems. Other, non-technical criteria, are maturity and popu-

#### 1.2. SCOPE

larity of the language, and the well developed tool support. SDL's standardization ([ITU94]) makes it suitable for official authorization procedures, in some of which it is already mandatory. SDL is a supported input format of a considerable number of commercial and academic codesign environments, as outlined in chapter 2.

The automated design flow from SDL to software is state of the art and widely used. The ability to automatically generate application specific hardware from SDL enables the use of SDL in a HW/SW–codesign environment. This makes it possible to use SDL specifications for hardware and software.

### 1.2 Scope

The work presented here deals with the automated design of application specific hardware from SDL in a rapid prototyping HW/SW-codesign environment. It is targeted towards reactive hard real-time embedded controllers. Timing constraints are assumed to have the form of end-to-end deadlines, i.e. a given response time that may elapse until the reaction to an external event is finished. In hard real-time systems, in contrast to soft real-time, the violation of a deadline can lead to catastrophic consequences, up the loss of lives. In this class of systems the correct real-time behavior has to be *proven* during design. Analyzability and guaranteeable worst case response times therefore take precedence over average or best case throughput and latency.

In the rapid prototyping scenario, for cost and flexibility reasons, as much functionality as possible will be implemented in software. Application specific hardware is necessary for processes with deadlines that are too short to be met in software and as a connection to the embedding environment. The envisioned type of application therefore are fast I/O-tasks with relatively low computational complexity. In this sense, application specific hardware is regarded like a pre-processor for external events rather than a co-processor.

The automated design process is part of the rapid prototyping environment REAR presented in [PMK<sup>+</sup>00]. Its rapid prototyping target architecture is a configurable and scalable heterogenous multiprocessor system. A board with a field programmable gate array (FPGA), the so called configurable I/O processor CIOP, is tightly coupled with the microprocessor based units. Functionality targeted to hardware can be specified in SDL. Additionally, standard or custom hardware modules, e.g. written in the hardware description language VHDL, can be included in the HW/SW-codesign environment. To automatically generate hardware from SDL, a compiler translates textual SDL to VHDL. This work investigates the efficiency of the generated hardware in terms of resource usage and timing properties. Different implementation models are developed together with the real-time analysis algorithms needed to determine the guaranteeable worst case behaviour.

### 1.3 Overview

There is a number of research groups and commercial efforts in the context of embedded systems design with SDL, some of which also include application specific hardware. An overview of them is given in chapter 2.

Chapter 3 introduces the specification language SDL. Next to the functional specification, real-time analysis requires a description of the timely properties of the embedding system, which are expressed with the help of event streams. These, together with the given deadlines, define the timing contstraints of the system to be designed. Finally, a method for including predefined, non-SDL components in the specification is suggested.

The transformation principle behind the automated generation of hardware from SDL is called the implementation model. Chapter 4 presents three implementation models for SDL, the server model, the serialized and the parallel activity thread model, as well as the combination possibilities of them. As will be seen, next to the hardware generated for each new specification, there is a number of reusable components like e.g. message queues implementing SDL's asynchronous communication, and timers to be considered. In analogy to software they are named "run-time components".

With functional specification, timing constraints and implementation model known, the real-time analysis from chapter 5 is possible. The primary task here is the calculation of the worst case response times to external events, considering the different implementation models and run-time components. As by-product, an upper bound on the necessary length of the message queues can be given. The consideration of event dependencies during real-time analysis can bring a relaxation of a possibly too pessimistic worst case scenario.

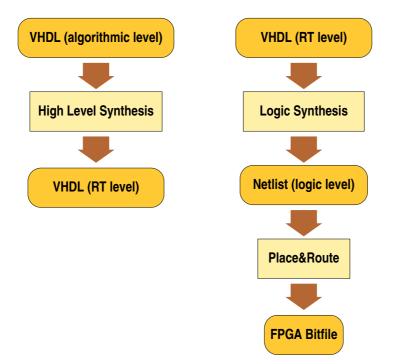

Chapter 6 details the automated design process from SDL to hardware. It describes the rapid prototyping environment in which the presented methods were integrated. The abstract SDL specification is not directly translated to a netlist of logic gates. Instead it is compiled into a high level model in the hardware description language VHDL, using the so called SDL-Compiler. After this step, reusable and additional external hardware components are integrated with the generated VDHL blocks. This includes the interface to the likewise automatically generated software. The complete VHDL model is processed further using commercial synthesis and place-and-route tools.

The rapid prototyping environment also formed the testbed for several

#### 1.3. OVERVIEW

application examples. They were used to gather on-hand experience in a real environment. The gained hardware synthesis and real-time analysis results are presented together with an evaluation in chapter 7. The work finishes with conclusions and indications of future work in chapter 8.

# Chapter 2 Related Work

In the last 30 years, an extremely large number of specification languages has been developed. For a classification, [GVNG94] identifies four basic concepts: concurrency (control or data oriented concurrency), hierarchy (structural or behavioral hierarchy), communication (message passing or shared memory) and synchronization (synchronous or asynchronous). In different fields of application, languages with different characteristics have been found to be useful. A good overview is e.g. given in [JRM<sup>+</sup>99].

The degree of abstraction required depends on the phase of the design process. During the requirements phase, a modeling at *system level* is appropriate. Here, the required functionality is defined. Architecture and implementation details are not fixed yet. There are few indications about timing, except for some global constraints. At the *algorithmical level* and *register transfer (RT) level*, the level of detail increases, until the implementation is completely defined.

Table 2.1 which was adapted from [MdCP01] lists typical time granularities and models of computations at the different levels of abstraction. It shows representative specification languages used in the hardware and software domain and their association to these design levels.

For the description of hardware at the algorithmical and RT-level, the languages VHDL and Verilog ([IEE00],[IEE95]) are de-facto standard with an excellent tool support. In a VHDL model at RT-level, be it a structural or a behavioural description, each operation is assigned to one clock cycle. RT-level synthesis tools, like e.g. Synopsys Design Compiler translate it to a equivalent network of registers and combinational logic. After logic optimization, resource allocation and mapping a netlist of components from a

|            | Time          | Computational     | HW             | $\mathbf{SW}$ |

|------------|---------------|-------------------|----------------|---------------|

|            | Granularity   | Model             | Languages      | Languages     |

| System     | Transactions  | Task graphs,      | StateCharts,   | SDL, Matlab,  |

| Level      |               | communicating     | SDL, Java      | Java, Esterel |

|            |               | processes         |                |               |

| Algorithm  | Computational | Control Flow      | VHDL, Verilog, | C/C++         |

| and        | Steps         | Graph, Data Flow  | C/C++ with     |               |

| Functional |               | Graph             | extensions,    |               |

| Level      |               |                   | e.g. SystemC   |               |

| Register   | Clock Cycles  | Finite State      | VHDL, Verilog, | Assembler     |

| Transfer   |               | Machines,         | RT-C           |               |

| Level      |               | Boolean equations |                |               |

Table 2.1: Specification Language Overview

target library is generated. From this netlist, vendor-specific place-and-route tools generate a layout of the digital circuit.

In contrast to this, at the algorithmical level, the timing is not or only very roughly fixed. Here as well, a description in VHDL or Verilog is usual. This kind of model can be handled by a high-level synthesis tool like e.g. [BR98]. It generates a processor, consisting of controller and data path, which implements the specified behaviour. To achieve this, the steps scheduling, resource allocation and binding have to be performed. The loosely defined timing means, that a given operation, e.g. an addition, can be scheduled in different clock cycles. This makes it possible to find a schedule, where components, e.g. the adder, can be reused and therefore resources saved.

In the last years, many institutions have attempted to introduce C-based languages for hardware design at algorithmical and RT-level (e.g. Stanford's HardwareC, Irvine's SpecC, SystemC by Synopsys, C-Level by EASICS, Cynlibs by CynApps). The idea is to use the wide-spread language C and C-based development environments by extending C with libraries and classes to express hardware specific concepts, in particular concurrency and timing. In most of these frameworks, the level of detail is exactly the same as in dedicated hardware languages. Therefore, even though the same language as for software is used, due to the implementation specific degree of detail, no unified view on the entire system can be taken. The acceptance in the hardware design community on the other hand is difficult. The willingness to adapt a new language is especially low if the advantages are not clearly seen. A further problem lies in the lacking standardization of the various proposals.

A number of HW/SW-Codesign approaches are based on the specifica-

tion language SDL. A SDL specification consists of parallel processes, whose behaviour is specified with extended finite state machines. SDL processes communicate via asynchronous messages.

**Pulkkinen** ([PK92]) and **Turner** ([CT97]) use SDL to model electronic circuits at RT-level. SDL's event triggered semantics, the lacking features for an exact modeling of time and the missing broadcast mechanism make it poorly suited for a detailed description of electronic devices and circuits. This results in long winded, clumsy specifications. The advantage over the already presented HW modeling methods, e.g. VHDL, remains unclear, as well as how these approaches could be integrated in an automated hardware design flow.

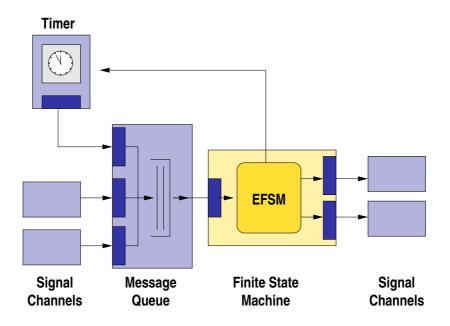

All other approaches use SDL for a functional specification at system level. Two implementation models, which preserve the semantics of SDL are the server model and the activity thread model. In the **server model**, each SDL process is implemented as a single RTOS task in SW, respectively as a separate VHDL entity in the HW implementation, each with its own message queue. In contrast to this, the **activity thread model** maps each activity thread, i.e. each chain of activations in the SDL model caused by one stimulating event (an event from the environment or a timer output), to one RTOS task respectively HW entity.

The terms server model and activity thread model stem from the telecommunications area, where they are used to describe different stategies to implement multilayer communication systems ([Svo89]). In the server model, each protocol unit from one OSI layer is implemented as a single software task, communicating with other layers via messages. In the activity thread model, one software task processes an incoming or outgoing request through several layers, avoiding queueing and process management overhead.

Henke and Mitschele-Thiel ([HKMT97]) proposes the employment of efficient methods known from the manual implementation of communication systems in an automated software design process based on SDL. In their realization of the activity thread model, each SDL process is implemented as a reentrant procedure. Each activity thread is a sequence of calls to these procedures, whereby each SDL-signal-output statement is replaced by the procedure call corresponding to the signal's destination process. Here, special attention has to be paid towards a sementically correct implementation, especially in the cases "multiple output statements" and "action after output" (for more details see section 4.4). Two execution models, the basic and extended activity thread model, are presented. In the basic activity thread model, all activity threads are implemented in one operating system (OS) task; the processing of a new external signal is postponed until the processing of the previous signal has been finished. In the extended activity thread model, each activity thread is implemented in its own OS-thread. Here, timely interleaving of several activity threads is possible and depends on the applied scheduling strategy. Obviously, the procedures implementing SDL processes have to be protected with a semaphore.

**Commercial code generators** for SDL targeting software, like SDT's CAdvanced, CBasic and CMicro C-code generators ([Tel]), only support the server implementation model. In an implementation of a SDL specification on a single processor, the theoretically parallel SDL processes are sequentialized. The timely ordering depends on the scheduling algorithm. In the so called light integration (all SDL processes in one OS task), scheduling is implemented in the task body which is generated by the code generator. In a tight integration scheme, one SDL process equals one OS task; here, the scheduling is determined by the operating system. Naturally, these implementation decisions have a strong impact on the real-time behaviour. This problem area is investigated in [Kol01].

Several approaches generate VHDL using the server model. The main focus here is mapping the abstract communication between SDL processes to existing interfaces and protocols.

A framework for the automated design of high-performance communication subsystems is presented by Schiller in [CS98]. The parallel, hardwarebased target architecture consists of RISC-processors, specialized protocol function units, programmable and synthesizable protocol automata, and memory, connected via a crossbar switch. C-code for the processors, microcode for the programmable protocol automata and especially RT-level VHDL for the synthesizable protocol automata are generated from SDL. One synthesizable protocol automaton, which implements one SDL process, consists of an I/O-interface connecting it to the input queue and the crossbar switch, an ALU-interface to a local ALU, and an execution and control unit; i.e. control and data path are seperated. I/O-interface and ALU-interface are predefined components adapted to the target architecture. The execution and control unit is generated by a SDL-to-VHDL compiler. It implements only the bare finite state machine of the SDL process. The storage of state and variables and all data operations are located in the ALU. The direct generation of register-transfer level, i.e. cycle-fixed VHDL is possible, because the data width is fixed to 32 bit and the execution duration of operations of the ALU is known, once the compiler has mapped all parts of the transition to ALU-commands. This work is very specialized and efficient for communication protocols, but not easily transferable to other applications.

The SDL-to-VHDL translator described by **Glunz** in [Glu94] and [GKRM93] presents an architecture for implementing general SDL specification in hardware. The target architecture for each SDL process consists of

3 parallel VHDL entities: a receiver unit, a message queue and a processing unit. The receiver unit is responsible for the input of SDL messages. It must run independently from the other units to ensure SDL's non-blocking sendoperation. The message queue stores the incoming SDL messages. The processing unit directly implements the extended finite state machine (EFSM) of the SDL process. This architecture is the basis for several other approaches ([DMVJ97],[BRM<sup>+</sup>99]), and is also presented in greater detail in section 4.3. An important focus of the work is SDLs abstract communication. It presents a formalism to describe the actual hardware channels and their protocols which realize the communication. For modularity and reuse, the protocols can be layered, distinguishing between application independent and application specific. At the lowest level, the protocols are defined in RT-level VHDL. An implementation description finally maps the logical SDL signal channels to these physical channels, which are taken from a library. It further defines the necessary length and the coding and decoding procedures for the message queue. Even though the main target of this SDL-to-VHDL system seems to have been on simulation, Glunz emphasizes that the generated VHDL is synthesizable, which has been confirmed in [Rin98]. The direct generation of RT-level VHDL from SDL is possible, because the integrated protocol implementations are at RT-level and all data operations at SDL level are written in "native" VHDL and directly inserted in the generated finite state machine. The scheduling of these operation is hence the responsibility of the designer at SDL level, which represents somewhat a contradiction to the desired implementation independent SDL system specification. The modular and layered specification of receiver unit and also message queue is very flexible. Compared with "monolithic" components, however, it leads to a resource and execution time overhead, which adds to the communication overhead inherent to all server model implementations.

In [DMVJ97], the VHDL generation is embedded in the codesign environment **COSMOS**. An SDL description is translated to an intermediate format, which consists of processes communicating via remote procedure calls over abstract channels. Each SDL process is allocated one abstract channel, which represents the input message queue and its interface. The SDL processes' behaviour is translated to the corresponding finite state machine. During a partitioning step, state machines may be splitted and merged. During an interactive, human guided compilation, the abstract channels are mapped to communication units. For these, finally an implementation from a library is selected and the required interfaces and interconnections are generated. The generated VHDL model is targeted at simulation and high level synthesis, i.e. timing and the final RT-level hardware architecture are not fixed in the SDL-to-VHDL step. **Arexsys**<sup>1</sup>, the commercial spin-off of the TIMA laboratory, markets a codesign environment based on COSMOS. The CASE-tool environment, which includes cosimulation, architectural exploration and design implementation is described in [MdCP01]). A case study, where these tools were used for the HW/SW codesign of an image processing unit at Aerospatiale Missile Division (specification in SDL, generation of C and VHDL) is presented in [ABG<sup>+</sup>99]. Interestingly, in the COSMOS environment high level synthesis is no longer used for further processing of the generated VHDL. As also noted in [BRM<sup>+</sup>99], high level synthesis often yields poor results when generating the controller and datapath for the VHDL model of the SDL processes' behaviour, which already is in form of a finite state machine. On the other hand, it is not possible to predict in the general case what kind of operations will be specified in the SDL transitions, and therefore how many cycles they will need in hardware. The solution, like described in [CSMJ00], is to use only the scheduling step of high level synthesis, that is to assign all operations in the generated VHDL to clock cycles. The structure of the FSM is left intact and resource allocation and binding are performed by RT-level synthesis tools.

The **Cadence Cierto VCC** environment ([Cad99a])<sup>2</sup> is based on Berkeley's Polis approach ( $[BCG^+97]$ ). Similarly to the Arexsys evironment presented above, it aims at a continuous design flow from a system level specification towards implementation. It supports a number of input languages, e.g. Esterel, C, VHDL and a subset of SDL. Next to architectural exploration, cosimulation and performance estimation, also a link to an implementation in C and VHDL is described in [Cad99b]. However, no details on the implementation of SDL processes in hardware have been found.

Slomka et al. present in [SDMH00] a rapid prototyping system for high performance communication systems based on SDL. The core of their co-design system is a Java based SDL-Compiler, which was utilized and developed further in cooperation with the rapid prototyping project presented in this work. For the data-intensive applications from the communication systems domain, a mixed hardware synthesis approach is applied ([BRM+99]). Run-time components are defined and synthezised at RT-level while the behaviour of the SDL process, possibly with many data operations, is synthesized using a high-level synthesis system. To address the already mentioned limitations of high-level synthesis, a novel implementation scheme is proposed in [SDM01]. Similar to Schillers work ([CS98]), each SDL process is separated into control and data path. The finite state machine of the SDL

<sup>&</sup>lt;sup>1</sup>www.arexsys.com

<sup>&</sup>lt;sup>2</sup>www.cadence.com/technology/hwsw/ciertovcc

process is implemented at RT-level in one hardware or software entity, while the body of the transitions form a separate entity, which can be synthesized using high-level synthesis. In contrast to Schiller, no predefined ALU is used, but an own processing unit is synthesized for each transition. First results indicate a considerable communication overhead, which leads to a only minimally reduced resource usage.

The work of **Hemani et al.** ([SKH98], [HSK<sup>+</sup>99]) is based on a concept aiming to support SDL's dynamic process creation feature also in hardware. Here, one entity is created for each SDL process class, storing and loading the context of each process instance after a simple schedule. Due to the dynamic instantiation, a signal's receiver cannot be determined statically. This necessitates a central supervisor unit in the communication subsystem. What remains unclear is at which point the overhead caused by this infrastructure is smaller than the resources multiple instances provided from the start would cause. For a large number of active instances, on the other hand, the serialization due to the shared processing unit would cause a very slow response time. This in turn challenges the decision for implementation in hardware compared with software.

Concluding, it can be remarked that the large body of work concerning automated implementation of SDL in hardware utilizes the server implementation model. Much attention is paid to the realization of SDLs abstract communication on concrete components and protocols. A further issue is the refinement of timing down to the cycle-true specification required for the synthesis of a digital circuit. None of the approaches known address the problem of real-time behaviour and analysis.

## Chapter 3

# Specification with SDL

This work uses the Specification and Description Language SDL for the functional specification of the system under development. Section 3.1 presents the language SDL, concentrating on the language features relevant for implementation in general and on the subset which is supported in hardware.

SDL is however not intended for the specification of non-functional aspects. In the context of hard real-time systems, particularly the real-time constraints are of importance. This is dealt with in section 3.2, which introduces the language annotations chosen for expressing timing constraints, and the underlying event stream model for describing the temporal behaviour of the embedding system.

Next to the parts of the design functionally described in SDL, it is also possible to include predefined hardware components and IP in the design process, which is described in section 3.3.

### 3.1 Functional Specification with SDL

#### 3.1.1 Background

SDL is a Specification and Description Language standardized as ITU (International Telecommunication Union) Recommendation Z.100 for the specification of telecommunication systems ([ITU94]). The first description of the language stems from 1980. Since then, a new language version is presented every four years, with a varying size of differences between subsequent versions. In SDL-88, the basic concepts and model of computation as well as syntax and semantic are fully defined. SDL-92 introduced object oriented design and is the language version currently supported by all commercial SDL-tools and is also the basis of this work. The latest major SDL version is SDL-2000, which aims at a seamless link with object modelling, in particular UML, and an improved use of SDL for implementation.

SDL can be regarded as a profile of the well known UML (Unified Modeling Language) model from the Object Management Group. In some respects it exceeds the UML requirements and has well defined semantics where UML has vaguer "semantic variation points". The class models of SDL follow the usual UML object model notation. The language SDL has a graphical representation (SDL-GR) and an equivalent textual representation (SDL-PR).

Initially, SDL has been developed for the telecommunications domain. It is however well suited to describe event-driven, reactive systems in general, and has increasingly been used in the design of all kinds of embedded systems. Today, there exists an excellent tool support for SDL. It includes support for system modeling, syntax and semantic check, formal verification, simulation, links to testing and implementation in software. Largest vendor is Telelogic AB, Sweden, with its tool SDT. This work used SDT Version 3.1.

### 3.1.2 Language Elements of SDL-92

Like mentioned above, SDL-92 introduces object orientated features. Object orientation is useful for the specification and design process, since objects with similar characteristics can be combined in classes. In SDL-92, object classes are called "types". An actual implementation, however, always consists of instantiated objects, but not of classes. Instances in SDL can be either instantiated types or can be directly described. How these instances were derived is not important from the implementation point of view; particularly if dynamic object creation is not supported, which is assumed in this work. Therefore, without restriction of generality, SDL's object oriented features are not considered for the rest of this work. All language objects, e.g. processes, blocks, signals, are regarded as instances.

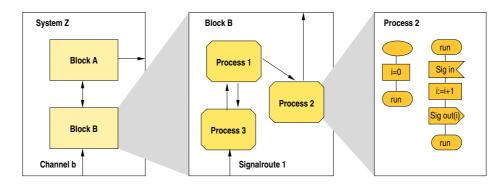

Figure 3.1: Example SDL System Structure

#### 3.1. FUNCTIONAL SPECIFICATION WITH SDL

**Structure** in SDL is expressed with a hierarchy of *blocks* and *processes* (see Figure 3.1). A SDL *system* consists of one or several *blocks*, which can in turn be build of *blocks*. Communicating *blocks* and the *environment* are connected via *channels*. The lowest level of refinement are the parallel SDL *processes*, which can communicate via *signals*<sup>1</sup> over *signal routes*. Each *process* keeps incoming signals in its own private *message queue*.

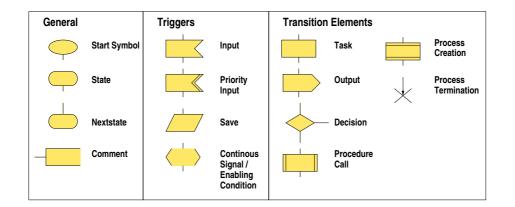

The **Behaviour** of a SDL process is described in form of an extended finite state machine (EFSM), consisting of *states* and *transitions*. Figure 3.2 summarizes the most important elements of the EFSM with their graphical and textual representation.

Figure 3.2: SDL-92 EFSM Elements

The *start symbol* denotes the *initial transition*, which is executed once at the start of the SDL system. It brings the SDL process into a defined state, but can also contain arbitrary transition elements.

SDL knows a number of different *triggers* which can be defined for a transition from a state: The signal *input* triggers the transition upon the arrival of the denoted signal, removing the signal from the message queue. A *continuous signal* triggers when the given boolean expression evaluates true. *Enabling conditions* combine the first two, triggering only when the signal is available and the condition is fulfilled; the signal remains in the queue until this is the case. *Priority inputs* are a special case of the *input* symbol. They define that the given signal is to be consumed first, even if it is not the first in the message queue. The *save*-statement indicates that the given signal has to be kept in the queue, even if it has no transition to trigger in the current state.

<sup>&</sup>lt;sup>1</sup>In cases where a confusion with VHDL signals is possible, SDL signals will exchangeably be termed SDL messages.

The transition body can contain an arbitrary number of *tasks*, *outputs*, *decisions*, *procedure calls*, and the *nextstate*-symbol, to name the most important. A *task* is a container for data operations, which can be expressed formally using arithmetic expressions, but also informal text. The *output*statement sends the given signal to a given process or signal route. Recurring parts of the state machine can be put into a *procedure*, which can be called from anywhere in the process. *Nextstate* defines the state that has to be assumed at the end of the transition. The *process creation* and *termination*symbol specify the dynamic creation and termination of the given process at run time, which is however excluded from the implementation in hardware.

SDL's chief communication mechanism is asynchronous sending and receiving of SDL signals, which can optionally carry data. Generally, data is declared local to each process and cannot be accessed from outside. There are however three exceptions to this rule. *Remote procedures* belong to the context of the exporting process, but can be called from a different process, and therefore can allow access to the remote process's data. The *import*construct allows reading local variables of a remote process, but only values, which have been released with the explicit *export*-statement. These two mechanisms form no principal exception from SDL's basic communication scheme. They can in fact be implemented using signal interchange and additional states. In contrast to this stands the *view/reveal*-mechanism, which allows a process to always read the actual value of the revealed variable of the remote process. The use of view/reveal is not recommended by Z.100.

**Data** types in SDL are abstract data types, i.e. the definition of literals, operators and their semantics is possible in the system specification. There are, however, a few predefined data types for frequently used types like *boolean*, *integer*, *real*, *character*, *charstring*, *time* and *duration*, as well as composite types like *array* and *struct*. With the help of a *syntype*-definition, a new name for an existing data type can be given and, useful with regard towards an implementation in hardware, its range of values can be limited.

SDL assumes a global **Time**, whose actual value is accessible with the *now*-statement. It makes, however, no assumptions on a timely synchronization of actions, nor on communication and execution times. Similarly, the scaling of the predefined *time* and *duration* data types is left as an implementation issue. A *timer* can be started from inside a process transition. After the given duration, it sends a signal to the requesting process, using the process' message queue.

#### 3.1.3 Model of Computation

Blocks in SDL are useful as hierarchical structuring element, and e.g. define the visibility of viewed variables, but they have no influence on the behaviour of the SDL system, which is entirely defined by the processes. SDL processes are defined to be concurrent, i.e. no specific execution order is prescribed. Synchronization and communication take place asynchronously over the SDL signals, with a non-blocking send and blocking receive. Processes are therefore modelled as independent from each other as possible, meaning communication and synchronization must only be realized where it is explicitly demanded by the specification with the statements send, import, view and remote procedure call.

Processes are activated when a transition is triggered. Like outlined in section 3.1.2, the two basic trigger mechanisms are signal input and continuous signals, where a boolean condition is evaluated. The variables contained in such a boolean equation, however, can only be local variables or imported/viewed variables from other processes. To trigger a transition, the values of these variables would have to change, which in turn can only happen inside a triggered transition. This means, that an activation of any part of the SDL system can only be initiated by either a signal from the system's environment or an output from a timer. Signals from the environment, i.e. external events, and timer outputs are subsumed with the expression triggering events of the SDL system. <sup>2</sup>

The detailed model of computation of a single SDL process is as follows: First, the message queue is checked if it contains a signal which has a priority input in the current state, and if true the corresponding transition is executed. Secondly, the first signal in the queue is evaluated. If an input for this signal is specified in the current state, and if applicable the enabling condition evaluates true, the transition is triggered, and the signal is removed from the queue. The signal remains in the queue as long as the enabling condition is false. If there is no input statement for the signal, it is removed from the queue and discarded. In the case of a save-statement, it is kept in the queue. At this point, the next signal in the message queue is regarded. Only if there is no more signals in the queue to be processed, the continuous signals are evaluated.

This execution policy means that the processes' message queue cannot be a simple First-In-First-Out-Buffer (FIFO). In order to realize priority input, save and enabling conditions, it has to be possible to view all buffer elements, and to remove signals from random positions. If these three language

$<sup>^{2}</sup>$ An exception are the so called *spontanous transitions*, which are used to model random behaviour, like e.g. system failures.

elements are excluded, the message queue is reduced to a FIFO. Obviously, this has consequences on the modeling style. Without a save-statement, for instance, it is no longer possible to use the message queue as a buffer for data to be processed later, since the signals are removed from the queue as fast as possible, either to be consumed or discarded.

Returning once again to the classification criteria proposed by Gajski mentioned at the beginning of chapter 2, the specification language SDL is characterized by *control oriented concurrency*. In contrast to data-oriented languages, which describe data streams and their interaction, SDL processes specify concurrency and synchronization of the control structures. SDLs blocks imply a *structural hierarchy*. Since process behaviour cannot be further refined in SDL-92, no behavioural hierarchy is given. *Communication* is mainly realized via *message passing* with the exception of the view/reveal-mechanism which implements a shared memory concept. *Synchronization* is *asynchronous*, in an event-driven fashion using messages (SDL signals).

#### 3.1.4 Discussion

Summarizing the previous sections, SDL is excellently suited for the specification of control-dominated, event-driven systems, whose behaviour can be described in the fashion of a finite state machine. Descriptions in SDL are advantageous for implementation on distributed systems, since a minimum on assumptions is made concerning synchronization and communication between processes. SDL favours an implementation independent specification at an abstract level. It dissociates the functionality from the communication and the interface to the outside, with advantages in reusability and maintainability. Further, already mentioned advantages are its standardizition, maturity, popularity and well developed tool support.

On the other hand, SDL is not intended for an explicit description of data flows, nor for continuous systems. It is possible to create a periodic behaviour with the help of one or several timers, which trigger arithmetic operations inside the finite state machines. Tools like Matlab or MatrixX, however, are certainly better equipped for the design of e.g. a closed loop control. Neither has SDL been envisioned for a detailed description of an implementation or for instance defining an architecture of processing units, busses and software components.

A major weak point in SDL is the concept of time. The language has no provision for a precise specification of timing constraints. Expressing time with the help of SDL timers is, according to [Ols94], only possible in systems where "tolerances on the time intervals are > 100 times the average instruction time of the CPU". The problems arising with the SDL timer concept particularly in software implementations on a single processor are adressed in [Kol01]. Further disadvantages include the lack of a broadcast mechanism and the lack of a behavioural hierarchy inside SDL processes, which can lead to cluttered processes.

## 3.2 Timing Constraints

Reactive systems can be modelled adequately in SDL, where a SDL system is activated by triggering events, i.e. a timer output or an external event from the environment. In reactive real-time systems, this response to an event has to occur within a given time, the *deadline*. In the context of reactive systems, relative, end-to-end deadlines can be assumed. A real-time analysis has to prove that the system under development will meet the given deadlines. To be able to perform such a real-time analysis, the timely behaviour of the environment has to be modelled. It is necessary to have information, e.g. bounds on, the timely distribution of the triggering events, since the reaction time to one event can be influcenced by other events, depending on the time of their occurrence.

In hard real-time systems, where a deadline miss has to be avoided under all circumstances, the *worst case* has to be covered. In this case, the well known methods which have been developed to describe queueing systems ([Kle75]) cannot be applied, since they are based on statistics and therefore only allow statements on e.g. mean values and distribution, but not on the worst case. On the other hand, it is not useful to enumerate all possible points in time of the occurrence of the different events, and it is a severe restriction to stipulate that events may only occur at a few, discrete points in time (e.g. only periodically). The method employed instead is to give *bounds* on the timely distribution of the events. For real-time analysis, as will be seen in chapter 5, the minimum timely distance of events is relevant. A very powerful model to express this is the *event stream model* proposed by Gresser ([Gre93b]), which will be outlined below.

Event stream model The basic information expressed by the event stream model is how many events of a type can occur within a given time interval I, under the assumption that I can be located anywhere in time.

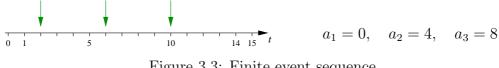

**Definition:**  $a_j$  is the smallest time interval in which j events can occur (3.1)

Figure 3.3: Finite event sequence

Obviously,  $a_1 = 0$  is always given, since one event can occur in one instant. The small example in Figure 3.3 depicts the worst case event sequence consisting of three events that would satisfy  $a_1 = 0, a_2 = 4, a_3 = 8$ . The time in this and in the following examples is given in absolute numbers without measurement unit; it can be multiplied with any time unit. Time values from the set of real numbers are assumed. To find out if any given event sequence complies with  $a_i$ , a window of size  $a_i$  has to be moved along the time axis. At no time, more than j events may show in the window.

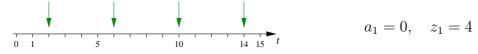

In order to be able to also completely characterize a *infinite* sequence of events, a second parameter, the cycle  $z_i$  is introduced:

**Definition:**

$$a_j + k \cdot z_j$$

is the smallest time interval in which  $(k+1) \cdot j$  events can occur,

$k \in \mathbb{N}_0$  (3.2)

Now, like depicted in Figure 3.4, an event sequence with period 4 can be described with  $a_1 = 0, z_1 = 4$ .

$a_j$  and  $z_j$  together are termed an event tuple:

$$\begin{pmatrix} Cycle \ z_j \\ Interval \ a_j \end{pmatrix}$$

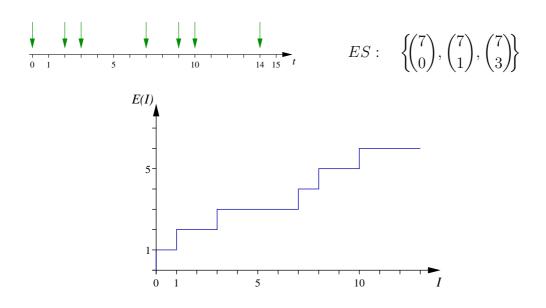

If no cycle can be given,  $z_i = \infty$  is assumed. An event stream is a set of event tuples, whereby the restrictions given by all event tuples have to be equally fulfilled. Now it is possible to concisely describe complex event combinations, e.g. sporadic events, jitter and event groups.

$$ES: \quad \left\{ \begin{pmatrix} z_j \\ a_j \end{pmatrix} \right\} = \left\{ \begin{pmatrix} z_1 \\ a_1 \end{pmatrix}, \begin{pmatrix} z_2 \\ a_2 \end{pmatrix}, \dots, \begin{pmatrix} z_n \\ a_n \end{pmatrix} \right\}$$

(3.3)

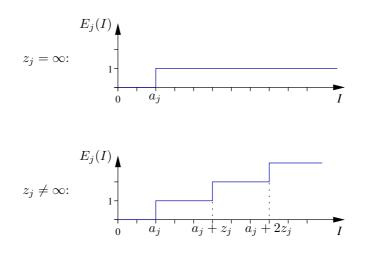

The event function E(I) expresses the constraints given by the event stream in a different fashion: For any given time interval I it gives the maximum number of events which can occur in it, taking into account all event tuples. The contribution  $E_i(I)$  of one event tuple j to the event function is given as:

Figure 3.4: Periodic event sequence

$$E_{j}(I) = \begin{cases} 0 & ; I < a_{j} \\ \left\lfloor \frac{I - a_{j}}{z_{j}} + 1 \right\rfloor & ; I \ge a_{j} \land z_{j} < \infty \\ 1 & ; I \ge a_{j} \land z_{j} = \infty \end{cases}$$

(3.4)

The operator  $\lfloor x \rfloor$  denotes the integer-function, which rounds off its argument to the nearest integer smaller or equal than x. Figure 3.5 shows graphically the contribution  $E_j(I)$  of one event tuple i to the event function.

The event function E(I) of the event stream is the sum of the contributions of all n event tuples:

$$E(I) = \sum_{j=1}^{n} E_j(I) = \sum_{j=1}^{n} \left\{ \begin{bmatrix} 0 & ; I < a_j \\ \left\lfloor \frac{I - a_j}{z_j} + 1 \right\rfloor & ; I \ge a_j \land z_j < \infty \\ 1 & ; I \ge a_j \land z_j = \infty \end{bmatrix} \right.$$

(3.5)

Figure 3.6 depicts an example event stream with one possible event sequence compliant with these restrictions on the left-hand side of the figure. Expressed in words, the event stream poses the following bounds: In a time interval of length 3 never more than 3 events may occur, whereby any time interval of length 1 may contain 2 events at maximum, and only one event may occur at the same time (interval length 0); this can repeat itself after 7 time units. The event function corresponding to the given event stream is drawn on the bottom of the figure.

However, not every combination of event tuples constitutes a valid event stream, in the sense that in contains no internal inconsistencies. Such a inconsistency is given when the minimum interval for a number of events can only be reached by violating the restrictions given by a different event tuple. This is expressed by the following equation, which has to be met for all I to obtain a valid event stream:

$$\forall I_2 > I_1 : E(I_2) - E(I_1) \le E(I_2 - I_1) \tag{3.6}$$

Figure 3.5: Contribution to the event function by one event tuple

**Event dependencies** While event streams describe the temporal characteristic of one event type, event dependencies deal with relations between events of different types. Like before, minimal time distance between events are of interest for a worst case analysis. Therefore, in addition to the event streams, for each group of dependent events a **event dependency matrix EDM** is given:

$$\mathbf{EDM} = \left(\begin{array}{cc} ed_{11} & ed_{12} \\ ed_{21} & ed_{22} \end{array}\right)$$

Each element  $e_{kl}$  of the EAM denotes the minimal temporal distance between an occurrence of k and a subsequent occurrence of l. Obviously,  $ed_{kk}$  is equal to the distance between two events of a type  $a_2$  given by the event stream.

**Summary** The temporal characteristics of the embedding system are specified with deadlines, event streams and event dependencies, which give a lower bound on the timely distance of events. Event streams and deadlines are annotated to the triggering events (external signals and timer outputs), event dependency to the system properties in the SDL system. Keywords and syntax of these annotations are subsumed in Table 3.1. Deadlines, event streams, respectively the derived event functions, and event dependencies are input to the real-time analysis presented in chapter 5.

Figure 3.6: Event stream example

| Real–Time Extensions                        |                            |

|---------------------------------------------|----------------------------|

| #RZA ES{ $(z_1 \ a_1) [, (z_j \ a_j)] * $ } | event stream $ES$          |

| #RZA Deadline $d$                           | deadline $d$               |

| #RZA ED $k \ l \ ed$                        | event dependency $ed_{kl}$ |

Table 3.1: SDL Annotations

## **3.3** Predefined Components

From the point of view of the SDL system, predefined components are functional blocks which are specified in a different language than SDL. The scope of this work does not include general multi-language design like outlined in [JRM<sup>+</sup>99], e.g. a specification given in equal parts in SDL and Matlab. The focus here, with a specific view towards implementation in hardware, is on standard components for which highly optimized designs already exist. An example are peripheral components at the interface to the embedding system like e.g. a PWM module, for which commercial IP versions are available.

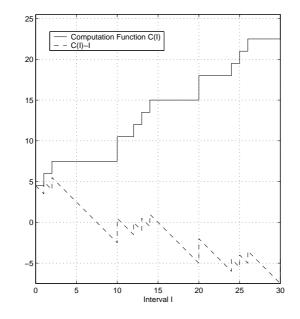

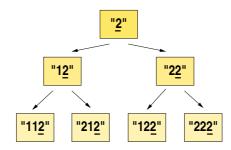

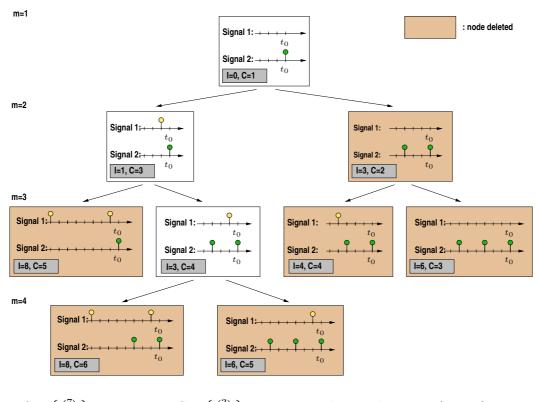

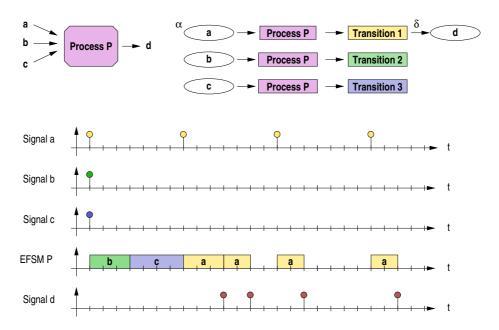

It is possible to explicitly include such a predefined component in the SDL system specification. A SDL block is assigned to represent the predefined component as a black box. In an annotation to SDL, the assignment to the component is fixed. The SDL block can either be left empty; this is allowed in SDL to account for early specification phases. Or it can contain a description of the component's behaviour in SDL, if the component should be included in the simulation at SDL level. The predefined component is linked to the rest of the SDL system using the well known communication methods: When SDL signals are used, the included components actively communicate with the SDL processes via the message queues. With shared variables and remote procedure calls, on the other hand, the component can be accessed from within a SDL process, i.e. in the task bodies of the finite state machine transitions.