Technical University of Munich TUM School of Computation, Information and Technology

# Code Optimization and Generation of Machine Learning and Driver Software for Memory-Constrained Edge Devices

Rafael Christopher Stahl

ii

Technical University of Munich TUM School of Computation, Information and Technology

# Code Optimization and Generation of Machine Learning and Driver Software for Memory-Constrained Edge Devices

Rafael Christopher Stahl

Vollständiger Abdruck der von der TUM School of Computation, Information and Technology der Technischen Universität München zur Erlangung eines

#### Doktors der Ingenieurwissenschaften (Dr.-Ing.)

genehmigten Dissertation.

Vorsitz:

Prof. Dr. Andreas Herkersdorf

Prüfende der Dissertation:

1. Priv.-Doz. Dr. Daniel Mueller-Gritschneder

2. Prof. Andreas Gerstlauer, Ph.D.

Die Dissertation wurde am 20.12.2023 bei der Technischen Universität München eingereicht und durch die TUM School of Computation, Information and Technology am 18.06.2024 angenommen.

iv

# Acknowledgment

First, I would like to thank the German Ministry of Education and Research (BMBF) and the taxpayers for funding my research.

I want to thank Prof. Schlichtmann for providing me with the opportunity to pursue my research at his chair.

A special thanks goes to my colleagues for contributing to the great environment during this time.

My deep and heartfelt gratitude goes to my supervisor, Daniel Müller-Gritschneder. Your constant support, exceptional teaching skills and deep expertise were essential for the completion of this thesis.

Finally, I am grateful to my family, partner and friends for their endless encouragement, patience and love throughout this time.

vi

# Abstract

Compact electronic devices that interact with the physical world, so-called edge devices, are essential for a wide range of applications that advance efficiency, convenience and well-being. Their cost and power consumption must be low because they are deployed in large quantities and often run on batteries. This constrains the available resources on edge devices tightly, especially for memories, which contribute significantly to cost and power consumption. This motivates the need for more research to optimize software that is deployed on microcontrollers, which are the computer chips at the heart of most edge devices.

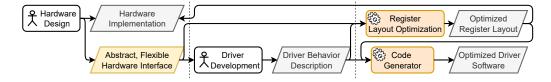

The contributions presented in this thesis focus on the code optimization and code generation for the deployment of machine learning tasks on single and multiple cooperating devices as well as on the generation of device drivers at the interface between hardware and software. Modern compilers have largely exhausted the potential for optimization from the high-level programming language to machine code. Therefore, this work explores the translation from a domain-specific representation to the high-level programming language. Code generation automates, simplifies and generalizes this manual software development process.

In this thesis a novel method to partition neural network layers is developed. It could be used to reduce the memory usage of certain machine learning models by up to 76.2% without introducing significant run time overhead. Additionally, this method was used to improve a distributed machine learning inference flow so that it can fully scale memory usage by incorporating more cooperative devices, while reducing communication demand by up to 28.8% compared to previous methods. Automated optimization of driver code was able to reduce the number of memory accesses by 36%, the estimated run time by 52% and the code size by 22%. viii

# Contents

| 1        | Intr | oduction                                                    | 13 |

|----------|------|-------------------------------------------------------------|----|

|          | 1.1  | Motivation                                                  | 13 |

|          |      | 1.1.1 Machine Learning Inference on MCUs                    | 14 |

|          |      | 1.1.2 Distributed Machine Learning Inference                | 14 |

|          |      | 1.1.3 The Interface Between Hardware and Software           | 14 |

|          | 1.2  | Contribution of this Thesis                                 | 15 |

|          |      | 1.2.1 Fused Tiling for Optimized ML Inference               | 15 |

|          |      | 1.2.2 Optimized Distributed ML Inference                    | 16 |

|          |      | 1.2.3 Automated HW/SW Interface Definition and Optimization | 16 |

|          | 1.3  | Structure of this Thesis and Previous Publications          | 16 |

| <b>2</b> | Bac  | kground                                                     | 19 |

| -        | 2.1  | Microcontrollers                                            | 19 |

|          | 2.2  | Deep Neural Networks                                        | 21 |

|          |      | 2.2.1 Dense Layer                                           | 22 |

|          |      | 2.2.2 Convolutional Neural Networks                         | 23 |

|          | 2.3  | Deep Learning Frameworks                                    | 25 |

|          | 2.4  | Summary                                                     | 27 |

| 3        | Stat | te of the Art                                               | 29 |

| 0        | 3.1  | Deep Learning Inference on Edge Devices                     | 29 |

|          | 3.2  | Fused Tiling                                                | -  |

|          | 0.2  | 3.2.1 Memory-aware Scheduling                               |    |

|          |      | 3.2.2 Memory Layout Planning                                | 33 |

|          | 3.3  | Distributed Inference                                       | 34 |

|          | 3.4  | Driver Software on Edge Devices                             | 35 |

|          | 3.5  | Summary                                                     | 36 |

| 4        | Fus  | ed Tiling for Memory Optimization in DNN Inference          | 37 |

| -        | 4.1  | Introduction                                                |    |

|          | 4.2  | Fused Depthwise Tiling (FDT)                                | 39 |

|          | 4.3  | Automated Tiling Exploration                                | 41 |

|          | 1.0  | 4.3.1 Memory-aware Scheduling                               | 41 |

|          |      | 4.3.2 Memory Layout Planning                                | 44 |

|          |      | 4.3.3 Block-based Path Discovery                            |    |

|                |              | 4.3.4 Automated Graph Transformation                                     | 51         |  |  |  |  |

|----------------|--------------|--------------------------------------------------------------------------|------------|--|--|--|--|

|                |              | 4.3.5 Implementation                                                     | 52         |  |  |  |  |

|                | 4.4          | Experimental Results                                                     | 55         |  |  |  |  |

|                |              | 4.4.1 Automated Tiling Exploration                                       | 55         |  |  |  |  |

|                |              | 4.4.2 Fused Depthwise Tiling                                             | 56         |  |  |  |  |

|                | 4.5          | Summary                                                                  | 57         |  |  |  |  |

| 5              | Opt<br>ence  | imization of Memory and Communication in Distributed DNN Infer-          | 59         |  |  |  |  |

|                | 5.1          | e Motivation                                                             | <b>59</b>  |  |  |  |  |

|                | $5.1 \\ 5.2$ | Contribution                                                             | 59<br>61   |  |  |  |  |

|                | 5.2<br>5.3   | Methods for DNN Partitioning                                             | 61<br>62   |  |  |  |  |

|                | 0.0          | 5.3.1 Baseline                                                           | $62 \\ 62$ |  |  |  |  |

|                |              | 5.3.2 Pipelining                                                         | 63         |  |  |  |  |

|                |              | 5.3.3 Feature Partitioning with FFMT                                     | 64         |  |  |  |  |

|                |              | 5.3.4 Weight Partitioning with FDT                                       | 64         |  |  |  |  |

|                | 5.4          | Optimized DNN Partitioning                                               | 68         |  |  |  |  |

|                | 0.4          | 5.4.1 ILP-based Memory Footprint Minimization                            | 68         |  |  |  |  |

|                |              | 5.4.2 ILP-based Communication Optimization for Weight Partitioned Layers |            |  |  |  |  |

|                | 5.5          | Experimental Results                                                     | 70         |  |  |  |  |

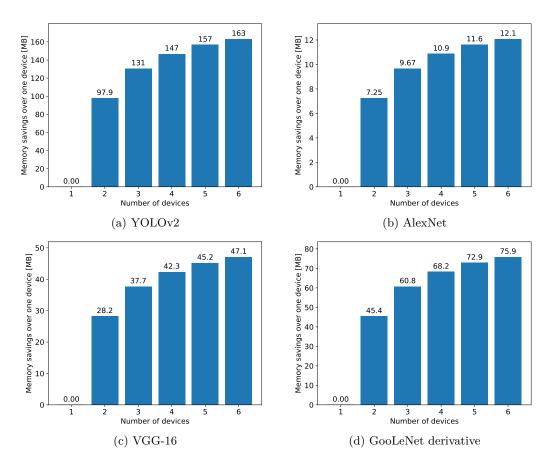

|                | 0.0          | 5.5.1 ILP-based Memory Footprint Minimization                            | 71         |  |  |  |  |

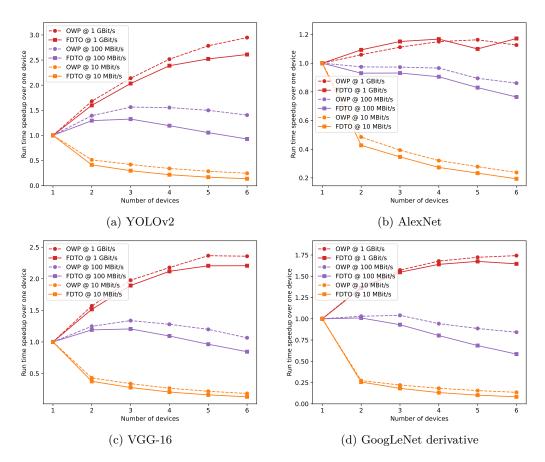

|                |              | 5.5.2 ILP-based Communication Optimization                               | 71         |  |  |  |  |

|                |              | 5.5.3 Evaluation on Raspberry Pi Edge Cluster                            | 72         |  |  |  |  |

|                | 5.6          | Summary                                                                  | 76         |  |  |  |  |

| 6              | Har          | dware/Software Interface Generation and Optimization                     | 77         |  |  |  |  |

|                | 6.1          | Motivation                                                               | 77         |  |  |  |  |

|                | 6.2          | Contribution                                                             | 79         |  |  |  |  |

|                | 6.3          | C Language Extension                                                     | 79         |  |  |  |  |

|                |              | 6.3.1 Bit Field Group Definition                                         | 80         |  |  |  |  |

|                |              | 6.3.2 Hardware Side Effects                                              | 81         |  |  |  |  |

|                |              | 6.3.3 Behavior Description                                               | 83         |  |  |  |  |

|                |              | 6.3.4 Implementation                                                     | 83         |  |  |  |  |

|                | 6.4          | Heuristic Optimization                                                   | 85         |  |  |  |  |

|                |              | 6.4.1 Control-Data-Flow Analysis                                         | 85         |  |  |  |  |

|                |              | 6.4.2 Bit Field Access Conflict Graph (BFACG)                            | 85         |  |  |  |  |

|                |              | 6.4.3 Bit Field Group Simplification                                     |            |  |  |  |  |

|                |              | 6.4.4 Heuristic Algorithm                                                | 87         |  |  |  |  |

|                | 6.5          | Automated Code Generation                                                | 89         |  |  |  |  |

|                | 6.6          | Experimental Results                                                     | 91         |  |  |  |  |

|                | 6.7          | Summary                                                                  | 92         |  |  |  |  |

| 7              | Con          | nclusion and Outlook                                                     | 93         |  |  |  |  |

| Ac             | Acronyms 95  |                                                                          |            |  |  |  |  |

| Bibliography 9 |              |                                                                          |            |  |  |  |  |

| CONTENTS        | xi  |

|-----------------|-----|

| List of Figures | 107 |

| List of Tables  | 109 |

### CONTENTS

# Chapter 1

# Introduction

ICROCONTROLLERS are ubiquitous in the world today and are expected to become even more important in the future. A microcontroller (or MCU for <u>microcontroller</u>  $\mathbf{L}$  unit) is an integrated circuit that contains all the essentials of a programmable computer: memory to store program instructions and working data, at least one processor core that executes instructions, and interfaces to the outside world through peripheral devices. The advantages of MCUs over larger computers are their low size, cost and power consumption. These properties allow to easily embed MCUs into other devices responsible for a raised standard of living, such as medical, industrial, communication, transportation, home and consumer applications [32, 17, 29, 74, 40, 2]. When added to a system that would normally not be programmable, MCUs can improve safety, efficiency, functionality and flexibility. To achieve these improvements, the system requires software, that is, instructions for the MCU to execute. Such software is running in a tightly constrained environment because the available resources in terms of computing capability and amount of memory are extremely limited. The topic of this thesis is the optimization and automated generation of software that is suitable for deployment on resource-constrained devices. Optimization is desired because MCUs are often produced in large quantities and have long lifetimes. Therefore, even small improvements can yield large total savings. While there has been massive research progress since the inception of MCUs and their software, this thesis presents advances of the state-of-the-art in the following specific areas.

- Machine Learning Inference on MCUs

- Distributed Machine Learning Inference

- The Interface between Hardware and Software

## 1.1 Motivation

The following presents the challenges addressed with the approaches presented in this thesis. Solutions are proposed in the subsequent section.

### 1.1.1 Machine Learning Inference on MCUs

Machine learning applications on self-sufficient devices offer superior possibilities over cloud computing approaches in terms of communication demand, latency and data privacy. Such devices have a wide range of computation classes, and it was shown that certain machine learning workloads can be performed even on tiny, low-power microcontroller-type devices. MCUs have become sufficiently capable to run machine learning applications such as keyword spotting, visual wake-up, anomaly detection or radar-based gesture recognition. In these applications, a machine learning model that has previously been trained on a larger machine is deployed and computes a prediction for new input, a process also called *infer*ence. Machine learning inference is heavily constrained by the limited resources on MCUs, which spawned a large field of research known as TinyML or Extreme Edge AI [104, 55]. This thesis will focus on reducing the memory demand of TinyML applications. There are a number of TinyML solutions that tackle this issue by sacrificing some model accuracy to reduce the memory demand, such as quantization, pruning and neural architecture search. Although there also exist methods that are able to reduce memory demand without degrading model accuracy, they may increase inference run time significantly or are limited in their applicability to different types of models.

#### 1.1.2 Distributed Machine Learning Inference

On top of the challenge of limited working memory, the huge number of pre-trained model parameters of modern machine learning models require sufficient storage memory. One possible solution is to run the machine learning inference task in a distributed fashion, where the pre-trained model parameters are partitioned and distributed across multiple devices to reduce the amount of data on each individual device [22, 64, 106]. Furthermore, many deployments of devices already match such a system architecture when they are connected to each other via a local network, for example, a cluster of surveillance cameras. Distributed inference also lends itself to applications in which participating devices are mostly idle because new inputs arrive rarely. Thus, their unused processing power can support the devices that receive the input. The challenges addressed in this thesis are optimal partitioning of the data of the machine learning model and optimization of the communication demand imposed by device cooperation.

#### 1.1.3 The Interface Between Hardware and Software

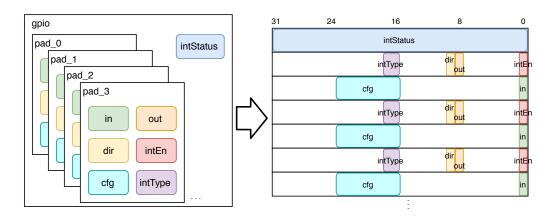

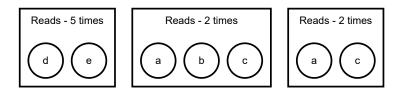

The peripheral devices, or short *peripherals*, of an MCU are its connection to the outside world [75, 60]. Sensors and actuators can be connected to such peripherals through pins. The control of peripherals is enabled by low-level hardware interfaces that are usually implemented as memory-mapped registers. Write accesses to special addresses may induce behavior in the peripheral, and read accesses to them can return data to the processor. The way in which the hardware registers are mapped to memory locations is commonly dictated by what is most convenient for the hardware design. It follows that the software accesses to these memory-mapped registers are not optimized with regard to software metrics, such as code size and the number of necessary accesses. However, since the amount of memory and compute time on MCUs is tightly constrained, it is desirable to optimize the interface between hardware and software. Another important resource in the life cycle of an MCU is the cost of software development. To reduce it, parts of the development flow have to be simplified and automated whenever possible. Instead of being able to focus on just driver behavior, developers are challenged by having to additionally consider the register layout of the peripheral, performance of their accesses and the resulting memory footprint. On top of that, using low-level interfaces directly in driver and application code may pollute the source code with macros and bit manipulation operations, decreasing readability and maintainability. While this can be alleviated by using idioms like a Hardware Abstraction Layer (HAL) that hides low-level code, such layers of abstraction prevent behavior-specific optimization, causing inferior performance and memory footprint [30]. The challenges of optimization and effort of software development are addressed in this thesis by a method for optimized code generation of driver interface software.

### **1.2** Contribution of this Thesis

For all identified challenges, this thesis proposes to solve them using a similar approach. Each problem is first mathematically modeled so that the desired metrics can be optimized. In all cases, the developed methods are implemented within a design automation software tool to demonstrate its applicability and effectiveness in a wide range of test cases.

#### 1.2.1 Fused Tiling for Optimized ML Inference

The inference task for a trained machine learning model can be described as a directed graph with nodes representing high-level operations and edges representing intermediate buffers. If the lifetime of two such buffers do not overlap, their memory storage may overlap, allowing to reduce the overall memory demand. A previously existing method to further reduce the memory demand is *fused tiling*, which will be described in this thesis [4, 106, 24, 13, 67, 68, 57, 25]. Fused tiling is a process in which the size of the intermediate buffers is reduced by calculating them in *tiles*, while also decoupling their lifetimes by *fusing* multiple consecutive operations. A new contribution of this thesis is *Fused Depthwise Tiling* that applies fused tiling in novel ways to enable new tiling opportunities without any run time overheads that would be induced by existing fused tiling methods. These new opportunities come from a wider applicability to more types of operations compared to existing methods that focus solely on convolutions. Combined with existing fused tiling, TinyML memory optimization could be improved significantly by expanding the available design space. To demonstrate the effectiveness of fused tiling and the improvement achieved by the new method, this thesis describes an end-to-end deployment flow that automatically determines where and how to apply fused tiling optimally on any given machine learning model. This flow also requires suitable memory-aware scheduling of operations and memory buffer layout planning. Hence, these two steps are also automated and efficiently implemented to conduct a fast exploration. Optimized tiling opportunities are found quickly through a method called path discovery, which analyzes any given machine learning model and explores possible fused tiling configurations. Expanding the fused tiling design space with Fused Depthwise Tiling improved the average memory reduction of sampled models from 32.8% to 46.3% with an unchanged run time overhead of 12.8%. When targeting performance-aware designs, the overhead could be eliminated while still achieving 28.8% average memory reduction.

#### 1.2.2 Optimized Distributed ML Inference

In distributed machine learning inference, fused tiling also helps reduce the memory demand of each individual device, with the added benefit that tiles can be computed in parallel by all cooperating devices. Additionally, it is possible to apply fused tiling for the reduction of the storage memory required by each device, which is presented first in this work. This thesis describes a process that simultaneously optimizes for computation, memory and communication demands of a distributed deployment. The approach includes joint optimization of computation and the memory demands for both working memory and storage memory by distributing data evenly over all cooperating devices. This allows to run an application in the distributed scenario that would be too demanding for a single device. Furthermore, communication demand is minimized by finding an optimized configuration of the fused tiling. A fully distributed deployment of different machine learning models is demonstrated on a Raspberry Pi cluster to explore trade-offs between run time, memory requirements and communication overhead for different network bandwidths and device counts. For six devices on 100 Mbit/s connections, the integration of fused tiling additionally leads to a reduction of communication demands by up to 28.8%. This results in run time speed-up of the inference task by up to 1.52x compared to partitioning without fusing. Automatic optimization of the partitioning configuration could reduce the memory footprint per device by 25% over a handpicked configuration from previous work.

#### 1.2.3 Automated HW/SW Interface Definition and Optimization

The smallest unit of a peripheral interface is called *bit field*. A bit field is a value that the processor can read or write to interact with the peripheral. Each bit field consists of one or more bits that are accessed atomically, that is, all at once. The first step toward a more optimized interface between hardware and software is the design and definition of a new specification format for the bit fields that enables new opportunities for optimization. An extension for the C programming language is described in this thesis, which allows one to define a flexible hardware/software interface, where the mapping between bit fields and memory addresses is not yet predetermined. This language extension allows developers to focus on desired software behavior using special features such as bit field array and hierarchy, while not having to consider performance implications imposed by the low-level interface. An optimized mapping of the bit fields to a register layout is determined by a heuristic method. Finally, a code analysis and generation approach that takes advantage of this optimized layout is shown. The approach is able to combine accesses to different bit fields to reduce the total number of accesses, and it inserts base pointers systematically to reduce memory usage through code reuse. In simple examples of driver code, the number of memory accesses is reduced by 36%, the estimated run time is reduced by 52% and the driver code size is reduced by 22%. This could be achieved at the cost of an 8.7x larger register map. The complexity of the source code is reduced by 39% when measured by Halstead effort.

### **1.3** Structure of this Thesis and Previous Publications

The remainder of this thesis is organized as follows. Additional background on MCUs and deep neural networks is given in Chapter 2. The state of the art prior to the publications

associated with this thesis is presented in Chapter 3. The description of the technical contributions is split into three chapters that are based on the following previous publications.

The use of fused tiling for memory optimization in deep learning inference is presented in Chapter 4 and is based on: Rafael Stahl, Daniel Müller-Gritschneder and Ulf Schlichtmann: "Fused Depthwise Tiling for Memory Optimization in TinyML Deep Neural Network Inference", in "TinyML Research Symposium 2023" [91]. This conference paper proposes a new tiling method that reduces memory usage without inducing any run time overhead compared to previously existing methods. It improves TinyML memory optimization significantly by reducing memory of models where this was not possible before while additionally providing alternative design points for models that show high run time overhead with existing tiling methods. Furthermore, an automated end-to-end flow with a new path discovery method is proposed that ensures all compared tiling methods are applied optimally for a fair comparison.

In Chapter 5, contributions to distributed deep learning inference on edge devices are discussed. These are based on: Rafael Stahl, Alexander Hoffman, Daniel Müller-Gritschneder, Andreas Gerstlauer and Ulf Schlichtmann: "DeeperThings: Fully Distributed CNN Inference on Resource-Constrained Edge Devices", in "International Journal of Parallel Programming", volume 49, 2021 [89]. This journal paper proposes an approach that supports a full distribution of CNN inference tasks by partitioning commonly used layer types along with a holistic optimization across layers. Memory, computation and communication demand is jointly optimized with techniques that combine both feature and weight partitioning with a communication-aware layer fusion method. The journal paper is an extension of the following conference paper: Rafael Stahl, Zhuoran Zhao, Daniel Müller-Gritschneder, Andreas Gerstlauer and Ulf Schlichtmann: "Fully Distributed Deep Learning Inference on Resource-Constrained Edge Devices", in "Embedded Computer Systems: Architectures, Modeling, and Simulation: 19th International Conference (SAMOS) 2019" [92].

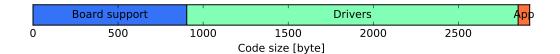

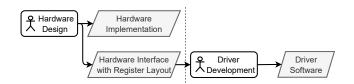

Chapter 6 details the driver generation for optimizing memory-mapped register interfaces and is based on: Rafael Stahl, Daniel Müller-Gritschneder and Ulf Schlichtmann: "Driver Generation for IoT Nodes with Optimization of the Hardware/Software Interface", in "IEEE Embedded Systems Letters", volume 12, no. 2, 2019 [90]. This journal paper proposes a new method to reduce memory size, performance and development effort for device drivers. This is achieved by describing the driver behavior with a new C-like domain-specific language. The layout of the driver register interface is optimized so that register accesses can be combined. The required source code for the driver software is generated in an automated flow.

This thesis is concluded in Chapter 7.

Chapter 1. Introduction

# Chapter 2

# Background

BEFORE going into the details of the existing work and the contributions of this thesis, this chapter covers the foundation and introduces terminology used throughout the remainder of this thesis. Core concepts are the hardware platform of a microcontroller and deep neural networks used in machine learning.

### 2.1 Microcontrollers

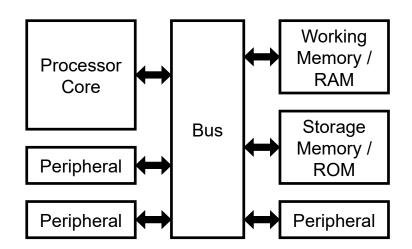

A MicroController Unit (MCU) is a small computer on a single integrated chip [75, 60]. The common components of an MCU are shown in Figure 2.1. All communication between components is facilitated by one or more busses. A program and any static data are stored in storage memory, also called read-only memory (ROM), which is nowadays typically implemented as flash memory. The instructions of a program are read and executed by one or more *processor cores*. A core has a few internal registers for temporary working data, but an MCU also incorporates *working memory* to store larger amounts of data. Working memory is almost always implemented as random-access memory (RAM) - usually SRAM. Also on the bus, although often on a secondary lower-speed bus, are the peripheral devices. Peripherals that are present in almost every MCU are timers, interrupt controllers, input/output pin controllers (General Purpose Input/Output (GPIO)) and converters between analog and digital signals (Analog Digital Converter (ADC), Digital Analog Converter (DAC)). The interface between hardware and software is predominantly implemented through memorymapped registers. This means that the processor core is executing regular memory load or store instructions and the system bus will redirect certain predefined address ranges to peripheral devices instead of the system memories. The smallest logical unit of a peripheral interface is a device parameter that can be read or written by the processor. In this thesis, the device parameters are called *bit fields*. The behavior of the individual bit fields within the memory-mapped registers is defined by the peripheral hardware specification. Typically, an MCU is provided to customers along with device driver code that abstracts this low-level interface to a more intuitive user-oriented one. An additional abstraction layer, called the hardware abstraction layer (HAL), may be introduced to separate driver behavior from lowlevel primitives [30]. Instead of accessing a raw memory address and performing shift and mask arithmetic, a bit field is accessed by its name through a HAL function. Chapter 6

Figure 2.1: Common components of an MCU.

will present contributions toward an optimized hardware/software interface supported by automatic code generation.

The performance of a program running on an MCU is determined by the properties of all the mentioned components. First, the processor frequency limits the speed at which instructions can be executed. Its instruction set architecture dictates how many instructions are required to perform a desired computation. Bus and memory speeds and dynamic congestion activities can also have a great impact on overall performance. Many details of the microarchitecture, such as caches and branch prediction, influence program performance to a great extent as well. The focus of this thesis lies on the memories of an MCU. They limit the size of programs and data that can be stored on the device and are a major factor in the cost and energy consumption of the system because they take up a large portion of the chip area. For example, a popular microcontroller STM32F051R8T6 has been analyzed for its components [71] and the memories occupy more chip area (23%) than the core (22%) or peripherals (21%) with the remaining area dedicated to interconnects and I/O pads. Optimizing the memory usage of an application therefore either reduces cost and energy consumption or allows one to deploy a more advanced functionality that requires more memory.

The size and computation class of MCUs is at the very low end after servers, desktop computers, mobile and embedded devices. Compared to specialized hardware that has its function fixed, MCUs offer the ability to be programmed flexibly because they have a general purpose processor. Specialized hardware also requires a great deal of effort into chip design, while MCUs are available "off-the-shelf". These properties make MCUs a suitable platform for the Internet of Things (IoT) that connects huge amounts of tiny devices for applications such as smart cities, smart homes and industrial automation [8]. The devices in the outer layer of the IoT that interact with the physical world are called *edge devices* or *edge nodes*.

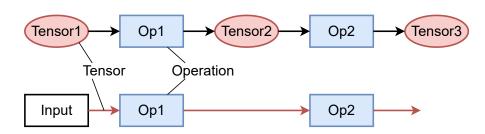

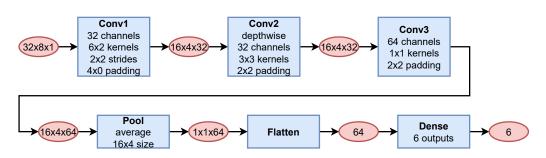

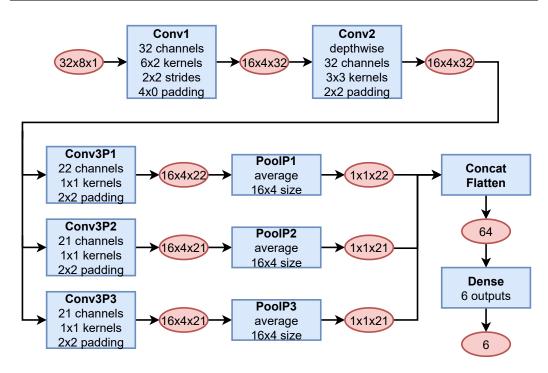

Figure 2.2: Example machine learning model architecture.

### 2.2 Deep Neural Networks

As MCUs became more capable, they could be established as a viable platform even for one of the most demanding application classes of machine learning [14, 95]. Although many machine learning applications run on large server farms or the *cloud*, such a deployment has various disadvantages compared to directly running an application on the device that senses new input and needs to act on it. The additionally required communication limits the bandwidth at which data can be exchanged between a device and its backend, also affecting the economics of a cloud solution. Since the two communication partners are often physically distant and have to communicate over the internet, the connection may have significant latency or be unreliable. Furthermore, the data to be processed must leave the device, raising concerns about privacy. These points motivate the deployment of machine learning applications on the IoT edge or completely off-grid. Terms for such a deployment have only recently been established as TinyML or Extreme Edge AI [104, 55].

A machine learning model is defined primarily by its *model architecture*. It describes which input arguments are accepted by the model, how these arguments are processed by the model computationally, and finally, what outputs are returned by the model. Computations are carried out on entities called *tensors*. Their primary attributes are their dimensionality and data type. While some modern model architectures include tensors of dynamic shape, they are typically not implemented dynamically in TinyML to avoid dynamic memory allocation and the increased complexity of dynamic operators. Instead, a static upper size bound is chosen and any unused data are dropped during inference. An example model architecture is shown in Figure 2.2. The top graph represents tensors as nodes of the graph, in contrast to the alternative notation on the bottom, which represents tensors as the graph edges or special properties of the operation nodes. Both notations are common and will be used in this thesis. The upper one is more clear about the fact that tensors may be reused by multiple successor nodes, while the lower notation is more concise and is more compatible with graph algorithms since there is only one type of node.

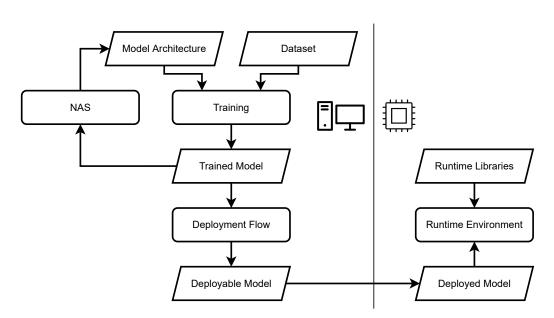

Besides the model architecture, a machine learning model also comprises trained static parameters, called weights and biases, or just *weights*. They are arguments of the operations within the model architecture and are determined by *training* the model. Figure 2.3 shows a generic end-to-end TinyML flow from the dataset and model architecture to the model deployed on a target device. Training takes a dataset and the model architecture and adjusts its weights so that the performance of the model on new unseen input is optimized. Optionally, the model can be refined with neural architecture search (NAS), a process that

Figure 2.3: Generic TinyML flow.

automatically optimizes the model architecture. After the training stage, the model is deployed to its target device, where it can be fed with new input to predict the output values in a process called *inference*.

A model architecture with more than one operation is called a deep neural network (DNN). Since all modern practical machine learning models fulfill this criterion, the term DNN is used as an umbrella term for all neural networks in this thesis.

#### 2.2.1 Dense Layer

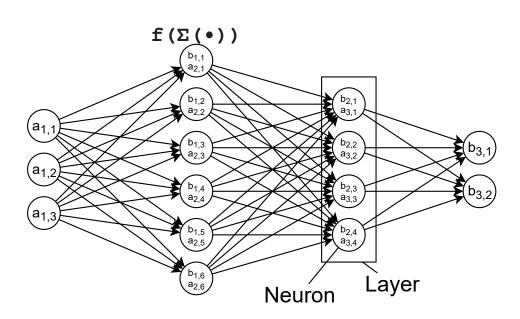

Figure 2.4 shows an example DNN consisting of three *layers*. Layers are equivalent to the operations described above and operate on tensors, which are shown here as individual *neurons*. A layer that connects all input neurons with all output neurons is called *fully-connected* layer or also *dense* layer. Given the number of input neurons  $M_l$  and output neurons  $K_l$  for layer l, the computational operation of a fully-connected layer can be expressed as follows [95].

$$b_{l,k} = f\left(\left(\sum_{m=1}^{M_l} a_{l,m} \cdot w_{l,m,k}\right) + v_{l,k}\right), \quad k \in \{1, \dots, K_l\}$$

(2.1)

$a_{l,m}$  is the *m*-th element of the input neurons vector  $\mathbf{a}_l \in \mathbb{R}^{M_l}$ ,  $b_{l,k}$  is the *k*-th element of the output neurons vector  $\mathbf{b}_l \in \mathbb{R}^{K_l}$ ,  $w_{l,m,k}$  is the *m*, *k*-th element of the weight matrix  $\mathbf{W}_l \in \mathbb{R}^{M_l \times K_l}$ ,  $v_{l,k}$  is the *k*-th element of the bias vector  $v_l \in \mathbb{R}^{K_l}$  and *f* is an *activation function*. An activation function is a nonlinear function that is essential for the operation of a DNN. If there were no activation functions, a DNN would only be able to model linear relationships between inputs and outputs. Common activation functions are sigmoid,

Figure 2.4: Example DNN with three layers.

hyperbolic tangent and rectified linear unit (ReLU), with the latter being most suited in the context of TinyML, because it can be computed quickly and is meaningful for quantized integer types.

Aside from dense layers, any common mathematical operation can be included in a neural network. The addition of bias values was already included in Equation 2.1, but can also be defined as an individual operation that represents element-wise addition. Different combinations of operations and how they are connected to each other define different types of DNN. Widely used ones are the standard feed-forward DNN presented here, auto-encoder networks, recursive neural networks and transformer networks. Almost all modern DNNs are convolutional neural networks, which will be described in more detail in the following section.

### 2.2.2 Convolutional Neural Networks

Convolutional neural networks (CNNs) are of special interest for the contributions of this thesis due to their structure and because they are the most widely used model architecture in popular neural networks [84, 99, 57]. CNNs are motivated by classification tasks that take images as input. Images are represented as three-dimensional tensors for image pixel width, image pixel height and the number of color channels. The third dimension is often named *channels*, or especially for tensors other than the input tensor, *feature maps*. In later layers of a model and in use cases other than image recognition, the channels do not represent colors. Processing such large three-dimensional tensors with fully-connected layers would have extreme computational and memory requirements. This motivates a new type of layer that does not connect all input neurons with all output neurons. This new layer type called

convolutional layer takes advantage of the property of images that their data are spatially correlated. A DNN that contains any type of convolutional operation is also a CNN. A convolutional layer takes three-dimensional tensors as input, which corresponds to a set of feature maps. For example, an initial RGB input image consists of three feature maps, one for each color channel. The operation then applies a set of *filters* to this tensor, and each filter produces a single feature map of the output tensor. A filter consists of multiple two-dimensional *kernels*, one for each input feature map. The filters with their contained kernels are trainable parameters and are also called weights. As such, the computational operation of a convolutional layer can be expressed as follows [95].

$$\mathbf{B}_{l,o} = f\Big(\sum_{c=1}^{C_l} \operatorname{corr}(\mathbf{A}_{l,c}, \mathbf{W}_{l,c,o})\Big), \quad o \in \{1, \dots, O_l\}$$

(2.2)

The matrix  $\mathbf{A}_{l,c}$  is the *c*-th feature map of the input tensor  $\mathbf{A}_l \in \mathbb{R}^{X_l \times Y_l \times C_l}$ , the matrix  $\mathbf{B}_{l,o}$  is the *o*-th feature map of the output tensor  $\mathbf{B}_l \in \mathbb{R}^{X_l \times Y_l \times O_l}$  and the matrix  $\mathbf{W}_{l,c,o}$  is the kernel that connects the *c*-th feature map of the input with the *o*-th feature map of the output. The kernels are contained in the four-dimensional weight tensor  $\mathbf{W}_l \in \mathbb{R}^{U_l \times V_l \times C_l \times O_l}$ , where  $U_l$  and  $V_l$  are the width and height of the kernels, respectively. The activation function is again f. The function  $\operatorname{corr}(\mathbf{A}, \mathbf{W})$  computes the two-dimensional cross-correlation, for which the x, y-th element is computed with the following formula.

$$\operatorname{corr}(\mathbf{A}, \mathbf{W})_{x,y} = \sum_{(u=-\lfloor \frac{U}{2} \rfloor)}^{\lfloor \frac{U}{2} \rfloor} \sum_{(v=-\lfloor \frac{V}{2} \rfloor)}^{\lfloor \frac{V}{2} \rfloor} a_{x+u,y+v} \cdot w_{u,v}$$

(2.3)

Note that there may be additional properties of a convolution that are not considered in these definitions. For example, a stride refers to a step size at which the feature maps are read, and a padding can be defined in different ways that expands the input feature map borders to produce larger output feature maps.

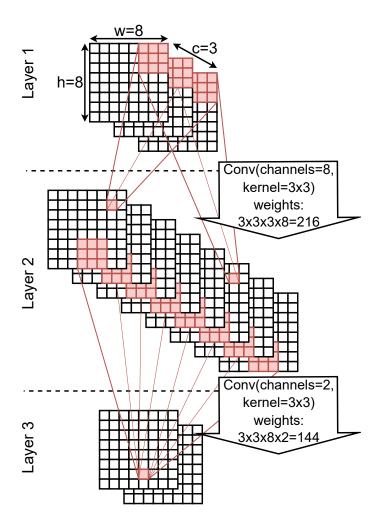

Figure 2.5 shows a CNN consisting of two layers with kernel dimensions  $U_1 = V_1 = U_2 = V_2 = 3$ . The input tensor has dimensions  $\mathbf{A}_1 \in \mathbb{R}^{8 \times 8 \times 3}$  and is processed by the first convolution with  $O_1 = 8$  output channels, resulting in the intermediate tensor  $\mathbf{B}_1, \mathbf{A}_2 \in \mathbb{R}^{8 \times 8 \times 8}$ . The second convolution with  $O_2 = 2$  output channels produces the final output  $\mathbf{B}_2 \in \mathbb{R}^{8 \times 8 \times 2}$ . Note that, as highlighted with a few examples, each output neuron depends on all input neurons at the same x and y coordinates across all input channels, with additional neighboring input neurons being included for kernel dimensions larger than 1x1. A padding of one pixel was added around the input edges in the width and height dimensions of the input to obtain the same feature map dimensions in the output.

Aside from this base case of a convolutional layer, there are many variations. A depthwise convolution refers to a variant that comprises a single filter, of which each kernel produces an individual output feature map instead of summing their results. In pointwise convolution, the kernel sizes are constrained to  $1 \times 1$ , acting as a weighted sum over the channels of each input pixel. The combination of depthwise and pointwise convolution is called depthwise separable convolution and is a common technique to reduce the number of parameters while keeping the neuron dependencies of the standard convolution. Due to their high dimensionality, convolutional operations usually are the most computationally and memory-intensive in many CNNs. Given the focus of resource-constrained MCUs in this thesis, it is important to consider convolutions in any optimization method.

Figure 2.5: Example CNN with two layers.

## 2.3 Deep Learning Frameworks

As DNNs drove advances in many different fields by employing more sophisticated models and larger datasets, the need for software frameworks that support the end-to-end deployment from the source model to the target hardware has increased. Deep learning frameworks let the user define a model architecture and automatically generate optimized executable code for training or inference. The machine learning implementations for the contributions of this thesis use deep learning frameworks to achieve competitive results that are comparable to existing work. Many popular deep learning frameworks like TensorFlow [1], PyTorch [73] and MXNet [19] use an intermediate representation (IR) to implement graph-level optimizations on high-level deep learning operators. These operators are then implemented with target-specific libraries to accelerate them. TensorFlow Lite is a framework specifically targeted at "mobile and edge" devices, providing only a subset of operators and a reduced runtime environment [35]. TensorFlow Lite for Microcontrollers (TFLM) is an even smaller subset that is suitable for MCUs, reducing runtime memory overhead to values below 50 kB [28]. DarkNet is a deep learning framework that stood out because it achieved state-of-the-art results with the YOLO object detection models [78, 80]. For this reason, it was used in the existing work on which the contributions in Chapter 5 are based.

A more advanced approach to model optimization is introduced with machine learning compilers such as Apache TVM [20], Glow [81] and XLA [82]. Instead of treating each operator individually, these tools have a global view of operators that enables crossoperator optimizations like operator fusion and global memory planning. New platforms can be targeted with less engineering effort, because not every operator needs a handwritten implementation. An IR of a machine learning compiler can lower directly to operations that are available for the specific target platform, e.g. matrix/vector multiplications for Accelerators/GPUs or scalar multiplications for simple MCUs.

Apache TVM is used for the implementation of the contributions in Chapter 4 because the presented optimization method requires complex cross-operator transformations and TVM provides the appropriate tooling to implement them. TVM is a state-of-the-art machine learning compiler capable of transforming various input formats of DNN models into various deployable output formats. All the deep learning frameworks mentioned above can provide a DNN model format that is recognized by TVM as input. The compilation flow is divided into two major steps with their respective IRs that are aware of the machine learning domain. First, TVM transforms the input model graphs into the *Relay* IR where graph-level transformations can be applied. Relay has a human-readable representation that is structured as follows.

Functions are defined with the def statement and take a number of runtime parameters and return a return value. Every tensor value is annotated with a Shape that declares the dimensions of that tensor. Arguments named Const represent the weights and biases. Expressions can either be nested (func1(func2(x))) or aliased with a variable name, here %0 - %5. The example code describes a toy function main that takes the 32x32 3-channel image named input\_1 as input and returns a vector of five float values. It first applies a 3x3 convolution (nn.conv2d) with bias addition (add) and ReLU activation (nn.relu), followed by a 2x2 max pooling operation (nn.max\_pool2d) and finally a fully-connected layer (nn.dense) with ReLU activation. After all optimizations have been applied on the Relay level, the model is transformed to the second IR, called *TIR*. TIR is a low-level representation that only acts on the scope of fused operations and is the direct input to various backends that are able to produce output for different deployment scenarios. For example, C code for deployment on microcontrollers or CUDA code for deployment on Nvidia GPUs. TVM was chosen as the basis for the implementation because its Relay IR is very suitable for adding complex transformation passes. To achieve competitive results compared to widely-used frameworks like *TensorFlow Lite for Microcontrollers*, the *Ahead-of-Time (AoT) TVM backend* was chosen for the work presented in Chapter 4 because it generates static code that is able to run the DNN inference without the full TVM run-time libraries. In TVM, many DNN operations are fused to completely eliminate intermediate buffers. For example, a convolution with bias addition and activation function is carried out by adding the bias and applying the activation function while calculating each individual convolution output value. All intermediate buffers between such fused operations do not contribute to the peak memory usage of the deployed model.

### 2.4 Summary

Microcontrollers are integrated circuits with a focus on low price and power consumption, dictated by the chip area, of which a large part is dedicated to memory sizes. These devices are often used to perform smart functionalities, for example in IoT applications. One increasingly popular approach for processing large amounts of data collected by edge devices is machine learning, typically with deep neural networks containing some form of convolutional layer. Deep learning frameworks and compilers are software tools that support the development and deployment of DNN models.

Chapter 2. Background

## Chapter 3

# State of the Art

HIS chapter presents a comprehensive review of the current state of the art to establish a clear baseline for the contributions of this thesis. Existing optimization approaches for memory-constrained devices in the area of deep learning inference and device drivers are reviewed.

### **3.1** Deep Learning Inference on Edge Devices

As already outlined in the Introduction and Background, machine learning is valuable for many applications on constrained devices. DNNs can be fed with large, complex and noisy sensory input data and transform them into an output that is easy to interpret, e.g., a classification result. The focus of this thesis lies on the inference side, assuming that a trained model already exists. DNN inference is demanding in terms of computation, energy and memory resources.

A widely used solution to overcome the limited resources in low-power devices is to offload computation to other infrastructure, such as cloud or fog devices [47, 87]. Although this typically allows for much more powerful models, the input and output data need to be transferred over a network. Transferring raw data requires high bandwidth between the edge device and the cloud backend. The physical distance between the two introduces network latency, which can be a dealbreaker for real-time applications. The network and backend infrastructure add significant cost and reduce the overall reliability of the entire inference solution. Furthermore, the inference input and result may be sensitive data that must not leave the edge device. Due to inferior latency, bandwidth, privacy and cost, there is a strong push to move DNN inference to edge devices with the TinyML paradigm. A load-aware approach presented in [100] focuses on partitioning and distributing parts of a model between different levels of processing power. During inference, the model can stop at an intermediate layer if it has high confidence in a result. Although such a model would execute edge-only for certain inputs, it still carries all the downsides of the full cloud offloading for the others.

Of course, it is challenging to run DNN inference on constrained edge devices, but even demanding applications such as keyword spotting, visual wake-up, anomaly detection and radar gesture recognition were shown to be deployable to tiny MCUs with only a few hundred kilobytes of working memory [12, 102]. One core challenge is the limited RAM available for intermediate storage of run-time buffers. During training of a model, all data are typically represented as 32-bit floating-point values. This level of precision is not necessary for accurate inference, and therefore, various quantization methods have been developed [33, 52, 27]. Today's machine learning frameworks support quantization of all weight and activation data to at least 8-bit integers with low effort. This reduces the model size up to 4x in both ROM and RAM and additionally makes it faster and more efficient to execute. *Post-training quantization* is applied on an already trained model and does not require retraining, while quantization-aware training refers to a process in which the model is quantized during training. Another related model compression technique is pruning [15, 103, 9]. Here, weights that have a negligible impact on the model result are removed completely. On its own, this would result in sparse data structures that introduce a significant performance penalty on general purpose hardware. A more advanced pruning technique is structured pruning, in which whole rows of a dimension are systematically dropped [41, 37]. Quantization and pruning are both effective methods to reduce the size of the deployed model at the cost of some model accuracy. There exist various device-local methods to optimize performance and memory usage on a single device, such as shrinking and compressing the DNN [54, 42, 15, 69]. Applying these methods can reduce the output accuracy, thus no longer making the model a viable solution. As such, there will always be models that are too complex for a single device.

Another approach to bring deep learning inference to constrained devices is the design of model architectures specifically for constrained devices [43]. More generally, NAS is another method that is able to find compromises between the core metrics of memory usage, run time (or power consumption) and accuracy. Given a dataset and a method for evaluating fitness, many different network architectures are systematically searched to find the most suitable one [98, 58, 12]. Often, this will be a multi-objective optimization on the Pareto front across the core metrics. NAS has enormous search spaces, but in the TinyML domain, these become more manageable.

All memory optimization methods mentioned so far have in common that they change DNN parameters and, therefore, the DNN's behavior and inference results. One method to reduce memory usage without changing any DNN behavior is fused tiling, which is the basis for the contributions of Chapter 4 and is discussed in the following section.

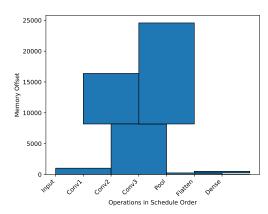

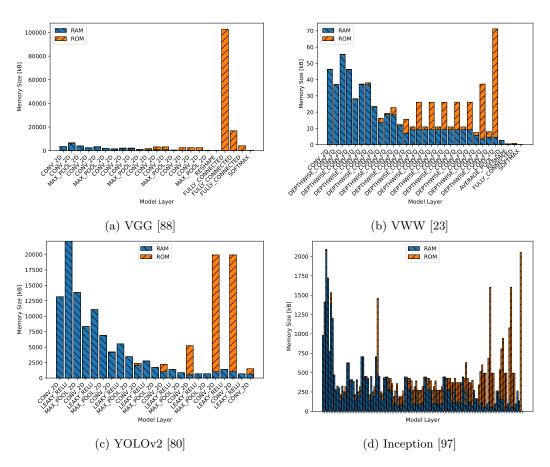

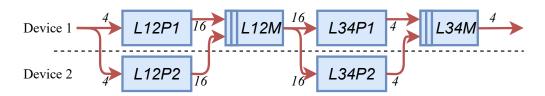

### 3.2 Fused Tiling

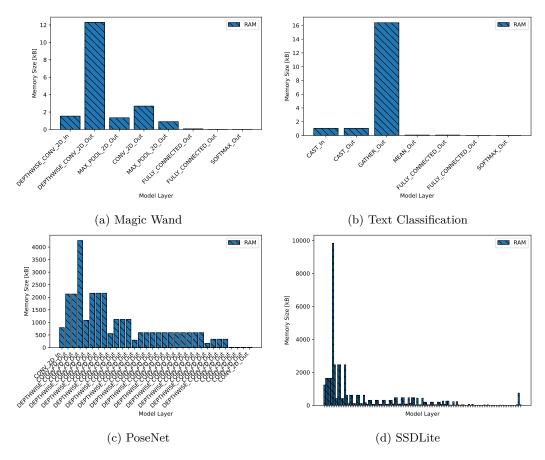

It is observed that many DNNs have an architecture where only a single or very few intermediate buffers dominate the memory requirements of the entire model. Figure 3.1 shows four popular models where this observation can clearly be seen [28, 50, 72, 84].

Fused tiling is a method that reduces the required memory of such large intermediate buffers by changing the order of computation across operators. *Tiling* by itself refers to the splitting of DNN operations into multiple *tiles*, or also called *partitions*, which can then be computed independently of each other. It is used primarily within a single operation to accelerate execution through parallel computation, for example, in processor cores or processing elements of a hardware accelerator [58, 4]. Another application of tiling is the partitioning of DNNs so that they can be run distributed over several devices [106]. This will be discussed in more detail in Section 3.3. *Fusing* by itself refers to the process of

Figure 3.1: RAM usage of DNN intermediate buffers.

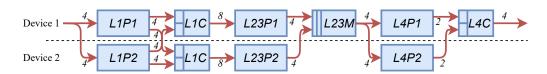

combining multiple operations into a single one that intersperses their low-level operations. For non-tiled operations, this usually refers to the fusion of all element-wise operations that are part of the tensor operations. For example, after a dense layer, it is trivial to fuse the bias addition and activation function into the computation of each output element. *Fused tiling* is the combination of both ideas, where the tiled operations are fused together. Since fusing element-wise operations is trivial, this thesis is particularly concerned with the fusion of multiple commonly used high-level operations, such as dense and convolutional layers. These notably have wider input dependence than element-wise operations, which makes their fusion non-trivial. Fused tiling, as presented in existing literature, will be referred to as Fused Feature Map Tiling (FFMT).

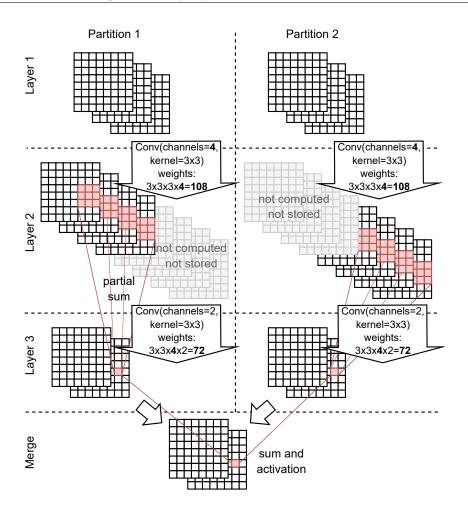

FFMT refers to the fusion of convolutional layers when they are partitioned along their feature maps. Figure 3.2 illustrates FFMT on two consecutive convolutional operations as part of a DNN. The three sets of feature maps are the input of the first operation, an intermediate buffer and the output of the second operation. Since the intermediate buffer is larger than the input and output, calculating it in a tiled manner could reduce the mem-

Figure 3.2: FFMT applied to two consecutive CNN layers.

ory requirements of their computation. FFMT does this by splitting all feature maps of the intermediate tensor buffer into partitions. Convolution operations have spatial locality, which allows one to produce output feature maps from split inputs mostly independently. However, convolution kernels larger than 1x1 cause an *overlap* in the input partitions that accumulates additively over all fused operations. Overlap refers to data that must be calculated by multiple partitions redundantly. More generally, overlap is introduced by an operation if its kernel size is larger than its stride size in the dimension that is partitioned. For example, a convolution with kernel size 6x2 and stride size 2x2 introduces overlap when partitioned along the first dimension, but not when partitioned along the second dimension. The example in Figure 3.2 shows how two operations are split into two partitions and their overlap caused by 3x3 convolutions is highlighted. Since the goal is a reduced working memory usage, the order of operations is important. After calculating the first partition of the large intermediate buffer, the fused second convolution must be executed directly afterward to free the memory usage of the partitioned intermediate buffer. Only then can the second partition of the buffer be calculated. In this way, the large intermediate buffer must never be kept in memory in its entirety. In FFMT there is no inherent limit to the number of consecutive convolutions until the overlap becomes too large to achieve memory savings or the run time overhead becomes impractical. The convolutional operations tiled with FFMT may be interleaved with other operations, such as simple element-wise operations such as bias addition and activation functions. Convolutions are often interleaved with pooling operations, but even these may be part of the partitions as long as their input size does not introduce constraints that are too restrictive. Notably, the partition boundaries must not split the input of a pooling operation or overlap must be introduced.

FFMT is not a new concept introduced in this thesis and is described in more detail in the related literature [4, 106, 24, 13, 67, 68, 57, 25]. FFMT was first employed for reducing peak memory usage in [24], but their path discovery requires partially manual effort from the user. Other works that use FFMT with automated path discovery are [13, 67, 68, 57, 25].

### 3.2.1 Memory-aware Scheduling

For many DNNs, scheduling is trivial because their graphs do not contain any branches. The operation nodes are scheduled in the order in which they are located on the single path of the graph. In other words, there is only a single possible topological sort of the graph. However, with tiling, parallel paths are introduced in the DNN graph and different schedules become possible that determine the lifetime of the intermediate buffers and, hence, peak memory. It then becomes a challenge to find the schedule that minimizes peak memory. Scheduling for optimal run time has been widely studied and has also been applied in the context of machine learning [93]. A simple approach to memory optimization is to iterate all possible topological sorts of the DNN graph [56]. The run time of this enumeration can quickly become unmanageable for more complex DNN graphs. While optimal memory-aware scheduling has been achieved before in [3] using a dynamic programming approach with adaptive canceling, tiled graphs with large number of partitions and many split operations can still quickly cause unmanageable run times. Tiled DNNs resemble series-parallel graphs (SP-graphs), that is, graphs that only consist of series and parallel compositions of other SPgraphs and the base case of a single node. Optimal memory-aware scheduling of SP-graphs has been solved with a polynomial-time algorithm by [48] based on [61].

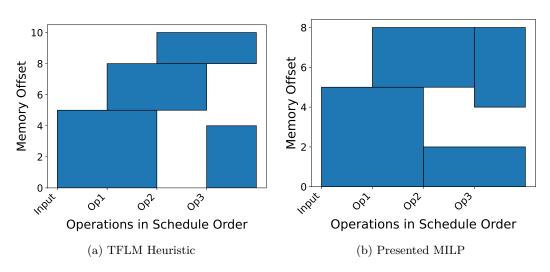

#### 3.2.2 Memory Layout Planning

After a schedule has been determined, all intermediate buffers of the DNN graph have to be mapped to concrete memory locations. Optimizing this mapping for minimal memory usage is a nontrivial task because buffers can overlap in memory, as long as they are not live at the same time. Thus, many buffers can be placed at overlapping memory locations to save total memory space. Determining optimal placement is an NP-complete resource allocation problem. TensorFlow Lite for Microcontrollers (TFLM) employs a greedy heuristic to approximate the optimal solution [77][86][6]. When the buffers are movable between operations, the problem becomes trivial, because they can then be packed as compactly as possible after each operation [56]. But this requires copy operations, which negatively impact performance. The Apache TVM machine learning framework implements a heuristic approach based on hill-climbing and simulated annealing that outperforms the TFLM heuristic in many cases [20].

This thesis contains contributions to methods for scheduling and layout planning for the fused tiling approach presented in Chapter 4.

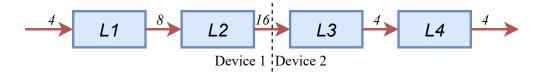

### **3.3** Distributed Inference

For many applications, the overall performance of the system can be greatly improved by distributing more computation to other devices [22]. An orthogonal solution is therefore the utilization of multiple cooperative devices to carry out the DNN inference task in a distributed and cooperative fashion. In many existing applications of edge devices, a large number of them are available and already connected with each other via a local network, for example, a cluster of surveillance cameras. This means that many existing installations already have the required system architecture for performing distributed inference. Another advantage of distributed inference is that, when inputs arrive, most devices are idle, given the low duty cycles of common sensor devices. Thus, a low-cost but efficient solution can be established by utilizing the idle time of other edge devices. Fully distributed inference has previously been achieved by the approach of MoDNN [64]. MoDNN distributes a DNN across multiple mobile phones connected via a wireless network. The approach distributes both the input and output data of the layers, as well as the weight data across devices. While this approach is able to partition weights, it focuses mainly on sparse fully-connected layers, i.e. fully-connected structures, where some weights are zero. The approach does not take the communication between fully-connected layers into account, and weight-intensive convolutional layers are not addressed. Furthermore, the approach proposes to process networks in a layer-by-layer fashion, requiring all devices to synchronize by exchanging data after each layer. Another way to achieve fully distributed inference is layer pipelining [65]. However, this method is unable to evenly distribute the memory demand for typical models.

Model distribution has previously been researched in the context of hardware accelerators. The work in [4] presented such a method, with the central idea of fusing the first few layers of the network to reduce the total transfer of data to and from the chip. In contrast to this thesis, the fusion method in [4] targets memory-constrained accelerators instead of similarly constrained individual edge devices. Fusing optimization for the accelerator is only investigated for the feature-intensive layers, while the fusing approach presented in this thesis additionally targets the weight-intensive layers. Other works on accelerators have focused on aggressive parallelization and do not apply to single/few core devices [7]. Another related topic is the distribution of tasks within a network of collaborative edge devices. Several methods are proposed on how this should be done [83, 18], but these works handle general tasks and focus on the network parameters. In contrast, the work presented in this thesis deals with internals of fully-connected and convolutional operations to remove dependencies between tasks, which would have had to be respected by more general approaches. The use of larger-scale edge devices to share work was explored in [49], but this has the disadvantage that a more powerful device is added to the network along with its additional power requirements.

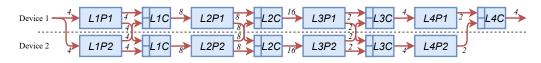

Table 3.1 contrasts the existing work with the work presented in this thesis. Pipelining is a simple method for distributed inference, but it cannot evenly partition the data. FFMT is only capable of partitioning convolutional layers, cannot partition weights, and introduces overhead from overlapping partitions. MoDNN also uses a one-dimensional variant of FFMT

| Work                                  | Layer Types | Able to Split      | Restrictions        |

|---------------------------------------|-------------|--------------------|---------------------|

| Pipelining [65]                       | FC & Conv   | Features & Weights | Uneven partitions   |

| FFMT [4, 106, 24, 13, 67, 68, 57, 25] | Conv        | Features           | Overhead of overlap |

| MoDNN [64]                            | Sparse FC   | Features & Weights | No layer fusion     |

| Chapter 4 [91]                        | FC & Conv   | Features           | -                   |

| Chapter 5 [92, 89]                    | FC & Conv   | Features & Weights | -                   |

Table 3.1: Comparison of Inference Partitioning Methods

to partition feature maps of convolutional layers, but it is additionally capable of splitting the weights of sparse fully connected layers. It does not involve any layer fusion beyond trivial element-wise operations. In Chapter 4, the primary goal of fused tiling is to reduce the required working memory (RAM) for the storage of large intermediate buffers. A novel fused tiling method is introduced to achieve this without the overhead of overlaps. Chapter 5 will demonstrate another application of the novel fused tiling method for distributed inference that reduces static memory usage (ROM).

### 3.4 Driver Software on Edge Devices

The development of driver software for edge devices requires significant engineering effort as part of the product development cost. This has previously been addressed with improved ways of specifying driver behavior. Devil [66] and HAIL [94] are domain specific languages (DSLs) that provide mechanisms to describe the relationships between bit fields in a more granular way. Their description format consists of so-called triggers that define side effects that define how accesses to one field might affect another. HAIL allows one to define logical and sequential dependencies between bit fields and includes a mechanism to access multiple parameters together in a single block. In Devil, the defined register layout has a fixed register layout, which prevents optimization of that layout. For HAIL, the register layout is not specified in the language itself, but must be provided as configuration input. The central issue with these languages is that they are completely new languages that are unfamiliar to driver developers. Laddie [105] is an extension to Devil with the same issue. NDL [26] is a DSL that builds on top of Devil by extending it with a driver state-level function, which is beyond the scope of the work presented here.

On tightly constrained edge devices in the MCU class, driver software can occupy a significant share of the available storage memory. Optimizing the way bit fields are mapped to registers is a possible way to reduce this memory demand. Register layout optimization was investigated in [59]. The work defines costs for the different configurations of bit fields in registers, while also considering combined accesses. The objective function includes the total code size and a performance metric defined as instruction costs weighted by the number of occurrences during profiling. The user needs to choose whether the optimization should focus on code size or performance. The authors define a hardware cost as the total number of registers that are occupied after register allocation. They present an integer linear programming (ILP) formulation which can optimize for either software or hardware cost, but admit that such an ILP cannot be solved in a reasonable amount of time. As a practical solution, they provide two heuristic approaches.

Chapter 6 presents an approach that combines optimization of the register layout with

a novel way to specify driver behavior.

### 3.5 Summary

This chapter provided an overview of the existing work that the contributions of this thesis build upon and extend. Deep learning inference on edge devices has been achieved with cloud offloading, model compression techniques and complex neural architecture search. Fused tiling is a method to reduce peaks in memory usage to reduce the overall memory requirements of DNN inference. Distributed inference is yet another way to reduce memory requirements by sharing the inference work across multiple cooperating devices. Finally, optimized driver software is vital to reduce memory overhead from other sources than the DNN itself.

# Chapter 4

# Fused Tiling for Memory Optimization in DNN Inference

INYML is a field that has recently been enabled by advances in both hardware and software [104]. General hardware improvements and the introduction of specialized hardware accelerators for machine learning operations bridged the gap on one side [46] and on the other, compression techniques, as introduced in the background chapter, closed that gap [95, 99, 27]. Although even training on MCUs is possible [36], this chapter focuses on inference and how it can be optimized effectively, especially in terms of memory demand.

## 4.1 Introduction

Section 3.2 introduced fused tiling and the existing Fused Feature Map Tiling (FFMT) method. Quantization and pruning techniques are orthogonal to fused tiling because tiling can always be applied additionally to such compression techniques. Neural architecture search is also an orthogonal optimization method. It can be applied along with the methods described in this chapter and might even interact symbiotically, because architectures that would have been rejected for their large memory usage could also be considered as candidates. Fused tiling is especially effective for models that have a single or very few intermediate buffers that dominate the memory usage. This chapter explores how fused tiling is applied effectively to reduce memory usage.

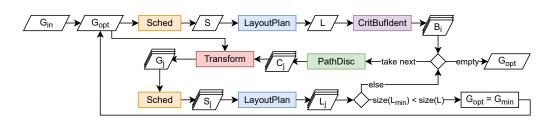

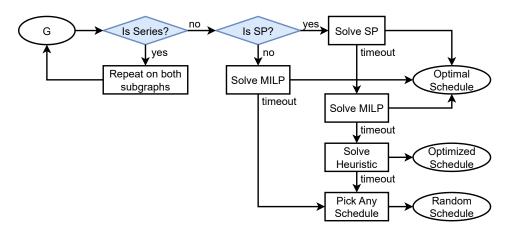

The main contribution of this chapter is the introduction of a so-far unexplored fused tiling method for the memory optimization of DNNs. This method, called Fused Depthwise Tiling (FDT), enables new tiling opportunities that reduce peak memory usage without any run time overhead that would be introduced by existing methods. Additionally, FDT can be applied to a wider variety of layer types than existing methods that focus solely on convolutions. A model can be tiled with existing methods and FDT in conjunction so that the design space for TinyML memory optimization is overall expanded. To explore this expanded tiling design space, an end-to-end deployment flow is described that automatically determines where and how to apply fused tiling optimally on any given DNN. Exploiting tiled graphs for memory reduction additionally requires a suitable memory-aware scheduling

Figure 4.1: Automated tiling exploration flow.

of operations and an optimized mapping from memory buffers to a memory layout. Hence, these two steps are also automated and efficiently implemented to conduct a fast exploration. To quickly find optimized tiling opportunities, a process called path discovery is run that analyzes the DNN graph and explores possible tiling configurations. This thesis is the first work to present FDT and this chapter details its application to memory optimization of DNN inference.

In summary, the contributions are as follows.

- 1. The tiling method FDT applied for the memory optimization of DNNs to expand the design space by reducing memory further or eliminating run time overheads.

- 2. An automated exploration with a new block-based path discovery to find suitable tiling configurations, a memory-aware scheduling and optimal memory layout planning.

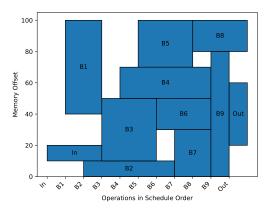

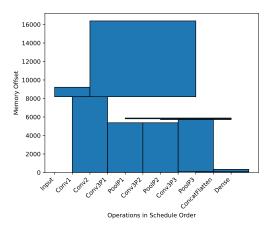

This chapter will describe an optimization flow using both mentioned fused tiling methods to reduce memory usage in DNNs. Figure 4.1 gives an overview of the steps involved in this flow. Firstly, the operations of the given DNN graph  $G_{in}$  are scheduled in a memoryoptimized order S. After the schedule has been fixed, all required intermediate buffers are placed into a linear memory space such that the total required peak memory is minimal. The resulting memory layout L is analyzed to extract a list of intermediate buffer candidates  $B_i$  that may reduce total memory usage if they were to be tiled. These buffer candidates are passed to the *path discovery* in descending order sorted by their size. The path discovery step identifies tiling configuration candidates  $C_j$  for the first buffer candidate. If no configuration could be found that reduces the memory usage, the next buffer candidate is tested. All configuration candidates are passed to the actual graph transformation pass that applies tiling on the DNN graph to produce graph candidates  $G_j$ . These are again evaluated by scheduling and memory layout planning. If the memory size of the smallest found layout  $L_{min}$  is smaller than the current layout L, the corresponding tiling configuration improved memory usage and the currently best graph candidate  $G_{opt}$  is updated. The optimization flow works iteratively. The newly generated tiled DNN graph  $G_{opt}$  is evaluated again as new input beginning with scheduling. The flow terminates when no buffer candidate  $B_i$ produces a tiling configuration that reduces the layout size further. Each step of this flow is described in detail in this chapter.

Figure 4.2: FDT applied to two consecutive dense layers.

# 4.2 Fused Depthwise Tiling (FDT)

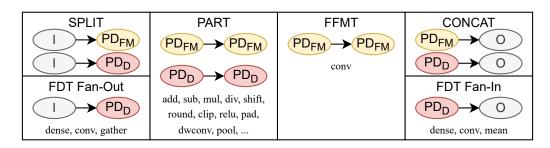

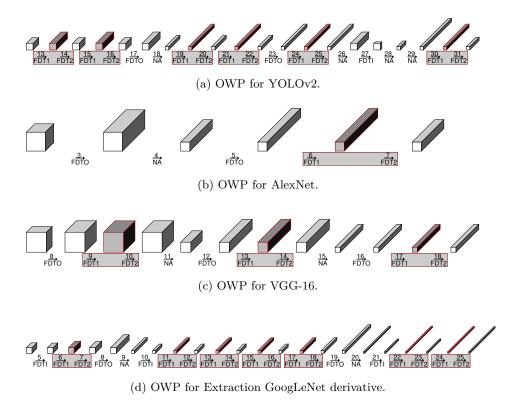

Fused Depthwise Tiling (FDT) is a novel fused tiling method proposed by this thesis. In Chapter 5 it will be applied as a means of partitioning DNN weights of fully-connected layers and convolutional layers that have a large number of weights. This chapter will discuss the application of FDT for the optimization of working memory, i.e. RAM, whereas the work presented later targets the static parameters, i.e. ROM.

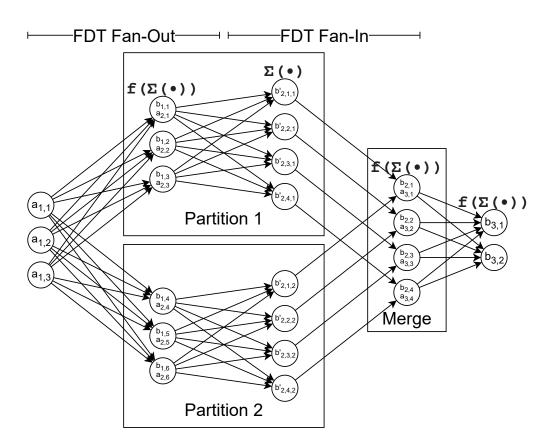

The primary goal of fused tiling for memory optimization is the splitting of large intermediate tensor buffers so that their partitions can be computed independently with reduced memory demand. As shown in Figure 4.3, FDT does this in the depthwise dimension instead of along the feature maps as with FFMT (compare Figure 3.2). Switching to the depthwise dimension avoids any overlap in the intermediate buffer. However, it requires that the input and output buffers are fully available to every partition, because every single output feature map is the result of summing all input feature maps after applying a convolutional filter. Figure 4.2 helps explain this concept with two consecutive dense layers tiled into two partitions. Half of the original six output neurons of the first layer (*FDT Fan-Out*) are computed in each partition using all input neurons. For the second layer (*FDT Fan-In*), the

Figure 4.3: FDT applied to two consecutive CNN layers.

original four output neurons can only be computed partially, because not all input neurons are available to every partition. However, since a dense operation is a sum of products, all partial values of all partitions can be recombined by summing them element-wise and applying the activation function afterwards in a new appended *Merge* operation. Since activation functions are nonlinear, this imposes a limit of two FDT-partitioned operations for each tiled sequence.

Whereas FFMT requires spatial locality of all operations, FDT can be applied to a wider range of operations where all output elements depend on all input elements as long as there is no interdependence between the output elements. Examples of operations that can only be tiled by FDT are dense operations and pairs of embedding lookup (e.g. TensorFlow gather function) and axis reduction (e.g. by taking the mean).

Figure 4.4: Architecture of the running example.

Figure 4.5: Example DNN graph for scheduling.

# 4.3 Automated Tiling Exploration

It is not meaningful to demonstrate the theoretical memory usage of fused tiling methods in isolation, because the practical memory usage is heavily affected by the entire end-toend deployment flow with the interdependent problems of tiling configuration, operation scheduling and layout planning. Each of these problems will be addressed in this section. The flow in which these steps are embedded is already shown in Figure 4.1.

## RUNNING EXAMPLE:

The entire automated tiling exploration flow will be demonstrated on a running example of a simple DNN. Its architecture is a simplified version of the *Key Word Spotting* DNN of MLPerf Tiny [11] and is shown in Figure 4.4. The box-shaped nodes of the graph represent layer operations and the nodes with rounded corners represent the intermediate tensor buffers that store the tensor data. The input tensor represents a two-dimensional spectrogram with length 32 and eight frequency bins. The architecture consists of three convolutional layers with widely varying characteristics, followed by an average pooling layer and a fully-connected layer.

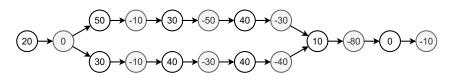

## 4.3.1 Memory-aware Scheduling

Figure 4.5 introduces an example DNN graph with two parallel paths, as might be produced by fused tiling. Although the goal of tiling is to produce evenly sized partitions, this cannot always be achieved due to various constraints of the involved DNN operations. For example, convolutions partitioned by 2x2 tiles using FFMT cause very uneven partitions when their feature map size is small and even more so if they are fused with pooling operations. The example demonstrates that the optimal schedule is not trivial. The optimal schedule first

Figure 4.6: Example DNN graph transformed as task graph.