# TUM School of Computation, Information and Technology DER TECHNISCHEN UNIVERSITÄT MÜNCHEN

Lehrstuhl für Sicherheit in der Informatik

## Virtualization-assisted Dynamic Binary Analysis and Operating System Security

Sergej Proskurin

Dissertation

# TUM School of Computation, Information and Technology DER TECHNISCHEN UNIVERSITÄT MÜNCHEN

## Virtualization-assisted Dynamic Binary Analysis and Operating System Security

#### Sergej Proskurin

Vollständiger Abdruck der von der TUM School of Computation, Information and Technology der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender: Prof. Jens Grossklags, Ph.D.

Prüfer der Dissertation: 1. Prof. Dr. Claudia Eckert

2. Prof. Vasileios P. Kemerlis, Ph.D.

3. Prof. Michalis Polychronakis, Ph.D.

Die Dissertation wurde am 06.04.2022 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 30.08.2022 angenommen.

### **Acknowledgements**

I have stumbled across the fascinating world of virtualization technology very early in the second year of my studies. I remember enjoying my first presentation about microkernels and hypervisors. At the time, even though I was instantaneously intrigued by the call of the concepts, I did not expect this path to take me on such an adventurous journey, which has eventually led to this work. Along the way, I have stumbled across a number of great findings, insightful acquaintances, and inspiring collaborations, which, in the end, have helped me putting the pieces together. For this I am grateful.

This dissertation would not have been possible without constant support and encouragement of many people, to whom I would like to express my gratitude. First and foremost, I would like to thank Prof. Dr. Claudia Eckert for giving me the opportunity to pursue a doctoral degree in virtualization-assisted security and to fulfill my dream of spending time in the United States. Also, I would like to specially thank my supervisors and second advisors at the Stony Brook and Brown University, Prof. Dr. Michalis Polychronakis and Prof. Dr. Vasileios Kemerlis, for your incredible support, inspiration, and guidance. I have greatly enjoyed working with you and debating in our endless discussions. You have been great advisors and have helped me push through, even in the most frustrating hours.

Thank you Prof. Dr. Apostolis Zarras and Prof. Dr. Jens Grossklags. Over the years, both of you have given me a strong and persistent hold, encouragement, and assistance on a professional but also on a personal level. I feel lucky having both of you on my side.

My special gratitude to Dr. Tamas Lengyel, Dr. Sebastian Vogl, and Dr. Jonas Pfoh. Your work has inspired and helped me finding my own way into the world of virtualization.

A huge thanks to all students at the Technical University of Munich, who have assisted me over the years. In particular, I would like to express my gratitude to the virtualization team, comprising Marius Momeu, Christopher Roehmheld, Florian Jakobsmeier, Charlie Groh, and Ulrich Fourier. Without any doubt, you have been a helping hand.

Also, a huge thanks to my dearest colleagues at the Chair for IT Security as well as the Secure Operating Systems department at Fraunhofer AISEC. In particular, I would like to personally thank Steffen Wagner. It was my pleasure working with you.

I would like to thank my family and closest friends for the unconditional love, understanding, and support throughout my entire studies.

Finally, I would like to thank Marina, my dearest and best friend. I wholeheartedly thank you for your patience, your support on so many levels, your wisdom and great advice, your persistent encouragement and believe in my abilities, and for so many more super powers. You have been a rock, my strongest hold, throughout this incredible ride. Thank you.

#### **Abstract**

Virtualization technology has undergone a paradigm shift, in which it has turned its focus from virtualizing servers to assisting the security of operating systems. The technological drive has made virtualization an omnipresent and integral element in the digital world. Most of the modern application processors have added a wide-ranging set of hardware extensions to support system virtualization. The accompanied technological advances and the resulting benefits in regard to resource isolation have inspired researchers to change their perspective on virtualization and to form novel virtualization-assisted techniques for dynamic binary analysis and operating system defenses. Their motivation has helped them to repurpose the virtualization extensions for security. Specifically, they suggested to move security services out of the operating system into an isolated environment guarded by the hypervisor. Over time, virtual machine introspection have evolved and proven effective, even against sophisticated malicious actors; the strong isolation and inspection capabilities of the hypervisor ensure that even compromised virtual machines cannot easily mislead or directly manipulate the security frameworks, which retain an unimpaired view over the virtual machine's binary state. These capabilities have led to a substantial rise in adoption of security-driven virtualization techniques in private and industry sectors leveraging virtualization for *dynamic binary analysis* and *operating system security*.

Disregarding the benefits of virtualization-assisted security frameworks, prior work faces a set of challenges. For instance, a general limitation of virtualization-assisted security frameworks is that they cannot be deployed *on-demand*; they require a compliant hypervisor to be set up in advance underneath the target operating system to implement the necessary foundation. Further, modern virtual machine introspection based frameworks rely on hardware-supported capabilities to dynamically analyze sophisticated malware in a *stealthy* way. While these capabilities have evolved and shown great potential on x86-based, and especially Intel architectures, they lack the necessary foundation for virtual machine introspection to be equally effective on other architectures. For instance, this is one of the reasons why ARM has received insufficient attention with regard to stealthy analysis, despite its breakthrough and increasing acceptance in the server market. Undeniably, the motivation behind moving security services into isolated environments has helped security experts gain improved inspection, resilience, and stealth capabilities with

regard to virtual machine introspection based dynamic analysis of sophisticated malware. Yet, virtualization-assisted operating system security frameworks do not always need to fully outsource their logic and capabilities; this strategy constrains the portability of virtualization-assisted security measures as they rely on the logic integrated into the hypervisor or a security framework operating inside a different virtual machine.

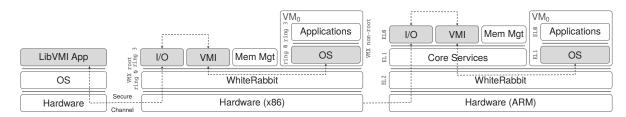

In this work, we explore novel virtualization-assisted techniques to further enhance their capacity with regard to security by addressing the above challenges. Specifically, we position our research around two main pillars, which guide our work towards improving the state-of-the-art virtualization-assisted primitives for *dynamic binary analysis* and *operating system security*. We begin our work by establishing a foundation for both research directions that allows us to deploy arbitrary virtualization-assisted frameworks on-demand. In this context, we address the first of the presented challenges by introducing a thin microkernel-based hypervisor, WhiteRabbit, which we use to dynamically deploy virtualization-assisted primitives. We exemplify a scenario by installing a virtual machine introspection framework underneath a running Linux system, without leaving any inguest artifacts behind. We demonstrate that the virtualization overhead of our prototype can compete with prominent hypervisors and hence presents a viable alternative.

We then turn our attention towards the first pillar, namely improving the state-of-the-art of virtualization-assisted primitives for dynamic binary analysis. Specifically, we develop novel primitives for setting and single-stepping software breakpoints on ARMv7 and ARMv8 application processors—specifically on the AArch32 and AArch64 execution state of the ARMv8 architecture—in a stealthy way. To achieve this, we repurpose the virtualization extensions to overcome the shortcomings of the hardware-intended monitoring mechanisms. We extend the Xen Project hypervisor with the ability to dynamically allocate and switch among different second level address translation tables on ARM to define different views on the guest-physical memory. To the best of our knowledge, we are the first to leverage this capability to hide software breakpoints in the guest's memory on AArch64. By additionally de-synchronizing the TLB-organization, we manage to establish a stealthy solution on AArch32. We demonstrate the effectiveness of our work by equipping the state-of-the-art dynamic binary analysis framework, DRAKVUF, with our primitives, and hence establish the foundation for stealthy dynamic binary analysis on ARM.

By addressing the second pillar of our research, we utilize virtualization to fortify security-critical operating system components. We introduce selective memory protection (xMP) primitives to empower guests with the ability to isolate and protect sensitive data in isolated xMP domains in kernel and user space against data-oriented attacks. We do no longer consider the system's virtualization extensions as components that are available solely to the hypervisor. Instead, we incorporate them as inherent building blocks into the operating system's subsystems, and hence allow them to define custom policies. Thus, we interface the Linux memory management with Xen to define different views on the guest-physical memory, which we repurpose for creating disjoint xMP domains. Combined with Intel's in-guest EPTP switching capabilities, we do not require the virtual machine to interact with the hypervisor to maintain the set of xMP domains, once they have been set

up. By additionally equipping pointers to data inside xMP domains with context-bound HMACs, we manage to obstruct data-oriented attacks. We apply xMP to process credentials and page tables in kernel space, and cryptographic material of selected applications in user space. We show that the xMP primitives entail only a limited overhead and present an effective defense against data-oriented attacks.

Finally, we conclude our research by focusing on the next higher abstraction level of the virtualization technology. Specifically, we enhance the security of modern operating system level virtualization techniques (containers) on Linux. We introduce Jesse, a static analysis based framework for tailoring policies for the Linux Secure Computing (seccomp) mode. Jesse utilizes an abstract interpretation based constant propagation to identify an over-approximated set of system call numbers the binaries in a specific Docker container are authorized to invoke. In addition, we combine Jesse with the state-of-the-art container and library debloating techniques to narrow down only the necessary regions of the libc, which Jesse considers during the analysis. Once we extract the authorized system calls, we compile seccomp policies to restrict access to unnecessary, and potentially vulnerable system calls. Through our prototype, we demonstrate that Jesse is an effective means to thwart existing real-world container escalation exploits.

Overall, through our research, we demonstrate that the potential of virtualization technology has not yet been explored to its full extent with regard to security. Our prototypes reveal that the introduced virtualization-assisted primitives do not only advance the state-of-the-art in dynamic binary analysis, but also open and prospect new horizons of novel operating system security architectures.

### Kurzfassung

Die Virtualisierungstechnologie hat einen Paradigmenwechsel vollzogen, bei dem sie ihren Schwerpunkt von der Servervirtualisierung auf die Unterstützung der Sicherheit von Betriebssystemen verlagert hat. Der technologische Fortschritt hat die Virtualisierung zu einem allgegenwärtigen und integralen Bestandteil der digitalen Welt gemacht. Heute haben die meisten modernen Anwendungsprozessoren eine breit-gefächerte Palette von Hardwareerweiterungen zur Unterstützung der Virtualisierung eingeführt. Die sich daraus ergebenden Vorteile im Hinblick auf die Ressourcenisolierung haben Forscher dazu inspiriert, ihre Perspektive auf die Virtualisierungstechnologie zu ändern, um neue virtualisierungsgestützte Techniken für die dynamische Binäranalyse und den Schutz von Betriebssystemen zu entwickeln. Um dies zu erreichen, haben Forscher die Konzepte der hardwaregestützten Virtualisierungserweiterungen neu interpretiert und für die Systemsicherheit umfunktioniert. Insbesondere schlugen sie vor, Sicherheitsdienste aus dem Betriebssystem in eine isolierte Umgebung zu verlagern, die vom einem Hypervisor bewacht wird. Daraus hat sich im Laufe der Zeit ein neuer Mechanismus entwickelt, der als Introspektion virtueller Maschinen bezeichnet wird. Dieses Verfahren hat sich selbst gegen raffinierte böswillige Akteure als wirksam erwiesen. Die ausgeprägten Fähigkeiten des Hypervisors im Bezug auf die Ressourcenisolierung und Inspizierung stellen sicher, dass selbst kompromittierte virtuelle Maschinen die ausgelagerten Sicherheitsdienste nicht leicht irreführen oder direkt manipulieren können, weil die Sicherheitsdienste trotz einer potenziellen Systemkompromittierung eine unbeeinträchtigte Sicht auf den binären Zustand der virtuellen Maschine beibehalten. Aus diesem Grund haben diese Fähigkeiten zu einem erheblichen Anstieg der Akzeptanz von sicherheitsorientierten Virtualisierungstechniken im privaten sowie im industriellen Sektor für die dynamische Binäranalyse und die Sicherheit von Betriebssystemen beigetragen.

Abgesehen von den Vorteilen, die virtualisierungsgestützte Sicherheitsdienste mit sich bringen, stehen vorherige Forschungsarbeiten vor einer Reihe von Herausforderungen. Beispielsweise besteht eine allgemeine Einschränkung virtualisierungsgestützter Sicherheitsdienste darin, dass sie nicht spontan *auf Abruf* eingesetzt werden können; Sie erfordern einen kompatiblen Hypervisor, der im Voraus eingerichtet werden muss, um die erforderliche Grundlage zu implementieren. Darüber hinaus verlassen sich moderne Dienste, die auf

der Introspektion virtueller Maschinen basieren, auf hardwaregestützte Funktionen, um technisch anspruchsvolle Malware auf *verdeckte Weise* dynamisch zu analysieren. Obwohl sich diese Fähigkeiten mit der Zeit weiterentwickelt und großes Potenzial auf x86-basierten und insbesondere Intel-Architekturen gezeigt haben, fehlt ihnen die notwendige Grundlage, um auf anderen Architekturen gleichermaßen effektiv zu sein. Dies ist zum Beispiel einer der Gründe, warum ARM bisher trotz seines Durchbruchs und der zunehmenden Akzeptanz auf dem Servermarkt nur unzureichende Aufmerksamkeit im Hinblick auf verdeckte Analyse erhalten hat. Die Motivation, Sicherheitsdienste in isolierte Umgebungen zu verlagern, hat Sicherheitsexperten unbestreitbar zu einer verbesserten Inspektion, Widerstandsfähigkeit und Tarnung in Hinsicht auf dynamische Analyse anspruchsvoller Malware verholfen. Allerdings müssen virtualisierungsgestützte Sicherheitsdienste für Betriebssysteme ihre Logik und Fähigkeiten nicht immer vollständig auslagern. Tatsächlich schränkt diese Strategie die Portabilität virtualisierungsgestützter Sicherheitsmaßnahmen ein, weil sich die ausgelagerten Dienste vom eingesetzten Hypervisor abhängig machen.

In dieser Arbeit untersuchen wir neue virtualisierungsgestützte Techniken, um ihre Kapazität im Hinblick auf die Sicherheit weiter zu verbessern. Um dies zu erreichen gehen wir die oben genannten Herausforderungen an. Insbesondere positionieren wir unsere Forschung um zwei Hauptsäulen, die unsere Arbeit stützen, um den Stand der Technik von virtualisierungsgestützten Grundbausteinen für die dynamische Binäranalyse und die Sicherheit von Betriebssystemen zu verbessern. Bevor wir uns jedoch den beiden Säulen widmen, beginnen wir unsere Arbeit, indem wir eine Grundlage für beide Forschungsrichtungen aufstellen. Diese Grundlage erlaubt uns beliebige virtualisierungsgestützte Dienste dynamisch—auf Bedarf—bereitzustellen. In diesem Zusammenhang gehen wir die erste der vorgestellten Herausforderungen an, indem wir einen leichtgewichtigen Mikrokernelbasierten Hypervisor, den wir als WhiteRabbit bezeichnen, vorstellen. Wir verwenden WhiteRabbit, um virtualisierungsgestützte Bausteine dynamisch zur Verfügung zu stellen. Wir veranschaulichen ein Szenario, in dem wir einen Dienst zur Introspektion virtueller Maschinen dynamisch unter einem aktiven Linux-System installieren, ohne jegliche Analyseartefakte im Gastsystem zu hinterlassen. Wir zeigen, dass der virtualisierungsbedingte Mehraufwand unseres Prototyps mit führenden Hypervisor Systemen konkurrieren kann und somit eine realistische Alternative zu heutigen Systemen darstellt.

Anschließend wenden wir uns der ersten Säule zu, die sich damit befasst, den Stand der Technik von virtualisierungsgestützten Bausteinen für die dynamische Binäranalyse zu verbessern. Hierfür untersuchen wir die ARM Architektur, um Defizite zu identifizieren und neuartige Techniken zu entwickeln, die für eine effektive virtualisierungsgestützte dynamische Binäranalyse erforderlich sind. Insbesondere entwickeln wir neuartige Bausteine, die es uns ermöglichen auf ARMv7- und ARMv8-Anwendungsprozessoren—speziell auf der AArch32 beziehungsweise AArch64 Architektur—getarnte Software-Breakpoints zu setzen und zu überspringen. Diese Bausteine bleiben für das Gastsystem verborgen und stellen die Basis für eine getarnte dynamische Binäranalyse dar. Um dies zu erreichen, nutzen wir die Virtualisierungserweiterungen des Systems in einer neuen Weise, die es uns ermöglicht die nicht-vorhandene Hardwareunterstützung in Hinblick auf eine

getarnte Binäranalyse zu ersetzen. Hierfür erweitern wir den Xen-Projekt-Hypervisor um die Fähigkeit, dynamisch verschiedene erweiterte (Second Level) Seitentabellen auf ARM zuzuweisen und zwischen ihnen zu wechseln, um verschiedene Sichten auf den Gastphysischen Speicher zu definieren. Nach unserem besten Wissen, sind wir die ersten, die diese Fähigkeit nutzen, um Software-Breakpoints im Speicher des Gastes auf AArch64 zu verstecken. Indem wir zusätzlich den Assoziativspeicher, also den Translation Lookaside Buffer des Systems de-synchronisieren, gelingt es uns, eine getarnte Lösung auf AArch32 zu etablieren. Wir demonstrieren die Effektivität unserer Arbeit, indem wir den dynamischen Binäranalysedienst DRAKVUF mit unseren Bausteinen ausstatten und somit die Grundlage für eine getarnte dynamische Binäranalyse auf ARM ermöglichen.

Für die zweite Säule unserer Forschung nutzen wir Virtualisierungstechniken, um sicherheitskritische Betriebssystemkomponenten zu härten. Wir stellen Bausteine für die Selective Memory Protection (xMP), also für einen selektiven Speicherschutz vor, die Gastsystemen ermöglichen, sensible Daten in isolierten xMP-Domänen im Benutzeradressraum und im Adressraum des Betriebssystemkerns zu isolieren und vor datenorientierten Angriffen zu schützen. In diesem Zusammenhang betrachten wir die Virtualisierungserweiterungen des Systems nicht mehr als Komponenten, die nur dem Hypervisor allein zur Verfügung stehen. Stattdessen binden wir sie als inhärente Bausteine in die Subsysteme des Betriebssystems ein und erlauben ihnen eigene Regeln zu definieren. So ermöglichen wir eine Schnittstelle zwischen der Linux-Speicherverwaltung und Xen, um verschiedene Sichten auf den Gast-physischen Speicher zu definieren. Wir nutzen die unterschiedlichen Sichten auf den Gast-physischen Speicher, um disjunkte xMP-Domänen zu erstellen. Indem wir zusätzlich Zeiger auf Daten innerhalb von xMP-Domänen mit kontextgebundenen HMACs ausstatten, gelingt es uns, datenorientierte Angriffe zu unterbinden. Wir wenden unsere xMP Implementierung auf Datenstrukturen mit Prozessberechtigungen und Seitentabellen im Adressraums des Betriebssystemkerns und auf kryptographisches Material ausgewählter Anwendungen im Benutzeradressraum an. Schließlich zeigen wir, dass die xMP-Bausteine nur einen begrenzten Rechenmehraufwand verursachen und gleichzeitig eine effektive Verteidigung gegen datenorientierte Angriffe darstellen.

Wir schließen unsere Forschung ab, indem wir uns auf die nächsthöhere Abstraktionsebene der Virtualisierungstechnologie konzentrieren. Insbesondere verbessern wir die Sicherheit moderner Virtualisierungstechniken auf Betriebssystemebene (Container) unter Linux. In diesem Kontext stellen wir Jesse, einen auf statischer Analyse basierender Dienst zur Anpassung von Richtlinien für den Linux Secure Computing (seccomp) Modus, vor. Jesse verwendet eine auf abstrakten Interpretation basierende Konstantenpropagierung, um eine Obermenge von Systemaufruf-Nummern zu identifizieren, die die Programme in einem bestimmten Docker-Container aufrufen dürfen. Darüber hinaus kombinieren wir Jesse mit Container- und Bibliotheks-Debloating-Techniken, um nur die notwendigen Bereiche der 1ibc Bibliothek einzugrenzen, die Jesse während der Analyse berücksichtigt. Sobald wir die autorisierten Systemaufrufe extrahiert haben, kompilieren wir seccomp-Richtlinien, um den Zugriff auf nicht-benötigte und potenziell verwundbare Systemaufrufe einzuschränken. Durch unseren Prototypen demonstrieren wir, dass Jesse in der Lage

ist existierende Container-Eskalations-Exploits in der realen Welt zu verhindern.

Insgesamt zeigen wir durch unsere Forschung, dass das Potenzial der Virtualisierungstechnologie in Bezug auf die Sicherheit noch nicht vollständig ausgeschöpft ist. Unsere Prototypen zeigen, dass die eingeführten virtualisierungsgestützten Bausteine nicht nur den Stand der Technik in der dynamischen Binäranalyse voranbringen, sondern auch neue Horizonte von Betriebssystem-Sicherheitsarchitekturen eröffnen.

## **Contents**

| 1 | Intro | duction                                                  |

|---|-------|----------------------------------------------------------|

|   | 1.1   | Motivation                                               |

|   | 1.2   | Research Questions                                       |

|   | 1.3   | Thesis Statement and Contribution                        |

|   | 1.4   | Publications                                             |

|   | 1.5   | Outline                                                  |

| 2 | Tecl  | nical Background 1                                       |

|   | 2.1   | Virtualization Technology                                |

|   |       | 2.1.1 Process-level Virtualization                       |

|   |       | 2.1.2 OS-level Virtualization                            |

|   |       | 2.1.3 System-level Virtualization                        |

|   | 2.2   | Hardware-assisted Virtualization Extensions              |

|   |       | 2.2.1 Execution Environments                             |

|   |       | 2.2.2 CPU Virtualization                                 |

|   |       | 2.2.3 Memory Virtualization                              |

|   |       | 2.2.4 Device Virtualization                              |

|   | 2.3   | Virtual Machine Introspection                            |

|   |       | 2.3.1 The Scope and Benefits                             |

|   |       | 2.3.2 The Semantic Gap                                   |

|   | 2.4   | Summary                                                  |

| 3 | Sys   | em Architecture 4                                        |

|   | 3.1   | Conceptional Target System                               |

|   | 3.2   | Comprehensive Threat Model                               |

|   | 3.3   | Summary                                                  |

| 4 | On-   | emand Deployment of Virtualization-assisted Frameworks 5 |

|   | 4.1   | Threat Model                                             |

|   | 4.2  | The W   | hiteRabbit VMM                                                                  |

|---|------|---------|---------------------------------------------------------------------------------|

|   |      | 4.2.1   | On-the-Fly Virtualization                                                       |

|   |      | 4.2.2   | Bridging the Semantic Gap                                                       |

|   |      | 4.2.3   | Hiding Techniques                                                               |

|   | 4.3  | Evalua  |                                                                                 |

|   |      | 4.3.1   | System Setup                                                                    |

|   |      | 4.3.2   | Performance                                                                     |

|   |      | 4.3.3   | Effectiveness                                                                   |

|   | 4.4  | Discus  |                                                                                 |

|   |      | 4.4.1   | Countermeasures                                                                 |

|   |      | 4.4.2   | Limitations                                                                     |

|   | 4.5  |         | d Work                                                                          |

|   | 4.6  |         | ary                                                                             |

|   | 1.0  | Samm    | ary                                                                             |

| 5 | Stea | Ithy Mo | onitoring on ARM 73                                                             |

|   | 5.1  | The No  | eed for Alternative Monitoring Primitives on ARM                                |

|   |      | 5.1.1   | Debug Exceptions                                                                |

|   |      | 5.1.2   | Translation Lookaside Buffer                                                    |

|   | 5.2  | Threat  | Model                                                                           |

|   | 5.3  |         | Kernel Monitoring Primitives                                                    |

|   |      | 5.3.1   | Implementing Kernel Tap Points                                                  |

|   |      | 5.3.2   | Novel Single-Stepping Mechanism                                                 |

|   |      | 5.3.3   | Xen altp2m on ARM                                                               |

|   |      | 5.3.4   | Splitting the TLBs                                                              |

|   | 5.4  | Evalua  |                                                                                 |

|   |      | 5.4.1   | System Setup                                                                    |

|   |      | 5.4.2   | DRAKVUF on ARM                                                                  |

|   |      | 5.4.3   | Performance                                                                     |

|   |      | 5.4.4   | Effectiveness                                                                   |

|   | 5.5  | Discus  | sion                                                                            |

|   |      | 5.5.1   | Alternative Tracing Methods                                                     |

|   |      | 5.5.2   | Limitations                                                                     |

|   |      | 5.5.3   | Malicious Abuse of Stealthy Tracing Primitives                                  |

|   | 5.6  | Related | d Work                                                                          |

|   | 5.7  | Summ    | ary                                                                             |

|   |      |         |                                                                                 |

| 6 | Sele | ctive M | emory Protection 10                                                             |

|   | 6.1  | Memo    | ry Partitioning and Isolation Capabilities on Intel $\ldots \ldots \ldots 10^4$ |

|   |      | 6.1.1   | Memory Protection Keys                                                          |

|   |      | 6.1.2   | The Xen altp2m Subsystem                                                        |

|   |      | 6.1.3   | In-Guest EPT Management                                                         |

|   | 6.2  | Throat  | Model 10                                                                        |

|   | 6.3 | Selective Memory Protection Primitives        | 108 |

|---|-----|-----------------------------------------------|-----|

|   |     | 6.3.1 Memory Partitioning through xMP Domains | 108 |

|   |     | 6.3.2 Isolation of xMP Domains                |     |

|   |     | 6.3.3 Context-bound Pointer Integrity         | 111 |

|   | 6.4 | Integrating xMP into Linux                    |     |

|   |     | 6.4.1 Buddy Allocator                         |     |

|   |     | 6.4.2 Slab Allocator                          |     |

|   |     | 6.4.3 Switches across Execution Contexts      | 115 |

|   |     | 6.4.4 User Space API                          | 118 |

|   | 6.5 | Use Cases                                     |     |

|   |     | 6.5.1 Protecting Page Tables                  |     |

|   |     | 6.5.2 Protecting Process Credentials          |     |

|   |     | 6.5.3 Protecting Sensitive Process Data       |     |

|   | 6.6 | Evaluation                                    |     |

|   |     | 6.6.1 System Setup                            |     |

|   |     | 6.6.2 Performance Evaluation                  |     |

|   |     | 6.6.3 Scalability of xMP Domains              | 126 |

|   |     | 6.6.4 Security Evaluation                     |     |

|   | 6.7 | Discussion                                    |     |

|   |     | 6.7.1 Extensions to xMP                       |     |

|   |     | 6.7.2 Limitations                             |     |

|   | 6.8 | Related Work                                  |     |

|   | 6.9 | Summary                                       |     |

|   |     |                                               |     |

| 7 | Enh | incing Security of Linux Containers           | 137 |

|   | 7.1 | Binary Analysis and System Call Filtering     | 140 |

|   |     | 7.1.1 Linux Secure Computing Mode             | 140 |

|   |     | 7.1.2 Abstract Interpretation                 |     |

|   |     | 7.1.3 Applying Abstract Interpretation        | 143 |

|   | 7.2 | Threat Model                                  | 146 |

|   | 7.3 | System Call Number Analysis                   | 147 |

|   |     | 7.3.1 Hypotheses for a Sound Analysis         | 148 |

|   |     | 7.3.2 Control-Flow Graph Construction         | 149 |

|   |     | 7.3.3 System Call Number Identification       | 151 |

|   |     | 7.3.4 Refining seccomp Policies               | 155 |

|   | 7.4 | Use Case: Enhancing Docker Container Security | 157 |

|   |     | 7.4.1 Dissecting Docker Containers            | 157 |

|   |     | 7.4.2 Abstract Interpretation                 | 157 |

|   |     |                                               | 158 |

|   |     | 7.4.4 Withstanding Real-World Exploits        | 159 |

|   | 7.5 | Evaluation                                    | 162 |

|   |     | 7.5.1 Precision and Coverage                  | 162 |

#### Contents

|              |       | 750 December 1 de Maniero             | 1/1 |  |

|--------------|-------|---------------------------------------|-----|--|

|              |       | 7.5.2 Reasons for Incomplete Mappings |     |  |

|              |       | 7.5.3 Impact Evaluation               | 165 |  |

|              | 7.6   | Discussion                            |     |  |

|              |       | 7.6.1 Soundness                       | 168 |  |

|              |       | 7.6.2 Limitations                     | 169 |  |

|              | 7.7   | Related Work                          | 172 |  |

|              | 7.8   | Summary                               | 174 |  |

|              |       | ·                                     |     |  |

| 8            | Con   | clusion                               | 175 |  |

|              | 8.1   | Contribution                          | 176 |  |

|              | 8.2   | Future Research Direction             | 178 |  |

|              | 8.3   | Final Words                           | 181 |  |

| Glossaries   |       |                                       |     |  |

| <b>.</b> .   | oodai |                                       | 183 |  |

| Bibliography |       |                                       |     |  |

## **List of Figures**

| 2.1 | Different perspectives on the machine                                | 17  |

|-----|----------------------------------------------------------------------|-----|

| 2.2 | Process VM runtime                                                   | 18  |

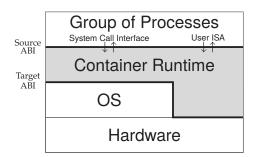

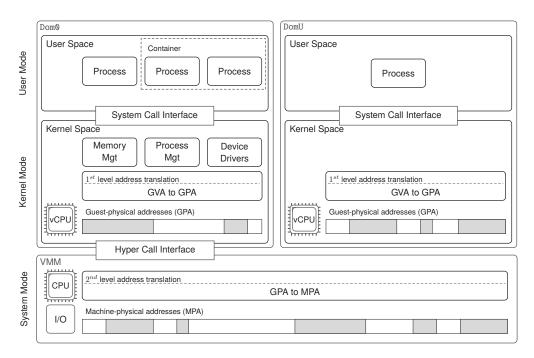

| 2.3 | Container runtime                                                    | 21  |

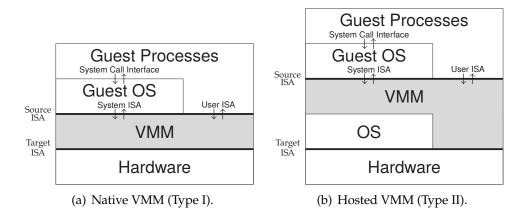

| 2.4 | Native and hosted system VMs                                         | 25  |

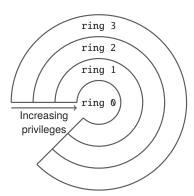

| 2.5 | Privilege hierarchy on the x86 architecture                          | 29  |

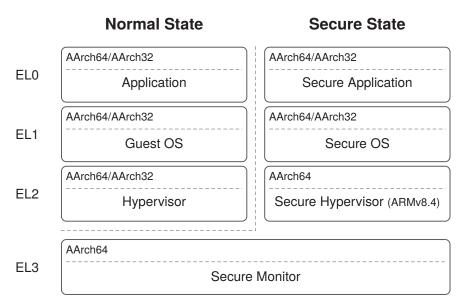

| 2.6 | Privilege hierarchy on the ARMv8 architecture                        | 30  |

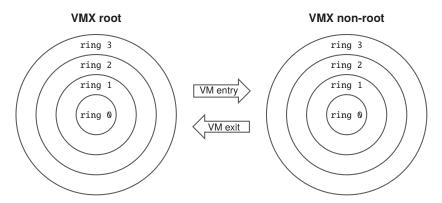

| 2.7 | Privilege hierarchy of the x86 VMX modes                             | 31  |

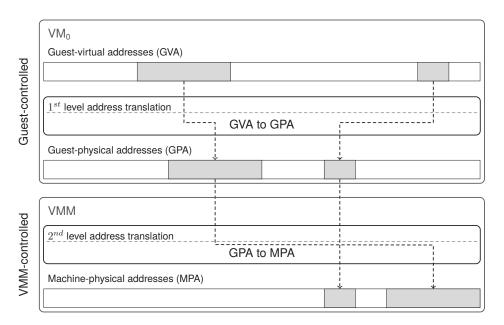

| 2.8 | Virtual memory system architecture                                   | 33  |

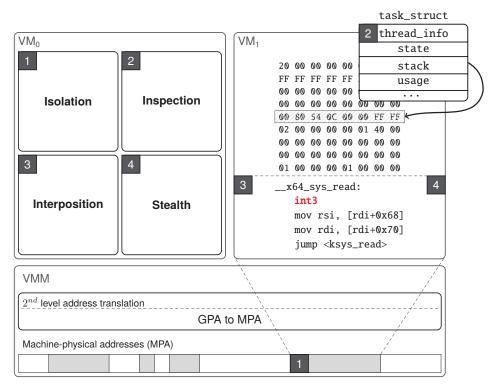

| 2.9 | Capabilities of a VMI-aware VMM                                      | 36  |

| 3.1 | Target system architecture                                           | 46  |

| 4.1 | Architecture of WhiteRabbit                                          | 54  |

| 4.2 | Relocation of WhiteRabbit                                            | 61  |

| 5.1 | Architecture of a VMI-based dynamic binary analysis framework on ARM | 81  |

| 5.2 | Alternative single-stepping mechanism                                | 82  |

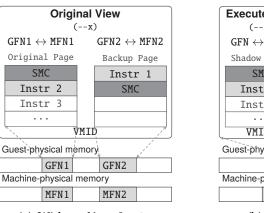

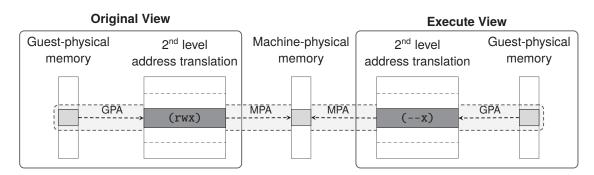

| 5.3 | Views on the guest-physical memory: access permission remapping      | 84  |

| 5.4 | Alternative single-stepping mechanism using split TLBs               | 86  |

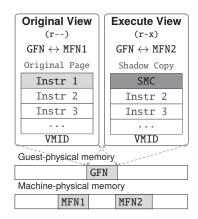

| 5.5 | Views on the guest-physical memory: GFN remapping                    | 87  |

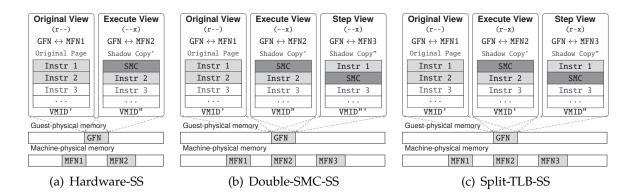

| 5.6 | Alternative single-stepping configurations                           | 90  |

| 6.1 | Selective memory protection domains                                  | 109 |

| 6.2 | xMP memory protection domains                                        | 110 |

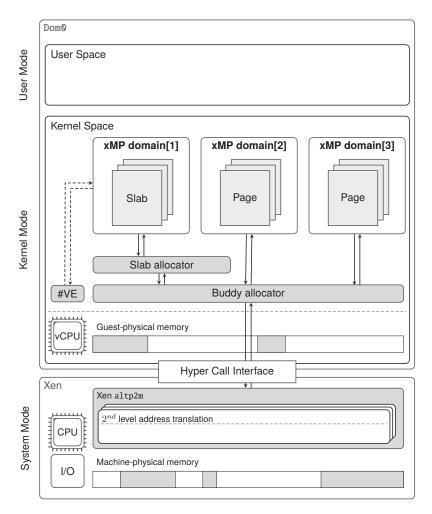

| 6.3 | Integrating xMP into the Linux slab and buddy allocators             | 114 |

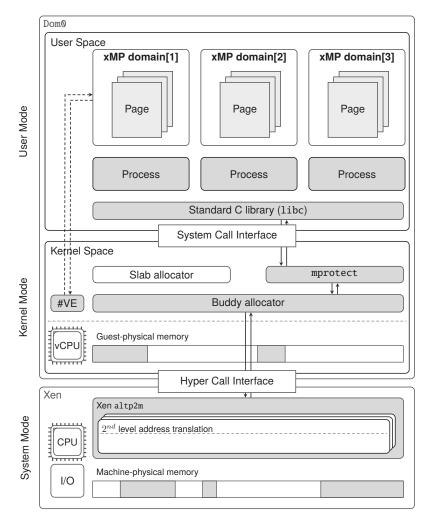

| 6.4 | Integrating xMP into Linux user space                                | 117 |

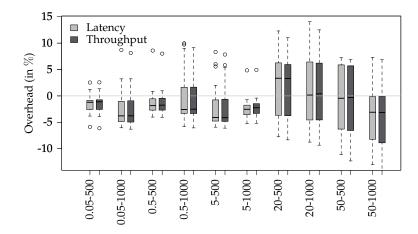

| 6.5 | Performance impact of xMP on Nginx                                   | 126 |

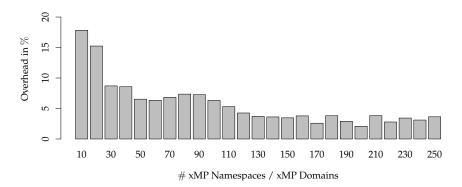

| 6.6 | Scalability of xMP domains                                           | 127 |

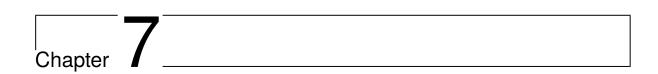

| 7.1 | Abstract interpretation example                                      |     |

| 7.2 | Three phases of the seccomp profile generation process               | 147 |

## **List of Tables**

| 4.1 | Virtualization overhead of WhiteRabbit compared with Xen and Linux KVM | 64  |

|-----|------------------------------------------------------------------------|-----|

| 4.2 | Performance overhead of WhiteRabbit: SPEC CPU2017                      | 64  |

| 4.3 | Performance overhead of WhiteRabbit: LMbench                           | 64  |

| 5.1 | Monitoring overhead of DRAKVUF on ARM: LMbench                         | 91  |

| 5.2 | Monitoring overhead of DRAKVUF on ARM: Phoronix                        | 92  |

| 6.1 | Performance overhead of xMP: LMbench                                   | 124 |

| 6.2 | Performance overhead of xMP: Phoronix                                  | 125 |

| 7.1 | Identified system call numbers in container images                     | 159 |

| 7.2 | Percentage of restricted system calls per container image              | 160 |

| 7.3 | Identified system call numbers in binaries of the Debian image         | 164 |

#### Introduction

Change has never happened this fast before, and it will never be this slow again.

— Graeme Wood

Virtualization technology has come a long way since its origin at IBM in 1960s. At that time, IBM implemented CP-40, the first hypervisor that supported virtual memory and full system virtualization for IBM's System/360 mainframes [Bro09]. The CP-40 hypervisor and, in particular, its successor CP-67 was a turning point for IBM, and since then has inspired future technology and paved the way for virtualization, as we know it today. System virtualization has had its peak in the 1960s and 1970s, yet, in the 1980s and 1990s, the lack of computing power has restrained the development of hypervisors for new architectures [Bro09]. In the past two decades, virtualization has experienced its renaissance. The continual technological advances have gained momentum required to increase the computing power to an extent to which virtualization became attractive; virtualization has improved the utilization and energy consumption of the thriving hardware resources, which were otherwise not exploited to their full capacity. Over time, most of the modern application processor architectures added hardware support for virtualization. In fact, today, virtualization is omnipresent and has become an integral element of our everyday lives. Driven by the concept of abstraction, virtualization techniques are embedded in different architectural levels, with each being responsible to implement an isolated and simplified view on the underlying resources [SN05]. One of the most prominent application scenarios is the modern cloud infrastructure that utilizes virtualization technology to improve the availability and overall resource utilization of physical servers; clustering a high number of virtual machines on a small set of powerful physical machines helps distributing and optimally utilizing the available resources that would otherwise not reach their capacities. At the same time, particularly with regard to the increasing complexity of malware and the rising value of data privacy and integrity, the security demands on such infrastructures exploded. Consequently, the rising demands have strongly influenced the research on operating system (OS) security through virtualization, which drives the main focus of this work. To motivate our work, the following summarizes our main research direction, the entailed challenges that we aim to overcome, and our vision of virtualization-assisted OS security that, we believe, will strongly affect the design of future hypervisor and OS architectures.

#### 1.1 Motivation

Exploiting vulnerabilities has never been as lucrative as it is today. The modern world of digitalization and highly interconnected systems has inspired malicious actors and organizations to form a new business model that utilizes a wide range of malware types, with each type designed to target a particular group of interest. Different malware types are classified into different categories based on the applied infection and execution strategy, volatility, and stealth [Vog15, Rut06a]. Often, the concept of sophisticated and stealthy malware hinges on unauthorized behavior modification of high-privileged and security-sensitive software [Rut06a]. The identification of the malicious behavior is often extremely difficult, yet, vital for providing remedies in form of security patches.

To further complicate the situation, malware authors additionally impede static and dynamic analysis by resorting to obfuscation techniques [UPBSB15, JRWM15]. For instance, run-time packers present one of the most commonly applied obfuscation methods for malware. Packers are responsible—contrary to what the term, packer, implies—for unpacking (i.e., reconstructing) the original malware binary at run-time. This process, e.g., decompresses or decrypts the packed code in memory and can involve an arbitrary number of unpacking layers. Each layer is responsible for unpacking another layer until the original binary has been restored. Sophisticated malware packers involve multiple, potentially encrypted layers of unpacking elements that can be interleaved with code sequences of the packed binary, and even distributed among different processes. Further combined with anti-debugging and integrity validation checks [Rut04, CAM+08, BCK+10, SAM14, BBF<sup>+</sup>16, MANP17], it takes a lot of effort, even for highly skilled reverse engineering experts, to fully comprehend the malicious behavior and intent, and to narrow down the malware's point of entry. Taken into account the time and finances required to detect, analyze, and counteract security breaches renders this an economically unsustainable and almost hopeless situation, without having the right tools at hand.

The growing complexity of modern malware drives security experts to increasingly leverage virtualization technology to assist malware detection and analysis [CN01, GR03, DRSL08, PSE11, GDXJ11, VKSE13, LMP+14, PLM+18]. In fact, almost two decades ago, researchers became aware of the benefits offered by virtualization with respect to security [CN01]. They have suggested to move security applications out of the OS into a high-privileged environment that can be realized through system virtualization. In essence, system virtualization adds a high-privileged software layer, the hypervisor (also known as the virtual machine monitor (VMM)), between the OS and the underlying hardware. The VMM manages system resources and exposes only a narrow virtual hardware interface, the virtual machine (VM), that forms an isolated execution environment for guest OSes. In this way, the VMM bares only a limited attack vector, yet, at the same time, it maintains a

<sup>&</sup>lt;sup>1</sup>Throughout this work, we use the terms *hypervisor* and *VMM* interchangeably to describe the high-privileged virtualizing software layer that implements a virtual hardware interface, beneath which it transparently manages hardware resources on behalf of guest OSes [SN05].

complete and untainted view over the entire VM's binary and register state [PG74, Pfo13].<sup>2</sup>

These properties have inspired researchers to form novel virtualization-assisted techniques for security, which they have coined virtual machine introspection (VMI) [GR03]. VMI assists security experts to analyze and manipulate the state of guest OSes from the outside. The VMM's strong isolation capabilities ensure that even compromised VMs cannot manipulate the virtualization-assisted monitors, which can operate from a different VM or from the VMM itself. More importantly, virtualization lends external monitors an omniscient character and inherently hinders malware inside VMs from deluding the analysis, and thus has become indispensable for malware analysts and reverse engineers.

Over time, VMI techniques have proven effective. In particular the rich variety of hardware-supported virtualization extensions of the x86 architecture—with a strong emphasis on Intel—has given research on VMI the necessary ground for inspiration and progress. Yet, to benefit from these techniques, a VMI-aware VMM must be set up in advance underneath the target system; a constraint for the massive application of VMI. In other words, systems that were not explicitly set up for VMI cannot benefit from these capabilities. Without VMI, to perform memory forensics, reverse engineers would need to resort to complex data-recovery methods to extract memory contents by relying on potentially compromised OS mechanisms. To break through the given constraint, one must call into question the rigid deployment strategy of VMMs. Specifically, if we recall sophisticated virtualization-based rootkits that employ on-the-fly virtualization techniques to subvert OSes [Rut06b, RT07, Zov06], the question arises whether we can adopt similar techniques to deploy thin VMMs to facilitate VMI and other virtualization-assisted frameworks on-demand. Besides, inspired by the ingenuity of attackers, one should investigate the benefits of such on-the-fly deployment strategies and question whether or not other hardware architectures can benefit from similar mechanisms.

Regardless of the VMM deployment strategy, virtualization has helped defenders to gain the upper hand in the never-ending arms race against the malicious actors. In fact, over the past few years, there has been a substantial rise in adoption of virtualization technology in analysis frameworks in both commercial [VMR20, Fir20, Bit20] and open-source applications [PSE11, VKSE13, LMP+14, Lib20, Vol20]. Facing the new challenge, attackers have quickly adapted and equipped malware with anti-virtualization techniques [CAM+08, BCK+10, SAM14, MANP17], which scrutinize the execution environment for artifacts to reveal and evade VMI-based analysis frameworks. This feature has lent malware a split personality that actively avoids revealing its logic to security experts and hence poses a new challenge for reverse engineers. This situation, in turn, has formed a new incentive for VMI researchers to investigate a novel property, namely stealth, that has not received sufficient attention in the past. Even though perfect VM transparency (i.e., the ability of being undistinguishable with real hardware) is infea-

<sup>&</sup>lt;sup>2</sup>We disregard AMD Secure Encrypted Virtualization (SEV), AMD SEV Encrypted State (SEV-ES), and AMD SEV Secure Nested Paging (SEV-SNP) extensions to encrypt the guest's memory (and register state) to make them inaccessible to a benign, yet, potentially vulnerable VMM.

sible in practice [GAWF07], the modern trend towards system consolidation through virtualization renders the goal of VM transparency obsolete. Discrepancies between physical and virtual machines cannot completely hide the presence of a virtual environment [Rut04, CAM+08, Pfo13, SAM14, MANP17, TBZ+18].

At the same time, server virtualization is becoming omnipresent. Thus, a virtualized system does not necessarily indicate that its sole purpose is malware analysis. Therefore, it does not make economic sense for attackers to exclude virtual environments. Nevertheless, malware can still detect VM-based analysis systems, through artifacts, ranging from guest-accessible memory to register contents. Contrary to VM transparency, this highlights the value of the stealth property. Previous research has shown that VMI-based analysis frameworks can achieve a high degree of stealth [PSE11, Pfo13, LMP+14] by means of modern hardware virtualization extensions of the x86 architecture. Contrary to x86, other architectures struggle to foresee hardware capabilities that facilitate, in particular, stealthy VMI. This places a great emphasis on the question of how to conceal VMI-based analysis frameworks on architectures without the necessary hardware support.

One concrete example is given by the ARM architecture. ARM has become the leading processor architecture for mobile, wearable, and Internet of Things (IoT) devices. Through the continuously increasing computing performance and the added hardware support for virtualization, ARM has recently started claiming a bigger slice of the server market pie as well [Ama20, The20b]. As such, it will not be long before malware starts more regularly targeting the ARM architecture. Therefore, the stealthy operation of VMI on ARM is an obligation to successfully analyze and proactively mitigate this growing threat. Stealthy VMI has proven itself perfectly suitable for malware analysis on x86—the dominant player in the virtualization and server industry—, yet, it lacks the foundation required to be equally effective on ARM [PLM+18]. While previous work employs VMI techniques on ARM for security purposes [YY12, GVJ14, TKFC15], it does not emphasize its stealthy nature. Consequently, cloaking analysis frameworks remains an open question and emphasizes the need for novel primitives, which empower stealthy monitoring on ARM.

Until recently, the virtualization extensions of the system's Instruction Set Architecture (ISA) have served the sole purpose of supporting the VMM in managing, isolating, and efficiently distributing the system's hardware resources among different VMs. With VMI, this perspective has changed; virtualization extensions are used to facilitate powerful malware detection and analysis systems. Yet, we claim that the capacity and possibilities provided by virtualization have not yet been explored to their full extent. From this vantage point, we believe that modern OS and VMM architectures require a paradigm shift, in which services of the VMM can become an integral part of the OS. Our vision is to integrate, in particular, the strong memory isolation capabilities of the virtualization extensions into the guest to assist critical elements of the OS. Consequently, in this work, we investigate entirely new ways of repurposing virtualization extensions to define in-guest policies, which are enforced by the underlying VMM. This work further considers ways of supporting the security of OS-level virtualization and ultimately sets the ground for novel in-guest primitives that can form a strong defence in kernel and user space.

#### 1.2 Research Questions

This work intends to investigate and highlight the capabilities of virtualization techniques that have not yet been explored to their full potential with regard to security. Specifically, we approach this high-level goal from two different security perspectives, in which we leverage virtualization for (i) stealthy dynamic binary analysis and (ii) OS security. To accommodate both perspectives, we form the following two main research questions, the answer to which renders the main focus of this work. The first question addresses how to employ virtualization to improve the state-of-the-art foundation for dynamic binary and malware analysis techniques. The second question considers aspects of virtualization that can assist modern OSes in guarding sensitive components against sophisticated attacks. To complement both questions, we take into account the x86 as well as the ARM architecture. Overall, our key research questions can be further subdivided into the following concrete objectives:

(Q1) How can we realize stealthy VMI on the ARM architecture? With ARM becoming one of the most prevalent architectures for mobile, wearable, IoT, and now even in the server market, it presents an attractive target for malicious actors. We have to investigate whether the architectural capabilities of modern ARM virtualization extensions meet the demands of VMI-based malware analysis tools that have proven effective on x86. In particular, the question arises to what extent the ARM architecture can ensure stealthy VMI and what means are necessary to empower it?

(Q2) How can we apply virtualization to enhance the security of OS components? Given the strong memory isolation capabilities of virtualization, the first question that comes into mind is which OS components can benefit from this competence. To answer this question, we must determine and investigate potential hardware-architectural deficits that struggle protecting against certain attack patterns. Assuming there is a need for novel in-guest memory isolation primitives that leverage hardware's virtualization extensions, we have to answer the question which architectural modifications of the modern OSes and VMMs are necessary to empower the OS subsystems with the new capabilities to promote virtualization-assisted security on different software levels.

(Q3) How can we assist OS-level virtualization to enhance its isolation capabilities? The global accessibility and flexibility of modern OS-level virtualization solutions (i.e., containers) has gained popularity. Containers share the OS kernel with the host, yet, unlike system virtualization techniques, they lack strong isolation capabilities. Still, the communitity utilizes containers not only for convenient packaging of services but also for security-critical tasks. At this point, the question one has to answer is whether and how we can enhance the isolation of containers to improve their overall security.

<sup>&</sup>lt;sup>3</sup>Throughout this work, we refer to both x86 and x86-64 as the x86 architecture.

#### 1.3 Thesis Statement and Contribution

Thesis statement: virtualization-assisted security has not yet been explored to its full extent; modern hardware-supported virtualization extensions supply the necessary foundation to (i) establish stealthy primitives for dynamic malware analysis frameworks on ARM architectures (despite their hardware deficits for stealthy monitoring), and (ii) transform the design of modern OS architectures such that they can leverage the strong memory isolation capabilities of the virtualization extensions to enhance the security of its subsystems.

The following summarizes the concrete contributions of this work, which address the identified key research questions and provide a glimpse into the true potential of virtualization technology with regard to security.

We propose a flexible VMM deployment strategy to facilitate on-demand deployment of VMI frameworks and virtualization-assisted security primitives for OS subsystems.

We begin our work by investigating on-the-fly virtualization techniques to overcome the rigid nature of VMM deployment. Specifically, we lay out a minimalistic microkernel-based VMM architecture that leverages on-the-fly virtualization techniques for deployment on x86 and ARM architectures. The main objective of the new VMM architecture is to dynamically and transparently shift a running OS into a virtual environment, an inspiration that we borrow from the Blue Pill rootkit for x86 [Rut06b, RT07]. Yet, as so often in security, we transform the originally malicious intention behind this technology for the benign purpose of equipping virtualization-assisted security-driven frameworks with a flexible deployment strategy; this strategy facilitates periodic, sporadic, as well as permanent—yet retrospective—deployment of only the absolutely necessary virtualization components, avoiding immense, error-prone, and, for many purposes, irrelevant code base of traditional VMMs. Once deployed, our architecture allows to transparently unfold an extensible, microkernel-based architecture underneath the dynamically virtualized OS. In this way, we broaden the capability horizon of the OS, in particular, through strong and fine-grained memory isolation features that are otherwise not available to the OS.

We support our design with a prototype, WhiteRabbit, that dynamically virtualizes a running Linux by leveraging hardware virtualization extensions of the x86 architecture. We highlight that even though our prototype focuses on dynamically and transparently deploying a VMI infrastructure for local and remote VMI frameworks, it can similarly deploy the necessary means required to assist the deployment of functionality that assists in-guest security-relevant subsystems of the dynamically virtualized OS.

*Impact:* By exploring this research direction, we establish a flexible, on-demand deployment strategy that can act as a vehicle for VMI frameworks as well as virtualization-assisted in-guest security subsystems on x86 and ARM. In fact, we can apply this strategy to many techniques that we propose throughout this work. Further use cases include protecting, monitoring, and forensic analysis of managed corporate and IoT infrastructures.

Publication: Parts of this contribution have been published in the paper [PKZ18].

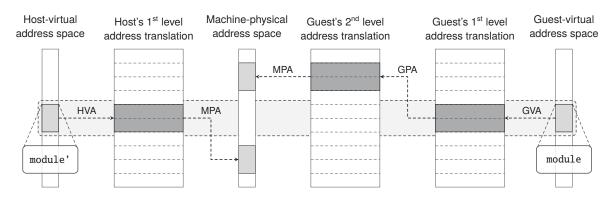

We identify and overcome deficits of the ARMv7 and ARMv8 architectures to facilitate novel primitives for stealthy virtualization-assisted malware analysis on ARM. hardware-supported virtualization extensions on Intel form a solid foundation for stealthy VMI. Inspired by Intel, we define a set of requirements that are necessary to establish stealthy monitoring on the ARM architecture. In this regard, we have identified that, contrary to Intel, the ARMv7 and ARMv8 architectures lack sufficient hardware capabilities required for stealthy VMI. (While ARM generally does not support stealthy single-stepping, its 32-bit execution state, AArch32, in addition, has no notion of execute-only memory pages; every code page has to be readable and executable.) As such, we shift our focus towards exploring and developing new primitives that empower ARM for stealthy malware analysis, despite the spotted architectural shortcomings. To compensate unmet requirements for stealthy monitoring, as a first step, we propose a novel single-stepping primitive, without using the hardware-intended functionality—which by itself can reveal the analysis framework. Further, we equip the Xen project hypervisor with the ability to dynamically allocate and switch among different guest-physical memory views. Specifically, we implement the Xen alternate p2m (altp2m) subsystem for the ARM architecture. This subsystem allows an external monitor to switch among a set of second level address translation (SLAT) tables to enforce different memory access permissions of individual guest-physical page frames per view and remap individual guest frames to different machine frames. That is, instead of switching permissions of individual guest frames in one global view, Xen altp2m allows us to switch among different views—immediately changing the guest's perspective on the guest-physical memory.

Impact: By combining both of the above methodologies, we form the basis for stealthy VMI on AArch64. In addition to that, we tackle the architectural deficit of AArch32 with respect to *execute-only* memory; we utilize the Xen altp2m implementation in a way that allows us to take control of the Translation Lookaside Buffer (TLB) organization on AArch32. By de-synchronizing the TLB organization, we manage to hide instrumented code pages in the guest's memory and realize the foundation for stealthy VMI on AArch32. Finally, we develop and open source the foundation for the binary analysis framework DRAKVUF [LMP+14] and hence establish the means for stealthy dynamic malware analysis on both AArch32 and AArch64.

*Publication:* Parts of this contribution have been published in the paper [PLM<sup>+</sup>18].

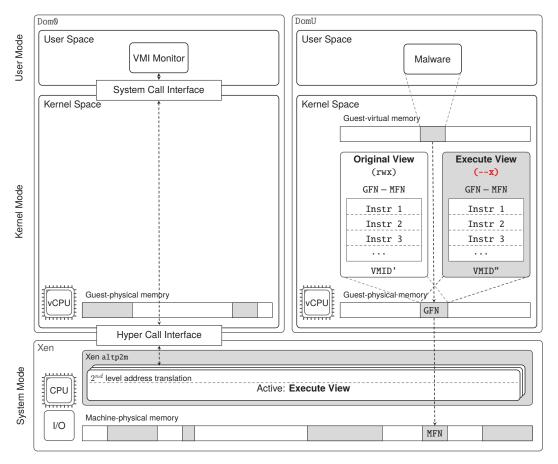

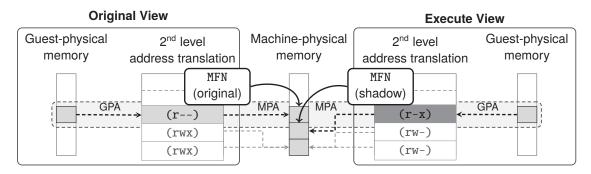

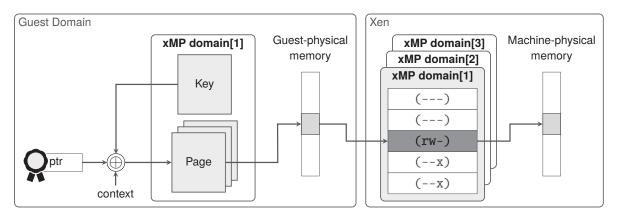

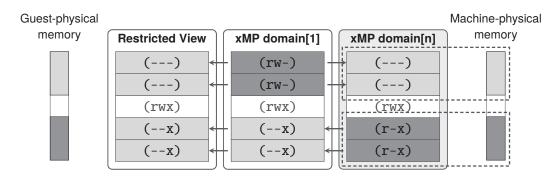

We integrate virtualization capabilities into guest OSes to establish in-guest memory isolation primitives for protecting sensitive data against data-oriented attacks. Having built a solid foundation for stealthy VMI on ARM architectures, we shift the focus of our research on virtualization towards empowering guest OSes with additional capabilities with respect to security. In this regard, we investigate and leverage the unique properties of the modern Intel virtualization extensions to promote Extended Page Table (EPT) management tasks to the guest OS. Combined with the Xen altp2m subsystem, we utilize the Intel EPT pointer (EPTP) switching capability to manage different views on the

guest-physical memory from inside a VM. In this way, we lend the guest the capability to interact with the system's virtualization extensions, without any hypervisor interaction. We extend the memory management system of the Linux kernel to realize *xMP*, an inguest virtualization-assisted *selected memory protection primitive* for guarding sensitive data against data-oriented attacks in both user and kernel space. Specifically, xMP combines Intel's EPTP switching and the Xen altp2m subsystem to control different guest-physical memory views, to isolate sensitive data in disjoint xMP domains. We equip in-kernel management information and pointers to sensitive data in xMP domains with authentication codes, whose integrity is bound to an immutable context to impede data-oriented attacks. In a more concrete application scenario, we apply xMP to guard all page tables and process credentials in the Linux kernel, as well as sensitive data in user-space applications, with only minimal performance overhead. Finally, we integrate xMP into the Linux namespaces framework, and hence form the foundation for virtualization-assisted OS-level virtualization (container) protection against data-oriented attacks.

Impact: This contribution establishes the foundation for *virtualization-assisted security* mechanisms that allow to alleviate the strict separation between an OS and a VMM. The implemented use cases demonstrate the flexibility and power of the introduced concepts by hardening different subsystems of the Linux kernel, user space processes, as well as containers against data-oriented attacks. The virtualization-assisted security primitives are building blocks, which extend the capabilities of the OS to leverage the system's virtualization extensions for security, without having to outsource security-relevant logic into the VMM. In other words, contrary to VMI techniques, any VMM that implements a common Application Programming Interface (API) for virtualization-assisted security can assist in-guest security subsystems in a way that is completely indifferent to the semantic knowledge of the OS.

*Publication:* Parts of this contribution have been published in the paper [PMG<sup>+</sup>20].

We support OS-level virtualization by statically generating last line of defense seccomp policies to limit the number of system calls available to Docker containers. In addition to isolating selected OS resources through xMP namespaces from potentially compromised containers, we introduce Jesse, a static analysis based framework for generating Linux seccomp policies for non-obfuscated binaries in Docker containers. The system call interface of modern OSes offers user space applications access to a high number of system calls. Unfortunately, a vulnerability in one of those system calls can pave the way for attackers to compromise the entire OS kernel. By following the *principle of least privilege*, with Jesse, we aim at granting containers access only to those system calls that are absolutely necessary for their genuine execution. Jesse statically generates policies for the seccomp facility on Linux that has the capability to filter out unused and potentially vulnerable system calls. Specifically, Jesse implements an abstract interpretation based constant propagation for conservatively connecting system calls to identified system call invocations (syscall instructions) in binaries. By additionally applying dead code elimination techniques to

used general-purpose libraries, such as libc, we make sure that the generated system call filters consider only those system calls that are relevant for the container's execution.

*Impact:* Even though the proposed implementation targets ELF binaries in Docker containers compiled for the x86 architecture, its general concepts are independent of the architecture and are similarly applicable to all binaries of the system.

*Publication:* At the time of submission, parts of this contribution have been accepted and are to appear in the paper [GPZ23].

#### 1.4 Publications

Parts of the contributions in this work base upon the following published, scientific, and peer-reviewed articles. Not all parts of our work were published before the date of submission of this thesis. Work that has been submitted for review is stated as such at appropriate locations.

- [PKZ18] Sergej Proskurin, Julian Kirsch, and Apostolis Zarras. Follow the WhiteRabbit: Towards Consolidation of On-the-Fly Virtualization and Virtual Machine Introspection. In IFIP International Conference on ICT Systems Security and Privacy Protection (IFIP SEC), 2018.

- [PLM<sup>+</sup>18] Sergej Proskurin, Tamas Lengyel, Marius Momeu, Claudia Eckert, and Apostolis Zarras. Hiding in the Shadows: Empowering ARM for Stealthy Virtual Machine Inrospection. In *Annual Computer Security Applications Conference (ACSAC)*, 2018.

- [PMG<sup>+</sup>20] Sergej Proskurin, Marius Momeu, Seyedhamed Ghavamnia, Vasileios P. Kemerlis, and Michalis Polychronakis. xMP: Selective Memory Protection for Kernel and User Space. In *IEEE Symposium on Security and Privacy (S&P)*, 2020.

- [GPZ23] Charlie Groh, Sergej Proskurin, Apostolis Zarras. Free Willy: Prune System Calls to Enhance Software Security. To appear in ACM/SIGAPP Symposium on Applied Computing (SAC), 2023.

The following published, scientific, and peer-reviewed articles comprise further contributions that have not been considered in this work.

- [PMK12] Sergej Proskurin, David McMeekin, and Achim Karduck. Smart Camp: Building Scalable and Highly Available IT-Infrastructures. In *IEEE International Conference on Digital Ecosystems and Technologies (DEST)*, 2012.

- [PKE15] Sergej Proskurin, Fatih Kilic, and Claudia Eckert. Retrospective Protection utilizing Binary Rewriting. In *Deutscher IT-Sicherheitskongress*, 2015.

- [PWS15] Sergej Proskurin, Michael Weiss, and Georg Sigl. seTPM: Towards Flexible Trusted Computing on Mobile Devices based on GlobalPlatform Secure Elements. In *International Conference on Smart Card Research and Advanced Applications (CARDIS)*, 2015.

- [MPR<sup>+</sup>21] Mathias Morbitzer, Sergej Proskurin, Martin Radev, Marko Dorfhuber, and Erick Quintanar Salas. SEVerity: Code Injection Attacks Against Encrypted Virtual Machines. In *IEEE Workshop on Offensive Technologies (WOOT)*, 2021.

At the time of submission of this dissertation, the following work remains under review:

Marius Momeu, Fabian Kilger, Christopher Roemheld, Simon Schnückel, Sergej Proskurin, Vasileios P. Kemerlis, and Michalis Polychronakis. Immutable Memory Management Metadata for Commodity Operating System Kernels. *Under review*, 2022.

#### 1.5 Outline

The remainder of this work is organized as follows. In Chap. 2, we summarize the foundations regarding virtualization technology to assist the reader in better understanding the course and details of our work. In this chapter, we outline relevant components of the hardware virtualization extensions, and conclude with a discussion about the benefits and challenges of VMI. We then proceed with Chap. 3, in which we put the perspective of our research directions and the individual objectives into a concrete frame. In this regard, we introduce a conceptual, hardware-independent target system architecture that allows us establish a bird's eye perspective upon the overall picture of the contributions of this work. We further present a comprehensive, and generic threat model describing the adversarial capabilities targeting the abstract system. We extend our assumptions of the generic threat model for each framework presented in the following chapters.

Having laid out the necessary foundation, we proceed with Chap. 4 – 7, which present the main pillars of our research. Yet, before we begin addressing our research objectives (Sec. 1.2), in Chap. 4, we elaborate an alternate, on-demand deployment strategy for virtualization-assisted services. Specifically, we present WhiteRabbit, a thin microkernel-based VMM that can be deployed on-the-fly. We exemplify a specific use case, in which we apply WhiteRabbit to deploy a VMI-based framework on a running Linux. At the same time, we underline WhiteRabbit's ability to act as a generic vehicle, which is not limited to VMI, and hence can be leveraged to dynamically deploy any of the virtualization-assisted services of the following chapters. We conclude this chapter by assessing and comparing the virtualization overhead of WhiteRabbit with Linux KVM and the Xen hypervisor.

Further, in Chap. 5, we focus on improving the state-of-the-art VMI techniques on ARM. In this chapter, we identify that ARM does not provide the necessary hardware support in regard to stealthy monitoring. To compensate the missing hardware capabilities, we explore alternative directions for VMI. We repurpose the system's virtualization extensions to implement novel primitives for setting and single-stepping software breakpoints in a stealthy way, without using the intended hardware mechanisms. We integrate the presented strategy into the dynamic binary analysis framework, DRAKVUF, and hence empower ARM with the ability to stealthy monitor guest OSes. We conclude this section by extensively assessing the performance and effectiveness of the introduced primitives.

In Chap. 6, we turn our attention towards reinforcing the security of OS components through virtualization. We leverage virtualization extensions on Intel to establish selective memory protection (xMP) primitives, which we intend to use against data-oriented attacks in kernel and user space. We equip the Linux memory management system with the ability to configure and switch among different views on the guest's physical memory. By configuring the views in a sophisticated way, we establish the means for protecting sensitive data in kernel and user space in isolated and disjoint xMP domains. In addition, we equip in-kernel management information and pointers to sensitive data in xMP domains with context-bound authentication codes to obstruct data-oriented attacks. We conclude this section by assessing the performance and security of the introduced xMP primitives.

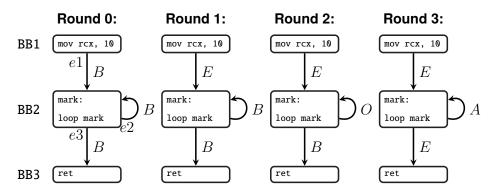

In Chap. 7, we focus on enhancing the security of OS-level virtualization (i.e., containers) techniques. Contrary to the previous chapters, we utilize the Secure Computing (seccomp) mode of the Linux kernel to reduce the system call interface. In this way, we intend to eliminate unnecessary and potentially vulnerable system calls, which would be otherwise freely available to the containers. Specifically, we introduce Jesse, a framework that combines a set of static analysis techniques to tailor seccomp policies for (containerized) Executable and Linkable Format (ELF) binaries. Jesse either extracts binaries from container images (or directly takes them from the file system) and applies an abstract interpretation based constant propagation technique to identify authorized system calls for a given binary. Additionally, we combine Jesse with state-of-the-art library debloating techniques to associate each of the exported functions in the standard C library (libc) with a set of system calls it requires for its execution. In the end, Jesse combines the identified system calls of the analyzed binary with the system calls of each libc function the analyzed binary requires. Finally, Jesse uses the extracted system calls to generate secomp policies for the respective Docker containers. We conclude this chapter by evaluating the precision of our analysis and by applying Jesse to popular Docker images and protecting them against real-world container escalation exploits.

We conclude this dissertation in Chap. 8, in which we summarize our contributions and provide an outlook on future research directions with regard to enhancing the state of virtualization-assisted analysis and OS security.

# **Technical Background**

If you can't explain it simply, you don't understand it well enough.

— Albert Einstein

This chapter assists the reader with the fundamentals that are essential to the understanding of the remainder of the dissertation. In particular, the following sections cover different concepts of the virtualization technology, the necessary means for their implementation, and the benefits and challenges behind VMI. In other words, the conveyed knowledge of this chapter renders the necessary foundation, upon which we base our research on virtualization-assisted dynamic binary analysis and OS security.

# 2.1 Virtualization Technology

The adoption of virtualization techniques in modern computer systems has become omnipresent and unavoidable. In fact, virtualization is deeply embedded in various computer system components, which we often do not consciously, or directly associate with virtualization itself. For instance, even though *virtual memory* is regarded as a given construct, it represents one form of virtualization that allows to decouple, or abstract the management of the limited physically available memory resources of one or multiple interconnected systems. This form of virtualization contributes to better performance and overall physical memory utilization, as well as security through address space isolation. Further examples for virtualization comprise among others: virtual system calls [Bov14a] which increase the performance of selected system calls by emulating their functionality in user space; and the extended Berkeley Packet Filter (eBPF) in-kernel virtual machine which establishes an execution environment for user-supplied programs in the Linux kernel, e.g., for filtering network traffic or unauthorized system calls, tracing, and in-kernel optimization [Fle17]. While these virtualization techniques transparently assist us in our every-day life, in this thesis, we mainly focus on virtualization techniques that establish isolated execution environments for individual (or groups of) processes or entire OSes.

One of the key concepts of virtualization is its ability to manage complexity [SN05]. To fully understand even the most complex systems, we can break down their complex structure into a hierarchy of different levels of *abstraction*; higher, more abstract levels build upon, yet, do not involve with the implementation details that are encapsulated by lower abstraction levels. Instead, the abstraction levels are separated by *well-defined interfaces* that hide complex implementation details. At the same time, the interfaces impose a strict specification; software written for one interface will not work on another. As a result, components residing at higher levels of abstraction receive a simplified view over the lower components in the hierarchy, yet, have to adhere to the specific interface.

To clarify the general idea, let us apply the concept of managing complexity to the above scenario of virtual memory. Virtual memory hides the complexity of managing the physical memory behind a well-defined memory management interface. That is, the virtual address spaces presented to processes—that we regard as system components at a higher abstraction level—embody an abstract, or simplified view of the underlying memory management subsystem at the heart of the OS kernel. The well-defined abstraction interface, relaxes the constraints of the underlying implementation details. In fact, it provides an illusion to user space processes of possessing exclusive access to an immense amount of memory resources, defined by the virtual address space. Specifically, this interface hides the underlying memory management system implementation that is responsible, amongst others, for governing physical memory, page tables, memory overcommitment, and swapping. At the same time, the interface strictly defines how the processes can interact with the virtual address space. By following the specifications of the interface, processes can execute, access, and even allocate and release additional memory, without any concern about these and further details of the overall architecture.

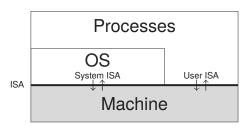

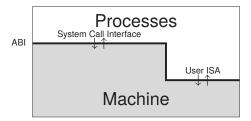

- (a) The ISA interface defines the machine. (b) The ABI interface defines the machine.

Figure 2.1: Different interfaces define different perspectives on the machine [SN05].

Similarly, the inherent properties of physical computer architectures define strict and immutable interfaces. Two interfaces that we consider relevant for this work are the *Instruction Set Architecture (ISA)* and the *Application Binary Interface (ABI)* (Fig. 2.1).

**Instruction Set Architecture:** The ISA represents the lowest interface that interlinks the hardware with the software. It defines the architecture's instruction set, registers, (virtual) memory, and the interrupt and exception architecture. Fig. 2.1(a) illustrates a simplified representation of this interface. In the figure, we further distinguish between components of the user ISA and system ISA, which are visible to less- or highprivileged software, respectively. While the user ISA is responsible for establishing an execution environment for software, the system ISA assists the OS in managing the system's hardware resources. The microarchitecture of different Central Processing Units (CPUs) ensures that software, developed for a specific ISA, is compatible to all CPU variants that implement the same ISA. Thus, the ISA is responsible for software compatibility and strictly regulates which software components are authorized to access specific parts of the underlying system.

**Application Binary Interface:** Similar to the ISA, we can subdivide the ABI into the *system* call interface and the less-privileged user-visible part of the ISA. Fig. 2.1(b) sketches this division. Through the system call interface, OSes offer less-privileged user space applications a uniform link that governs access to the OS internals. In other words, the system call interface lends processes in user space the ability to request and communicate with system resources, such as memory and I/O devices.

To sum up, the ISA strictly defines an interface between the OS and the underlying hardware, binding the OS to the particular architecture (Fig. 2.1(a)). Similarly, the ABI separates user space applications from the details implemented by the OS and hardware, ultimately creating dependencies between the applications and the overall platform (Fig. 2.1(b)). In both cases, the respective interface hides the complexity of the implementation details underneath the particular interface, lending software (at higher abstraction levels) an abstract view of the underlying *machine* upon which it is executing. In this regard, an OS perceives the machine through the angle that is defined by the ISA; whereas from the perspective of

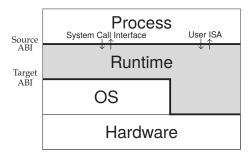

Figure 2.2: Process VM runtimes implement and expose a virtual ABI to processes [SN05].