# A Framework to Generate High-Performance Time-stepped Agent-based Simulations on Heterogeneous Hardware

## Jiajian Xiao

Vollständiger Abdruck der von der TUM School of Computation, Information and Technology der Technischen Universität München zur Erlangung des akademischen Grades eines

## Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

## Vorsitzender:

Prof. Dr. Florian Matthes

#### Prüfende der Dissertation:

- 1. Prof. Dr.-Ing. habil. Alois Christian Knoll

- Prof. Wentong Cai, Ph.D.,

Nanyang Technological University

Die Dissertation wurde am 11.04.2022 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 12.08.2022 angenommen.

## Abstract

Agent-Based Simulation (ABS) is a modelling approach where simulated entities i.e., agents, perform actions autonomously and interact with other agents based on a set of rules. ABSs have demonstrated their usefulness in various domains such as transportation, social science, or biology. Agent-based simulators commonly rely vastly on Central Processing Unit (CPU)-based sequential execution. As a result, they often suffer from long execution times, especially when the simulation model is complex and the scale is large.

One approach to circumvent this problem is to employ heterogeneous hardware, e.g., systems equipped with both CPUs and Graphics Processing Units (GPUs). Although existing works have shown this to be a promising solution, simulators that support heterogeneous hardware are still not widely utilized. As this thesis demonstrates, blame can be laid on the difficulties to find a viable partition of simulation components to run on different hardware devices as well as steep programming requirements to enable ABSs on heterogeneous hardware.

To ease the aforementioned issues, in this thesis, we present a full framework for automated generation of high-performance simulation code targeting heterogeneous hardware. The framework consists of two parts: OpenABLext and OptCL (short for Optimise performance targetting high-performance domain-specific Languages). OpenABLext significantly extends the existing OpenABL, a tool designed for generating high-performance ABS programs from sequential representations by parallelising the execution of so-called step functions which implement the agent-based models. We first extend its supported hardware to include multi-core CPUs, GPUs, and Field-Programmable Gate Arrays (FPGAs) by designing an OpenCL backend, allowing the incorporation of a wide range of hardware devices. We address OpenABL's limitation of 2-dimensional and 3-dimensional simulation environments by supporting graph-based simulation spaces in OpenABLext, opening it up for simulation types such as transport simulation which commonly use graph-based networks. A conflict resolution mechanism is introduced to ensure the simulation results of a parallel simulation run do not deviate from a sequential run, significantly improving reproducibility. Eventually, an online dispatcher is proposed as part of OpenABLext to enable automatic best suitable hardware selection for different simulation parts. In a comprehensive simulation study, we show OpenABLext not only drastically simplifies the programming effort

but also produces simulation code that outperforms other similar state-of-the-art approaches. With OptCL, we extend the idea of the online dispatcher to further boost the performance of the generated code on top of OpenABLext by enabling a collaborative execution (co-execution) mode where multiple hardware devices work simultaneously on different simulation parts. Through static analysis of data dependencies among compute-intensive code regions and performance predictions, the tool selects the best hardware for each simulation part as well as the execution schemes. The OptCL middleware operates at a language independent layer, a so-called Intermediate Representation. Therefore, it can not only benefit OpenABLext but also many other C-like Domain Specific Languages (DSLs). We demonstrate the power and versatility of OptCL by applying it to OpenABLext as well as another commonly used DSL called SYCL. In both scenarios, up to 21x speed-ups can be achieved.

The full framework proposed in this thesis significantly reduces the effort of employing heterogeneous hardware environments for agent-based simulation and thereby paves the way for the high-performance execution for a large variety of simulation models.

# Zusammenfassung

Agentenbasierte Simulation ist ein Modellierungsansatz. In der agentenbasierten Simulation, viele kleine Einheiten d.h. Agenten führen autonom Aktionen aus und interagieren mit anderen Agenten. Es ist ein Ansatz zur Systembewertung, der in verschiedensten Bereichen wie z.B. den Sozialwissenschaften, der Biologie, oder im Transportwesen Anwendung gefunden hat. Gängige agentenbasierte Simulatoren verlassen sich immer noch stark auf hauptsächlich CPU-gestützte Ausführung, was dazu führte, dass sie oft unter langen Ausführungszeiten leiden, insbesondere wenn der Simulationsumfang groß oder komplex ist.

Durch den Einsatz heterogener Hardware, wie z.B. Systemen, die sowohl mit CPUs als auch mit GPUs ausgestattet sind, lässt sich, wie in vielen Arbeiten bereits vielversprechend gezeigt, dieses Problem reduzieren. Was der Akzeptanz und Anwendung heterogener Systeme im Simulationsbereich jedoch noch entgegensteht, ist die Tatsache, dass die Programmierung heterogener Hardware fundierte und auch spezialisierte Kenntnisse erfordert. Dies wird in dieser Arbeit anhand zweier Machbarkeitsstudien demonstriert, die zeigen, dass es einen erheblichen Aufwand erfordert, um eine optimierte Performanz für agentenbasierte Simulationen in heterogenen Hardwareumgebungen zu erreichen: Die erste Studie veranschaulicht dies an einer Plattform bestehend aus GPU and CPU, die zweite an einem System mit einem FPGA und einer CPU. Um die Programmierung von agentenbasierten Simulationen für heterogene Hardwareumgebungen zu vereinfachen, wird in dieser Arbeit das Framework OpenABLext entwickelt. OpenABLext basiert auf OpenABL, welches darauf ausgelegt ist, hoch-performante agentenbasierte Simulationen aus sequentiellen Repräsentationen zu generieren und die Ausführung sogenannter Stufen-Funktionen (welche die eigentlichen agentenbasierten Modelle implementieren) zu parallelisieren. OpenABLext erweitert diese Plattform um die Unterstützung von Multicore-CPUs, GPUs und FPGA durch die Einführung eines OpenCL-Backends. Da OpenABL nur 2D- und 3D-Simulationsräume unterstützt, wird die Plattform in dieser Arbeit außerdem um die Fähigkeit ergänzt, graphenbasierte Simulationsräume zu ermöglichen. Des Weiteren wird ein halbautomatischer Konfliktlösungsmechanismus entwickelt, um sicherzustellen, dass die Simulationsergebnisse in der parallelen Ausführung nicht von der einer sequenziellen abweichen. Schließlich wird ein Online-Dispatcher als Teil von OpenABLext vorgestellt, welcher automatisch die am besten geeignete Hardware für die verschiedenen Teile einer Simulation auswählt. In detaillierten Leistungsbewertungen zeigt sich die verbesserte Leistung von OpenABLext sowie das Potenzial von FPGAs im Kontext der agentenbasierten Simulation. Als weitere Leistungsverbesserung wird der Online-Dispatcher um einen kollaborativen Ausführungsmodus erweitert, der es erlaubt, verschiedene Simulationsteile auf mehreren Hardwareumgebungen gleichzeitig auszuführen. Dies wird durch eine neu-entwickelte Middleware namens OptCL unterstützt, welche durch statische Analyse von Datenabhängigkeiten zwischen rechenintensiven Coderegionen und Leistungsvorhersagen die beste Hardware für jeden Simulationsteil auswählt und festlegt, ob diese Teile auf homogener Hardware oder in kollaborativer Ausführung abgearbeitet werden sollen. Die Middleware selbst arbeitet auf einer IR-Ebene, die es erlaubt, dass sie nicht nur mit OpenABLext, sondern auch mit anderen C-ähnlichen DLSs genutzt werden kann. Diese Vielseitigkeit wird durch die Anwendung mit SYCL, ein verbreitetes DSL, demonstriert.

Das in dieser Arbeit vorgestellte Framework bestehend aus OpenABLext und OptCL vereinfacht die Entwicklung von hoch-performanten agentenbasierten Simulationen erheblich.

# Acknowledgements

I would like to thank my supervisor Prof. Dr. Alois Knoll for giving me the opportunity to pursue my Ph.D. under his supervision and his inspiration in helping me find my research directions. I would also like to express my sincere gratitude towards Prof. Dr. Wentong Cai from the Nanyang Technological University for his mentorship and guidance. His plentiful knowledge in the field of high-performance computing has helped me a lot.

Special thanks go to Dr. Philipp Andelfinger and Dr. David Eckhoff for their incredible support and mentorship. Without them this thesis would not be possible. A special mention to Görkem Kılınç for giving me the unique chance to supervise his master's thesis. His work plays an important part in my research. I would also like to thank Dr. Heiko Aydt and Dr. Suraj Nair for offering me the opportunity to work at TUMCREATE.

Further, I would like to thank all my colleagues at TUMCREATE who have been providing me with a fantastic research environment. Of all my colleagues, I would like to give special thanks to Dr. Daniel Zehe and Dr. Jordan Ivanchev for their inspiration and support in many of my research works.

A very special gratitude goes out to all down at Singapore National Research Fund for helping and providing the funding for the work.

Lastly, I would like to thank my family for their support with all matters of the heart. A special thank goes to my wife Ms. Wang Yanting for her exceptional support.

# Contents

| $\mathbf{C}$ | onter  | nts     |                                                                |   | ix   |  |

|--------------|--------|---------|----------------------------------------------------------------|---|------|--|

| Li           | ist of | Figur   | es                                                             |   | xiii |  |

| Li           | ist of | Table   | S                                                              |   | xvii |  |

| A            | crony  | yms     |                                                                |   | xix  |  |

| 1            | Intr   | roducti | ion                                                            |   | 1    |  |

|              | 1.1    | Motiv   | ation                                                          |   | 1    |  |

|              | 1.2    | Proble  | em Statement                                                   |   | 3    |  |

|              | 1.3    | Key C   | Contributions                                                  |   | 4    |  |

|              | 1.4    | Outlin  | ne                                                             | • | 5    |  |

| 2            | Sta    | te of t | he Art                                                         |   | 7    |  |

|              | 2.1    | Agent   | -based Simulation                                              |   | 8    |  |

|              |        | 2.1.1   | Constraints for the studied Agent-Based Simulation (ABS)s      |   | 9    |  |

|              |        | 2.1.2   | Computational Aspects of ABS                                   |   | 10   |  |

|              | 2.2    | Hardy   | vare Platforms                                                 |   | 11   |  |

|              |        | 2.2.1   | Many-Core Central Processing Unit (CPU)                        |   | 11   |  |

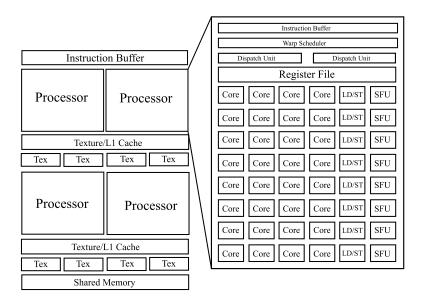

|              |        | 2.2.2   | Graphics Processing Unit (GPU)                                 |   | 12   |  |

|              |        | 2.2.3   | Accelerated Processing Unit (APU)                              |   | 14   |  |

|              |        | 2.2.4   | Field-Programmable Gate Array (FPGA)                           |   | 14   |  |

|              |        | 2.2.5   | Other Hardware Platforms                                       |   | 16   |  |

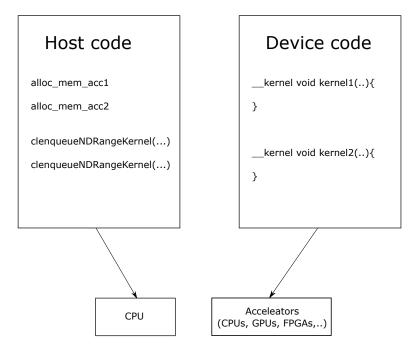

|              | 2.3    | Open    | Computing Language (OpenCL)                                    |   | 16   |  |

|              | 2.4    | Addre   | ssing the Challenges of Agent-Based Simulation on Accelerators |   | 17   |  |

|              |        | 2.4.1   | Hardware Assignment                                            |   | 19   |  |

|              |        |         | 2.4.1.1 Static Assignment                                      |   | 20   |  |

|              |        |         | 2 / 1 2 Dynamic Assignment                                     |   | 23   |  |

|   |      | 2.4.2    | Minimisation of Data Transfer Overheads                             | 24       |

|---|------|----------|---------------------------------------------------------------------|----------|

|   |      |          | 2.4.2.1 Overlapping of Communication and Computation                | 25       |

|   |      |          | 2.4.2.2 Computation Replication at Partition Boundaries             | 25       |

|   |      | 2.4.3    | Scattered Memory Accesses                                           | 26       |

|   |      |          | 2.4.3.1 Manual Caching in Shared Memory                             | 28       |

|   |      |          | 2.4.3.2 Heuristics for Agent Update Order                           | 29       |

|   |      |          | 2.4.3.3 Representation of Irregular Data Structures by Arrays       |          |

|   |      |          | and Grids                                                           | 30       |

|   |      | 2.4.4    | Maximisation of Parallelism                                         | 33       |

|   |      |          | 2.4.4.1 Multiple Replications in Parallel                           | 34       |

|   |      |          | 2.4.4.2 Window-based Event Execution                                | 34       |

|   |      |          | 2.4.4.3 Speculative Execution                                       | 35       |

|   |      |          | 2.4.4.4 Computation Sorting                                         | 36       |

|   |      | 2.4.5    | Abstraction from Hardware Specifics                                 | 37       |

|   |      |          | 2.4.5.1 Frameworks to Support Simulation Development                | 37       |

|   |      |          | 2.4.5.2 Unified Memory Access                                       | 38       |

|   | 2.5  | Towar    | ds an automated parallelisation framework for ABS                   | 39       |

| 3 | Feas | sibility | Studies: Accelerating Agent-based Simulations on Het-               |          |

|   |      | •        |                                                                     | 41       |

|   | 3.1  | Introd   | uction                                                              | 42       |

|   | 3.2  | Relate   | ed Work                                                             | 42       |

|   | 3.3  | City N   | Mobility Simulator(CityMoS)                                         | 45       |

|   | 3.4  | Feasib   | ility Study 1: Model-level vs Sense-Think-Act-level Parallelisation | 46       |

|   |      | 3.4.1    | Simulation Settings                                                 | 46       |

|   |      | 3.4.2    | Overview                                                            | 47       |

|   |      | 3.4.3    | Baseline: CPU-Based Execution                                       | 49       |

|   |      |          | 3.4.3.1 Architecture                                                | 49       |

|   |      |          | 3.4.3.2 Implementation                                              | 50       |

|   |      |          | 3.4.3.3 Performance Evaluation                                      | 50       |

|   |      | 3.4.4    | Sense-Think-Act-level parallelisation (Partial Offloading)          | 51       |

|   |      |          |                                                                     |          |

|   |      |          | 3.4.4.1 Architecture                                                | 51       |

|   |      |          |                                                                     | 51<br>52 |

|   |      |          | 3.4.4.2 Implementation                                              |          |

|   |      | 3.4.5    | 3.4.4.2 Implementation                                              | 52       |

|   |     |        | 3.4.5.2 Implementation                                        | 55 |

|---|-----|--------|---------------------------------------------------------------|----|

|   |     |        | 3.4.5.3 Performance Evaluation                                | 57 |

|   |     | 3.4.6  | Discussion                                                    | 58 |

|   | 3.5 | Feasib | ility Study 2: Agent-Based Traffic Simulation (ABTS) on FPGAs | 61 |

|   |     | 3.5.1  | Simulation Settings                                           | 61 |

|   |     | 3.5.2  | FPGA-based Execution                                          | 62 |

|   |     |        | 3.5.2.1 Architecture                                          | 62 |

|   |     |        | 3.5.2.2 Implementation                                        | 63 |

|   |     |        | 3.5.2.3 Performance Evaluation                                | 66 |

|   | 3.6 | Summ   | ary                                                           | 67 |

| 4 | Cor | orotin | g High-Performance Code for Agent-Based Simulations           |    |

| - |     |        | geneous Platforms Using OpenABLext                            | 69 |

|   | 4.1 |        | luction                                                       | 70 |

|   | 4.2 |        | round                                                         | 71 |

|   |     | 4.2.1  | Related Work                                                  | 71 |

|   |     | 4.2.2  | OpenABL                                                       | 73 |

|   | 4.3 |        | OpenABL to OpenABLext                                         | 74 |

|   |     | 4.3.1  | User-Specified Environments                                   | 75 |

|   |     | 4.3.2  | Open Computing Language (OpenCL) code generation for Het-     |    |

|   |     |        | erogeneous Hardware                                           | 76 |

|   |     |        | 4.3.2.1 OpenCL for GPUs and CPUs                              | 77 |

|   |     |        | 4.3.2.2 OpenCL code generation for FPGAs                      | 79 |

|   |     |        | 4.3.2.3 Code Generation for Co-execution                      | 80 |

|   |     |        | 4.3.2.4 Hardware Selection with Online Dispatcher             | 83 |

|   |     | 4.3.3  | Conflict Resolution                                           | 84 |

|   | 4.4 | Evalua | ation                                                         | 88 |

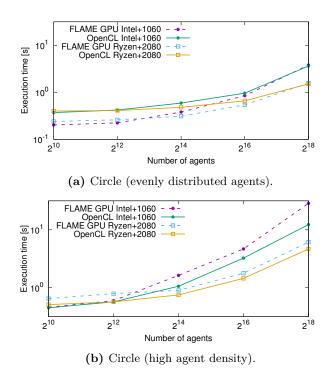

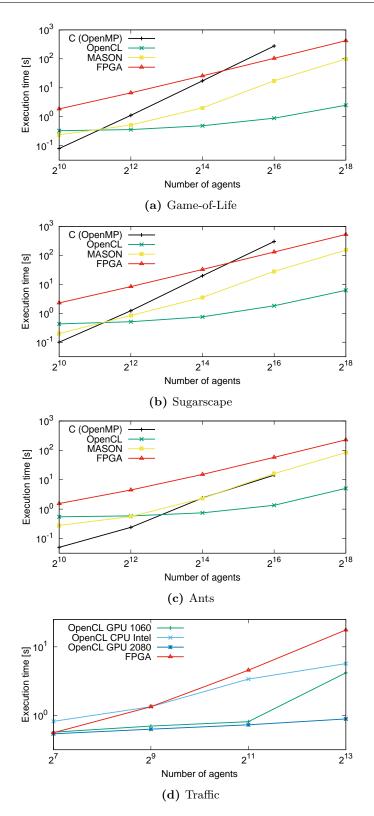

|   |     | 4.4.1  | OpenCL backend                                                | 89 |

|   |     | 4.4.2  | Conflict resolution                                           | 90 |

|   |     | 4.4.3  | Online dispatcher                                             | 91 |

|   | 4.5 | Summ   | ary                                                           | 92 |

| 5 | Sau | oozina | more Performance - Enhancing Co-execution Capability          |    |

| J | _   | h Opt( |                                                               | 95 |

|   | 5.1 | _      | luction                                                       | 96 |

|   | 5.2 |        | round and Related Work                                        | 97 |

|   |     | 5.2.1  | OpenABLext                                                    | 97 |

|   |     |        |                                                               |    |

|    |        | 5.2.2  | SYCL                                                       |

|----|--------|--------|------------------------------------------------------------|

|    |        | 5.2.3  | Abstract Syntax Tree (AST)                                 |

|    |        | 5.2.4  | Related work                                               |

|    | 5.3    | The O  | ptCL Middleware                                            |

|    |        | 5.3.1  | Step 1: Data Dependency Analysis                           |

|    |        | 5.3.2  | Step 2:Profiling                                           |

|    |        | 5.3.3  | Step 3: Hardware Assignment and Program Reconstruction 106 |

|    |        | 5.3.4  | Optimisation                                               |

|    |        |        | 5.3.4.1 Enhanced Dependency Detection 108                  |

|    |        |        | 5.3.4.2 User-specified merge_function 108                  |

|    |        |        | 5.3.4.3 Single Kernel                                      |

|    | 5.4    | Evalua | ation                                                      |

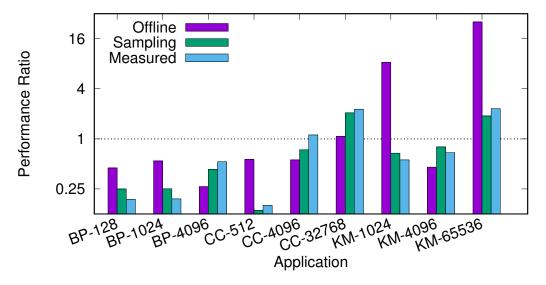

|    |        | 5.4.1  | Profiling Approaches Comparison                            |

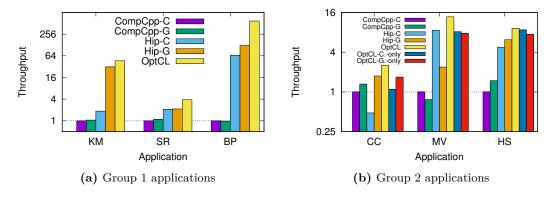

|    |        | 5.4.2  | Case Study 1: SYCL                                         |

|    |        | 5.4.3  | Case Study 2: OpenABLext                                   |

|    | 5.5    | Summ   | ary                                                        |

| 6  | Cor    | clusio | n & Outlook                                                |

|    | 6.1    | Summ   | ary 117                                                    |

|    | 6.2    | Outloo | ok                                                         |

| Bi | iblios | raphy  | 12                                                         |

# List of Figures

| 2.1 | GPU architecture                                                         | 13 |

|-----|--------------------------------------------------------------------------|----|

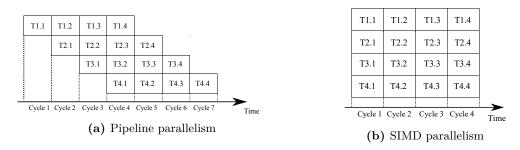

| 2.2 | Pipeline parallelism versus SIMD parallelism. We assume four tasks,      |    |

|     | each task being divided into four operations (e.g., T1.1 - T1.4)         | 15 |

| 2.3 | OpenCL programming paradigm                                              | 17 |

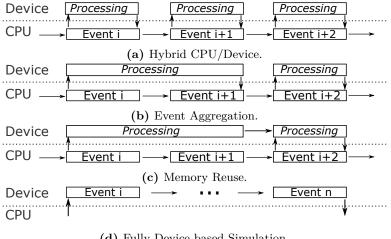

| 2.4 | Four CPU-device simulation schemes [1]. Devices can be GPUs or many-     |    |

|     | core CPUs                                                                | 22 |

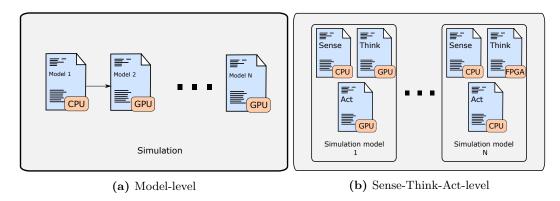

| 2.5 | Model-level vs Sense-Think-Act-level parallelisation schemes             | 40 |

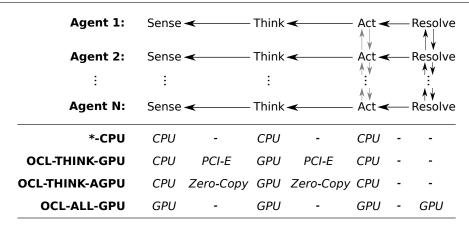

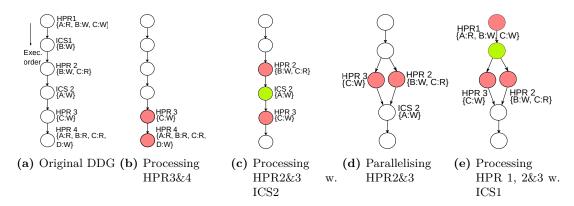

| 3.1 | Top: dependencies among the stages in a simulation time step. If inter-  |    |

|     | agent dependencies are ignored during the Act stage, a separate conflict |    |

|     | resolution stage is required. Bottom: the execution schemes considered   |    |

|     | in our experiments and the means of data transfer from one stage to the  |    |

|     | next                                                                     | 49 |

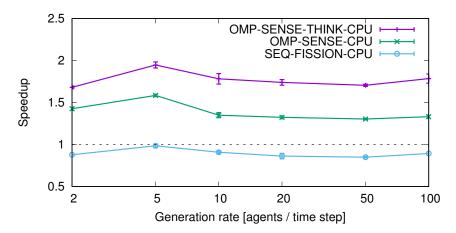

| 3.2 | Speedup with standard errors when parallelising Sense (OMP-SENSE-        |    |

|     | CPU) or Sense and Think (OMP-SENSE-THINK-CPU) over sequential            |    |

|     | execution (SEQ-CPU). Loop fission (SEQ-FISSION-CPU) results in a         |    |

|     | slight slowdown.                                                         | 51 |

| 3.3 | Total execution time on the dedicated CPU for the Think stage of the     |    |

|     | car-following model and lane-changing model when varying the work-       |    |

|     | group size                                                               | 53 |

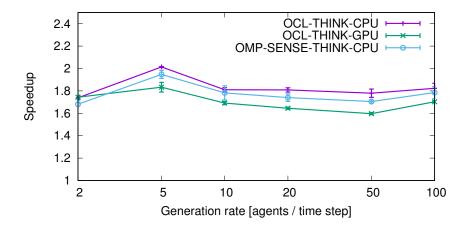

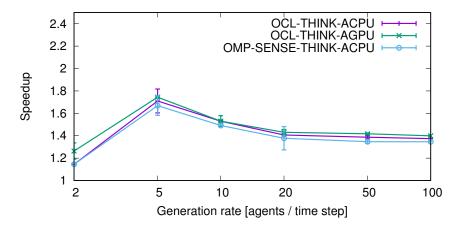

| 3.4 | Speedup with error bars showing standard errors over sequential ex-      |    |

|     | ecution when parallelising Sense by OpenMP and Think by OpenCL           |    |

|     | (OCL-THINK-CPU) and when offloading Think to the dedicated GPU           |    |

|     | (OCL-THINK-GPU)                                                          | 54 |

| 3.5 | Speedup with error bars showing standard errors over sequential exe-     |    |

|     | cution when parallelising Sense by OpenMP and Think by OpenCL on         |    |

|     | the CPU portion of an APU (OCL-THINK-ACPU) and when offloading           |    |

|     | Think to the GPU portion of an APU (OCL-THINK-AGPU)                      | 55 |

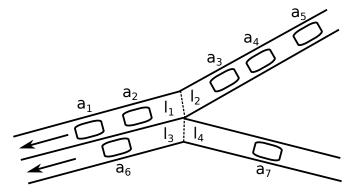

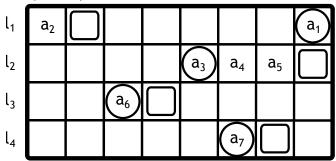

| 3.6 | Road network representation in OCL-ALL-CPU and OCL-ALL-GPU.              | 56 |

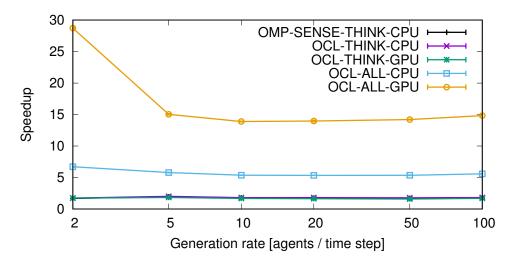

| Overall comparison of the execution schemes over sequential execution                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| with error bars showing standard errors                                                                    | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Neighbour search                                                                                           | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Illustration of pipelined processing of agents                                                             | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

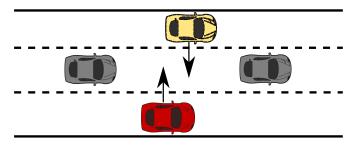

| Illustration of a possible collision due to our double-buffering design                                    | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

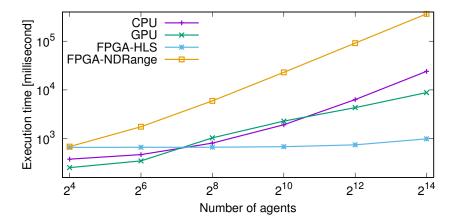

| Performance comparison between CPU, GPU, FPGA-HLS and FPGA-                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| NDRange                                                                                                    | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

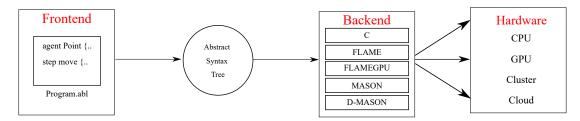

| An overview of the OpenABL framework                                                                       | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $Agents \ are \ sorted \ by \ their \ {\tt position} \ (e.g., {\tt EdgeID} \ and \ {\tt PositionOnEdge}).$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Each element in the environment array keeps a mem_start and a mem_end                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| pointer to its agents in global memory                                                                     | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

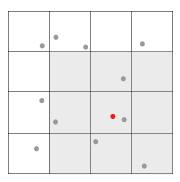

| In a grid with cell width at least the search radius, the neighbour search                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                            | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ,                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ,                                                                                                          | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                            | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                            | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

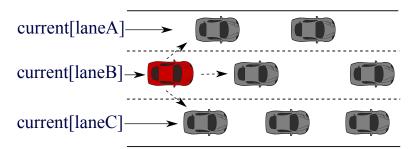

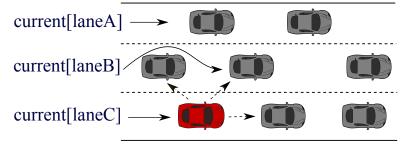

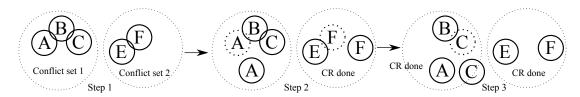

|                                                                                                            | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| •                                                                                                          | 0.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                            | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

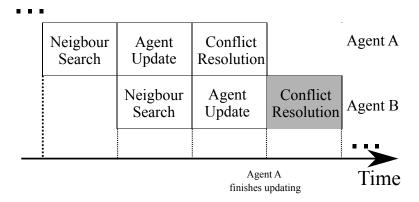

|                                                                                                            | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

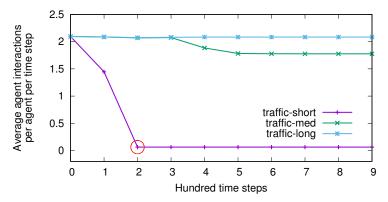

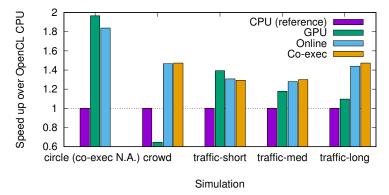

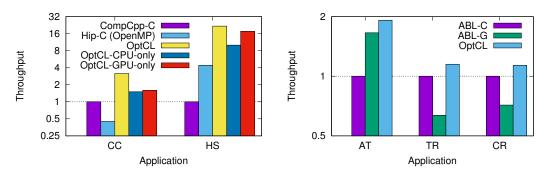

| Evaluation of the proposed online dispatcher on Platform 1                                                 | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

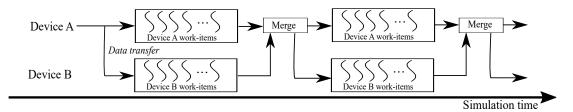

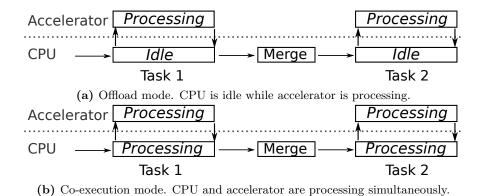

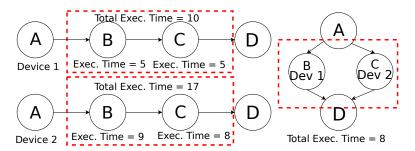

| Offload mode vs co-execution mode                                                                          | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

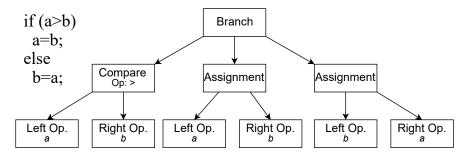

| An example Abstract Syntax Tree (AST) generated from an if-else clause.                                    | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

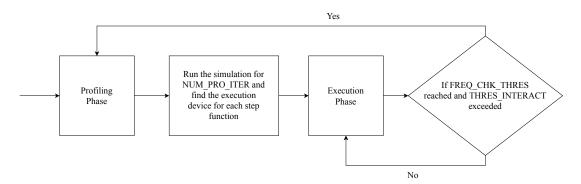

| An overview of Optimise performance targetting high-performance domain-<br>specific Languages (OptCL)      | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                            | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| •                                                                                                          | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |