TECHNISCHE UNIVERSITÄT MÜNCHEN

Bachelor's Thesis in Informatics

# Performance Portability and Evaluation of Heterogeneous Components of SeisSol Targeted to Upcoming Intel HPC GPUs

Ludwig Kratzl

TECHNISCHE UNIVERSITÄT MÜNCHEN

Bachelor's Thesis in Informatics

# Performance Portability and Evaluation of Heterogeneous Components of SeisSol Targeted to Upcoming Intel HPC GPUs

# Portierung und Leistungsanalyse heterogener Komponenten von SeisSol für zukünftige Intel HPC GPUs

Author:Ludwig KratzlSupervisor:Prof. Dr. Michael BaderAdvisor:M. Sc. Ravil DorozhinskiiSubmission Date:15/07/2021

I confirm that this bachelor's thesis in informatics is my own work and I have documented all sources and material used.

Garching, 15/07/2021

Ludwig Kratzl

### Acknowledgments

I would like to pay my special regards to my supervisor Prof. Dr. Michael Bader and my advisor Ravil Dorozhinskii for their great guidance throughout this work. My sincere thanks also goes to three members of the Intel cooperation for their fast and productive support. I would also like to thank the Department for Geophysics at the Ludwig-Maximilian University for providing me access to the Heisenbug machine. Last, I want to thank my family and friends, especially my sister Franziska Kratzl, who has inspired and motivated me to study.

# Abstract

For the first time in over 20 years, Intel is selling discrete graphics cards, including products for high-performance computing, scheduled for release in 2022. This thesis investigates programming models for the upcoming Intel GPUs and selects the Sycl standard, provided by oneAPI and hipSYCL, to port the heterogeneous components of SeisSol. The modules in question in SeisSol are analyzed and extended, and their efficiency is assessed using a Roofline Model analysis. Similar experiments are performed using Sycl with CUDA as a backend to test whether this combination can replace all native GPU approaches. This work demonstrates that already the low-power series of Intel's discrete GPUs can reach over 85 % of their peak performance using this portability, making them superior to integrated graphics chips. However, further measurements also show that Intel MPI needs to be improved before it can be used on supercomputers. With an Nvidia RTX 3090 and Intel Arria 10 FPGA, it is proven that Sycl's cross-platform approach works but that its efficiency heavily depends on the implementation of the standard.

# Kurzfassung

Erstmals seit über 20 Jahren verkauft Intel diskrete Grafikkarten, darunter auch Produkte für High-Performance Computing, die 2022 erscheinen sollen. Die vorliegende Arbeit untersucht Programmiermodelle für die erscheinenden Intel-GPUs und selektiert den Sycl-Standard, bereitgestellt durch oneAPI und hipSYCL, für die Portierung von SeisSols heterogenen Komponenten. Die betreffenden Module in SeisSol werden analysiert und erweitert und die Effizienz der Portierung mithilfe eines Roofline-Diagramms durchgeführt. Ähnliche Experimente werden mit Sycl und CUDA als Backend durchgeführt, um zu prüfen, ob diese Kombination alle nativen GPU-Ansätze ersetzen kann. Diese Arbeit demonstriert, dass schon die Low-Power Serie von Intels diskreten GPUs an 85 % ihrer Spitzenleistung mit der Portierung herankommt und damit den integrierten Grafikchips überlegen ist. Allerdings zeigen weitere Messungen auch, dass Intel MPI vor dem Einsatz auf Supercomputern verbessert werden muss. Mit einer Nvidia RTX 3090 und Intel Arria 10 FPGA wird belegt, dass Sycls Crossplattform Ansatz funktioniert, aber dessen Effizienz stark von der Implementierung des Standards abhängt.

# Contents

| Ac | knov                      | vledgm  | iv<br>v<br>1<br>s<br>Js   |    |  |  |  |  |  |  |

|----|---------------------------|---------|---------------------------|----|--|--|--|--|--|--|

| Ał | ostrac                    | ct      |                           | iv |  |  |  |  |  |  |

| Kι | ırzfa                     | ssung   |                           | v  |  |  |  |  |  |  |

| 1. | Intr                      | oductio | on                        | 1  |  |  |  |  |  |  |

| 2. | Fundamentals              |         |                           |    |  |  |  |  |  |  |

|    | 2.1.                      | Intel C | GPUs                      | 3  |  |  |  |  |  |  |

|    |                           | 2.1.1.  | Gen11 Architecture        | 3  |  |  |  |  |  |  |

|    |                           | 2.1.2.  | Iris Xe Architecture      | 5  |  |  |  |  |  |  |

|    |                           | 2.1.3.  | Intel GPUs in HPC         | 6  |  |  |  |  |  |  |

|    | 2.2.                      | Intel C | GPU Programming           | 6  |  |  |  |  |  |  |

|    |                           | 2.2.1.  | OpenMP                    | 6  |  |  |  |  |  |  |

|    |                           | 2.2.2.  | OpenCL                    | 7  |  |  |  |  |  |  |

|    |                           | 2.2.3.  | Sycl                      | 8  |  |  |  |  |  |  |

|    | 2.3.                      | SeisSc  | ol                        | 9  |  |  |  |  |  |  |

|    |                           | 2.3.1.  | Numerical Scheme          | 9  |  |  |  |  |  |  |

|    |                           | 2.3.2.  | Heterogeneous Components  | 11 |  |  |  |  |  |  |

|    |                           | 2.3.3.  | Performance Portability   | 13 |  |  |  |  |  |  |

| 3. | Analysis and Design       |         |                           |    |  |  |  |  |  |  |

|    | 3.1.                      | Device  | e                         | 15 |  |  |  |  |  |  |

|    |                           | 3.1.1.  | CUDA compared to Sycl     |    |  |  |  |  |  |  |

|    |                           | 3.1.2.  | Design and Implementation | 18 |  |  |  |  |  |  |

|    |                           | 3.1.3.  | Correctness               | 19 |  |  |  |  |  |  |

|    | 3.2.                      | Gemn    | nForge                    | 20 |  |  |  |  |  |  |

|    |                           | 3.2.1.  | Design                    | 21 |  |  |  |  |  |  |

|    |                           | 3.2.2.  | Implementation            | 22 |  |  |  |  |  |  |

|    |                           | 3.2.3.  | Correctness               | 23 |  |  |  |  |  |  |

| 4. | Evaluation and Discussion |         |                           |    |  |  |  |  |  |  |

|    | 4.1.                      | Device  | e                         | 27 |  |  |  |  |  |  |

|    |                           | 4.1.1.  | Single Accelerator        |    |  |  |  |  |  |  |

|    |                           | 4.1.2.  | Multi GPU                 | 29 |  |  |  |  |  |  |

#### Contents

|     |                 | 4.2.1.<br>4.2.2.<br>SeisSo<br>4.3.1. | Forge          Roofline Model Analysis with Intel GPUs          Roofline Model Analysis with CUDA backend          I          SeisSol-Proxy          Benchmarks | 32 |  |  |  |  |  |  |

|-----|-----------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|--|

| 5.  | Con             | clusion                              |                                                                                                                                                                 | 41 |  |  |  |  |  |  |

| A.  | Figu            | res                                  |                                                                                                                                                                 | 42 |  |  |  |  |  |  |

| Lis | List of Figures |                                      |                                                                                                                                                                 |    |  |  |  |  |  |  |

| Lis | List of Tables  |                                      |                                                                                                                                                                 |    |  |  |  |  |  |  |

| Bil | oliog           | raphy                                |                                                                                                                                                                 | 47 |  |  |  |  |  |  |

# 1. Introduction

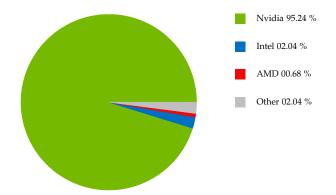

In 2019, Intel announced the 12th generation of its GPUs, including the first discrete Graphics Cards for over twenty years. The new series of products, Intel Iris Xe ( $X^e$ ), contains a revisited Instruction Set Architecture as well as models for office applications with low power consumption (Xe-LP), computer games, and general high-performance (Xe-HP and Xe-HPG), and HPC (Xe-HPC). While the Xe-LPs are already available by the Iris Xe Max "DG1", Intel did not release representatives of the other GPUs by the time of this thesis. However, the Leibniz Rechenzentrum (LRZ) recently announced to convey its SuperMUC-NG into a new phase<sup>1</sup>: To fit the needs of modern AI computations, they are going to expand the 15th fastest supercomputer in the world with the Iris Xe-HPC GPU called "Ponte Vecchio". This announcement could change future HPC architectures, as until now, most HPC centers rely on Nvidia GPUs: As described in Figure 1.1, from the top 500 supercomputers worldwide, 147 of them used accelerators or co-processors in November 2020, of which over 95 % were coming from the Nvidia product stack. Consequently, HPC applications are often developed with CUDA, the native language and API for Nvidia GPUs, which does not apply to Intel. Therefore, LRZ's breakthrough decision comes with the price that any CUDA code must be ported before running it on its new cluster. This especially concerns strategic partners of the LRZ like the Technical University of Munich (TUM), which uses the SuperMUC-NG as its base supercomputer.

One affected application will be SeisSol, an open-source software for numerical simulations of earthquakes and seismic waves. SeisSol was initially designed with an MPI+OpenMP model, targeted to computations on CPUs and accelerators like Co-Processors [1]. However, recent changes in SeisSol took a step towards Performance Portability by substituting OpenMP with CUDA, resulting in a doubled speedup by exploiting native programming features like shared memory and launch bounds [2]. Similar work has already been preceded with HIP, the programming language and toolkit for AMD graphics cards [3]. Nevertheless, neither HIP nor CUDA can be employed to target Intel GPUs. Therefore, SeisSol is not tunable to the future Intel GPUs running in LRZ or other supercomputers, as OpenMP only supports limited capabilities to access the offload device.

This thesis analyzes existing heterogeneous components of SeisSol and applies all necessary changes to adapt them to Intel GPUs. The work is structured as follows:

Chapter 2 introduces the topic by first summarizing the known hardware details of the existing and upcoming Intel GPUs. After that, available programming models for them are discussed and it is shown that Sycl, a cross-platform standard to program accelerators, fits best for portability. Additionally, an overview of available implementations of Sycl is given,

<sup>&</sup>lt;sup>1</sup>https://www.lrz.de/presse/ereignisse/2021-05-04-SuperMUC-NG-Phase-2\_ENG/

and hipSYCL and oneAPI are selected for compilation and performance evaluation. Next, the numerical scheme of SeisSol, based on a high-order Discontinuous Galerkin method and its implementation [4] solving the underlying system of Hyperbolic Partial Differential Equations, is summarized. With that, the necessity for high-performance parallelism and fine-tuned GPU kernels that justify the employment of native or low-level programming concepts like Sycl over OpenMP is explained. Finally, the term Performance Portability is discussed, and a Roofline Model analysis is chosen as success criteria for the main compute kernels.

Chapter 3 examines three submodules for heterogeneous access: Device, a facade for accelerator accesses, Yateto, providing a DSL to express tensor operations, and GemmForge, a code generator for batched General Matrix Multiplications (GEMMs), which implements the DSL of Yateto. It explains changes that were crucial in order to add support to the Sycl standard and focuses on how these modifications apply to use Sycl not only on Intel GPUs but also on FPGAs and arbitrary accelerators.

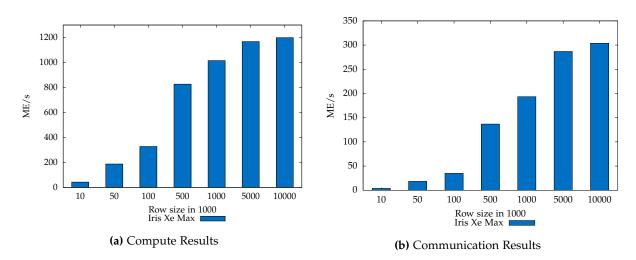

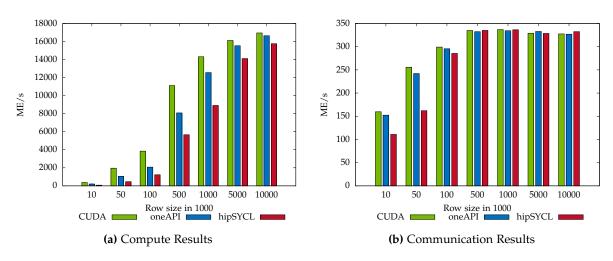

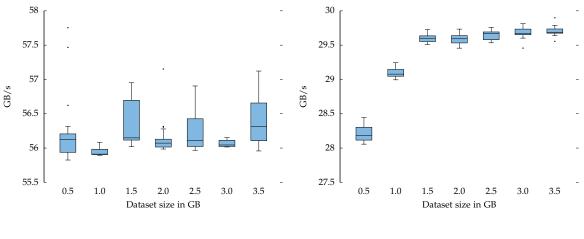

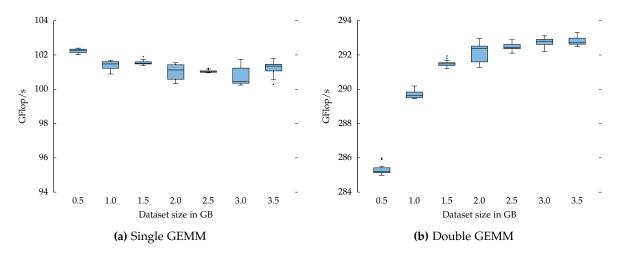

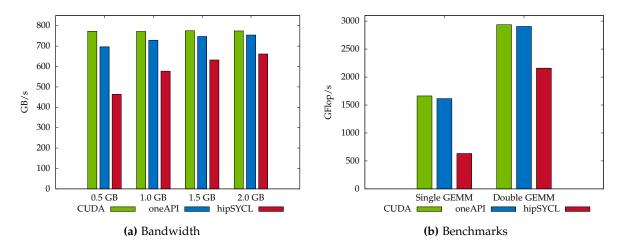

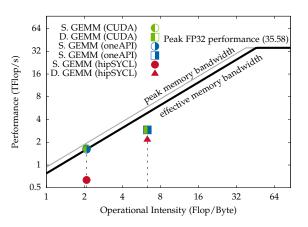

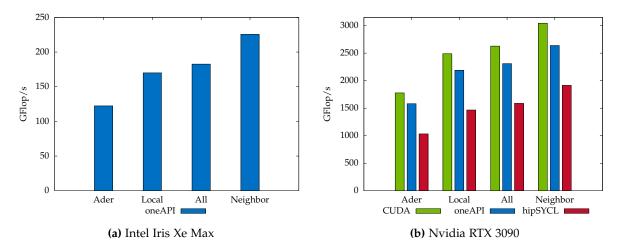

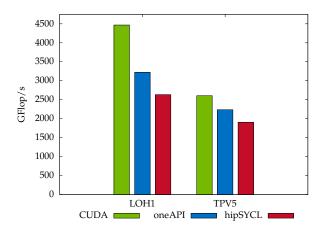

Chapter 4 evaluates Performance Portability by various benchmarks: At first, a parallel Jacobi Relaxation solver is performed on Intel's DevCloud with one and two Iris Xe Max "DG1" GPUs using Intel MPI. This shows that GPU-aware Intel MPI is available and is suitable for SeisSol, however needs further optimization before productive utilization. At the same time, the chapter demonstrates that DG1 is already able to get close to peak performance on dense GEMM operations and shows its superiority against SoC designs like the 9th Generation UHD Graphics P630. Running SeisSol proxy implementation and two benchmarks establishes a proof-of-concept of all changes and proofs that SeisSol will be able to run on the new SuperMUC-NG. Furthermore, explorative performance analyses using Intel Arria 10 FPGAs and two Nvidia RTX 3090 GPUs are performed, showing that the Sycl standard could replace all native GPU code in the future from a functional perspective, but not from a performance one. At last, this thesis ends with a summary and conclusion and describes future work which should be done once the new Intel GPUs are available.

**Figure 1.1.:** Market share of vendors of accelerators within the top 500 supercomputers. Total count of centers using GPUs or Co-processors: 147. Nvidia is significantly more often in use (140 of 147). Data extracted from https://www.top500.org/statistics/ using the ranking from November 2020. Accessed 05/21.

2

# 2. Fundamentals

This chapter summarizes fundamentals necessary to port SeisSol for the new Intel GPUs. First, Intel's latest integrated graphics chip (Gen11) and parts of its performance characteristics are examined. The following subsection accomplishes the same for all known details of Iris Xe series and compares these two generations among each other. Then, available programming models and compilers for any Intel GPU are discussed, and Sycl, together with oneAPI and hipSYCL, is selected for the remaining parts of this thesis. The following section dives deeper into heterogeneous components of SeisSol, mainly Device, Yateto, and GemmForge: It explains their structure and implementation details and justifies them with the help of SeisSol's Numerical Scheme, which is established in the same section. With this in mind, methods to evaluate all changes in terms of performance are analyzed, and Roofline Model analysis, in combination with several benchmarks and tests, is chosen as success criteria.

## 2.1. Intel GPUs

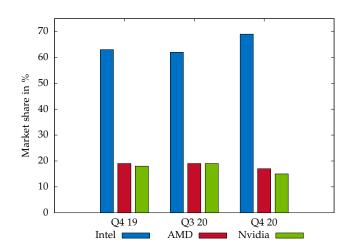

Contrary to what is popular assumed, Intel has been developing GPUs for over twenty years. For example, they released their first own discrete Graphics Card in 1998 with the i740 and i752, only three years after Nvidia but without success. However, they continued their work towards that: The Extreme Graphics and GMA series were mainly used as chipsets on a motherboard independent of other components like a CPU, resulting in limited performance aspects. With Intel HD Graphics (Generation 5 and later), Intel switched to a System on a Chip (SoC) architecture. From then, Intel processors did not only contain CPUs with several cores but also a GPU. This design led to a huge triumph in the GPU market: Though Figure 1.1 demonstrates the dominance of Nvidia in terms of HPC, Figure 2.1 shows the victory of the SoC architecture in the consumer market. In 2020, nearly 70% of all GPUs were Intel products (however, note that this is different when only considering discrete GPUs). In 2010, Intel again made a step towards discrete accelerators with the Xeon Phi manycore architecture. Initially inspired by previous GPU researches, this design has now been canceled in favor of Iris Xe series. The following subsections examine the latest GPU series, Gen11, and compare its characteristics with known details of the upcoming Iris Xe product stack.

### 2.1.1. Gen11 Architecture

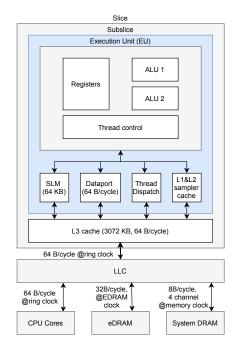

All investigations in this subsection are based on Intel architectural white papers [5] [6], if not otherwise indicated. Figure 2.2 gives a graphical overview of the subsequent explanations.

Figure 2.1: Market share of vendors of overall installed GPUs. Intel's proportion is notable greater than AMD's or Nvidia's. Data extracted from https:// www.jonpeddie.com/press-releases/g pu-shipments-soar-once-more-in-q4. Accessed 05/21.

Gen11 architecture structures itself, similar to its predecessor Gen9, in a single slice connected via a Ring Bus with CPU Cores and a coherent shared Last-Level-Cache (LLC). Each slice contains an L3 cache and slice-common components as well as eight subslices.

A subslice clusters eight execution units together with an L1 and L2 texture sampler cache and a shared local memory (SLM) of 64 KB. Here, Gen9 differs from Gen11: The SLM of Gen9 is attached outside of the subslice. Also, all subslices contain a dataport, a general-purpose memory unit for load and store operations with 64 Byte read and write bandwidth per second, and a thread dispatcher that assigns threads to execution units.

An Execution Unit (EU) is the main basic block of an Intel GPU. It is a computational unit consisting of two SIMD ALUs pipelined across seven available hardware threads. The ALUs have a vector width of 128 Bit, allowing up to four FP32 (32-bit floating point) or eight FP16 (16-bit floating point) operations simultaneously. With Fused Multiply Add (FMA) commands, a single EU can reach up to 16 FP32 or 32 FP16 operations per cycle: 2 (ALUs) · (4 or 8 SIMD-

**Figure 2.2.:** Schematic structure of the Intel Gen11 architecture: A slice groups into subslices that cluster several execution units (EUs). The GPU is connected with the CPU by a shared LLC

width)  $\cdot$  2 (FMA) = 16 or 32 operations. Therefore, a complete GPU results in a theoretical peak performance of  $8 \cdot 8 \cdot 16$ , 32 = 1024 FP32 or 2048 FP16 operations per cycle, respectively.

The memory bandwidth, on the other hand, is limited to its hierarchy. However, L1 and L2 sampler caches become only active in texture or image surface sampling, which is typically not relevant for high-performance computations. Therefore, the bandwidth of the GPU is

initially constrained by the 3 KB L3 cache of a subslice. Next follows the LLC (3 MB) shared by CPU and GPU and an optional embedded DRAM (eDRAM), serving as an additional cache level. Last, the connection of LLC to the system's memory control limits the memory bandwidth of all caches: For Gen11, this is 8 B per cycle on four channels, resulting in a theoretical bandwidth of system memory frequency times 4 times 8 Byte.

### 2.1.2. Iris Xe Architecture

The Iris Xe series is an iteration of Intel's Gen12 architecture. This subsection summarizes architectural details of the new Xe series based on the announced products of the LP series and an architectural overview shown at the Architecture Day 2020 [7]. One of the main benefits of the new architectural style are so-called tiles. Every tile resembles a single Iris Xe, that are together interconnected via a so-called XeLink. This feature is crucial to compute clusters like considered in this work. The following explanations show how the other known specifications apply to the four Xe sub-architectures.

- Iris Xe LP: By the time of writing, LP is the only released series. Intel Iris Xe Graphics G7 follows the SoC design, whereas Iris Xe Max DG1 (Discrete Graphics 1) is the standalone version equipped with 4 GB of memory. Both have a single slice and no additional tiles. One main difference between these GPUs and Gen11 is the number of subslices and execution units. In the case of Iris Xe LP, six subslices contain 16 EUs on each slice, whereas in Gen11, there are 8 for both. Hence, the minimum number of total EUs is 96 compared to 64 per slice. Using a boost clock of 1650 MHz and a memory clock of 2133 MHz, these two GPUs reach a theoretical peak bandwidth of 68.3 GB/s or 2.5 FP32 OP/s. Iris Xe Max SG1 (Server Graphics 1) is another model based on the aforementioned specifications but containing 8 GB of onboard DDR4 memory.

- Iris XE HPG: Iris Xe HPG DG2 is an improved variant of DG1 announced for the end of 2021. Internet leaks<sup>1</sup> reveal variants with 128, 256, and 512 EUs. It can be speculated that these high counts of EUs get achieved by multiple slices within a GPU. Assuming the same clock, ALU count, and SIMD width as with the LP series, 3.4 to 13.5 TFlop/s are reachable. However, other leaks state a clock speed of 2.2 GHz, making the DG2 a direct competitor to Nvidia's RTX 3070 in terms of Flop/s.

- **Iris XE HP**: The HP series comes with up to four tiles that could scale performance linearly with the peak one of XE HPG products. Apart from that, no details are known at the time of writing.

- Iris XE HPC: A GPU series with its codename "Ponte Vecchio" is designed to run on supercomputers like SuperMUC-NG (compare Chapter 1) or Aurora. The first details were announced at the HPC Devcon 2019<sup>2</sup>: 16 compute tiles distributed across two blocks combine Rambo cache and I/O link tiles. A total number of EUs was not unveiled so far. Therefore, no assumptions about the ultimate peak performance are viable.

$<sup>^{1}</sup> https://www.tomshardware.com/news/intel-dg2-gpu-specifications-show-serious-potential ^{2} https://www.intel.com/content/www/us/en/events/hpcdevcon/overview.html$

#### 2.1.3. Intel GPUs in HPC

Today, Intel GPUs are not widespread in HPC applications because of their limited performance characteristics. However, there is still research on them. For example, Gera et al. investigate the performance characteristics of Gen9 architecture, showing that these GPUs can reach their peak performance [8]. Deakin and McIntosh-Smith examine Iris Pro 580 Graphics (Gen9) in combination with Sycl [9]. They demonstrate that the peak bandwidth and execution time is equal to OpenCL. Additionally, they show that Sycl can also produce competitive performance compared to native performance models. Li et al. compare the Xeon Phi architecture with an Nvidia Tesla GPU, however, without accessing an integrated graphics chip [10]. Similar has been performed by Theodoro et al. [11]. Christgau and Steinke, on the other hand, perform a closely related work to this thesis: They port their tsunami simulation easyWave from CUDA to Sycl using Intel's compatibility tool, showing acceptable Performance Portability, but also areas for improvements of oneAPI [12]. To the best of the author's knowledge, no other investigations on the available Iris Xe products have been carried out in the area of HPC so far.

### 2.2. Intel GPU Programming

This section discusses programming models for Intel GPUs and compares their syntax by a Saxpy (Single-Precision A·X Plus Y) example and emphasizes features or missing concepts with help of the literature. Starting with the most widely used, OpenMP, it continues with OpenCL, Intel's direct programming concept so far, and ends with the Sycl standard. Its implementations provided by oneAPI and hipSYCL are then selected for the rest of this work.

#### 2.2.1. OpenMP

OpenMP is a standardized language extension for C/C++ and Fortran and allows quick parallelization by parallel regions, work-sharing constructs, or task-based thread scheduling. It is assumed that most readers are familiar with the general concepts of OpenMP. Therefore, the next paragraph focuses on GPU offloading.

Starting from version 4.0, OpenMP can be used to offload code to non-host devices like FPGAs and GPUs with the help of target regions, which are assignable to a device indexed by the OpenMP runtime. Parallel regions within a target region can be nested into teams that create a kernel-like hierarchization into blocks and threads similar to CUDA. However, a runtime system is responsible for distributing work between compute units. There exists a broad variety of compilers, for instance, GCC, Intel CC, or LLVM with Clang, which support OpenMP offloading, making OpenMP highly portable. Appendix A.1 shows a Saxpy benchmark implemented with OpenMP offload, including data mapping of host to device pointers and vice versa. In direct comparison to Sycl or OpenCL, OpenMP can achieve better performance results [9]. Additionally, it could already get close to the peak performance with Intel's Xeon Phi series at an early stage of the offload support [13]. On the other hand, OpenMP can also create higher runtimes in several applications than their native counterparts,

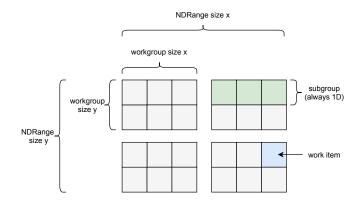

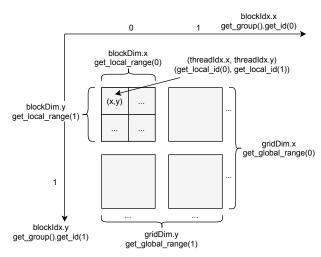

**Figure 2.3:** Example for OpenCL and Sycl kernel indexing. A 2D range of (6,4) groups into four (3,2) workgroups. Each workgroup consists of two subgroups (green) of length three, containing the smallest component, a work item (blue). Note that OpenCL defines global and local ranges for their kernels instead of local block counts and their thread sizes as in CUDA or HIP.

like CUDA [14], and require deep low-level analysis and custom features to tune a code for a specific platform via local shared memory, FMA operations, or register bounds [15]. Because of this and the fact that SeisSol requires these features to minimize the execution time spent on numerical macro kernels, the usage of OpenMP is declined for Intel GPUs in SeisSol.

#### 2.2.2. OpenCL

OpenCL is a cross-platform standard developed by the Khronos Group primarily used for parallel or heterogeneous systems. By the time of writing, version 3.0 is the latest release. In the following, only crucial ideas of OpenCL C are summarized, as the rest of this thesis dives deeper into its concepts with the Sycl abstraction of OpenCL. Further readings are available in the standard [16] or tutorials [17] [18]. The OpenCL standard consists of four models: The platform, memory, execution, and programming model.

The platform model defines a host device (typically a CPU) that is always provided by the runtime. Hence, there is at least one execution environment guaranteed to be available. Additionally, the host acts as a master thread, connecting multiple OpenCL devices that queue so-called commands or command groups. A command, on the other hand, is a small sub-program, mostly called a *kernel*, that gets executed by one of the available devices.

The execution model assigns an n-dimensional index space to a kernel, closely related to blocks and threads in CUDA or teams and threads in OpenMP. This hierarchical structure is called an NDRange (N-dimensional range) and is used to distribute work to hardware threads of a device. For common OpenCL devices like GPUs, N is limited to three dimensions. An NDRange structures itself into workgroups (blocks/teams) consisting of work items (threads) performing the actual work. Therefore, the global NDRange equals the count of workgroups times the size of each one. Figure 2.2.2 illustrates this idea using a 2D range of size (6,4). There is also an intermediate 1D structure between workgroups and work items, called subgroups. Subgroups were introduced in version 2.0 of the standard and are used to cluster work items and assign them to a single hardware thread (comparable to a SIMD lane). However, as they do not impact this work, further readings are referred to [19].

The memory model defines three main types of memory: Private memory is only visible to a single work item, whereas local memory gets shared within a workgroup. Finally,

#### 2. Fundamentals

there is global memory accessible by a complete NDRange. For Intel GPUs, these memories are mapped with the same memory available in the hardware (compare Figure 2.2 in the last section). OpenCL also allows declaring global memory as so-called unified shared or host memory. Unified shared memory is managed by the runtime and gets automatically transferred between host and device via page fault mechanisms when accessed. On the contrary, host memory follows the same idea, but data is transferred via a PCI-E bus and does not migrate back from the device.

A combination of the discussed three models results in the OpenCL programming model available by the OpenCL framework. Traditionally, this model is expressed with the C programming language, but a C++ extension is also available [20]. Various vendors provide OpenCL for their products, including Nvidia and Intel, resulting in good portability. Additionally, Fang et al. showed that OpenCL gets similar performance results as CUDA under fair condition [21]. Nevertheless, OpenCL is not used to port SeisSol for Intel GPUs for three reasons: Firstly, OpenCL C comes with a large overhead of boilerplate code, which makes dynamic code generation cumbersome. That issue is furthermore emphasized by the necessity to separate kernel and host code. Due to the length of an OpenCL code, no example is provided in the appendix of this work, but it is referred to the book of Ravishekhar and Bhattacharyya, where Saxpy is implemented in Chapter 1 [18] and stays exemplary for these concerns. Secondly, there is a modern C++17 programming abstraction to OpenCL called Sycl that recently received new attention with Intel's oneAPI platform. oneAPI contains a Sycl compiler called *data-parallel c++* (dpcpp), available in both a packaged and open-source variant, that already received good results while porting CUDA code to Intel's own products [12]. Therefore, it is believed that the performance gap between Sycl and OpenCL or OpenMP, like reported by Silvia et al. [22], will minimize or not apply to Intel's software stack in the future. Thirdly, Sycl today allows different backends than OpenCL, for example, CUDA, which allows to create native applications.

#### 2.2.3. Sycl

Sycl [23] is another Khronos standard, initially designed on top of the OpenCL backend. However, as mentioned in the section before, it also allows different backends like CUDA, increasing portability by reducing dependencies on OpenCL. Sycl is a fully C++17 conform standard, which means that no additional syntactical extension is needed to create and launch a kernel, but only Sycl libraries. With its single-source approach (device and host code are mixable), Sycl can highly reduce lines of code within a program, speed up development time, and improve the readability of heterogeneous code [24]. Due to its relation to OpenCL, Sycl follows the same models. Thus, all explanations of platform, execution, and memory from the previous section also apply to Sycl. Obviously, the programming model deviates as OpenCL C can't access C++ features like lambdas or template functions. Listing A.2 implements a Saxpy benchmark using Sycl and raw C pointers. In direct comparison to OpenCL, the brevity and conciseness of the Sycl code can be highlighted, assuming the reader is familiar with C++ lambda expressions. If not, introductory works to Sycl help to explain this part in detail [25]. By the time of writing, there exist at least four Sycl implementations, including Codeplay's ComputeC++, Xilinx's TriSYCL, hipSYCL provided by the University of Heidelberg [26], and Intel's oneAPI. For this thesis, hipSYCL and oneAPI are selected as development platforms for three reasons: Firstly, both are open-source available and installable on HPC machines without additional configuration. For hipSYCL, there is also a spack package available, adding more convenience to test setups like used in this work. Spack is an HPC package manager, which installs an application and all its dependencies from source code, which is important as the targeted test systems do not allow changes without administrative access. Secondly, both of them support CUDA as code backend, which is used to ensure the correctness of SeisSol by comparing the results obtained with Sycl with the native CUDA ones. Thirdly, and most importantly, it is expected that Intel's Sycl compiler is highly tuned for Intel devices, and therefore will be available on all HPC systems that employ Intel GPUs like the "Ponte Vecchio". Hence, evaluations using oneAPI should create an outlook on what is expectable in the future in terms of performance results.

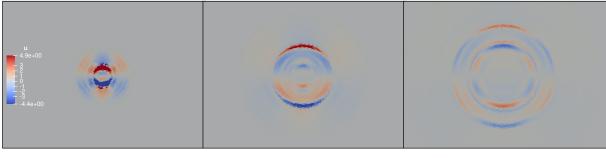

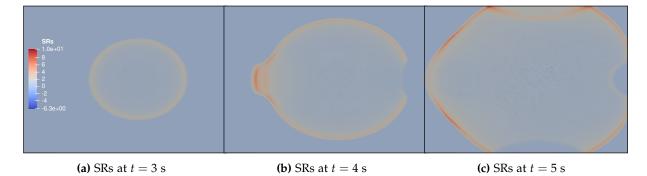

### 2.3. SeisSol

SeisSol is an open-source "scientific software for the numerical simulation of seismic wave phenomena and earthquake dynamics"<sup>3</sup>. An example of a real-world application of SeisSol is the 1994 Northbridge or the 2004 Sumatra-Andaman earthquake. This section introduces SeisSol and its heterogeneous components by providing an overview of its numerical scheme build upon a High-Order Discontinuous Galerkin (DG) method using ADER time integration and Local or Global Time Stepping (LTS/GTS). Hence, the necessity of small GEMM kernels generated during compilation is justified. The subsequent section provides a big picture of SeisSol's heterogeneous components distributed to three libraries, namely, Device, Yateto, and GemmForge that are analyzed and extended in Chapter 3 with Sycl compliant code. The last section defines the term Performance Portability and how it is applied in this thesis.

#### 2.3.1. Numerical Scheme

SeisSol provides a numerical solver for the three-dimensional elastic wave equation driven by velocities and stresses. This can be modeled by a system of linear hyperbolic Partial Differential Equations (PDEs) as expressed in Equation 2.1.

$$\frac{\partial q}{\partial t} + A(s)\frac{\partial q}{\partial x} + B(s)\frac{\partial q}{\partial y} + C(s)\frac{\partial q}{\partial z} = 0$$

(2.1)

$q(s,t) = (\sigma_{xx}, \sigma_{yy}, \sigma_{zz}, \sigma_{xy}, \sigma_{yx}, \sigma_{xz}, u, v, w)$  is a nine-component vector containing stresses  $\sigma_{ij}$  and particle velocities u, v, w in the Cartesian space  $s = (x, y, z) \in \mathbb{R}^3$ . A stress  $\sigma_{ij}$  determines the force on a plane *i* within a body in direction *j*. *A*, *B*, *C* are space-dependent Jacobi matrices adding the Lamé parameters  $\lambda$  and  $\sigma$  as well as the mass density  $\rho$ . The Lamé parameters are used to define the relationship between stress and strain in elastic deformation.

<sup>&</sup>lt;sup>3</sup>http://www.seissol.org/

SeisSol uses a Discontinuous Galerkin (DG) method for spatial discretization. In the DG method, 2.1 is transformed into its weak form by multiplying it with test functions  $\Phi$  and integrating it over the domain  $\Omega$ . The result is then semi-discretized into finite elements  $\Omega_k$  that present a new state in a time step and are linked by a numerical flux. SeisSol applies an adaptive grid of tetrahedral meshes, allowing to vary the mesh size depending on the importance of geological regions. Additionally, SeisSol combines the DG method with the ADER scheme for time discretization as described by Käser and Dumbser [27] [28] which leads to a high-order representation of  $\hat{Q}$  at each time step  $t_n$  of tetrahedron  $\Omega_k$  shown in Equation 2.2. Note that the following descriptions are based and summarized on the work of Heinecke et al. [1].

$$\hat{Q}_{k}^{n}(s) = (\phi_{1}, ..., \phi_{B_{O}})(\xi(s))Q_{k}^{n}$$

(2.2)

This equation combines orthogonal polynomial basis functions  $\phi_j(\xi)$ ,  $j \in 1, ..., B_O$ , which are space-dependent, and time-dependent degrees of freedom  $Q_k^n \in \mathbb{R}^{B_O \times 9}$ . The count of bases  $B_O$  is determined by the convergence order O. A typical size for O is six, resulting in  $B_6 = 56$  basis functions. Therefore, this characteristic size is used later in the benchmarks for a Roofline Model analysis.  $\xi$  is a translation of an arbitrary Cartesian coordinate s = (x, y, z)into a reference point, here a tetrahedron of a mesh. The fully discretized update scheme in SeisSol for a degree of freedom at time  $t_{n+1} = t_n + \Delta t$  based on  $Q_k^n$  is provided in Equation 2.3.

$$Q_k^{n+1} = Q_k^n + V_k - \sum_{i=1}^4 F_{k,i}$$

(2.3)

Note that if the time steps  $\Delta t$  are equally for every tetrahedron, one speaks of Global Stepping (GTS), but also individual values are allowed (Local Time Stepping, LTS). The partitioning of tetrahedrons into equivalent time steps is one of the key ideas of SeisSol

The heart of the update scheme form *Compute Kernels* denoted as *V*, *F*, consisting of tensor operations and depending on time  $T_k^{n,\Delta t}$ . That explains and justifies the focus of this work on optimizing that part of SeisSol's numerical scheme, as these kernels are executed enormously often, depending on the simulated time and count of tetrahedrons in the mesh. Some of them are illuminated in the following to emphasize these considerations. More detailed explanations can be found in previous work [29].

$T_k^{n,\Delta t}$  describes the *Time Kernel* and approximates time-predicted values of the degrees of freedom in  $[t_n, t_{n+1}]$  of a tetrahedron k by a Taylor expansion. The time derivatives of this expansion are expressed by a recursive scheme using multiplication of stiffness matrices, mass matrices, the previous result of the recursion, and a linear combination  $\in \mathbb{R}^{9 \times 9}$  of A, B, C.

$V_k$  describes the *Volume Kernel* depending on  $T_k^{n,\Delta t}$ , following a similar scheme as the time derivatives of it.

$F^{k,i}$  expresses the numerical *Flux Kernel* for a tetrahedron  $\Omega_k$  over its faces i = 1, ..., 4 depending on  $T_k^{n,\Delta t}$ . Again, there are tensor operations by multiplying unique flux matrices, face-local matrices, and the time kernel *T*. For completeness, *F* can also express the *Dynamic Rupture Kernel* or boundary conditions, which are explained in detail in preceded work [29].

#### 2.3.2. Heterogeneous Components

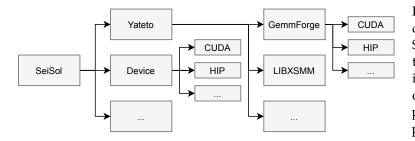

The last subsection summarized the underlying numerical scheme and how it is expressed by tensor operations. Considering SeisSol and GPUs, these are implemented by three modules, as illustrated in Figure 2.4, that together enable GPU access: Yateto, GemmForge, and Device. Device is essentially a primary API endpoint to prepare and synchronize computations of the numerical scheme. Yateto generates code to express tensor operations with GEMM operations and corresponding calls GEMM libraries under the assumption of using it in the context of an ADER-DG method. GemmForge, on the other hand, implements GEMM code generation for GPUs, until now only using CUDA and HIP, and leverages performance by exploiting knowledge of the application domain. One main advantage of this design is that one does not need to change code within SeisSol if adding a new accelerator API. In the following, the most important aspects of all repositories are illuminated and how they apply to Intel GPUs. Chapter 3 then use this information to analyze and implement necessary changes.

**Figure 2.4:** Summary of the crucial heterogeneous components in SeisSol: Yateto provides a DSL to express the numerical scheme implemented by GemmForge or other GEMM libraries. Device presents a facade to a typical GPU programming model like Sycl.

#### Device

Device<sup>4</sup> implements Facade [30] and Adapter [30] design patterns for accelerator accesses. It provides an API abstracting common GPU programming concepts, including memory allocation, copying data from or to the device, and synchronization, but also a custom stack on the global memory of a device and a stream buffer for out-of-order tasks. Additionally, there is a sub-interface for common GPU algorithms containing data initialization and scaling, reduction, and batched array manipulation<sup>5</sup>. As stated in Chapter 1, there have been implementations of this facade in CUDA [2] and HIP [3] so far. For Intel GPUs, a new adaptee needs to be implemented in Sycl.

Device is primarily an API to prepare and finalize data for GEMMs but is also responsible for synchronizing kernels and balance a workload to queues. SeisSol already calls all methods of the facade in the right order and produces numerical correct results with the CUDA implementation [2]. Therefore, if the Sycl implementation behaves exactly like the CUDA one, the results must be logically correct. A deeper analysis of what that means for the implementation is available in Chapter 3. Moreover, the repository contains a parallel Jacobi benchmark and several test suites that can be used or extended to ensure correctness and

<sup>&</sup>lt;sup>4</sup>https://github.com/SeisSol/Device

<sup>&</sup>lt;sup>5</sup>A batched array is considered as a contiguously allocated area of memory containing logically separated containers.

for evaluation. The benchmark is implemented with an MPI+X model, where X can be any GPU programming model or language wrapped by Device. Thereby, it may demonstrate that the targeted MPI implementation is Intel-GPU aware. This is especially important, as SeisSol relies on the same design idea and does not work without GPU-aware MPI.

#### Yateto

Yateto<sup>6</sup> (Yet Another Tensor Toolbox) is a code generator, providing a domain-specific language (DSL) to express tensor operations [4]. Yateto was explicitly designed for generating kernels establishing them via 2D tensor (or GEMM) operations used in Partial Differential Equation (PDE) solvers, particularly in the ADER-DG method. Because of this, it is possible to reason about generated kernels executing on hardware, which does not apply to a generalized code generator. This includes, for example, that most matrices fit into low-level caches or that all dimensions stay fixed during runtime. Moreover, the application context immediately justifies the focus of optimizing these operations as they are the building block of solving the ADER-DG scheme. Yateto delegates the generation of kernels to GEMM libraries, for instance, LIBXSMM<sup>7</sup>, targeting SIMD Intel CPU architectures, or GemmForge, targeting Nvidia [2] and AMD GPUs [3]. For GPUs in general, Yateto allows passing batched GEMMs, increasing the time data remains on a GPU. A batched GEMM operation is defined in Equation 2.4 and summarized based on previous work [2].

$$C_e = \alpha \cdot Op(A_d) \cdot Op(B_f) + \beta \cdot C_e \tag{2.4}$$

*A*, *B*, *C* are real matrices such that Matrix-Matrix-Multiplication is defined. *e* is the index of the current batch operation, *d* is either *e* or omitted if *A* is constant throughout the batches. The same holds for *f* and *B*. Op(M) is either  $M^T$  or *M*. Note that two special cases of GEMMs, Copy-Scaled-Add (CSA) and initialization, are treated individually by Yateto, which becomes important when changing GemmForge later in this thesis. Additionally, note that all matrices are stored in column-major forward due to the origin of SeisSol in Fortran.

Considering Intel GPUs, Yateto does not need major changes, as the current design already allows to switch between the AMD and Nvidia GPU architectures. Therefore, the rest of this thesis does not focus on Yateto and assumes that an additional option for Intel GPUs is already available.

#### GemmForge

GemmForge<sup>8</sup> is SeisSol's code generator for batched GEMM operations on a GPU, as mentioned in the section before. GemmForge allows specifying a GPU architecture, which is passed to a GEMM, CSA, or initialization code generator. Exploiting the programming model of the target architecture, the code is generated following the same optimization ideas on any GPU model, which are summarized in the following based on preceded work [2].

<sup>&</sup>lt;sup>6</sup>https://github.com/SeisSol/yateto

<sup>&</sup>lt;sup>7</sup>https://github.com/hfp/libxsmm

$<sup>^{8} \</sup>tt https://github.com/ravil-mobile/gemmforge$

Inspired by Rivera et al. [31], GemmForge splits a single matrix-matrix multiplication into a sum of outer products, distributed parallelly to up to three Nvidia warps. Dorozhinskii and Bader denote these as *team*, and the first *m* threads of a team *active threads*. The size of a team is determined by the count of rows of  $Op(A_d)$ . Each load or store of any column (recall the column-major layout of SeisSol) of *A* or *C* by a team then leads to coalesced memory access. Furthermore, each active thread loads one element of the same column of *A* into a register and combines it with a row of matrix *B*, which is loaded into the shared memory of a GPU. At the beginning of a kernel execution, intermediate results of a multiplication are stored in registers and copied back to global memory at the end of the entire product. These resulting fine-tuned kernels are further optimized by loop-unrolling and CUDAs launch\_bounds hint for the compiler, limiting the number of registers per thread to avoid register spilling.

Evaluating these techniques, the CUDA implementation of GemmForge outperforms native HPC libraries like cuBLAS<sup>9</sup> and can reach the theoretical peak performance of a GPU [2]. This is attributable to the fact that these types of kernels are 1) memory bound and 2) allow the techniques as described above due to the known structure of the matrices at runtime. This does not apply to general GEMMs like those processed by cuBLAS. GemmForge's HIP implementation follows the same ideas and also gets close to peak performance [3].

Regarding Intel GPUs, the architectural layer of the code generation has to be extended to include object-oriented concepts of C++ and to skip optimizations that are not expressible by Sycl (like register limitations). However, no specialized GEMM implementations for Sycl are created in this work as there is not much experience on performance characteristics of Intel GPUs in the literature yet. Instead, the existing technique as described above is employed, even though it might not be optimal for Intel GPUs in general. The correctness of the implementation is ensured by an existing test-suite for GEMM operations and new suites for CSA and initialization created in this work. The next section summarizes how the described changes and evaluations for Sycl and Intel GPUs refer to Performance Portability.

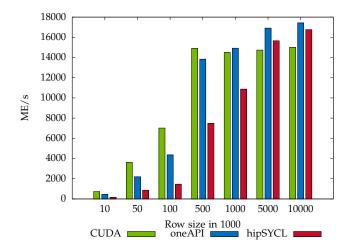

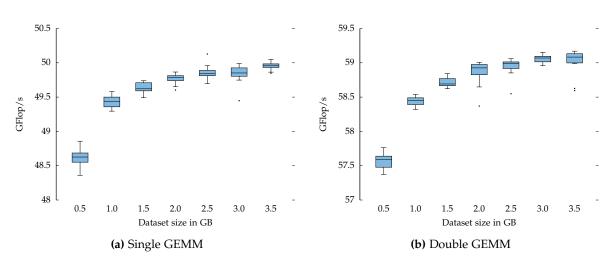

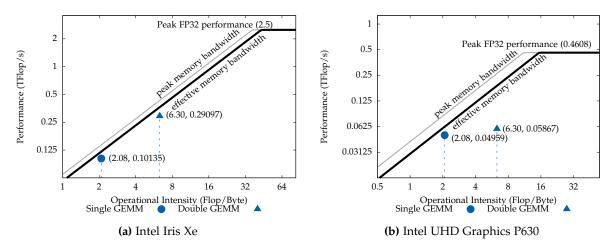

#### 2.3.3. Performance Portability

Performance Portability is a non-standardized term in computer science for a) providing a correct piece of software to a new platform and b) evaluating performance relative to the new underlying architecture at once. Pennycook et al. define Performance portability as follows: Performance Portability is "a measurement of an application's performance efficiency for a given problem that can be executed correctly on all platforms in a given set" [32]. This work stays to a single problem on two platforms for Performance Portability: A single and a double GEMM benchmark provided by GemmForge, that maps to a compute kernel solved by SeisSol in a typical setup and runs on an Iris Xe Max, Gen9 UHD Graphics P630, and Nvidia RTX 3090. Therefore, the suggested metric of their work is not applied. Instead, evaluations of performance results are performed directly by a Roofline Model analysis [33].

A Roofline Model is a visualization for performance characteristics of both a device and an algorithm. It plots operational intensity (in floating-point operations per byte) against

<sup>&</sup>lt;sup>9</sup>https://docs.nvidia.com/cuda/cublas/index.html

measured performance (in Flop/s) of an algorithm, thus showing if its performance is either memory-bound (i.e. limited by the bandwidth) or compute-bound (i.e. limited by the count of operations a CPU can execute per cycle). An operational intensity can be received by hardware performance counters or estimated by dividing the numbers of Flops by the count of bytes processed in the algorithm. On the other hand, the theoretical peak performance on both labels is retrieved either with the specification of a device or by microbenchmarks. The latter can create fairer conditions for GPUs, as the theoretical bandwidth is not achievable by default floating-point data types. The closer an algorithm gets to these peak performances, the more efficient it uses the underlying hardware.

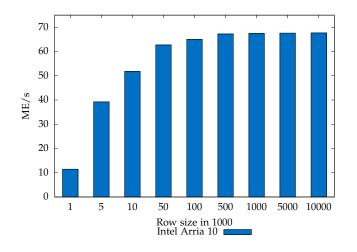

For the parallel Jacobi and SeisSol itself, benchmarks provided by these applications are executed on the two Intel GPUs, a single Intel Arria 10, and a compute cluster containing two Nvidia RTX 3090. Chapter 4 introduces the execution environments as well as the parameter and the output of the algorithms in detail.

# 3. Analysis and Design

The last chapter introduced SeisSol's heterogeneous components, Yateto, Device, and Gemm-Forge, and gave an idea of what changes are required to support Intel GPUs with the Sycl programming model. This chapter analyzes Device and GemmForge in detail and designs a new implementation using the existing CUDA code as a template such that the Sycl code is functionally equivalent to it. Next, important implementation details are provided, for example, individual reductions for both hipSYCL and oneAPI, and the correctness of all changes is ensured by various test suites.

### 3.1. Device

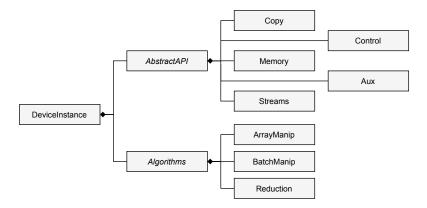

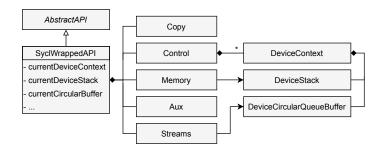

Device provides a Singleton [30] interface facade for an arbitrary accelerator API and common GPU algorithms. Figure 3.1 shows a higher-level overview of the structure of its CUDA implementation, which is summarized in the following.

**Figure 3.1:** Structure of CUDA components of Device. AbstractAPI hides the implementation of native features like data transfer in Copy or custom ones like a GPU stack provided by Memory. Algorithms encapsulates typical parallel algorithms like reduction.

Memory implements the allocation and deletion of global, shared, and page-locked memory. Additionally, it includes a custom GPU stack on the global memory used for quick data access in SeisSol's compute kernels with push and pop operations. Copy transfers 1D or padded 2D data from a host to a device or vice versa, either synchronously or asynchronously. Streams maintains CUDA device streams which are similar to a kernel queue in Sycl, allowing to introduce further levels of parallelism. All streams are ordered and managed by a circular queue buffer implemented by Streams. Control initializes and selects a CUDA device by a certain id number and synchronizes it. Aux contains a test kernel and a method for error checking.

ArrayManip and BatchManip are parts of the Algorithms component and implement shortcut methods for batched or non-batched array initialization and scaling, whereas Reduction aggregates an array depending on an arithmetic operator.

In the following subsections, this architecture is used as a template for the Sycl implementation. They answer, which design concepts of Sycl are different and why they prevent performing an automatic conversion, for example with Intel's compatibility tool<sup>1</sup>. For that, CUDA API is compared with Sycl API, and inconsistencies between the programming models are extracted. Subsequently, changes in the architecture (compared to Figure 3.1) are designed, implemented, and verified.

#### 3.1.1. CUDA compared to Sycl

This subsection illuminates differences and similarities between CUDA and Sycl needed for designing the Sycl implementation of Device and, later in the chapter, GemmForge. These considerations remain with the most crucial aspects received by the author's experience during this work. Note that there are more ways to express aspects from one language within the other, for example, explicit device management in CUDA or subgroups in Sycl. However, as they do not play a role in later changes, they are not consulted in the following explanations based on CodePlay's migration guide<sup>2</sup>.

One difference between Sycl and CUDA is that Sycl is designed to access arbitrary devices, whereas CUDA is not. That already leads to a break in the programming concepts: As described in Section 2.2.2, the Sycl platform model holds next to a host device all other devices (for example, CPUs or FPGAs) that are accessible. Therefore, in Sycl, a programmer is responsible for selecting a GPU over all other devices. In CUDA, there is no need for such filtering, as only Nvidia GPUs are available. Furthermore, CUDA automatically detects and provides the best device on a machine. Sycl needs a device selector or a lookup of the underlying platforms to express the same concept.

Next, CUDA has a global static context presented by the runtime. Therefore, launching a kernel does not require calling any C++ objects or holding a context like a Sycl queue. Additionally, kernels in CUDA per default execute on a default stream, i.e., passing a stream explicitly to a kernel is not necessary for CUDA. Sycl does not have such implicit queuing. Furthermore, Sycl streams are per default out-of-order, which means that any kernel passed to a queue can be executed in any order. That is not the case with CUDA, where streams are in-order.

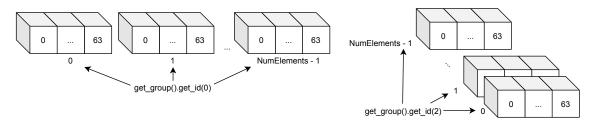

The index space of CUDA is very similar to Sycl except in terms of notation. In CUDA, for example, a work item is called a *thread*, a work-group a *block*, and an NDRange a *grid*. Calculations of a global thread index in Sycl follow the same regulations as in CUDA in all dimensions, but Sycl also has convenient functions and objects to circumvent these computations. An example for 1D indexing using CUDA and a verbose and abbreviated variant in Sycl is provided in Equation 3.1 to 3.3. On the other hand, Figure 3.2 compares CUDA and Sycl 2D index space labeled with method calls necessary to access the information.

<sup>&</sup>lt;sup>1</sup>https://software.intel.com/content/www/us/en/develop/tools/oneapi/components/dpc-compatibili ty-tool.html

<sup>&</sup>lt;sup>2</sup>https://developer.codeplay.com/products/computecpp/ce/guides/sycl-for-cuda-developers/migrat ion

Note that both the figure and equation assume that all Sycl calls are performed on an nd\_item within a kernel function. For CUDA, the same is asserted but without the need for the latter.

$$blockIdx.x \cdot blockDim.x + threadIdx.x$$

(3.1)

$$\equiv get\_group().get\_id(0) \cdot get\_local\_range(0) + get\_local\_id(0)$$

(3.2)

$$\equiv$$

get\_global\_id(0)

However, one essential difference is the way how the index space is created in both programming models. A CUDA kernel launcher requires a specification of  $m_k$  blocks and  $n_k$  threads per dimension k. That results during runtime in a grid size of  $m_k \times n_k$ , or  $m_k$  blocks of size  $n_k$ . Sycl reverses this idea: A kernel function takes a (global) NDRange (or grid in the CUDA terms) of size  $m_k \times n_k$  per dimension and a local size  $n_k$  of all workgroups (blocks). This difference of launching a kernel index has to be considered while porting CUDA to Sycl code.

CUDA and Sycl share the same ideas regarding the memory model as described in Section 2.2.2 but express it with different syntax. For example, shared memory can be allocated within a kernel in CUDA but outside of a kernel in Sycl. Nevertheless, Sycl allows two different data management strategies: Raw C pointers, which are unconstrained accessible via pointer arithmetics, and memory buffers. Memory buffers provide an abstraction of memory and are fully maintained by the Sycl runtime. They are not directly accessible by index operators but rather with an accessor object. Buffers and accessors in combination with out-of-order queues enable the Sycl runtime to build dependency graphs. Similar to OpenMP tasking, Sycl can then schedule kernels with this graph and may add more parallelism.

Furthermore, CUDA default memory copy operations are synchronous, whereas asynchronous ones require a different set of func-

(3.3)

**Figure 3.2.:** CUDA (first line) and Sycl (second line) indexing in comparison for a 2D index space. Except for different wording and additional object hierarchies in Sycl, both follow the same design idea. Note that all methods must be called within a kernel. Sycl additionally requires to call the methods on an nd\_item.

tions. In Sycl, those operations need to be submitted on a queue when using raw pointers. Any queuing in Sycl returns an event that is executed asynchronously and can be waited for. Alternatively, there are wait operations on a queue that synchronize it completely with the host. However, synchronizing a single queue does not synchronize the complete device, as there can be multiple queues per device. Comparing to CUDA, synchronizing Nvidia GPUs is commonly performed either per device completely or per single stream.

### 3.1.2. Design and Implementation

Using the CUDA architecture as a template and aware of the discrepancies and similarities between both programming languages, the Sycl part of Device is designed and implemented as follows:

- A container class called DeviceContext is created, which is instantiated during the initialization phase of the Control component and filled with each available definition of a concrete accelerator installed at a given system. However, to enable GPU-aware MPI, all non-level zero backends are excluded regarding Intel GPUs, as it is only available on the latter one. The filled vector is sorted by a newly introduced environment variable, PREFERRED\_DEVICE\_TYPE, requiring a value of either GPU, CPU, or FPGA. This allows to set and switch devices at runtime by an index: Because the context class holds all references that are specific per device (like the queue buffer or the stack), pointers to them are updated once a device was changed. Nevertheless, it is still a user's responsibility to distribute the work to the maximum count of the same device types.

- For reasons of the Single-Responsibility principle of Software Engineering, dedicated classes Stack and DeviceCircularStreamBuffer are created, instead of including them directly in Memory or Stream. Note that all queues in the buffer are created in-order.

- All data managements in Memory or Copy are handled via C raw pointers instead of buffers. Buffers are great for automatic dependency management, but this is not a use-case for SeisSol and therefore, they are not used for this work. Additionally, omitting buffers reduces the overhead which is caused by the runtime with them.

- Furthermore, any memory copy operations are synchronized, except if methods are explicitly marked as asynchronous. Additionally, to the best of the author's knowledge, there are no 2D memory copy operations for strided memory transfer in Sycl. Due to that, they are implemented manually via a for-loop.

- Any kernel indexing in Algorithms is directly converted using Figure 3.2. The global kernel index space is created by multiplying CUDA blocks and threads in every dimension, whereas the local range inherits CUDA block size.

- Instead of checking error codes as returned from CUDA API, an asynchronous exception handler is passed to any queue. Furthermore, all assertions on the integrity of a method are expressed with exceptions.

- Two implementations of Reduction are provided: The first one bases on the Sycl reduction library implemented by oneAPI. The second one is a custom implementation for platforms like hipSYCL that do not implement this part of the standard.

- The build system compiles all Sycl code with O3 optimization. Furthermore, Ahead-of-Time (AoT) compilation is activated if any preferred device is set. That can increase the performance of a kernel as it does not have to be assembled at runtime via Just-In-Time

compilation. Additionally, AoT compilation is mandatory for FPGAs. All other changes in the build files are excluded here but are available at the public GitHub repository for interested readers.

Appendix A.3 shows an updated Figure 3.1 that summarizes the design changes in the API component regarding Sycl based on the descriptions above.

#### 3.1.3. Correctness

Correctness of the implementation is ensured by three examples and test suites. The first example submits a test kernel and transfers mock data between the host and a device, whereas the second example is an *HelloWorld* test for GPU-aware MPI. For both tests, a limitation was encountered on a local Intel HD Graphics 620. It does not have hardware support for double-precision floating points. These types are only supported if IGC\_EnableDPEmulation environment variable is set to 1. The same holds for the Iris Xe Max GPU<sup>3</sup>. However, this does not impact SeisSol, as the precision is definable at compile-time. Both tests pass their requirements on the local HD Graphics P620, but note that Intel MPI requires setting I\_MPI\_OFFLOAD environment variable to 2 before running MPI with device pointers.

The parallel Jacobi benchmark is a more complex example implemented for CPUs and GPUs, which is summarized based on preceded work [3] in the following. It approximates a solution of a system of diagonal-dominant linear equations Ax = b by converging to a fixpoint given by  $\phi(x_k) = x_k + M^{-1}r$ . *M* contains diagonal elements of *A*, and  $r = b - Ax_k$  is the residual value of a current convergence step. The implementation in the repository splits computations of matrix-vector products and distributes these across all MPI ranks. Each rank is assigned to a single GPU. Intermediate and final results are propagated with MPI collectives. For reproducibility, the benchmark uses a fixed band matrix *A*, solution vector *x* and initial approximation  $x_0$  stated in Equation 3.4. Additionally, the maximum error is set to  $\epsilon = 10^{-7}$ .

$$A = \begin{pmatrix} 2 & -1 & 0 & 0 & 0 & 0 \\ -1 & 2 & -1 & \dots & 0 & 0 & 0 \\ 0 & -1 & 2 & 0 & 0 & 0 \\ \vdots & & \ddots & & \vdots & \\ 0 & 0 & 0 & 2 & -1 & 0 \\ 0 & 0 & 0 & \dots & -1 & 2 & -1 \\ 0 & 0 & 0 & 0 & -1 & 2 \end{pmatrix}, x_0 = \begin{pmatrix} -10 \\ \vdots \\ -10 \end{pmatrix}, x = \begin{pmatrix} -1 \\ \vdots \\ -1 \end{pmatrix}$$

(3.4)

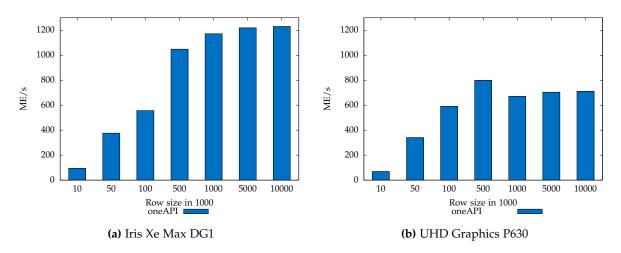

Running this example on Intel HD Graphics P620 and one or two Iris Xe Max with row sizes  $\{10^k | k = 3, 4, 5, 6, 7\} \cup \{5 \cdot 10^k | k = 3, 4, 5, 6\}$  of *A* using oneAPI in the packaged version result in equal outcomes using Intel MPI, indicating that the Sycl implementation is correct and Intel GPU-aware MPI works. Similar experiments were performed using native CUDA,

<sup>&</sup>lt;sup>3</sup>https://community.intel.com/t5/Intel-DevCloud/Iris-Xe-MAX-node-is-missing-double-precision-s upport/td-p/1247876?profile.language=de

oneAPI (open-source), and hipSYCL with one and two RTX 3090 and OpenMPI without UCX layer. The same results were obtained with that setup, as well.

Last, all available tests for the Reduction part of the algorithms library were executed. Additionally, they were extended by suites for the custom implementation of 2D memory copy as well as tests for array manipulations. As all tests are passing, the correctness of Algorithms is also verified under the assumption that they do not contain errors.

### 3.2. GemmForge

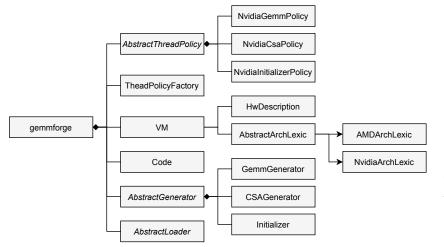

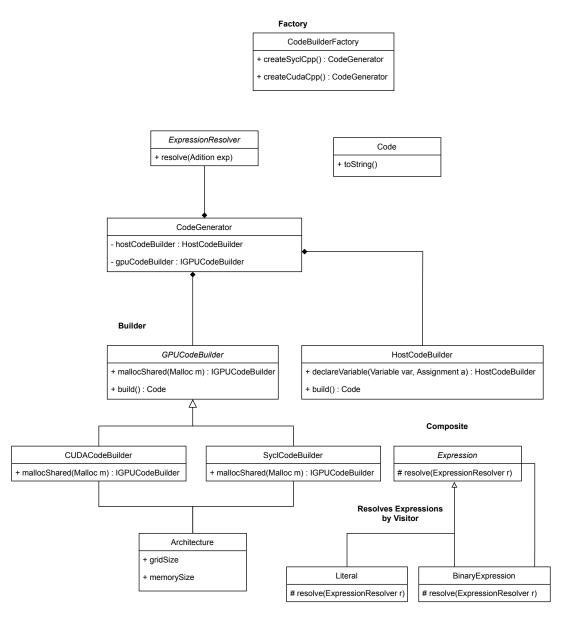

GemmForge is a Python module for generating batched GEMM kernels as introduced in Section 2.3.2. Parallel to this thesis, GemmForge was redesigned by the community compared to its original structure described by Dorozhinskii [2]. The following section always refers to the design provided by the tag v0.0.204, for which Figure 3.3 shows a truncated overview of its architecture.

Figure 3.3: Architectural style of GemmForge. VM stores important hardware details of a vendor model. AbstractThreadPolicy defines a strategy to create a kernel index space. AbstractGenerator and AbstractLoader generate batched GEMM kernels with the help of the Code dictionary.

VM is a container class for a GPU vendor. It contains HwDescription storing hardware details like the size of shared memory or the maximum count of threads for a GPU model. AbstractArchLexic is a facade for vendor-specific language syntax used by the code generators. AbstractThreadPolicy is a Strategy Pattern [30] exploiting these data to define an indexing space of a kernel. Default policies are specific for Nvidia GPUs created by a Factory [30] class but can be extended for other GPU manufacturers. AbstractGenerator and AbstractLoader are base classes for batched GEMM code generation as described in Section 2.3.2. AbstractGenerator analyzes the underlying VM and thread policy to create a kernel launcher, a kernel itself, and a belonging header. AbstractLoader is a sub-generator for loading data into shared memory. Code serves as a dictionary for C++ code generation. CSAGenerator, GemmGenerator, and Initializer are the respective generator implementations.

One issue thereby is that the GemmForge implementation is tailored to CUDA and HIP. HIP and CUDA share almost all programming concepts except for minor syntactical differences.

Therefore, only the bare necessities like thread indexing within a kernel are abstracted in AbstractArchLexic. Other concepts like launching kernels, creating an index space with dimension objects, or synchronization within a block are not abstracted, resulting in a nondisjoint separation between GPU and host code. The following section discusses two designs that change the architecture of GemmForge such that GPU and host code are fully separated.

#### 3.2.1. Design

The main challenge of GemmForge design is to eliminate mutually exclusive concepts in CUDA and Sycl that are difficult to generalize and that prevent to solely add a third implementation to AbstractArchLexic. For example, declaration of shared memory in CUDA takes place within a kernel but in Sycl outside of it. Or: Sycl kernels are typically expressed with anonymous lambda methods, whereas CUDA uses functions labeled with a language extension. All these discrepancies are not issues in Device, where each implementation is isolated from the other ones.

To tackle these problems, two design options are considered: The first one targets to completely refactor all three generators by introducing a Composite Pattern [30] in combination with GPU and host code Builders [30] to express a formal grammar for each programming language. That design implements a fully GEMM-independent code generation package for default C++, CUDA, HIP, and Sycl code. Furthermore, Sycl and CUDA code is interchangeable and allows transferring CUDA to Sycl step-by-step, if necessary. Appendix A.4 emphasizes these ideas by a class diagram.

The second design aims to add more levels of abstraction into AbstractArchLexic and move all GPU-specific code to overridden methods of derived classes. At the same time, all non-shared information needed during the generation phase in the parameters of such a method is unified. For example, the method in AbstractGenerator, which creates a kernel, is extended by a count of requested local memory. This parameter then acts as an offer that can be consumed or not. In this case, SyclArchLexic can use this hint to declare the local memory during the kernel setup, whereas NvidiaArchLexic ignores it. Moreover, the same parameter is passed to a standalone version for creating local memory within the kernel code. The CUDA architecture lexicon accepts this parameter, whereas the Sycl one, on the other hand, skips that method completely.

This work follows the second variant for the following reason: The first design requires a complete re-implementation of GemmForge with a complex structure of many different classes implementing the Composite and Code Builder patterns. An experimental setup<sup>4</sup> using C# confirms any concerns on this. Therefore, and due to uncertainties accompanying that design regarding time limitations, the ideas of redesigning GemmForge were discarded.

<sup>&</sup>lt;sup>4</sup>https://github.com/ZaubererHaft/GemmForge-Experimental

#### 3.2.2. Implementation

At the chosen design, a new architecture lexicon SyclArchLexic is added and all GPU-specific method calls in the generators are deferred to AbstractArchLexic or Code. Furthermore, the existing methods are extended with offers to mutually exclusive concepts discarded or consumed by vendor-specific implementations as described in the section before. Additionally, passing a non-null stream or queue pointer as a parameter is asserted in the generated kernel launcher. Hence, the method always gets the right context where to submit a GEMM operation. So far, this was either null or a stream from the CircularBuffer of the Device submodule passed as a parameter by SeisSol. Within CUDA a null (or zero) stream is valid for a kernel launcher, as it resembles the default stream. Using Sycl, one can't make assumptions about a device and need a correct platform chosen by Device (compare Section 3.1.1). Figure 3.4 illustrates the solution to that problem by a shortened kernel launcher generated by GemmForge. Initially, the change broke the compatibility to SeisSol, but a fix was provided by the community during this work, such that SeisSol always passes a stream that is different from null.

| <pre>void gemm(const float * A, const float * B,</pre>                                | <pre>void gemm(const float * A, const float * B,</pre>                 |

|---------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| <pre>float * C, unsigned NumElements,</pre>                                           | <pre>float * C, unsigned NumElements,</pre>                            |

| <pre>void* streamPtr) {</pre>                                                         | <pre>void* streamPtr) {</pre>                                          |

| dim3 Block(64, 1, 1);                                                                 | range<3> Block(64, 1, 1);                                              |

| <pre>dim3 Grid((NumElements + 1 - 1) / 1, 1, 1);</pre>                                | <pre>range&lt;3&gt; Grid((NumElements + 1 - 1) / 1, 1, 1);</pre>       |

| <pre>cudaStream_t stream = (streamPtr != nullptr) ?</pre>                             | <pre>if (streamPtr == nullptr)</pre>                                   |

| <pre>static_cast<cudastream_t>(streamPtr) : 0;</cudastream_t></pre>                   | <pre>throw std::invalid_argument();</pre>                              |

| <pre>kernel&lt;&lt;<grid,block,0,stream>&gt;&gt;(A, B, C,</grid,block,0,stream></pre> |                                                                        |

| NumElements);                                                                         | <pre>queue *stream = static_cast<queue *="">(streamPtr);</queue></pre> |

| CHECK_ERR;                                                                            | <pre>kernel(stream, Grid, Block, A, B, C, NumElements);</pre>          |

| }                                                                                     | }                                                                      |

**Figure 3.4.:** Shortened GEMM kernel launcher of CUDA (left) and Sycl (right) generated by Gemm-Forge. Pointers A, B, C contain NumElements contiguously batched matrices. Active threads per kernel are determined by the y-index range, whereas z index range is not set by the GEMM generator. The Sycl code asserts a valid context provided by the streamPtr and implicitly checks errors by exceptions thrown by the runtime.

The remaining part of the Sycl implementation in the respective generators is derived from the CUDA code similar as performed in Section 3.1.2, except for one difference. In Device, the thread indexing is directly converted by the corresponding methods (recall Figure 3.2 for an overview). However, this direct indexing causes issues using Sycl with CUDA backend<sup>5</sup>: The linear index in CUDA allows up to  $2^{31} - 1$  threads along x-axis. However, the CUDA implementation for Sycl used by oneAPI and hipSYCL does not map the x-axis of Sycl to the x-axis in CUDA but to the z-axis, which is limited to  $2^{16} - 1$ . In a typical setup of SeisSol, more than 2 GB of data is used. Assume matrix sizes of  $C \in \mathbb{R}^{56 \times 56}$ ,  $A \in \mathbb{R}^{56 \times 9}$ ,  $B \in \mathbb{R}^{9 \times 9}$  with single precision. This results in  $2 \cdot 1024^3$  B  $\div ((56 \cdot 56 + 56 \cdot 9 + 9 \cdot 9) \cdot 4$  B)  $\approx 144281$

<sup>&</sup>lt;sup>5</sup>https://github.com/intel/llvm/issues/1388

NumElements, each requiring 64 threads to process the biggest matrix A with a quadratic size of 56. Therefore, a direct conversion raises a CUDA\_ERROR\_INVALID\_VALUE, as the maximum number of threads in y, z direction in CUDA is exceeded.

To solve this problem, an additional abstraction layer is introduced for thread indexing in each generator provided by AbstractArchLexic. For CUDA and HIP, the current implementation is adopted without changes. For Sycl, the indexing strategy in GemmForge is switched as follows: The local size of a range is passed also to the global one. However, the global range is extended by multiplying the z-size with the count of threads, and not the x-size. That results in a re-ordering of the blocks along the z-axis. Figure 3.5 illustrates this change using a generic global space and a fixed local space of 64 along x-axis.

**Figure 3.5.:** Generalized index space for CUDA (left) and Sycl (right) used in GemmForge kernel launcher. Because the CUDA backend for Sycl maps the z-axis in Sycl to the x-axis in CUDA when using a 3D range, it is necessary to exchange both during GEMM code generation using Sycl.

Due to a lack of information about Iris Xe HPC series, no separate thread policy classes for Intel are added. It is to believe that tuning the LP series is not productive for the upcoming high-performance products. In Chapter 4, all performance analyses are therefore performed with the default thread policy. Regardless of that, the hardware descriptions of Iris Xe Max and UHD Graphics P630, as found in Section 2.1.2, are added to compute the active threads for the GEMM operation.

### 3.2.3. Correctness

To verify all changes, GemmForge test suite for GEMM operations is executed, containing setups for transposed and non-transposed matrices A, B, C as well as different values for  $\alpha$ ,  $\beta$ . The tests fill these matrices with random numbers and compare the resulting matrix C with a simple CPU implementation producing C' using their absolute difference  $|c_{ij} - c'_{ij}|$ . A test fails if this difference is higher than a fixed maximum error  $\epsilon = 10^{-5}$ . Furthermore, similar tests are implemented for CSAGenerator and Initializer generators but with the unused matrices removed.

The tests were executed on Iris Xe Max and UHD Graphics P630 using oneAPI in the packaged version as well as on Nvidia RTX 3090 using oneAPI (open-source variant) and hipSYCL. All GemmGenerator tests passed on all machines. The same held for CSAGenerator and Initializer using RTX 3090. However, P630 and DG1 raised a runtime exception CL\_INVALID\_WORK\_GROUP\_SIZE when executing these tests using oneAPI or created illegal

results with hipSYCL. Investigating this problem using the open-source variant of oneAPI<sup>6</sup> reveals that the total local size calculated with get\_local\_range(0) · get\_local\_range(1) · get\_local\_range(2) must not exceed PI\_KERNEL\_GROUP\_INFO\_WORK\_GROUP\_SIZE provided by an accelerator. For P630, this value is set 256, for DG1, it is 512, which can be reproduced by running clinfo<sup>7</sup>. That means that a local size of a kernel range is limited to 256 or 512 for these devices, respectively. However, CSAGenerator and Initializer index their matrices fully within the local index. For example, initialization of batched matrices  $A_k \in \mathbb{R}^{56\times 9}$  creates a local indexing space of at least  $64 \cdot 9 = 576$  when aligning the row size to 64. That already exceeds the maximum local size of both devices.

For DG1, this problem is circumventable by not aligning the x-size to a multiplier of Nvidia warp size of 32, which allows running the tests and SeisSol proxy application. In contrast to that, P630 can't run both applications because even with unaligned row sizes, a minimum of  $56 \times 9 = 504$  threads per workgroup is required. For more resource-intensive simulations, both limitations on the local size are a drawback compared to Nvidia, where a thread block is limited to 1024 threads<sup>8</sup>. Nevertheless, it is expectable that Intel HPC GPUs allow a higher maximum number of threads per workgroup, maybe similar to Nvidia. On that account, the index generation is not changed such that it is compatible with the integrated graphics chips.

<sup>&</sup>lt;sup>6</sup>https://github.com/intel/llvm/blob/sycl/sycl/source/detail/error\_handling/enqueue\_kernel.cpp

<sup>7</sup>http://manpages.ubuntu.com/manpages/bionic/man1/clinfo.1.html

<sup>&</sup>lt;sup>8</sup>https://docs.nvidia.com/cuda/cuda-c-programming-guide/index.html, Section 2.2

# 4. Evaluation and Discussion

This chapter evaluates all introduced changes and their effect on SeisSol using two test systems: Intel DevCloud<sup>1</sup> and Heisenbug<sup>2</sup> provided by the Geophysics department of the Ludwig-Maximilian University (LMU). The DevCloud allows requesting multiple compute nodes, equipped with one to many Iris Xe Max, integrated UHD Graphics P630, or even Arria 10 FPGAs. Heisenbug system comes without a job scheduler for their two Nvidia RTX 3090 and a single AMD EPYC 7662 64-Core Processor. Both types of GPUs were already used for verifying the correctness of all changes in the previous sections, but without focusing on platform details. Therefore, Table 4.1 gives an overview of the most important performance characteristics and properties crucial for the subsequent measurements.

|                        | Inte         | l DevCloud        | Heisenbug             |

|------------------------|--------------|-------------------|-----------------------|

|                        | Iris Xe Max  | UHD Graphics P630 | RTX 3090              |

| Peak FP32 Flops        | 2.50 TFlop/s | 460.8 GFlop/s     | 35.58 TFlop/s         |

| Max. threads per block | 512          | 256               | 1024                  |

| Peak bandwidth in GB/s | 68.30        | 41.60             | 936.20                |

| Sycl platform          | onoA         | PI (packaged)     | oneAPI (open-source), |

| Syci plationit         | OlleA        | II (packageu)     | hipSYCL, CUDA         |