# DEPARTMENT OF INFORMATICS TECHNICAL UNIVERSITY OF MUNICH

Master's Thesis in Informatics

# Design, Implementation and Test of Efficient GPU to GPU Communication Methods

Stepan Vanecek

# DEPARTMENT OF INFORMATICS

TECHNICAL UNIVERSITY OF MUNICH

Master's Thesis in Informatics

Entwurf, Entwicklung und Test von Effizienten Kommunikationsmethoden zwischen GPUs

# Design, Implementation and Test of Efficient GPU to GPU Communication Methods

Author:Stepan VanecekSupervisor:Prof. Dr. Martin SchulzAdvisor:Bengisu Elis, M.Sc.Submission Date:Abgabetermin (15. November 2020)

I confirm that this master's thesis is my own work and I have documented all sources and material used.

Ich versichere, dass ich diese Master's Thesis selbständig verfasst und nur die angegebenen Quellen und Hilfsmittel verwendet habe.

Ort, Datum

Stepan Vanecek

# Acknowledgments

I would like to thank my advisor, Ms. Bengisu Elis, for her help with the project. Moreover, I would like to thank everyone who supported me, especially my family.

## Abstract

Stencil codes are commonly used to solve many problems. On parallel heterogeneous systems with CPUs and GPUs, the domain is usually split and assigned to GPUs, where it is further divided to GPU blocks. The iterative distributed stencil computation consists of two steps – computation and communication, where the subdomains exchange boundary data, also called 'halo exchange'. On multi-node systems, it is crucial to efficiently transfer data from one GPU to another via MPI, as a de-facto standard solution in HPC.

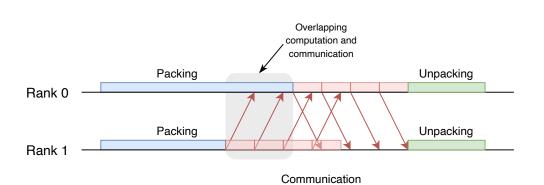

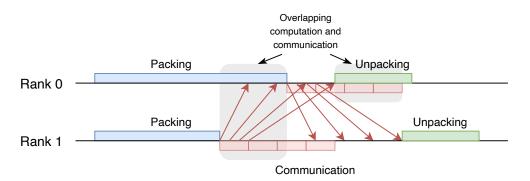

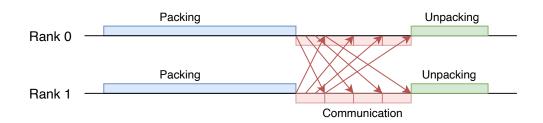

In this master thesis, methods of GPU-to-GPU data exchange via MPI are examined with focus on halo exchange. The thesis describes a design of a set of naive baseline approaches and a set of optimized solutions called taskqueue. The main idea behind the taskqueue approach consists in overlapping packing and unpacking (computation) with host-to-host MPI communication, and in reusing one kernel for both packing and unpacking workloads to eliminate the kernel launch, termination, and synchronization overheads. The implementation relies on pinned host memory, a segment of main memory that is accessible by both the CPU and GPU, that the parties use to communicate. A portable solution that runs on both NVidia and AMD GPUs is designed, so that the differences on both platforms can be observed.

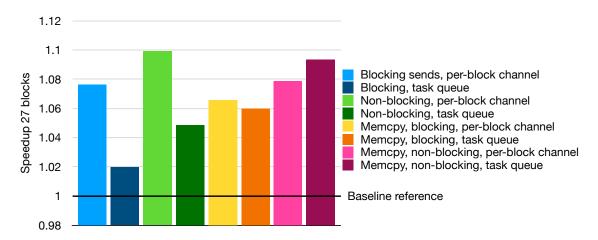

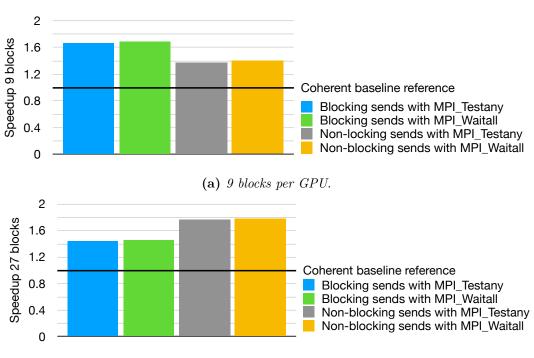

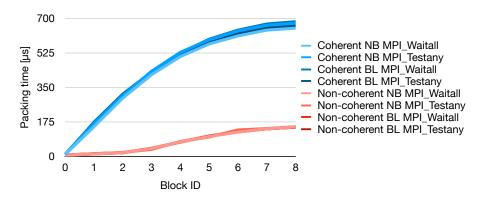

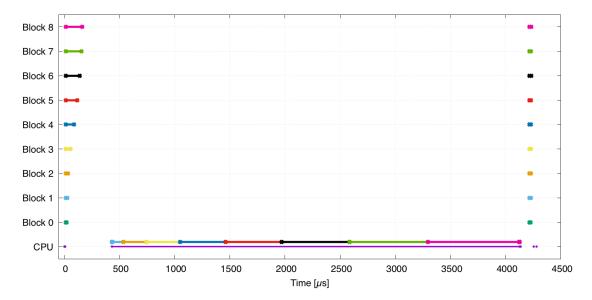

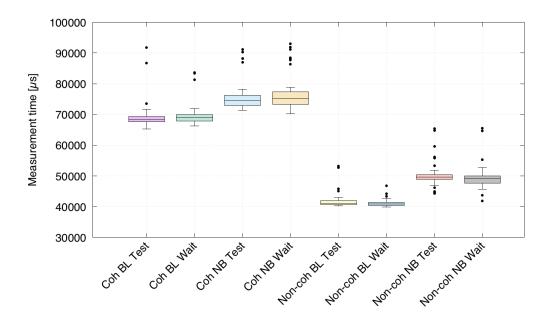

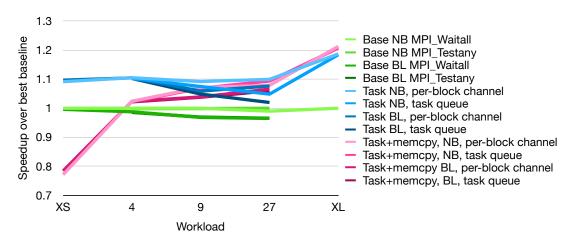

The performance of the task queue approaches is evaluated against a baseline reference on both and NV idia and AMD testbeds. The tests on NV idia yield a stable speedup that ranges from 1.09 to 1.21 for different workload sizes. Contrary to that, this approach did not prove useful on the AMD testbed, as it needed more than  $200 \times$  as much time to finish. The main reason for that are problems with concurrently reading from and writing to one memory location by the CPU and GPU.

This observation, and other observations made mainly on the AMD testbed, are identified and their implications are discussed in this work. It reveals some rigours of platform-agnostic GPU development, and discovers some unexpected behaviour patterns on the AMD GPUs combined with MPI usage. Finally, optimization to the taskqueue algorithm are proposed so that it would hopefully achieve better performance also on the AMD testbed.

# Contents

| 1 | Intro | oductio | <b>1</b>                                                                                             | 1 |

|---|-------|---------|------------------------------------------------------------------------------------------------------|---|

|   | 1.1   | GPUs    | and Heterogeneous architectures                                                                      | 1 |

|   | 1.2   | Motiva  |                                                                                                      | 2 |

|   | 1.3   | Goal .  |                                                                                                      | 3 |

|   | 1.4   | Struct  | re of this document                                                                                  | 4 |

| 2 | Bac   | kground | I                                                                                                    | 5 |

|   | 2.1   | Genera  | ll-Purpose Graphics Processing Units                                                                 | 5 |

|   |       | 2.1.1   | GPGPU Programming                                                                                    | 6 |

|   |       | 2.1.2   | GPGPU Architecture                                                                                   | ) |

|   | 2.2   | HIP .   |                                                                                                      | 1 |

|   |       | 2.2.1   | HIP and CUDA 12                                                                                      | 2 |

|   |       | 2.2.2   | Compiling HIP code                                                                                   | 2 |

|   |       | 2.2.3   | Alternatives to HIP                                                                                  | 3 |

|   | 2.3   | MPI .   |                                                                                                      | 1 |

|   |       | 2.3.1   | Communication types                                                                                  | 5 |

|   | 2.4   | Relate  | d research and technologies                                                                          | 7 |

|   |       | 2.4.1   | CUDA-aware MPI                                                                                       | 7 |

|   |       | 2.4.2   | CPU-to-GPU Callbacks                                                                                 | ) |

|   |       | 2.4.3   | Other relevant research                                                                              | ) |

|   |       | 2.4.4   | Learnings from related research                                                                      | 1 |

|   | 2.5   | Descri  | ption of the use-case                                                                                | 1 |

|   |       | 2.5.1   | Detailed specification                                                                               | 3 |

| 3 | Des   | ign and | Implementation 25                                                                                    | 5 |

|   | 3.1   | -       | l implementation patterns                                                                            | 7 |

|   |       | 3.1.1   | Code organization                                                                                    | 7 |

|   |       | 3.1.2   | Program workflow                                                                                     | ) |

|   |       | 3.1.3   | Data initialization and allocation                                                                   | ) |

|   |       | 3.1.4   | Compilation                                                                                          | 2 |

|   | 3.2   | Packin  | g and Unpacking                                                                                      | 2 |

|   |       | 3.2.1   | Buffer allocation $\ldots \ldots 3^4$ | 4 |

|   |       | 3.2.2   | Parallelization of packing and unpacking functions                                                   | 5 |

|   |       | 3.2.3   | device functions andglobal wrappers 36                                                               | 3 |

|   |       | 3.2.4   | Device memory implementation                                                                         |   |

|   | 3.3   | Baselir |                                                                                                      |   |

|   |       | 3.3.1   | Workflow                                                                                             |   |

|   |       | 3.3.2   | Non-coherent buffers                                                                                 |   |

|     | 3.4          | Taskqueue approach                                           | 4 |

|-----|--------------|--------------------------------------------------------------|---|

|     |              | 3.4.1 Goals                                                  | 4 |

|     |              | 3.4.2 Concept                                                | 6 |

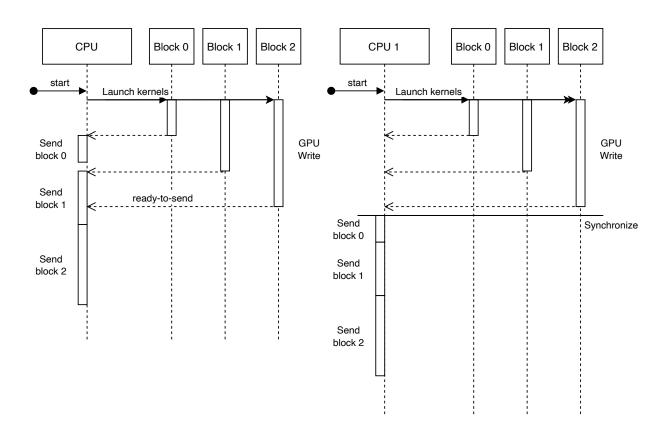

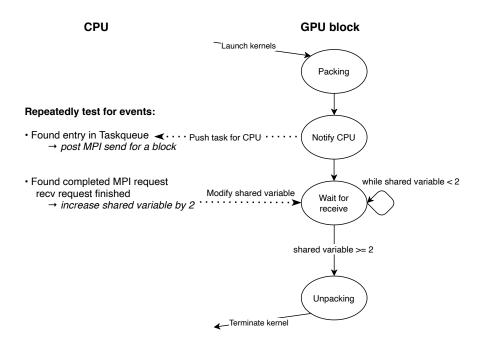

|     |              | 3.4.3 Workflow                                               | 7 |

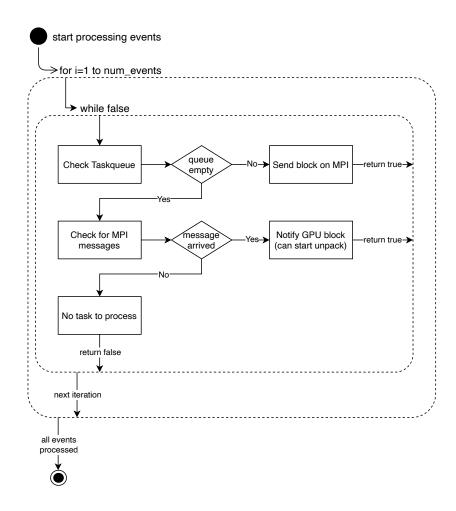

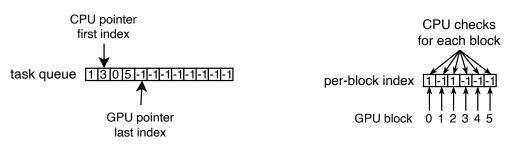

|     |              | 3.4.4 Implementation details                                 | 0 |

|     | 3.5          | Memcpy version                                               | 3 |

|     |              | 3.5.1 Workflow                                               | 3 |

|     |              | 3.5.2 Memory copy logic                                      | 8 |

|     | 3.6          | Other optimizations                                          | 9 |

|     |              | 3.6.1 Multiple threads on the CPU side                       | 9 |

|     |              | 3.6.2 Pipelining packing, memcpy, and send operations        | 0 |

|     |              | 3.6.3 Minor optimizations                                    | 1 |

|     | 3.7          | -                                                            | 1 |

|     |              | *                                                            | 1 |

|     |              |                                                              | 2 |

|     |              |                                                              | 2 |

|     |              |                                                              |   |

| 4   |              |                                                              | 3 |

|     | 4.1          |                                                              | 3 |

|     | 4.2          | 1                                                            | 3 |

|     | 4.3          | 1 0                                                          | 4 |

|     |              | 1                                                            | 5 |

|     |              | <b>5</b> 1                                                   | 6 |

|     | 4.4          |                                                              | 8 |

|     | 4.5          | 1                                                            | 8 |

|     |              |                                                              | 8 |

|     |              | 4.5.2 Taskqueue                                              | 3 |

|     |              | 4.5.3 Full problem size                                      | 0 |

|     |              | 4.5.4 Profiling taskqueue variants                           | 1 |

|     |              |                                                              | 3 |

|     | 4.6          | 1                                                            | 7 |

|     |              |                                                              | 7 |

|     |              | 4.6.2 Taskqueue                                              | 2 |

|     |              |                                                              | 3 |

|     | 4.7          | Summary of the performance measurements                      | 6 |

| 5   | Sum          | imary and outlook 9                                          | a |

| 5   | 5.1          |                                                              | 9 |

|     | 5.2          | Performance results                                          |   |

|     | 0.4          | 5.2.1 NVidia                                                 |   |

|     |              | 5.2.2 AMD                                                    |   |

|     | 5.3          | S.2.2         AND         10           Conclusion         10 |   |

|     | $5.3 \\ 5.4$ | Outlook                                                      |   |

|     | 0.1          | 5 4 4 5 6 4 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7              | 9 |

| Lis | st of l      | Figures 10                                                   | 5 |

| List of Tables | 107 |

|----------------|-----|

|                |     |

| Listings       | 109 |

|                |     |

| Bibliography   | 111 |

|                |     |

# **1** Introduction

"The world naturally works in parallel, and so parallelism is a helpful tool for modeling the real world." [25] "Parallelism implies the operation of more than one task at the same time. [...] Parallel computing is the methodology involved in utilizing the concept of parallel processing and its implementation on available computer architecture, related hardware and software to solve an application problem." [14]

Using this paradigm, it is possible to solve problems that are too large to be computed in a single stream of instructions and data. The frequency of current processors (CPUs) has not risen significantly in the last decade, as shown by K. Rupp in [30]. Therefore, the number of instructions per second that a single stream can process has not risen either. In order to solve more complex problems in a feasible amount of time, it is thus necessary to parallelize the computation in some way. Because of this fact, there is a lot of stress on parallelism as a means of improving performance of applications in the area of High-performance computing (HPC).

In [10], M. Flynn proposed a taxonomy that distinguishes two types of parallelism – data and instruction parallelism. The former describes scenarios where multiple pieces of data are processed simultaneously. When only data parallelism is present, we speak of "Single Instruction Stream-Multiple Data Stream" (SIMD) parallelism. This class describes use-cases with a single stream of instructions, where a single instruction is applied to multiple pieces of data simultaneously. This applies mainly to vectors (for example SSE or AVX<sup>1</sup>) on CPUs or to Graphics Processing Unit (GPU) computing. Combining instruction and data parallelism approaches corresponds with the "Multiple Instruction Stream-Multiple Data Stream" (MIMD) class. In this class, there are multiple streams of instruction that work on different pieces of data in parallel. Today this approach is applied at multiple levels – we can run multiple threads in a process, multiple processes on CPU cores, and we can create systems composed of multiple nodes. There are many standardized frameworks to simplify the development of MIMD applications. In the realm of HPC, the most prominent ones are OpenMP for shared memory systems and MPI for both shared and distributed memory systems. In today's systems, applications often make use of multiple approaches to parallelism simultaneously.

# 1.1 GPUs and Heterogeneous architectures

GPGPUs (General Purpose Graphics Processing Units) present an extension to the classical CPU-based computing model. GPGPUs often feature thousands of threads. These threads can be used as an instrument for massive parallelism. Modern GPUs are

<sup>&</sup>lt;sup>1</sup>Intel's x86 ISA extensions for vector instructions. SSE stands for Streaming SIMD Extensions, AVX for Advanced Vector Extensions.

usually used as co-processors. Whenever the computation is parallelizable, CPUs can offload suited parts of the computation to GPUs, so that the particular subproblem is solved by a GPU in parallel and therefore faster. System architectures featuring CPUs and GPGPUs are one of the most common examples of heterogeneous system architectures. In the most recent Top500 [1] list from June 2020, 30 % of the systems use accelerators, and over 90 % of them are GPUs.

In the recent years, GPGPU computing has been increasing in importance in HPC applications, as GPUs have proven to be useful thanks to their massive SIMD parallelism capabilities. Today's high-end GPUs can outperform CPUs, while also being more power efficient thanks to more lightweight cores. "As of 2016, the ratio of peak floating-point calculation throughput between many-thread GPUs and multicore CPUs is about 10, and this ratio has been roughly constant for the past several years." [16]

However, even a GPU has a limited computing power. Most powerful GPUs nowadays reach the order of lower tens of TFLOPS. As of 2019, "the most powerful GPUs can deliver single-precision performance as high as 16 TFLOPS" [34] <sup>2</sup>. In order to increase the overall computing power, multiple GPUs are needed. However, GPUs still require some interaction with the host system – the CPU. One CPU can and often does serve multiple GPUs, but this number is limited. There is a lot of cooperation and communication between the parties, and large amounts of data are transferred. These actions put load on the CPU and the system bus, which has a limited bandwidth, to name a few examples. In order to avoid this problem and enable scalability beyond a couple of GPUs on top of one CPU, we usually introduce multiple nodes. Such a node consists of a CPU that operates one or a handful of GPUs. The nodes are connected with each other via a high-speed interconnect system, for example Infiniband or Omnipath. For inter-node communication, MPI is used as a de-facto standard solution.

There are two kinds of communication – intra-node, where communication between CPU, GPUs, NIC, and other devices takes place, and inter-node, where nodes communicate with other nodes. In order to utilize the computing capabilities in this topology, applications are usually written such that CPUs offload some parts of the computation to GPUs, while they still remain responsible (among other possible tasks) for the data exchange between GPUs and coordination in general. There are other approaches available which lessen the importance and role of the CPU in the communication; they will be discussed in section 2.4.

# 1.2 Motivation

Communication bandwidth and latency are crucial factors when designing parallel applications that do not run on systems with shared memory. The parties involved in the computation need to collaborate, which is accomplished via synchronization in form of data transfers. In the case of parallelized iterative algorithms, this procedure is repeated in each iteration, thus taking place very often. In general, a poorly performing communication scheme affects the performance of the whole application. Therefore, having an efficient

$<sup>^2\</sup>mathrm{NVidia}$ Volta V<br/>100S – 16.4 TFLOPS, AMD Radeon Instinct MI60 – 14.7 TFLOPS (single-precision performance)

method of communication between the parties is extremely important for the vast majority of parallel applications running on distributed memory systems.

As mentioned previously, inter-node communication in a system can be realized via MPI. The first version of MPI [11] was released in 1994. MPI performs well in the classical CPU to CPU communication (or communication between different processes running on one CPU), which was the standard computing model when MPI was designed. Nevertheless, the standard MPI model is not well suited for using GPUs for computationally intensive tasks, which is the current trend. Adding GPUs makes the communication scheme more complex. In some implementations, the CPU is still in charge of the communicate directly in some cases as well. Technologies that manage this communication are presented in section 2.4.

Today, we still need CPU to CPU communication. On the top of that, the CPU needs to communicate with its GPUs. Finally, different GPUs need to synchronize data among each other as well. While the first scenario is covered by MPI and the second one is usually well optimized by vendor-specific APIs, the last one is not that straightforward. This is because neither the MPI model was designed for such heterogeneous systems, nor is it in the focus of vendor-specific APIs that aim primarily on CPU-GPU data transfer and synchronization as the standard use-case. There are existing approaches to the last type of communication as well, however they are not suitable for all kinds of host and/or device architectures, are not that performant, or easy-to-use and widespread. For this reason, the last of the three communication schemes – GPU to GPU communication – is the focus of this master thesis.

# 1.3 Goal

The goal of this project is to design and examine possible approaches to transferring data from one GPU to another. The focus is put on the efficiency of communication. The target use-case for which the solution will be designed is a stencil code. "A stencil is a stylized matrix computation in which a group of neighboring data elements are combined to calculate a new value. They are typically combined in the form of a sum of products." [29] Stencil code is a piece of code that performs computations on stencils. The code usually works on an iterative basis, thus the data exchange between adjacent points on the grid takes place repeatedly.

"Stencil computations are commonly used in solving partial differential equations, image processing, and geometric modelling." [29]. Solving partial differential equations is a key technique for many widely-used scenarios, such as heat transfer or fluid dynamics simulations. As stencil codes present a solution to many common problems, it is desirable to find an efficient way to solve the problem.

The exact use-case for the stencil code remains undisclosed, however a detailed description and specification of the problem this thesis examines is described in section 2.5.

In order to process stencil codes in parallel, the domain is split between the compute units (usually CPU processes or threads, or GPU blocks) so that each unit is responsible for a fraction of the original problem. As the stencil code needs up-to-date information from adjacent cells, one tries to split the domain so that the largest possible portion of the necessary data is present on the same computing unit. However, the domain decomposition will always end up with boundaries. "Running stencil codes on distributed memory computers requires extended boundary elements to be cached and exchanged to satisfy stencil pattern locally. This elements of the sub-domain boundary are called halo. Halo exchange is often used jargon in computational sciences. It means data movement between two parallel processes holding neighbouring parts of the decomposed domain." [36]

# 1.4 Structure of this document

This document is organized as follows. The next chapter provides more detailed background information regarding this project – it presents GPU architectures and HIP, summarizes available technologies on efficient GPU-to-GPU communication, and gives a detailed description of the use-case. Chapter 3 describes a naive "baseline" implementation and the proposed algorithm "taskqueue" in detail. Chapter 4 presents performance results of the proposed and implemented set of solutions, and chapter 5 concludes the work and gives an outlook for future development.

# 2 Background

In this chapter, the technologies and research efforts related to our work are presented. First, a summary of GPGPU architecture and programming is provided. Next, the C++ runtime API and GPU kernel language HIP, that was used use for the implementation, is introduced. Then, a short introduction to MPI follows. Next section covers related research and technologies on optimizing data transfers between GPUs, commanding CPUs from GPUs, and other related areas. Finally, section 2.5 provides in-detail description and definition of the use-case and the problem space.

# 2.1 General-Purpose Graphics Processing Units

Graphic Processing Units (GPUs) are specialized circuits that were originally created and used to accelerate graphics computations on computers. In order to manage that, lots of independent calculations have to be performed in a short time. GPUs featured an efficient parallel design in order to exploit that attribute. The capability to perform specialised operations for graphics computing in highly parallel manner started to be attractive also for other disciplines as well. Those made use of the limited capabilities and tried to exploit the massive parallelism GPUs offer. GPU vendors eventually adapted their hardware and ISAs to make GPUs easy to use also for other applications outside of the realm of graphics processing, hence the term General-Purpose GPUs. The year 2007 is an important milestone in GPGPU development as in this year, CUDA was released. It brought simplification and generalization of parallel programming on GPUs, compared to previous APIs, such as OpenGL or Direct3D, where the computation must have been expressed as work with pixels [16]. GPGPUs are the common type of GPUs currently.

Today, GPGPUs are used in a plethora of disciplines. Most prominent are use-cases for graphics processing, video rendering, gaming, cryptography, and scientific computing. In the area of scientific computing, lots of computationally-intensive application can profit from GPGPU computation. The use-cases include weather forecasting, many kinds of simulations, quantum mechanical physics modelling, and many others.

In this section, GPGPU architecture and the approaches to their programming will be briefly introduced. AMD terminology and specifications will be used, namely AMD Graphics Core Next (GCN) GPU microarchitecture and ISA. Competing NVidia products have, in general, very similar features and functionalities, often only marketed under different names. The focus is put on AMD GCN in this section as the GPUs of one of our testbeds are based on 5th generation of GCN, called "Vega 20". Moreover, as NVidia and CUDA are very popular and widely known, this section might serve as comparison for those readers who are already familiar with NVidia and CUDA concepts.

#### 2.1.1 GPGPU Programming

The main advantage of GPGPUs compared to classical CPU programming is the massive parallelism that GPUs enable. GPUs are composed of many SIMT (Single-Instruction Multiple Threads) cores and can therefore work on many pieces of data simultaneously. Different SIMT cores can either work on larger sets of data together or run different programs. From this perspective, it can be said that GPUs are capable of MIMD parallelism.

In heterogeneous CPU-GPU systems, GPUs are used to execute computationally intensive sections of a program that can be done at least partially in parallel. When a program reaches a parallelizable subproblem, the CPU can delegate it to one or more GPUs to solve it more efficiently. In this scenario, the GPU serves as a co-processor to the CPU. When the GPU is utilized to solve a part of the program, there is a performance penalty for doing so. The CPU has the program, the data, and the resources already available in caches and registers, but none of this holds true for the GPU. Therefore, before a GPU can start computing, the particular program has to be loaded and scheduled to GPU cores, and the necessary data has to be made available as well. Classically, this is done by copying the necessary data from the main memory to the GPU memory, but there are other approaches as well. The start-up phase takes, of course, some time to finish. Therefore, offloading work to a GPU is not immediate, and this penalty has to be reckoned with. In general, problems that are not complex yet require large amounts of data movement would therefore not be suited for GPU offloading.

Vega Shader ISA [5] defines a complete application as a program that runs on the host CPU and a set of device (GPU) programs, called kernels. The host part of the program controls the program by "commands that set GCN internal base-address and other configuration registers, specify the data domain on which the GCN GPU is to operate, invalidate and flush caches on the GCN GPU, and cause the GCN GPU to begin execution of a program." [5]

#### Parallelization hierarchy

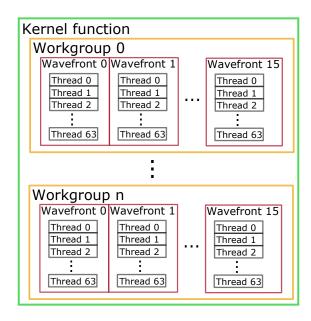

There are multiple hierarchical constructs that help programmers grasp the parallelization at different levels according to their needs. One can both distinguish each thread from each other and group and GPU's SIMT units together to work with them as a whole. The atomic unit of computation is a thread, also called work item or worker. It represents the single instruction and data stream of the device program. Figure 2.1 visualises the hierarchy, the presented terms are described in the following paragraphs.

**Wavefront** Threads are grouped to wavefronts (called 'warp' in CUDA terminology). There are 64 threads in a wavefront in contrast to 32 threads in a CUDA warp<sup>1</sup>.

Wavefront can be understood as the SIMT unit of the GPU. The threads in a wavefront run in lockstep, which means the same instruction is applied to all threads of a wavefront at a time. As each thread can operate on a different set of data, wavefronts present a huge parallelization potential.

$<sup>^1\</sup>mathrm{When}$  porting code between AMD and NVIDIA devices, this difference shall be taken into account.

Figure 2.1: Parallelization divisions in a GPU kernel function.

If the device function contains conditional statements, which is not uncommon, the whole wavefront executes both *if* and *else* branches, while the instructions of one of the branches are masked off for those threads that would not enter it (do not meet the *if* condition). The only exception is when all threads fall into the same branch. Then, the instructions from the other branch are not executed at all. This actuality should be taken into consideration by the programmers as including lots of branches that can be evaluated differently by different threads may impact the performance as all branches will be executed in a serial fashion.

**Workgroup** Workgroups (called 'thread block' in CUDA terminology) are groups consisting of 1 to 16 wavefronts. The device function called from the host consists of a number of workgroups. The number is defined by the programmer and usually serves to split the domain. A workgroup is always scheduled (more on workload scheduling in section 2.1.2) on one compute unit ('streaming multiprocessor' in Nvidia terminology) where threads run in parallel, which means that the threads of a workgroup

- run on a GPU at the same time, and

- can share resources in the workgroup via local memory (see 2.1.1).

As there are 64 threads per wavefront and up to 16 wavefronts per workgroup, a workgroup can consist of up to 1024 threads.

**GPU kernel dimensions** The hierarchy of threads, wavefronts, and workgroups defines how the threads can be scheduled on the hardware, which threads will run in lockstep, or can share resources. However, the programmers do not need to specify that manually.

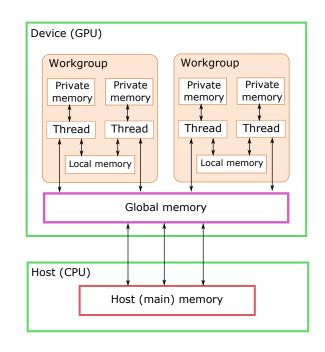

Figure 2.2: High-Level Memory Configuration on GCN ISA. [5]

Instead, the programmer only needs define how to split the domain in 2 ways – defining the grid and block dimensions. A problem is split into n blocks and each block is further split into m threads. Both of those are specified as 3-dimensional spaces to simplify abstracting common problems, which often also have 3 dimensions. The programmer defines number of blocks and threads in each dimension. By this, the size of the problem is specified. If 1- or 2-dimensional space is needed, the problem sizes in the third and eventually the second dimension are set to 1.

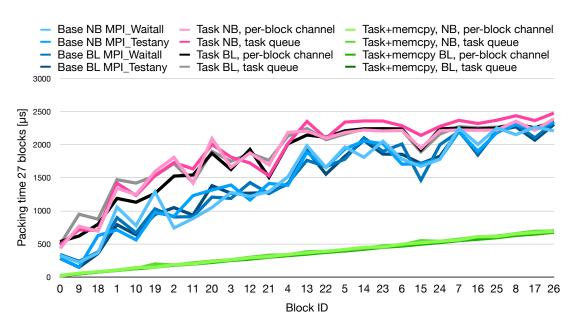

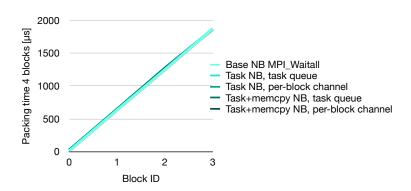

An example setup also used in our measurements is that we split the domain into  $3 \times 3 \times 3 = 27$  blocks and each of those has 128 threads in one dimension  $(128 \times 1 \times 1 = 128)$ .

#### **Memory Management**

Unlike with CPU programming, the GPU does not manage its memory automatically. That means that the programmer is, apart from writing the parallel program for the GPU itself, also responsible for memory transfers between the parties. Those can be from the host (CPU) memory to the memory of the device (GPU), the other way around, or between two devices on the same node. The first two are frequently used – from host to device as a way to provide the GPU with the data to work with and from device to host to deliver the partial result back to CPU.

From a programmer's perspective, we distinguish three kinds of memory on GPU – private memory, local memory, and global memory. They differ in their availability to different segments of the GPU. The hierarchy of these types of memory is visualised in figure 2.2.

**Private memory** Private memory (called 'local memory' in CUDA terminology) is the finest-grained memory type. It is only available to the thread that owns it and cannot be accessed by another thread. This memory is used for local variables that may differ from thread to thread. [26]

**Local memory** Local memory, also denoted Local Data Share or LDS (called 'shared memory' in CUDA terminology) is the scratchpad memory of a GPU that is shared among wavefronts (CUDA warps) of a workgroup (CUDA thread block). [26] Using local memory, the GPU can save resources for storing pieces of data that do not change for different threads in a workgroup, compared to keeping that piece of data to each thread's private memory. Moreover, threads within a workgroup can use this memory to share data and to communicate as changes made by one thread will be seen by other threads. "Local data share (LDS) is a very low-latency, RAM scratchpad for temporary data with at least one order of magnitude higher effective bandwidth than direct, uncached global memory." [5]

**Global memory** Global memory (also called 'global memory' in CUDA) is the third type of memory on the GPU. It is accessible for all work items of all workgroups on the whole GPU. Device memory allocation operations (hipMalloc for HIP or cudaMalloc for CUDA) allocate memory in this segment. One can think of global memory as a GPU equivalent to main memory of the CPU.

**Pinned host memory** Pinned host memory, also called page-locked or zero-copy memory, is yet another kind of memory accessible from the GPU, however it does not reside on the GPU itself. Pinned host memory is a segment of the host (main) memory that can be directly accessed by the device via a bus, usually PCI express (alternatively NVLink for NVidia products). Classical host memory is typically pageable, meaning the host OS kernel can move the physical data on the main memory, for example it can be offloaded to HDD. Contrary to that, page-locked memory stays on main memory and is not moved by the CPU. Therefore, accesses to the page-locked memory segments from the GPU, which are direct and do not need to involve the CPU, can be performed. The size of page-locked memory is, however, limited, so allocating too much memory of this type could lead to performance issues, as it is used by the GCN ISA for other purposes as well, for example for hipMemcpy memory copy in HIP (see section 2.2). Moreover, page-locked memory is used not only by GPUs. "MPI uses pinned pages for communicating over interconnect" [19].

Accesses to data allocated on pinned host memory (assuming the data is not cached, which is our case) are slower compared to all previous types as the data needs to go over the system bus. On the other hand, both host and devices can read from and write to the data located in pinned host memory. Accessing data directly on the pinned host memory is called zero-copy access.

Pinned host memory is used not only for direct accesses by the GPU as described above. When data between the host and device is copied, transferring data from or to a pinned host memory segment is faster compared to a pageable segment of main memory as the GPUs can access it directly. Therefore, it might also be beneficial to put frequently copied data on the pinned host memory as well. Nevertheless, as all memory transfers between the host and device go through this segment, allocating too much data on pinned host memory can decrease the performance of other memory copy operations between host and devices drastically.

It is possible to choose between 2 coherency options for pinned host memory in HIP:

- Coherent memory allows fine-grained synchronization, such as atomic operations. As the name suggests, the data accesses remain coherent across multiple devices. In order to achieve this, the memory is not cached, meaning the data needs to be loaded from and stored back to the main memory each time, which presents a performance penalty. [2]

- Non-coherent memory is more efficient. It can be cached and therefore repeated load/store operations will be much faster. On the other hand, it cannot be synchronized while the kernel is running. As the data gets stored and accessed from caches, coherency is not guaranteed as the segments of data in the cache or main memory might not be the most recent ones. [2]

# 2.1.2 GPGPU Architecture

The focus of GPGPUs, unlike CPUs, is mainly on parallel computation. They are designed to be the slave of the host system and to take over computation that was assigned to it. GPUs can traditionally deal very well with arithmetic operations on integers. More recently, the support of floating point units (both half-, single-, and double-precision) was improved and now is comparable to that of CPUs [16]. As GPUs have a very narrow focus on computation, their compute units are usually simpler compared to CPUs. It does not need to run an OS, it does not need to connect peripherals, switch contexts, and many other duties a CPU has. This makes GPU cores more lightweitght, which means that the FLOP/mm<sup>2</sup> is higher and thus GPUs are easier to manufacture and more power-efficient. Thanks to these characteristics, their price per FLOPS is lower.

### Workload scheduling

A GPU consists of a Command Processor and one or more Shader Engines, in case of our AMD MI-50 GPU, there are four of them. The shader engine is composed of a Workload Manager and a set of Compute Units (CUs). (There are 15 CUs per shader engine on MI-50). Scheduling starts with the command processor reading a command package from command queues (one or more per GPU). The command processor splits the command package in workgroups, and distributes them to the workload managers. Then, a workload manager further splits the workgroup and creates wavefronts for the CUs and distribute the workgroups to the compute units. [7]

User-defined blocks (wavefronts) get scheduled on compute units. All threads of a workgroup run on one CU at the same time. The local memory (LDS) is attached to each CU, so that the threads in a CU can share data, which maps to the programmer's perspective discussed in 2.1.1.

#### Memory hierarchy

Similarly to CPUs, GPUs have multiple options for storing the data in hardware that differ in their capacity and speed of access. The fastest and also the smallest one are the register files. Between register files and global memory, there are L1 caches and an L2 cache. The L1 cache is private for each CU, while L2 cache is global. The cache line size is 64 B [5], however for NVIDIA devices, it is 128 B [23] (the size is stored in variable warpSize in HIP). Finally, the global memory is the largest memory type that is also the slowest to access. "In a typical arrangement, registers for the various processing elements pull data from a set of L1 caches, which in turn access a unified, on-chip L2 cache. The L2 cache then provides high-bandwidth, low-latency access to the GPU's dedicated video memory." [5]

For each CU, the register file consists of scalar general-purpose registers (GPR) and vector GPRs. Vector GPRs contain the data for CU's vector SIMT units, while scalar registers contain data common to all threads in a wavefront, such as pointer arithmetic or constant data. These pieces of data are used by CU's scalar unit.

Accesses to pinned host memory are the slowest ones, as they need to go though the system bus. Depending on coherency settings, it is or is not cached, as describen in section 2.1.1.

#### Connectivity

The GPU is connected to its global memory, for our AMD MI-50, it is 32 GB HBM (High Bandwidth Memory). Next, there are PCIe controllers ensuring connectivity to the host. Finally, there are also DMA engines there, which are capable of directly accessing host's main memory. They are responsible for asynchronous memory copies between the host and the device, and possibly between multiple devices. [7]

# 2.2 HIP

Heterogeneous-Computing Interface for Portability (HIP) [37] is a C++ runtime API and C++-based kernel language. It is designed to ease transferring from vendor-locked CUDA applications to a portable code. CUDA is a programming language and API used for programming NVidia devices. Hence, programming with CUDA comes with vendor lock-in to NVidia hardware. NVidia has been a dominant player on the GPU market. According to [24], the market share of NVidia in the segment of discrete GPUs has been approximately between 60% and 75% in 2018. The rest of the market belongs almost entirely to AMD. In GPU sales overall, Intel is the market leader thanks to its dominance in integrated GPU segment. The dominance of NVidia in the discrete GPU segment is one of the reasons why CUDA programs are so widespread and vice-versa. The other reason is that CUDA has presented an efficient and simple to understand programming model when it was released in 2007 and it took years before other products caught up.

HIP is a part of AMD ROCm (Radeon Open Compute) platform that contains software projects focussing on HPC programming. ROCm is an open source modular platform that enables its users to install, on top of the core components, only the components that

#### 2 Background

| CUDA                                                                | HIP                                 |

|---------------------------------------------------------------------|-------------------------------------|

| <pre>my_kernel&lt;&lt;<grid, block="">&gt;&gt; (args)</grid,></pre> | hipLaunchKernelGGL(my_kernel, grid, |

| my_kerner<                                                          | block, LDS_size, stream, args)      |

| cudaMalloc                                                          | hipMalloc                           |

| cudaMallocHost                                                      | hipHostMalloc                       |

| cudaMemcpy                                                          | hipMemcpy                           |

| cudaStreamCreate                                                    | hipStreamCreate                     |

| cudaDeviceSynchronize                                               | hipDeviceSynchronize                |

Table 2.1: Comparison of some frequently-used CUDA and HIP API calls.

they intend to use. Version 1.0 was released in 2016. As the whole platform is not so mature yet, it is still rapidly evolving, as of autumn 2020.

We chose HIP for implementing our solutions mainly thanks to its capability of compiling code for both NVidia and AMD devices. This means that a single version of code can be run and evaluated on both platforms. This way, the code that was produced is fully portable and therefore measurements on both NVidia and AMD GPUs over the same piece of source code can be made. The experiments and benchmarks performed in [35] suggest that HIP has a comparable performance to competing C++ runtime APIs & GPU kernel languages. This will be presented in section 2.2.3 in more detail.

# 2.2.1 HIP and CUDA

HIP accepts the popularity of CUDA and presents an alternative, yet as similar as possible, solution. Its syntax is very similar to the one of CUDA. Table 2.1 presents some frequentlyused API calls for comparison. Often, the only difference is the cuda or hip prefix. The complete list of CUDA runtime APU functions supported by HIP can be found in [27]. Unlike CUDA, HIP is open-source (released under MIT license) and the code should be compilable both for NVidia and AMD devices, hence "Interface for Portability".

HIP comes with functionality called 'HIPify'. This program should ease the transition from CUDA to HIP code, called 'hipification'. There are two flavours of this program – hipify-perl and hipify-clang. The former is a rather simple program based on string replacement. It mainly converts CUDA API calls and data types to HIP syntax. The latter is more sophisticated and tries to resolve dependencies as well. Nevertheless, neither of the programs is intended to work fully independently. Human supervision and interaction is always necessary, maybe with the exception of very trivial use-cases. From our experience with hipify-perl, manual code checking and corrections of the code are necessary; the tool does not do much beyond what could be done by a series of Find&Replace operations.

# 2.2.2 Compiling HIP code

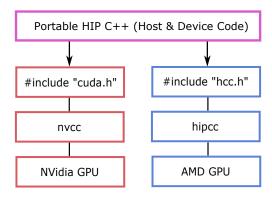

As mentioned above, HIP source code can be compiled for both NVidia and AMD devices. As those have different ISAs, the compiled binaries, unlike the source code, are different.

Figure 2.3: Compiling HIP code for AMD and NVidia devices. [7]

The binaries are vendor-specific, even microarchitecture-specific, depending on which device the programmer compiles the code for.

To enable this, there are two underlying compilers for HIP code – HIP-NVCC and HIP-Clang – each compiling for one of the vendors. As figure 2.3 shows, different platform-specific components get included when compiling for each platform. hip\_nvcc is the program for compiling for NVidia devices. In brief, HIP header files are capable of translating HIP code to CUDA-like code that can be compiled by NVCC, which is NVidia's closed-source compiler for CUDA code. Contrary to that, HIP-Clang builds up on LLVM/Clang compiler and enables compiling HIP source code for AMD devices. Another alternative used to be hip-hcc compiler, using the hcc compiler under the hood, however it was deprecated in release 3.5 [37] in summer 2020.

hipcc is the overarching compiler for HIP that utilizes one of the underlying compilers – either HIP-NVCC or HIP-Clang. The programmer can either let hipcc detect for which vendor it should compile or manually define it in variable HIP\_PLATFORM with nvcc for NVidia and hcc for AMD. As hipcc builds on other compilers, the programmer can utilize the functionality of these compilers, including compiler flags etc. However, NVCC reads different flags than Clang, so the flags for compilation with hipcc will often be different when compiling for an AMD device compared to compiling for an NVidia device.

#### 2.2.3 Alternatives to HIP

There is a plethora of GPU programming languages that could be alternatives to HIP and a thorough analysis of those is beyond the scope of this section. All in all, the choice of programming language is not crucial for this project. A choice is sufficient as long as it performs well, is easy to use, works on both NVidia and AMD GPUs, is under active development and there is a large community behind the project.

ROCm platform supports multiple programming languages, such as OpenMP, OpenCL, and HIP. The AMD System Runtime (ROCr) is built on HSA Runtime API which enables executing programs written in those programming languages on AMD hardware and a host system with Linux OS. [3] Alternatives outside of ROCm platform include NVidia's CUDA,

more recently OpenCL's extension SYCL, Intel's heterogeneous computing HPC approach DPC++ (Data Parallel C++) and many others. As our focus lies, apart from NVidia, also on AMD devices, the compatibility with this vendor is a must. This requirement rules out CUDA, the most prominent programming language for NVidia GPUs.

**CUDA** CUDA is a GPU programming framework developed by NVidia for their devices. It is compiled with NVCC, which is NVidia's proprietary compiler.

**OpenMP** "ROCm offers support for offloading compute to AMD GPUs in multi-node deployments via the OpenMP application programming interface using pragma target offload directives." [4]

HC++ HC++ is a programming language, similar to C++ AMP by Microsoft. It was deprecated in favour of HIP recently, therefore, no further development of this project is to be expected.

**OpenCL** OpenCL is a heterogeneous programming framework that can be used to program both NVidia and AMD devices. It defines a C API and a kernel programming language – OpenCL C. On AMD devices, there are two drivers that support OpenCL C – AMDGPU-Pro and ROC's HSA runtime API. [35]

In [35], the authors evaluate performance of ROCm programming frameworks – namely OpenCL, HC++, and HIP. Unfortunately, comparison with OpenMP is missing there. The authors use several real-world workloads and benchmarks to evaluate performance of the different frameworks on the same hardware. They conclude that from this trio – all running on ROCm platform – is HIP the best performing solution overall. The authors also compare performance of OpenCL with AMDGPU-Pro and ROC's HSA Runtime. The ROCm version slightly outperforms AMDGPU-Pro in applications that are not bound by memory copy. On the other hand, in other applications, ROCm version tends to perform worse. The authors conclude that the main reason for this is the API call overhead of HSA platform, along with memory transfers. What's more, the paper also presents a comparison of HIP and CUDA code running on the same NVidia hardware. There, they do not measure any noticeable overhead so they could conclude that HIP brings portability while not losing on performance when compared to CUDA. Based on their findings, HIP was chosen as a portable solution for both platforms that does not have any noticeable performance when compared to the available alternatives.

# 2.3 MPI

MPI (Message Passing Interface) is a standard that defines an API enabling both intraand inter-node communication between processes. It is a de-facto standard solution for running parallel programs on HPC distributed memory systems. It is also very popular for shared memory systems. First version of MPI was released over 25 years ago and the most recent version – MPI 3.1 [12] – was released in 2015. The motivation behind creation of MPI was the desire to create a cross-vendor API standard for shared as well as distributed memory systems which would replace vendor-specific solutions that had been used previously. Having achieved that, one could ensure portability of applications across systems by different vendors and also made programmers' work more efficient as they did not need to learn to work with new solution every time they would use a different system.

The main function of MPI is to connect the endpoints (processes) and ensure both synchronization and data exchange in form of messages. The implementation is not a part of the standard; it only defines the characteristics of the API.

An MPI program is a set of processes launched, depending on the settings and system, on one or more nodes. The processes are isolated from each other, which means that they cannot access each other's resources (RMA being an exception), however they are connected to each other and can send messages to each other. An MPI process can, but may not, be realised as an OS process of the host node. All processes run the same binary, however they usually operate over different sets of data. Such an approach is called Single Program Multiple Data (SPMD). The actual synchronization and isolation of the processes, as well as implementation of the API calls is may be different for each product yet all products should comply with the MPI standard. Therefore, an application written in compliance with MPI standard should work on all correct implementations. However, this does not work the other way around – an application that works on one MPI implementation may not work with other implementation or system.

There are multiple efforts to implement the MPI standard – both open source and proprietary. The popular ones include:

- OpenMPI

- MPICH

- MVAPICH2

- Intel-MPI

#### 2.3.1 Communication types

It is possible to classify MPI communication types by different measures. One of them is the number of involved parties – MPI offers means to point-to-point and collective communication. Another possible classification distinguishes one- and two-sided communication depending on how many parties are actively involved in a message transfer. These could be further divided by other characteristics, such as whether an operation is blocking or non-blocking.

#### Point-to-point vs. Collective communication

**Point-to-point communication** Point-to-point communication includes only two parties. A typical example is a send-receive operation. One party, the sender, posts a send operation, and the receiver posts a matching receive operation. The operations are always matched and the operations are used as a hint for the MPI engine to enable and process the

operation. Typical API call examples are different variants of send and receive operations: MPI\_Send, MPI\_Recv, MPI\_Isend, MPI\_Irecv.

**Collective communication** Collective communication involves multiple parties, typically either one party spreading its data to many others (broadcast – MPI\_Bcast or scatter – MPI\_Scatter), or all involved parties combining its data to compute a result, for example a sum (reduction – MPI\_Reduce). There is a plethora of collective operations that define combinations of collecting, combining, and spreading data from multiple parties.

Moreover, there is another special use-case for collective communication – synchronization. MPI offers means to synchronize among processes, meaning all specified<sup>2</sup> processes have to reach the barrier in order for the processes to be allowed to continue computation. Such a synchronization point is created with MPI\_Barrier.

Collective operations are usually considered two-sided communication. As collective communication operations, apart from synchronization, are not used in the implementation of our solutions, we will not get more in depth on collective communication.

#### One- vs. two-sided communication

**Two-sided communicaiton** Two-sided communicaiton is the classical communication model where all parties – most typically the sender and the receiver – post MPI calls that trigger the data exchange. Two-sided communication covers both point-to-point communication, such as send-receive operations, and collective communication, such as broadcast. Technically, one could imagine a broadcast operation as a sequence of send-receive operations. In order for two-sided communication to work properly, several criteria have to be met. All parties need to post matching API calls for the communication to succeed. For example MPI\_Send and MPI\_Irecv match, while MPI\_Bcast as sender and MPI\_Recv as receiver do not. What's more, parameters of the operations, such as the sender and receiver ID, size of the message, tags, and the communicator, need to match as well to ensure correct routing from the source to the destination.

**One-sided communication** Unlike two-sided communication, one-sided communication does not need a tuple of matching API calls to work. Instead, one-sided communication uses RMA (Remote Memory Access) to directly access other process's memory without having to communicate with the target CPU or involving it otherwise. Such a memory region has to be first created by the host with MPI\_Win\_create to allow RMA access to the specified memory segment. Then, the memory from that segment can be written to with MPI\_Put or read from with MPI\_Get. The accesses can be synchronized by MPI\_Win\_fence, which partially resembles memory fence operations.

Usually, one sided communication is point-to-point. There are also approaches using RMA in some stages of collective operations, such as in [20], however the communication itself still remains two-sided.

<sup>&</sup>lt;sup>2</sup>The subset of processes involved in synchronization and other collective operations is defined by a communicator – a construct that contains a subset of processes.  $MPI_COMM_WORLD$  is a default communicator containing all processes.

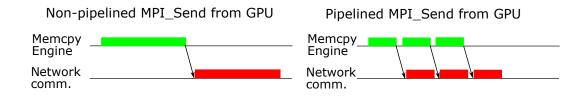

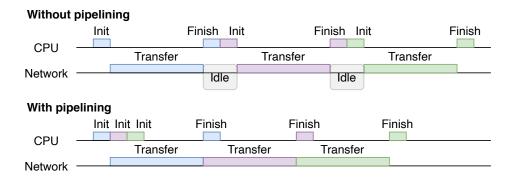

Figure 2.4: Pipelining of memcpy from GPU memory and MPI\_Send.

#### Blocking vs. Non-blocking communication

Some MPI calls wait until the API call has completed, whereas others might return immediately, while the task is still being in progress. An example of a blocking MPI call can be MPI\_Recv that blocks the stream execution until the receive buffer has been written to. Contrary to that, MPI\_Irecv is a non-blocking call. There, the programmer defines the parameters of the received message, however the message can arrive at a later point while the host had worked on other tasks, for example. In order to still have control of the data flow, MPI offers API calls that check the status of a non-blocking call, such as MPI\_Test.

# 2.4 Related research and technologies

Our work focuses, broadly speaking, on communicating data from one GPU to another one with MPI as a layer communicating in between the processes that command the GPUs. There are some existing technologies and there has been a lot of research and a lot of approaches on transmitting data between GPUs.

The majority of the technologies and research available are focussed on CUDA and therefore NVidia devices exclusively. However, it is beneficial to have an overview of those technologies and approaches as well. Some of those technologies exist with an equivalent or similar functionality for AMD hardware, others work exclusively on NVidia devices for the time being.

# 2.4.1 CUDA-aware MPI

CUDA-aware MPI is a broad term that describes an MPI implementation that has built-in functionality for cooperation with potential CUDA devices attached to the node. The functionality can usually be enabled and disabled.

The most common use-case for a GPU-MPI interaction is either sending data located on a GPU over to another MPI process or receiving data for a GPU over MPI. The naive algorithm would copy the data from GPU memory over to the one of the CPU and then trigger MPI communication (or vice-versa for receiving). However, thanks to UVA (Unified Virtual Addressing, introduced in CUDA 4.0), all data on the whole system resides on a single virtual address space. That means, a subspace that belongs to main memory, another subspace that belongs to the first GPU, and possibly another subspaces that belong to the subsequent GPUs or other devices attached have unique address spaces. This way, each address clearly belongs to the main memory or one of the GPU's memories, and the physical location of each piece of data can be identified based on its address. An MPI installation aware of this can use any of the physical memories as a source or target buffer for the transmitted data. Then, the programmer does not have to specifically copy the data between CPU and GPU as this can be taken care of through the CUDA-aware implementation transparently to the programmer. Moreover, depending on the implementation, it can be optimized by pipelining those two data movement operations, as sketched in fig. 2.4. [17]

### GPUDirect

The main performance gain of GPUDirect is its ability to share page-locked memory segments between GPU and MPI. A brief description of page-locked (pinned host) memory was provided in section 2.1.1. Memory copies between CPU and GPU go through main memory's page-locked segment. The same segment is used by MPI to putting data on the interconnect. Normally, a memory transfer via MPI from GPU memory goes in the following way in case of send operation: GPU memory  $\rightarrow$  page-locked CUDA memory (on main memory) ( $\rightarrow$  pageable memory)  $\rightarrow$  page-locked MPI memory  $\rightarrow$  network; and reverse for receive operation. However, with GPUDirect, the copies between CUDA and MPI page-locked memory segments can be omitted, as they can share the same segment. This way, additional memory copies are omitted, therefore the performance is better because there is fewer memory transfers needed. With GPUDirect, a piece of data goes through the following locations in case of send operation: GPU memory  $\rightarrow$  page-locked memory)  $\rightarrow$  page-locked memory transfers needed. With GPUDirect, a piece of data goes through the following locations in case of send operation: GPU memory  $\rightarrow$  page-locked memory shared by CUDA and MPI (on main memory)  $\rightarrow$  network; and again in reverse for receive. [17]

### **GPUDirect RDMA**

GPUDirect RDMA technology is an optimization of GPUDirect. The main idea of this technology lies in MPI being able to access GPU's memory. The data can be transferred from GPU memory directly on the NIC and on the interconnect network. This approach brings two advantages: first, there is less data movement needed in order to perform an operation, and second, the main memory or CPU are not involved in the data movement as the data goes directly from the GPU on the network. This factor reduces stress on the main memory. On the data movement path for a send operation remain only GPU memory  $\rightarrow$  network and the same in reverse for receive. [17]

### **GPUDirect Async**

GPUDirect Async is an evolution of GPUDirect RDMA. The functionality aims on enabling asynchronous MPI communication from GPU kernel's perspective, so that the GPU can trigger MPI operations that were previously prepared by the CPU. This approach can help overlap kernel launch overhead with useful computation – for example, the GPU kernels can be actively waiting for an incoming MPI data transfer instead of launching them after the operation on CPU finishes. However, the communication is still restricted to the kernel boundaries, therefore the overhead of terminating and launching new kernel still impacts the performance. [9,18]

#### Research related to CUDA-aware MPI

There have been many research papers published on extending and optimizing the CUDAaware functionality for various MPI operations and implementations. The authors in [18] compare existing approaches to network communication triggered by GPU. They point out, among other technologies, GPUDirect Async, as one of the recent promising approaches, however they still find the possibility of communication only at the kernel boundary limiting. The reason for that are kernel launch times, which become significant in modern architectures when needing to communicate over the network frequently. "Depending on the size of the kernel stream presented to the scheduler and the details of the target hardware, the launch latencies can vary from 3 µs - 20 µs" [18]. As they point out, the kernel launch overhead becomes an important issue hindering the performance, so they, as well as we, propose a way of communication that does not require killing the kernel. To overcome the problems presented by the existing approaches, they propose an approach 'GPU Triggered networking' where GPUs can post messages directly to NIC. The NIC contains structures previously created by the CPU, that can be located by matching tags. The system can communicate without GPU kernel needing to be killed. Similarly to [18], the authors of [8] propose a framework on one-sided RDMA communication that can trigger network communication from the GPU itself, so that the GPU can communicate without CPU interventions.

The authors in [40] present a GPU-aware extention to MVAPICH2, along the lines of pipelining and overlapping of asynchronous CPU-GPU memory copies and asynchronous MPI communication as sketched in fig. 2.4. [13] focuses on optimizing CUDA-aware MPI for managed memory.

In [15], the authors present an approach to make some functionalities of CUDA-aware MPI available also for OpenACC+MPI and the authors of [28] utilize AMD's DirectGMA technology – a competitor to NVidia's GPUDirect – to make low-latency high-bandwidth DMA data transfers between FPGA and GPU with OpenCL.

An analysis of the available solutions performed at LLNL showed that CUDA-aware MPI-related technologies do not perform well enough in mitigating the overhead caused by involving GPU computation. Their findings can be summarised to the following points:

- When using CUDA-aware MPI, the MPI communication is not triggered before all kernel functions have finished.

- The overhead for launching a kernel multiple times once for packing the data to send and once for unpacking the received data is high and should be reduced.

• The NIC buffers (on Sierra supercomputer) are not large enough to efficiently utilize GPUDirect RDMA or GPUDirect Async. However, this limitation is specific to LLNL's hardware, and may not be an issue at all on other systems.

#### 2.4.2 CPU-to-GPU Callbacks

The authors of [33] developed an approach that lets the GPU overtake some of the CPU's usual responsibilities, such as triggering hard-drive access, network communication, or system calls. The provided implementation, however, does not aim at high performance – it rather eases up the programming effort and makes the code more future-proof. The CPU still remains responsible for performing the tasks. These are, however, requested and triggered by the GPU kernels.

The implementation uses zero-copy memory which can be accessed by both the CPU and the GPU. The GPU can therefore create requests for the CPU by writing to this memory. Equally, the CPU can write to this memory segment to let the GPU know that the callback has finished. This way, GPU kernels can run asynchronously and do not need to wait for the callback to finish. Still, the GPU kernel can poll the status of the callback.

In our approach, a simplified variant of this general idea was used. As there is only a handful of very specific tasks in our approach, there is no need for large generality, such as argument passing logic or using special callback handles, that impact the performance.

There are also other approaches that allow commanding CPU from the GPU. For example, [38] focuses on triggering CPU system calls from the GPU, however this approach is less relevant as our focus is not on system calls.

#### 2.4.3 Other relevant research

**MPI API calls from GPU** There are also approaches that focus on triggering MPI communication from GPU, such as [22]. It enables triggering MPI calls directly from GPU kernel. Similarly to the other approaches, there is a callback to the CPU that performs the MPI call in the background. When waiting for the CPU to execute the MPI request, the GPU kernels have to break. The authors implement this by terminating and starting the kernels again. The registers are stored in and loaded from the GPU global memory to enable continuity of the program flow. This pattern goes against our aim to start the kernels only once per iteration.

Apart from previously mentioned research efforts, there are other research focusses worth mentioning, although they are not that closely related with our work:

Approaches on integrating task-based heterogeneous CPU-GPU programming with MPI, such as [6,31], present ways to dynamically schedule work on host or device.

In [32], the authors propose a universal approach to efficiently pack and unpack various MPI non-contiguous data types on GPUs before or after inter-process communication with MPI. The framework contains multiple schemes that correspond to typical periodicities or shapes of non-contiguous data and selects one of them based on the data type to achieve good performance. A similar, however not as universal approach is proposed in [39]. Both of the approaches were proposed to extend MVAPICH2.

#### 2.4.4 Learnings from related research

There are several patterns that were presented in this section and that could lead to efficiently implementing our solution. Even though CUDA-aware MPI was not used in our solutions mainly because of its lock-in to NVidia hardware, its concepts are still worth considering. Mainly the pipelining of CPU-GPU and MPI communication could bring a speed-up to our solution as well. Moreover, pipelining of those operations should not be hard to implement in HIP so that it works in a platform-agnostic manner – both on NVidia and AMD devices. On top of that, one can consider pipelining the solution at a more general scale. This will be presented more in detail in section 3.6.

Concerning CPU and GPU communication, as well as [33], our solutions also utilize zero-copy memory as main interface for communication. Even though we do not need such generality and focus rather on performance, the main idea of our approach is similar to the one presented in [33].

'GPU Triggered networking' presented in [18] is also an approach worth examining further, but this remains out of scope of this work as the implementation of that would not be very straightforward on AMD devices. Moreover, this solution could also lead to performance degradation for the same reasons GPUDirect RDMA did not work on LLNL's Sierra.

# 2.5 Description of the use-case

In chapter 1, there was a brief summary of the use-case being investigated in this work – the goal is to perform halo exchange between cells located on different GPU nodes. This section will provide more details that specify the use-case further.

We consider a general stencil code with halo exchange at the end (or at the beginning) of each iteration. The stencil code remains undisclosed. When optimizing the performance of the application as a whole, this lack of information would be a limitation. With such limited knowledge of the problem, it is only possible to restrict oneself to a general scenario. As the stencil code is unknown, it is for instance not possible to experiment with overlapping communication (halo exchange) with computation (stencil computation), which is a frequently used technique for increasing performance in such cases. On the other hand, being oblivious to the actual use-case enables developing a universal solution that can be applied to a plethora of implementations that fit the general scenario – distributed stencil computation on multiple GPU nodes.

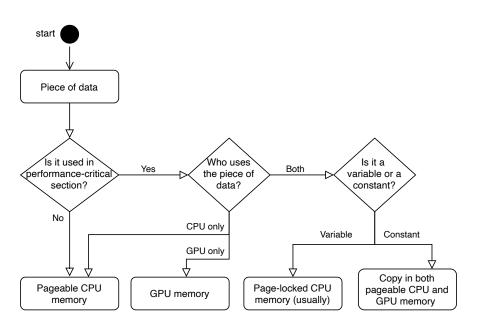

Such a demarcation of the use-case sets the overall workflow of the application. The application runs for multiple iteration and each iteration consists of an arbitrary stencil computation that takes place on GPUs and a communication round. Before the communication procedure starts, the data relevant for the communication is located on the main memory (CPU). Nevertheless, the data produced by the stencil computation is not ready to be sent directly. Instead, it has to be preprocessed before sending, which consists in writing data to a contiguous *send buffer*. This procedure will be referred to as **packing**. Analogously to that, the same procedure in reverse (will be called **unpacking**) takes place on the receiving side. Unpacking is a procedure where the data received in one piece in *receive buffer* (or *recv buffer*) is processed the inverse way to packing and as a result,

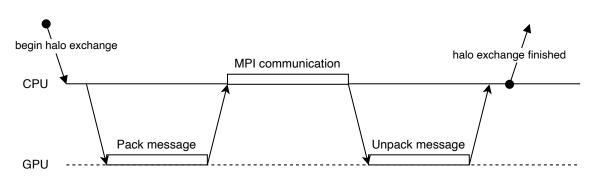

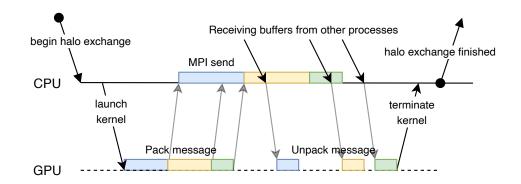

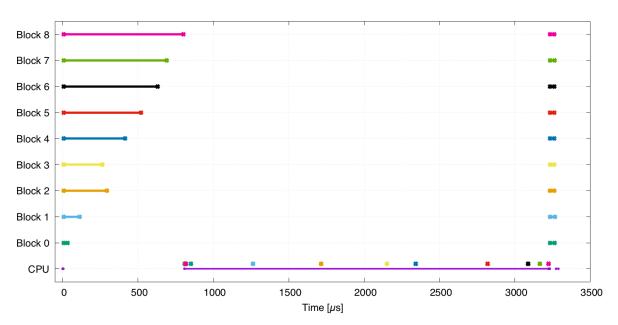

**Figure 2.5:** General workflow of the halo exchange. First, the GPU packs the message to send in send buffer. Next, the CPU communicates over MPI. Once the communication finishes, the GPU can unpack the message in recv buffer.

the data is available for the next stencil iteration in the form and on the address the next stencil iteration expects it. Our implementation remains oblivious both to the stencil code as well as the way the data is packed and unpacked. In the measurements, mock workloads were used instead. There are multiple possible use-cases for implementing packing and unpacking functionality. The most common and simplest is gathering non-contiguous data into a contiguous buffer to ease MPI communication when the MPI implementation does not deal well with non-contiguous data transfers. Other, less common use-cases, may optimize packing routing to skip sending some boundary data that do not change between iterations so the old value remains up-to-date. Next, it can be used for compressing or aggregating the data so that the amount of data sent over the network is reduced. Finally, one may need to encrypt and decrypt the data if there is a need to not send the data in plaintext over the network. Regardless of the use-case, the packing and unpacking is parallelized and takes place on the GPU as well, in order for it not to be the bottleneck that hinders the performance of the application.

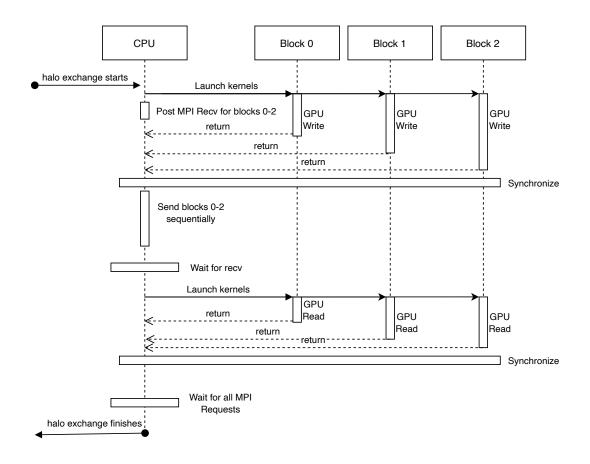

The halo exchange consists of multiple steps. Before it begins, the stencil computation resulted in writing to multiple memory locations on the CPU. First, the input data needed for the packing function needs to be made available for the GPU. Then, the packing takes place. As soon as packing finishes, the resulting buffer is communicated to another GPU (be it on the same or different node). Finally, the received data is processed (unpacked) on the target GPU and made available to the CPU so that it can start the next stencil iteration. Each GPU block has its own buffer so this process is performed for each block. The workflow can be seen in fig. 2.5.

Halo exchange in general needs to deal with parallelism on multiple stages:

- There are multiple MPI processes (ranks) be it on one or multiple physical nodes that communicate among each other.

- Each MPI process may be split further in threads to deal with concurrent tasks on the CPU side more efficiently. We, however only consider one GPU per MPI process.

- Each GPU is split into blocks that work independently on each other. They work on

independent sets of data and the resulting data of each block may be communicated with different MPI rank.

• Each GPU block is expected to exploit GPU's SIMT and SIMD parallelism., i.e. it consists of multiple threads.

#### 2.5.1 Detailed specification

There are some details that further specify the examined use-case and set some boundaries to the problem dimensions.

- The lifetime of kernel functions for packing and unpacking is bounded by the halo exchange segment. That means, the kernel functions cannot start before the current iteration of stencil computation has finished and it must be terminated before the next stencil iteration begins.

- The grid size for packing and unpacking is (up to) 27 blocks. The grid consists of  $3 \times 3 \times 3 = 27$  blocks. Each block may consist of multiple threads.

- Even though each block may exchange data with a different GPU, an arbitrary block b always sends data to block b and receives data from block b.

- The size of the *send* and *receive buffers* may differ for each block and can range from 8 B to 1 MB ( $=1 \times 10^6$  B). The sizes of the *send buffer* and the *recv buffer* are the same for each block. Obviously, block b has the same size on both the sender and the receiver GPU.

- The size of each block is defined at the beginning of the program and does not change.

- The sender and recipient of each block's buffers are defined at the beginning of the program and do not change.

- The halo exchange finishes when all blocks of all GPUs finished unpacking, the unpacked data is available to the CPU, and the unpacking kernels have terminated.

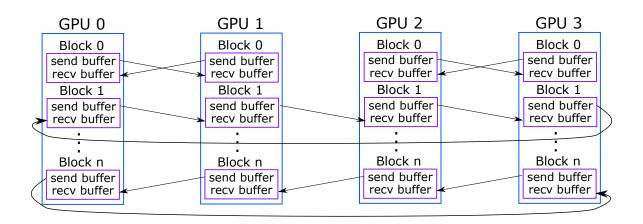

Figure 2.6 illustrates a possible communication scheme for 4 GPUs, which in our case also maps to 4 MPI processes. In this example, different blocks receive data from and send data to different GPUs. While for block 0, the data is sent to and received from rank + 1for even and rank - 1 for odd indices, for blocks 1 and n, the send operations are directed to (rank + 1)%size and (rank - 1)%size, respectively. An interesting observation is that for block 1 (and analogously for block n), all GPUs have the same buffer sizes. This is the case due to the fact that for those blocks, all GPUs are connected with each other. Contrary to that, communication concerning block 0 can be split into two subsets where the GPU communication scheme is interconnected – {GPU 0, GPU 1} and {GPU 2, GPU 3}. The buffer sizes on block 0 can therefore be different for those subsets.

**Figure 2.6:** An example communication scheme. Block x always communicates with block x of another GPU. In this example, block 0 exchanges data pairwise – with preceding and succeeding GPU, respectively, data of block 1 is sent to the succeeding GPU and data of block n is sent to preceding GPU.

# 3 Design and Implementation

Transferring data between GPUs in halo exchange was examined from many perspectives. On the top of the naive baseline implementation, an alternative approach, that will be referred to as *taskqueue*, was developed. Within this general framework, multiple concepts, that can potentially increase the performance, were considered. Some of these concepts were implemented in order to prove or disprove the performance gain they bring. As these concepts develop different ideas and target different aspects of the process, it is possible to combine more of them into one implementation.

Therefore, one can assign each design decision a dimension and the resulting space will cover all possible options resulting from combinations of the concepts. The following concepts, that were considered and implemented as different variants of the *taskqueue* approach, will be discussed in this section apart from the baseline implementation:

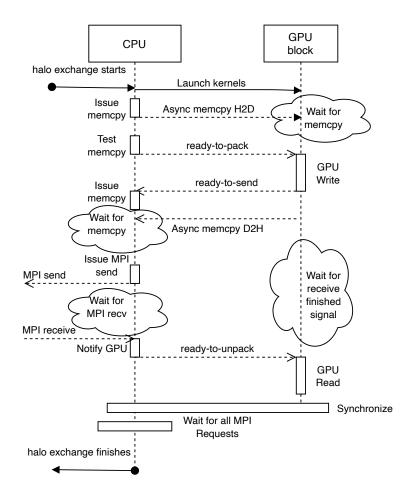

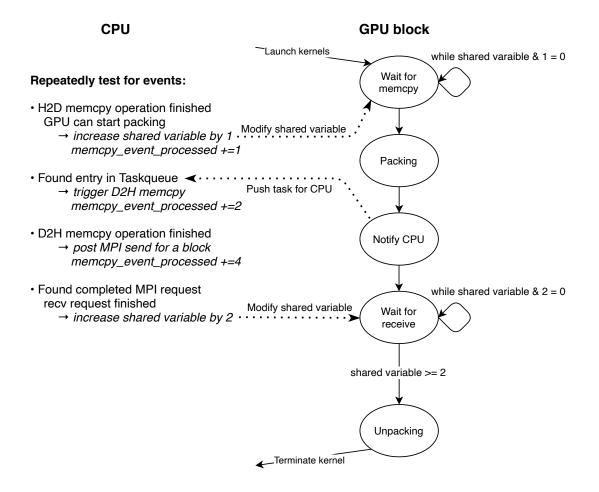

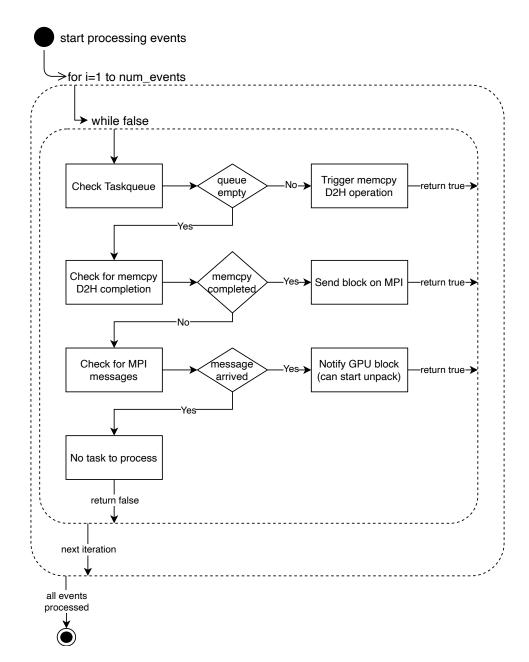

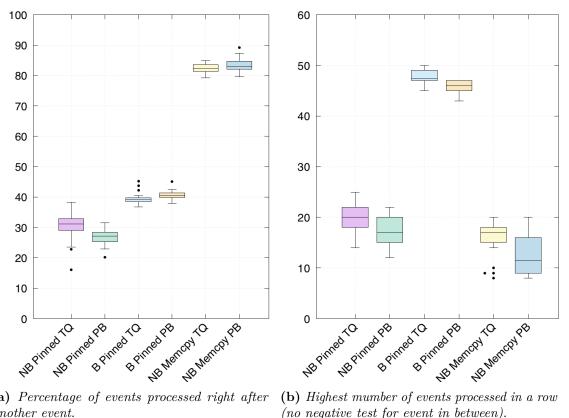

- Task queue vs. per-block channel The original task queue approach uses a single task queue per CPU where all GPU blocks communicate with the CPU. A variation of this is an approach where each GPU block has its own channel for communication with the CPU.

- **Pinned memory** vs. **Memcpy** The GPU reads from and writes to pinned (zero-copy) memory in the first case, or uses memory copies between the host and the device to work with local data. The former is the 'standard taskqueue' approach. The latter will be referred to as *memcpy* or *device memory* approach.

- MPI blocking and non-blocking communication The send operations are done either with blocking (MPI\_Send) or non-blocking (MPI\_Isend) MPI calls. The receive operations are always non-blocking MPI\_Recv.

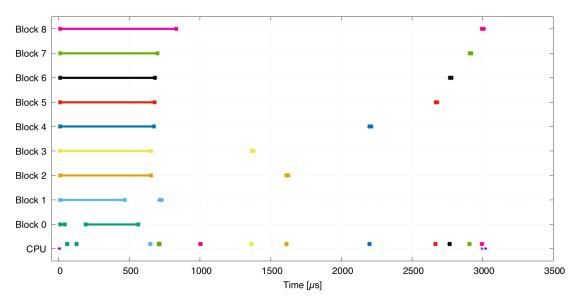

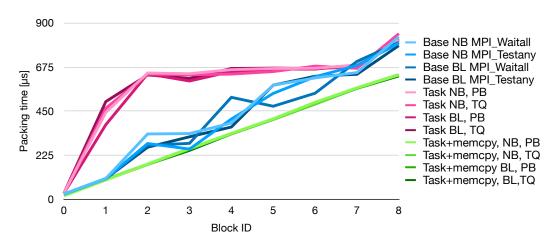

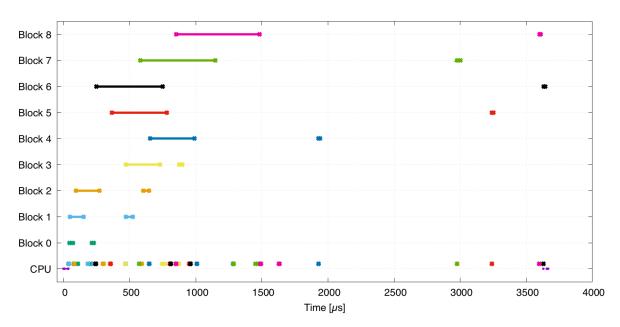

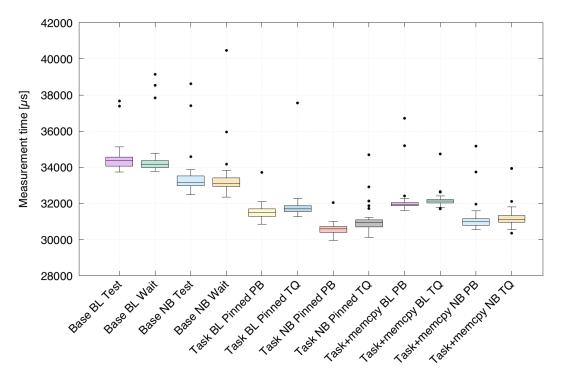

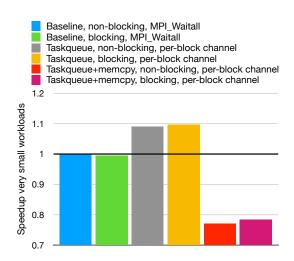

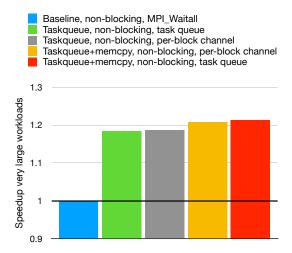

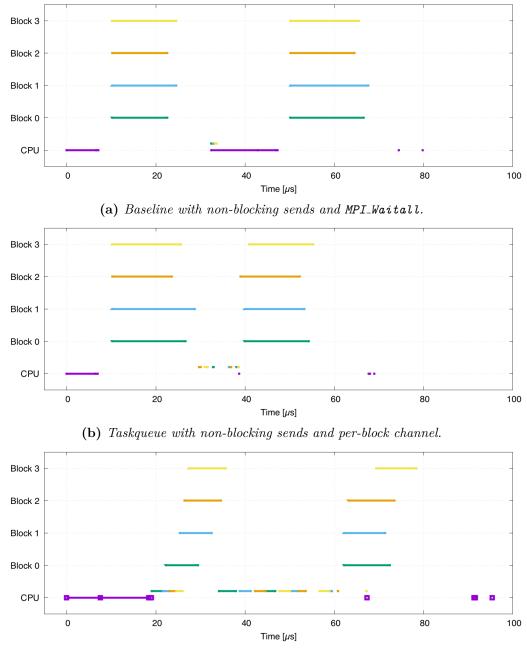

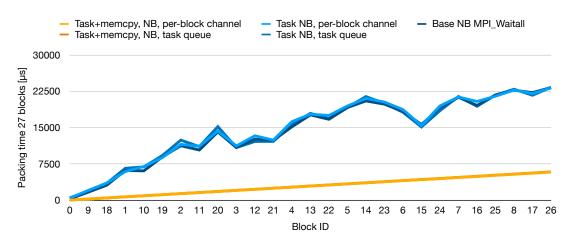

Having many possible implementations resulting from the combination of the different options, it is possible to implement them and measure the performance both against each other and against the baseline code. Tables 3.1 and 3.2 (3.1 for baseline and 3.2 for taskqueue) show the concepts that were developed and the options that rise from combining the approaches.