Technische Universität München Fakultät für Elektrotechnik und Informationstechnik Lehrstuhl für Schaltungsentwurf

## Design of a 9-50 GHz CMOS Integrated Readout Circuitry for Spin Wave Characterization

### Eugen Egel

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs**

genehmigten Dissertation.

Vorsitzender: Prof. Dr.-Ing. Werner Hemmert

Prüfer der Dissertation:

- 1. Prof. Dr.-Ing. habil. Markus Becherer

- 2. Assoc. Prof. György Csaba, Ph.D.

Die Dissertation wurde am 12.09.2019 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 10.02.2020 angenommen.

## Abstract

Most Complementary Metal-Oxide-Semiconductor (CMOS) based circuits consume very high-power at microwave frequencies. Emerging Spin Wave (SW) based devices may offer an alternative to CMOS in certain high-speed signal processing applications, e.g. the computation of the Fourier transform. SW devices inherently operate at frequencies in the range of tens GHz and carry very low energy. It makes the SW devices potentially energy efficient, but the challenge of an effective SW detection remains. Current SW detectors require Brillouin Light Scattering (BLS) equipment or external network analyzers connected to wave guides, but an on-chip SW characterization is still missing. However, it is needed for production ready applications.

Here, it is assumed that SWs will be detected using an on-chip loop antenna located below a thin, insulating magnetic Yttrium-Iron-Garnet (YIG) film. Micromagnetic simulations indicate that a near field loop antenna with an area of  $1 \,\mu\text{m}^2$  could recover a signal power of -80 to  $-90 \,\text{dBm}$ .

Starting with the model of an on-chip loop antenna as a sensing element for SWs, the readout circuitry is designed and simulated using 40 nm CMOS technology. This is done in order to characterize the detected SWs in regards to their frequency, amplitude and phase. The readout system covers operating frequencies of 9-50 GHz with a SW detection resolution of better than 20 MHz. The analysis shows that a signal power of less than -90 dBm, induced in the transducer, can be detected. The measurement resolution of the induced voltage in the antenna is below  $2.5 \,\mu$ V. For the phase shift measurement, the deviation from an ideal curve is expected to be below  $37.8^{\circ}$ . The estimated power consumption of the readout circuitry ranges from 50 mW to 70 mW, depending on the operating frequency.

The presented readout circuitry is highly suitable for on-chip SW characterization and offers an integrated alternative to currently used SW detecting systems. Moreover, this readout system can be modified for other inductive sensing elements, such as microstrip lines or coplanar waveguides. A modification of the readout system for the Direct Current (DC) readout of the combined Spin Pumping (SP) Inverse Spin Hall Effect (ISHE) is also feasible.

# Contents

| 1        | Intr | roduction                                                | 1        |

|----------|------|----------------------------------------------------------|----------|

| <b>2</b> | Spir | n Wave Sensors                                           | <b>5</b> |

|          | 2.1  | Combination of Spin Pumping and Inverse Spin Hall Effect | 6        |

|          |      | 2.1.1 Spin Pumping                                       | 6        |

|          |      | 2.1.2 Inverse Spin Hall Effect                           | 7        |

|          |      | 2.1.3 Spin Wave Detection                                | 8        |

|          | 2.2  | Near Field Coplanar Waveguide Antenna                    | 8        |

|          | 2.3  | Near Field Loop Antenna                                  | 10       |

|          |      | 2.3.1 Resistance of the Transducer Model                 | 11       |

|          |      | 2.3.2 Inductance of the Transducer Model                 | 12       |

|          |      | 2.3.3 Voltage Source of the Transducer Model             | 12       |

| 3        | Fun  | damentals                                                | 15       |

|          | 3.1  | Matching                                                 | 15       |

|          | 3.2  | Scattering Parameters for Two-Port Network               | 16       |

|          | 3.3  | Noise Figure                                             | 18       |

|          | 3.4  | Gain                                                     | 20       |

|          | 3.5  | Linearity                                                | 20       |

|          |      | 3.5.1 1 dB Compression Point                             | 20       |

|          |      | 3.5.2 3rd Order Intercept Point                          | 21       |

|          | 3.6  | Stability                                                | 22       |

|          | 3.7  | Port-to-Port Isolation                                   | 23       |

|          | 3.8  | Phase Noise                                              | 24       |

| 4        | Spir | n Wave Readout Circuitry Design                          | 25       |

|          | 4.1  | Reference to the Author's Publications                   | 25       |

|          | 4.2  | General Concept of the Spin Wave Readout Circuitry       | 27       |

|          | 4.3  | Low Noise Amplifier                                      | 28       |

|          |      | 4.3.1 General Considerations                             | 28       |

|          |      | 4.3.2 Functionality of Implemented Topology              | 29       |

|          |      | 4.3.3 Recommended Publications                           | 33       |

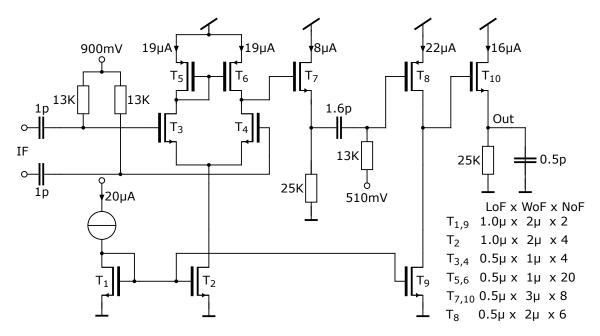

|          | 4.4  | Mixer                                                    | 35       |

|          | . =  | 4.4.1 General Considerations                             | 35       |

|          |      | 4.4.2 Functionality of Implemented Topology              | 36       |

|          |      | 4.4.3 Recommended Publications                           | 40       |

|          |      |                                                          | -        |

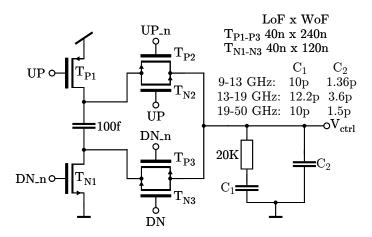

|          | 4.5  | Voltage Controlled Oscillator              | 41 |

|----------|------|--------------------------------------------|----|

|          |      | 8                                          | 41 |

|          |      |                                            | 41 |

|          |      |                                            | 41 |

|          |      | 4.5.2.2 LC Oscillator                      | 45 |

|          |      | 4.5.3 Recommended Publications             | 50 |

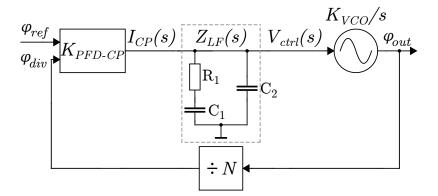

|          | 4.6  | Phase Locked Loop                          | 50 |

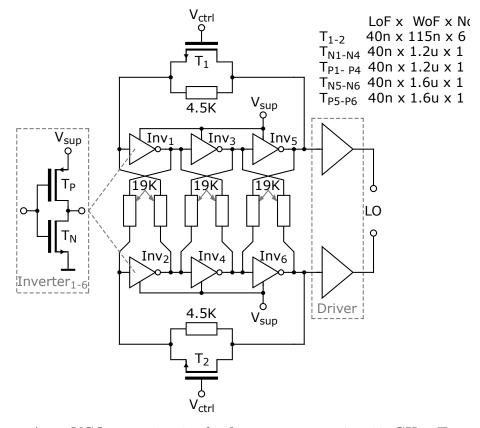

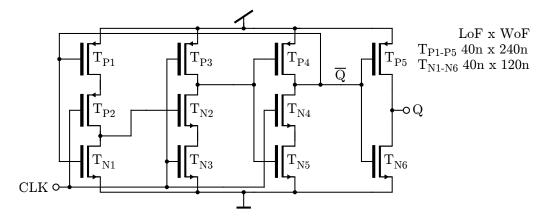

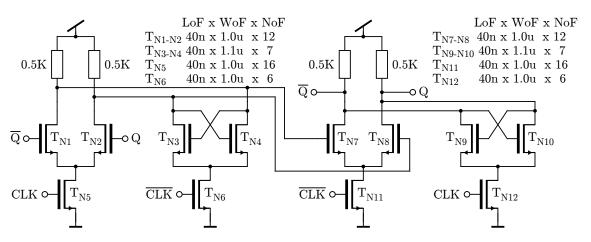

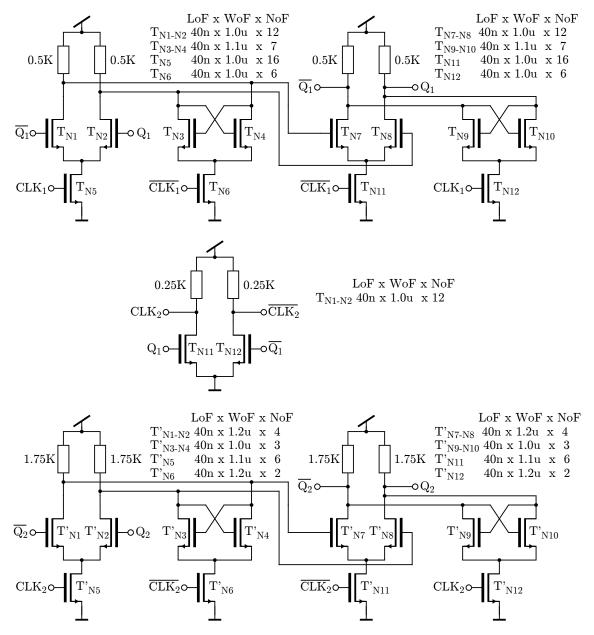

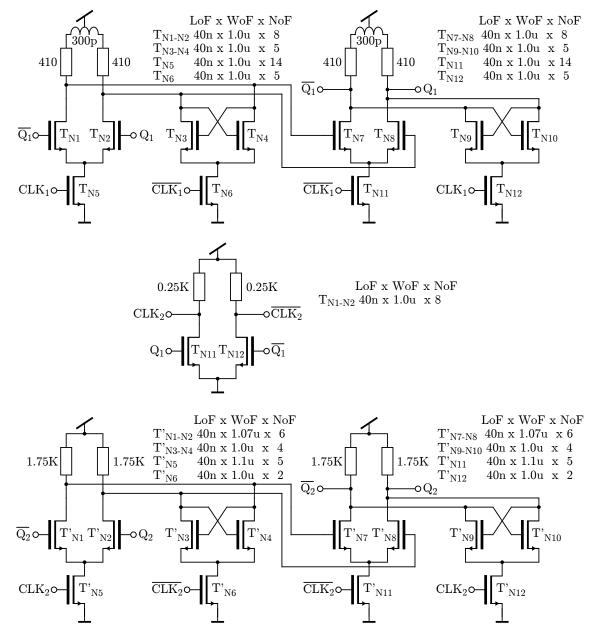

|          |      | 4.6.1 Frequency Divider                    | 51 |

|          |      | 4.6.1.1 True Single-Phase Clocking Divider | 51 |

|          |      | 4.6.1.2 Static Frequency Divider           | 53 |

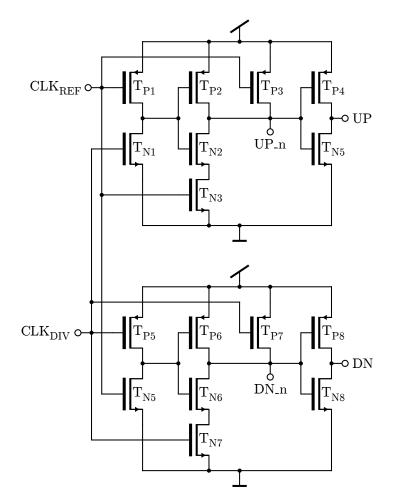

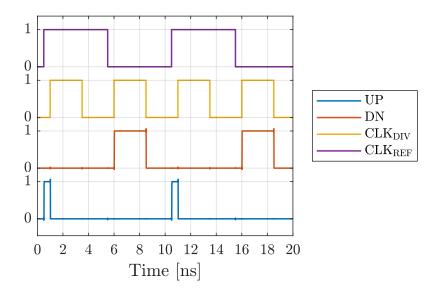

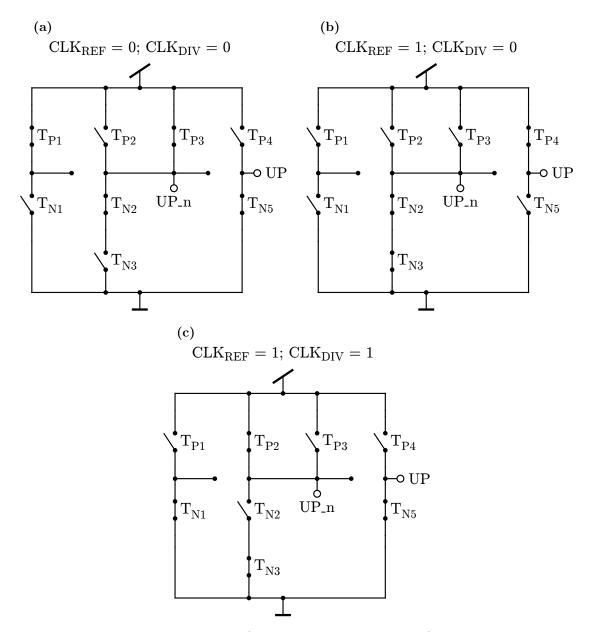

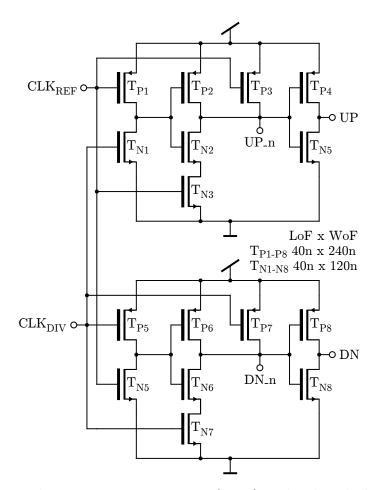

|          |      | 4.6.2 Phase Frequency Detector             | 55 |

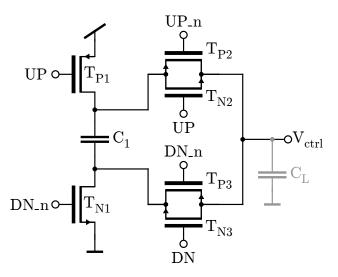

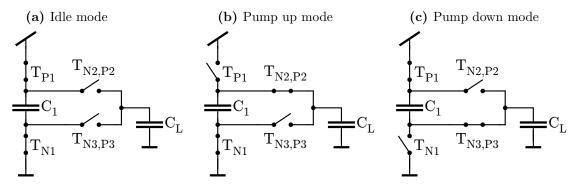

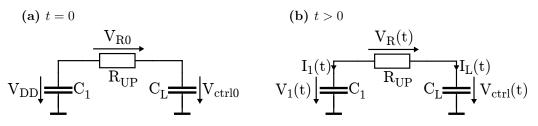

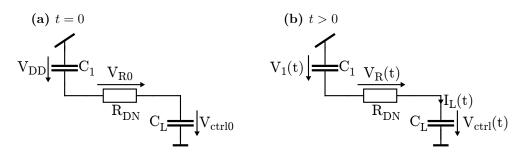

|          |      | 4.6.3 Charge Pump                          | 57 |

|          |      |                                            | 62 |

|          |      | 4.6.5 Recommended Publications             | 65 |

|          | 4.7  | Operational Amplifier                      | 66 |

| <b>5</b> | Sim  | ulation Results of the Readout Circuitry   | 69 |

| Ŭ        | 5.1  |                                            | 69 |

|          |      | -                                          | 69 |

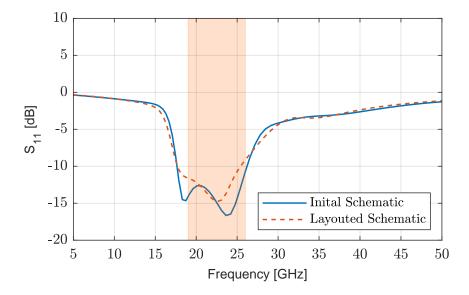

|          |      | 5.1.2 Input Matching                       | 71 |

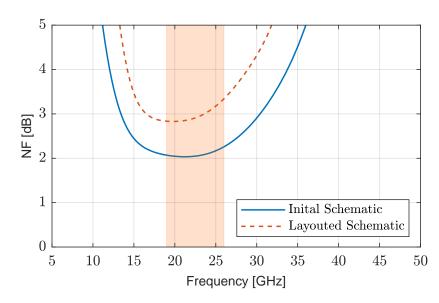

|          |      | 5.1.3 Noise Figure                         | 71 |

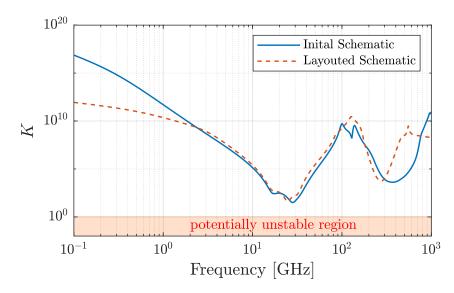

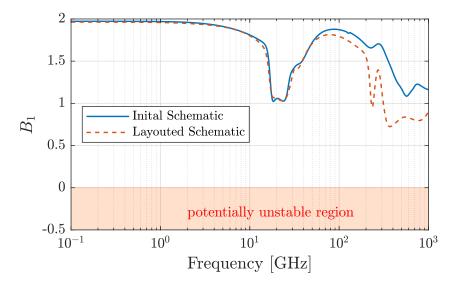

|          |      | 5.1.4 Stability $\ldots$                   | 71 |

|          | 5.2  | Mixer                                      | 73 |

|          |      | 5.2.1 Conversion Gain                      | 73 |

|          |      | 5.2.2 Noise Figure                         | 74 |

|          |      | 5.2.3 Port-to-Port Isolations              | 75 |

|          |      | 5.2.4 Distortion                           | 75 |

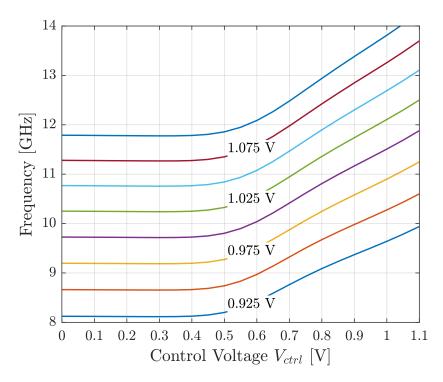

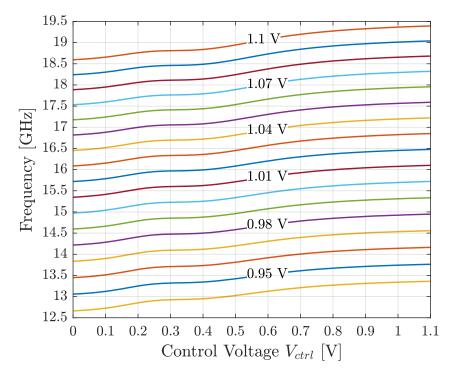

|          | 5.3  | Voltage Controlled Oscillator              | 76 |

|          |      | 5.3.1 Frequency Tuning                     | 76 |

|          |      | 5.3.1.1 Ring Oscillator                    | 76 |

|          |      | 5.3.1.2 LC Oscillator $\ldots$             | 79 |

|          |      |                                            | 80 |

|          | 5.4  | Phase Locked Loop                          | 81 |

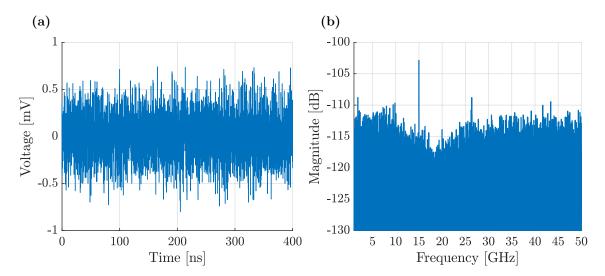

|          |      | 5.4.1 Phase Noise                          | 81 |

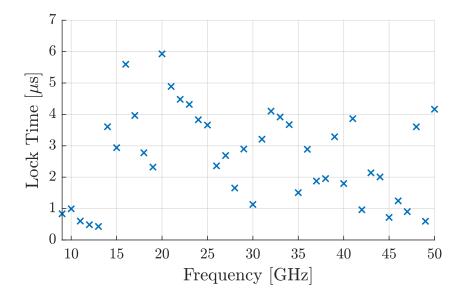

|          |      | 5.4.2 Lock Time                            | 82 |

|          | 5.5  | Operational Amplifier                      | 83 |

| 6        | Spir | n Wave Characterization                    | 85 |

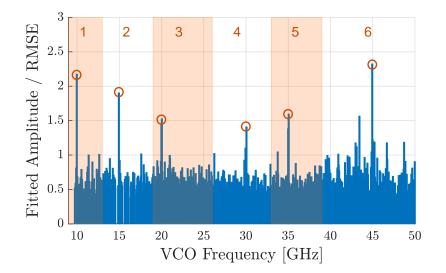

|          | 6.1  |                                            | 86 |

|          | 6.2  | Amplitude                                  | 88 |

|          | 6.3  | Phase                                      | 89 |

| 7        | Imp  | oact of Interconnect Parasitics            | 91 |

| 8        | Cor  | nclusion                                   | 97 |

| -        | 8.1  |                                            | 97 |

|          | 8.2  |                                            | 98 |

|          |      | -                                          |    |

| A                     | Schematics with Electronic Device Values | 101 |

|-----------------------|------------------------------------------|-----|

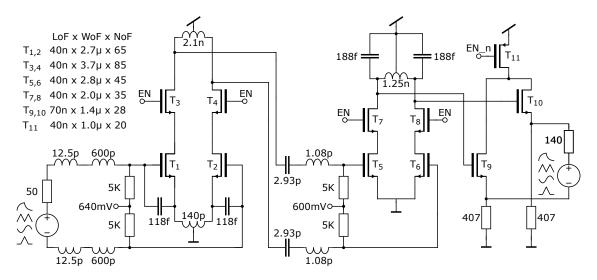

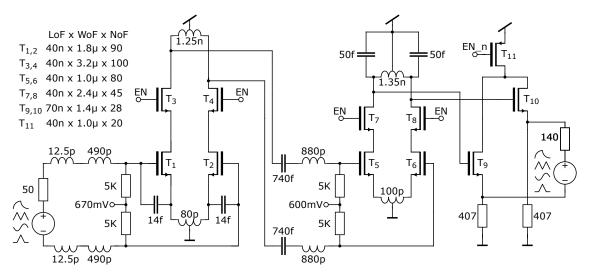

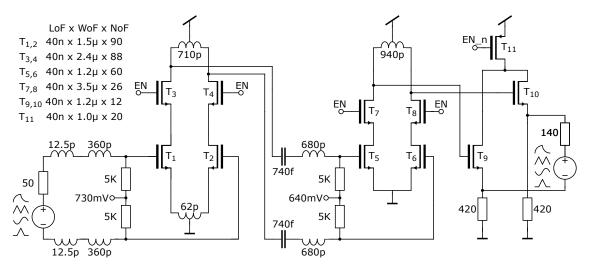

|                       | A.1 Low Noise Amplifier                  | 101 |

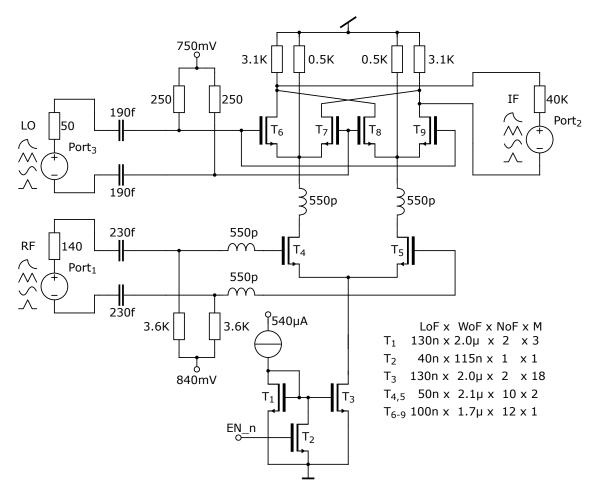

|                       | A.2 Mixer                                | 105 |

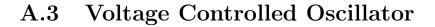

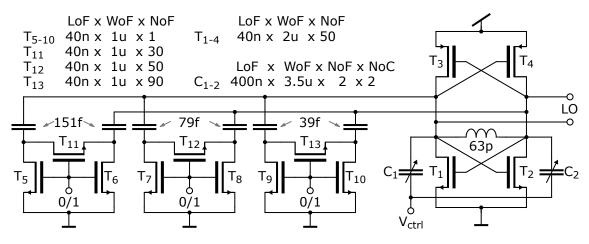

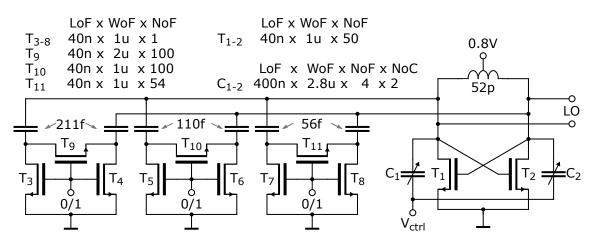

|                       | A.3 Voltage Controlled Oscillator        | 106 |

|                       | A.4 Phase Locked Loop                    |     |

|                       | A.5 Operational Amplifier                |     |

| в                     | Simulation Results                       | 115 |

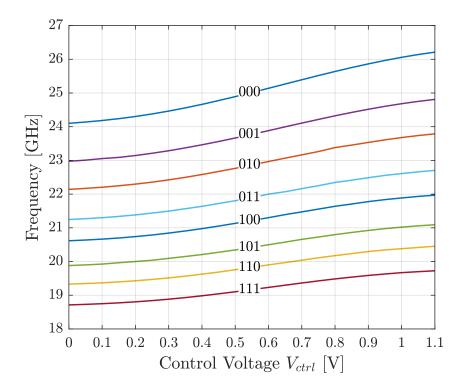

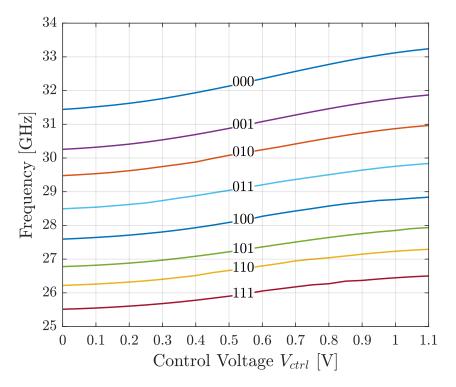

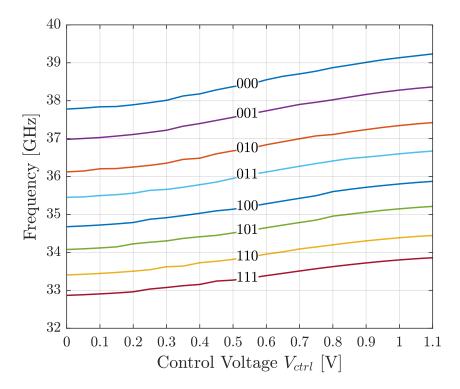

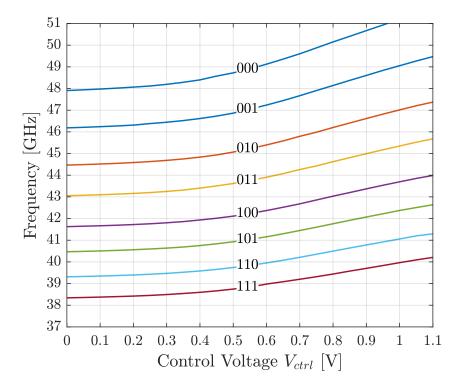

|                       | B.1 VCO frequency tuning                 | 115 |

| С                     | Matlab Code                              | 119 |

| Acronyms              |                                          |     |

| List of Figures       |                                          |     |

| List of Tables        |                                          |     |

| Bibliography          |                                          |     |

| Author's Publications |                                          |     |

| Ac                    | cknowledgements                          | 153 |

## Chapter 1

## Introduction

Today, CMOS is the leading technology used in Integrated Circuits (ICs). The tremendous progress in downscaling CMOS technology nodes over the past few decades has enabled the development of new products, like smartphones or home automation systems, that were inconceivable 20 - 30 years ago. Such innovative products have radically transformed both our society and the way we live, commute and communicate.

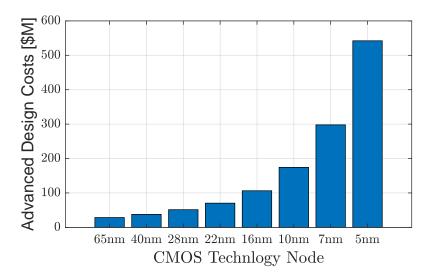

The leading companies in the semiconductor industry have already started with the production of the 7 nm node technology and 3-5 nm nodes are expected to be production ready in the next 3 years [2,3], providing even more computation power per unit area. However, such advanced technology nodes mean enormous costs for research and development. Moreover, the design costs (e.g. qualification, physical and software design, verification, prototype, validation) for advanced technology chips are rising as well [1]. Figure 1.1 shows the rising design costs of the advanced

**Figure 1.1:** Rising design costs for the advanced technology nodes. Costs include Intellectual Property (IP) qualification, architecture, verification, physical and software design, prototype, validation. [1]

nodes, as a consequence the number of companies going to use these advanced technologies is limited. Hence, GlobalFoundries, one of the leading semiconductor companies, recently announced that they are ceasing from the production of the 7 nm technology due to high costs [4].

Experts also see a twilight of the Moors Law in the CMOS technology. Downscaling the size of transistors is becoming challenging due to quantum effects [5]. However, this does not mean the end of progress. Alternatives, like the Tunneling Field Effect Transistor (TFET), Nanomagnetic Logic (NML), SW devices and the recently introduced Magnetoelectric Spin-Orbit (MESO) devices [6], are considered as extension of the CMOS technology or even going beyond with promising performance in low power applications [5,7]. Considering delays and energy per Arithmetic Logic Unit (ALU) operation, there are only few devices, such as TFETs, that could outperform CMOS in traditional Boolean computing [8], postulated by Shannon [9]. SW devices provide a possibility to execute both Boolean and non-Boolean computations. However, the experts see potential in SW devices especially for non traditional wave based computing, similar to optical computing [10], as they could perform more efficiently at image and video processing tasks [11, 12].

The general idea of SW devices (see Figure 1.2) is: (1) convert a charge current into a magnon current, in order to process the information in a magnonic domain and (2) convert back the SW signal into the electronic domain for post processing [13]. Transistors, as a key element in today's ICs, are also feasible in magnonics and could play a significant role for signal processing in emerging magnonic systems. In [14]

Figure 1.2: Schematical overview of the conversion between electronics, spintronics and magnonics with charge of electrons, spin of electrons and magnon, accordingly, as quanta for information processing. The electronic domain is used to control transducers converting the signal into the magnonic domain, where information is processed in an energy efficient way and is finally converted back into the electronic domain. Figure is adopted from [13, Figure 1].

Chumak describes the operational principle and physical mechanisms of a magnon transistor based on the four-magnon scattering mechanism. The theory and a prototype of the magnon transistor as a switch, based on SW interference, are published by Balynsky in [15, 16]. A majority gate, as another component in the magnonic system, is also experimentally proven [17–20]. From theoretical point of view Csaba and Papp show a SW device for computing Fourier transform, that could consume much less power than modern Central Processing Unit (CPU) performing the same Fourier transform operations [12, 21]. Similar to the Fourier transform calculation in optics, a magnetic lens can be used to manipulate propagating SWs [22].

The main advantage of spintronics, as compared to conventional electronics, is the energy efficiency due to the absence of an electrical current and the corresponding producing Joule heating. For signal processing the coupling between electron spins is used instead of electron transport, as a consequence no additional electromigration. [13,23]

Besides, fast and power efficient data processing is made possible by the operation frequency of SW devices in a GHz to THz range at room temperature [24, 25]. It could play a significant role in analyzing huge amounts of data in a very short time in future applications such as autonomous driving or content searching and pattern recognition in video files.

One of the first SW related papers was published in 1963 by Schlömann, who investigated the conversion of electromagnetic power into SW power from a theoretical point of view [26]. Today, magnonics has become one of the most intense research areas worldwide as it is seen as a candidate for going beyond CMOS technology.

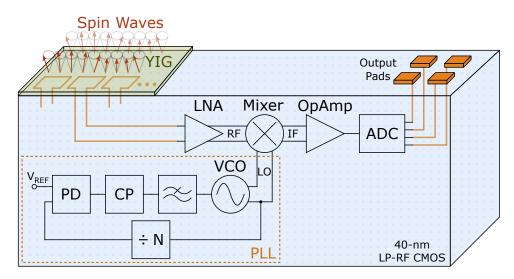

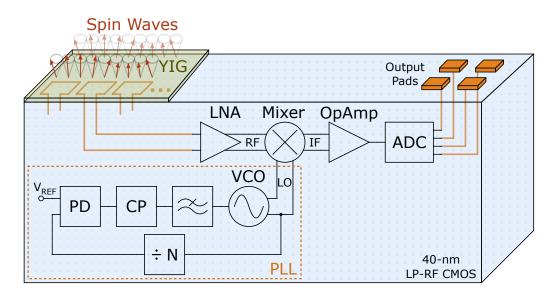

Figure 1.3: Conceptual schematic of Spin Wave (SW) on-chip detection. The SWs, propagating in the YIG film, are picked up with near field on-chip antennas. The transduced signal is processed in a CMOS Integrated Circuit (IC) (see Chapter 4). Information about SW frequency, amplitude change or phase difference between two SW signals is provided at the output pads in a digital form.

Nevertheless, the interface between a SW system and an electronic system remains one of the biggest bottlenecks to the integration of SW devices in consumer applications [21, 27, 28]. Producing SW devices on a single chip with CMOS technology is challenging, since efficient interfaces between a SW device and an electronic system are required.

There are several mechanisms for SW generation. A common way of SW excitation is a stripline with an AC current placed next to a SW propagating area [29]. Another possibility is usage of the Spin Hall Effect (SHE) [30, 31] or spin-torque nano-oscillators [32].

For the detection of the SWs Brillouin Light Scattering (BLS) [33] spectroscopy is often used [22, 32]. Picking up the SW signal with a small near field antenna is another method for the detection [13]. A brief overview of SW sensors is given in Chapter 2.

A single SW device or even a whole magnonic system integrated with a CMOS circuitry could look like the concept depicted in Figure 1.3. There is no integrated SW device to this date, enabling the characterization of propagating parameters of the SW such as the frequency, amplitude or phase. Instead, relatively bulky and expensive measurement setups are used for this purpose. But on the long run, if the trend goes to analyze SWs with low costs and to offer products with magnonic systems inside, it is obvious that SW devices have to be integrated together with electronics on a single chip or alternatively with a flip chip method.

In this work the concept for an on-chip SW device characterization is developed. Based on assumptions made for the near field loop antenna (see Chapter 2), the CMOS readout circuitry is designed. The operating principle is based on a heterodyne receiver, as depicted in Figure 1.3. The picked up SW signal is amplified by a Low Noise Amplifier (LNA) at Radio Frequency (RF) and millimeter Wave (mmW). Afterwards, the signal is down-converted by a mixer to Intermediate Frequency (IF). Local Oscillator (LO) signal, required for the mixer, is generated by a Voltage Controlled Oscillator (VCO), which is controlled by a Phase Locked Loop (PLL). Finally, an Operational Amplifier (OpAmp) additionally amplifies the IF signal, before it can be digitized by an Analog-to-Digital Converter (ADC).

In order to evaluate the performance of the designed circuitry (LNA, mixer, VCO, PLL and OpAmp) some fundamental parameters are described in Chapter 3. The operation principle of the CMOS building blocks, depicted in Figure 1.3, is explained in more detail in Chapter 4 and their simulation results are described in Chapter 5. In this thesis, the circuitry design is focused on the components affecting the output of the OpAmp, i.e. the design of an ADC is not considered. However, the ADC design at lower operating frequencies (10 - 60 MHz) is relatively straightforward. Hence, the SW characterization regarding its frequency, amplitude change and phase shift is done at the OpAmp output and is demonstrated in Chapter 6. For the first order approximation of the interconnect parasitics and their influence on the circuitry performance, the layout of the LNA is created and described in Chapter 7. Chapter 8 concludes the dissertation and proposes further development steps of the SW readout circuitry.

## Chapter 2

## Spin Wave Sensors

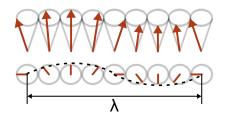

SWs are the propagating stimuli of electrons magnetization. Similar to the phonons as quasiparticles of lattice vibrations in a solid state, the SWs can be described by its quasiparticles, the magnons. While lattice vibrations are defined by the deflection of neighboring atoms from its equilibrium state, the SWs are described by the phase relation of precessing magnetic moments of neighboring electrons [34, pp. 12-13]. The visualization of a SW with its wave length is depicted Figure 2.1. The excitation of a spin results in the delayed deflection of the neighboring spins, which excite the next spins. Such propagation of the deflected spins forms the Spin Wave (SW). For more fundamental physical background of the SWs and the mathematical descriptions of its device models, the reader is referred to [13, 35–38] as well as to the recent magnetism roadmap [39].

Figure 2.1: Sketch of the excited electron spins magnetized in same direction, forming the Spin Wave (SW). The wave length is defined as a distance of the excited spins with the same phase.

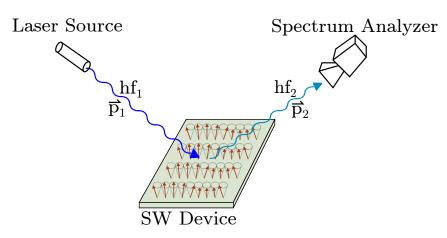

In order to analyze SWs, X-ray spectroscopy [40] or time-resolved Magneto-Optic Kerr Effect (MOKE) [41] can be used. However, the commonly used technique for detecting and characterizing the SW device probes is  $\mu$ -BLS [33]. Especially, the possibility to visualize the spacial propagation of the SWs with high temporal resolution makes this equipment attractive for research. The SW frequencies up to 500 GHz with a resolution around 50 MHz can be measured [33]. The simplified operating principle of the BLS is sketched in Figure 2.2. A probe with propagating SWs is irradiated with a monochromatic laser light of certain energy  $hf_1$  and momentum  $\vec{p_1}$ . Based on the spectrum analysis of the reflected light with energy  $hf_2$ and momentum  $\vec{p_2}$ , a statement can be made about propagating SWs in the sample.

Figure 2.2: The principle of the BLS measurement technique for SW characterization. The frequency difference of the incident and scattered waves is used to analyze the SWs propagation in a sample. The spectrum analysis of the reflected electro-magnetic wave is performed with a Fabry–Pérot interferometer [33].

For more details of the  $\mu$ -BLS measurement technique for SW characterization the reader is referred to [33].

There are several possibilities to transduce the SW signal into electronic domain. Each of them has right to exist for certain applications with their pros and cons. However, only some of the SW transducers with acceptable performance and lowest manufacturing costs will dominate the market or certain market niche. In this chapter SW sensors with a potential to be integrated with an electronic system [35, p. 36], directly or with flip chip method, are briefly described.

### 2.1 Combination of Spin Pumping and Inverse Spin Hall Effect

In order to understand the sensing principle of the SWs by the combination of the Spin Pumping (SP) and Inverse Spin Hall Effect (ISHE), each of the both processes is separately described in the following subsections.

### 2.1.1 Spin Pumping

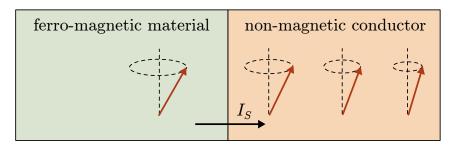

In simple terms, the SP is a generation process of spin current from magnetization dynamics [42, p. 2]. This phenomenon occurs at the interface between a magnetic material and a metallic conductor, i.e. the SWs in magnetic material pump the spin current into the adjacent conductor. The corresponding theory of the SP is proposed by Tserkovnyak [43]. As depicted in Figure 2.3 the spin orientation in the magnetic material aligns the electron spins in the non-magnetic metal, resulting in the spin current  $I_S$  perpendicular to the spin orientation. Besides, the propagating torque of the magnetization precision decreases by entering the metallic region, due to enhanced Gilbert damping.

The reciprocal effect of the SP is the Spin Transfer Torque (STT), i.e. from the

Figure 2.3: Spin Pumping (SP) effect by contacting the magnetic material with a non-magnetic metallic conductor. The magnetization dynamics in magnetic materials result in the spin current  $I_S$  flowing into the adjacent conductor.

spin current in the conductor the SW in the magnetic material like YIG can be excited. To generate the spin polarized current, the conventional charge current has first to be passed through the magnetic material with a certain magnetization direction. [42]

#### 2.1.2 Inverse Spin Hall Effect

The Hall effect, discovered by Edwin Hall in 1879 [44], describes the movement of electrons in a conductor while applying an external magnet field. Due to the Lorentz force, the electrons deflect from their moving direction perpendicular to the current and the external magnetic field directions. This results in the Hall voltage at the appropriate conductor edges proportional to the strength of the applied magnetic field.

A similar effect is considered for the spin current, generated from the charge current, even without an external magnetic field. The SHE is postulated by Dyakonov and Perel [45, 46]. The first experimental proves of the ISHE and SHE are provided by Bakun [47] and Kato [48], respectively. The reciprocal effect to the SHE is the ISHE, that is used to convert the spin current into the electrical charge current [49, 50].

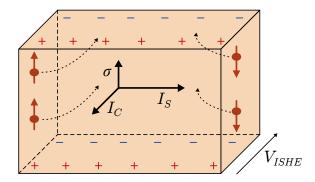

The schematic visualization of the ISHE is shown in Figure 2.4. From [49] we know,

Figure 2.4: Sketch of the working principle of the Inverse Spin Hall Effect (ISHE). The spin current  $I_S$  with the spin polarization  $\sigma$  results in the electrical charge current  $I_C$  and the ISHE voltage  $V_{ISHE}$  [49].

that the electrical current  $I_C$  is proportional to the cross product of the spin current  $I_S$  and the spin polarization  $\sigma$

$$I_C \propto I_S \times \sigma.$$

(2.1)

If we assume a spin current  $I_S$  from left to right and the spin-up polarization  $\sigma$ , then the electrons bend into the drawing plane [49]. Same happens with the spin-down electrons flowing from right to left. Consequently, the difference of the potentials, symbolized by plus and minus, results in between the front and the back of the sketched conductor. As shown by Chumak [50], the inversion of the spin current direction leads to the inversion of sign of the measured ISHE voltage  $V_{ISHE}$ .

#### 2.1.3 Spin Wave Detection

The combination of the Spin Pumping (SP) and Inverse Spin Hall Effect (ISHE), described above, [37, 51] can be applied to detect Spin Wave (SW). The SWs, propagating in YIG, can used to generate the spin current in an adjacent conductor and consequently the ISHE voltage, that can be measured and analyzed by an *IC*. It is noted, that the frequency information is lost with this detection methodology and only DC voltage can be transduced to the electronic domain. However, it significantly relaxes the requirements for the IC readout circuitry.

For the nanoscale SW based spectrum analyzer, proposed by Papp [21], the combination SP-ISHE, as the SW sensing element, can be reasonably applied for the SW analysis, alternative to the loop antennas. The frequency information of the SWs is coded in the positions of the placed sensors.

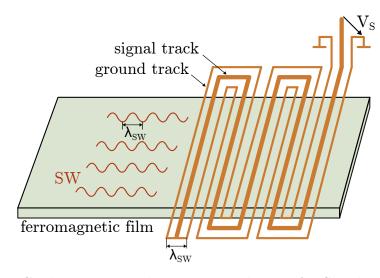

### 2.2 Near Field Coplanar Waveguide Antenna

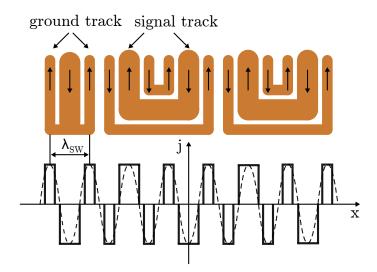

The inductive coupling of the magnetization dynamics can be realized with a coplanar waveguide, which is appropriately sized to the expected SW frequency. Such inductive detection is often called Propagating Spin Wave Spectroscopy (PSWS). Vlaminck [52] demonstrated the SW excitation and detection in 1 - 15 GHz frequency range with the coplanar antenna, as depicted in Figure 2.5. With the coplanar waveguide excited SWs propagate through the ferromagnetic thin film and are picked up by the identical coplanar antenna on the detection side. The signal path of the antenna is inside of two ground tracks serving as return conductors. The width of the signal track is twice of the ground track, in order to keep the sheet resistance of the whole signal path constant. Finally, the induced voltage  $V_S$  in the antenna has been analyzed with a Vector Network Analyzer (VNA) [52]. It is to be noted, that the output port of the proposed coplanar waveguide is suitable for the IC CMOS detection as well.

The folded structure of the coplanar waveguide, proposed by Vlaminck [52], allows precise adjustment of the SW frequency excitation and its detection. The antenna geometry also improves the transduction efficiency between the magnonic and electronic domains [52]. The frequency adjustment is realized by an appropriate sizing

Figure 2.5: Coplanar waveguide as sensing element for SW detection propagating in a ferromagnetic thin film, e.g. YIG. The meander structure of the antenna improves the efficiency of the transduction [52]. The distance between two ground tracks of the waveguide should equal to the wavelength of the propagating SWs, in order to achieve high signal sensitivity (see also Figure 2.6).

of the distances between the signal and ground tracks. To understand this relationship, the spatial current density flow in the antenna is sketched in Figure 2.6. Here we can see, that the distance between two ground tracks of the waveguide results in from the SW frequency. From the assumed fact, that the width of the signal track is twice of the ground track, dimensions of the remaining geometric parameters can be calculated. A detailed analysis of the coplanar waveguide transducer with different geometries is described in [52]. An alternative inductive detection of the SWs

Figure 2.6: Spatial distribution of the current density flowing through the coplanar waveguide. The geometry of the waveguide is selected with the target for achieving a close approximation to a sinusoidal distribution as close as possible. Figure is adopted from [52].

with a U-form waveguide is reported in [53]. Besides, the Propagating Spin Wave Spectroscopy (PSWS) detection methodology is described in [29, 54–56].

### 2.3 Near Field Loop Antenna

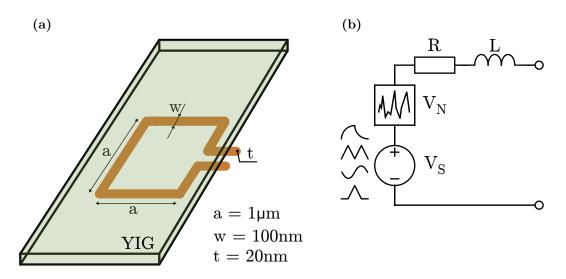

To use the magnetic loop antenna, as a transducer from the SW signal into an electrical one, is the next possibility for the SW sensing [133]. It provides a low resistive and scalable sensing area. The on-chip antenna can be placed below the magnetic thin film with a low damping material, like YIG (see Figure 2.7a).

The model of the loop antenna is approximated by an ideal voltage source with the serial resistance and inductance, as depicted in Figure 2.7b. In addition, the noise source represents mainly the thermal noise, caused by the resistance. The thermal agitation of the magnetic moments is negligible compared to the thermal noise of the 50  $\Omega$  loop resistance. The equivalent resistance of the magnetic noise is in the range of 1 m $\Omega$  [133]. A relatively low magnetic noise originates from the damping of the YIG material. As shown by Scholz [57], the intensity of magnetic fluctuation is associated with the magnetic damping coefficient.

Figure 2.7: Sketch of the loop antenna placed below the non-conductive material YIG (a) and its equivalent circuit model (b). The squared loop antenna has the side length a, width of the wire w and thickness of the wire t. The resistance R and the inductance L result in from the geometry of the transducer. In addition, the model includes the voltage source  $V_S$  with the noise source  $V_N$ , originated mainly from the thermal noise of the conductor.

The integrated loop antenna as a sensor for electromagnetic near-field measurement has been extensively considered by Uddin [58] during his dissertation. Here, based on his work, the first order model of the loop antenna has been derived, i.e. neglecting the eddy currents, dielectric losses, radiation resistance and other second order effects [58, p. 27]. The resulted values for the resistance, the inductance and the voltage source are described below.

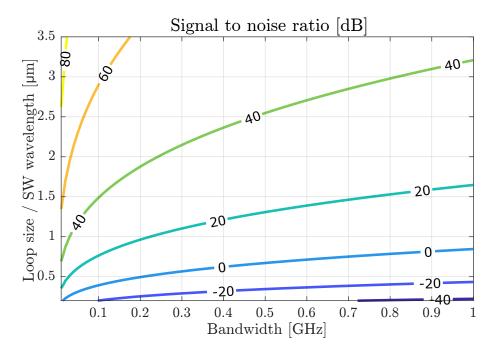

Figure 2.8: Simulated Signal-to-Noise Ration (SNR) of the squared loop antenna depending on its size and the considered bandwidth. The ordinate of the graph is normalized to the wavelength of the SW. As to expect, a larger area and a smaller bandwidth show a better SNR. [134]

As reported in [133], the considered squared loop antenna with an area of  $1 \,\mu\text{m}^2$  could induce signal with an amplitude in the range of tens microvolts. Besides, as depicted in Figure 2.8, the Signal-to-Noise Ration (SNR) is around  $20 - 40 \,\text{dB}$  with a restriction to a 100 MHz bandwidth.

#### 2.3.1 Resistance of the Transducer Model

For the current flowing through a conductor at high frequencies the skin effect has to be kept in mind, i.e. the current density near the surface could be higher than near the middle of the wire's cross section. Thus, the skin depth (Equation 2.2) [58, p. 27] has to be considered for the resistance calculation of the loop antenna

$$\delta = \frac{1}{\sqrt{\pi f \mu_0 \mu_r \sigma}},\tag{2.2}$$

where f is the considered operating frequency of the SW device (9 - 50 GHz),  $\sigma$  is the gold conductivity  $(4.47 \frac{\text{A}}{\text{Vm}})$ ,  $\mu_0$  is the magnetic constant  $(4\pi \cdot 10^{-7})$  and  $\mu_r$  is the relative permeability of the medium.

At the highest considered frequency of 50 GHz the skin depth is around 350 nm. Thus, for the assumed dimensions of the squared loop antenna the skin effect can be neglected, i.e. the current fills the entire cross section. Consequently, the resistance of the transducer can be approximated by the standard formula in Equation 2.3

$$R = \frac{4a}{\sigma w t},\tag{2.3}$$

where a is the side length of the loop antenna equal to  $1 \,\mu\text{m}$ , w is the wirde width of 100 nm and t is the wire thickness of 20 nm. The resulted resistance of the loop antenna is equal to  $49 \,\Omega$ . That fits very well to the transmission line standard of  $50 \,\Omega$ .

#### 2.3.2 Inductance of the Transducer Model

The inductance of a planar square loop antenna can be calculated with Equation 2.4 [58, pp. 27-28]

$$L = \frac{\mu_0 \mu_r 4a}{2\pi} \Big[ \ln\left(\frac{a}{r}\right) - 0.77401 + \frac{\mu_r}{4} \Big], \qquad (2.4)$$

where a is the side length of the loop antenna  $(1 \,\mu\text{m})$ , r is the radius of the wire,  $\mu_0$  is the magnetic constant and  $\mu_r$  is the relative permeability of the medium. The above formula for the inductance calculation is applied for a circular cross section. In order to estimate the inductance for a rectangular cross section, the equivalent radius can be approximated with Equation 2.5 [59]

$$r = \frac{w}{2(1+1.13\log(\frac{w}{t}))}$$

(2.5)

with the width of the wire w equal to 100 nm and the thickness of the wire t equal to 20 nm. With the assumed dimensions, listed above, the inductance of the loop antenna results in 2.44 pH. As reported in [133], the presence of the magnetic YIG film influence the inductance of the loop. Performing the Object Oriented Micro-Magnetic Framework (OOMMF) [60] simulations, the inductance of the transducer model is finally approximated to 25 pH, i.e. the YIG material is the main contributer to the inductance of the transducer.

#### 2.3.3 Voltage Source of the Transducer Model

The induced voltage peak in the loop antenna can be estimated by Equation 2.6 [133]

$$V_S = a^2 f \mu_0 M_s M_{defl}, \tag{2.6}$$

where a is the side length of the loop antenna  $(1 \,\mu\text{m})$ , f is the considered operating frequency of the SW device  $(9 - 50 \,\text{GHz})$ ,  $\mu_0$  is the magnetic constant,  $M_s$  is the saturation magnetization of YIG  $(1.4 \cdot 10^5)$  and  $M_{defl}$  is the relative SW amplitude of 0.01.

Considering the lowest frequency of 9 GHz the induced voltage amplitude is around  $16 \,\mu\text{V}$ . It is important to mention, that the induced voltage is dependent on the size

of the loop antenna and the frequency of the SW device. Besides, the non-considered imperfections at the interface between the YIG and the transducer would highly impact the picked up signal power. Nonetheless, the above considerations show the first estimation of the loop antenna's model, required as input for the readout circuitry, described in Chapter 4. Thus, the induced voltage amplitudes around  $10 - 20 \,\mu\text{V}$  are considered for the 50  $\Omega$  transducer with the self-inductance around  $25 \,\text{pH}$ .

## Chapter 3

## **Fundamentals**

This chapter briefly summarizes the parameters required to characterize circuit components like LNA, mixer and PLL with VCO described in Chapter 4. Here, only basic definitions and statements required for the design are mentioned. For more detailed information the reader is referred to the respective references mostly taken from Razavi [61], Lee [62], Nguyen [63] and Pozar [64].

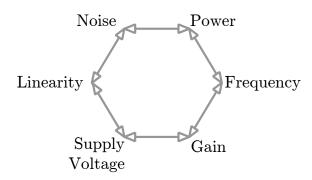

It is obvious that it is impossible to design a circuit while having all parameters at best performance. Thus, trade-offs are required depending on an application. The RF design hexagon depicts this problem in Figure 3.1. In case of the designed spectrum analyzer the trade-offs are made especially between noise, power and frequency. Having a wide frequency bandwidth and, at the same time, high gain over the whole operating frequency is challenging. Thus, the compromises have to be made. Due to the relatively low voltage values, expected at the input of the LNA, the linearity provides less of a concern.

Figure 3.1: RF design hexagon representing trade-offs between parameters, e.g. the smaller the influence of the noise and the wider the operating frequency band, the more power is consumed by the circuit. [61, p. 4]

### 3.1 Matching

If the signal's wavelength reaches the range of device's physical dimensions, then the electronic components can no longer be modeled as lumped elements [64, p. 1], i.e.

poor matching leads to undesirable reflections and possibly voltage attenuations [61, p. 258]. The question arises, whether the matching technique is needed, if the targeted operating frequency of the IC is in the range of 9 - 50 GHz. If the half of the signal's rise or fall time approaches the one-way propagation time along the signal path, the impedance matching between two ports is required [65]. In low- $\kappa$ (dielectric constant lower than 3.9) materials the propagation velocity v of the signal energy is estimated to be

$$v > \frac{c}{\sqrt{3.9}} \approx 15 \,\frac{\mathrm{cm}}{\mathrm{ns}}.\tag{3.1}$$

The variable c denotes the speed of light in free space. The rise time  $t_R$  (10 – 90% change) of a sinusoidal signal can be approximated by

$$t_R = \frac{2 \arcsin(0.9)}{2\pi f} \approx \frac{0.35}{f},$$

(3.2)

$$7 \,\mathrm{ps} < t_R < 39 \,\mathrm{ps}, \quad f \in [9 \,\mathrm{GHz}, 50 \,\mathrm{GHz}].$$

(3.3)

Consequently, for interconnect distances  $d_{|9\,\text{GHz}} > 2.925 \text{ mm}$  and  $d_{|50\,\text{GHz}} > 0.525 \text{ mm}$  transmission line terminations are required, i.e. for all RF and millimeter Wave (mmW) inputs and outputs connected to the pads of the chip.

The simplest way to match the LNA input to  $50 \Omega$  for a wide frequency band is to connect a resistor with  $50 \Omega$  in parallel to the source. However, as shown in [61, p. 51] this method dramatically deteriorates the Noise Figure (NF), such that values less than 3 dB cannot be achieved. Consequently, other techniques are required to achieve an input matching of the  $50 \Omega$  without the integration of the physical  $50 \Omega$ resistor with thermal noise. Some of these implemented methods are mentioned in Chapter 4. More details of other matching techniques, like the L-Match,  $\pi$ -Match or T-Match, are described in [62, pp. 94-104].

### 3.2 Scattering Parameters for Two-Port Network

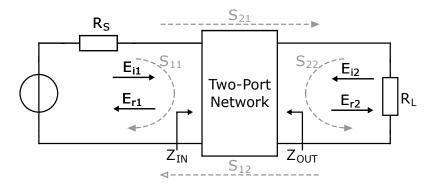

In practice, measuring voltages and currents directly is more difficult than measuring power at high RF or mmW frequencies [64, p. 178], e.g. applying open- and short-techniques could lead to undesired oscillations [62, p. 225]. Thus, it is common practice to characterize RF and mmW devices, circuits or whole systems by parameters that can be obtained from power measurement [61, p. 71]. These parameters are called *scattering parameters* or *S-parameters*. Figure 3.2 visualizes the definition of the S-parameters of a two-port network. Mathematical definitions are stated in Equations 3.4-3.7 [61, pp. 71-73]

$$S_{11} = \frac{E_{r1}}{E_{i1}}_{|E_{i2}=0},\tag{3.4}$$

Figure 3.2: Illustration of the S-parameter definitions of a two-port network with source resistance  $R_S$  and load resistance  $R_L$ .  $E_i$  and  $E_r$  denote incident and reflected waves, respectively.  $Z_{IN}$  and  $Z_{OUT}$  represent input and output impedances of the two-port network.

$$S_{12} = \frac{E_{r1}}{E_{i2}}_{|E_{i1}=0},\tag{3.5}$$

$$S_{22} = \frac{E_{r2}}{E_{i2}}_{|E_{i1}=0},\tag{3.6}$$

$$S_{21} = \frac{E_{r2}}{E_{i1}} = 0. \tag{3.7}$$

$S_{11}$  represents the accuracy of the input matching.

$S_{12}$  represents the coupling of the output signal to the input signal.

$S_{22}$  represents the accuracy of the output matching.

$S_{21}$  represents the gain of the circuit.

$E_{i1}$  is the incident wave at the input.

$E_{r1}$  is the reflected wave at the input.

$E_{i2}$  is the incident wave at the output.

$E_{r2}$  is the reflected wave at the output.

$E_{i1,i2} = 0$  means that there is no reflection from the source or load, respectively.

The most relevant of the above mentioned parameters is  $S_{11}$ , as it describes the input matching accuracy of the designed spectrum analyzer (see Chapter 4). In order to test the designed receiver, the input of the LNA has to be connected with an external measurement setup, i.e. the cable length of the equipment is above the wave length of the input signal. Besides, the input of the LNA has to be matched to the standard 50  $\Omega$  termination.

Often  $S_{11}$  is expressed in dB and lower values mean better matching or less reflection at the input. A typically acceptable value is -10 dB [61, p. 259]. As shown in Chapter 5 the goal is set to design the LNAs with  $S_{11}$  parameter lower than -10 dB, i.e. less than 10% is reflected back.

Another relevant parameter is the *reflection coefficient*  $\Gamma$  defined as [62, p. 222]

$$\Gamma = \frac{Z_L - Z_0}{Z_L + Z_0},\tag{3.8}$$

with load impedance  $Z_L$  and reference impedance  $Z_0$ . Considering the reflection coefficient at the input of an LNA,  $S_{11}$  and  $\Gamma$  are one and the same. The variables  $Z_L$  and  $Z_0$  from Equation 3.8 correspond to  $Z_{IN}$  and  $R_S$  from Figure 3.2, respectively.

### 3.3 Noise Figure

The Noise Figure (NF) is one of the key performance metrics in IC design. It shows the Signal-to-Noise Ration (SNR) degradation of the signal propagating from input to output of a circuit component and is defined as [61, p. 49]

$$NF = \frac{SNR_{IN}}{SNR_{OUT}}.$$

(3.9)

An LNA, for instance, amplifies the signal and the noise at the input by the same factor. Thus, at the output the same SNR is expected, if the LNA is noiseless. In this case the NF is equal to 1. In practice, however, the NF is always greater than 1, due to the existence of noisy components inside the LNA. [64, pp. 502-503]

Input matching plays a significant role for the NF, too. Equation 3.10 shows the degradation of the NF in case of a mismatched circuitry. For a non-zero reflexion coefficient  $\Gamma$  the NF increases. NF<sub>M</sub> denotes the NF of a perfectly matched input impedance. [64, p. 511]

$$NF = 1 + \frac{NF_M - 1}{1 - |\Gamma|^2}$$

(3.10)

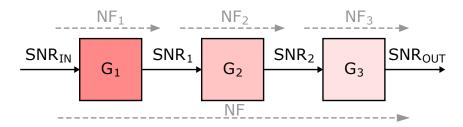

An LNA is commonly designed with more than one stage. In this case the designer has to keep in mind that the most critical stage regarding the NF is the first one. The Friis formula [66] points out in Equation 3.11 that the NF of a cascaded circuit directly depends on the NF of the first stage. NFs of the following stages contribute to the whole NF as well, but are reduced by the power gains  $G_i$  of the previous stages. This fact is visualized in Figure 3.3.

$$NF = NF_1 + \frac{NF_2 - 1}{G_1} + \frac{NF_3 - 1}{G_1G_2} + \frac{NF_4 - 1}{G_1G_2G_3}...$$

(3.11)

Since the NF is an expression of power at the input and output of a circuit component, it is often expressed in dB

$$NF_{|dB} = 10 \log(NF). \tag{3.12}$$

Figure 3.3: Schematical overview of a cascaded network with gain  $G_i$  and noise figure NF<sub>i</sub>, calculated as ratio of the SNR at the stage input to the SNR at the stage output. NF<sub>1</sub> is the main contributor to the whole NF.

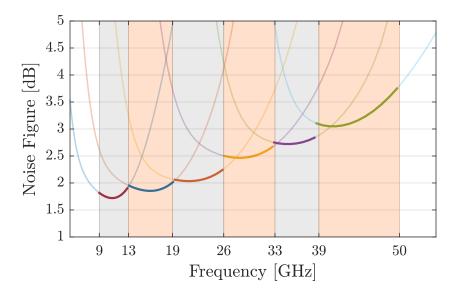

A receiver LNA typically has an NF of  $2 - 3 \,\mathrm{dB}$  [61, p. 255], dependent on the operating frequency bandwidth of the LNA. Due to a relatively high bandwidth of the designed LNAs (see Chapter 4), the goal was to achieve NFs around 3 dB.

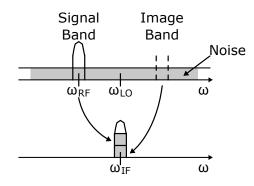

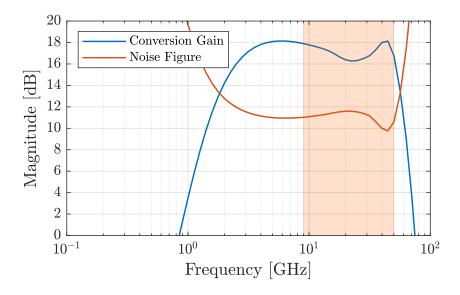

The definition of the NF for a mixer is the same as for the LNA, as stated in Equation 3.9. However, the NF is distinguished by two types, Single-Sideband (SSB) and Double-Sideband (DSB). The SSB NF is higher than the DSB by 3 dB in most cases, due to the additional noise from the image band [61, p. 344].

Figure 3.4 shows the noise contribution of the image band to the total noise at the output of the mixer, i.e. the noise at  $\omega_{LO} + (\omega_{LO} - \omega_{RF})$  is also down-converted to the IF, same as the RF signal. Thus, it reduces the SNR at the output by a factor of 2, if the noise power at the image band is equal to the noise power in the signal band.

In case of a direct-conversion mixer, i.e.  $\omega_{LO} = \omega_{RF}$ , the signal power is also available in the image band. Hence, the SNR at the mixer output is not degraded and the DSB can be applied for NF quantization. However, for the SW spectrum analyzer the LO frequency is swept over a large frequency band and it is challenging to design a VCO with a sweep step size in Hz range. As described in Section 5.3, the step size is around 20 MHz. Consequently, the SSB definition for the NF consideration is used in this thesis.

Figure 3.4: Noise contribution from the signal band and the image band to the total noise at the IF output of the mixer. By down-converting the RF signal to the lower IF signal, the additional undesired noise at  $\omega_{LO} + (\omega_{LO} - \omega_{RF})$  is added to the noise from the signal band at  $\omega_{LO} - \omega_{RF}$ .

### 3.4 Gain

As already mentioned in the previous Section 3.3, the gain of the receiver LNA should be large enough in order to minimize the contribution of subsequent circuit components, like the down-conversion mixer, to the overall NF. There are several definitions for the power gain dependent on considered nodes of a two-port network with source and load matching blocks [64, pp. 558-561]. However, in ICs with an LNA driving a mixer directly, no matching between these two components is required, since the wavelength of the RF/mmWave signal is much larger than the physical dimensions of the interconnections between these two circuit components [61, p. 257], [67]. Thus, it is more convenient to consider the voltage gain A (see Equation 3.13), instead of the power gain, in order to characterize the performance of the LNA.

$$A = \frac{V_{OUT}}{V_{IN}} \tag{3.13}$$

As already mentioned in Section 2.3, the input voltage for the LNA is expected to be in the range of  $10 - 20 \,\mu\text{V}$ . In order to have at least  $200 \,\mu\text{V}$  at the input of the mixer, the voltage gain of the LNA has to be more than 26 dB.

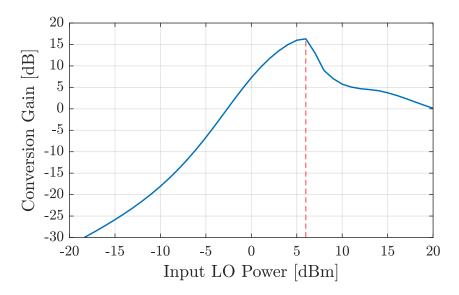

The signal amplification by an active mixer is called *conversion gain*, the ratio of the voltage amplitudes of the IF signal to the RF signal. Typical values of the voltage conversion gain for a mixer are around 10 dB [61, p. 339].

### 3.5 Linearity

All practical amplifiers have a certain dynamic range for the minimum and maximum power that can be applied at the input in order to have a reasonable output signal. The applied minimum input power, that can be detected at the output, is limited by noise. The applied maximum input power is limited by saturation seen at the output due to the finite power supply of the circuit and non-linear effects of active devices, like transistors.

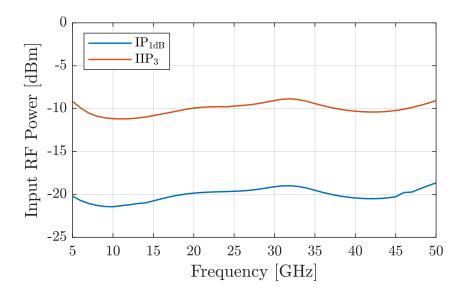

For the designed spectrum analyzer, relatively low input voltages of  $10 - 20 \,\mu\text{V}$  are expected, so there is no risk for saturation at the output of the designed circuit components. However, in order to benchmark an LNA or a mixer regarding the dynamic range, the 1 dB compression point and the 3rd order intercept point are reasonable parameters to consider. The simulation results are presented in Chapter 5.

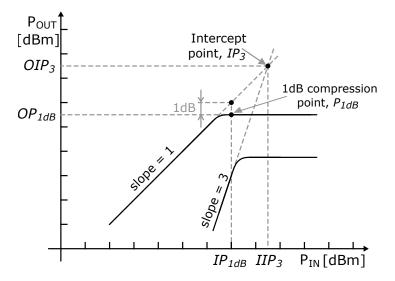

#### 3.5.1 1 dB Compression Point

Figure 3.5 visualizes the definition of the 1dB compression point of a non-linear device. For an ideal amplifier the dependence between input power and output power always remains linear. In practice, the gain starts to reduce at a certain point. The deviation of the output power level from the ideal value by 1 dB is defined as  $1 \ dB$  compression point. For the compression parameter either the input or the output

Figure 3.5: Definitions of the linear distortion parameters the 1 dB compression point  $P_{1dB}$  and the 3rd order intercept point  $IP_3$ . The curves represent the 1st and the 3rd order intermodulation products of the output power versus the input power in a log-log scale. Both responses indicate a compression at a certain input power. The ideal responses are extended with dashed lines.

power can be considered and defined as the Input referred 1 dB compression Point  $(IP_{1dB})$  or as the Output referred 1 dB compression Point  $(OP_{1dB})$ , respectively. [64, pp. 512-513]

#### 3.5.2 3rd Order Intercept Point

The definition of the 3rd order intercept point is visualized in Figure 3.5. Similarly to the 1 dB compression point, the input and the output power of a network is considered. Assuming an ideal device the output power, caused by the 3rd order terms of the Taylor series (see Equation 3.15), increases thrice as fast as for the 1st order, i.e. at a certain point, the Intercept Point (IP<sub>3</sub>), these two curves intersect. The corresponding input and output powers are identified by the 3rd Order Input Intercept Point (IIP<sub>3</sub>) and the 3rd Order Output Intercept Point (OIP<sub>3</sub>), respectively.

In general, an input response of a non-linear system can be modeled using a Taylor series. For an input signal with a single frequency  $\omega$  the system response has harmonics at  $n \cdot \omega$ , n = 1, 2, 3, ..., which can be easily filtered out in most cases. However, an input signal with two closely placed tones has also higher order frequency components at the sum and at the difference of the input frequencies. If we assume an input signal  $v_i$  with an amplitude  $V_0$  and two tones at  $\omega_1$  and  $\omega_2$

$$v_i = V_0(\cos\omega_1 t + \cos\omega_2 t), \tag{3.14}$$

then the time response  $v_o$  at the output is equal to [64, pp. 513-514]

$$\begin{aligned} v_o &= a_0 + a_1 V_0 \cos \omega_1 t + a_1 V_0 \cos \omega_2 t \\ &+ \frac{1}{2} a_2 V_0^2 (1 + \cos 2\omega_1 t) + \frac{1}{2} a_2 V_0^2 (1 + \cos 2\omega_2 t) \\ &+ a_2 V_0^2 \cos(\omega_1 - \omega_2) t + a_2 V_0^2 \cos(\omega_1 + \omega_2) t \\ &+ a_3 V_0^3 \left( \frac{3}{4} \cos \omega_1 t + \frac{1}{4} \cos 3\omega_1 t \right) + a_3 V_0^3 \left( \frac{3}{4} \cos \omega_2 t + \frac{1}{4} \cos 3\omega_2 t \right) \quad (3.15) \\ &+ a_3 V_0^3 \left[ \frac{3}{2} \cos \omega_2 t + \frac{3}{4} \cos(2\omega_1 - \omega_2) t + \frac{3}{4} \cos(2\omega_1 + \omega_2) t \right] \\ &+ a_3 V_0^3 \left[ \frac{3}{2} \cos \omega_1 t + \frac{3}{4} \cos(2\omega_2 - \omega_1) t + \frac{3}{4} \cos(2\omega_2 + \omega_1) t \right] + \cdots . \end{aligned}$$

A special case occurs for the 3rd order, when the resulting frequency is close to the input frequency and thus cannot be filtered out properly. Especially with a rising input power the 3rd order terms of the Taylor series are not negligible, due to the power of 3 amplitude dependence. The undesired terms are marked with a bold font in Equation 3.15. The *3rd order intercept point* is therefore of great interest for the characterization of signal distortion. For the derivation of the above mentioned statements and for more detailed information on the non-linear signal distortion the reader is referred to [64, pp. 512-516].

### 3.6 Stability

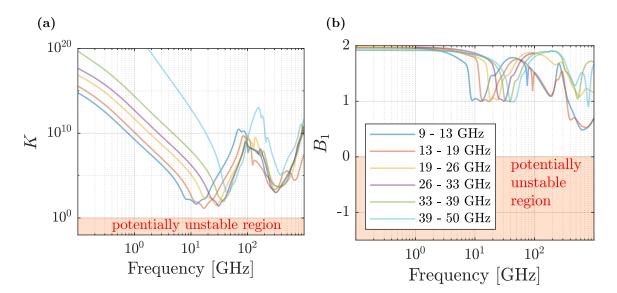

Stability is indisputably the most important performance parameter for all electronic circuits and especially for RF and mmW circuit designs. Achieving a greater value for the gain or a lower NF of a circuit becomes irrelevant without a corresponding degree of stability. Thus, the stability parameters have to be verified continuously during the design flow, not only for the operating frequency band, but also for sufficiently wide range of frequencies.

In order to prove the circuit is *unconditionally stable*, i.e it does not start to oscillate under any conditions for source and load impedances at any frequency, the following conditions derived from Rollet stability [68] have to be met [63, p. 418-421]

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{2|S_{12}S_{21}|} > 1,$$

(3.16)

$$B_1 = 1 + |S_{11}|^2 - |S_{22}|^2 - |\Delta|^2 > 0, \qquad (3.17)$$

where K and  $B_1$  conventionally used stability parameters and  $|\Delta|$  is the determinant absolute value of the scattering matrix, defined as

$$|\Delta| = |S_{11}S_{22} - S_{12}S_{21}|. \tag{3.18}$$

An alternative way to prove unconditional stability with just one criterion was proposed by Edward [69]. The stability factor  $\mu$  is defined as

$$\mu = \frac{1 - |S_{11}|^2}{|S_{22} - S_{11}^* \Delta| + |S_{12}S_{21}|} > 1.$$

(3.19)

As already mentioned in Section 3.1 in ICs there is no need to match the LNA output to the mixer input, if the wire length between these two components is small enough. Besides, the load impedance of the LNA can be well controlled to avoid deviation from the nominal value. Thus, the above mentioned stability criteria are relatively pessimistic [61, pp. 259-260].

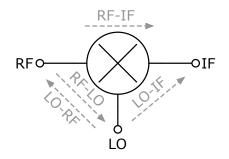

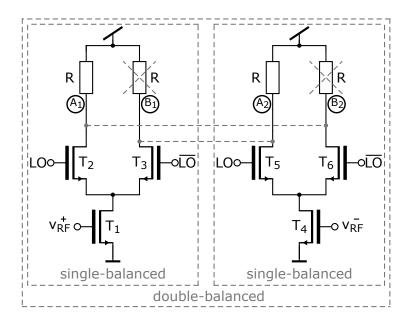

### 3.7 Port-to-Port Isolation

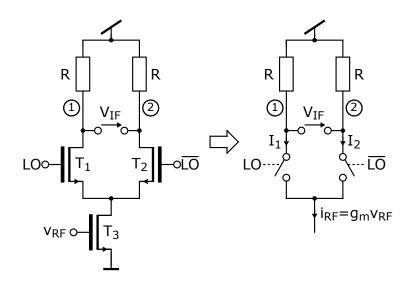

Capacitive coupling from one port to another is an issue in electronic components, especially in RF and mmW circuit design. Here, the port-to-port isolation of a mixer is considered. Figure 3.6 sketches the mixer with the input ports RF, LO and the output port IF. The port isolation is defined as the ratio of the voltages at one port to another port of the same frequency. In practice, four kinds of feedthroughs between the ports are used: LO-IF isolation, LO-RF isolation, RF-LO isolation and RF-IF isolation.

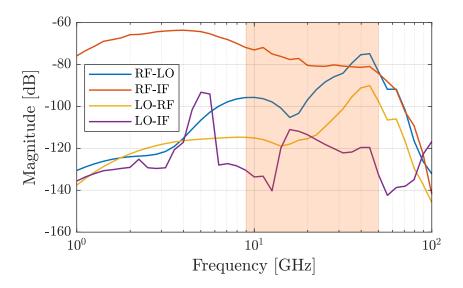

The most critical type is the LO-RF feedthrough, as it produces both a DC offset at the IF port and an undesirable propagation to the transducer (input of the LNA) with a consequent radiation of the signal. Besides, the LO signal is typically several orders of magnitude higher than the RF and IF signals. The LO-IF and RF-IF couplings are less critical since the LO and RF frequencies at the IF port are subsequently filtered out by an operational amplifier with a band pass characteristic. The RF-LO feedthrough deteriorates the spectrum of the LO signal. Due to the significant difference in magnitude (more than 40 dB) between the RF and LO signals this coupling issue is negligible. [61, p. 340], [63, pp. 637-638]

**Figure 3.6:** Port-to-port feedthroughs of a mixer with Radio Frequency (RF), Local Oscillator (LO) and Intermediate Frequency (IF) ports. The coupling between the ports is caused by parasitic capacitances of the used electronic devices.

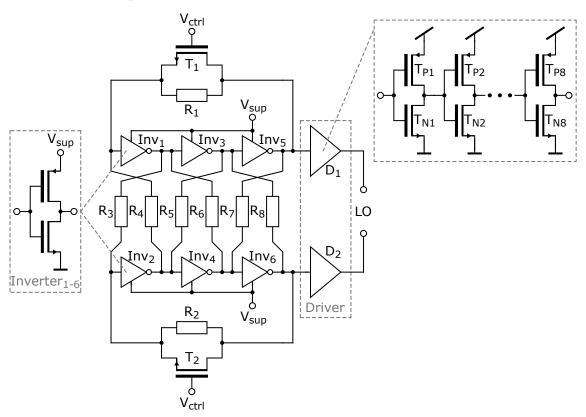

### 3.8 Phase Noise

The spectrum of a practical Voltage Controlled Oscillator (VCO) is not an ideal Dirac delta function at the nominal oscillating frequency  $f_0$ , as it contains deviated frequency components next to  $f_0$ , due to thermal, flicker or other noise sources. This phenomenon is called *phase noise* or *jitter noise* in the time domain. Figure 3.7 visualizes the fluctuation of the frequency around the nominal value  $f_0$ , which causes an instability of the LO signal in time domain. Consequently, the precision of the SW frequency and phase detection suffer.

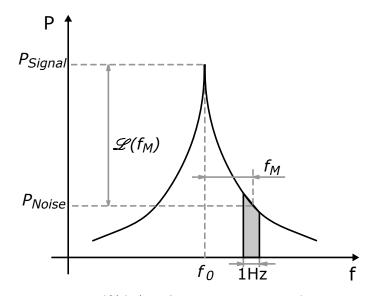

The phase noise (see Equation 3.20) is defined as the ratio of the noise power at offset frequency  $f_0 + f_M$  with 1 Hz bandwidth and the carrier power (signal power at  $f_0$ ) [63, p. 590].

$$\mathscr{L}(f_M) = 10 \log \frac{P_{Noise}}{P_{Signal}} = 10 \log \left(\frac{\text{Noise Power in 1 Hz at } f_0 + f_M}{\text{Carrier Power}}\right) \left[\frac{\text{dBc}}{\text{Hz}}\right] (3.20)$$

Consider an offset frequency  $f_M$  at 1 MHz of an oscillator operating at the carrier frequency  $f_0$  25 GHz. What does a phase noise of  $-80 \frac{\text{dBc}}{\text{Hz}}$  mean? It means that the signal power at the frequency  $f_0 + f_M = 25.001 \text{ GHz}$  in a 1 Hz bandwidth is 80 dB lower than the signal power at the frequency  $f_0 = 25 \text{ GHz}$ . For more theoretical background on phase noise in oscillators, the reader is referred to a publication by Hajimiri [70].

**Figure 3.7:** Phase noise  $\mathscr{L}(f_M)$  defined by the ratio of the noise power  $P_{Noise}$  at the frequency  $f_0 + f_M$  to the signal power  $P_{Signal}$  at the frequency  $f_0$ . The power is calculated for a frequency band of 1 Hz.

## Chapter 4

# Spin Wave Readout Circuitry Design

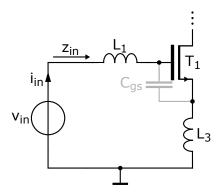

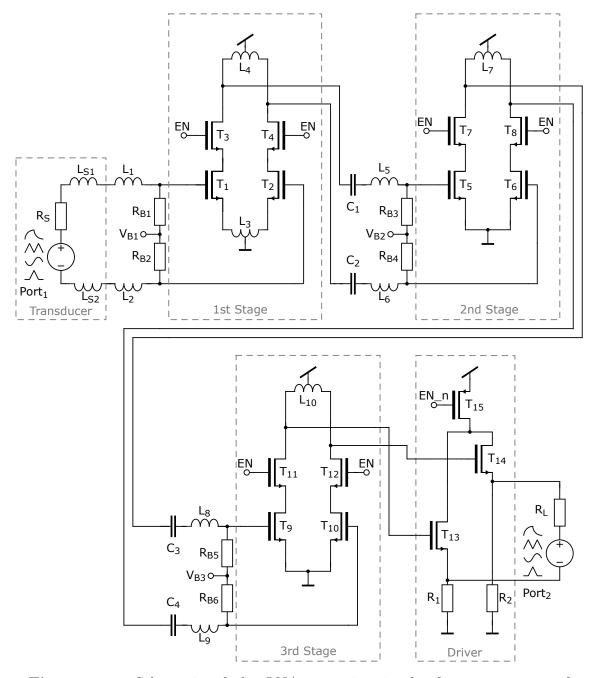

Based on the assumptions for the SW transducer presented in Chapter 2, the readout circuitry design is presented in this chapter. The development process of the circuitry is portrayed in Section 4.1 by referencing the author's related publications and emphasizing some currently known weak points of the presented results. After introducing the general concept of the SW characterization in Section 4.2, the readout circuitry components, such as the LNA, mixer, VCO, PLL and OpAmp are detailed in Sections 4.3-4.7, respectively.

### 4.1 Reference to the Author's Publications

The concept of the SW on-chip detection was first presented in [133]. The paper points out the need of an on-chip detection of SWs and consequently the necessity of dedicated CMOS circuitry. The loop antenna, as a possible SW transducer to the electronic domain, is described as well. The readout circuitry, presented in [133], enables a first approximation of the expected circuitry performance, based on previously published papers. Besides, it presents the three stage LNA that covers the frequency range of 10 - 40 GHz with the gain of 20 dB. Details on the LNA are published in [132]. The main idea, to cover such a high frequency range with the single LNA design, is placing the resonant frequency of each amplifying stage at different frequency points.

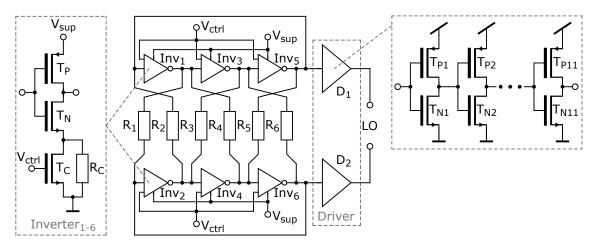

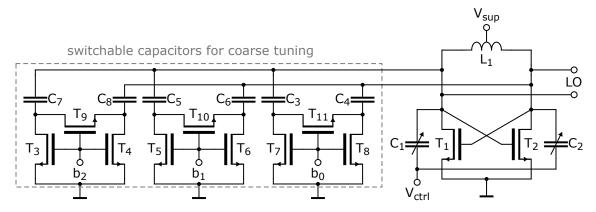

The extension of the readout circuitry with the designed mixer and OpAmp in addition to the previously designed LNA is presented in [134]. Here, the SW spectrum analyzer was designed for the frequency range of 5-50 GHz. The concrete methodology for the frequency, amplitude and phase detection of the SWs is described and substantiated with appropriate simulation results. However, for the LO signal an ideal voltage source has been used instead of a VCO. Besides, for the inductors an ideal Simulation Program with Integrated Circuit Emphasis (SPICE)-model was implemented. In contrast to the topologies designed with 65 nm technology [132–134], fully differential LNAs, mixer and VCOs were implemented in the latest publication [135]. Based on the findings for the design in 65 nm CMOS technology, the design with 40 nm CMOS technology from GlobalFoundries is presented. The big advantage of the provided 40 nm CMOS technology is the presence of the RF and mmW libraries with devices modeled for up to 100 GHz. Moreover, it includes the Optimum Inductor Finder (OIF) kit as a lookup table with inductor models allowing faster design and more realistic representation compared to the previously used ideal model.

As mentioned in [134], it was attempted to design the circuitry covering the whole frequency range of 5-50 GHz with a single receiver topology. The most relevant advantage of such an approach is a relatively low chip area and consequently lower manufacturing costs. However, the poor noise performance does not allow to pick up a relatively small transducer signal power of less than 90 dBm with respect to a  $50 \Omega$  impedance. Consequently, the frequency range 5-50 GHz was split in several frequency bands in order to achieve a better NF of the LNA.

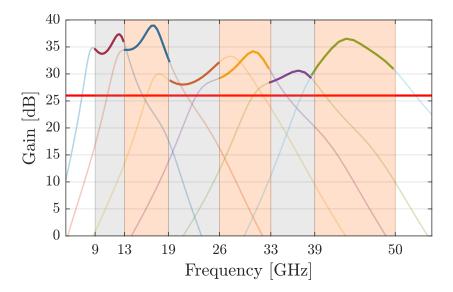

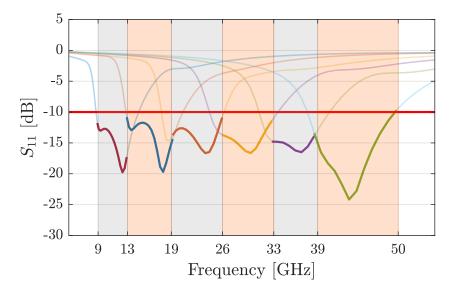

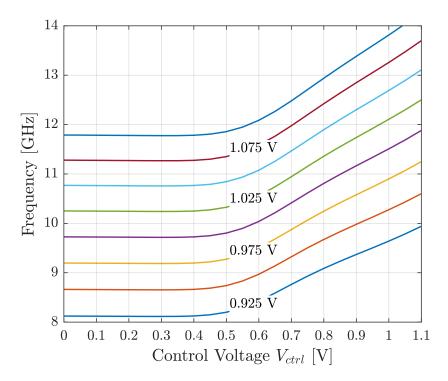

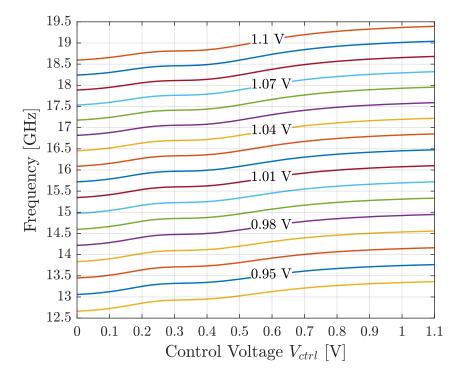

The SW readout circuitry published in [135] is further extended in the content of this thesis. PLL circuitry is additionally introduced. Besides, some optimizations regarding the power consumption of the readout circuitry have been achieved. It is also important to mention, that the LNA designed for 5 - 9 GHz in [135], is not unconditionally stable, as recent analysis has shown. Relatively large inductor values were required for lower operating frequencies (5 - 9 GHz), i.e. a larger chip area and relatively poor modeling provided by the foundry. Thus, the frequency range for the SW characterization considered in this work is reduced to 9 - 50 GHz. Table 4.1 shows the allocation of the 9 - 50 GHz bands of the circuit components covering the corresponding frequency range with a single design topology.

Table 4.1: Frequency bands of the SW readout circuitry components. The check mark reflects a single topology of the LNA, mixer and VCO covering the corresponding frequency range, i.e. there are 6 different designs for the LNA, 1 for the mixer, covering the whole frequency range, and 6 for the VCO.

| Bands | Freq. Range [GHz] | LNA          | Mixer        | VCO          |

|-------|-------------------|--------------|--------------|--------------|

| 1     | 9 - 13            | $\checkmark$ |              | $\checkmark$ |

| 2     | 13 - 19           | $\checkmark$ |              | $\checkmark$ |

| 3     | 19 - 26           | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| 4     | 26 - 33           | $\checkmark$ |              | $\checkmark$ |

| 5     | 33 - 39           | $\checkmark$ |              | $\checkmark$ |

| 6     | 39 - 50           | $\checkmark$ |              | $\checkmark$ |

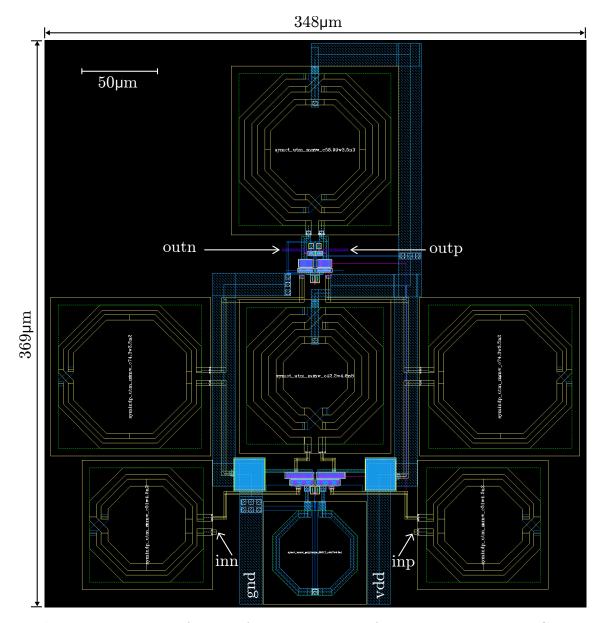

**Figure 4.1:** Concept of the SW detection with on-chip near field antennas placed below Yttrium-Iron-Garnet (YIG). The picked up signal is amplified and converted to lower frequencies with a circuitry realized in 40 nm CMOS technology. The digital information on the SW frequency, amplitude change and phase shift can be analyzed at the output pads.

### 4.2 General Concept of the Spin Wave Readout Circuitry

To convert magnetic excitations into an electrical signal,  $50 \Omega$  near field loop antennas can be placed below a dielectric thin film of yttrium iron garnet (YIG) with low damping (see Figure 4.1). The sensing system of the antennas can be placed in such a way that the SWs at higher frequencies propagate to the transducers with the readout circuitry operating at higher frequencies and the SWs at lower frequencies propagate to the lower ones. Similar to the idea published by Papp in [21, Figure 1].

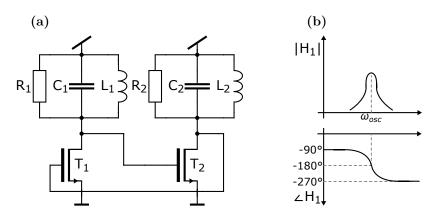

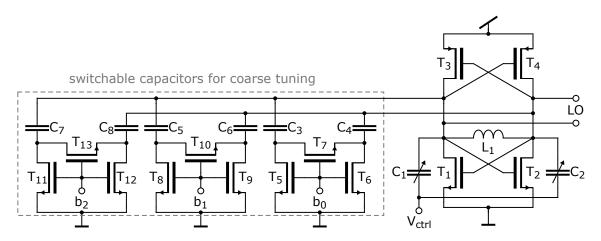

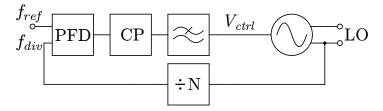

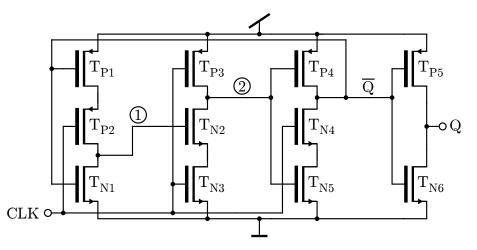

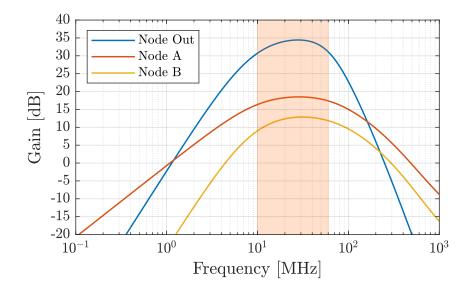

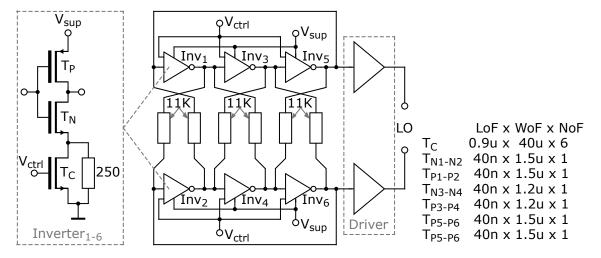

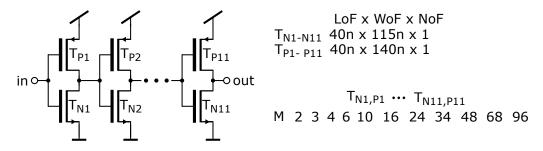

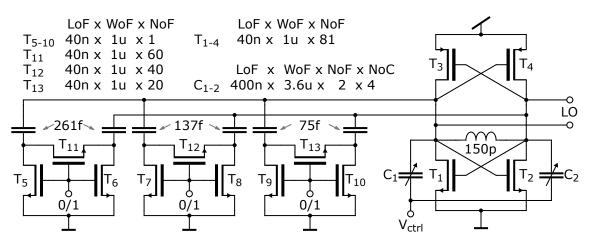

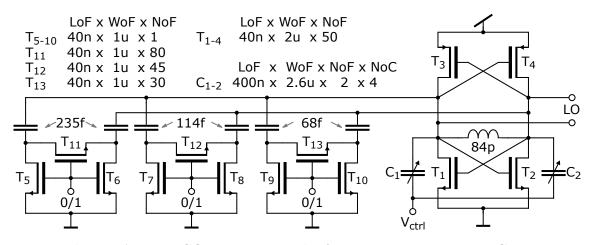

As mentioned in Section 2.3, micromagnetic simulations show that the SWs induce an electrical signal power of -80 to -90 dBm in the transducer [133]. This periodic signal is amplified by a differential LNA. The ultra-wideband mixer converts the amplified signal to lower IFs in the range of 10 - 70 MHz. In order to realize the conversion, the LO signal is required at the second input of the mixer. The LO signal is generated in the VCO. The PLL controls the frequency of the VCO. Subsequently, the OpAmp with a gain of 60 dB increases the IF signal to voltage values around 100-200 mV. Finally, the amplified and down-converted SW signal can be digitized by an ADC, that provides information about the SWs frequency, amplitude and phase change. The ADC is out of the scope of this thesis and is not described in the following Sections. The evaluation of the simulated frequency, amplitude and phase detection of the SWs is considered at the output of the OpAmp and described in Chapter 5.

### 4.3 Low Noise Amplifier

#### 4.3.1 General Considerations

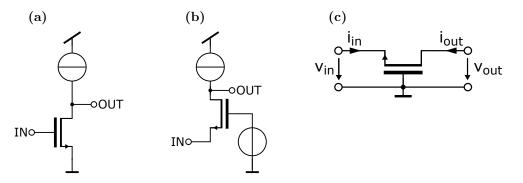

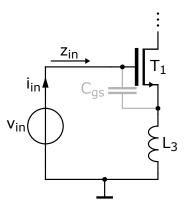

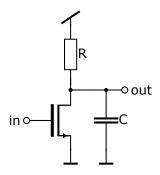

The LNA is the most critical part of the whole receiver circuitry regarding the noise contribution. Thus, a careful design is essential for achieving a low NF and consequently to be able to detect relatively low input voltages below  $10 \,\mu$ V. In general, two transistor configurations are commonly used as inputs to the LNAs: Common Source (CS) and Common Gate (CG) circuits (see Figure 4.2).

On the one hand, the CG provides more accurate and broadband input matching, since the resistance looking into the source of the transistor is equal to the reciprocal of the transconductance  $g_m$ . Considering the small signal equivalent circuit of the CG in Figure 4.2c, the input resistance can be derived as shown in Equation 4.1. Subsequently, the 50  $\Omega$  input resistance can be adjusted with an appropriate selection of device dimensions. On the other hand, the CS is better for a lower NF. Depending on the application, if a NF greater than 4 dB is acceptable, than the CG configuration is a better choice [61, p. 293]. In our case, with a targeted NF around 3 dB or lower, the choice for the CS topology is obvious.

$$z_{in} = \frac{v_{in}}{i_{in}} = \frac{-v_{gs}}{-i_{ds}} = \frac{v_{gs}}{v_{gs}g_m} = \frac{1}{g_m}$$

(4.1)

**Figure 4.2:** (a)Common Source (CS), (b) Common Gate (CG) and (c) the equivalent small signal circuit of the CG. In RF and mmW design the CS is used for a lower NF. For better input matching the CG is a better choice.

As mentioned in Section 4.1, the single-ended LNA was initially considered as a circuit part for the possible realization of the SW readout concept. However, the disadvantage of this topology is its high sensitivity to the parasitic ground inductance [62, p. 387]. It cannot be guaranteed that the ground of the transducer is at the potential as the ground of the source of the input CS transistor or rather at the bottom of the source degenerating inductor. Thus, the performance of the LNA can degrade significantly. Besides, undesirable noise in the signal bandwidth can couple from other building blocks, e.g. VCOs, through the ground plate to the transducer. An alternative is a fully differential LNA. It solves the above mentioned problem since the absolute potential of the sensor is not amplified. The fully differential

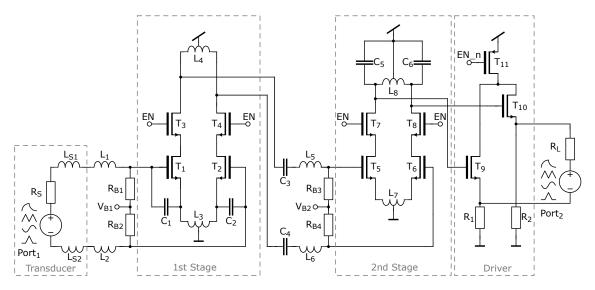

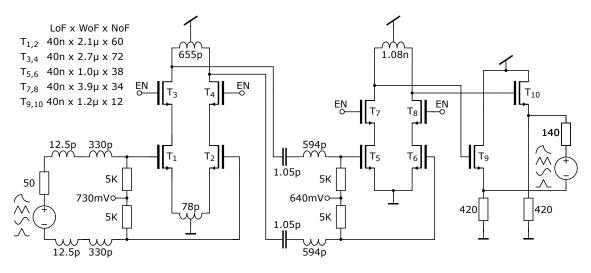

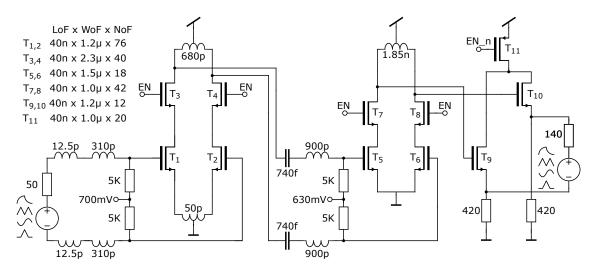

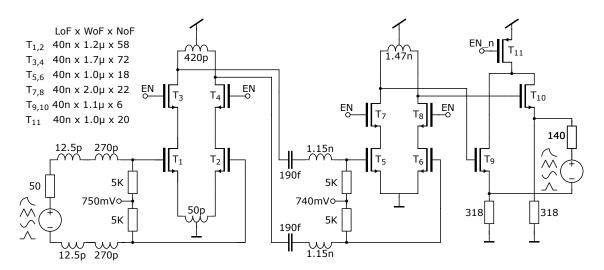

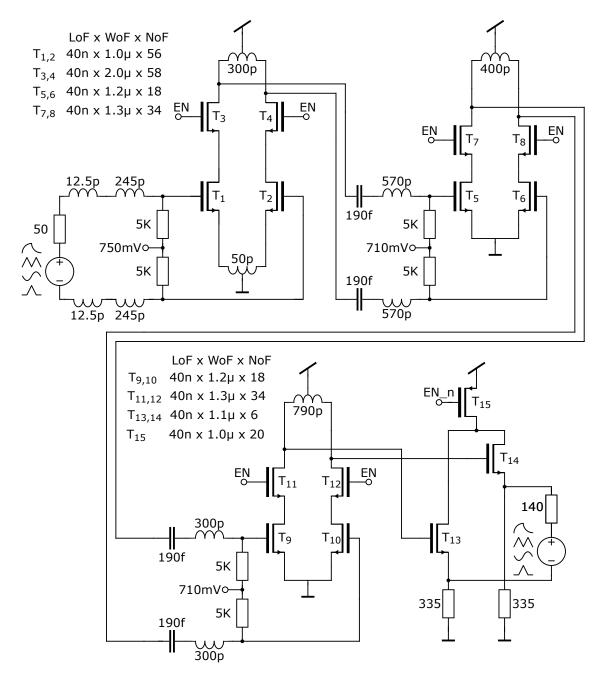

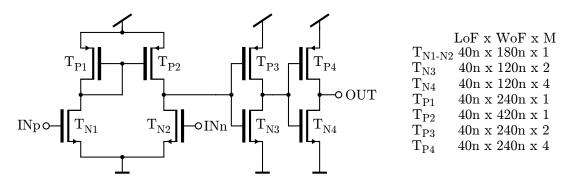

**Figure 4.3:** Topology of the LNA operating in the frequency range of 9 - 13 GHz. The differential transducer signal is amplified in two stages, which is capacitively coupled with  $C_{3,4}$ . Each stage is implemented with a common-source and cascode circuitry. The load impedance of the LNA is driven by source followers. EN symbolizes *enable* signal, switching between ground 0V and supply voltage 1.1V.

LNA also rejects common-mode disturbances [62, 388]. However, the advantages of a fully differential LNA come with an increased power consumption. To keep the NF at the same level, the total current has to be doubled.

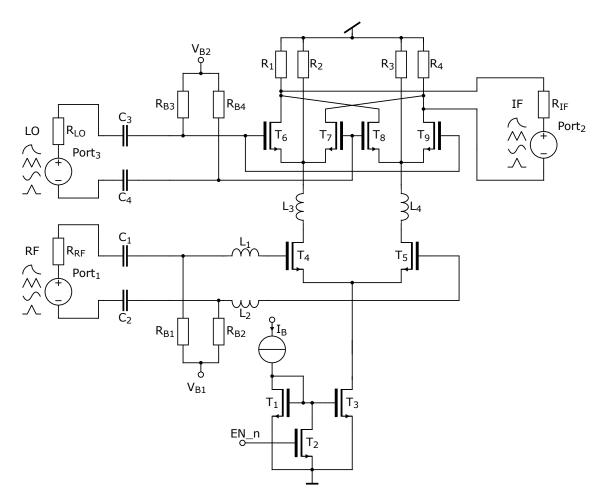

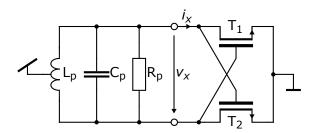

# 4.3.2 Functionality of Implemented Topology

Figure 4.3 shows the topology of the fully differential LNA designed to operate in the frequency range of 9 - 13 GHz. The LNA has two amplifying stages, the transducer model at the input (Port 1) and the impedance converter to drive the output load (Port 2).

Topologies of the LNAs designed for other frequency bands are very similar, except for the values of the electronic devices. In this Section, the function of all circuitry parts is explained and the relevant topological differences of the LNAs operating at frequencies higher than 13 GHz are mentioned as well. All LNA circuits with the parameter values of the electronic devices can be found in Appendix A.1.

$\mathbf{R_{S}}, \mathbf{L_{S1}}, \mathbf{L_{S2}}$  Source Impedance: The input of the LNA is the impedance model of the transducer. For all selected frequency bands the same model is assumed, i.e.  $R_S = 50 \Omega$  and  $L_{S1,S2} = 12.5 \text{ pH}$ . As simulations have shown, the imaginary part of the input impedance is negligible. Consequently, the input matching of the LNA to the real part, equal to  $50 \Omega$ , is more relevant. It is worth mentioning, that the LNA can be adopted to other input impedances. However, it is viable for the first approach, to design the LNA for a  $50 \Omega$  input, since most measurement setups are calibrated to a  $50 \Omega$  impedance.  $\mathbf{R}_{\mathbf{L}}$  Load Impedance: The output of the LNA is the input of the mixer. As already mentioned before and explained in more detail in Section 4.4, the designed mixer covers the whole frequency range of 9 – 50 GHz with a single topology, i.e. the load impedance  $R_L$  remains unchanged for all LNAs, operating in different frequency bands. During the design and optimization of the mixer, reasonable performance results have been achieved with an input impedance of the mixer equal to 140  $\Omega$ . Thus, the load resistance  $R_L$  of the LNA is set to 140  $\Omega$  and the LNA is designed to match this value. Consequently, by connecting the LNA with the mixer, the achieved performance of the mixer remains almost unchanged.

$T_{1-2}, T_{5-6}$  Common-Source: CS is a standard circuit in analog design for amplifying the input voltage. Unfortunately, with a standard approach it has no gain at high frequencies (here 9-50 GHz), due to the poles in the transfer function from the load capacitance at the output and the parasitic overlap capacitances between the gate, drain and source nodes. Thus, other techniques, described below, are needed to achieve amplification by means of resonance effect at required higher frequencies. For that purpose, inductors have to be introduced in the circuitry.

$T_{3-4}$ ,  $T_{7-8}$  Cascode Transistors: In the CS circuit the parasitic overlap capacitance between gate and drain produces a feedback between the input and the output nodes. Depending on the dimensions of the electronic devices it produces an input impedance with a negative real part at certain frequencies, i.e. the circuit becomes potentially unstable [61, pp. 266-269]. To overcome this issue cascode transistors can be introduced in order to increase the isolation between input and output [61, p. 284]. The cascode circuit is a combination of the CS with the CG. On the one hand, it improves the stability of the LNA. On the other hand, every additional electronic device, especially at the input of the LNA, contributes to the noise of the circuitry.

$L_3, L_7$  Inductive Source Degeneration: Degenerating inductors provide an additional possibility to improve the input matching  $(S_{11})$  of the LNA. Starting from Kirchhoff's Voltage Law (KVL) (Equation 4.2) the small signal input impedance  $z_{in}$  is derived in Equation 4.3 [61, p. 284]. Finally, we see that  $z_{in}$  contains a real frequency-independent term, allowing better adjustment of the matching parameter  $S_{11}$  of the LNA.

$$v_{in} = \frac{i_{in}}{C_{gs}j\omega} + (i_{in} + v_{gs}g_m)L_3j\omega = \frac{i_{in}}{C_{gs}j\omega} + (i_{in} + \frac{i_{in}}{C_{gs}j\omega}g_m)L_3j\omega$$

(4.2)

$$z_{in} = \frac{v_{in}}{i_{in}} = \frac{1}{C_{gs}j\omega} + L_3j\omega + \frac{g_m L_3}{C_{gs}}$$

(4.3)

Here,  $C_{gs}$  stands for the parasitic overlap capacitance between gate and source nodes.  $g_m$  symbolizes the small signal transconductance of the transistor  $T_1$ . The relevant circuit parts of the LNA are depicted in Figure 4.4.

In order to achieve the best possible symmetry for the differential topology, center tap symmetric inductor has been implemented.

Figure 4.4: CS circuit with parasitic gate-source-capacitance and degenerating inductor. Small letters used for the input parameters mean small signal consideration.

$C_{1-2}$  Increase of Gate-Source-Capacitance: Setting the frequency-independent part  $\frac{g_m L_3}{C_{gs}}$  of the input impedance  $z_{in}$  (see Equation 4.3) equal to 50  $\Omega$  results in a relatively low value for the inductance  $L_3$ . The solution in this case would be to decrease the transistor transconductance  $g_m$ , i.e. an increase of the channel length and consequently a degradation of the NF [71]. The second possibility is to increase the gate-source-capacitance by placing an additional capacitor in parallel. [61, p. 285]

$L_{1-2}, L_{5-6}$  Canceling Reactive Component: The input impedance derived in Equation 4.3 contains an imaginary part, that has to be zero for an appropriate input matching [61, p. 295]. Similar to the consideration made for inductive degeneration, we can introduce a serial inductor in the signal path as depicted in Figure 4.5. For the small signal voltage  $v_{in}$  and input impedance  $z_{in}$  we can write the following Equations

$$v_{in} = i_{in}(L_1 j\omega + \frac{1}{C_{gs} j\omega}) + (i_{in} + v_{gs} g_m) L_3 j\omega,$$

$$= i_{in}(L_1 j\omega + \frac{1}{C_{gs} j\omega}) + (i_{in} + \frac{i_{in}}{C_{gs} j\omega} g_m) L_3 j\omega,$$

(4.4)

$$z_{in} = \frac{v_{in}}{i_{in}} = \frac{1}{C_{gs}j\omega} + (L_1 + L_3)j\omega + \frac{g_m L_3}{C_{gs}}.$$

(4.5)

Finally, the parameter  $L_3$  introduces an additional degree of freedom that can be treated to achieve a better input matching by finding the values for the electronic devices at the intended frequency, i.e. Equation 4.6 has to be valid.

$$\frac{1}{C_{gs}\omega} = (L_1 + L_3)\omega \tag{4.6}$$

Figure 4.5: CS circuit with parasitic gate-source-capacitance, degenerating inductor  $L_3$  and serial inductor  $L_1$  for canceling the reactive component of the small signal input impedance  $z_{in}$ .

$L_4, L_8$  Inductive Loading: In RF and mmW circuit design it is common to replace resistive loading with inductive loading, as it provides better matching. Consequently, the time constant of the output node is reduced, due to a low inductor serial resistance. Moreover, the voltage headroom is increased for the cascode circuit, due to a low DC voltage drop at the inductor. The load inductors resonate with the total capacitance at the output nodes of each stage, allowing operation at much higher frequencies than with resistive loading. [61, pp. 266-267] To achieve a wider operating bandwidth of the LNA, the resonant frequencies at the output and input nodes have an offset [62, p. 384].

$C_{5-6}$  Capacitive Load Increase: The capacitors  $C_{5-6}$  are only inserted in the LNAs operating up to 19 GHz, in order to increase the load capacitance at the output nodes of the second stage. The alternative is to implement a high inductance for  $L_8$  to achieve resonance at the same required frequency. However, to fabricate inductor values higher than 2.5 nH in an IC with an acceptable quality factor is difficult. Besides, the provided inductor models in 40-nm CMOS technology from GlobalFoundries are limited to around 3 nH.

$C_{3-4}$  Capacitive Coupling: The two stages of the LNA are coupled by capacitors, i.e. only high frequency components of the signal can propagate from the first stage to the second stage. This provides flexibility for adjusting the DC operating point of the transistors  $T_{5-6}$  and at the same time blocks undesired frequency components coming from the first stage.

$T_{9-10}$ ,  $R_{1-2}$  Impedance Converter: The *impedance converter* turns the impedance from a high resistive node to a low resistive node. The main drawback of the implemented circuit is the attenuation of the LNA gain. Depending on the operating frequency of the LNA the gain degrades by approximately 10 dB. However, the direct connection of the mixer to the output of the LNA's second stage reduces the gain of the stage as well. To create the above mentioned 140  $\Omega$  source impedance for a proper operation of the mixer, the impedance conversion is required. Moreover, this driver at the LNA output additionally isolates the mixer from the LNA, i.e. the LO-RF feedthrough of the mixer is suppressed.  $\mathbf{R}_{B1}, \mathbf{R}_{B2}$  Bias Resistors: Biasing is indispensable for adjusting the DC operating point of the transistors. Thus, it is important to have stable bias voltages over the whole operating temperature range and a resilience against supply voltage variations. Here, the bias voltage sources  $V_{B1}$  and  $V_{B2}$  are assumed to be ideal. However, the commonly used in IC design bandgap voltage references can be applied. Another possibility is the implementation of a current source with reduced Process, Voltage supply and Temperature (PVT) variation [74]. Bear in mind, that large enough resistor values for  $R_{B1}$  and  $R_{B2}$  have to be selected to avoid attenuation of the input signal and to minimize the equivalent noise current [62, p. 384].

$\mathbf{T}_{3-4}, \mathbf{T}_{11}$  Switches: The gates of the cascode transistors  $T_{3-4}$  are connected to the *enable* signal, i.e. during the operation period of the LNA, the gates are connected to the supply voltage  $V_{DD} = 1.1$  V and in the off-time to the ground 0 V. The same consideration holds for the Positive-Channel Metal-Oxide-Semiconductor (PMOS) transistor  $T_{11}$  with the inverted enable signal. Switching off the power supply of some building blocks obviously reduces the power consumption of the whole IC system. Additionally, the parasitic interconnect coupling to other circuits is reduced.

So far, the building blocks of the LNA operating in the frequency range 9 - 13 GHz has been explained. The schematics for other frequency bands are very similar, however the dimensions of the electronic devices are different. The sizes of the inductors and capacitors are reduced in order to shift the resonant frequency to higher values. The width of the transistors is reduced resulting in a lower DC power consumption.

To achieve a voltage gain greater than 26 dB, LNAs with 2 stages were sufficient as proven by the simulation results in Chapter 5. However, at the frequency band 39 - 50 GHz an additional stage was required to achieve a reasonable gain. The schematic of the LNA operating in 39 - 50 GHz is depicted in Figure 4.6. The third stage is identical to the second one and increases the resonance effect at frequencies around 50 GHz.

# 4.3.3 Recommended Publications

Fritsche [75] demonstrates an LNA with 3 dB bandwidth from 54.5 to 72.5 GHz. Details on the layout and considerations on the interconnects in case of mmW circuits are reported. A 2-stage cascode LNA is used as a topology.

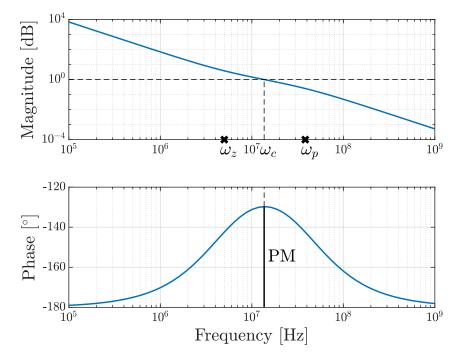

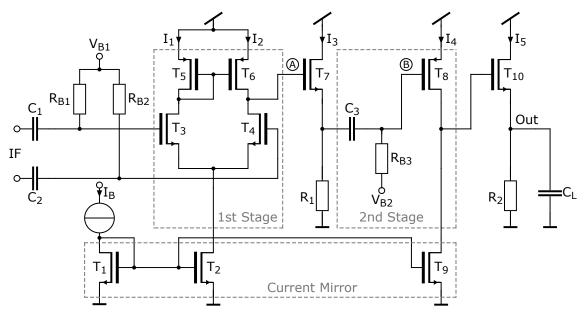

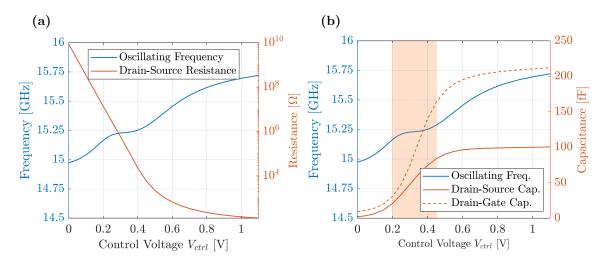

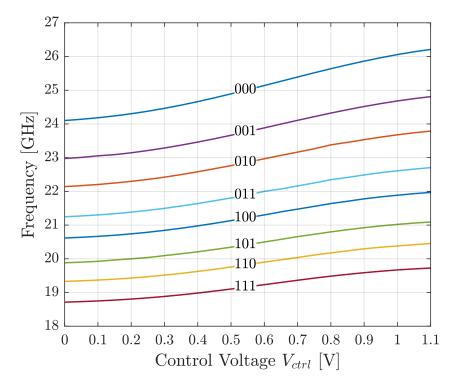

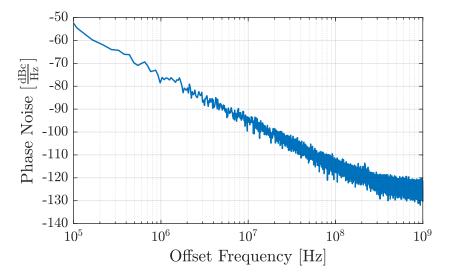

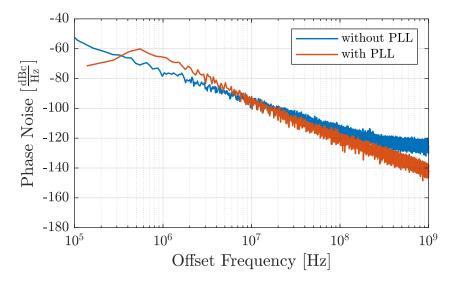

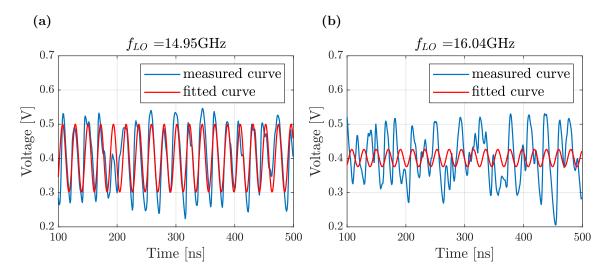

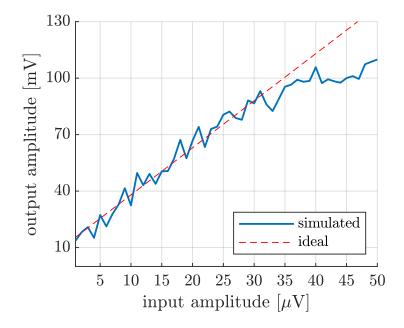

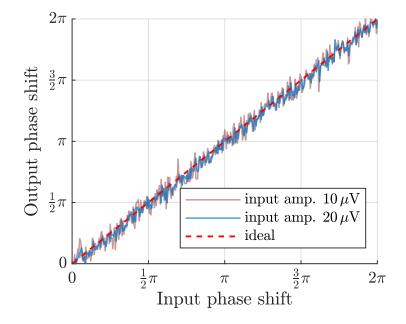

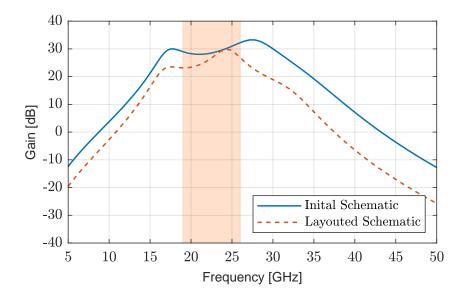

A 3-stage Ultra-Wideband (UWB) LNA operating in 30 - 50 GHz is reported by Yang [76].