# Design-Dependent Monitors to Track the Timing of Digital CMOS Circuits

Jahnavi Kasturi Rangan

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

# Doktor-Ingenieurs (Dr.-Ing.)

genehmigten Dissertation.

Vorsitzender: Prof. Dr.-Ing. Ralf Brederlow

## Prüfende der Dissertation:

- 1. apl. Prof. Dr.-Ing. habil. Helmut Gräb

- 2. Prof. Dr.-Ing. Steffen Paul

Die Dissertation wurde am 28.05.2019 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 23.09.2019 angenommen.

# Abstract

Decrease in technology nodes has resulted in increased process and environmental variations (PVT) of semiconductor devices. These increased PVT variations in turn have a higher impact on digital circuit timing. To avoid timing errors in worst case scenarios, substantial guardbands are added to the operating frequency and supply voltage of circuits. These guardbands make sure that the required timing performance is met, however, this results in increased power consumption, area, cost and design time. Additionally, verifying if the timing criteria are met after manufacturing of chips is of utmost importance. For this reason, multiple test-structure circuits are required to be implemented on different parts of a chip such that the timing behavior of these test-structures are highly correlated to the behavior of a chip. The measurement data from these monitors should be able to predict the timing of the complete chip with high accuracy.

This thesis presents synthesis of design-dependent ring oscillators which aim to track the delays of setup-time critical paths of a chip. In the design-dependent ring oscillator (DDRO) approach, at first a set of setup-time critical paths are identified and grouped based on their similarities of timing behavior across PVT space. Subsequently, a DDRO is constructed for each group of critical paths. Frequency measurements from DDROs then directly represent the timing of their respective critical path groups.

In this work, in addition to the state-of-the-art method various DDRO synthesis formulations are developed and their accuracy to track critical path timing is evaluated. Moreover, the computational complexity of DDRO synthesis method is significantly reduced by using static timing analysis (STA) instead of analog simulation to characterize delays. Additionally, usage of developed heuristic optimization algorithms instead of direct solvers further reduces the computational complexity to synthesize DDROs. Furthermore, suitable clustering algorithms are selected such that a single DDRO can be constructed for a group of critical paths. The DDRO synthesis and clustering methods are evaluated on a sub-40nm technology. Based on the evaluation of DDROs, the synthesis methods proposed in this thesis tracks the timing of a digital design much better than other state-of-the-art timing monitors. Amongst the monitors investigated, DDROs are found to be the best suited timing monitors for large-scale industrial designs, in particular due to their reduced synthesis complexity.

# Acknowledgment

This work was supported by the German Federal Ministry of Education and Research (BMBF) under the project number 16ES0303 within the funding project RESIST-RESilient transport InfraSTructure to extreme events. This work was concluded during my work as a PhD candidate at Infineon Technologies A.G., Neubiberg, Germany.

First and foremost, I would like to thank my professor Apl. Prof. Dr.-Ing. habil. Helmut Graeb for generously being my adviser for my PhD thesis. He constantly encouraged and guided me through all the stages of my thesis. His advice on my research work and career has been invaluable. His deep knowledge and experience in the field of circuit optimization and electronic design automation has been greatly favorable for my research work.

I am extremely thankful to Infineon Technologies A.G. for giving me an opportunity to pursue an industrial PhD in collaboration with the Technical University of Munich, Germany. I am especially thankful to all my fantastic team members for not only sharing their extensive technical knowledge but also for their guidance and moral support during the past three years. Not only have I had technical knowledge growth, but I have also grown as an individual under their guidance. Thank you also for the delightful and interesting discussions.

I am thankful to Dr.-Ing. Nasim Pour Aryan who was my supervisor at Infineon Technologies and a colleague over the past three years and now a very good friend. I would like to thank her for all the discussions we had technical and otherwise. I am also grateful to her for reviewing my dissertation and for all the words of encouragement. Many Thanks to Mr. Jens Bargfrede who closely guided me throughout the research work. His words of wisdom helped me during the tough days of my research. Moreover, his deep technical knowledge in integrated circuits, mathematics and programming was a guiding light for my research. Furthermore, I am extremely thankful to Mr. Christian Funke whose tremendous knowledge in the field of timing of digital circuits was a constant source of novel ideas. He constantly challenged my knowledge on the subject and kept me on my toes which helped me understand the global picture and the practical usage of my work. Moreover, his advice on presenting my research to various audiences has helped me develop and improve my presentation skills.

Special thanks to Dr. Rainer Kress, Dr.-Ing Klaus Oettinger, Mr. Steffen Rost, Mr. Werner May who gave me the wonderful opportunity to be part of Infineon family and pursue my PhD. Many thanks to Dr.-Ing Petra Nordholz and Mr. Thomas Moehring who are my other team members at Infineon who made the work environment spirited, interesting and enjoyable. Furthermore, I would like to thank Lantao Wang who did his master thesis and internship under my supervision at Infineon. His work supported my research which helped the completion of the my research.

This PhD thesis would have never been a success without the support of my parents-Mr. Kasturi Rangan, Ms. Kamakshi and my extended family. Throughout my life, they have been a constant source of encouragement and extend their support to pursue my dreams and achieve my goals. Their moral support is invaluable and I would like to express my deepest gratitude for being such a wonderful family.

I would like to thank my friend Faisal Caeiro who inspired me to pursue my dreams and supported me through all the stages of my PhD thesis.

Finally, last but not the least my special thanks to all my friends who are a part of my life and believed that I could achieve any goal that I set for myself.

# Contents

| 1 | Intro | oduction                                     | 1  |

|---|-------|----------------------------------------------|----|

|   | 1.1   | Motivation                                   | 1  |

|   | 1.2   | State of the Art                             | 4  |

|   | 1.3   | Contributions of this Work                   | 5  |

|   | 1.4   | Structure of this Dissertation               | 6  |

| 2 | Back  | cground                                      | 7  |

|   | 2.1   | Process Variations                           | 7  |

|   | 2.2   | Classification of Process Variations         | 9  |

|   | 2.3   | Voltage Variations                           | 11 |

|   | 2.4   | Temperature Variations                       | 13 |

|   | 2.5   | Timing of Digital Circuits                   | 14 |

|   | 2.6   | Timing Analysis of Digital Circuits          | 17 |

|   | 2.7   | Timing Monitors: Related Work                | 18 |

| 3 | Desi  | gn-Dependent Timing Monitors                 | 25 |

|   | 3.1   |                                              | 25 |

|   | 3.2   |                                              | 27 |

|   | 3.3   | Characterization of Tile Delay Sensitivities | 30 |

|   | 3.4   | Synthesis Using Optimization Solvers         | 33 |

|   | 3.5   | Delay-Tracking-Based DDRO                    | 36 |

|   | 3.6   |                                              | 37 |

|   | 3.7   | Evaluation of DDROs                          | 50 |

|   | 3.8   | Summary                                      | 51 |

| 4 | Expe  | erimental Results of DDROs                   | 53 |

|   | 4.1   |                                              | 53 |

|   | 4.2   |                                              | 54 |

|   | 4.3   |                                              | 60 |

|   | 4.4   |                                              | 64 |

|   | 4.5   |                                              | 66 |

|   | 4.6   |                                              | 68 |

|   | 4.7   |                                              | 70 |

|   | 4.8   | * 0                                          | 73 |

|   | 4.9   | *                                            | 76 |

|   | 4.10  | Summary                                      | 77 |

## Contents

| 5  | 5 Methods to Group Critical Paths                        |         | 79  |  |  |

|----|----------------------------------------------------------|---------|-----|--|--|

|    | 5.1 Hierarchical Clustering                              |         | 79  |  |  |

|    | 5.2 KMeans++ Clustering $\ldots \ldots \ldots \ldots$    |         | 83  |  |  |

|    | 5.3 Model-Based Clustering                               |         | 87  |  |  |

|    | 5.4 Analysis of Clustered Critical Paths                 |         | 90  |  |  |

|    | 5.5 Summary $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |         | 92  |  |  |

| 6  | 6 DDRO Synthesis for Large-Scale Digital Design          |         | 95  |  |  |

|    | 6.1 DDRO Delays versus Critical Path Cluster O           | Centers | 96  |  |  |

|    | 6.2 DDRO Delays versus Critical Path Delays .            |         | 100 |  |  |

|    | 6.3 Summary $\ldots$                                     |         | 101 |  |  |

| 7  | 7 Summary and Outlook                                    |         | 103 |  |  |

| Α  | A List of Symbols                                        |         | 107 |  |  |

| В  | B List of Abbreviations                                  |         | 113 |  |  |

| Bi | 3ibliography 12                                          |         |     |  |  |

# **1** Introduction

# 1.1 Motivation

Electronic systems are used extensively in safety critical applications involving public health, property and environment. Hence it is essential to ensure the correct working and reliability of the electronic systems in use. Some examples of these safety critical systems could be anti-lock braking systems in automobiles, motor and gear controllers, airbag controllers, fly-by-wire aircraft, shut-down systems at nuclear power plants [1], and electronics in the field of medicine and recreation. Due to the nature of these applications, safety critical electronic systems are required to operate across a wide range of environmental conditions and workload. Therefore, to ensure safe operation, reliability and robustness of safety critical systems are of prime importance.

Compared to former larger technology nodes, the performance of electronic circuits such as timing are further influenced by variations in manufacturing, environment and aging [2] [3] [4] [5] [6]. Variations in timing of digital circuits due to manufacturing and environmental variations might lead to timing errors which in turn could lead to failure of electronic systems. To prevent such failures, analysis and implementation of a chip is performed with worst case scenarios. Thus, additional design guardbands are added based on worst case timing analysis and is verified by a sign-off method. This pessimistic approach ensures the requested circuit performance which is the operating frequency, but at the cost of larger area, higher power consumption and increased design time.

Furthermore, manufactured chips could be subjected to more variations with deteriorated timing attributes due to process or aging which are not modeled accurately and resulting in mismatches between hardware and the model. Thus, the timing of certain chips might not meet the required timing criteria. Therefore, speed binning [7] [8] of all the produced chips is performed where, as the name suggests, the chips are categorized based on their frequency. Additionally, post-silicon chip validation [9] [10] is done to verify if the required timing criteria are met. Thus, based on these steps, the yield of manufactured chips, i.e. the percentage of chips amongst the complete set which meet the required timing criteria, is obtained.

During the post-silicon chip validation, additional guardbands known as test guardbands are added to check if chips meet the timing criteria due to test inaccuracies and because the chips could be subjected to additional variations and aging. Moreover, after manufacturing, no two chips are identical and also, multiple tests on the same chip show different results. An example of addition of test guardbands is done by overcompensating the frequency of the given chip. This means that if a chip is set to work at frequency

#### 1 Introduction

$f_C$  Hz, then the chip is verified for  $f_C + \Delta f_C$  Hz. The added guardband  $\Delta f_C$  depends on the accuracy of timing prediction of the entire chip during post-silicon chip validation.

For accurate prediction of chip timing, performing an exhaustive test, i.e. to test each path of a design to ensure zero defects is not feasible either with scan test methods [11] or with functional test patterns [12]. Moreover, increase in test time results in increased test costs and thus the test time should be minimized. Therefore, this thesis proposes to use timing monitors as test structures that can be placed on multiple parts of a chip and are used to evaluate the delay of a chip at the given fabrication condition and at different voltage and temperature conditions. Formerly, generic ring oscillator which are single cell type test structures were used to evaluate the chip timing behavior. However, these monitors are not adequate since they are not design-specific and therefore do not reflect the timing behavior of a chip.

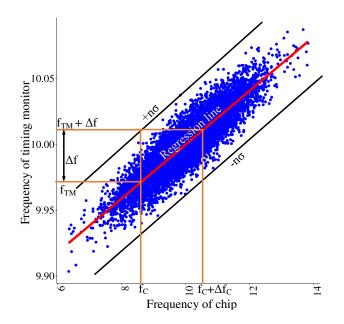

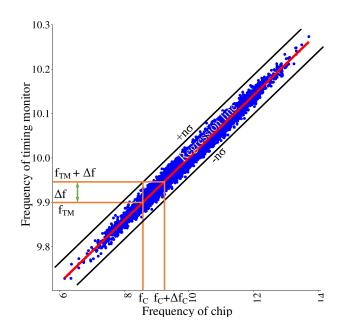

Figures 1.1 and 1.2 show examples of timing monitors which have poor and good correlation to the manufactured chips, respectively. Figures show  $f_{TM}$ , the minimum frequency of the timing monitor which corresponds to the chip frequency  $f_C$ , that meets the required timing criteria. Since the measurement frequency of timing monitors cannot have 100% correlation with the chip frequency, classifying only chips below  $f_{TM}$  could result in chips which are classified as a good chip but might not meet the required timing criteria.

Therefore, a certain test guardband by overcompensating frequency  $\Delta f$  is added which is based on the quality of timing monitors. The timing monitor in Figure 1.1 does not accurately reflect the timing behavior of the chip and therefore, has larger test guardband. On the other hand, the timing monitor in Figure 1.2 is highly correlated to the chip frequency and thus has reduced test guardband. Therefore, the yield of the produced chips could be higher by using a good timing monitor which has a sharper screening in comparison to a poorly correlated timing monitor.

Thus, a set of timing monitors is required to be designed and implemented which can precisely represent the timing behavior of chip design across process, temperature and voltage conditions. Furthermore, it should be ensured that these timing monitors collectively represent the timing behavior of all the blocks on the chip such that they can fully reflect the timing behavior of the chip. Additionally, correlating timing monitors whose timing behavior represent the timing behavior of an industrial design could also aid in the improvement of timing models. Thus, the design of design-dependent timing monitors are also considered as an integral part towards the improvement of timing models.

In summary, design-dependent timing monitors which reflect the delay behavior of a digital design help in the substantial reduction of test guardbands and increase the yield of produced chips. This thesis dives into this design specific approach and endeavors to provide different design methods for the design-dependent timing monitors which are highly correlated to a given digital design. Moreover, different methods are discussed which can reduce the required number of timing monitors making them feasible to evaluate of timing of large scale industrial designs.

### 1.1 Motivation

Figure 1.1: Example of a timing monitor with poor correlation to manufactured chips thus resulting in increased test guardbands and resulting in low chip manufacturing yield

Figure 1.2: Example of a timing monitor with good correlation to manufactured chips thus resulting in reduced test guardbands and resulting in high chip manufacturing yield

# 1.2 State of the Art

The state-of-the-art performance monitors can be broadly classified into two categories, namely, generic monitors and design-dependent monitors. The aim of this thesis is to build monitors which can mimic the delay behavior of a given design. Therefore, the existing state-of-the-art monitors are analyzed with respect to the quality of representing the timing behavior of a given digital design.

Traditional timing monitors are generic ring oscillator (GRO) monitors and processspecific ring oscillators (PSROs) [13] [14] [3] [15]. These monitors are constructed with a single cell type. A ring oscillator is built by connecting the output of a chain of inverting CMOS standard cells or circuit blocks to its input, in form of a closed loop. The frequency of oscillation of a ring oscillator is measured to obtain the signal propagation delay through the chain of inverting CMOS circuit which are built to analyze the technology node at an early stage.

GROs are simple structures with low design and area cost. PSROs are also made of single cell type ROs, but are built in order to extract the sensitivity of delay of circuits w.r.t. specific process parameters. This means, not only frequency but current and voltage drop of these test structures are measured. However, both GROs and PSROs are neither based on the analysis of all standard cell types nor on the timing behavior of critical paths. This makes correlating the design-specific and path-specific behavior to these ring oscillators very complex [9] [16] [17] and thus PSROs and GROs are not suitable candidates to represent the timing of a chip design.

To represent the delay behavior of a chip, design-dependent monitors were developed. One of the design-dependent monitors is the in-situ approach. The concept of in-situ monitors is to evaluate the timing of a chip by monitoring its setup-time critical paths. Hence, an additional flip-flop, so called *shadow* flip-flop, with a delayed clock is placed alongside the capture flip-flop of a critical path [18] [18] [19]. Due to the addition of shadow flip-flops in critical paths of the design, in-situ monitors are intrusive to the design. Moreover, the additional flip-flops added to thousands of critical paths result in a tremendous increase in area and power overhead.

The drawbacks of GROs and in-situ monitors are overcome by representative critical path (RCP) [20] monitors. Hence, a single monitor is used to represent all the setup critical paths in a design. Although RCPs are design-specific, having only one monitor to represent all the critical paths makes the RCP inaccurate. The drawback of RCPs is overcome by tunable replica circuits (TRCs) [21], which are built adjacent to the critical paths and tuned to track their delays. However, TRCs are intrusive and highly complex to design.

The drawbacks of the mentioned approaches are overcome by employing design dependent ring oscillator (DDRO) monitors [22] [23] [24]. In the DDRO approach, setup critical paths are grouped based on their similarities w.r.t. delay sensitivities to PVT. For each path group, a DDRO consisting of a chain of tiles is constructed, where a tile is a chain of standard cells of equal type. The objective of the DDRO is to match the timing behavior of the target critical path group. The state-of-the-art DDROs however, do not consider the impact of input transition time and output load of a tile during the DDRO synthesis. Moreover, due to the concept of sensitivity matching, these DDROs are forced to use SPICE-based delay characterization which makes them unsuitable for large-scale industrial designs. Additionally, process parameters affecting delay sensitivities differ for each technology node. Thus, majorly contributing process parameters impacting the delay sensitivities have to be evaluated for every technology node. Furthermore, given that it is highly challenging to compute delay sensitivities with high accuracy, sensitivity-based DDROs might result in tracking delay with poor quality to their respective critical paths.

In summary, there is a lack of highly accurate monitoring systems whose timing behavior match the timing behavior of a chip across various conditions of PVT. Thereby, evaluating the timing of a chip such that the voltage and timing overestimation of a chip can be reduced effectively by the reduction of guardbands.

# 1.3 Contributions of this Work

This thesis focuses on the methods to synthesize DDROs to represent the timing of critical paths in a digital design. Thereby, a new method of DDRO synthesis is proposed which uses delay-tracking for construction of DDROs in contrast to the sensitivitytracking used in the existing state-of-the-art method [22]. Furthermore, high accuracy settings for the characterization of building blocks of DDROs are proposed which involves delay characterization with realistic environment. Moreover, quadratic programming with higher accuracy for the DDRO synthesis is proposed instead of the linear programming used in the existing state-of-the-art method [22]. With the high accuracy settings for delay characterization and DDRO objective, direct solvers for the DDRO synthesis result in infeasible CPU run-times. Therefore, three new heuristic algorithms are developed which have reduced and feasible CPU run-times.

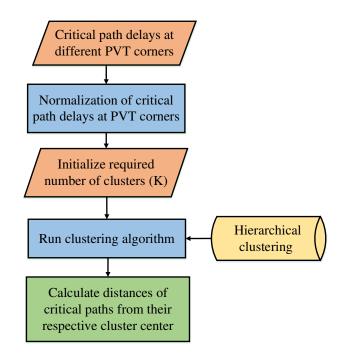

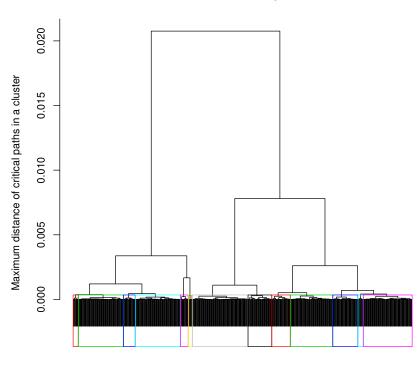

To further reduce the computational complexity, delay characterization for DDRO synthesis is obtained by static timing analysis (STA) instead of SPICE simulation, which is used in the state-of-the-art method. Also, to facilitate DDRO synthesis for large scale industrial designs, critical paths are identified by STA and three different clustering methods for the grouping of critical paths are investigated; namely, KMeans++, Hierarchical clustering and model based clustering. For each group of critical paths one DDRO is synthesized. Additionally, using STA makes it feasible to obtain the delays of thousands of critical paths on a chip and thus makes the DDRO synthesis feasible for large scale designs. DDROs are synthesized for groups of critical paths and evaluated for their timing tracking ability of their respective group. To assess the quality of the developed DDRO synthesis method, DDROs are built and evaluated for an industrial technology below 40nm. The proposed DDRO synthesis methods are evaluated by computing the delay tracking error with respect to the given target critical path. Parts of this work have been published in [25] and submitted to TCAS-1 journal to be published in January 2020 [26].

## 1 Introduction

# 1.4 Structure of this Dissertation

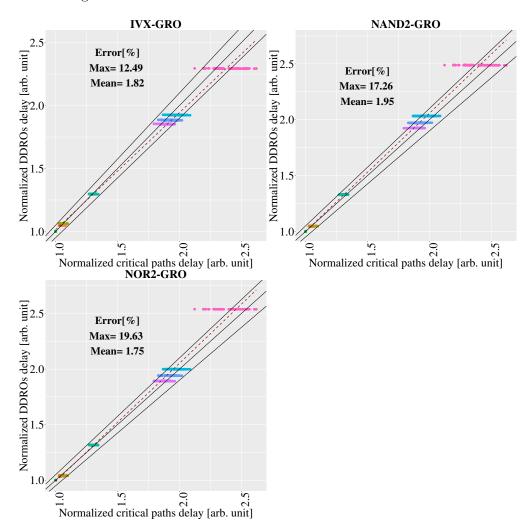

The remainder of this dissertation is structured as follows. In Chapter 2, the literature on the causes of process, voltage and temperature variations, along with their impact on the timing of digital circuits is reviewed. Furthermore, the existing state-of-the-art timing monitors used for evaluating the timing of technology nodes and chip design are explained. In Chapter 3, the design goal of DDROs to evaluate timing of critical paths on a chip is explained. Moreover, mathematical formulations of the sensitivity-based DDROs are introduced. Additionally, enhanced methods of characterizing the delay of building blocks of DDROs are presented. Furthermore, the concept and formulation of delay-tracking-based DDRO synthesis is presented. This Chapter also describes three new heuristic methods developed to solve the DDRO optimization problem. Chapter 4 presents results of DDRO synthesis for various scenarios: (1) various DDRO formulations and synthesis methods, (2) various accuracies of delay characterization, (3) synthesis of DDROs using direct solver versus heuristic method, (5) synthesis of DDROs using extracted data from STA, (6) synthesis of DDROs with different parameter settings of the solver and (7) quality of delay matching of DDROs versus generic ring oscillators (GROs). Chapter 5 explains the three different clustering methods investigated to group critical paths namely Hierarchical, KMeans++ and Expectation-Maximization algorithms. Furthermore, in order to evaluate the best suited method to cluster critical paths for DDRO synthesis, the results of the three algorithms are compared. In Chapter 6 DDROs are synthesized for each critical path cluster and are evaluated w.r.t their respective cluster. Chapter 7 summarizes the various DDRO synthesis results and concludes on the DDRO matching quality.

The scaling of technology nodes has resulted in scaling of the process, temperature and voltage (PVT) variations. This scaling of PVT variations has a significant impact on the timing of digital circuits. This impact on timing performance in worst case can result in failure of manufactured chips. In order to establish error free timing performance of a chip, the different sources and impact of PVT variations have to be analyzed and modeled [27] [28]. This Chapter explains the different sources of manufacturing variations along with their classification. Furthermore, the cause and impact of environmental variations on timing of digital circuits are explained. Moreover, to verify the timing of a digital design, methods used to analyze the timing for digital circuits are explained. Additionally, the existing state-of-the-art timing monitors to evaluate the timing of a chip post-silicon are explained.

# 2.1 Process Variations

Process variations are the unintentional physical variations observed in the transistor parameters of devices and interconnects from intended theoretical design values [29]. These variations are observed in the form of deflected device characteristics from its actual intended behavior [30].

The procedure to manufacture integrated circuit is done on a silicon wafer along with several chemical and mechanical processes. At first, a desired material is deposited on a wafer, after which photo-lithography is performed to transfer the required pattern on to the wafer using light. Finally, etching is done to remove the unwanted material from the wafer. These processes are repeated several times to manufacture a complete chip. However, these chemical and mechanical steps are subjected to process variations which impacts the performance of manufactured devices within die as well as between die-to-die, wafer-to-wafer, and lot-to-lot [31].

The uniformity of the fabricated transistor is highly dependent on the precision and control of the lithography process. The wavelength of light used in the lithography process is  $\lambda = 193$  nanometers and has remained the same since the 130nm technology node [32]. Due to this, there is an increased amount of diffraction occurring during the lithography process which results in critical dimensions (CD) and the device structure gets increasingly blurred [33]. Advanced process methods are developed which are used to reduce the blurring effect of the fabricated transistors. However, it is still highly challenging to reduce the absolute deviation of the physical parameters of the transistors.

The physical parameters of transistors which result in performance variation of these devices is given as follows: The critical dimensions (CD) of a MOSFET transistor are determined by the channel length (L) and width (W). Therefore, varying these parameters

from their nominal values result in significant variation from the expected performance of MOSFETs. Moreover, dielectric layer which isolates the gate electrode from the substrate has a specific thickness (Tox) and is critical to the device behavior. Additionally, threshold voltage (Vth) which is the minimum voltage required to switch on a transistor is another important parameter which defines MOSFET's performance. The drive current of the transistor is directly proportional to W/L. Therefore, fluctuations of the transistors width (W) and length (L) directly influence its drive current. Additionally, channel length variation also alters the transistor threshold voltage (Vth) which directly influences the drive current and thereby the switching time of transistors. The following Subsections explain the variations of transistor parameters due to different process variations.

## 2.1.1 Line Edge Roughness

Line edge roughness (LER) is the result of random variations at the edges of gate pattern resulting in roughness of the printed gate pattern edge. Photo-resists are light sensitive materials used to create required geometric patterns of transistors along with light insensitive material known as photo-masks. Light sources of specific wavelengths are used for the removal of photo-resists during the transistor manufacturing. LER is caused by statistical variations of the photon count or imperfections occurring during the removal of photo-resist and therefore, is a source of intrinsic parameter fluctuations in MOSFETs. Moreover, with decreasing technology nodes, the wavelength of the light source used in photo-lithography is larger than the critical dimensions of transistors which results in larger transistor gate variations. Thus, LER is an major source of variation of channel length [34] [35].

## 2.1.2 Random Dopant Fluctuation

The channel region of a transistor is doped with atoms of a material different from the substrate. This determines and controls the transistor threshold voltage (Vth). These doped atoms are known as impurity atoms or dopants. Addition of dopants is performed using ion implantation where the dopant atoms are randomly placed into the transistor channel. However, the process of ion implantation leads to statistical variations in the actual number of implanted dopants. The change in number of dopants in the channel regions affects the carrier potential energy which in turn affects the threshold voltage and current. Thereby impacting the drive strength of a transistor. In older technology nodes, thousands of dopant atoms were implanted in the channel region. Therefore, a deviation of few atoms had negligible impact on the transistor behavior. However, with the shrinking technology nodes, only tens of dopant atoms are used which results in larger mismatch of transistor behavior [36] [37].

## 2.1.3 Optical Proxity Effect

Optical proximity effect (OPE) is the variation in the size and shape of a transistor feature due to the proximity of other neighboring devices. OPE occurs at the step of photo-lithography due to the diffraction of light with the neighboring structures. Polysilicon material is used as the gate contact and is effected due to OPE. Thus, OPE results in variations of the effective transistor length as a function of local layout. This results in process induced systematic intra-die variations [4].

## 2.1.4 Gate Oxide Thickness Variations

The gate oxide can be grown by using oxygen and nitrogen with an absolute accuracy of 12 inter atomic layers. Incorrect gas flow during the oxide growth can result in gate oxide thickness variations. Non-uniform or ultra-thin gate oxide thickness causes variations in threshold voltage across the wafer and can also cause gate leakage current. Moreover, former technologies had gate oxide thickness (TOX) of tens of inter atomic layers and had larger gates which resulted in negligible impact of TOX variations. However, in technologies below 30 nm with oxide thicknesses between 13 nm (approx. 515 inter atomic spacings), TOX variations can result in substantial uncertainty in threshold voltage [38].

# 2.2 Classification of Process Variations

Timing of a digital design is an important performance parameter that varies due to process variations. Therefore, the classification and effect of different sources of process variations have to be taken into consideration while modeling the switching time of a transistor or a digital logic gate. The sources of different process variation are classified as follows [29]:

## 2.2.1 Systematic Variations

Systematic or deterministic variations are produced due to the steps involved in the manufacturing flow. In the manufacturing steps, optical proximity effects caused during lithography process is one of the main root causes for the process variation. Optical proximity effects (OPE) mainly result in variation in layout design and fall into the category of systematic variation. Thus, the amount of variation introduced across dies and wafers is approximately the same and this can be corrected using techniques such as optical proximity correction (OPC) methods.

#### 2.2.2 Non Systematic Variations

Non systematic variations are random variations which are generated from various process steps in the manufacturing flow. Due to the randomness of these variations, they are statistically modeled and are further classified based on their behavior into inter-die (global variation) and intra-die (local variation).

## 2.2.2.1 Inter-die Variation

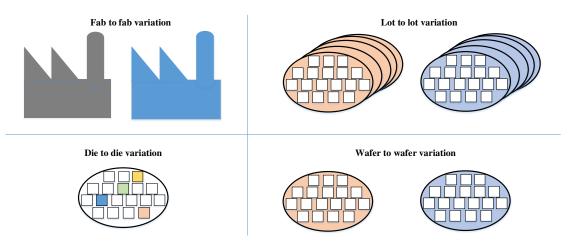

Inter-die variations result in process variations which affect the performance parameters between two manufactured dies. In this case, the parameters within one die is assumed to be affected in the same way and result in a uniform value within the die. Figure 2.1 shows different types of inter-die variation.

Figure 2.1: Different types of inter-die variation [29]

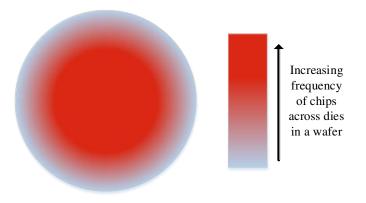

Die to die variations can occur due to the mis-alignment of masks exposed one after another in the lithography process. Wafer to wafer variations can occur due to inexact placement of the wafers in the equipment when processing different wafers. Lot to lot variations can occur due to different parameter settings during the working of the wafer equipment. Fab to fab variation can occur due to a specific condition set for the manufacturing of each of fab. An example of the impact of inter-die variations on chip frequency is shown in Figure 2.2. From Figure 2.2, it can be seen that the speed of the manufactured dies decreases with increase in distance from the center of the wafer. Thus, the dies lying in the inner concentric regions on the wafer on an average have higher speed than the outer concentric regions.

## 2.2.2.2 Intra-die Variation

Intra-die variations are classified as local variation and affect different parts of the same chip differently. Due to process variations, different devices on the same chip have different physical dimensions and result in difference in performance within the chip. With the decrease in technology node, the effect of inter-die variations have been increasing and contribute to a major part of the total process variation. Intra-die variations can be further classified as follows:

1. **Random Variations**: As the name suggests, these variations are random and not correlated to the variations in other parts of the chip. Two main causes of these

Figure 2.2: Variations across dies in a wafer [29]

variations are random dopant fluctuation (RDF) and line edge roughness (LER), as described in Subsections 2.1.2 and 2.1.1, respectively.

2. Spatially Correlated Variations: These include the process variations within the die where different parts of the die could have process variations correlated to each other due to the effect of certain proximity. Basic manufacturing effects such as etching and photo-lithography are the main causes for these variations. The physical dimensions of a transistor such as channel length (L), width (W) and oxide thickness is generally affected by spatially correlated variations.

# 2.3 Voltage Variations

With the decrease in technology nodes, environmental variations such as voltage and temperature also have larger impact on the performance of semiconductor devices. Moreover, for some power efficient designs, electronic circuits are operated in sub-threshold voltage regions. Small variations of voltage in sub-threshold regions can lead to erroneous performance of circuits. Voltage fluctuations in semiconductor devices are mainly caused due to the following reasons:

## 2.3.1 IR Drop

IR drop is also known as voltage drop, occurs due to the flow of current through the parasitic resistance of the power supply grid. The voltage fluctuation is given by Ohm's law

$$\Delta V_{IRdrop} = R_{grid} \cdot i(t) \tag{2.1}$$

where  $\Delta V_{IRdrop}$  is the voltage fluctuation,  $R_{grid}$  is the parasitic capacitance of the power grid, *i* is the current which is dependent on time *t*.

#### 2.3.2 Current Derivative Noise

Current derivative noise occurs due to parasitic inductance. Packaging of semiconductors does not scale as fast as scaling of the CMOS technology node which introduces larger parasitic inductance. This results in larger current noise with the decrease in technology node. Voltage variation due to current derivative noise is given by:

$$\Delta V_{\frac{di}{dt}} = L_{parasitic} \frac{di}{dt} \tag{2.2}$$

where  $\Delta V_{\frac{di}{dt}}$  is the voltage variation due to current derivative noise and  $L_{parasitic}$  is the parasitic inductance. Furthermore, the combination of voltage droop and current derivative noise could either lead to voltage drops or to voltage overshoots [2] [39]. The following section describes the impact of voltage variation on timing of digital circuits.

#### 2.3.3 Impact of Voltage on Timing of Digital Circuits

The impact of voltage variation on circuit timing for a specific temperature is shown in Figure 2.3. It can be seen that the delay of circuit increases with decrease in voltage. The relationship between CMOS logic gate propagation delay and supply voltage can be written as [2]:

$$t_{gate} \propto \frac{V_{DD}}{(V_{DD} - V_{TH})^{\theta}} \tag{2.3}$$

where  $t_{gate}$  is the delay of a CMOS logic gate,  $V_{DD}$  is the supply voltage,  $V_{TH}$  is the threshold voltage and  $\theta$  is the technology dependent parameter. It can be seen that small changes in  $V_{DD}$  close to the value of  $V_{TH}$  result in larger changes in gate delay  $t_{gate}$ . In order to evaluate the voltage changes on the semiconductor device and account for the timing variation, on chip test structures or sensors are required to monitor the voltage variations.

#### 2.4 Temperature Variations

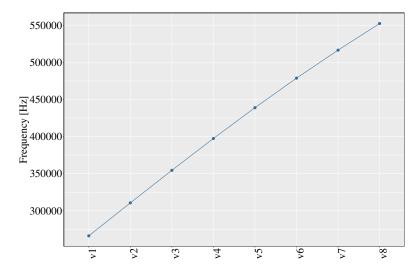

Figure 2.3: Frequency of a ring oscillator with increasing voltage at a constant temperature

# 2.4 Temperature Variations

Temperature variation is yet another major factor for performance variation on semiconductor devices. The main causes for the changes in temperature on device are (1) changes in the ambient temperature and (2) local temperature variations due to power dissipation in transistors at the region of high activity, also known as hot spots [2] [39]. Temperature variations also have time constants which can vary between milliseconds to seconds.

Figure 2.4 shows the impact of circuit delay with varying device temperature at different voltages. Due to the decrease in carrier mobility in the semiconductor and increase in parasitic resistance of the interconnect, an increase in the temperature increases the delay of a circuit. However, in smaller technology nodes a new effect namely the inverted temperature effect (ITE) has become prevalent where at lower voltages, the delay of a circuit decreases with increase in temperature.

In summary, it can be seen that the delay of a circuit is highly impacted by process, temperature and voltage variations. Therefore, digital circuits have to be extensively analyzed for their timing behavior. To ensure proper functioning of circuits, timing analysis should ensure that all timing constraints are met across all possible different conditions of PVT. The next section explains about the methods that are used for the analysis of circuit timing.

Figure 2.4: Frequency of a ring oscillator with increasing temperature at different voltages

# 2.5 Timing of Digital Circuits

Digital circuits consists of a combination of logical and synchronous elements. Moreover, these circuits can be classified into data path and clock path. Data paths are the ones where the data signal transmits through the circuit. Clock paths are the ones where the clock signal flows to different sequential cells. The logic portion of the digital data path consists purely of CMOS gates without memory and are built using NMOS and PMOS transistors. Edge-triggered flip-flops are used as sequential cells in synchronous digital circuits [40]. The clock path mainly connecting the flip-flops used in the synchronous circuits also consists of certain logic gates. In very large scale industrial (VLSI) designs, basic logic gates and flip flops are the building blocks of larger digital circuits and they are pre-designed in the form of standard cells. A collection of standard cells for a certain technology node compose a standard cell library.

In order to evaluate the performance of digital circuits, transistors which are the smallest building blocks of these digital circuits are modeled for each technology node using transistor parameters based on a standard known as BSIM parameters [41]. These transistor models are then used to pre-characterize the functionality and performance of the standard cells in terms of timing, power, etc.

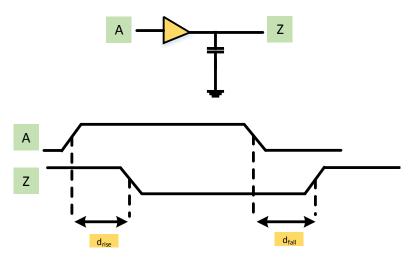

Figure 2.5 shows the propagation delay or timing of an inverter cell. The time taken between the output transition (Z) reaching 50% of its final value and input transition (A) reaching 50% of its final value is termed as propagation delay of a cell. Based on the timing analysis of standard cells, the propagation delay of a logic gate depends on (1) process parameters (P), (2) voltage (V), (3) temperature (T), (4) input transition time or slope of input signal, (5) output RC load, (6) timing arc, and (7) rising or falling transition at the input pin as shown in Figure 2.5.

Figure 2.5: Propagation delay of a standard cell

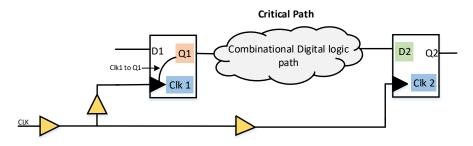

Figure 2.6 illustrates an example of a digital circuit where a logical path is sandwiched between a launch and a capture flip-flop. The time taken between the clocking of data at the launch flip flop at Q1 in Figure 2.6 and the arrival of the data at the capture flip-flop D2 is known as the timing of data path in a combinatorial digital path. The clocking of data at the launch flip-flop also considers the time taken for the data to propagate between CLK1 to Q1. Thus, the clock-to-Q-delay of the launch flip-flop is also added to compute the propagation delay of the data path.

Additionally, there also exist clock paths which are timing paths that are completely traversed by clock signals. Generally only buffers and inverters gates are used in the clock paths. However, gated clock paths are sometimes used for power saving where a gated clock path could have other logic gates such as AND, NAND gates. Thus, there exists two different kinds of clock paths:

- 1. Launch path: This is the timing path of the clock signal between the clock source and the launch flip-flop.

- 2. Capture path: This is the timing path of the clock signal between the clock source and the capture flip-flop

Simple edge triggered flip-flops used for synchronous circuits have typically two inputs and one output pin. The input pins are the clock and data signal input pins. A clock signal with a specific time period is given into the clock pin. The data signal pin receives its input either from an input port or another logic circuit. The output pin of a flip-flop is the data which is captured by the edge of the clock input. The amount of time taken for the clock to propagate the data signal is known as clock-to-Q-delay of the flip-flop. Moreover, for the data to be clocked in correctly and maintain signal integrity, flip-flops define two inherent features which are explained as follows [42]:

1. Setup time: In an ideal flip-flop, the data signal (D) can arrive at the time when the clock edge is triggered. However, in practical scenarios for the clock edge to

Figure 2.6: Example of a combinatorial digital path

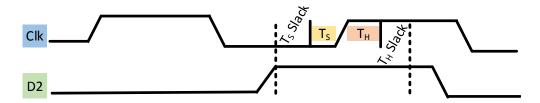

capture the data signal correctly, the data signal must arrive earlier than the clock edge and remain stable at the time of arrival of the clock edge. The amount of time the data must arrive before the clock edge for the clock to safely capture the data signal is known as the setup time of the flip-flop.  $T_S$  in Figure 2.7 shows the setup time for a flip-flop.

2. Hold time: In order to ensure data signal integrity, the data signal (D) should remain stable for a certain amount of time after the transition of the active edge of the clock. This time is known as the hold time of the flip-flop.  $T_H$  in Figure 2.7 shows the hold time for a flip-flop.

Figure 2.7: Example of timing checks at a capture flip-flop for a combinatorial digital path

An industrial design of digital circuits could consist of millions of digital paths consisting of synchronous and logic circuits. In order to ensure correct working of all these paths, the timing constraints such as setup and hold times explained earlier should be met, i.e. for setup time, the data signal (D) should arrive before the setup time of the flip-flop, and for hold time, the data signal should remain stable for a certain time. The set of digital paths in synchronous logic circuits which have the largest and smallest propagation delays are known as critical paths of a digital design. These critical paths tend to violate the setup and hold timing constraints. Critical paths whose data signal (D) comes after the required setup time  $T_S$  of a flip-flop result in a setup time violation. Critical paths whose data signal (D) changes before the required hold time  $T_H$  of a flip-flop results in a hold-time violation.

In order to check the timing violations of a digital design, extensive timing analysis of circuits are to be performed and all the timing conditions of a design should be met. Moreover, as explained earlier these paths also undergo timing variations due to PVT variations. Thus, the timing analysis performed should also consider these variations to ensure correctness of timing. The following Subsections explain two different methods for analyzing timing of digital circuits.

# 2.6 Timing Analysis of Digital Circuits

# 2.6.1 SPICE

SPICE is a software which can simulate the different electrical performances of an electronic circuit. SPICE uses mathematical models of transistors and other common circuit components such as resistors, capacitors, etc. to simulate the given digital circuits. The input parameters for timing analysis using SPICE simulation are:

- 1. SPICE netlist of the given set of digital synchronous circuit.

- 2. Netlist of the standard cells used in the digital circuits.

- 3. SPICE models for different electrical devices for different conditions which includes the models for global and local variations.

- 4. SPICE deck which contains the description of the timing analysis to be performed.

SPICE based timing analysis is more accurate than other methods due to extensive characterization of each standard cell and parasitic RC and specific conditions of input parameters. However, due to this extensive analysis, the SPICE based timing analysis for thousands of paths is computationally very complex and results in non-feasible CPU run-times [43].

## 2.6.2 Static Timing Analysis

Static timing analysis (STA) is an exhaustive method to analyze and verify timing of digital circuits. The main motivation of using STA instead of SPICE is due to the reduced CPU run-times through which tens of thousands of critical paths of a design can be analyzed and timing verified in a feasible run-time. Moreover, with SPICE it would be extremely complex to create the environment for timing analysis and perform an exhaustive timing analysis on the entire digital design. Furthermore, it is also impossible to check local variations of all the critical paths with SPICE based simulations, thus proving that STA is a better tool to evaluate timing of a chip.

First, delays of the standard cells are pre-characterized using SPICE simulation for various PVT conditions, input transition times and output loads. These pre-characterized delays are stored and used for STA. To run STA, a digital design along with the clock definitions and specification regarding the external environment such as input-output ports and delay constraints are given. STA then validates whether the given digital design functions without any timing violations at given clock frequencies and supply voltage conditions by performing setup and hold timing checks. Moreover, with STA

the entire digital design with all the timing checks for all possible digital paths and design scenarios can be analyzed in one run [44] [45]. However, the worst case delay at each standard cell is assumed during STA which results in pessimistic timing analysis. This in turn influences the performance of circuits and also results in increased area, power dissipation and cost.

Therefore, to reduce the pessimism in guardbands, the timing of each chip should be evaluated accurately. Timing monitors are used to evaluate the timing of a design or a technology node after manufacturing on different chips and different parts of the chip. Based on the measured timing from these timing monitors across various conditions of PVT, the guardbands can be reduced by decreasing the operating supply voltage and/or increasing the speed of the chip.

# 2.7 Timing Monitors: Related Work

Timing monitors are test structures which are placed on a chip. These test structures are used to evaluate the influence of PVT variations on the timing of digital circuits. The state-of-the-art test structures are designed either to monitor the timing of a specific technology node or to monitor the timing of a specific chip design. The different stateof-the-art timing monitoring methods are described in the below Subsections.

## 2.7.1 Path Delay Tests

With the decrease in technology nodes, there is an increase in the mismatch between the results of timing analysis using timing models and silicon. This may have an impact on the circuit performance and correct functioning of the digital system. Therefore, there is a need to validate the timing on silicon. One of the methods of validating timing on silicon is by measuring the path delays on the chip [11]. Path delay tests aims to analyze the overall delay of path or the sum of the delays of each element on the path [46]. Scan chain testing is used as a method to analyze and detect timing errors on silicon.

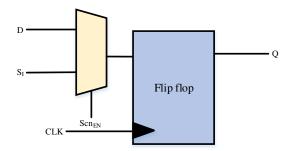

Figure 2.8: Scan flip-flop

The structure of a scan flip-flop is shown in Figure 2.8. The scan flip-flop uses a 2 input multiplexer where one input is the data input (D) for functional mode of the circuit. The second input is the scan input signal  $(S_I)$ . The enable signal  $(Scn_{EN})$  controls if

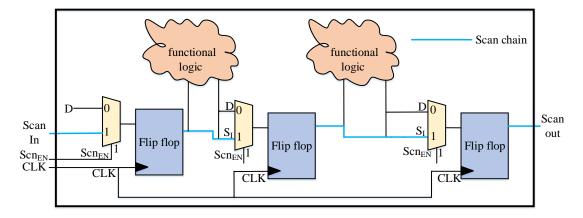

the circuit works in scan mode or functional mode. The output signal (Q) gives the captured data at the flip-flop. The flip-flop is also clocked by a clock signal (CLK). The scan flip-flop is the building block of a scan chain. The scan chain also requires input and output ports which are used to read-in and read-out the data through the scan chain. The first and the last flip-flops of the scan chain are connected to the scan in port and scan out port, respectively. Figure 2.9 illustrates a scan chain with input clock (CLK), scan input, scan enable signal and scan output. Delay path testing with scan chain is performed to detect variations in timing observed in the combinatorial logic block. The output of the scan chain is verified for correctness based on the input of the scan chain. This helps in understanding how much slower or faster the delay path is, in comparison to the prediction using timing models. Additionally, scan chains are used mainly for fault testing of functional circuits.

Figure 2.9: Scan chain

However, path delay tests have several disadvantages. By measuring only the path delays it would be difficult to extract the variations in PVT parameters and the model parameters. Furthermore, addition of a scan MUX, input and output scan ports are required for each scan chain. This results in higher area and power consumption. Moreover, a digital design consists of tens of thousands of paths and it would not be feasible to perform path delay testing on the entire design to verify timing.

## 2.7.2 Generic Ring Oscillators

Ring oscillators are standalone test structures which could be designed either based on a product or a technology node. These ring oscillators could be operated at frequency conditions similar to a product application. Additionally, the measurements from ring oscillators (ROs) are fundamentally closer to the behavior of a technology node where the random process variations are canceled due to averaging over the length of the ROs. ROs are used together with frequency divider circuits to enable ease of measurement of the frequency of ROs. Furthermore, ROs also aid in the analysis of power performance for a specific technology node. Ring oscillator test structures are also testable early in the development process of technology and characterization.

ROs can be designed to represent PVT variations such that the timing of a chip can be diagnosed during post silicon validation testing. The method proposed in [47] is to synthesize single cell type ring oscillators. Multiple ROs are generated from different cell types which show different effects of process variations. Since, these ring oscillators are not synthesized based on a digital design they are also known as generic ring oscillators (GROs). Also, the silicon measurement data from these ring oscillators are analyzed and either the different process parameters are modeled or the existing models of PVT variations are verified.

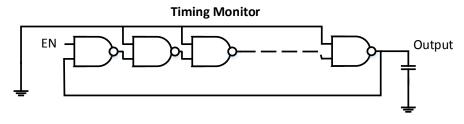

Figure 2.10 shows an example of a single-cell type ring oscillator. A single cell type is connected in chain with a feedback loop to oscillate. In order to oscillate, the connected cell types should be inverting. Moreover, an enable signal is used for enabling the oscillation. As seen in Figure 2.10, ROs are standalone structures and therefore complex methods of delay paths selection and activation need not be performed.

Figure 2.10: Example of a single-cell type ring oscillator

However, since GROs are not design specific they cannot predict the timing of a design. In order to predict the timing of a specific design, new methods of developing design-dependent timing monitor are explained in the next two sections.

## 2.7.3 Critical Path Replica Circuits

Critical path replica circuits are used to evaluate the timing a chip across PVT variations. The main advantage of the replica circuits is that they are designed to evaluate the timing behavior of a specific digital design. In [48] [49] [50], critical paths from a design are selected and replicated in the form of standalone test structures. The measurement results from these test structures directly correlate the timing behavior of the selected critical paths. However, a digital design could have thousands of critical paths and it is not feasible to generate a replica path for each critical path on a design.

In order to identify a feasible number of critical paths to generate replica circuits as given in [51], critical paths which have similar timing behavior are identified. After this, a set of minimum number of critical paths are sub-selected for which replica circuits are synthesized. In [52] and [53], the selection of critical paths are further improved by the usage of linear algebra and machine learning to dynamically select a set of critical paths monitors which can predict the timing behavior of a chip across PVT conditions.

Yet another method is proposed in [20] to synthesize test structures which replicate critical paths. An automated synthesis algorithm is used to build on-chip test structures that can replicates the various effects of parameters variations of all the critical paths on a chip. The synthesis method identifies the worst case delay of all the critical paths due to intra-die and inter-die variations on a chip and synthesizes a test structure to represent the worst case delay. The measurement on this replica circuit could be used to predict the worst case circuit delay of the entire chip. However, this test structure cannot evaluate random intra-die variations. Moreover, critical paths on a chip have very different timing behavior across different PVT conditions. Therefore, a single test structure will not be able to accurately represent the timing behavior of all the critical paths on a chip.

In order to overcome the disadvantage of critical path replica test structures, tunable replica circuits (TRC) are introduced in [21]. TRCs are built with different logic gate stages such as NAND and NOR stages. These logic stages are placed next to each pipeline stage of the functional circuit and are tuned to track the critical path delays at the respective pipeline stages. The number of TRCs required are much lesser than replica circuits in [48] [49] [50]. Moreover, unlike the replica circuits and generic ring oscillator test structures they can also detect local variations. However, TRCs are intrusive and are extremely complex to tune to replicate the timing behavior of critical paths.

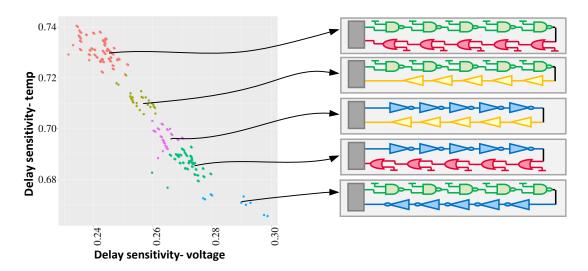

Figure 2.11: Clustering of similar behaving critical paths and DDRO synthesis for a cluster of critical paths

## 2.7.4 DDROs

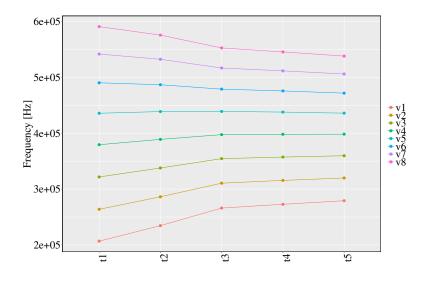

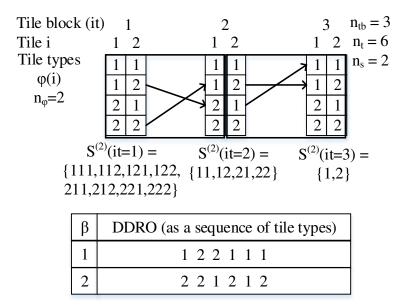

Design-dependent ring oscillators (DDROs) are standalone ring oscillator test structures which are designed to track the timing behavior of critical paths of a digital design. The DDROs are synthesized to match the delay sensitivities of critical paths. A set of critical paths for a digital design are identified and grouped together based on the similarity in their delay sensitivity behavior across PVT conditions. As shown in Figure 2.11, a DDRO is then synthesized per group of critical paths [22].

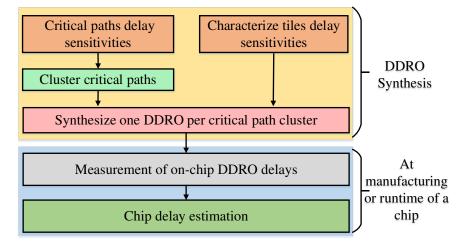

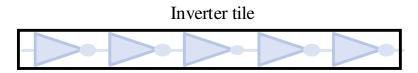

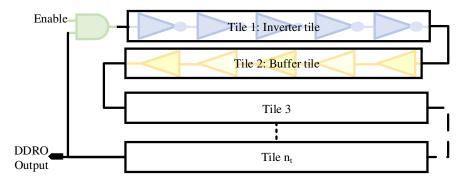

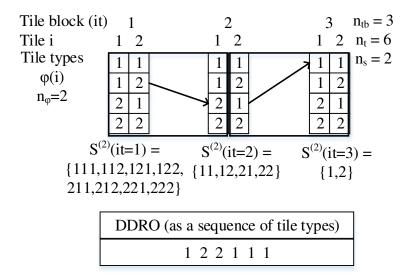

Figure 2.12 shows a method used in [22] to synthesize DDROs. At first, critical paths delay sensitivities are obtained of critical paths and similar behaving critical paths are grouped together. The next step is to synthesize one DDRO per critical path group such that the delay sensitivities of a DDRO match the delay sensitivities of the critical path group. In the DDRO synthesis, tiles are the building blocks of DDROs where tiles are made of chains of standard cells. Figure 2.13 shows an inverter tile example where a tile is made of 5 standard cells [22]. A DDRO is then synthesized using integer linear programming for a target critical path group. The integer linear programmer builds a DDRO by concatenation of tiles by matching the delay sensitivities of target critical path group by the summation of linear sensitivities of the selected tiles. The frequencies of DDROs on the chip are measured on silicon and assessed by which the timing of the target critical path group is evaluated.

Figure 2.12: State-of-the-art DDRO synthesis method

Figure 2.13: Example of a tile in a DDRO

There are several advantages of using DDROs in comparison to other timing monitors. DDROs are more accurate in comparison to having a single critical path monitor because multiple DDROs are synthesized for representing critical paths. Moreover, DDROs are non-intrusive test structures. The required number of DDROs to be placed on a chip is greatly reduced due to the synthesis of one DDRO per group of critical paths. Therefore, only few DDROs are required to accurately estimate the timing of all the critical paths on a chip. Furthermore, DDROs can be used in the early manufacturing stage for process tuning, guard-band reduction and also in the later stage for real-time timing prediction. The change of the monitor's purpose is done by redefining the target sources of variation.

However, these DDROs do not consider the impact of input transition time and output load during the synthesis. Moreover, due to the concept of sensitivity matching, these DDROs are forced to use SPICE-based delay characterization which makes it not feasible for large-scale industrial designs. Additionally, the majorly contributing process parameters impacting the delay sensitivities have to be evaluated for every technology node since the process parameters affecting the delay sensitivities differ for each technology node. Furthermore, computation of delay sensitivities with high accuracy is extremely challenging for the DDRO synthesis. Additionally, the state-of-art DDROs rely on the concept that matching delay sensitivities will create DDROs which can track the delays of critical path groups. Thus, given that the sensitivity based DDROs have several disadvantages, they might result in tracking delay with poor quality to their respective critical paths. Thus, in this work, further investigations are performed on the synthesis of DDROs to improve the quality of DDROs which enables them to accurately track the delays of critical paths on a chip across various conditions of PVT.

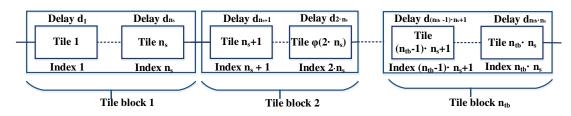

# **3** Design-Dependent Timing Monitors

The concept of the state-of-the-art design-dependent ring oscillators (DDROs) as an on chip timing monitor in [22] is introduced in Sec. 2.7 to improve performance of digital CMOS circuits and design closer to the edge. DDROs, as the name suggests are design specific monitors and are designed to represent critical paths on a chip design. In this chapter, in order to further improve the timing evaluation capabilities of DDROs and provide a more robust design, the following novel methods of DDRO synthesis are proposed: (1) in addition to the linear programming in the state-of-the-art DDROs in [22], quadratic objective is proposed in the DDRO formulation for matching delay sensitivities, (2) to improve DDROs matching quality, more accurate methods of 2-tile and 3-tile delay characterizations of building blocks of DDROs are described in addition to the state-of-the-art 1-tile delay characterization, (3) the implementation of DDRO synthesis formulation is explained for quadratic programming using a direct solver, (4) a new concept for the synthesis of DDROs is presented by tracking the delay of critical paths which can use STA data, thus, enabling their application in large scale industrial design, and (5) three new heuristic methods are developed as an alternative to direct solvers to solve the delay-tracking-based DDRO synthesis problem.

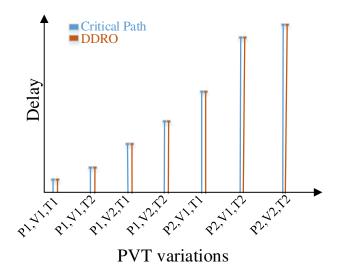

# 3.1 Design Goal of a DDRO

The fundamental goal of a DDRO as shown in Figure 3.1 is to mimic the delay behavior of a critical path or a group of critical paths across PVT conditions. The delay of a critical path varies non-linearly across PVT conditions and the aim of DDROs is to track the delay variations of the critical paths across the different PVT conditions. Frequency measurements of these DDROs on silicon represent the timing of critical paths and thereby monitors the timing of a chip. The main goal of this work is to further increase the DDRO delay tracking accuracy and to facilitate the DDRO synthesis for large-scale designs.

A DDRO is constructed by concatenating tiles of different types. The different tile types are combined in a specific manner to represent the timing behavior of the target critical path group. In this thesis, the DDROs are constructed by tiles which are chains of standard cells of equal type. Figure 3.2 gives an example of DDRO constructed from tile concatenations. The aim of using tiles instead of individual standard cells is to reduce the dependency of delay variations with respect to the output load and input slew. The timing of individual standard cells in a standard cell library are highly influenced by input conditions such as input slope and output load. In order to reduce this influence of input conditions, tiles are used in the synthesis of DDROs. A tile's inner most cells

#### 3 Design-Dependent Timing Monitors

Figure 3.1: Goal of delay-tracking DDRO: The behavior of the DDRO mimics the behavior of the critical path over the PVT parameters

are shielded from the impact of input slew and output load by the first and last few cells respectively.

Figure 3.2: Structure of a DDRO: Concatenation of tiles

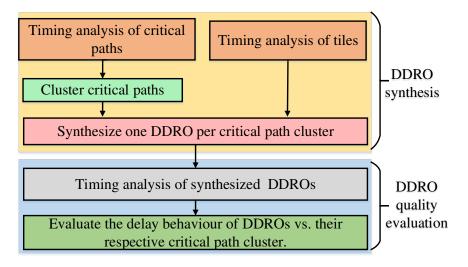

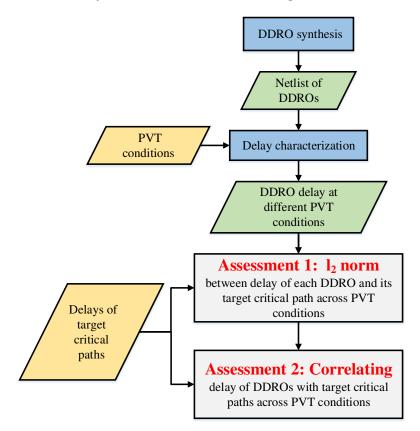

Figure 3.3 shows the structural outline of synthesis and evaluation of DDROs. A collection of types of standard cells are chosen and tiles are constructed for a selected tile length. The delay attributes of the constructed tiles are characterized across various PVT conditions. Furthermore, a set of critical paths on a design are identified and their timing attributes are characterized at various PVT conditions. In order to synthesize DDROs for a large scale industrial chip design, the number of synthesized DDROs should be limited to a feasible number. For this reason, critical paths are grouped based on their similarity in timing behavior and one DDRO is synthesized for each of the critical path groups using optimization methods. Synthesized DDROs are evaluated by comparing their delay-tracking behavior to their given respective critical path group.

Figure 3.3: Flow diagram for DDRO synthesis and evaluation

In this section, the concept of synthesizing DDROs is explained in detail. Sec. 3.2 presents the concept and formulation of the existing state-of-the-art sensitivity based DDROs. In addition to integer linear programming used previously in [22], a new formulation is described to improve DDRO delay matching in Sec. 3.2. In order to further reduce the impact of input slew and load in tiles, new methods of characterizing tile delays are explained in Sec. 3.3. Sec. 3.4 presents the implementation method of DDRO algorithms using traditional optimization solvers. In order to overcome the drawbacks of sensitivity based DDROs, Sec. 3.5 proposes a novel idea for the synthesis of DDROs by matching delays instead of delay sensitivities to critical paths. In Sec. 3.6, the drawbacks of using traditional solvers for DDRO synthesis are presented. Moreover, new Heuristic algorithms to optimize the DDRO objectives are explained, which overcome the drawbacks of traditional solvers.

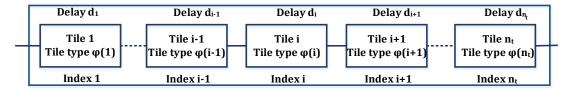

# 3.2 Formulation of Sensitivity-Based DDRO Design

This section first explains the formulation of state-of-the-art sensitivity-based DDROs. Later, a new optimization method is proposed to improve the DDRO's matching quality. Figure 3.4 illustrates a DDRO path comprising of  $n_t$  tiles where  $d_i$  is the delay of a tile at position *i*. In the DDRO synthesis, a specific tile type is selected for each tile position.  $\varphi(i)$  refers to the cell type used in the construction of tile at position *i*. The set of selected types of tiles in the tile library are built from standard cells such as AND, OR, NAND, etc. of various drive strengths and from different standard cell libraries. The number of cell types in the tile library is denoted as  $n_{\varphi}$ .

In order to match the delay sensitivities of DDROs to critical paths [22], delay sensitivities of tiles and critical paths are characterized, by the central difference method. Delay sensitivities by central difference method are calculated by varying each of the

#### 3 Design-Dependent Timing Monitors

PVT parameters  $\mathbf{p}$  from the nominal value  $\mathbf{p}_0$  by a small variation  $+\Delta \mathbf{p}$  above the nominal value and  $-\Delta \mathbf{p}$  below the nominal value [54] [25]:

$$\nabla d_Y(\mathbf{p}_0) \approx \frac{d_Y(\mathbf{p}_0 + \Delta \mathbf{p}) - d_Y(\mathbf{p}_0 - \Delta \mathbf{p})}{2 \cdot \Delta \mathbf{p}}$$

(3.1)

In Equation (3.1), the total number of parameters considered for the sensitivity analysis is  $n_P$  and  $d_Y(\mathbf{p}_0)$  is the delay of a circuit such as the propagation delay of a critical path  $d_{CP}(\mathbf{p}_0)$  or a tile delay  $d_i(\mathbf{p}_0)$ . SPICE simulation is used to perform the delay sensitivity analysis [55].

Figure 3.4: DDRO path structure

For the DDRO synthesis, the considered PVT parameters  $\mathbf{p}$  are globally varying and statistically independent. From Figure 3.4, the DDRO path is constructed by concatenating  $n_t$  tiles. Therefore, the delay of a DDRO path is the summation of delays of  $n_t$  tiles.

$$d_{DDRO}^{(X)} = \sum_{i=1}^{n_t} d_i^{(X)}(\mathbf{p})$$

(3.2)

The superscript (X) denotes the method of characterizing the tile delay sensitivities and is explained in Sec. 3.3. A linear model of tile delay  $d_i^{(X)}(\mathbf{p})$  is assumed around  $\mathbf{p}_0$  by a variation in the PVT parameters of  $\Delta \mathbf{p}$  using the sensitivity from Equation (3.1):

$$d_i^{(X)}(\mathbf{p}_0 + \Delta \mathbf{p}) = d_i^{(X)}(\mathbf{p}_0) + \nabla d_i^{(X)}(\mathbf{p}_0)^T \cdot \Delta \mathbf{p}$$

(3.3)

Inserting Equation (3.3) into (3.2) leads to a linear model of the DDRO path delay  $d_{DDRO}^{(X)}$  around  $\mathbf{p}_0$  by varying the parameters by  $\Delta \mathbf{p}$

$$d_{DDRO}^{(X)}(\mathbf{p}_{0} + \Delta \mathbf{p}) = \sum_{i=1}^{n_{t}} d_{i}^{(X)}(\mathbf{p}_{0}) + \sum_{i=1}^{n_{t}} \nabla d_{i}^{(X)}(\mathbf{p}_{0})^{T} \cdot \Delta \mathbf{p}$$

$$(3.4)$$

#### 3.2 Formulation of Sensitivity-Based DDRO Design

According to Equation (3.4), the DDRO delay sensitivity is the sum of all its tile delay sensitivities. The DDRO optimization goal is then devised to select the number of tiles  $n_t$  as well as the type  $\varphi(i)$  of each tile position  $\{i = 1, \ldots, n_t\}$ , such that the critical path sensitivity matches the DDRO sensitivity:

$$\min_{n_t,\varphi(i),i=\{1,\dots,n_t\}} \left\| \nabla d'_{CP}(\mathbf{p}_0) \cdot n_t - \sum_{i=1}^{n_t} \nabla d'^{(X)}_i(\mathbf{p}_0) \right\|_{pn}$$

(3.5)

pn specifies the type of vector norm. When pn = 1,  $l_1$  norm or linear (L) optimization is used similar to the state-of-the-art DDROs [22] and when pn = 2,  $l_2$  norm or quadratic (Q) optimization is used. The characterized delay sensitivities are normalized for tiles and critical paths to remove the physical units of different PVT parameters and to improve the problem condition of the objective by equalizing the value ranges among the different PVT parameters:

$$\nabla d_i^{'(X)}(\mathbf{p}_0) = \frac{\nabla d_i^{(X)}(\mathbf{p}_0)^T \cdot \Delta \mathbf{p}}{d_i^{(X)}(\mathbf{p}_0)}$$

$$\nabla d_{CP}^{'}(\mathbf{p}_0) = \frac{\nabla d_{CP}(\mathbf{p}_0)^T \cdot \Delta \mathbf{p}}{d_{CP}(\mathbf{p}_0)}$$

(3.6)

For the synthesis of DDROs, delays are analyzed at various PVT corners to evaluate the worst case timing of digital circuits. Digital circuits mostly include process corners namely nominal (NOM), fast (FAST) and slow (SLOW). The synthesized DDROs should consider the sensitivities of the target critical paths at all the timing corners. Sec. 3.2.1 describes the method that is used to include multiple PVT corners.

## 3.2.1 Delay Sensitivity Matching at Multiple PVT Corners

The synthesized DDROs by the method of delay-sensitivity matching are to be tracked across various conditions of PVT. Therefore, the delay sensitivities of tiles and critical paths across PVT conditions are collected together in a vector for the delay-sensitivity matching:

$$\nabla d_{CP}(\mathbf{p}_{PVT}) = \begin{bmatrix} \nabla d_{CP}(\mathbf{p}_{PVT_1}) \\ \nabla d_{CP}(\mathbf{p}_{PVT_2}) \\ \dots \\ \nabla d_{CP}(\mathbf{p}_{PVT_{n_{PVT}}}) \end{bmatrix}$$

(3.7)

#### 3 Design-Dependent Timing Monitors

$$\nabla d_i^{(X)}(\mathbf{p}_{PVT}) = \begin{bmatrix} \nabla d_i^{(X)}(\mathbf{p}_{PVT_1}) \\ \nabla d_i^{(X)}(\mathbf{p}_{PVT_1}) \\ \cdots \\ \nabla d_i^{(X)}(\mathbf{p}_{PVT_{n_{PVT}}}) \end{bmatrix}$$

(3.8)

where  $\{PVT_1, PVT_2, \ldots, PVT_{n_{PVT}}\}$  are the various PVT conditions and  $n_{PVT}$  is the number of PVT corners. The conventional method to characterize delay sensitivities using analog SPICE simulation has high computational complexity because it uses transistor models. As mentioned in Sec. 3.2, for sensitivity-based DDRO synthesis, the delay-sensitivities w.r.t. PVT parameters are characterized using central difference method [55]. Thereby, the number of simulations for each timing arch is  $3 \cdot n_p \cdot n_{PVT}$ , where  $n_p$  is the number of PVT parameters. Thus, delay sensitivity characterization using SPICE based timing analysis for thousands of critical paths is not feasible. In addition, the transistor parameters which vary globally and are statistically independent and should be identified for each of the standard cell libraries for every new technology node. Moreover, the major contributing parameters which have high influence on delay are unique for each standard cell library. These parameters have to be ascertained through extensive data analysis of delay sensitivities of tiles or standard cells. In order to avoid extensive data analysis of delay sensitivities and the transistor parameters, a new method to synthesize DDROs is explained in Sec. 3.5 which uses delays instead of delay sensitivities, thus eliminating the computational effort to compute the delay sensitivities.

# 3.3 Characterization of Tile Delay Sensitivities

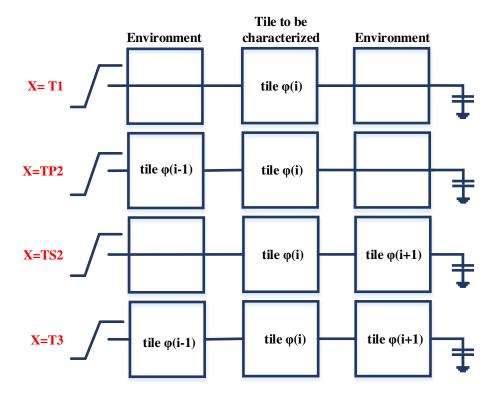

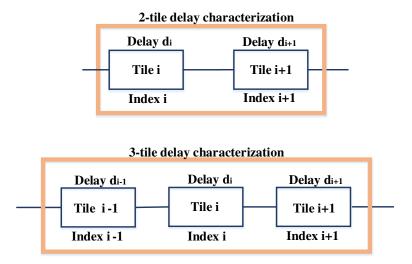

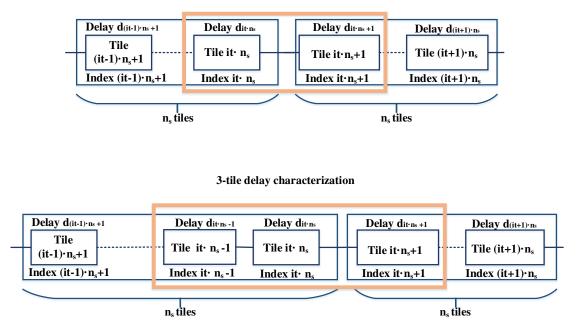

As mentioned before, tiles are used in the synthesis of DDROs where tiles are concatenated set of standard cells. The state-of-the-art method in [22] uses 1-tile delay characterization as explained in 3.3.1. In order to be able to linearly concatenate tile delays, the characterized tile delays need to be highly accurate. Moreover, tile delays and tile delay sensitivities using 1-tile delay characterization are affected by their input slope and output load conditions. Therefore, 1-tile delay characterization does not yield accurate values of delays. Thus, to increase the accuracies of tile delays, three additional methods of characterizing tiles are proposed in Sec. 3.3.2, and Sec. 3.3.3.

# 3.3.1 1-Tile Delay Characterization (T1)

A single combination of input transition time and output load values is used for the 1-tile delay characterization. The delay of the tile  $d_i^{(X)}$  is dependent on PVT parameters **p** and the tile type  $\varphi(i)$ . Moreover, for  $n_{\varphi}$  different tile types, each of the  $n_{\varphi}$  tile types makes  $n_T = n_{\varphi}$  possible tile delays and tile delay sensitivities for a certain tile position *i*. Thus, the number of tile delay characterizations increases linearly, O(N). In Figure 3.5,

Figure 3.5: Tile delay characterization methods

X = T1 represents 1-tile delay characterization with constant values of input transition and output load.

$$d_i^{(T1)}(\mathbf{p}) = d_i^{(T1)}(\varphi(i), \mathbf{p}) \tag{3.9}$$

The combination of input transition time and output load are chosen based on analysis of tile delay behavior. Moreover, the base tiles selected for the synthesis of DDROs could have different drive strength and therefore different input pin capacitances. This could lead to unequal input transition and output load seen by various tiles in a DDRO. Additionally, using ideal constant input transition time and output load is not realistic. This implies that, the characterized tile delays will not reflect the real delays when concatenated to form DDROs. Therefore, more accurate methods of tile characterizations are necessary in order to have a better match of timing behavior of DDROs to their respective target critical paths.

# 3.3.2 2-Tile Delay Characterization (T2)

In a 2-tile characterization, either the influence of the input transition on the tile is considered by adding a preceding tile in the characterization (TP2), or the influence of

#### 3 Design-Dependent Timing Monitors

the output load on the the tile delay is considered by adding a succeeding tile to the characterization (TS2). In Figure 3.5, X = TP2 represents the 2-tile delay characterization with preceding tile and constant value of output load. The delay of the tile  $d_i^{TP2}$  is dependent on PVT parameters **p**, preceding tile type  $\varphi(i-1)$ , and on the tile type  $\varphi(i)$  in the DDRO path. In Figure 3.5, X = TS2 represents the 2-tile delay characterization with constant value of input transition time and a succeeding tile as output load. The delay of the tile  $d_i^{TS2}$  is dependent on PVT parameters **p**, tile type  $\varphi(i)$ , and on the succeeding tile type  $\varphi(i+1)$  in the DDRO path. Moreover, for  $n_{\varphi}$  different tile types, each of the  $n_{\varphi}$  tile types have  $n_{\varphi}$  successor types which makes  $n_T = n_{\varphi}^2$  possible tile delays. Thus, the order of growth of tile delay characterizations increases quadratically,  $O(N^2)$ .

$$d_i^{(TP2)}(\mathbf{p}) = d_i^{(TP2)}(\varphi(i-1), \varphi(i), \mathbf{p})$$

$$d_i^{(TS2)}(\mathbf{p}) = d_i^{(TS2)}(\varphi(i), \varphi(i+1), \mathbf{p})$$

(3.10)

In the cases where tile types seleced in the tile library have different drive strengths, the tiles in a DDRO would experience different output loads. This also leads to different input transition times at the beginning of each tile. Therefore, although the accuracy of 2-tile delay characterization is more than 1-tile delay characterization, 2-tile delay characterization has limitations due to idealistic output loads or input transition times.

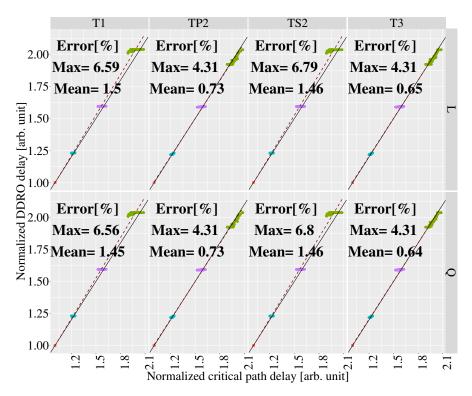

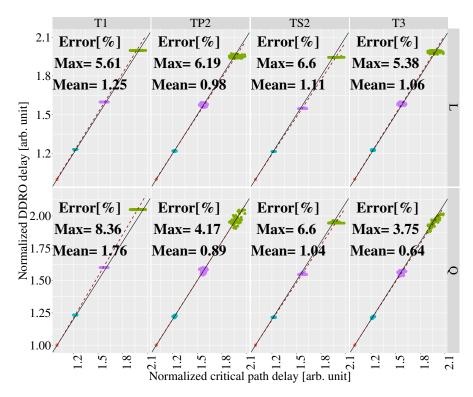

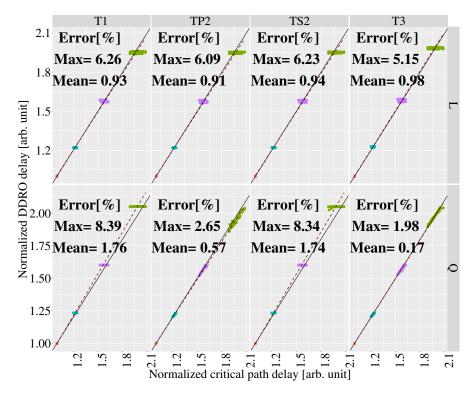

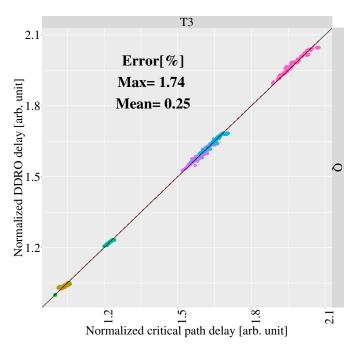

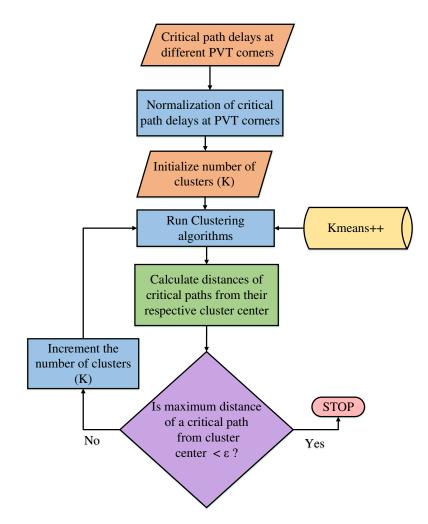

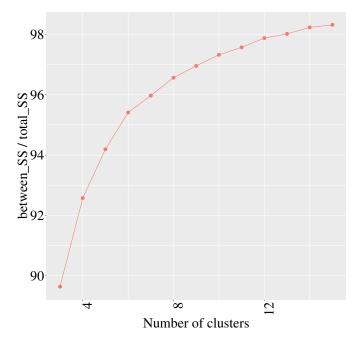

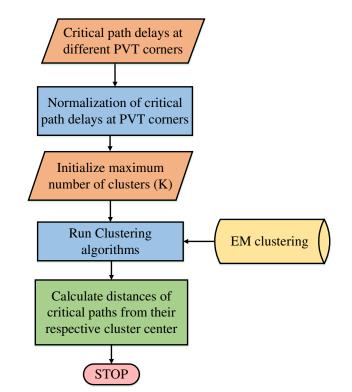

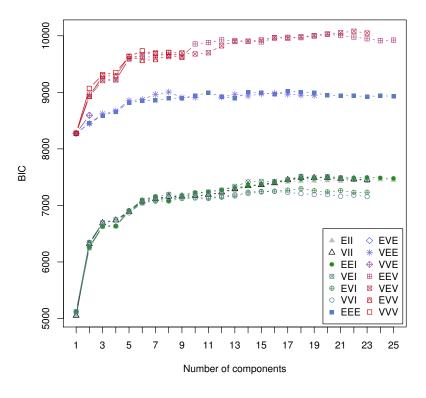

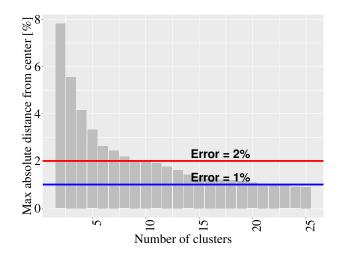

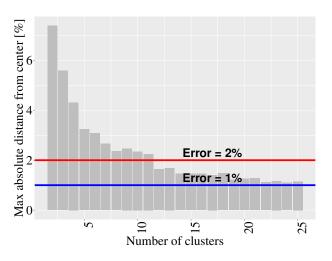

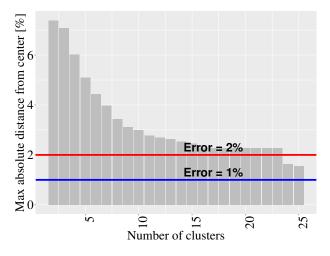

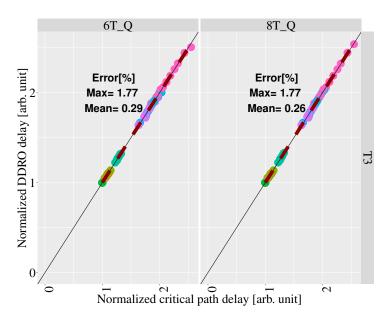

## 3.3.3 3-Tile Delay Characterization (T3)