# Technische Universität München Fakultät für Elektrotechnik und Informationstechnik

# Lehrstuhl für Entwurfsautomatisierung

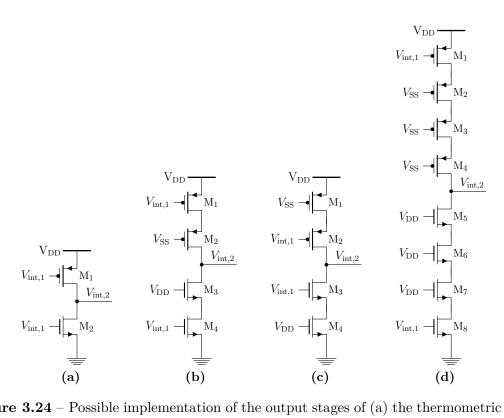

# Development of Analytical Behavioral Models for Digitally Controlled Edge Interpolator (DCEI) based Digital-to-Time Converter (DTC) Circuits

Sebastian Sievert, M.Sc. (TUM)

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines Doktor-Ingenieurs (Dr.-Ing.) genehmigten Dissertation.

| Vorsitzender:            |    | Prof. Dr. Andreas Herkersdorf             |

|--------------------------|----|-------------------------------------------|

| Prüfer der Dissertation: |    |                                           |

|                          | 1. | apl. Prof. DrIng. Helmut Gräb             |

|                          | 2. | Prof. DrIng., DrIng. habil. Robert Weigel |

Die Dissertation wurde am 18.04.2017 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 07.07.2017 angenommen.

## Abstract

Shrinking of CMOS process technology aims at reducing area, power, and cost while increasing the operation frequency of the fabricated circuits. Due to the quadratic dependency of power consumption from voltage, the supply voltage is lowered for smaller technology nodes to save power. For conventional digital-to-analog converters (DAC) the reduced voltage headroom complicates the circuit design. However, time converter circuits as time-to-digital converters (TDC) or digital-to-time converters (DTC) benefit from technology scaling: Faster transistors and lower parasitic capacitances enable a reduced minimum inverter delay, and a finer tuning of RC time constants is enabled through decreasing minimum capacitor sizes.

The present thesis concentrates on the investigation of DTCs, which got increasing attention from academical and industrial research in the past decade. These circuit types belong to the class of DACs, where the analog domain is time. DTCs apply a time delay, controlled by a digital code word, on a reference input clock, allowing a dynamic modulation of the DTC output signal's period and thus frequency. This concept enables various applications in the areas of frequency synthesis and wireline/wireless transmitters and receivers. Similar to conventional DACs, important performance characteristics include the full scale delay, resolution, nonlinearity, and monotonicity, but also power consumption and jitter or phase noise.

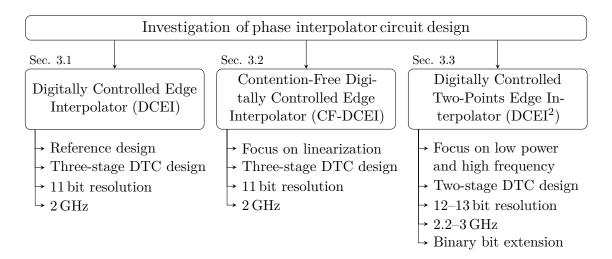

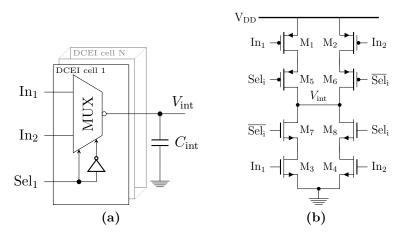

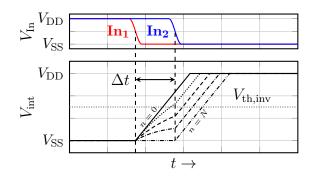

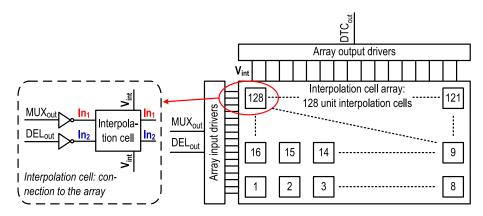

DTCs that target high time resolution are usually segmented into a multi-stage architecture with subsequent coarse and fine delay tuning stages. Recent literature discussed several architectures for coarse and fine tuning, including phase interpolator (PI) circuits for fine delay tuning. While PIs have the advantage of a well-defined tuning range, designs presented so far lack high linearity and show only resolutions of up to 5 bit. The primary focus of the present thesis is the design, modeling, and verification of PI based DTCs. The investigated PIs are implemented as digitally controlled edge interpolators (DCEI), belonging to PI types that operate on digital rail-to-rail signals. Their architecture is based exclusively on digital circuit elements, enabling to leverage technology scaling even further.

Based on an existing 2 GHz three-stage DTC design with 11 bit resolution (7 bit provided by the PI fine tuning stage), PIs' nonlinearity sources are elaborately analyzed with an analytical circuit model to confirm and quantify different sources of nonlinearity discussed in the literature so far. As the major source of nonlinearity are shoot-through currents during the phase interpolation, it is imperative for a high linearity design to suppress them. Linear PI designs published to date implement this and allow up to 5 bit resolution, however, they have several architectural drawbacks, including the limitation that the digital code is only applied on the rising output edge while the falling edge needs to be used for resetting the PI. The present thesis presents a linearized 7 bit PI that prevents shoot-through currents with additional control logic. The linearized PI enables interpolation on rising and falling edges through implementation of retention cells, that are complementary to the interpolation cells and render the PI reset unnecessary. While this linearization concept can lead to ideally perfect linearity, its main drawback is the increased power consumption due to the additional control logic. Therefore, a second novel PI architecture is developed in this thesis. A two-points PI exhibits two subsequent coarse and fine interpolations to double the full-scale interpolation range compared to the reference PI. This allows to reduce the reference three-stage DTC design to two stages, decreasing the power consumption and simplifying the overall DTC design. While it is usually no issue to double a given PI's interpolation range at the cost of a severely degraded linearity, the key innovation of the two-points PI is the prevention of the linearity degradation. The newly developed interpolation cells implement a k bit interpolation with a cell array of only  $2^{k-1}$  instead of  $2^k$  cells, with a minimum increase in the single interpolation cell's area compared to the reference PI. In order to thermometrically and binary controlled parts, is presented. It differs in several aspects from conventional hybrid DAC implementations and is a key design aspect for low power designs with enhanced resolution.

DTC discussions in the literature primarily focus on performances such as static nonlinearity, resolution, operation frequency, or power consumption. However, dynamic effects that are triggered by DTC code activity lead to dynamic errors, which are visible as additional dynamic nonlinearity. Depending on the code activity and targeted linearity, they can have a non-negligible impact on the DTC application. The mechanisms leading to dynamic effects are analyzed in detail, identifying supply regulators with finite regulation bandwidth as major contributor. Therefore, a dynamic effects compensation circuit is developed that aims at mitigating dynamic errors at supply regulator level.

Circuit designs for the present thesis resulted in three test chips that were fabricated in 28 nm standard CMOS technology. The developed DTCs operate in a frequency range of 2–3 GHz and provide resolutions of up to 13 bit (up to 10 bit provided by the PI), equivalent to a time resolution of 48 fs for 2.5 GHz operation frequency. Test chip verification shows excellent matching between circuit simulations, analytical circuit models, and test chip measurements of the static DTC nonlinearity. Furthermore, the implemented dynamic effects compensation is validated to be functional, even if a detailed verification is limited by the instrument noise, which is in the same order of magnitude as the targeted DTC resolution.

# Contents

| $\mathbf{Li}$ | st of | Abbreviations                                                                                                           | vii        |

|---------------|-------|-------------------------------------------------------------------------------------------------------------------------|------------|

| Li            | st of | Symbols                                                                                                                 | xi         |

| 1             | Intr  | oduction                                                                                                                | 1          |

|               | 1.1   | DTC Architectures and Circuit Design                                                                                    | 2          |

|               |       | 1.1.1 Coarse Tuning Architectures                                                                                       | 2          |

|               |       | 1.1.2 Fine Tuning Architectures                                                                                         | 4          |

|               | 1.2   | DTC Applications                                                                                                        | 5          |

|               |       | 1.2.1 Direct Digital Period Synthesis                                                                                   | 6          |

|               |       | 1.2.2 Clock and Data Recovery Circuits (CDR)                                                                            | 7          |

|               |       | 1.2.3 DTC Assisted TDCs                                                                                                 | 9          |

|               |       | 1.2.4 Fractional-N Sub-Sampling PLLs (SSPLL) and Multiplying DLLs (MDLL)                                                | 10         |

|               |       | 1.2.5 Polar and Outphasing Transmitters                                                                                 | 12         |

|               | 1.3   | Motivation and Objectives                                                                                               | $12 \\ 13$ |

|               | 1.0   |                                                                                                                         | 10         |

| <b>2</b>      |       | C Architecture and Characterization                                                                                     | 15         |

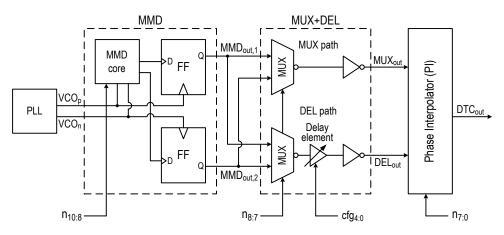

|               | 2.1   | Investigated Multistage DTC Architecture                                                                                | 15         |

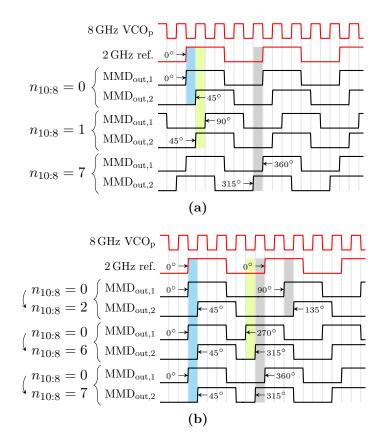

|               |       | 2.1.1 Multi-Modulus Divider                                                                                             | 16         |

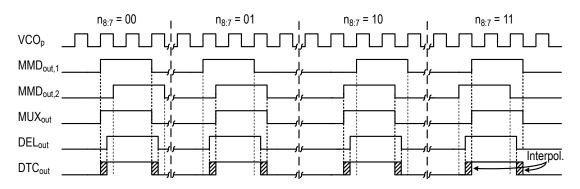

|               |       | 2.1.2 Multiplexer and Delay Element                                                                                     | 18         |

|               |       | 2.1.3 Phase Interpolator                                                                                                | 19         |

|               |       | 2.1.4 Digital Data Path                                                                                                 | 20         |

|               | 2.2   | DTC Performance Characteristics                                                                                         | 20         |

|               | 2.3   | Summary                                                                                                                 | 23         |

| 3             | Pha   | se Interpolator Design and Modeling                                                                                     | <b>25</b>  |

|               | 3.1   | Digitally Controlled Edge Interpolator                                                                                  | 26         |

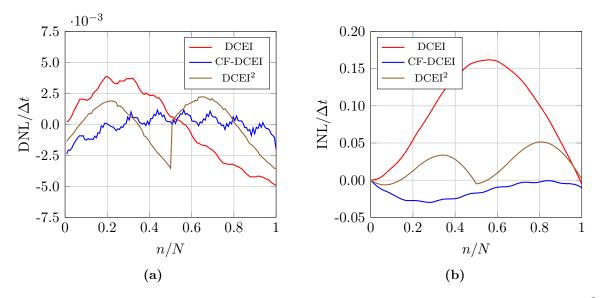

|               |       | 3.1.1 DCEI Model                                                                                                        | 28         |

|               | 3.2   | Contention-Free Digitally Controlled Edge Interpolator                                                                  | 32         |

|               |       | 3.2.1 Design and Implementation                                                                                         | 34         |

|               |       | 3.2.2 CF-DCEI Model                                                                                                     | 37         |

|               | 3.3   | Digitally Controlled Two-Points Edge Interpolator                                                                       | 42         |

|               |       | 3.3.1 Design and Implementation                                                                                         | 43         |

|               |       | 3.3.2 DCEI <sup>2</sup> Model $\ldots$ | 48         |

|               | 3.4   | Binary Bit Resolution Enhancement                                                                                       | 50         |

|               |       | 3.4.1 Architecture of a Binary Extended Cell Array                                                                      | 51         |

|               |       | 3.4.2 Binary Unit Cell Implementation                                                                                   | 53         |

|               | 3.5   | Summary and Conclusion                                                                                                  | 55         |

| <b>4</b>      | Dyr               | namic Effects in DTCs                                                                                                                                                    | <b>59</b>        |

|---------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

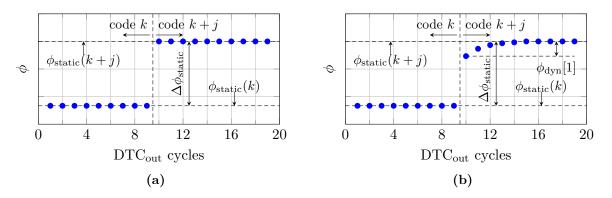

|               | 4.1               | Definition of Dynamic Errors and Dynamic INL                                                                                                                             | 59               |

|               | 4.2               | Root Causes of Dynamic Errors                                                                                                                                            | 60               |

|               |                   | 4.2.1 Code-Dependent Current Consumption                                                                                                                                 | 62               |

|               |                   | 4.2.2 Instantaneous Change of Average Current                                                                                                                            | 63               |

|               |                   | 4.2.3 Logic Current Consumption                                                                                                                                          | 65               |

|               |                   | 4.2.4 Digital Control Signal Timing                                                                                                                                      | 65               |

|               |                   | 4.2.5 Digital Control Signal Coupling                                                                                                                                    | 67               |

|               | 4.3               | Dynamic Error Simulation                                                                                                                                                 | 67               |

|               | 4.4               | Compensation for Load Current Variations at Supply Regulator Level                                                                                                       | 70               |

|               |                   | 4.4.1 DCEI <sup>2</sup> Compensation                                                                                                                                     | 71               |

|               |                   | 4.4.2 MMD Compensation                                                                                                                                                   | 73               |

|               |                   | 4.4.3 Compensation Impact on Dynamic Effects                                                                                                                             | 75               |

|               | 4.5               | Summary and Conclusion                                                                                                                                                   | 76               |

| <b>5</b>      | ЪΤ                | C Measurements                                                                                                                                                           | 79               |

| 9             | <b>D</b> 1<br>5.1 | Measurement Setup                                                                                                                                                        | 79<br>79         |

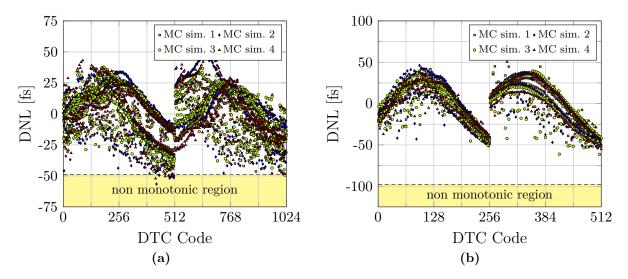

|               | $5.1 \\ 5.2$      | Quasi-Static CF-DCEI Nonlinearity                                                                                                                                        | 19<br>80         |

|               | $5.2 \\ 5.3$      | Quasi-Static $DCEI^2$ Nonlinearity $\dots \dots \dots$                   | 82               |

|               | 0.0               | 5.3.1 INL Tuning                                                                                                                                                         | 84               |

|               |                   | 5.3.2 Binary Bit Implementation                                                                                                                                          | 85               |

|               | 5.4               | Dynamic DTC Performance                                                                                                                                                  | 86               |

|               | 0.1               | 5.4.1 DCEI <sup>2</sup> Dynamic Effects Compensation $\dots \dots \dots$ | 89               |

|               |                   | 5.4.2 MMD Dynamic Effects Compensation                                                                                                                                   | 90               |

|               |                   | 5.4.3 Dynamic Error Measurement Limitations                                                                                                                              | 92               |

|               | 5.5               | Summary and Conclusion                                                                                                                                                   | 92               |

| 6             | Cor               | nclusion and Outlook                                                                                                                                                     | 95               |

| Λ,            | nnon              | dices                                                                                                                                                                    | 99               |

| $\mathbf{n}$  | А                 |                                                                                                                                                                          | <b>33</b><br>101 |

|               |                   | CF-DCEI Nonlinearity Model                                                                                                                                               |                  |

|               | C                 | Switched Capacitor Fine Tuning Nonlinearity Model                                                                                                                        |                  |

| т.            |                   |                                                                                                                                                                          |                  |

| Lı            | st of             | Figures                                                                                                                                                                  | 119              |

| Li            | st of             | Tables                                                                                                                                                                   | 123              |

| $\mathbf{Li}$ | st of             | References                                                                                                                                                               | 125              |

| $\mathbf{Li}$ | st of             | Author Publications                                                                                                                                                      | 135              |

| A             | cknov             | wledgments                                                                                                                                                               | 137              |

# List of Abbreviations

| ADC               | Analog-to-digital converter                            |

|-------------------|--------------------------------------------------------|

| ADPLL             | All-digital phase-locked loop                          |

| BBPD              | Bang-bang phase detector                               |

| CDR               | Clock and data recovery                                |

| CF-DCEI           | Contention-free digitally controlled edge interpolator |

| CMOS              | Complementary metal-oxide-semiconductor                |

| CORDIC            | COordinate Rotation DIgital Computer                   |

| CP                | Charge pump                                            |

| DAC               | Digital-to-analog converter                            |

| DC                | Direct current                                         |

| DCDL              | Digitally controlled delay line                        |

| DCEI              | Digitally controlled edge interpolator                 |

| DCEI <sup>2</sup> | Digitally controlled two-points edge interpolator      |

| DCO               | Digitally controlled oscillator                        |

| DDPS              | Direct digital period synthesis                        |

| DEL               | Delay element                                          |

| DFF               | D flip-flop                                            |

| DLL               | Delay-locked loop                                      |

| DNL               | Differential nonlinearity                              |

| DPC               | Digital-to-phase converter                             |

| DPS               | Digital period synthesis                               |

| DTC               | Digital-to-time converter                              |

| FCW               | Frequency control word                                 |

|                   |                                                        |

| FLL            | Frequency-locked loop                             |

|----------------|---------------------------------------------------|

|                |                                                   |

| $\mathbf{FS}$  | Full scale                                        |

| $\mathbf{FSR}$ | Full scale range                                  |

| IC             | Integrated circuit                                |

| I-DAC          | Current-steering digital-to-analog converter      |

| INL            | Integral nonlinearity                             |

| INTC           | Interpolation cell                                |

| ISSCC          | International Solid-State Circuits Conference     |

| LDO            | Low drop-out voltage regulator                    |

| $\mathbf{LF}$  | Loop filter                                       |

| LO             | Local oscillator                                  |

| $\mathbf{LSB}$ | Least significant bit                             |

| $\mathbf{LUT}$ | Look-up table                                     |

| MC             | Monte Carlo                                       |

| MDLL           | Multiplying delay-locked loop                     |

| MMD            | Multi-modulus divider                             |

| MOSFET         | Metal–oxide–semiconductor field-effect transistor |

| MSB            | Most significant bit                              |

| MUX            | Multiplexer                                       |

| NMOS           | N-channel MOSFET                                  |

| ODE            | Ordinary differential equation                    |

| PA             | Power amplifier                                   |

| PCR            | Periodic code ramp                                |

| PD             | Phase detector                                    |

| PI             | Phase interpolator                                |

| PLL            | Phase-locked loop                                 |

| PMOS           | P-channel MOSFET                                  |

| PSD            | Power spectral density                            |

| $\mathbf{PVT}$       | Process, voltage, and temperature variations |

|----------------------|----------------------------------------------|

| QVCO                 | Quadrature voltage controlled oscillator     |

| RETC                 | Retention cell                               |

| $\mathbf{RF}$        | Radio frequency                              |

| RPM                  | Random phase modulation                      |

| RX                   | Receiver                                     |

| SCCS                 | Short-circuit-current-suppression            |

| $\mathbf{SDR}$       | Software-defined radio                       |

| SoC                  | System on a chip                             |

| SRAM                 | Static random-access memory                  |

| SSB                  | Single-sideband                              |

| SSPD                 | Sub-sampling phase detector                  |

| $\mathbf{SSPLL}$     | Sub-sampling phase-locked loop               |

| TDC                  | Time-to-digital converter                    |

| $\operatorname{TDL}$ | Tapped delay line                            |

| $\mathbf{TF}$        | Transfer function                            |

| ТХ                   | Transmitter                                  |

| VCDL                 | Voltage controlled delay line                |

| VCO                  | Voltage controlled oscillator                |

# List of Symbols

| $\alpha$                  | Normalized DTC code                                                               |

|---------------------------|-----------------------------------------------------------------------------------|

| $\Delta \phi_{ m static}$ | DTC output phase difference due to code change                                    |

| $\lambda$                 | Channel length modulation factor in Shichman-Hodges transistor model              |

| $\mu_{ m n,p}$            | Electron mobility in n/p doped silicon                                            |

| $\phi$                    | DTC output phase                                                                  |

| $\phi_{ m dyn}$           | DTC output phase related to dynamic nonlinearity                                  |

| $\phi_{ m in}$            | Input signal's phase in a phase filtering DLL                                     |

| $\phi_{ m out}$           | Output signal's phase in a phase filtering DLL                                    |

| $\phi_{ m pd}$            | Phase shift related to propagation delay $t_{\rm pd}$                             |

| $\phi_{ m ref}$           | Reference signal's phase in a phase filering DLL                                  |

| $\phi_{ m static}$        | DTC output phase related to static nonlinearity                                   |

| $	au_{ m int}$            | RC time constant at interpolation node $V_{\rm int}$                              |

| heta                      | Phase shift between $S_{1/2}$ in an outphasing transmitter                        |

| $\Delta \phi$             | Phase enclosed between $In_{1/2}$ of a phase interpolator input                   |

| b                         | Control word for binary interpolation cells                                       |

| $d_{ m acc}$              | Accumulated frequency control word                                                |

| $\Delta i_{(k,k+j)}$      | DTC current deviation from $i_{\rm nom}$ for code change $n=k\rightarrow k+j$     |

| $\Delta t$                | Time spacing between the rising edges of the two phase interpolator input signals |

| $\Delta t_1$              | Interpolation range of the DCEI <sup>2</sup> 's first interpolation               |

| $\Delta t_{2,1/2}$        | Interpolation range of the DCEI <sup>2</sup> 's second interpolation              |

| $\Delta t_{\rm c}$        | Coarse tuning time resolution                                                     |

| $\Delta t_{\rm uc}$       | Ultra coarse tuning time resolution                                               |

| $d_{\rm sel}$             | MUX control signals in DDPS applications                                          |

| $f_{ m clk,MMD}$       | Clock signal generated by the MMD                                   |

|------------------------|---------------------------------------------------------------------|

| $f_{\rm clk,MUX+DEL}$  | Clock signal generated by the MUX+DEL                               |

| $f_{ m clk,PI}$        | Clock signal generated by the phase interpolator                    |

| $f_{ m nom}$           | Nominal DTC output frequency                                        |

| $f_{ m offset}$        | Frequency offset at DTC output due to programming                   |

| $f_{ m out}$           | DTC output frequency                                                |

| $f_{ m ref}$           | DTC reference frequency                                             |

| $i_{\rm base}$         | Constant static $DCEI^2$ current consumption                        |

| $i_{ m bias}$          | LDO bias current                                                    |

| $i_{ m clk}$           | Digital DTC current due to clocking                                 |

| $i_{ m comp}$          | LDO compensation current                                            |

| $i_{ m dig}$           | Total digital DTC current                                           |

| $I_{\mathrm{D,n/p}}$   | Drain current of n- and p-type MOS transistor                       |

| $i_{\mathrm{int},1}$   | Static $DCEI^2$ current consumption due to the first interpolation  |

| $i_{\mathrm{int},2}$   | Static $DCEI^2$ current consumption due to the second interpolation |

| $i_{ m load}$          | Load current the DTC imposes on the LDO                             |

| $i_{ m logic}$         | Digital DTC current due to logic circuitry                          |

| $i_{ m nom}$           | Total DTC current                                                   |

| $i_{ m nom,0}$         | DTC current not influenced by code changes                          |

| $i_{\rm nom, coarse}$  | DTC current of all blocks processing the coarse tuned signal        |

| $i_{\rm nom, fine}$    | DTC current of all blocks processing the fine tuned signal          |

| $i_{ m static,DCEI^2}$ | Total static $DCEI^2$ current consumption                           |

| $j_{ m coarse}$        | DTC code change in coarse tuning stage                              |

| $k_{\rm bin}$          | Phase interpolator resolution of binary controlled cells in bit     |

| $k_{\rm coarse}$       | DTC coarse tuning number of bits                                    |

| $k_{ m DTC}$           | DTC number of bits                                                  |

| $k_{ m fine}$          | DTC fine tuning number of bits                                      |

| $k_{ m MMD}$           | MMD number of bits                                                  |

|                        |                                                                     |

| $k_{\rm MUX+DEL}$                  | MUX+DEL number of bits                                                                                                   |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| $k_{\mathrm{PI}}$                  | Phase interpolator number of bits                                                                                        |

| $k_{\mathrm{therm}}$               | Phase interpolator resolution of thermometrically controlled array in bit                                                |

| $k_{\mathrm{total}}$               | Total phase interpolator resolution in bit                                                                               |

| n                                  | DTC code word                                                                                                            |

| $n_{\rm cycle}$                    | DTC output cycle number after code change                                                                                |

| $n_{ m dyn, err}$                  | Code sequence for dynamic error DTC tests                                                                                |

| $n_{ m mod}$                       | Code sequency for modulation dynamic error DTC tests                                                                     |

| $n_{\mathrm{ramp}}$                | Code sequency for frequency synthesis dynamic error DTC tests                                                            |

| $t_{\rm cross}$                    | Signal's crossing time of threshold voltage $V_{\rm th,inv}$                                                             |

| $t_{ m d}$                         | DTC output delay                                                                                                         |

| $t_{ m d,DEL}$                     | Propagation delay of DEL path in MUX+DEL stage                                                                           |

| $t_{ m d,inv}$                     | Propagation delay of inverter                                                                                            |

| $t_{\rm d,LSB}$                    | DTC time resolution                                                                                                      |

| $t_{\rm d,LSB,coarse}$             | DTC coarse tuning time resolution                                                                                        |

| $t_{\rm d,MUX}$                    | Propagation delay of MUX path in MUX+DEL stage                                                                           |

| $t_{ m d,therm}$                   | Delay for step between two neighboring thermometrically controlled DCEI cells                                            |

| $t_{ m int}$                       | Rise time for $V_{\rm int}: 0 \to V_{\rm th,inv}$                                                                        |

| $t_{ m int,0}$                     | Minimum rise time at $V_{\rm int}$                                                                                       |

| $t_{\mathrm{int},0,\lambda  eq 0}$ | Minimum rise time at $V_{\text{int}}$ for $\lambda \neq 0$                                                               |

| $t_{ m int,1,0}^{ m sc}$           | Minimum of $t_{\text{int},1}^{\text{sc}}$ due to programming                                                             |

| $t_{ m int,1}^{ m sc}$             | Delay until $V_{\rm out}^{\rm sc}$ starts to switch in the switched capacitor based fine tuning                          |

| $t_{ m int,2,0}^{ m sc}$           | Minimum of $t_{int,2}^{sc}$ due to programming                                                                           |

| $t_{ m int,2}^{ m sc}$             | Relevant fall time at $t_{\rm int,1}^{\rm sc}$ that influences the linearity of the switched capacitor based fine tuning |

| $t_{ m inv,min}$                   | Minimum inverter delay of a given technology                                                                             |

| $t_{ m out,0}^{ m sc}$             | Minimum rise time at $V_{\rm out}^{\rm sc}$                                                                              |

| $t_{ m out}^{ m sc}$           | Rise time at $V_{\rm out}^{\rm sc}$                                             |

|--------------------------------|---------------------------------------------------------------------------------|

| $t_{ m pd}$                    | Propagation delay                                                               |

| $t_{ m r,f}$                   | Rise/fall time of a rail-to-rail signal                                         |

| $B_{1/2}$                      | Binary controlled 50% DCEI <sup>2</sup> interpolation cell                      |

| $B_{1/4}$                      | Binary controlled $25\%$ DCEI <sup>2</sup> interpolation cell                   |

| $\mathbf{B}_x$                 | Binary controlled $DCEI^2$ interpolation cell                                   |

| C                              | Capacitance                                                                     |

| $C_{\mathrm{C},3}$             | MMD division-by-3 compensation capacitance                                      |

| $C_{\mathrm{C},5}$             | MMD division-by-5 compensation capacitance                                      |

| $C_{\rm C,LSB}$                | MMD LSB compensation capacitance                                                |

| $C_{ m int}$                   | Capacitance of phase interpolator's interpolation node $V_{\rm int}$            |

| $C_{\mathrm{load}}$            | Decoupling capacitor of LDO supply regulator                                    |

| $C_{\max}$                     | Maximum value for $C_{\text{tune}}$ in the switched capacitor based fine tuning |

| $C_{\min}$                     | Minimum value for $C_{\text{tune}}$ in the switched capacitor based fine tuning |

| $C_{ m ox}$                    | MOSFET gate oxide capacitance                                                   |

| $C_{\mathrm{PG}}$              | Gate capacitance of LDO pass-gate transistor                                    |

| $C_{\mathrm{tune}}$            | Tuning capacitance of the switched capacitor based fine tuning                  |

| $\mathrm{DEL}_{\mathrm{out}}$  | Delay element path output of MUX+DEL stage                                      |

| $\Delta T_{1/2}$               | Clock signal skew in source synchronous CDR circuits                            |

| $\Delta V_{\mathrm{PG,div-3}}$ | Voltage spike on $V_{\rm PG}$ due to MMD division-by-3 compensation             |

| $\Delta V_{\mathrm{PG,div-5}}$ | Voltage spike on $V_{\rm PG}$ due to MMD division-by-5 compensation             |

| $\Delta V_{\rm PG,LSB}$        | Voltage spike on $V_{\rm PG}$ due to MMD LSB compensation                       |

| $I_1$                          | Initial current of current integrating phase interpolators                      |

| $I_{\mathrm{D,off}}$           | Drain current in cut-off region                                                 |

| $I_{\mathrm{D,sat,0}}$         | Drain current in saturation region for $\lambda = 0$                            |

| $I_{\max}$                     | Maximum current of current integrating phase interpolators                      |

| $In_{1/2}$                     | Input signals of DTC fine tuning stages                                         |

| $\mathrm{INL}_{\mathrm{dyn}}$  | Dynamic INL                                                                     |

|                                |                                                                                 |

| $\overline{\mathrm{INL}_{\mathrm{dyn}}}$                    | Average dynamic INL for each DTC code                                                  |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------|

| $\sigma\left(\mathrm{INL}_{\mathrm{dyn}} ight)$             | Standard deviation of $INL_{dyn}$ for each code                                        |

| $\overline{\sigma\left(\mathrm{INL}_{\mathrm{dyn}}\right)}$ | Average of $\sigma$ (INL <sub>dyn</sub> ) over all DTC codes                           |

| $\mathrm{INL}_{\mathrm{int},1/2}$                           | $DCEI^2$ INL of first/second interpolation                                             |

| $\mathrm{INL}_{\mathrm{max}}$                               | Positive or negative peak value of $INL[n]$                                            |

| $\mathrm{INL}_{\mathrm{max}}^{\mathrm{sc}}$                 | Positive or negative peak INL of switched capacitor based fine tuning                  |

| $K_{\mathrm{n,p}}$                                          | $\mu_{ m n,p}C_{ m ox}$                                                                |

| $L_{\rm eff}$                                               | Effective transistor length                                                            |

| $\mathcal{L}(f)$                                            | Phase noise at frequency $f$                                                           |

| M                                                           | Relevant DTC code history depth for dynamic effects                                    |

| $\mathrm{MMD}_{\mathrm{out},1/2}$                           | MMD output signals                                                                     |

| $\mathrm{MUX}_{\mathrm{out}}$                               | Multiplexer path output of MUX+DEL stage                                               |

| N                                                           | Maximum DAC code, e.g. for DTCs or PIs                                                 |

| $P_{\rm LO}(f_{\rm LO})$                                    | Power of output carrier signal with frequency $f_{\rm LO}$                             |

| $P_{\rm noise}(f)$                                          | Power of noise floor at frequency $f$                                                  |

| $P_{\rm nom}$                                               | Nominal output signal power                                                            |

| R                                                           | Resistance                                                                             |

| $R_{1-4}$                                                   | Logic control signals of the CF-DCEI's retention cells                                 |

| $S_{1-4}$                                                   | Logic control signals of the $\rm DCEI^2/\rm CF\text{-}D\rm CEI's$ interpolation cells |

| $\operatorname{Sel}_{\mathrm{i}}$                           | Select signal of $i^{\text{th}}$ phase interpolator unit cell                          |

| $\operatorname{Sel}_{i,1/2}$                                | Select signals of $i^{\text{th}}$ DCEI <sup>2</sup> interpolation cell                 |

| $\overline{S_{1-2}}$                                        | Inverted logic control signals of the $\text{DCEI}^2$ 's interpolation cells           |

| $S_{\tau}(f)$                                               | Jitter power spectral density at frequency $f$                                         |

| $S_{\tau,s}(f)$                                             | Spectral density of jitter at frequency $f$                                            |

| T                                                           | Period of a signal                                                                     |

| $T_{\rm acc}$                                               | Clock to output delay of accumulator in DDPS applications                              |

| $T_{cell}$                                                  | Thermometrically controlled $\text{DCEI}^2$ interpolation cell                         |

| $T_{(k,k+j)}$                                               | Period for DTC code change $n = k \rightarrow k + j$                                   |

|                                                             |                                                                                        |

| $T_{ m nom}$                  | Nominal period                                            |

|-------------------------------|-----------------------------------------------------------|

| $T_{\mathrm{out}}$            | Period of DTC output signal                               |

| $T_{\rm ramp}$                | Period of DTC ramp generator                              |

| $T_{\rm trigger}$             | Period of DTC trigger signal for external measurements    |

| $T_{\rm VCO}$                 | Period of VCO output signal                               |

| V                             | Voltage                                                   |

| $V_{\mathrm{C},3}$            | MMD division-by-3 compensation voltage                    |

| $V_{\mathrm{C},5}$            | MMD division-by-5 compensation voltage                    |

| $V_{ m casc}$                 | LDO slow-loop output voltage                              |

| $V_{\rm C,LSB}$               | MMD LSB compensation control voltage                      |

| $V_{\rm DD}$                  | Supply voltage                                            |

| $V_{\rm DD,ext}$              | External supply voltage                                   |

| $V_{\rm DS}$                  | Drain-source voltage                                      |

| $V_{ m GS}$                   | Gate-source voltage                                       |

| $V_{ m int}$                  | Voltage at interpolation node of DTC fine tuning circuits |

| $V_{ m int,1}$                | First interpolation node of $DCEI^2$                      |

| $V_{ m int,2}$                | Second interpolation node of $\text{DCEI}^2$              |

| $V_{\rm int}^{\rm sc}$        | Tunable net of switched capacitor based fine tuning       |

| $V_{ m out}$                  | LDO output voltage                                        |

| $V_{ m out}^{ m sc}$          | Output net of switched capacitor based fine tuning        |

| $V_{\mathrm{PG}}$             | Voltage at LDO pass-gate transistor gate                  |

| $V_{\mathrm{ref}}$            | Bandgap reference voltage                                 |

| $V_{\rm SS}$                  | On-chip ground potential                                  |

| $V_{ m sup}$                  | DTC supply voltage                                        |

| $V_{ m th,inv}$               | Threshold voltage of CMOS inverter                        |

| $V_{ m tune}$                 | Tuning voltage of DLL                                     |

| $\mathrm{VCO}_{\mathrm{p/n}}$ | Differential VCO output signals                           |

| $W_{\rm eff}$                 | Effective transistor width                                |

- ${\rm Z}_{1/2}$  Complex outphasing signals of an outphasing transmitter

- $\rm Z_{out}$  Complex output signal of an outphasing transmitter

# 1 Introduction

Several system architectures in modern system on a chip (SoC) integrated circuits (IC) require circuit blocks for frequency synthesis or modulation, such as for generation of digital clock signals or for wireline/wireless communication systems. As modern process technologies favor digital circuits, systems are preferably implemented digitally and signals move from the analog to the digital domain wherever possible. Therefore, it would be desirable to implement fully digital circuits for the generation of arbitrary digital signals, i.e., clock signals of constant frequency or modulated signals. A circuit that allows the generation of such signals, while providing the possibility of a fully digital implementation, is the digital-to-time converter (DTC). DTCs, also called digital-to-phase converters (DPC) or phase rotators, apply a time delay  $t_d$  (equivalent to a phase shift  $\phi$ ) on a reference signal, based on a digital input code. As their output is usually a periodic clock signal, phase shift corresponds to time delay according to the output signal's period  $T_{out}$ :

$$\frac{\phi}{2\pi} = \frac{t_{\rm d}}{T_{\rm out}}.\tag{1.1}$$

Due to the scaling of CMOS process technology, the supply voltage is lowered to reduce power dissipation. This results in loss of dynamic range for conventional analog-to-digital converters (ADC) and digital-to-analog converters (DAC). However, transistors also get faster, allowing time processing circuits as time-to-digital converters (TDC) or DTCs to increase their time resolution and therefore benefit from process scaling.

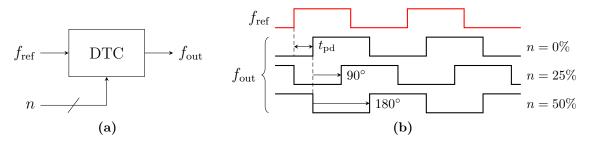

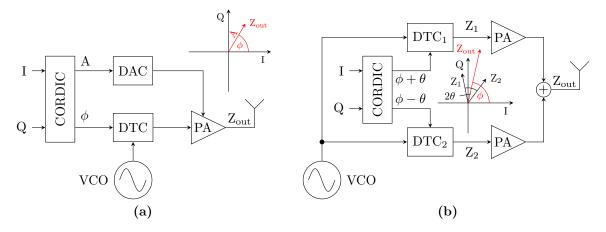

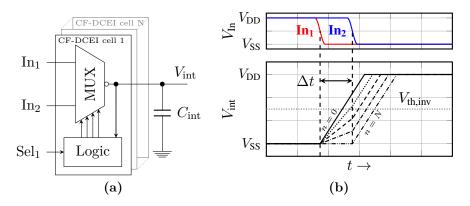

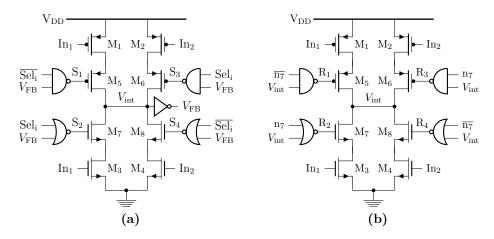

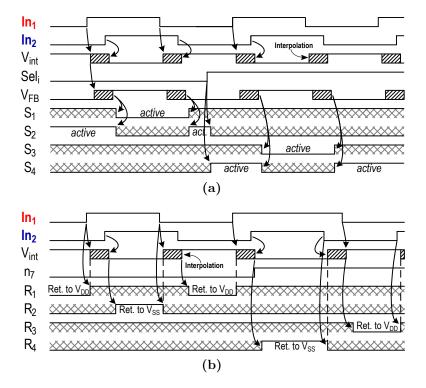

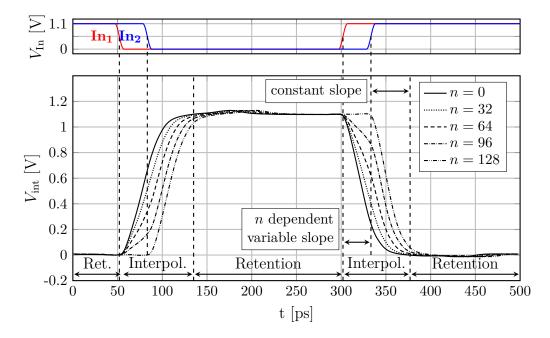

DTCs belong to the class of DACs, where the analog domain is time or phase. In most applications they operate on a rectangular input reference clock signal  $f_{\rm ref}$  and produce a rectangular output clock signal  $f_{\rm out}$ . Fig. 1.1(a) shows an overview of the DTC block. The digital code *n* controls the time delay (or the phase shift) of the output signal, while the relation between  $f_{\rm ref}$  and  $f_{\rm out}$  is determined by the DTC circuit architecture and its programming. Fig. 1.1(b) plots the relation between input and output waveforms exemplary for the case of  $f_{\rm out} = f_{\rm ref}$ , static DTC code *n*, and an output phase range of

**Figure 1.1** – Basic DTC operation: (a) top level overview on the DTC, and (b) example for relation between input reference signal and DTC output signal.

$0 - 2\pi$  for a code range of 0 - 100%. For n = 0 the delay between the input and output signal is only determined by the propagation delay  $t_{\rm pd}$  that the signal takes to propagate through the DTC. If the code is increased to n = 25%, the output is shifted by  $\pi/2 = 90^{\circ}$  compared to the case of n = 0 (assuming a perfectly linear DTC).

The further introduction is structured as follows: Section 1.1 reviews and compares popular DTC architectures and discusses their advantages and drawbacks. Afterwards Section 1.2 gives an overview on typical DTC applications, highlighting the benefits of DTCs when used to enhance or replace conventional circuit architectures. Finally, Section 1.3 outlines the present thesis and defines the key research objectives.

## 1.1 DTC Architectures and Circuit Design

State-of-the-art DTCs show a resolution of down to  $t_{d,LSB} = 19 \text{ fs} [1]$  and operation frequencies from the megahertz to the gigahertz domain. The best architecture can be chosen by trading off operation frequency, resolution, and jitter requirements, and depends highly on the targeted application. Before diving into the applications, typical DTC circuit architectures are reviewed.

If DTCs target high resolution, they are usually segmented into coarse and fine phase tuning stages. Common architectures for coarse tuning are the delay-locked-loop (DLL), divider, or multiphase voltage controlled oscillator (VCO) based approach, followed by a multiplexer (MUX). Their resolution  $t_{d,LSB}$  is limited either by the minimum inverter delay  $t_{inv,min}$  of the respective technology or by the frequency of their reference input  $f_{ref}$ . To overcome this limitation, subsequent fine tuning stages are used to provide a resolution of  $t_{d,LSB} \ll t_{inv,min}$ . For fine tuning switched capacitor circuits, phase interpolators (PI) or oversampling phase filters are used. In the following, the most popular concepts are described briefly and their advantages and limitations are discussed.

#### 1.1.1 Coarse Tuning Architectures

Coarse tuning blocks aim at providing a wide dynamic range with a coarse phase resolution  $t_{d,LSB,coarse}$  and high linearity. As this resolution is not sufficient for most applications, coarse tuning stages are constructed in a way that subsequent fine tuning blocks can be placed. The coarse tuning blocks discussed in the following have a resolution of  $k_{coarse}$  bit and generate  $N = 2^{k_{coarse}}$  evenly phase shifted signals.

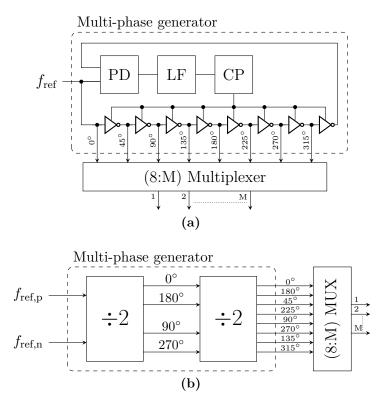

DLLs as shown in Fig. 1.2(a) consist of a voltage controlled delay line (VCDL) that is built from buffers or inverters, and regulate their delay in a negative feedback loop to ensure a delay range of  $2\pi$  [3–10]. The phase of the output signal is compared to the reference input by a phase detector (PD). The PD output is then low pass filtered by the loop filter (LF), which controls a charge pump (CP) to adjust the VCDL's delay. Another possibility of delay control is current starving of the single delay elements [6]. The MUX taps N evenly phase shifted signals which are generated from a reference with  $f_{\rm ref} = f_{\rm out}$ . The advantage of this architecture is the regulated  $2\pi$  range, that is accurate over process, voltage, and temperature variations (PVT). One drawback of this architecture is the long total delay of the buffer chain and hence accumulated jitter [11]. With an increasing number of delay stages the variance of each stages' delay increases along the line, with

Figure 1.2 – DTC coarse tuning architecture examples with  $k_{\text{coarse}}$  bit resolution: (a) DLL based coarse tuning, and (b) divider based coarse tuning [2].

maximum in the middle of the delay line [12]. The non-ideal delay of each delay stage is one source of nonlinearity in the DLL architecture. Another implementation featuring the described delay line is the tapped delay line (TDL), which lacks the DLL's control loop. This reduces the design complexity, saving the control loop design, but increases the nonlinearity and PVT sensitivity, which needs to be calibrated then [7,13].

Divider based coarse tuning stages generate N signals with a phase shift of min.  $T_{\rm ref}/2$ , followed by a MUX [2, 7, 13, 14], as shown in Fig. 1.2(b). An I/Q divider topology that operates on pseudo-differential input reference signals allows to generate signals of 0° and 90°, plus their pseudo-differential counterparts with 180° and 270°. As in case of the DLL, a MUX selects the coarse tuning output from the divider output signals. Compared to the DLL, the divider achieves low jitter and does not require a control loop. The implementation is fully digital, without the need of analog control blocks such as a CP. However, the input reference signal needs to have multiple times the frequency of the generated output signal.

As last coarse tuning approach, a MUX could tap directly N phase shifted output signals of a VCO or a ring oscillator [15, 16], for example N = 4 for a quadrature VCO (QVCO). The advantage is the use of the same circuit for reference clock generation and coarse tuning. However, to date no coarse tuning stages with a high order of N have been reported, that use this type of architecture.

Depending on the fine tuning architecture, which in the following examples require  $1 \leq M \leq 3$  adjacent phases as input, the MUX is implemented as (N : M) MUX. By changing the MUX implementation accordingly, each coarse tuning concept can be

Figure 1.3 – DTC fine tuning architectures: (a) switched capacitor based delay cell or DCDL, (b) PI [2], and (c) DLL based phase filter [16].

combined with any of the following fine tuning architectures.

For high orders of N or a high operation frequency the MUX implementation can be complicated. In addition to the coarse tuning block itself, it can contribute to nonlinearity. In general, it can be seen as a phase selector, for which the standard CMOS MUX is not necessarily the best implementation. Therefore, other implementations include MUX like circuits based on D flip-flops (DFF), thus sensitive to rising edges of the coarse tuning output [17–19], or a combination of logic gates, implementing MUX functionality [8].

#### 1.1.2 Fine Tuning Architectures

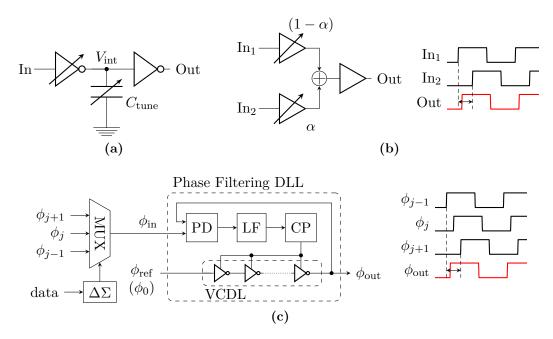

The following fine tuning architectures take the M output signals of the coarse tuning as input, and apply a phase tuning with high resolution. Therefore, their dynamic range should be limited to the resolution  $t_{d,LSB,coarse}$  of the coarse tuning block, to preserve monotonicity over all DTC stages.

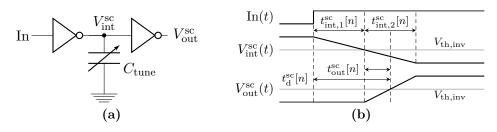

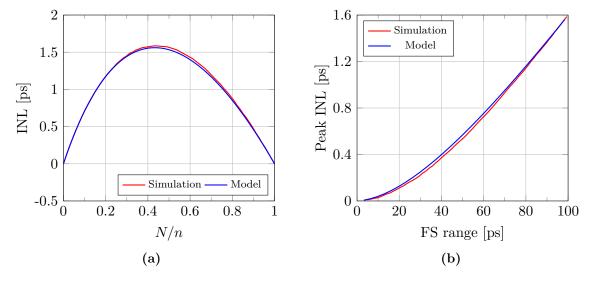

A fine tuning based on delay cells as shown in Fig. 1.3(a) tunes the RC constant of a node to modify the signal's zero crossing time [3, 7, 9, 10, 13, 15, 20-32], with an optional tunable inverter to adjust for PVT [7]. They are also referred to as switched capacitor based fine tuning or digitally controlled delay line (DCDL). The advantage of delay cells is their high linearity, as linear tuning of  $C_{\text{tune}}$  results in linear shifting of the zero crossing. The dominating source of nonlinearity is the  $C_{\text{tune}}$  dependent slope at  $V_{\text{int}}$ , that modulates the turn-on time of the output buffer [1,9]. Major drawbacks of this architecture are unwanted supply modulation through a code-dependent current consumption, high jitter through the degradation of the (dis)charge slopes, and a not well-defined delay range. Replica paths with inverted codes are necessary to equalize the current consumption over code [22–24, 26, 29] and calibration engines are used to cope with the undefined range [7].

DTCs integrated in phase-locked loops (PLL) use this fine tuning type commonly without coarse tuning [22–28, 30, 32, 33], relying only on a single stage DTC design. In general, multiple delay cells can be cascaded to ensure fast rise/fall times of the propagating signal, which improves sensitivity to supply and thermal noise [34] and prevents possible pulse swallowing at coarse tuning code changes [7].

PIs as shown in Fig. 1.3(b) have two input signals of identical frequency (M = 2), temporally shifted against each other by  $\Delta t$ , and produce an output signal weighted in time (or phase) domain from the inputs [1, 2, 6, 14, 16, 35-40]. The interpolation cells, to which the input signals are connected, are visualized as tunable buffers, but can be implemented differently. The PI output signal covers exactly  $\Delta t$  enclosed between  $\text{In}_{1/2}$ over code  $\alpha$ , but shows high systematic nonlinearity. A harmonic rejection technique has been implemented to linearize the PI [2], but at expense of a lower slew rate of the internal signals and hence, jitter. The present thesis focuses on PI based DTCs and gives a detailed analysis of different PI types and their systematic nonlinearity.

With a DLL as phase filter after a (N:3) MUX, oversampling can be explored to increase the DTC resolution [7,16]. The major difference of the phase filtering DLL from Fig. 1.3(c) compared to a regular DLL is the separation of PD and voltage controlled delay line (VCDL) input (compare Fig. 1.2(a) of the DLL based coarse tuning). The VCDL input  $\phi_{\rm ref}$  determines the frequency of the output signal, while  $\phi_{\rm in}$  determines its phase. To operate the DLL in a meaningful fashion,  $\phi_{ref}$  and  $\phi_{in}$  need to have an (on average) identical frequency. The reference  $\phi_{\rm ref}$  can be for instance equal to one of the coarse tuning signals (in front of the coarse tuning output MUX). The regulation loop consisting of PD, LF, and CP has a low pass characteristic due to the loop filter and locks the phase of  $\phi_{out}$  to  $\phi_{in}$ . If  $\phi_{in}$  changes,  $\phi_{out}$  follows with a delay determined by the control loop's bandwidth. The filtering effect of the DLL allows to switch between input signals with adjacent phases, and create an output signal with an average phase. This allows to apply oversampling and  $\Delta\Sigma$  modulation well known from PLL implementations for frational-N frequency synthesis [41]. The waveforms on the right hand side of Fig. 1.3(c) indicate the range of  $\phi_{out}$ 's phase for a given set of input signals. As it is well defined by the spacing of the input signals, it does not need further calibration. In [16] an impressive resolution of 14 bit is reported, however, new DTC codes cannot be applied immediately due to the phase filter's settling time. This reduces its practical use to applications with sufficiently slow changing input codes. A similar fine tuning was implemented in [42], where the (N:3) MUX in the coarse tuning stage was combined with the (3:1) MUX in front of the phase filter to a (N:1) MUX. This removes one MUX from the signal path, thus removing sources of jitter and nonlinearity, as well as saving power.

### **1.2 DTC Applications**

Many applications exist where DTCs are used to replace or enhance traditional architectures. Most of them came up only in the last decade and gained popularity through increasing DTC performance, resulting from architectural DTC enhancements and smaller technology nodes. Applications include usage in direct digital period synthesis (DDPS), clock-and-data-recovery circuits (CDR), in the feedback or reference path of a PLL, as fine delay in TDCs, or as direct phase modulators in polar or outphasing transmitters.

**Figure 1.4** – DDPS frequency synthesis: (a) DDPS circuit architecture [18], and (b) example operation of a 3 bit DDPS block for generation of  $f_{\text{out}} > f_{\text{ref}}$ .

One of the first DTC implementations was presented at ISSCC in 1990 [43], where a 5 bit DLL with subsequent MUX was used in the context of CDR.

While DTCs in PLLs often operate close to the reference oscillator's frequency, CDR and transmitter DTCs are required to operate at frequencies in the gigahertz range. This fact reflects in the architecture types chosen for the different applications. The following sections briefly introduce the mentioned DTC applications and highlight the advantages compared to prior DTC-less implementations.

#### 1.2.1 Direct Digital Period Synthesis

DDPS, also called digital period synthesis (DPS), is a technique that allows to synthesize clock signals (including spread spectrum clocks) for use in digital clocking or in communication systems in a purely digital manner. It was firstly introduced by Mair et al. in 2000 [44]. In principle, the circuit re-combines M signals of identical frequency  $f_{\rm ref}$  but different phases  $\phi_0, \phi_1, \ldots, \phi_M$  to generate an output signal with a different, mostly higher frequency  $f_{\rm out} > f_{\rm ref}$ . Digital programming allows then the control of  $f_{\rm out}$ .

As this architecture synthesizes periods by means of changing the output signal's phase with a DTC, the relation between phase and frequency is worth a brief look before discussing the circuit architecture. For continuous time signals, a frequency offset  $f_{\text{offset}}$  is related to a phase change  $\Delta \phi$  by

$$f_{\text{offset}} = -\frac{1}{2\pi} \frac{\Delta \phi}{dt},\tag{1.2}$$

where  $\Delta \phi$  is the phase change that needs to be applied in every clock cycle  $dt = 1/(f_{\text{out}} + f_{\text{offset}})$  [3]. Vice versa  $\Delta \phi$  is obtained by integrating (equivalent to accumulating in digital processing)  $f_{\text{offset}}$ .

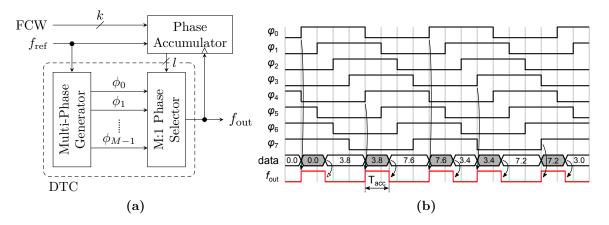

The heart of the DDPS systems is a DTC as presented in the coarse tuning section. Most architectures use an M phase generator followed by an (M:1) phase selector as shown in Fig. 1.4(a) [3,8,17–19,34,44,45]. The phase generator is most often implemented as DLL, but phase signals can also be tapped directly from an oscillator. Its output phases are exemplary plotted for M = 8 in Fig. 1.4(b). The phase selector forwards one of these signals to its output, based on a digital control word. The DTC programming is derived

| Clock Cycle | FCW | $d_{\rm acc}$ | $d_{\rm sel}$ |

|-------------|-----|---------------|---------------|

| 1           | 3.8 | 0.0           | 0             |

| 2           | 3.8 | 3.8           | 4             |

| 3           | 3.8 | 7.6           | 0             |

| 4           | 3.8 | 3.4           | 3             |

| 5           | 3.8 | 7.2           | 7             |

| 6           | 3.8 | 3.0           | 3             |

**Table 1.1** – Accumulator output for M = 8 and FCW = 3.8.

from accumulating (or integrating) a frequency control word (FCW), which is equivalent to  $f_{\text{offset}}$  from (1.2). The accumulator is clocked by  $f_{\text{out}}$ , which satisfies the assumption that the period needs to change on rate of  $f_{\text{ref}} + f_{\text{offset}}$ .

The waveforms in Fig. 1.4(b) and the related Table 1.1 show an example for FCW = 3.8, leading to an average period of  $f_{\rm out} \sim 2.11 f_{\rm ref}$ . The fractional FCW is accumulated to  $d_{\rm acc}$  and then truncated to  $d_{\rm sel}$ , which has a data width of l and is connected to the MUX control (the fractional MSB of  $d_{\rm acc}$  is added to its integer part to be precise). This leads to periods of  $3 - 4 t_{\rm d,LSB}$ , with a total average of 3.8  $t_{\rm d,LSB}$ . The clock to output delay of the accumulator  $T_{\rm acc}$  defines the duty cycle (which is not at 50%) and limits the maximum possible output frequency. As this programming scheme allows multiple code changes per reference cycle,  $f_{\rm out}$  can be much higher than  $f_{\rm ref}$ .

As single-stage phase selectors can only implement a coarse DTC resolution with reasonable design effort (max. of 5 bit reported in [8]), two-stage DTC architecture were presented [3,8]. Here a subsequent switched capacitor based fine tuning [8] or a PI [3] is employed to increase the resolution. Another two-stage DTC differs from the architectures described above and employs a multi-modulus divider (MMD) for coarse tuning and a DCDL for fine tuning [34]. This circuit omits high order phase selectors, however, it requires  $f_{\rm ref} > f_{\rm out}$ .

From system perspective, level and location of systematic spurs in the output spectrum can be related to the DTC's quantization noise or nonlinearity [14, 46, 47]. Therefore, DTCs with high resolution and low nonlinearity are preferred. Moreover, periodicity of the DTC code sequence is visible as spurs in the spectrum. The spurs can be reduced by randomizing the DTC programming through an accumulator implemented as 1<sup>st</sup> or 2<sup>nd</sup> order  $\Delta\Sigma$ -modulator [17–19], or by applying random dithering [33].

As DDPS is an open loop system, it can change its output frequency in a single output clock cycle. This fact and the possibility of a wide frequency range are the main advantages compared to PLLs. In addition, multiple DDFSs can share the same reference or multiplese generator. This enables the generation of multiple clocks at different frequencies from the same PLL [34] or DLL [8], thus reducing the number of on-chip synthesizers as well as moving clock generation to a fully digital domain.

#### 1.2.2 Clock and Data Recovery Circuits (CDR)

Wireline inter-chip communication systems aim continuously at higher data rates. This imposes design challenges on CDR circuits, which are implemented on receiver (RX) side to recover the transmitted data sequence from the distorted input signal together with its

Figure 1.5 – Source-synchronous interface with DTC phase adjustment [16].

clock signal.

Most wireline transmission systems are source-synchronous or source-asynchronous systems (also called plesichronous systems). In the synchronous case, data is transferred together with the reference clock signal, while in the asynchronous case the RX and transmitter (TX) chips generate their own reference frequencies, leading to a possible frequency shift between transmitting and receiving clock.

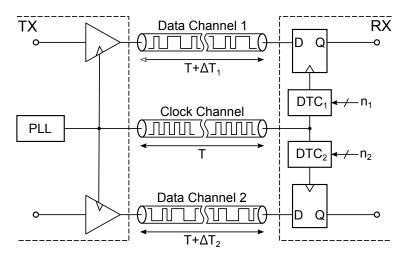

Multi-channel source-synchronous interfaces transmit data on multiple channels and a clock signal in a separate channel, as shown in Fig. 1.5 [16]. The imperfect matching and spacial channel separation on RX and TX side lead to skew between the data and clock signals, labeled here as  $\Delta T_{1/2}$ . On the RX side, the CDR circuit needs to correct the clock signal's phase for the skew  $\Delta T_{1/2}$  to sample the incoming data at the ideal time. For this purpose, each channel can shift the reference clock with a DTC [16].

Source-asynchronous systems need to adjust the frequency on top of a possible phase shift. Instead of using multiple PLLs at RX side to operate the CDR on several channels, a single PLL is used for reference clock generation and DTC can be used for phase and frequency correction [48]. As a slight frequency shift can be seen as continuous phase shift (see (1.2) for the relation between phase and frequency), it can also be corrected by the DTC. The DTC is required to allow modulo  $2\pi$  operation, which enables continuous phase shifts without unwanted wrap-arounds. Attractive circuits for this purpose are PIs or quadrature PIs, where quadrature refers to four input signals, shifted against each other by 90° [48–50], such as generated by a DTC coarse tuning stages based on a QVCO with subsequent (4 : 2) MUX. As the CDR's PIs operate mostly on sinusoidal signals, their linearity is much higher than in systems with digital signals and steep edges, where nonlinearity is the major drawback of PIs. Apart from this application type, PIs usually operate on digital signals. On DTC side the design focus is especially on the PI, as it needs to operate at data rates in the multi gigahertz range for state-of-the-art wireline transmission.

Figure 1.6 – Fractional-N ADPLL implemented with (a) integer-N divider and TDC, and (b) integer-N divider, DTC to realize fractional-N operation, and 1 bit TDC implemented as comparator.

#### 1.2.3 DTC Assisted TDCs

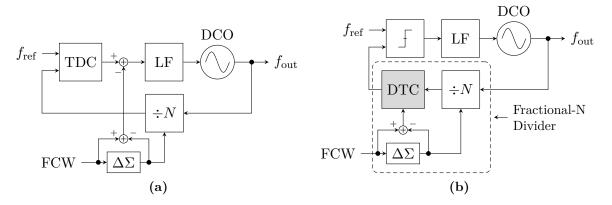

Fig. 1.6(a) shows the well known all-digital PLL (ADPLL), where TDCs are used as phase detectors to allow the fully digital implementation of the LF and the use of a digitally controlled oscillator (DCO) [51–54]. The ADPLL enables fractional-N operation through  $\Delta\Sigma$ -modulation of the integer-N divider in its feedback path. The divider control switches between different integer division ratios, resulting in an averaged output frequency through the low pass characteristic of the LF. The unavoidable error between the fractional FCW and the actual integer division ratio is substracted from the TDC output to reduce the code activity in front of the LF [30]. The TDC is one of the key blocks in the ADPLL's control loop. It requires high design effort and consumes a significant portion of the overall power. Furthermore, the generated fractional spurs depend mainly on its nonlinearity as well as its resolution.

If the integer-N divider is replaced by a fractional one, a bang-bang phase detector (BBPD) would suffice as TDC replacement. Fractional-N division can be realized by placing a DTC subsequently to the integer-N divider as depicted in Fig. 1.6(b), where the DTC adds the fractional part to the integer-N division. The phase error derived from the divider control word is fed to the DTC (phase error is obtained from frequency error through integration), which delays the signal accordingly. As DTCs have a certain quantization, the TDC could at least be relaxed in terms of detection range. The TDC range can now be in the domain of the DTC's resolution instead of the DCO period, resulting in a significantly simplified design.

A first approach was introduced in [55], where a 4 bit DLL based DTC was connected in series to the integer-N divider of the feedback loop, allowing to forward an intermediate divider output to the TDC. This allows to reduce the TDC range by four MSBs, simplifying the design and reducing the power consumption. This approach was taken one step further in [56], where a 9 bit switched capacitor (DCDL) based DTC allows to reduce the TDC range to only 8 ps. In [30, 57, 58] this concept was finally extended to a 10 bit switched capacitor based DTC, enabling to reduce the TDC to a BBPD. This allows to use a simple comparator as 1 bit TDC, solving the issues of TDC nonlinearity and resolution [59].

Another solution to the same problem is the use of a DTC in the reference instead of

Figure 1.7 – DTC-based fractional-N sub-sampling PLL [65].

the feedback path. It was first introduced in [28], where a sample based counter is used as phase detector. The ADPLL is restricted to integer-N mode if the DTC is deactivated, fractional-N mode is enabled when the DTC is used to a-priori delay the reference edges according to an accumulated FCW. The DTC is realized as digitally controlled Vernier delay line (similar to a DCDL), which is in principle a series of switched capacitor DTC cells. In [22, 33, 60–62] the reference path DTC is used to reduce the detection range of the TDC, resulting in the advantages discussed above.

While the discussed approaches reduce the requirements of the TDC regarding range, resolution, and nonlinearity, the DTC design moves into focus. At DTC level, resolution and nonlinearity can be handled with less design effort and lower power overhead [59]. Adaptive digital pre-distortion is applied in order to reduce the nonlinearity and adjust the delay range over PVT [57]. To keep the power and phase noise advantage of the DTC-based approach, the correction is only applied in the digital domain [59]. In addition,  $\Delta\Sigma$ -modulation can be used to overcome the limitations of the DTC resolution [63]. The full DTC range needs to cover the maximum expected error from  $\Delta\Sigma$ -control at the divider output, plus a margin for PVT [57], which is in the order of multiple VCO periods. Overall, BBPD based ADPLLs can achieve identical spur/noise performance while reducing the power and complexity compared to TDC based ADPLLs [64].

### 1.2.4 Fractional-N Sub-Sampling PLLs (SSPLL) and Multiplying DLLs (MDLL)

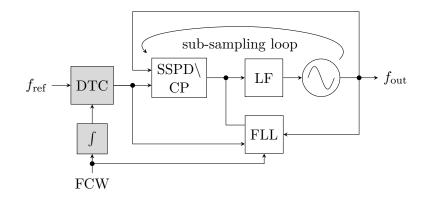

One step further in the direction of TDC assistance in the reference path allows the DTC to generate a shift of the reference clock to enable fractional-N operation. However, this technique was not explored for ADPLLs, but to enable fractional-N operation in sub-sampling PLLs (SSPLL) and multiplying DLLs (MDLL). Both, SSPLLs and MDLLs, are attractive architectures for clock generation, as they offer low power and low noise. In the following, the working principle of their integer-N version is recapped briefly, followed by a discussion of the DTC extension that enables fractional-N operation for both architectures.

The first SSPLL was published in 2009 [66]. Its block diagram is shown in Fig. 1.7, where the DTC is assumed to be bypassed for now and some digital processing on the FCW is left out for simplicity. It has two control loops, a sub-sampling loop and a frequency-locked loop (FLL), that share the same LF. The FLL resembles a regular PLL control loop and

Figure 1.8 – DTC-based fractional-N MDLL [69].

consists of an integer-N divider, a PD, and a CP. It is used to lock the oscillator to the desired target frequency for start-up purposes. After locking, the FLL is disabled to save power, and the sub-sampling loop remains to be the active control loop. The sub-sampling phase detector (SSPD) compares the phase of  $f_{\rm ref}$  and  $f_{\rm out}$  at every rising edge of  $f_{\rm ref}$ . As the divider is removed from the feedback loop, its power consumption and generated noise are removed from the system. However, as the output is compared directly to the reference, this system is limited to integer-N operation.

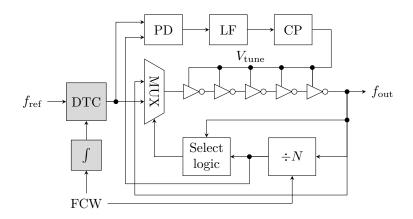

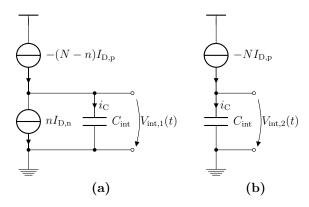

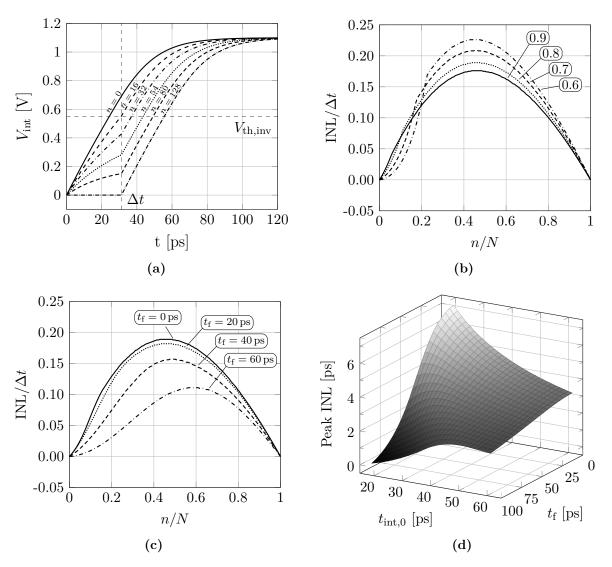

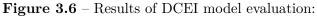

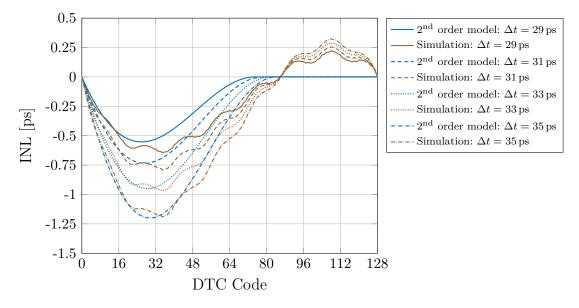

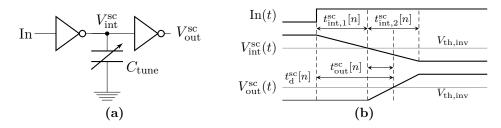

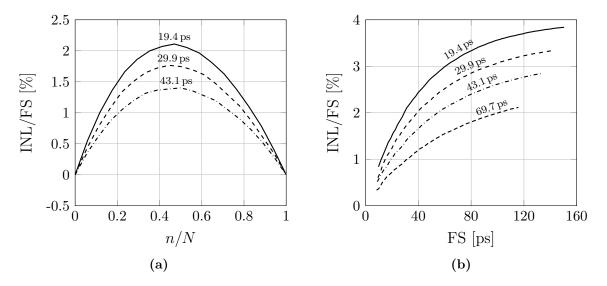

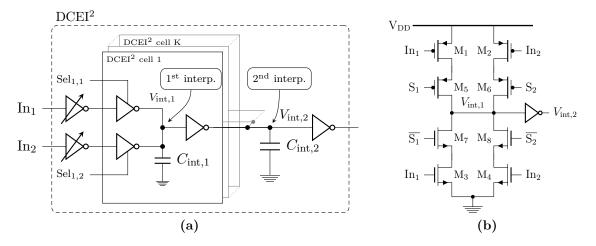

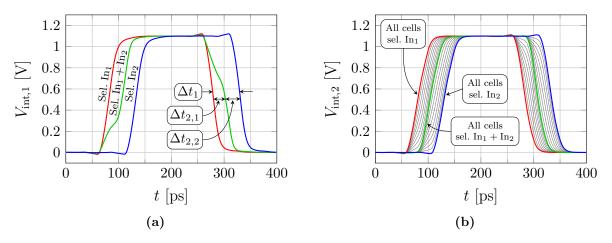

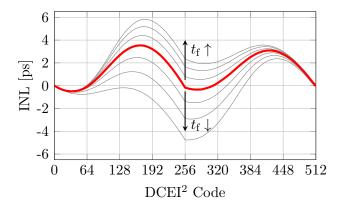

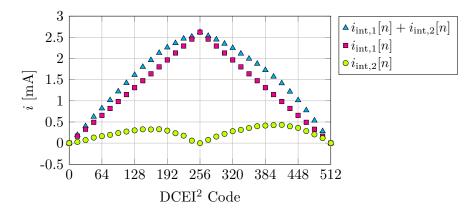

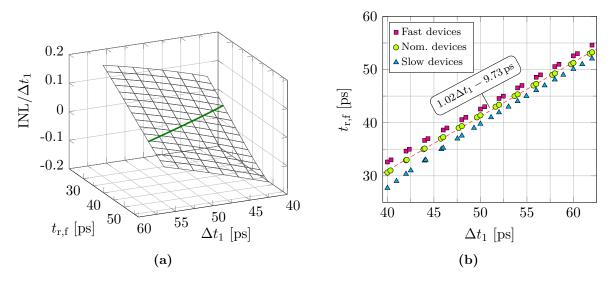

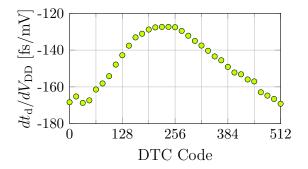

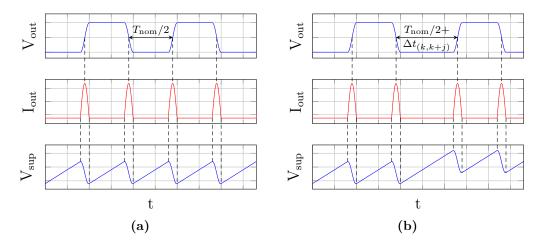

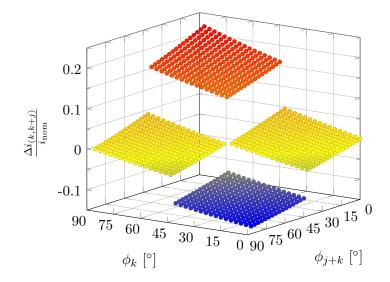

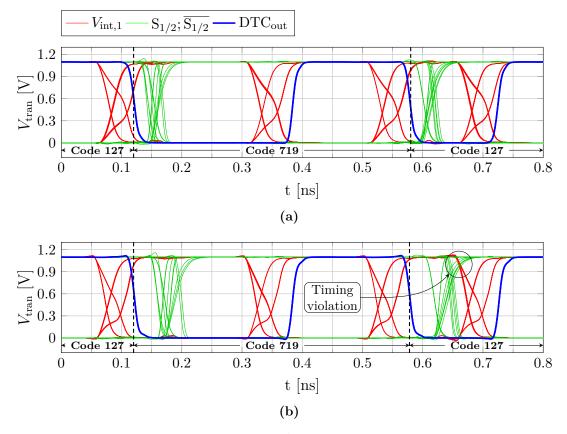

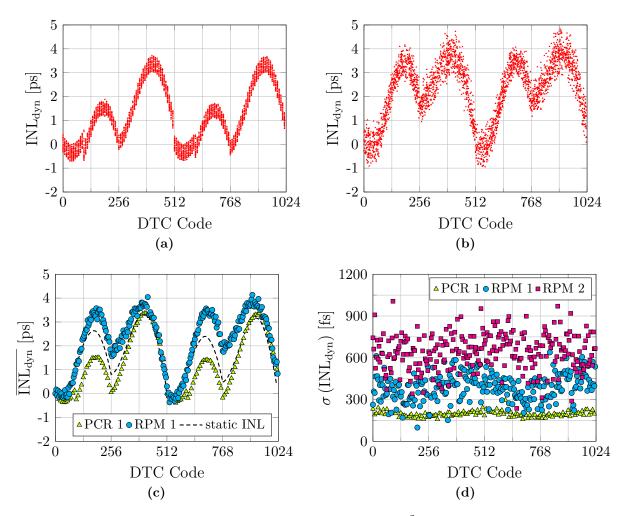

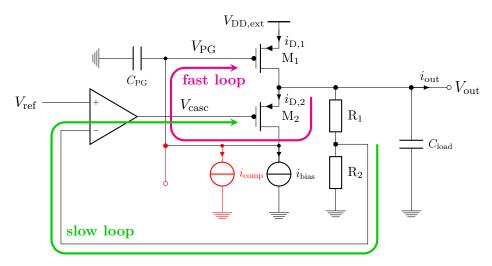

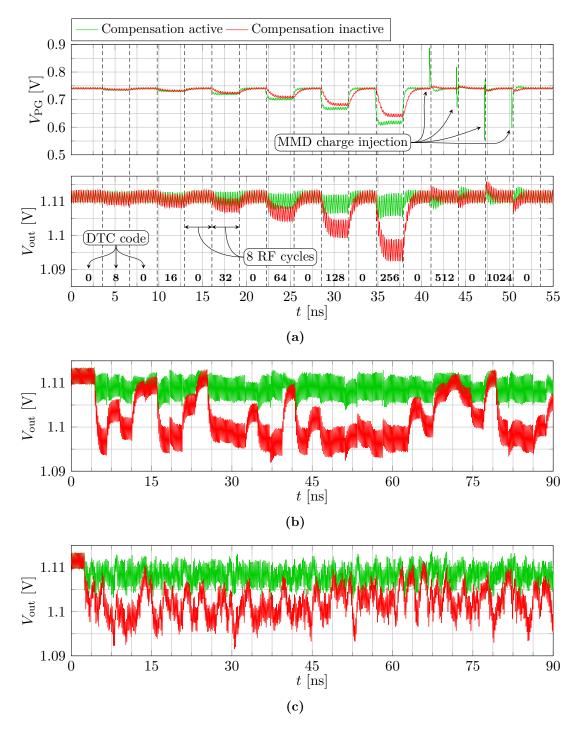

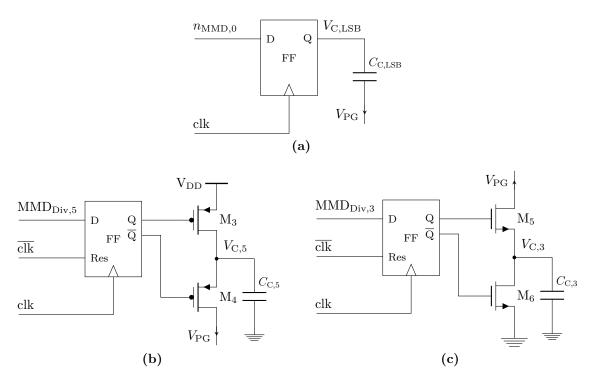

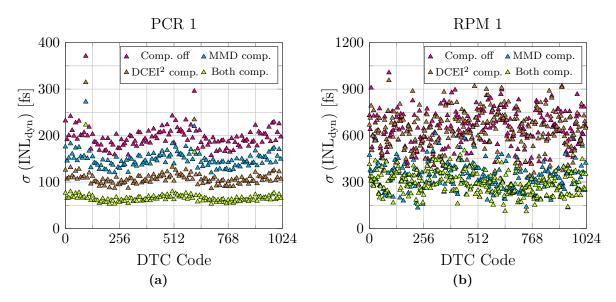

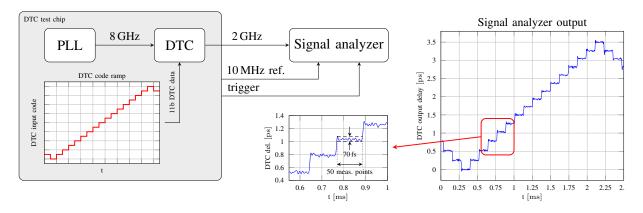

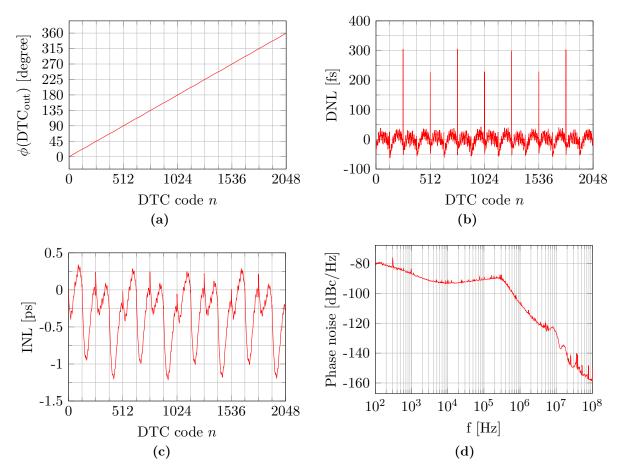

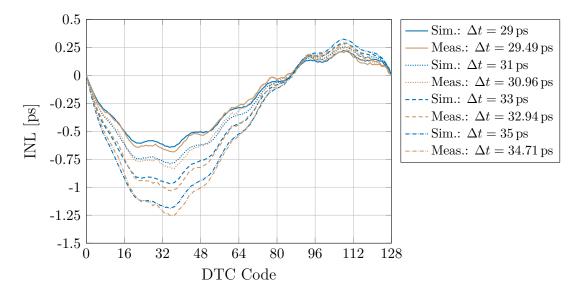

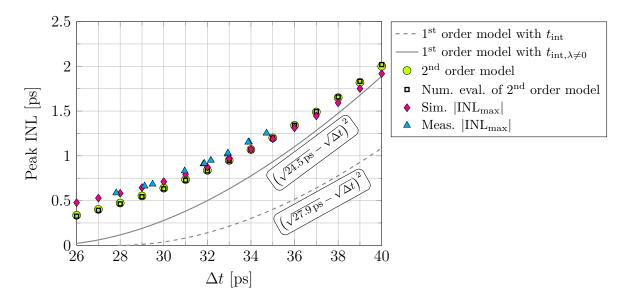

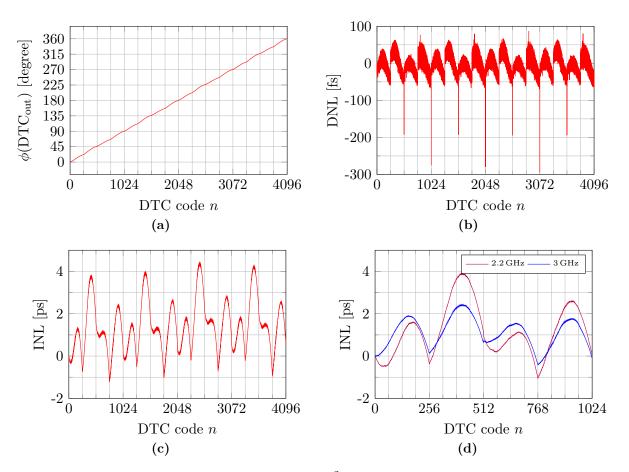

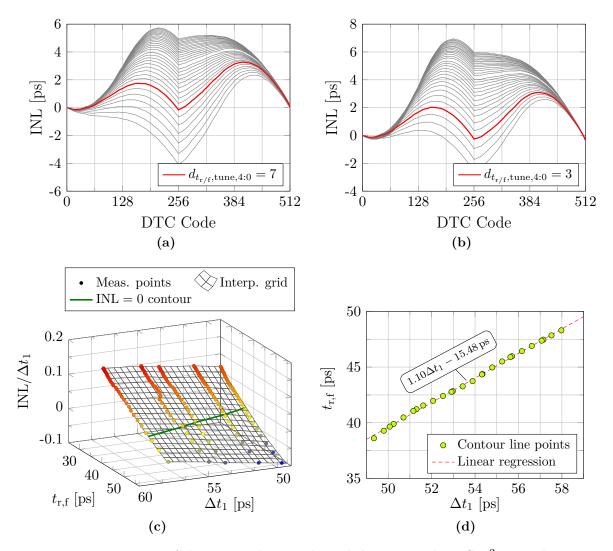

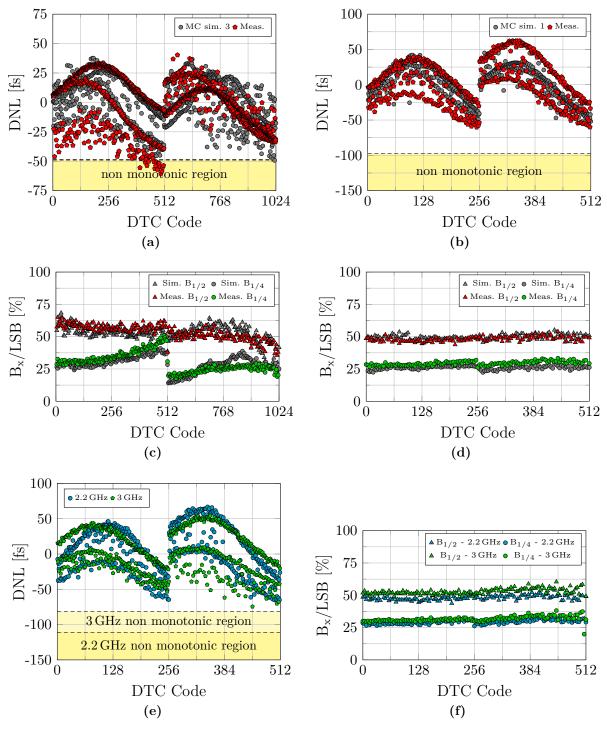

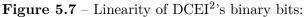

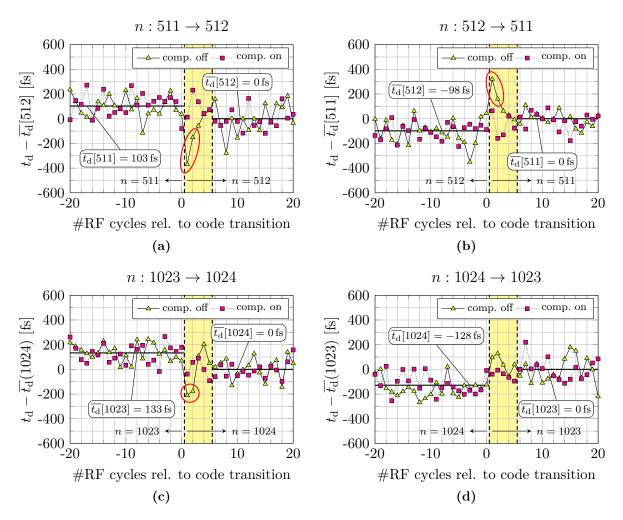

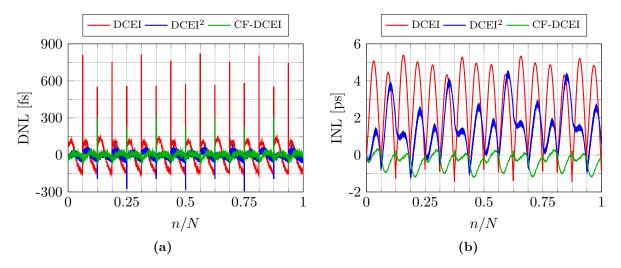

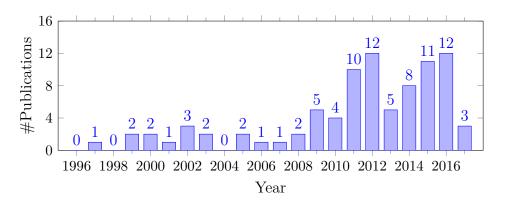

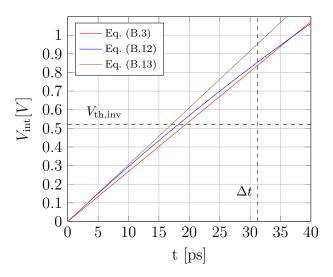

The MDLL was first published in 2002 [67], and its block diagram is shown in Fig. 1.8 where the DTC is assumed as bypassed and some digital processing on the FCW is left out for simplicity again. The MDLL consists of an odd number of subsequent inverters (in this example five) and one multiplexer (MUX), and its overall propagation delay can be tuned by the voltage  $V_{\text{tune}}$ . The tuning voltage is the output of the control loop consisting of PD, LF, and CP (optionally implemented digitally as DAC). It locks the output phase to the reference phase. Every  $N^{\text{th}}$  output cycle the select logic controls the MUX to forward a reference edge into the DLL, removing the accumulated jitter. While it brings the advantage of lower output noise up to a frequency offset of  $f_{\text{ref}}/2$  (a much higher offset than the loop filters of PLLs usually provide), the MDLL suffers mainly from two problems [68]: first,  $f_{\text{out}}$  can only be changed in integer multiples of  $f_{\text{ref}}$ , and second, the timing of the phase injection needs to be very accurate (low phase offset in the phase detector) as else strong reference spurs occur in the output spectrum.