### Technische Universität München Lehrstuhl für Sicherheit in der Informationstechnik an der Fakultät für Elektrotechnik und Informationstechnik

## Highly Efficient Implementation of Physical Unclonable Functions on FPGAs

## Stefan Gehrer

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines **Doktor-Ingenieurs (Dr.-Ing.)** genehmigten Dissertation.

Vorsitzender: Prof. Dr. Holger Boche

Prüfende der Dissertation:

1. Prof. Dr.-Ing. Georg Sigl

2. apl. Prof. Dr.-Ing. Walter Stechele

Die Dissertation wurde am 27. April 2017 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 14. August 2017 angenommen.

Physical Unclonable Functions (PUFs) are an innovative way to use uncontrollable production tolerances of Integrated Circuits (ICs) for the generation of device intrinsic cryptographic keys. Unfortunately, the huge area consumption of many PUF implementations on Field-Programmable Gate Arrays (FPGAs) made them infeasible in real world environments. This work presents a new method for highly efficient usage of Ring Oscillator (RO) PUFs on FPGAs.

The stability of such PUF outputs is essential for the reliability of the cryptographic key. Any bit error in a cryptographic key makes it unusable. Therefore, an extensive stability analysis involving both reversible environmental changes and irreversible aging effects was carried out.

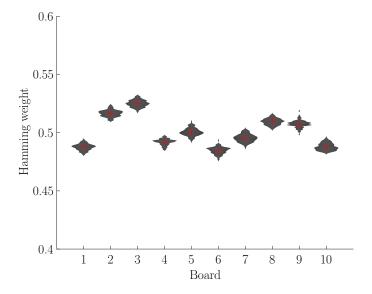

In the first part of this thesis, a basic implementation of RO PUFs on FPGAs is presented. The quality properties such as Hamming Weight (HW) or Hamming Distance (HD) promised a very good usability of RO PUFs on FPGAs. However, the generation of a 2136 bit PUF output consumed  $80\,\%$  of the available slices on a Xilinx Zyng Z-7020.

In the second part, the complex system of logic and routing resources on FPGAs was analyzed for their usability as entropy sources for PUFs in combination with partial reconfiguration. Different implementations of ROs were reconfigured on the same area of the FPGA to maximize the resource usage. Each of them occupied the same logic block on an FPGA, but used different logic and routing resources inside the block. A partial bit vector response was generated by each implementation. All of them were joined to a larger response vector that could be used to generate a cryptographic key.

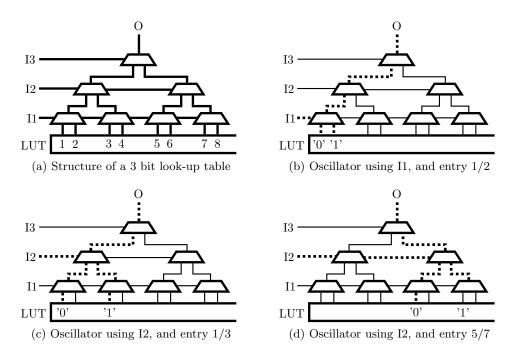

The implementation of this method showed that it is possible to decrease the required resources to generate a PUF response with a given length by almost 98% on a Xilinx Zynq. To achieve this big area shrinkage, every of the eight Lookup Tables (LUTs) within a logic block, and every of the six input pins within a LUT was used for a unique RO implementation. The min-entropy of this reconfigurable PUF was found to be 93% using different methods such as Context Tree Weighting (CTW), Principal Component Analysis (PCA), and the NIST SP 800-90B entropy test.

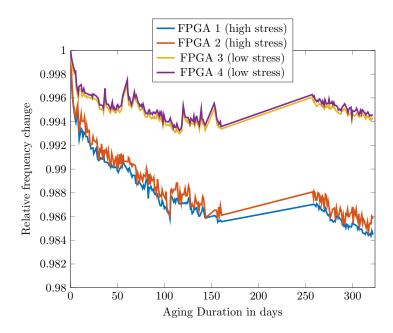

iv ABSTRACT

Robustness of the PUF against reversible environmental changes and irreversible aging effects is crucial for its reliability. Although the influence of environmental changes is studied in depth, there is still only limited research on aging effects. An accelerated aging test on 28 nm Xilinx Zynq FPGAs was performed for roughly one year in the third part of this thesis. The results were compared to the impact of reversible environmental fluctuations. A set of different designs with distinct types of logical stress was used to amplify the effects of various aging mechanisms. The impact of accelerated life conditions on the frequency of different RO PUFs was measured and analyzed. It was shown that the aging effect is dramatically accelerated with higher temperatures and voltages. The frequency of the ROs was lowered to around 98.6% of the initial value, after an effective accelerated aging duration of around 60 years. The reliability of the PUFs without error correction was decreased by up to 6 %. Furthermore, the experiments showed that aging effects reduced the reliability in the same order of magnitude as environmental variations, namely voltage and temperature variations.

In the last part of this work, an exemplary application of the partial reconfiguration PUF on FPGAs was shown. The reconfigurable PUF was used with the reliability measurements from the previous chapter to choose an appropriate PUF-based key generation scheme from the literature. The PUFKY algorithm was chosen in this work. The amount of slices that were needed to implement the RO PUF part of the system could be lowered by at least 79.4% when using the partial reconfiguration PUF. Furthermore, the usage of slices within the CLBs would be much more efficient when using the method presented in this work. A scheme was proposed which allows a secure boot of a PUF-based security module on an FPGA. The security module is able to load encrypted Intellectual Properties (IPs) from an unprotected non-volatile memory, as well as transmit new or modified IPs over-the-air while preserving the confidentiality and authenticity.

### Acknowledgments

Foremost, I would like to express my sincere gratitude to Prof. Dr.-Ing. Georg Sigl for supervising this thesis and all members of the Chair of Security in Information Technology for the fruitful discussions. I also thank my second examiner Prof. Dr.-Ing. Walter Stechele.

Being part of the security team at Bosch was an awesome experience. I enjoyed every conversation about work related and unrelated topics, and they greatly contributed to the success of my thesis. A dedicated thank you to Sébastien Léger for being a great supervisor at Bosch, as well as Dr. Jürgen Schirmer for always supporting me as a group leader. Furthermore, I would like to thank Dr. Paul Duplys, Christopher Huth, Hervé Seudié, Dr. Hans Löhr, Robert Szerwinski, Dr. David Förster, and Dr. Jan Zibuschka for all the discussions and the good times in Möglingen and Renningen.

I would like to thank my mother for her endless support, as well as Leah and Jennifer for the dedicated proof-reading of my thesis.

Last but not least, I would like to thank all my friends around the world for always being there for me and making life so much more fun. It would be pretty boring without all y'all!

## Contents

| Αl | Abstract          |                            |   |  |  |  |  |  |  |  |

|----|-------------------|----------------------------|---|--|--|--|--|--|--|--|

| A  | Acknowledgments v |                            |   |  |  |  |  |  |  |  |

| Li | st of             | Abbreviations xvi          | i |  |  |  |  |  |  |  |

| 1  | Intr              | oduction                   | 1 |  |  |  |  |  |  |  |

| 2  | Bac               | ground                     | 5 |  |  |  |  |  |  |  |

|    | 2.1               | PUF Concepts               | 5 |  |  |  |  |  |  |  |

|    |                   | 2.1.1 History              | 6 |  |  |  |  |  |  |  |

|    |                   | 2.1.2 Weak and Strong PUFs | 6 |  |  |  |  |  |  |  |

|    |                   | 2.1.3 Quality Measures     | 7 |  |  |  |  |  |  |  |

|    | 2.2               | PUF Types                  | 3 |  |  |  |  |  |  |  |

|    |                   | 2.2.1 Optical PUF          | 3 |  |  |  |  |  |  |  |

|    |                   | 2.2.2 Silicon PUFs         | 5 |  |  |  |  |  |  |  |

|    | 2.3               | PUF-based Key Generation   | 3 |  |  |  |  |  |  |  |

|    |                   | 2.3.1 Select               | 3 |  |  |  |  |  |  |  |

|    |                   | 2.3.2 Correct              | 9 |  |  |  |  |  |  |  |

|    |                   | 2.3.3 Compress             | 1 |  |  |  |  |  |  |  |

|    | 2.4               | FPGA                       | 1 |  |  |  |  |  |  |  |

|    |                   | 2.4.1 Overview             | 1 |  |  |  |  |  |  |  |

|    |                   | 2.4.2 Structure            | 2 |  |  |  |  |  |  |  |

|    | 2.5               | Cryptography               | 3 |  |  |  |  |  |  |  |

|    |                   | 2.5.1 Symmetric            | 4 |  |  |  |  |  |  |  |

|    |                   | 2.5.2 Asymmetric           | 5 |  |  |  |  |  |  |  |

viii *CONTENTS*

| 3 | Imp | olement  | ing PUFs on FPGAs 27                    |

|---|-----|----------|-----------------------------------------|

|   | 3.1 | Introdu  | action                                  |

|   | 3.2 | Theory   | 28                                      |

|   | 3.3 | Implem   | nentation                               |

|   | 3.4 | Experir  | mental Results                          |

|   |     | 3.4.1    | Area                                    |

|   |     | 3.4.2    | Speed                                   |

|   |     | 3.4.3    | Quality Properties                      |

|   | 3.5 | Conclus  | sion                                    |

| 4 | Enl | nancing  | Efficiency Using PR 45                  |

|   | 4.1 | Introdu  | action                                  |

|   | 4.2 | Prior W  | Vork                                    |

|   | 4.3 | Reconfi  | gurable PUF                             |

|   |     | 4.3.1    | Method 1: Using Different LUTs 49       |

|   |     | 4.3.2    | Method 2: Using Different Input Pins 50 |

|   |     | 4.3.3    | Combining Both Methods                  |

|   |     | 4.3.4    | Analysis of Shared Resources 54         |

|   | 4.4 | Implem   | nentation                               |

|   | 4.5 | Experir  | mental Results                          |

|   |     | 4.5.1    | Speed                                   |

|   |     | 4.5.2    | Frequencies                             |

|   |     | 4.5.3    | Uniformity                              |

|   |     | 4.5.4    | Bit Alias                               |

|   |     | 4.5.5    | Uniqueness                              |

|   | 4.6 | Entropy  | y Estimation                            |

|   |     | 4.6.1    | Context-Tree Weighting 63               |

|   |     | 4.6.2    | Principal Component Analysis 64         |

|   |     | 4.6.3    | NIST SP 800-90B Entropy Test            |

|   | 4.7 | Conclus  | sion $\dots$ 70                         |

| 5 | Rel | iability | Analysis 71                             |

|   | 5.1 | Introdu  | action                                  |

|   | 5.2 | Prior W  | Vork                                    |

|   | 5.3 | Aging    |                                         |

|   |     | 5.3.1    | Aging Mechanisms                        |

|   |     | 5.3.2    | Stress Design                           |

|   |     | 5.3.3    | Accelerated Environmental Conditions 78 |

|   |     | 5.3.4    | Implementation and Setup 79             |

|   |     | 5.3.5    | Experimental Results and Discussion 82  |

|   | 5.4 | Temper   | rature and Voltage                      |

|   |     |          | Theory                                  |

|   |     | 5.4.2    | Test Setup                              |

|   |     | 5.4.3    | Experimental Results 91                 |

| CONTENTS |  | ix |

|----------|--|----|

|          |  |    |

| c | TZ  | Commention Contain                      | 7      |

|---|-----|-----------------------------------------|--------|

| 6 | Key |                                         | ٠      |

|   | 6.1 | Introduction                            | $^{7}$ |

|   | 6.2 | SoC Platform                            | 8      |

|   | 6.3 | Error Correction & Key Generation 9     | 9      |

|   | 6.4 | Security Module                         | 1      |

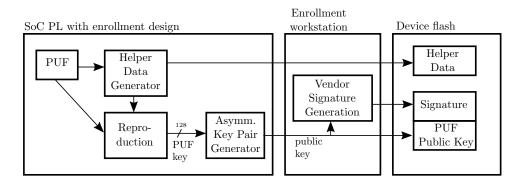

|   |     | 6.4.1 Enrollment Phase                  | 1      |

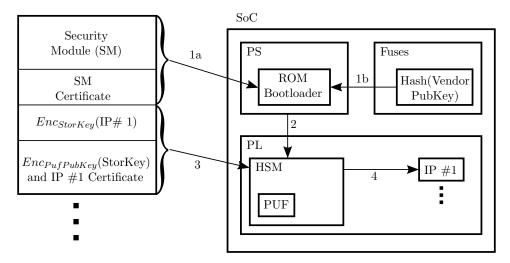

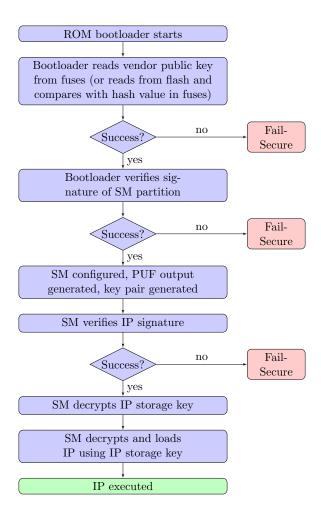

|   |     | 6.4.2 Security Module Boot Procedure 10 | 2      |

|   |     | 6.4.3 IP Loading Procedure              | 3      |

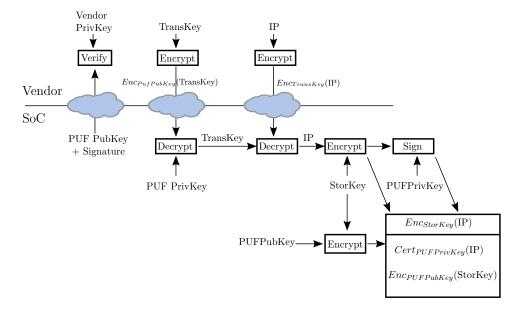

|   |     | 6.4.4 IP Storage Procedure              | 3      |

|   | 6.5 | Discussion                              | 5      |

|   | 6.6 | Conclusion                              | 6      |

x CONTENTS

# List of Figures

| 1.1  | Schematic of basic PUF behavior                               | 3  |

|------|---------------------------------------------------------------|----|

| 2.1  | Organization of PUF response data                             | 8  |

| 2.2  | Uniformity of a PUF response vector                           | 9  |

| 2.3  | Uniqueness of a PUF response compared to other devices        | 10 |

| 2.4  | Reliability of PUF under different environmental conditions . | 12 |

| 2.5  | Bit alias of a single PUF bit over all measured devices       | 14 |

| 2.6  | Schematic of a laser PUF                                      | 14 |

| 2.7  | Schematic of a RO PUF                                         | 15 |

| 2.8  | Schematic of an arbiter PUF                                   | 16 |

| 2.9  | Schematic of an SRAM PUF                                      | 17 |

| 2.10 | Generating cryptographic keys from noisy PUF responses        | 18 |

| 2.11 | Schematic of a fuzzy extractor                                | 20 |

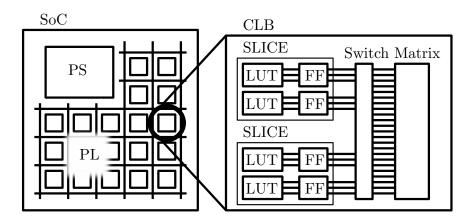

| 2.12 | Schematic of a modern SoC with PS part and a PL part          | 22 |

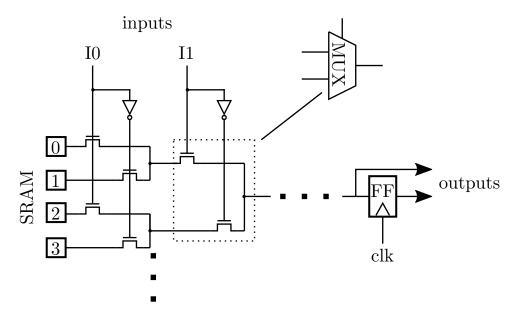

| 2.13 | Schematic of the implementation of a LUT on an FPGA           | 23 |

| 2.14 | Schematic of a symmetric key algorithm                        | 24 |

| 2.15 | Schematic of a public-key algorithm for encryption            | 25 |

| 2.16 | Schematic of public-key algorithm for digital signatures      | 25 |

| 3.1  | Schematic and implementation of 3-inverter RO PUF on FPGA     | 29 |

| 3.2  | Schematic and implementation of a TFF                         | 30 |

| 3.3  | Implementation of 3-inverter RO PUF on one slice              | 31 |

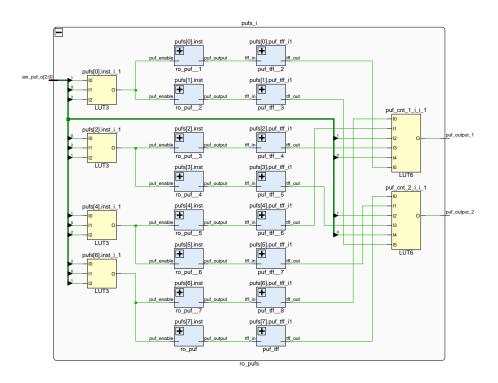

| 3.4  | Schematic of eight RO PUFs                                    | 32 |

| 3.5  | Biased pair of ROs                                            | 33 |

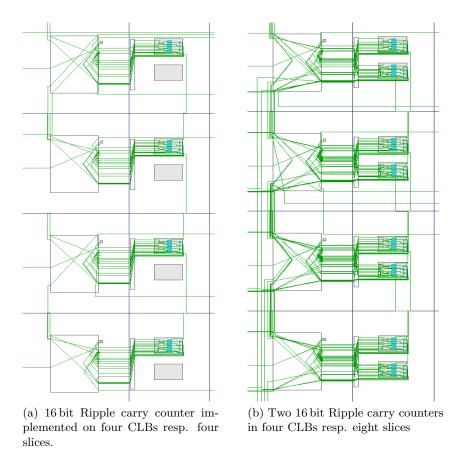

| 3.6  | Area efficient implementation of 16 bit asynchronous counters | 34 |

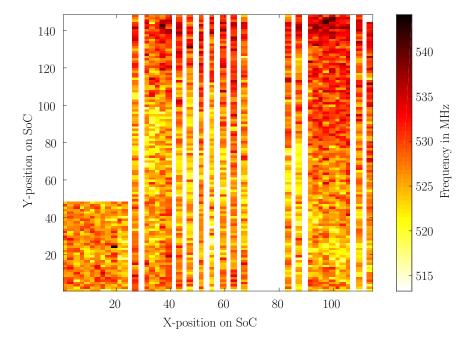

| 3.7  | Heatmap of 4272 ROs on the Zynq                               | 39 |

| 3.8  | Bean plot of the HW on 10 different boards                    | 40 |

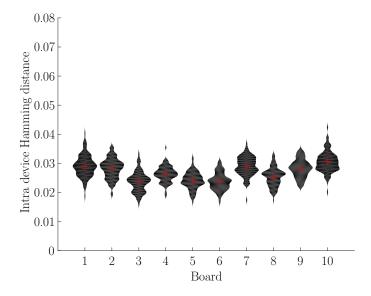

| 3.9  | Bean plot of the Intra-device HD                              | 41 |

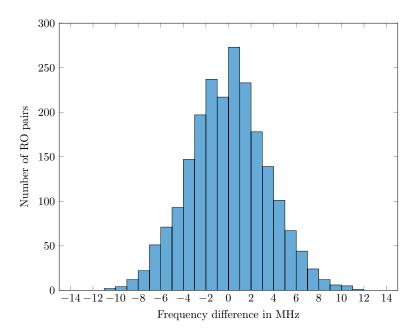

| 3.10 | Histogram of frequency difference between RO pairs                | 42 |

|------|-------------------------------------------------------------------|----|

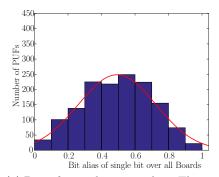

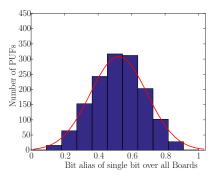

| 3.11 | Histograms of bit aliases measured over all boards                | 43 |

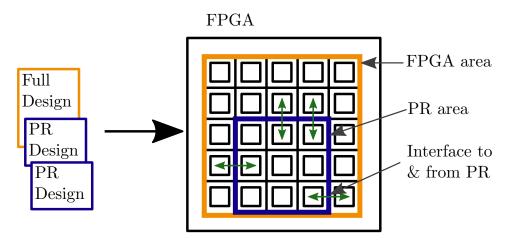

| 4.1  | Functional principle of partial reconfiguration                   | 46 |

| 4.2  | Using reconfigurable PUFs for key generation                      | 49 |

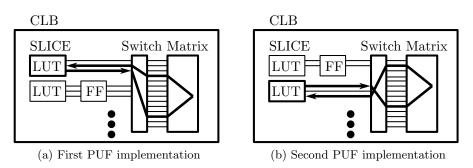

| 4.3  | Two PUF implementations on same CLB using different LUTs          | 50 |

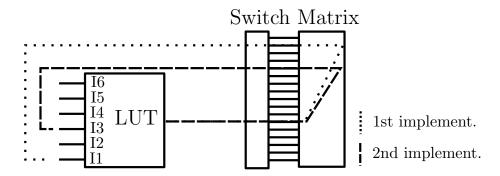

| 4.4  | Using different pins of a LUT                                     | 51 |

| 4.5  | Structure of a 3 bit LUT and different implementations of RO      | 52 |

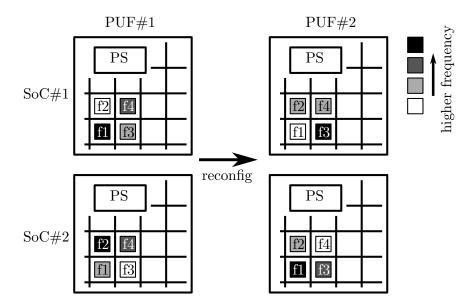

| 4.6  | Reconfiguration process on two SoCs                               | 53 |

| 4.7  | Possible shared resources between different RO implementations    | 55 |

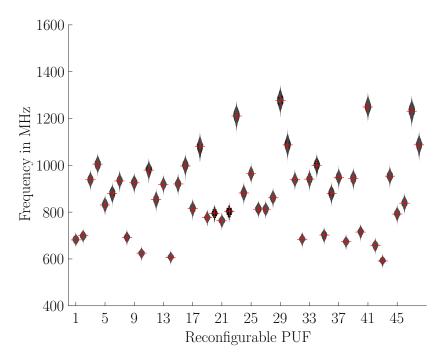

| 4.8  | Frequency distribution of all 48 RO designs on one board          | 58 |

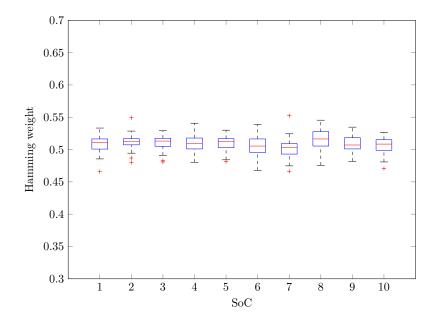

| 4.9  | HW of concatenated response vectors on each SoC                   | 59 |

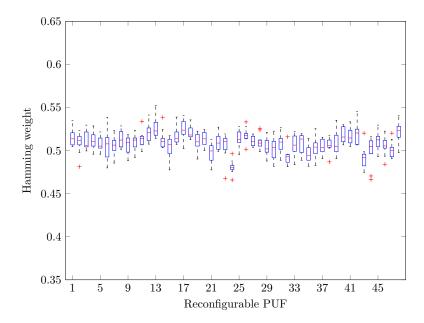

| 4.10 | Fractional HW of response vector of each PUF                      | 60 |

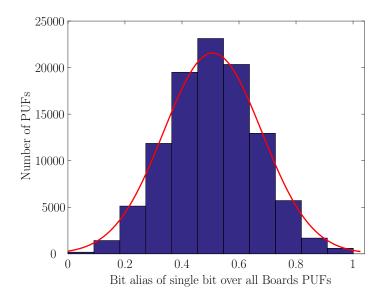

|      | Bit alias of all concatenated 2136 bit partial PUF responses .    | 61 |

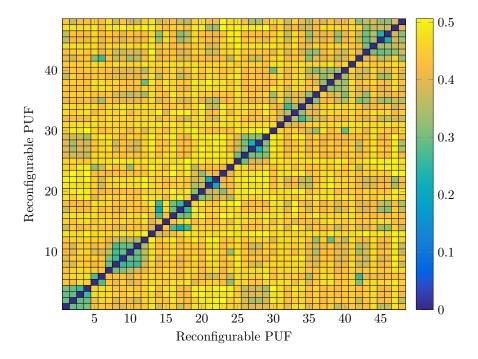

|      | Fractional HD between each partial PUF response                   | 62 |

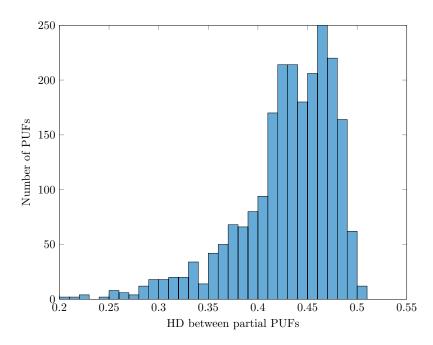

| 4.13 | Histogram of fractional HD between each partial PUF response      | 63 |

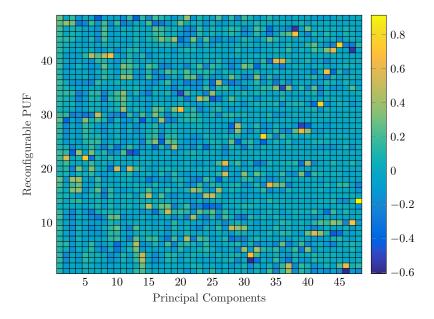

| 4.14 | Colorplot of the principal component coefficients                 | 65 |

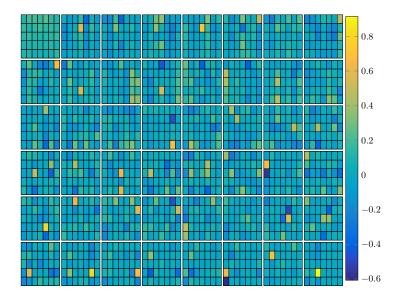

| 4.15 | Separated colorplot of the principal component coefficients       | 66 |

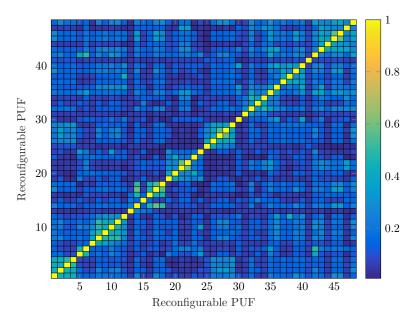

| 4.16 | Kendall rank correlation coefficient between reconfig. PUFs .     | 67 |

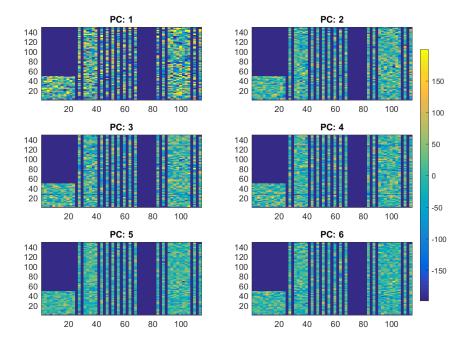

| 4.17 | Principal component scores for first six principal components     | 68 |

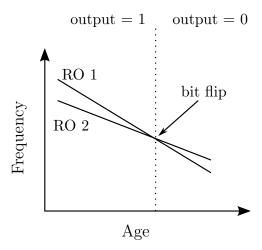

| 5.1  | Bit flip due to the aging of two ROs                              | 72 |

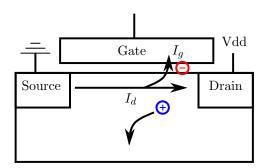

| 5.2  | HCI effect in a CMOS transistor                                   | 74 |

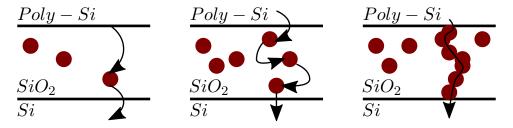

| 5.3  | NBTI effect in a PMOS transistor                                  | 74 |

| 5.4  | Schematic of TDDB effect                                          | 75 |

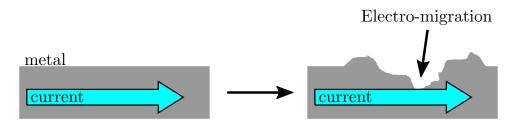

| 5.5  | Effect of EM in microelectronics                                  | 75 |

| 5.6  | Differently stressed columns on SoC                               | 76 |

| 5.7  | DC 0/1 stress and low/high frequency stress designs on LUT        | 77 |

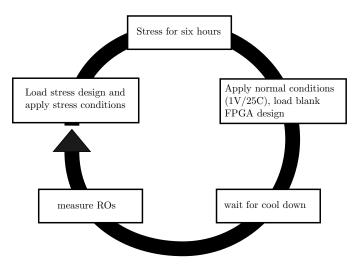

| 5.8  | Stress cycle used for aging an FPGA                               | 81 |

| 5.9  | Accelerated aging test setup                                      | 82 |

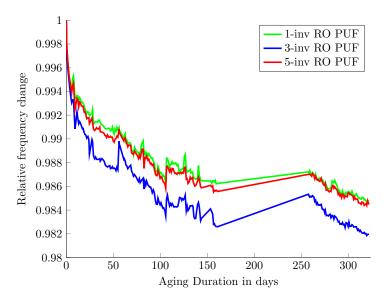

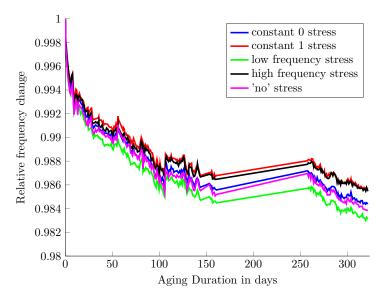

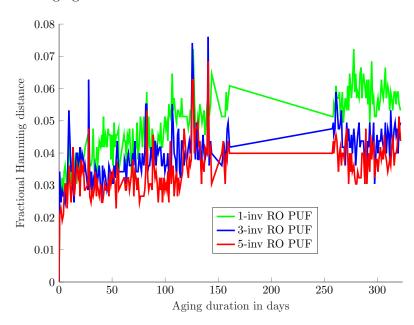

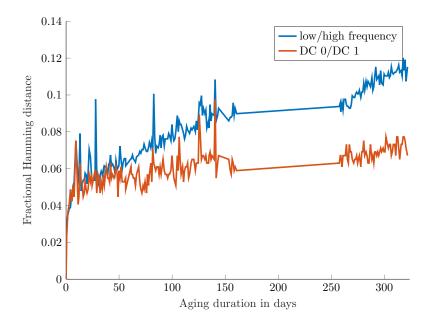

| 5.10 | Frequency degradation by different environmental stress           | 83 |

| 5.11 | Impact of amount of inverters on frequency degradation            | 84 |

| 5.12 | Impact of the electrical stress type on the frequency degradation | 84 |

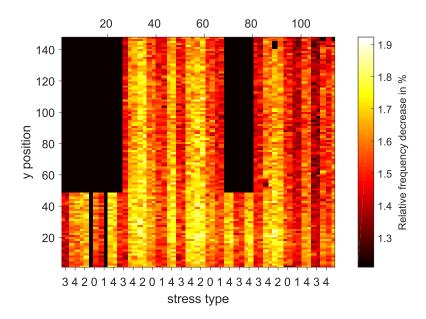

|      | Heatmap of frequency degradation by different electrical stress   |    |

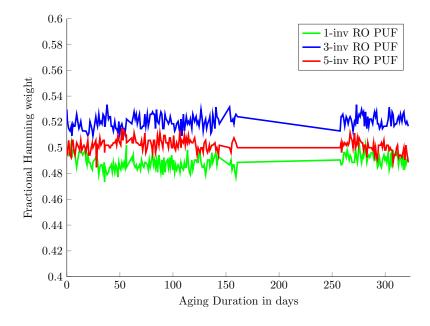

| 5.14 | Impact of the aging process on the HW of the PUFs                 | 86 |

| 5.15 | Impact of aging process on reliability of the PUFs                | 87 |

| 5.16 | Reliability when comparing differently stressed ROs               | 89 |

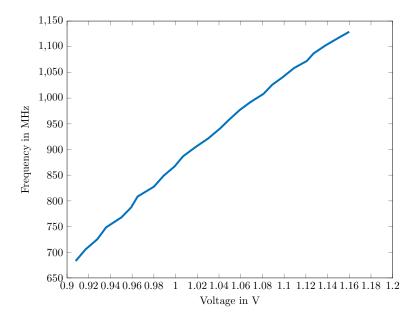

| 5.17 | Absolute frequency change when changing the FPGA voltage          | 91 |

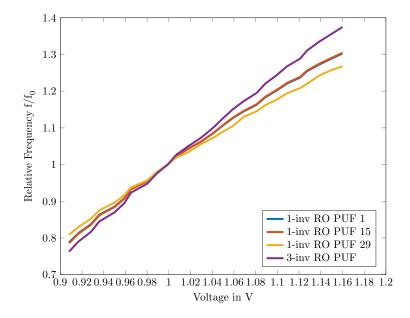

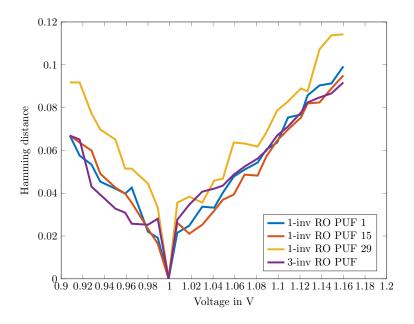

| 5.18 | Relative frequency change when changing the FPGA voltage          | 92 |

| 5.19 | Intra-device HD when changing the FPGA voltage                    | 92 |

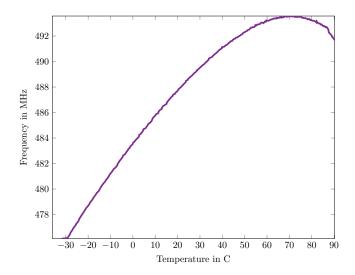

| 5.20 | Absolute frequency change when changing ambient temperature       | 93 |

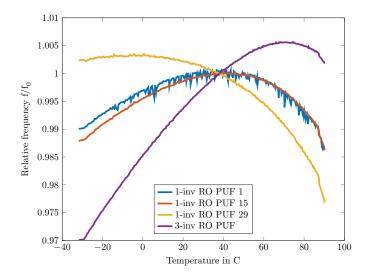

| 5.21 | Relative frequency change when changing ambient temperature       | 94 |

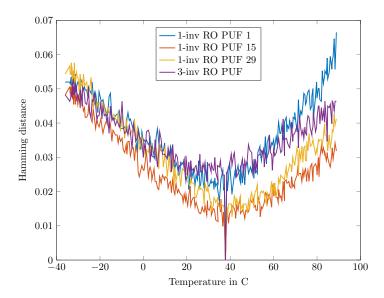

| 5.22 | Intra-device HD when changing the ambient temperature             | 95 |

| Ll | IST O | F FIGURES            |  |  |  |  |  |  |  |  |  |  |  | xiii |

|----|-------|----------------------|--|--|--|--|--|--|--|--|--|--|--|------|

|    | 6.1   | SoC enrollment       |  |  |  |  |  |  |  |  |  |  |  | 102  |

|    | 6.2   | SoC boot procedure   |  |  |  |  |  |  |  |  |  |  |  | 103  |

|    | 6.3   | SoC boot procedure   |  |  |  |  |  |  |  |  |  |  |  | 104  |

|    | 6.4   | IP storage procedure |  |  |  |  |  |  |  |  |  |  |  | 105  |

## List of Tables

| 2.1        | Notation symbols used for the measurement data                                                   | 7   |

|------------|--------------------------------------------------------------------------------------------------|-----|

| 3.1<br>3.2 | Resource utilization of a PUF design using 4272 RO PUFs Inter-device HD between each PUF outputs |     |

| 4.1        | Configuration of 48 reconfigurable PUF implementations                                           | 56  |

| 5.1        | Effects of different stress types on the frequency of ROs                                        | 78  |

| 6.1        | Comparison of implementations of key generation schemes                                          | 100 |

### List of Abbreviations

**AES** Advanced Encryption Standard

**ASIC** Application-Specific Integrated Circuit

**BBRAM** Battery Backed RAM

**CA** Certificate Authority

CAN Controller Area Network

CLB Configurable Logic Block

CMOS Complementary Metal-Oxide-Semiconductor

CTW Context Tree Weighting

**DES** Data Encryption Standard

**DFF** Data Flip-Flop

**DSC** Differential Sequence Coding

**ECC** Error Correcting Code

**ECDH** Elliptic Curve Diffie–Hellman

**ECU** Electrical Control Unit

**EM** Electro-migration

**EMI** Electromagnetic Interference

**FF** Flip-Flop

FHD Fractional Hamming Distance

FHW Fractional Hamming Weight

FPGA Field-Programmable Gate Array

GMC Generalized Multiple Concatenated Code

**HCI** Hot Carrier Injection

**HD** Hamming Distance

**HDL** Hardware Description Language

**HKMG** High- $\kappa$  Metal Gate

HMAC Keyed-Hash Message Authentication Code

**HW** Hamming Weight

**IBS** Index-Based Syndrome

IC Integrated Circuit

ICAP Internal Configuration Access Port

IP Intellectual Property

JEDEC Joint Electron Device Engineering Council

**LUT** Lookup Table

MAC Message Authentication Code

NIST National Institute of Standards and Technology

NMOS N-channel MOSFET

**MOSFET** Metal–Oxide–Semiconductor Field-Effect Transistor

**NBTI** Negative-Bias Temperature Instability

mux Multiplexer

**PBTI** Positive-Bias Temperature Instability

PCA Principal Component Analysis

PCAP Processor Configuration Access Port

**PGP** Pretty Good Privacy

PKI Public Key Infrastructure

PL Programmable Logic

PLD Programmable Logic Device

PMOS P-channel MOSFET

PR Partial Reconfiguration

PRD Partial Reconfiguration Design

PRNG Pseudorandom Number Generator

PROM Programmable Read-Only Memory

**PS** Processor System

PUF Physical Unclonable Function

**RM** Reed-Muller-Code

**RNG** Random-Number Generator

RO Ring Oscillator

SCA Side Channel Attack

**SM** Security Module

SoC System-on-Chip

SRAM Static Random-Access Memory

TDDB Time-Dependent Dielectric Breakdown

**TFF** Toggle Flip-Flop

TI Texas Instruments

## CHAPTER 1

#### Introduction

Our modern society is highly characterized by an increasing number of connected electronic devices in areas such as industry 4.0, smart homes, smartphones, and connected cars. The amount of those devices, the transmitted data, and the complexity increases tremendously every year. We rely more and more on the flawless, safe, and secure operation of these devices. But the connectivity of these devices also opens up many possible gateways for adversaries and makes them an interesting target. Furthermore, they potentially carry a lot of sensitive information while being run in an untrusted environment. Therefore, Intellectual Property (IP) and data privacy protection are major requirements for many companies such as IP vendors and manufacturers.

Information security has four main concepts to protect the communication and storage of information:

- 1. **Confidentiality** ensures that information is not available to unauthorized entities. This security goal is mostly achieved by using encryption of the data, where the encryption and/or decryption is only made possible to authorized entities using cryptographic keys.

- 2. **Integrity** refers to the absence of any data corruption for the whole life-cycle. Data can be manipulated or corrupted both when stored locally or when using a communication channel. A checksum is mostly used to meet this security goal.

- 3. **Authenticity** is the assurance that the identity of a subject is the identity claimed or the communicated information is from the source it claims to be from. Authenticity highly relies on integrity. Any manipulation or corruption of authenticated information and therefore

the tampering of its integrity – should be detected. The proof of authenticity can be made by something that is known (e.g. a password), something you have (e.g. a smartcard), or something you are (e.g. biometrics). Physical Unclonable Functions (PUFs) in particular make use of the latter, as intrinsic information is used. In secure communication, Message Authentication Codes (MACs) and electronic signatures based on Public Key Infrastructures (PKIs) are used to authenticate information and identities.

4. Availability refers to the ability to access information whenever it is needed. Systems that store and process information and communication channels have to function correctly at any point in time. Apart from random faults, common attack vectors are denial-of-service attacks.

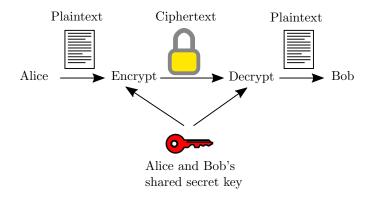

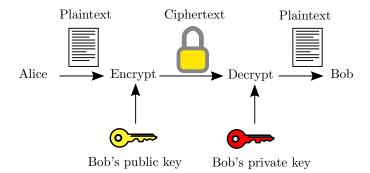

To protect both carried and transmitted information, cryptography relies on a secret key that has to be brought into and stored inside the system. The key can be used in a symmetric encryption, i.e., both sides are using the same key, to ensure confidentiality of the data. Another possibility is to use it in an asymmetric way with public and private key pairs to ensure integrity, authenticity, and/or confidentiality of the data. This makes knowledge of the cryptographic key an interesting target for adversaries.

The secret key is mostly stored in a non-volatile memory, e.g., flash memory or fuses. Flash memory, however, has the downside of being hard to integrate in modern Complementary Metal-Oxide-Semiconductor (CMOS) processes [WH11, Ini08, Che06]. Fuses on the other side are potentially susceptible to readout by decapsulation and optical analyses. Furthermore, a key management infrastructure is needed, as the key has to be brought into the device. If global master keys are used, losing it on one device would have an impact on every device. Storing a device specific key requires a key management, i.e., they have to be individualized, stored on the device during an enrollment phase, and potentially stored centralized as well. This makes the whole system less flexible and harder to maintain.

PUFs are using a new approach to create a device unique fingerprint or cryptographic key for authenticity, integrity, and confidentiality [PRTG02, GCvDD02, SD07]. The sources of randomness are the unpredictable variations during the manufacturing of Integrated Circuits (ICs). These functions are easy to evaluate, but hard to predict. It should be practically impossible to duplicate them. There is a wide range of types of PUFs, e.g., electronic PUFs, silicon PUFs, and surface PUFs. The idea was introduced by Pappu et al. [PRTG02] as the physical one-way function using an optical system. Nowadays, they are primarily used on ICs. The two mainly used types of PUFs are the delay-based and the memory-based PUF. The latter uses the unpredictable settle state of uninitialized digital memories like Static Random-Access Memorys (SRAMs) [GKST07, HBF09], flip-flops [MTV08],

or latches [SHO08]. Delay-based PUFs rely on the delay variations of routing and logic resources directly. One method to do this is with the arbiter PUF, which introduces a race condition between two or more paths [LLG<sup>+</sup>04]. Frequency differences between two or more Ring Oscillators (ROs) are used by the RO PUF [GCvDD02, MS11].

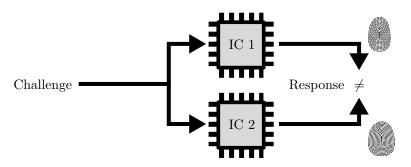

Figure 1.1: Schematic of basic PUF behavior.

Figure 1.1 shows the basic concept of a PUF. The same function is implemented on two different ICs. When those functions are challenged with the same input, each entity will produce a unique response output. It can be seen as a digital fingerprint and be used to authenticate devices or to generate unique cryptographic keys. Device aging and environmental influences such as voltage and temperature might have an influence on the PUF responses. The cryptographic keys have to withstand those variations and remain stable over the lifetime of the device.

The main advantage of silicon PUFs over embedded flash or fuses is their ability to be implemented using the same production process as the main circuit, which possibly saves cost for the device. Furthermore, when using reprogrammable hardware such as Field-Programmable Gate Arrays (FPGAs), the existing structures can be reused as PUFs. FPGAs are ICs that contain many programmable logic blocks, a complex routing system, and other dedicated logic elements. This gives them the ability to configure their hardware after manufacturing. The exact hardware implementation is not fixed as with Application-Specific Integrated Circuits (ASICs), but flexible. This makes them able to be updated in-field, which is important with the modern and fast developing technology. They are an interesting alternative in many modern applications, especially where the quantities are not high enough to justify an ASIC or where the flexibility and updatability is needed. One way to implement PUFs on FPGAs is explained and analyzed in chapter 3.

Most modern FPGAs already contain security features. Unfortunately, most of them are already broken by Side Channel Attacks (SCAs) [MKP11, MBKP11, MKP12, SW12, MOPS13]. SCAs are modern attacks that use information gained by observing the behavior of the physical implementation

of a cryptosystem. This ranges from timing, power consumption, sound, or electromagnetic emanation. Many countermeasures against SCAs are covered by patents. PUFs on the other hand offer a new possibility to implement own cryptographic functions that rely on intrinsic keys.

Implementing PUFs on FPGAs is very costly in terms of resources, as later shown in this thesis. Because the hardware has to be flexible, many resources are wasted by exclusively using them for the implementation of PUFs. Therefore, they are not affordable in most real world scenarios. In chapter 4, a new way to use PUFs more area efficiently on FPGAs is introduced. Instead of using just one PUF on a logic block of an FPGA, multiple PUFs are loaded on the same logic block in this work. By using modern FPGAs with Partial Reconfiguration (PR), the area can be reused. This way, more parts of the complex logic and routing system are used as entropy sources. Due to the reuse of resources, correlation between the PUFs might occur and lower the entropy of the PUF output. Therefore, analysis of the entropy is a main focus in that chapter.

Stability of the generated key is crucial for the usability of PUFs. This stands in contrast to challenge-response systems, where single bit flips are not fatal, as they can just be ignored. Both reversible and irreversible variations can alter the behavior of a PUF. Environmental conditions such as voltage and temperature are reversible variations. The effect of those altered conditions usually disappear once the cause is withdrawn. Device aging on the other hand is an irreversible variation that leads to a permanently changed behavior. The effects of aging on RO-based PUFs on an FPGA are analyzed in chapter 5. Voltage, temperature, and accelerated aging experiments on an FPGA using a climate chamber were done for almost one year. The results are then compared to the effects of reversible environmental conditions.

The generated keys can be used on modern SoCs in many different ways. To give an outlook about the possibilities of PUFs in securing a device and communication, a PUF-based key generation scheme and a security module using the FPGA and processor part of an SoC is presented in chapter 6. The key is generated solely on the FPGA and stays inside the FPGA. This makes it obsolete to get secret keys in or out of the FPGA. A public key can be used to communicate with the outside, whereas the private key is kept inside the device. The system is presented in detail and an estimation of resource usage on FPGAs is given.

## CHAPTER 2

Background

This chapter provides background information about the main subjects of this thesis: FPGAs, PUFs, and cryptography.

In the first section 2.1, the basic PUF concepts, a brief overview on the history and the quality measures of PUFs are explained. A selection of important PUF types is presented in section 2.2. The methods of generating cryptographic keys by using PUFs are explained in section 2.3. A short introduction on FPGAs is given in section 2.4, as the PUFs will be implemented on that platform in this thesis. The basic concepts of cryptographic algorithms will be explained in section 2.5.

### 2.1 PUF Concepts

The definitions of PUFs are not consistent in literature. To have a common understanding for this thesis, the definitions will be explained in this section. A PUF in general is a function that uses production tolerances to generate a device specific response. To use the response in a digital system and make it comparable, the response is usually in a binary form after post processing. The basic principle can be explained with the three words:

Physical A physical entity embodied in a physical structure.

Unclonable The exact implementation cannot be duplicated. However, it might still be possible to model the PUF using, e.g., machine learning.

**Function** In a mathematical sense, an input is mapped to an output. This is not true for PUFs, as they are usually noisy. Error correction has to

be used to replicate the original output. Furthermore most PUFs ('weak PUFs') are used with a fixed input to, e.g., generate a fixed cryptographic key. Maes et. al propose the term *probabilistic function* as more correct, as an input is mapped with a certain probability to an output value, due to noise.

#### **2.1.1** History

The basic idea of a PUF, without using that exact term, was already introduced by Bauder in 1983 [Bau83] and Simmons in 1991 [Sim91]. Simmons proposed an optical PUF that used reflection patterns to identify strategic arms in arms control treaties. Bauder used a paper PUF for anticounterfeiting of currencies. Posch et al. used an active coating to protect devices [Pos98]. In 2001, Pappu proposed an optical PUF construction and defined the general concept of PUFs [PRTG02]. However, he used the term physical one-way function. One year later Gassend et al. introduced the silicon PUF [GCvDD02] and used the term physical unclonable function for the first time. This started the research on many different types of PUFs, with a large focus on silicon PUFs. Older concepts were transformed to the new definition of PUFs, new concepts developed and combined.

Companies specialized on PUFs were established shortly after, such as Verayo in 2005 or Intrinsic ID in 2008.

#### 2.1.2 Weak and Strong PUFs

PUFs can be classified by their challenge-response behavior. As explained in the introduction, a PUF usually takes a challenge and answers with a response. A PUF is called a strong PUF if an attacker is unable to guess any response to an unused challenge during the lifetime of a device. This requires a very large challenge-response set to make it impossible for an attacker to just learn all of the pairs. Furthermore, it must be impossible for an attacker to build an accurate model of the PUF behavior. Many strong PUF designs fail the latter requirement, as in those cases, machine learning algorithms are able to model the PUF behavior.

A weak PUF is the term for any PUF that does not meet the requirements of a strong PUF. This can either mean that the PUF constructions were not appropriately designed or it was intentionally designed that way. Generating cryptographic keys is an example for the latter. This extreme case of just one challenge-response pair is not meant to communicate with another entity via challenge-response pairs. A fixed challenge is used to generate a device specific cryptographic key.

The sole purpose of a PUF in this thesis is the generation of a cryptographic key. Hence, only weak PUF constructions will be used and the challenge-response constructions will not be used. This has the advantage

| Symbol         | Description                                                  |

|----------------|--------------------------------------------------------------|

| $\overline{p}$ | Index of a PUF bit within response vector. $1 \le p \le P$   |

| P              | Length of PUF response vector                                |

| d              | Index of a device. $1 \le d \le D$                           |

| D              | Number of devices                                            |

| m              | Index of a measurement at a specific time and                |

|                | environmental condition. $1 \leq m \leq M$                   |

| M              | Number of measurements                                       |

| $r_{p,d,m}$    | Binary response bit $p$ of device $d$ within measurement $m$ |

| $R_{d,m}$      | Response vector of device $d$ at measurement $m$             |

| •              | with $R_{d,m} = \{0,1\}^P$                                   |

Table 2.1: Notation symbols used for the measurement data.

that any attacks on the strong PUF constructions do not apply to the systems used in this work.

#### 2.1.3 Quality Measures

All PUF constructions share a number of specific properties. The quality of a PUF can be measured in different ways. Distinct sets of properties such as randomness, steadiness, correctness, diffuseness, uniqueness, uniformity, or reliability are used in sometimes different definitions throughout the research on PUFs [HYKS10, SHO08, MCMS10, MGS13]. As there is no standard model that all researchers agree on, the terminology used in this work will be explained in this section.

#### Organization of PUF response data

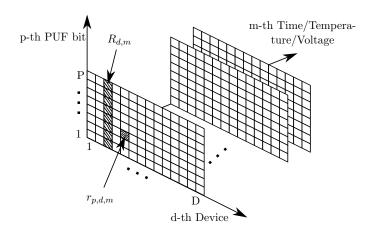

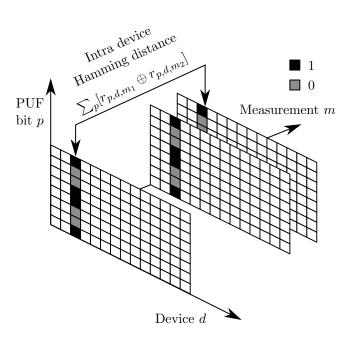

The responses of a PUF can be characterized by many different variables. Figure 2.1 shows the dimensions used in this work. The response is assumed to be in a binary form, i.e., the post-processing of analog data will not be covered in this section. Additionally, the notation symbols used in this work are summarized in Table 2.1.

When using a weak PUF for cryptographic key generation, a response vector R with a certain bit length P is needed. Therefore, P PUF structures, each returning a single bit p, have to be implemented. This is represented by the vertical axis. Each of those PUFs is situated on a different location of the device in case of the weak PUF. In a strong PUF scenario it could also be a set of challenge-response pairs.

The index of a device d, with  $1 \le d \le D$ , that the PUF will be used on is represented by the d-axis. Each device should generate a unique cryptographic key, i.e., the PUF response should be unique for every device. The

Figure 2.1: Organization of PUF response data. The three dimensions are: 1) PUF bit position within a PUF response vector, 2) the device on which the PUF is used, and 3) the date of the measurement and the corresponding environmental conditions such as voltage and temperature.

responses are measured for D different devices. Each device should have a unique P-bit wide PUF response.

The stability of a PUF response is very important. When they are used to generate cryptographic keys, a single bit flip could corrupt the whole key. To measure the stability of a PUF response, it will be measured multiple times and be compared to the initial measurement. These measurements are represented by the third m-axis. As the device will be used under real-world conditions, a variation of environmental conditions such as temperature and voltage, as well as device aging will be expected. The m-axis represents a set of M different time, temperature, and voltage conditions that the device will be tested with.

The PUF responses have a vector length of P bit. The response of a PUF system with P PUF bits on device d at condition m is defined as:

$$R_{d,m} = r_{1,d,m} || r_{2,d,m} || \dots || r_{P,d,m}$$

(2.1)

#### Uniformity

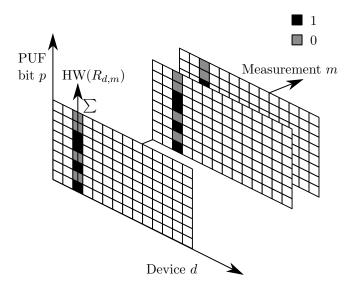

Each PUF system on a device returns a P bit wide vector. Uniformity defines the proportion of ones and zeros in this vector. An ideal, unbiased, statistically random system returns the same amount of ones and zeros. To measure this, the Hamming Weight (HW) is used. To calculate the HW of the response on device d at condition m, all ones of the P bit wide vector

9

are added up:

$$HW(R_{d,m}) = \sum_{p=1}^{P} (r_{p,d,m})$$

(2.2)

Figure 2.2: Uniformity of a PUF response vector. The distribution of zeros and ones show a bias towards one of those values. The HW is used to measure the uniformity by adding up each single PUF bit within a complete response.

Figure 2.2 shows an unbiased PUF response that produces the same amount of zeros and ones. This equals a HW of P/2 for a P bit wide vector. To be independent from the bit width of the response, the HW can be divided by the number of bits to get the Fractional Hamming Weight (FHW):

$$FHW(R_{d,m}) = \frac{HW(R_{d,m})}{P}$$

(2.3)

The ideal distribution is a FHW of  $\frac{P}{2}/P = 0.5$ . Every PUF response vector on any device, at any time, voltage, and/or temperature should always be close to this ideal value to guarantee a uniform distribution of ones

and zeros. This ensures that no fundamental design flaw was made when constructing the PUFs.

#### Uniqueness

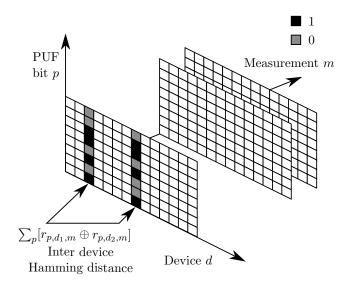

Figure 2.3: Uniqueness of a PUF response compared to other devices. The HD is used to measure the inter-device differences in the responses by calculating the xor of both vectors. Ideally, the two vectors differ in exactly half of their PUF bits.

As the PUFs are used to generate a device unique key, the statistical independence from PUFs on one device to the same PUF on another device has to be tested. This also makes it possible to distinguish chips of the same type from each other, just by using production tolerances. To compare two bit vectors with each other, the Hamming Distance (HD) will be used. The HD is the number of positions in which two PUF responses of the same implementation on two distinct devices,  $d_1$  and  $d_2$ , are different:

$$HD(r_{d_1,m}, r_{d_2,m}) = \sum_{p=1}^{P} [r_{p,d_1,m} \oplus r_{p,d_2,m}]$$

(2.4)

$$= \operatorname{HW}[R_{d_1,m} \oplus R_{d_2,m}] \tag{2.5}$$

Ideally the two vectors should differ in half of their bits to assume uncorrelated responses, i.e., the HD should be m/2. To be independent from

the bit length we divide the HD by the bit length P of the response to get the Fractional Hamming Distance (FHD):

$$FHD(R_{d_1,m}, R_{d_2,m}) = \frac{HD(R_{d_1,m}, R_{d_2,m})}{P}$$

(2.6)

The FHD should be close to the ideal value of  $\frac{P}{2}/P = 0.5$ .

As the results of different devices are compared with each other, this is commonly referred to as inter-device HD.

The uniqueness property takes all possible  $\binom{D}{2} = \frac{D(D-1)}{2}$  combinations of inter-device HDs into consideration. It can be calculated as the normalized sum of all possible inter-device HD combinations:

$$U = \frac{2}{D(D-1)} \frac{1}{P} \sum_{d_1=1}^{D-1} \sum_{d_2=d_1+1}^{D} \sum_{p=1}^{P} (r_{p,d_1,m} \oplus r_{p,d_2,m})$$

(2.7)

However, the inter-device HD can only be seen as a necessary condition to assume unique and uncorrelated results. Throughout this thesis, more approaches to rate the uniqueness of a PUF response will be presented, such as correlation analyses and compression algorithms.

#### Reliability

The stability of a PUF response throughout its lifetime and under all specified environmental conditions of the device is very important. Every bit flip of the response could corrupt a cryptographic key, the challenge response pair, or make the error correction harder. To estimate the stability of PUF responses, the HD is used again as shown in Figure 2.4.

The cryptographic key or the challenge-response pairs of a PUF will be defined under the initial characterization condition  $m_1$ . Each subsequent measurement of the PUF will be done under a different condition, due to aging, temperature, or voltage variations. It should however, still result in the same output over the lifetime of a device. As the responses of the same device are compared with each other, the HD for reliability is commonly referred to as intra-device HD. The HD between an initial measurement at condition  $m_1$  to a subsequent measurement at  $m_2$  can be calculated to:

Figure 2.4: The reliability of a PUF under different environmental conditions and age of the device. The intra-device HD is used to measure the occurrence of bit-flips when repeatedly measuring the same PUF on the same device and comparing it to the initial measurement.

$$HD(R_{d,m_1}, R_{d,m_2}) = \sum_{p=1}^{P} r_{p,d,m_1} \oplus r_{p,d,m_2}$$

(2.8)

Accordingly the intra-device FHD can be calculated to:

$$FHD(R_{d,m_1}, R_{d,m_2}) = \frac{HD(R_{d,m_1}, R_{d,m_2})}{P}$$

(2.9)

As the goal is the absence of any bit-flips within the responses on the same device, the ideal intra-device HD is zero.

2.2. PUF TYPES 13

#### Bit alias

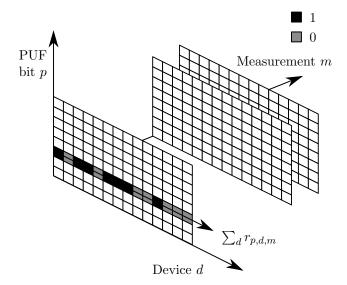

While uniformity refers to the bit distribution within the response on one device, the bit alias refers to the distribution of ones and zeros of the same single PUF output bit on different devices. This can be used to identify a badly implemented RO pair within the whole response. A bad bit alias automatically leads to a bad uniqueness as those PUF bits will not differ when measuring the inter-device HD. The bit alias of a PUF bit measured on D devices can be calculated to:

$$HW(R_{p,m}) = \sum_{d=1}^{D} [r_{p,d,m}]$$

(2.10)

Accordingly, the FHW can be calculated to:

$$FHW(R_{p,m}) = \frac{HW(R_{p,m})}{D} \tag{2.11}$$

The ideal bit alias is an equal distribution between ones and zeros, which refers to a FHW of 0.5.

## 2.2 PUF Types

The idea of PUFs is to use intrinsic physical properties to authenticate devices, objects, or systems. This concept is not new, as it has been already widely used with humans, by using, e.g., the fingerprint. A human fingerprint is an intrinsic feature that is given at birth and is (almost) unique for every person. It is easy to measure a fingerprint, but hard to permanently clone a fingerprint to another human being. This basic idea has been transferred to a wide range of non-electrical, electrical, and silicon devices. They share the requirement that they are easy to make, but hard to duplicate or control. A selection of PUF types will be presented in this section.

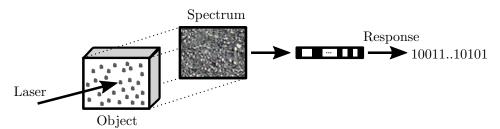

#### 2.2.1 Optical PUF

PUFs were first mentioned by Pappu [PRTG02] in 2002 as a physical one-way function (POWF). Figure 2.6 shows the construction of such a function. A helium—neon laser is used to radiate a token, in this case a glass sphere.

Figure 2.5: Bit alias of a single PUF bit over all measured devices. The bit alias is measured using the HW, i.e., the sum of a single PUF bit over all devices.

The resulting speckle patterns are recorded two-dimensionally. A Gabor transform was used to generate a 2400-bit key.

Figure 2.6: Schematic of a laser PUF. The laser hits an object and the resulting spectrum is recorded and converted to a binary response.

The exact orientation of the laser was used to generate different challenges for the function. The challenge orientations and the resulting Gabor hashes were recorded in a database during an enrollment phase. Whenever the device was needed to be verified, the challenge orientation was provided and the response requested. The response was then compared with the one stored in the database to authenticate the device.

Another example for optical PUFs are paper PUFs [CMK05, BSQ10, Kir04]. A variety of possibilities to use paper PUFs exist. An easy way is by scanning the package of a product after manufacturing. Later, the authenticity of the product can be verified by scanning the surface again and comparing it with the initially stored value. This can be interesting for

2.2. PUF TYPES 15

a low cost counterfeit protection for products that are counterfeited on a regular basis such as pharmaceutical products.

#### 2.2.2 Silicon PUFs

The main focus of research and usage of PUFs is aimed towards silicon PUFs as an intrinsic PUF on ICs. The source of randomness are the variations of digital delays due to production tolerances. The two mainly used types of intrinsic PUFs are the delay-based and the memory-based PUFs. The latter use the unpredictable settle state of uninitialized digital memories like SRAMs [GKST07, HBF09], flip-flops [MTV08], or latches [SHO08]. Delay-based PUFs rely on the delay variations of routing and logic resources directly. One method to do this is the arbiter PUF, which introduces a race condition between two or more paths [LLG<sup>+</sup>04]. Frequency differences between two or more ring oscillators are used by the ROPUF [GCvDD02, MS11].

Three mainly used PUFs will be presented in detail: the ROPUF, arbiter PUF, and the SRAM PUF.

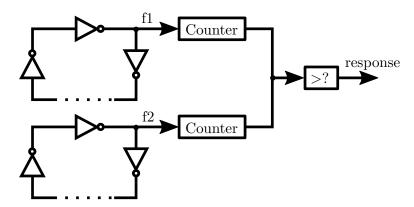

#### RO PUFs

ROs were among the first silicon-based PUFs that were proposed to extract entropy from ICs. As shown in Figure 2.7, an odd number of inverters are connected in a ring. This structure will begin to oscillate with a certain frequency  $f_x$  if the delay is sufficiently large. The exact frequency of this ring depends on production tolerances of the logic gates and the delay lines. The exact same implementation on two different locations of the chip or on the same location on two different chips will result in slightly distinct frequencies.

Figure 2.7: Schematic of a RO PUF. The frequency of two ROs is counted and compared with each other to generate one output bit.

As shown in Figure 2.7, this fact can be used to generate bits. Two identical implementations of ROs will oscillate with the frequencies  $f_1$  and  $f_2$  [SD07]. These frequencies will be slightly different due to the production tolerances. Two counters are started and ended at the same time to count the amount of oscillations of  $f_1$  and  $f_2$ . The results will be compared and a bit generated according to equation 2.12.

$$r(f_i, f_{i+1}) = \begin{cases} 1, & \text{if } f_i > f_{i+1} \\ 0, & \text{otherwise} \end{cases}$$

(2.12)

Using this technique, k-ROs will produce a  $\frac{k}{2}$  bit long response. Other techniques allow the creation of more bits, but they would be correlated, i.e., statistically dependent. By comparing every RO with each other, a total of  $\frac{k}{2} = \frac{k \cdot (k-1)}{2}$  combinations is possible. This however produces correlated results. A very fast or very slow RO will be dominant and effectively produce a lot of 1 or 0 bits, that are quickly predictable. If used in the conventional way of using each RO just for one bit generation, then ROs achieve one of the best statistical behaviors [KKR<sup>+</sup>12].

#### **Arbiter PUF**

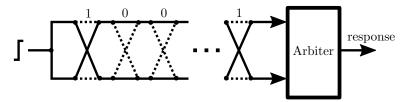

Arbiter PUFs are delay-based silicon PUFs. They were first introduced by Gassend et. al [GLC<sup>+</sup>04]. Instead of using frequencies, a race condition is introduced as a measure. Figure 2.8 shows the working principle of an arbiter PUF. The signal starting from the left is racing on two different paths. The Multiplexers (muxes) at the interconnects can either cross the signal paths or leave them straight. They are used to challenge the PUFs. The arbiter circuit at the end of the signal path decides which path was faster, i.e., which signal arrived at first, and produces an according binary response.

Figure 2.8: Schematic of an arbiter PUF. A signal is racing on two different paths that can be altered by using muxes. An arbiter circuit decides which one of the paths was faster and generates a response bit accordingly.

It is crucial that all paths are designed in perfect symmetry. Unequal length of paths will bias the PUF and lower the entropy dramatically, as the production tolerances are not the main factor of path differences. This makes 2.2. PUF TYPES 17

their implementation on FPGAs very hard. The exact internal structures of FPGAs are unknown. Therefore, ensuring an absolute identical symmetric implementation is difficult. Another problem occurs when the difference in delay between the two paths, caused by the random silicon process, is very small. This leads either to metastability when both signals arrive at the same time, or an unstable behavior.

When using the arbiter PUF as a strong PUF it is very prone to modeling attacks. The  $2^n$  possible challenges for n muxes have a linear correlation. By using same paths for different challenges, the entropy is lowered. Dominant paths, either very slow or very fast, highly influence the result of multiple challenges. By attacking the challenge-response pairs with machine learning, the response to a given challenge can be calculated without knowing the exact PUF structure. This violates the rule that a PUF should be unclonable.

#### **SRAM PUF**

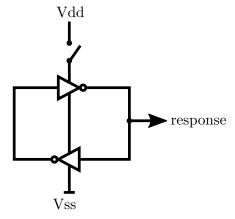

An SRAM is a silicon memory that uses a bistable circuit to store bits. The CMOS implementation is typically built with six transistors. As shown in Figure 2.9, two cross-coupled inverters form the memory cell. Two additional transistors are used for write and read operations. It is considered a volatile memory, as it loses its information after a power down.

Figure 2.9: Schematic of an SRAM PUF. The cross coupled inverters act as a memory cell and can store information. In case of a PUF, the initial state of the SRAM is used as a response.

The usage of an SRAM as a PUF was first proposed by Guajardo et al. [GKST07]. The bistable settle state of the SRAM is used as a PUF function. Upon enabling the supply voltage, the SRAM will be in a metastable state. As the paths are designed symmetrically, only production tolerances will define the 'stronger' path. This will determine the outcome bit of the

SRAM, i.e., the settle state. As the settle state is unique for every cell, it can be used as a PUF, as long as the SRAM cells are not pre-loaded with an initial value. Unfortunately, the SRAM cells of most FPGAs are preloaded by the hardware and therefore not usable as a PUF. Some research [SGB+10, WG14] on using this method, especially on older devices, exist but will not be covered in this thesis.

### 2.3 PUF-based Key Generation

Traditional secure key generation had two major premises: a) a good source of randomness to generate unique secure keys and b) a secure non-volatile memory to store the keys in a way that they cannot be read-out by an unauthorized third party. Especially the demand for secure storage becomes increasingly problematic. Embedded flash will be harder and especially costlier to implement in current and future feature sizes. PUFs are a way to fulfill both requirements at once. By using the device unique randomness, a unique key can be generated, and it does not have to be stored, as it can be reliably reproduced during its lifetime.

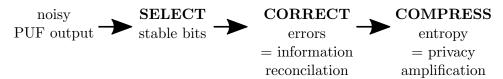

The PUF output bits cannot be directly used as a cryptographic key. Due to instability of the read-outs, bit flips will occur. They can be additionally enhanced by reversible and irreversible variations. A post-processing is necessary to generate stable, high-entropy cryptographic keys under different environmental conditions and during the complete lifetime of a device. Helper data algorithms are used to generate reliable keys. As shown in Figure 2.10, this process can be separated in three steps: select, correct, and compress [DGSV14].

Figure 2.10: The basic steps of generating cryptographic keys from noisy PUF responses.

#### 2.3.1 Select

In this first step only the most reliable bits can be selected. This makes the overall PUF response more stable and robust to environmental changes. When the frequency difference between two ROs is not high enough, a bit flip is very likely. Such PUF bits can be ignored in this first step. The information about the used and unused PUF bits is stored in helper data.

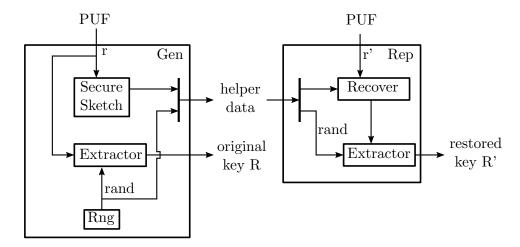

#### 2.3.2 Correct

The second step is error-correction. As the PUF response bits are unstable, this step tries to correct all possible deviations from the initially measured PUF output. Therefore, helper data is generated during a generation step to restore the initial PUF output. This should always lead to a stable error corrected PUF output, that can be used to generate a reliable cryptographic key. Commonly used error-correction schemes are secure sketches [DRS04, DGSV14] like syndrome coding or code-offset. A secure sketch consists of two procedures: Sketch and Recover. Sketching takes a PUF input r and returns a bit vector w. Recover on the other hand takes a noisy PUF output r' and the bit vector w and returns a r'', where the goal is that r = r''. The latter is called the correctness property. A second property of secure sketches is the security property. This ensures that if r contains a min-entropy of m, that an attacker cannot recover r with a probability grater than  $2^{-m}$ .

Two examples of secure sketches are the code-offset construction and the syndrome construction. The sketching procedure of the latter calculates a helper data string w as a syndrome to  $w := r \cdot H^T$ . In the recover procedure a syndrome s is calculated from the noisy PUF output to:  $s := r' \cdot H^T \oplus w$ . The syndrome decoder is then able to find an error word e such that  $s = e \cdot H^T$ , with the HW of e being within the correctable error margin. Using the error, the original PUF output can be recovered to  $r := r' \oplus e$ . Common choices for syndrome constructions are BCH codes [MVHV12], repetition codes [MTV09b], and Reed-Muller codes [MTV09b].

In the code-offset construction [DRS04, MTV09b, BGS<sup>+</sup>08, MTV09a, vdLSHT10] the sketching procedure XORs a random codeword c with the PUF response r to get  $w := r \oplus c$ . The recover procedure first calculates a noisy codeword from the noisy PUF output:  $c' := r' \oplus w$  and then uses an Error Correcting Code (ECC) to recover the original codeword c.

A fuzzy extractor can be seen as a generalization of a secure sketch and a strong extractor. As PUF outputs are usually not completely uniformly random, a certain min-entropy is guaranteed by a strong extractor. A fuzzy extractor extracts a stable output from a fuzzy source in a generation phase and reproduction phase. Figure 2.11 shows the schematic of a basic fuzzy extractor. At first the generation step is executed. A secure sketch is used to generate a helper data string from the initial PUF response. Accordingly, the response is used in a secure extractor with a random salt to generate the original key R. The random number is stored together with the helper data string as the helper data. The PUF system is now ready to be shipped.

Whenever the PUF system is used in the field, the goal is to regenerate the same key R. Therefore, the noisy PUF measurement r' is used together with the helper data string to regenerate the original response r. Then the regenerated original response is used together with the same random number salt in the extractor again to recover the key R'.

Figure 2.11: Schematic of a fuzzy extractor used for extracting high-entropy and stable keys from a noisy bit source. The generation phase on the left side is performed once to generate the corresponding helper data for the device and PUF. The helper data is then used together with the noisy PUF response to generate a stable key R in-field.

Traditionally, a fixed bit error probability is assumed for many silicon-based PUF responses. This approach however is very pessimistic as many PUF response bits are very robust. A soft-decision [MTV09a, MTV09b] secure sketch takes this into account. In these sketches every PUF response bit has its own error probability and takes an individual likelihood into account. The error correcting capabilities can be improved in comparison to hard-decision sketches. The main advantage is that less PUF bits are needed for the same failure rate and entropy level. On the other hand the decoding effort raises dramatically. When using RO PUFs, the frequency difference between two compared ROs can be used as an estimate for its bit error probability. A commonly used algorithm is a soft-decision maximum-likelihood decoding (SDML), as it offers a good performance, or generalized multiple concatenated (GMC) codes that use, e.g., recursively split Reed-Muller codes.

On the other hand, security criticism was recently raised by Delvaux et al. [DGSV14], that the leakage of soft-decision coding is underestimated. Powerful divide-and-conquer manipulation attacks are presented on some of the used soft-decision coding schemes.

Other presented key-generation algorithms are Index-Based Syndrome (IBS) [YD10] coding, Complementary-IBS coding [HMSS12, HDSMS12], or Differential Sequence Coding (DSC) [HWRL+13, HS14, HYS16]. IBS is a variant of the 1-out-of-n selection, where an index to the most reliable bit matching a codeword is stored. The index is used during reconstruction to select the bits again and reconstruct the codeword. The C-IBS is an

2.4. FPGA 21

extension of IBS, where not only the index to a PUF bit is stored as helper data, but also to complementary bits. This further increases the stability of the codeword. An ECCs is used to error correct the codeword and reproduce the key.

DSC is similiar to C-IBS, but in contrast to C-IBS, it has a fixed reliability and variable block size. A sequence of PUF outputs is searched for those outputs with an error probability under a predefined threshold. Unlike C-IBS, the block size is not fixed, but the end of one iteration provides the starting point for the next iteration of finding reliable bits.

#### 2.3.3 Compress

In this last step the entropy of a PUF response is compressed, as it is mostly not equal to its bit length. This can be both because of correlations between the PUF bits and possible leakage of the helper data. This step is also commonly referred to as privacy amplification. Most implementations use a lightweight hash algorithm like SPONGENT [MVHV12, HWRL+13] or the Toeplitz hash [BGS+08].

#### 2.4 FPGAs

FPGAs are ICs that are designed to be configured after manufacturing. The basic idea is to have a specific Hardware Description Language (HDL) that can be used to configure the circuit in-field. Programmable logic blocks on the FPGA can be configured as complex logic functions and memory elements can be used to store information. A complex routing system can be configured to route the signals throughout the FPGA. This section contains background information on the structures of modern FPGAs.

#### 2.4.1 Overview

FPGAs were developed from previously used Programmable Logic Devices (PLDs) and Programmable Read-Only Memorys (PROMs). In comparison to PLDs the logic blocks are much more complex. They contain memory elements such as Flip-Flops (FFs), and Lookup Tables (LUTs). Furthermore, the routing possibilities to connect different logic blocks with each other are enhanced. The leading companies pushing FPGAs were the 1983 founded Altera, and two years later in 1985 founded Xilinx. Both companies rely on SRAMs as the main building block of the LUTs. SRAMs are relatively cheap to manufacture, but require an external non-volatile memory to configure the logic blocks at start-up. Microsemi, 1985 founded as Actel, on the other hand relies on flash-based technology. The main advantage of flash-based FPGAs is that it is non-volatile and very robust against single-event upsets.

A recent trend is the combination of FPGAs with microcontrollers or microprocessors to a System-on-Chip (SoC). This allows a combination of flexible software solutions running on the processor and hardware accelerated implemented on the FPGA. Among the most popular devices are the Xilinx Zynq, Altera Cyclone, and MicroSemi's SmartFusion. In this thesis a Xilinx Zynq will be used, but the concepts presented are also transferable to other devices.

#### 2.4.2 Structure

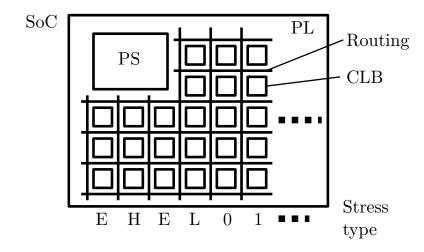

Figure 2.12: Schematic of a modern SoC with PS part and a PL part on the same chip. The right side of the figure shows the basic structure of a CLB containing LUTs, FFs, and a switch matrix.

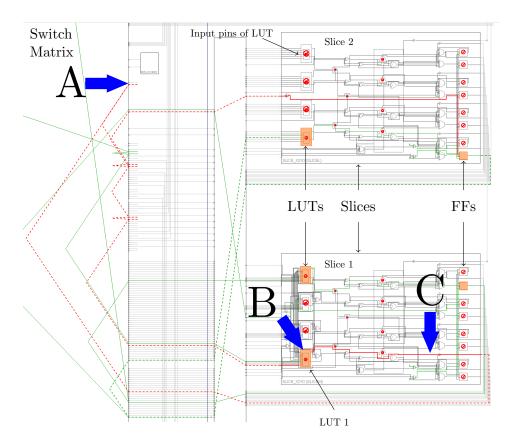

A schematic of the SoC used in this work is shown in Figure 2.12. The system consists of a hard-wired Processor System (PS) in the upper left part and a Programmable Logic (PL) part. The PL part of the system consists of many Configurable Logic Blocks (CLBs) and a complex routing system. The CLB is built up by several slices and a switch matrix that connects the slices to themselves and to the outside. A slice consists mainly of LUTs to implement logic functions, and FFs to store data. The Xilinx Zynq device, which is used in this work, has two slices per CLB. Each slice consists of four LUTs and eight FFs [Xil14b]. The LUTs can be used as either one 6 bit LUT, or two 5 bit LUTs.

Dynamic partial reconfiguration allows the FPGA part to be partly reconfigured during runtime, without interfering with the rest of the FPGA. This feature can be controlled by various interfaces, e.g., the Processor Configuration Access Port (PCAP) or the Internal Configuration Access Port (ICAP). In this work, we use the PCAP interface, that allows the PS to reconfigure the PL.

Figure 2.13 shows a commonly used implementation of a CLB using N-channel MOSFET (NMOS) pass transistors on an FPGA. This is the mainly

used implementation in modern devices as it consumes less area than using transmission gates [CB13]. Transmission gates on the other hand would have the advantage of providing a more stable signal level. Extra level restorer stages to refresh the signal level would not be needed. Chiasson and Betz [CB13] wrote an interesting work about the advantages of transmission gates on FPGAs and the current usage of pass transistors.

Figure 2.13: Simplified schematic of the implementation of a LUT on an FPGA.

The LUT values are stored in SRAM cells. In this work, 6 bit LUTs are used, i.e., 64 SRAM cells are needed to store the LUT information. The SRAM values of all LUTs are usually written when loading the configuration design of the FPGA from the external non-volatile memory. They do not change their values during runtime unless PR is used. The SRAM values propagate through a mux network that is controlled by the inputs I0 to I5 for a 6 bit LUT. For the sake of simplicity, extra buffer stages and level restorers, which are commonly found in real implementations, are left out in Figure 2.13. The usage of pass transistors is the reason why modern FPGAs have more NMOS than P-channel MOSFET (PMOS) transistors.

# 2.5 Cryptography

Cryptography is defined as the practice and study of writing and reading secret messages and codes. Two parties, e.g., Alice and Bob try to communicate with each other over an insecure channel. Active and passive third parties should be prevented from reading messages (confidentiality),

manipulating messages (integrity), claiming other identities (authenticity), or disturb the availability of information. Two different approaches to fulfill these requirements are symmetric and asymmetric cryptography. Both concepts will be explained briefly in the following subsections.

#### 2.5.1 Symmetric

Figure 2.14: Schematic of a symmetric key algorithm. Alice wants to send a secret message to Bob without a third party being able to read the information on the communication channel.

Figure 2.14 shows the basic concept of symmetric cryptography. Symmetric refers to the usage of the cryptographic key. A message has to be delivered securely from Alice to Bob. Alice uses a shared secret key to encrypt the plaintext. After receiving the ciphertext, Bob decrypts the message using the same shared secret key. The state-of-the-art symmetric cryptographic algorithm is Advanced Encryption Standard (AES). It is a block cipher that was developed by Joan Daemen and Vincent Rijmen as the successor of the Data Encryption Standard (DES). By using symmetric keys for encryption the confidentiality of data is ensured.

Another application purpose of symmetric keys are MACs. A MAC is a secure checksum that can be calculated using the plaintext and the symmetric key as input parameters. The MAC is sent together with the plain- or ciphertext to the receiver, which himself can calculate the MAC using the received text and the same symmetric key. The calculated MAC has to be the same as the received MAC. Only parties holding the symmetric key should be able to calculate a correct MAC to a given text. As long as the key is being kept secret between the participating parties, the authenticity and integrity of communicated information can be ensured.

Figure 2.15: Schematic of a public-key cryptography algorithm used for encryption of data.

#### 2.5.2 Asymmetric

Asymmetric key algorithms follow another approach. As shown in Figure 2.15, the keys used for encryption and decryption are different. The recipient of a message has a pair of keys: a private and a corresponding public key. In this case Bob has a private key, which he keeps secret and a public key, that he gives to Alice. Alice can use the public key to encrypt the plaintext. The ciphertext can only be decrypted by holders of the private key, which in this case is Bob. As long as Bob keeps his private key secret and Alice uses the correct public key, the confidentiality of the data is ensured.

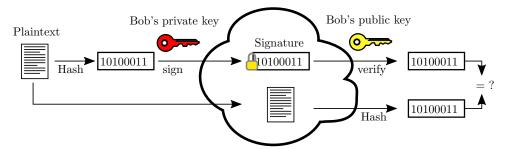

Figure 2.16: Schematic of public-key cryptography algorithm used for digital signatures.

Another possible use case of asymmetric ciphers are digital signatures as shown in Figure 2.16. The private key can be used to sign a message. By using the public key, this signature can be verified by any third party who has the corresponding public key. A valid signature, however, can only be calculated by the owner of the private key. This ensures authenticity and integrity of the data, as long as the private key is being kept secret and the correct public key is used.

In order to ensure the usage of the correct public keys, a PKI is needed.

The PKI can either be centralized with a trusted Certificate Authority (CA) certifying key pairs or be decentralized such as Pretty Good Privacy (PGP).

The state-of-the-art asymmetric algorithms are RSA and elliptic curve cryptography. RSA is named by its inventors Rivest, Shamir, and Adleman. It is based on the practical difficulty of factoring the product of two large prime numbers. Elliptic curve cryptography on the other, relies on the infeasibility of finding the discrete logarithm of random elliptic curve elements with respect to a publicly known base point. They play an integral role in modern authenticated communication, or to establish symmetric keys. Symmetric ciphers usually outperform the asymmetric algorithms, but don't offer the advantages of having two distinct keys.

# Implementing RO-based PUFs on FPGAs

The implementation of PUFs on FPGAs is already covered in many research papers. Most of them focus on gaining measurement data to show the properties of different PUF types. Very little research exists about efficiently implementing them on FPGAs. This chapter covers the question if an efficient implementation of RO-based PUFs on FPGAs is possible without using any partial reconfiguration. The experimental data from this chapter is later on used as a reference for quality measures and area efficiency.

The chapter is organized as follows: in section 3.1 a short introduction is given. Section 3.2 covers the theoretical aspects of implementing RO-based PUFs on FPGAs. In section 3.3 a design with 4272 ROs is implemented on a Xilinx Zynq device. The implemented design will be used and measured in section 3.4 to analyze the characteristics of the RO-based PUF with the focus on area, speed, and quality properties. In section 3.5 a conclusion is given with an outlook and motivation to the next chapter.

#### 3.1 Introduction

The SRAM cells on modern FPGAs are initialized at start-up and cannot be used as a PUF. As it is hard to implement exact symmetrical structures on FPGAs — which are needed for implementing own memory-based PUFs such as butterfly PUFs — the focus was set on delay-based PUFs. Because the arbiter PUF is susceptible to machine learning attacks [HMV12], RO-based PUFs will be used in this thesis. The main goal of this work is to create the bit source for a device unique key. Therefore, only PUFs with a fixed challenge are used, i.e., weak PUFs.

The RO PUFs were implemented on a Xilinx Zynq Z7C020. This device

uses CLBs with two slices each. Each slice contains four LUTs. Each LUT can be used as either one 6 bit LUT, or two 5 bit LUTs. Each LUT can use up to two additional FFs to store values. Apart from logic function generation, the slices can also be used for carry chain logic. Carry chain logic can be used for very fast adders, comparators, and counters. The signal path is optimized via a special direct routing to the next slice and CLB. Each slice can be used as a 4 bit carry chain [Xil14a].

RO-based PUFs try to use frequency differences caused by production tolerances to extract entropy from routing and logic. But this frequency also depends on many influences such as noise, reversible variations, irreversible variations, and location within the device. To minimize those influences on the measurement and maximize the effect caused by production tolerances, differential measurements, as explained in Figure 2.7, were used.

Different possible RO PUF constructions were analyzed for their area consumption, speed, and reliability. It is always a trade-off between those properties when using PUF technology. A high area consumption also leads to a higher cost. Especially in high volume products, this can turn out to be very expensive. Another aspect is speed: when using an Electrical Control Unit (ECU) of a car, tight timing constraints are demanded by the Controller Area Network (CAN) protocol. If a PUF-based key-generation slows down the whole device, those timing constraints might not be reached and the device would not work anymore. On the other hand, a low area PUF that is read-out very fast might lead to a very unstable behavior and an unreliable cryptographic key. Therefore, the requirements have to be analyzed in detail before designing the PUF. The main focus of this thesis is on an area optimized RO PUF implementation with good reliability. Every design was tested for their area usage, speed, uniqueness, uniformity, bit alias, and reliability.

## 3.2 Theory

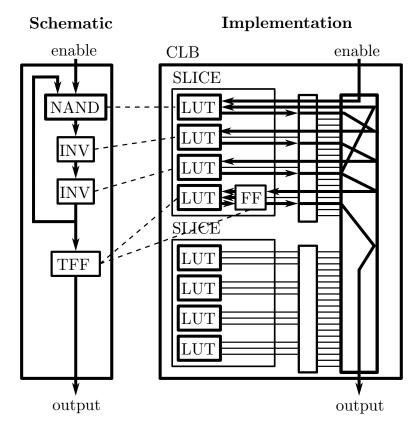

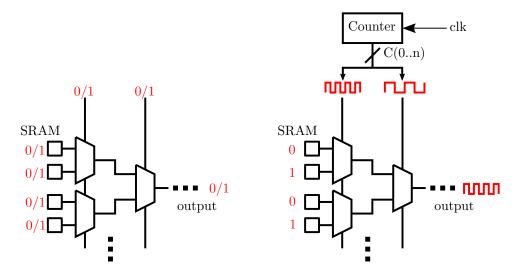

Figure 3.1 shows the schematic and an exemplary implementation of an RO PUF on an FPGA. In this case, three inverters are used in the oscillation chain. The first inverter is implemented as a NAND gate to be able to enable and disable the oscillation. Each inverter stage can be implemented by using a single LUT, i.e., a 1 bit LUT for an inverter and a 2 bit LUT for the NAND gate. The complex routing system is used to implement the forward-feeding and loop-feeding of the signals.

Many previous RO PUF implementations used very long inverter chains, to limit the frequency of the ring. A problem that occurs with the very short 3-inverter ring is that no current FPGA can handle the resulting frequencies in the synchronous clock domain. These frequencies usually lie between 500 MHz and 1 GHz, as shown later in this thesis. The downside of using

3.2. THEORY 29

Figure 3.1: Schematic and implementation of a 3-inverter RO PUF on an FPGA. A NAND gate is used to be able to enable and disable the oscillation. A TFF is used to halve the frequency.

large inverter chains is the large area usage without gaining more extractable entropy.

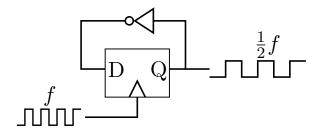

Another approach to lower the frequency is to use one or more Toggle Flip-Flops (TFFs) after the RO. A TFF changes its state ('toggles') on every input clock cycle. Figure 3.2 shows the structure of a TFF. A single Data Flip-Flop (DFF) and an inverter can be used to halve the frequency of an input signal. The high RO output frequency f is used as the clock signal of the DFF to cause an inversion of the output signal. The resulting frequency is exactly  $\frac{1}{2}f$ . It has to be ensured that the data path delay from the Q output of the DFF, through the inverter, to the D input of the DFF is not larger than the period of the DFF clock, i.e., the RO frequency.

By choosing an appropriate number of TFFs, the frequency can be lowered to an FPGA processable level. The TFF in Figure 3.1 is implemented on the remaining LUT of the upper slice. Again, the LUT is used to implement an inverter and additionally one FF for storing the current value. The output of the FF is then routed outside the CLB and used as the output frequency. Using this technique it is possible to implement a 3-inverter RO-PUF on a single slice. A downside of using TFFs on the Xilinx Zynq is that only one clock domain for memory elements is allowed per slice. This limits the amount of TFFs per CLB to two [Xil14b].

Figure 3.2: Schematic and implementation of a TFF

As explained in Figure 2.7, the frequency of two such chains can then be counted and compared to generate a single PUF bit. Various methods to implement the counters on FPGAs exist. One possibility is to use two synchronous counters that sample the RO frequencies with the global device clock [GCvDD02]. Every detection of a positive signal edge will then increment the counter. This, however, limits the RO frequency to half of the global clock frequency. This problem can be overcome by using TFFs.

Another possible method is the usage of an asynchronous counter [Mer14]. Two ripple counters are fed by the two RO frequencies. The global clock is used as a reference counter to start and stop both measurements at the same moment. The advantage of this method is that higher input frequencies can be processed. As long as the delay line capacity connecting the RO output with the counter is not too long to be charged in time and the first DFF can process the oscillation, very high frequencies can be processed. This also achieves a higher measurement precision, compared to a synchronous measurement. Another advantage of this method is the simple implementation and feasibility in FPGA logic. Most FPGAs have CLBs with integrated carry chains, which can be used to implement the counters very efficiently.

# 3.3 Implementation

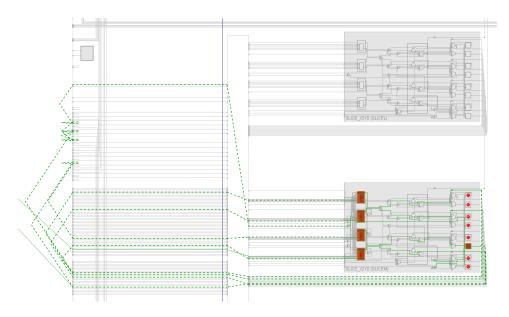

The implementation of RO PUFs on an FPGA requires some considerations. As a synthesis tool always optimizes a circuit for speed and area, a RO with unpredictable behavior would either throw a latch warning or be completely optimized out as it serves no purpose from a tool point of view. Additionally, every pair of ROs that is being compared had to be implemented exactly the same. The placement and routing had to be thoroughly constrained. The usage of slices, logic, pins, and routing was manually fixed to prevent any optimization by the synthesis tool. In earlier works, hard macros were used

in the Xilinx ISE suite. In the newest toolchain, Vivado, this feature was removed. As a replacement, constraints can be defined in the TCL format or the Xilinx proprietary XDC. In this thesis, mainly XDC constraints were used to fix the placement of logic and routing. Each RO implementation should only occupy one CLB and be limited from using outside logic and/or routing.