#### Technische Universität München

Fakultät für Informatik Lehrstuhl III - Datenbanksysteme

# A Distributed Data Processing Perspective on Industrial Real-Time Systems

Thomas Kothmayr

Master of Science with honours

#### Technische Universität München

Fakultät für Informatik Lehrstuhl III - Datenbanksysteme

## A Distributed Data Processing Perspective on Industrial Real-Time Systems

Thomas Kothmayr, M.Sc. with honours

Vollständiger Abdruck der von der Fakultät für Informatik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender: Prof. Dr. Uwe Baumgarten

Prüfer der Dissertation: 1. Prof. Alfons Kemper, Ph. D.

2. Prof. Dr. Harald Kosch, Universität Passau

Die Dissertation wurde am 03.03.2017 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 22.06.2017 angenommen.

The current generation of manufacturing systems relies on monolithic control software which provides real-time guarantees but is hard to adapt and reuse. These qualities are becoming increasingly important for meeting the demands of a global economy. Ongoing research and industrial efforts therefore focus on service-oriented architectures (SOA) to increase the control software's flexibility while reducing development time, effort and cost. With such encapsulated functionality, system behavior can be expressed in terms of operations on data and the flow of data between operators. In this thesis we consider industrial real-time systems from the perspective of distributed data processing systems. Data processing systems often must be highly flexible, which can be achieved by a declarative specification of system behavior. In such systems, a user expresses the properties of an acceptable solution while the system determines a suitable execution plan that meets these requirements. Applied to the real-time control domain, this means that the user defines an abstract workflow model with global timing constraints from which the system derives an execution plan that takes the underlying system environment into account. The generation of a suitable execution plan often is NP-hard and many data processing systems rely on heuristic solutions to quickly generate high quality plans. We utilize heuristics for finding real-time execution plans. Our evaluation shows that heuristics were successful in finding a feasible execution plan in 99% of the examined test cases. Lastly, data processing systems are engineered for an efficient exchange of data and therefore are usually built around a direct data flow between the operators without a mediating entity in between. Applied to SOA-based automation, the same principle is realized through service choreographies with direct communication between the individual services instead of employing a service orchestrator which manages the invocation of all services participating in a workflow.

These three principles outline the main contributions of this thesis: A flexible reconfiguration of SOA-based manufacturing systems with verifiable real-time guarantees, fast heuristics based planning, and a peer-to-peer execution model for SOAs with clear semantics. We demonstrate these principles within a demonstrator that is close to a real-world industrial system.

Die heutige Generation von Fertigungssystemen nutzt monolithische Kontrollsoftware, welche zwar Echtzeitgarantien bietet, aber dafür schwer wartbar und kaum wiederverwendbar ist. Diese Eigenschaften werden jedoch zunehmend wichtiger um den Anforderungen einer globalisierten Wirtschaft gerecht zu werden. Die aktuelle Forschung und Entwicklungsbestrebungen der Industrie setzen daher auf service-orientierte Architekturen (SOAs), um die Flexibilität der Kontrollsoftware zu erhöhen und dadurch Entwicklungsaufwand, -Zeit und -Kosten einzusparen. Durch die Kapselung der Funktionalität in SOAs kann das Systemverhalten dabei auf der Ebene von Operatoren, sowie dem Datenfluss zwischen diesen Operatoren, ausgedrückt werden. In dieser Arbeit betrachten wir daher industrielle Echtzeitsysteme vom Standpunkt der verteilten Datenverarbeitung.

Datenverarbeitungssysteme müssen oft hoch flexibel sein, was sich durch eine deklarative Spezifikation des Systemverhaltens umsetzen lässt. Nutzer beschreiben in solchen Systemen die Eigenschaften von akzeptablen Lösungen woraufhin das System selbsständig einen Ausführungsplan erstellt, welcher diese Eigenschaften erfüllt. Angewendet auf die Domäne von Echtzeitsystemen bedeutet dies, dass Nutzer einen abstrakten Ablaufplan in Form eines Graphen mit globalen zeitlichen Anforderungen defineren ausgehend von dem das System eigenständig einen Ausführungsplan erstellt, welcher die konkrete Systemumgebung berücksichtigt. Die Erzeugung solch eines Ausführungsplans ist meist NP-schwer, weswegen viele Datenverarbeitungssysteme heuristische Lösungen nutzen um in kurzer Zeit hochqualitative Lösungen zu erstellen. Wir nutzen ebenfalls Heuristiken um echtzeitfähige Ausführungspläne zu erstellen. Unsere Auswertung zeigt, dass Heuristiken in 99% der untersuchten Fälle einen echtzeitfähigen Ablaufplan erstellen konnten, falls solch ein Plan existiert. Datenverarbeitungssysteme sind zudem auf effiziente Kommunikation ausgelegt und tauschen daher Daten meist direkt zwischen den einzelnen Operatoren aus ohne über Dritte zu kommunizieren. In SOAs wird dieses Prinzip durch Servicechoreographien mit direkter Kommunikation zwischen den einzelnen Services umgesetzt, welche im Gegensatz zur Serviceorchestrierung durch einen Orchestrator stehen der die einzelenen Services aufruft und die Kommunikation zwischen ihnen verwaltet.

Die drei obenstehenden Prinzipien skizzieren bereits die wissenschaftlichen Beiträge dieser Dissertation: Die flexible Rekonfiguration von SOA-basierten Fertigungssystemen mit verifizierbaren Echtzeiteigenschaften, schnelle Generierung von Ausführungsplänen für solche Systeme mit Hilfe von Heuristiken und ein Peer-to-Peer Ausführungsmodell für SOAs mit einer klar definierten Semantik. Zusätzlich verdeutlichen wir diese Prinzipien in einem Demonstrator, der an ein Echtweltsystem angelehnt ist.

## Acknowledgements

I would like to express my gratitude to Prof. Alfons Kemper for enabling me to work on this research topic at his chair for the last years and for providing me with guidance and support throughout. Dr. Jörg Heuer and Dr. Andreas Scholz from our industry partner Siemens CT have also played a large role in the successful conduction of this research endeavor. I would like to thank them for the valuable discussions and their input to both the alignment and execution of my research. I also thank Prof. Kosch from the University of Passau for reviewing this thesis.

Special thanks go to Michele Blank who setup the electromechanical components of the real-world demonstrator described in this thesis. He also implemented the event-driven control software, which served as a basis for the time triggered architecture of the demonstrator. I also thank all students who worked in the context of the rtSOA project.

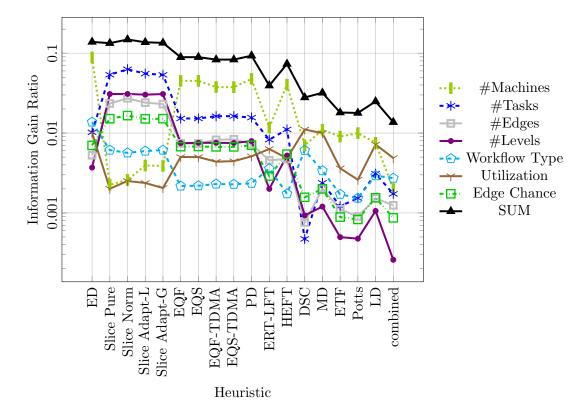

I would also like to thank all current and former members of the chair for database systems at TUM for their collegiality, input and the enjoyable working atmosphere. I would like to especially mention Aleksandar Bojchevski for giving me the idea to examine the information gain of various factors influencing the effectiveness of the rtSOA heuristics. Thank you to Silke Prestel for keeping my working hours largely free of paper work.

Lastly, thank you to my family and friends for the support and encouragement, whenever necessary.

Für Hannah, meinen Grund hart aber nicht zu lange - zu arbeiten.

## Contents

| 1 Introduction |     |                                                       |           |  |  |

|----------------|-----|-------------------------------------------------------|-----------|--|--|

|                | 1.1 | Distributed Data Processing                           | 2         |  |  |

|                | 1.2 | Background: Real-Time Systems                         | 5         |  |  |

|                | 1.3 | Goals and Contributions                               | 6         |  |  |

|                | 1.4 | Outline of the Thesis                                 | 7         |  |  |

| 2              | His | tory and Trends in Industrial Automation              | 9         |  |  |

|                | 2.1 | State of the Art in Industrial Manufacturing          | 12        |  |  |

|                | 2.2 | Emerging Technologies                                 | 13        |  |  |

|                |     | 2.2.1 Distributed Systems with the IEC 61499 Standard | 15        |  |  |

|                |     | 2.2.2 The Role of Service-Oriented Architectures      | 16        |  |  |

|                |     | 2.2.3 Industrie 4.0                                   | 23        |  |  |

| 3              | The | ertSOA Approach                                       | <b>25</b> |  |  |

|                | 3.1 | Design Goals and Principles                           | 25        |  |  |

|                | 3.2 | 2 System Model and Assumptions                        |           |  |  |

|                | 3.3 | 3.3 The rtSOA Architecture                            |           |  |  |

|                | 3.4 | 4 Execution Semantics                                 |           |  |  |

|                | 3.5 | 5 Discussion                                          |           |  |  |

|                |     | 3.5.1 Design Alternatives                             | 39        |  |  |

|                |     | 3.5.2 Related Work                                    | 42        |  |  |

xii Contents

| 4  | From  | m Specification to Solutions             | 49  |  |  |

|----|-------|------------------------------------------|-----|--|--|

|    | 4.1   | State Space Exploration                  | 52  |  |  |

|    |       | 4.1.1 Satisfiability Modulo Theories     | 53  |  |  |

|    |       | 4.1.2 Mixed Integer Linear Programming   | 54  |  |  |

|    |       | 4.1.3 Discussion and Related Work        | 57  |  |  |

|    | 4.2   | Heuristic Approaches                     | 59  |  |  |

|    |       | 4.2.1 Deadline Assignment Heuristics     | 59  |  |  |

|    |       | 4.2.2 Distributed Scheduling Heuristics  | 64  |  |  |

|    | 4.3   | Evaluation and Discussion                | 69  |  |  |

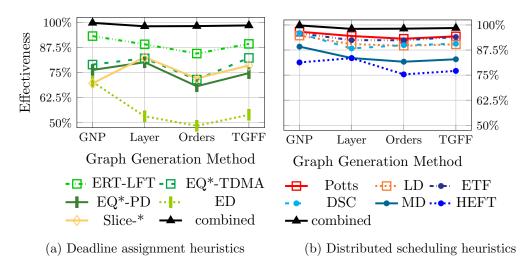

|    |       | 4.3.1 Effectiveness                      | 71  |  |  |

|    |       | 4.3.2 Information Gain                   | 77  |  |  |

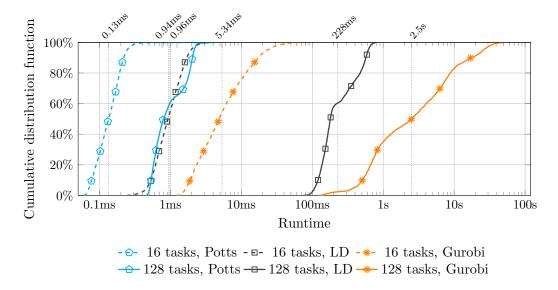

|    |       | 4.3.3 Runtime Comparison                 | 78  |  |  |

|    |       | 4.3.4 Conclusions                        | 80  |  |  |

| 5  | Vali  | idation                                  | 83  |  |  |

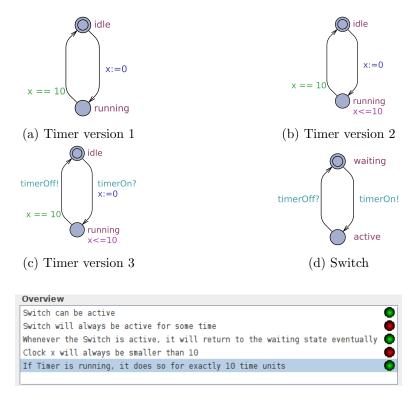

|    | 5.1   | Model Checking via Timed Automata        | 83  |  |  |

|    | 5.2   | Discrete Event Simulation                | 90  |  |  |

| 6  | Rea   | d-World Prototype                        | 93  |  |  |

|    | 6.1   | Software Runtime                         | 94  |  |  |

|    | 6.2   | Service Description and Discovery        | 96  |  |  |

|    | 6.3   | Changing Execution Plans                 | 96  |  |  |

| 7  | Con   | aclusion 1                               |     |  |  |

| A  | Test  | tbench and Benchmark Data Set            | 103 |  |  |

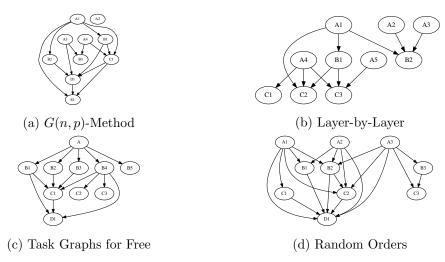

|    | A.1   | Graph Generation Methods                 | 103 |  |  |

|    | A.2   | Benchmark Data Set                       | 106 |  |  |

|    | A.3   | Testbench                                | 110 |  |  |

|    |       | A.3.1 Specification Language             | 111 |  |  |

|    |       | A.3.2 Data Set Specification             | 112 |  |  |

| В  | Arc   | hived Benchmarks of SMT and MILP-Solvers | 123 |  |  |

|    | B.1   | Benchmark of MILP-Solvers                | 123 |  |  |

|    | B.2   | Feasibility Benchmark of MILP-Solvers    | 124 |  |  |

|    | В.3   | Benchmark of SMT-Solvers                 | 126 |  |  |

| Bi | bliog | graphy                                   | 127 |  |  |

"Then there is the man who drowned crossing a stream with an average depth of six inches." - W.I.E. Gates

## CHAPTER 1

Introduction

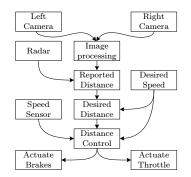

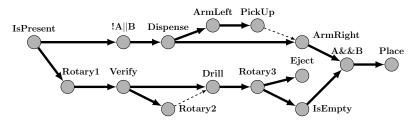

This thesis takes a distributed data processing perspective on industrial real-time systems. The main building block of this approach is a service-oriented architectural style that encapsulates mechatronic or computational functionality in self-describing services. We have therefore named our approach rtSOA. With these self-contained, reusable services the development of automation systems can be shifted to reasoning over the flow of data between service instances, thus taking a step into the direction of distributed data processing (DDP) systems. To realize a high level of flexibility, users of DDP systems often do not have to explicitly specify concrete execution plans. Users instead list the properties of acceptable solutions for which the DDP system will automatically generate a matching execution plan. This plan fulfills the specified requirements while hiding the complexities of the underlying networked system from the user. rtSOA applies this principle by only requiring the specification of global real-time constraints for a given task-graph, which constitutes the distributed realtime automation task. Timing constraints for individual service instances are derived automatically from the global constraints, the concrete placement of the services on machines and the configuration of the connecting network. The execution plan then consists of a schedule for the network and each participating device, so that the specified real-time requirements are realized.

rtSOA is focused on enabling wide-reaching reuse of existing code modules and enabling fast, iterative and incremental development for distributed real-time systems. The main use case for rtSOA lies within the area of industrial manufacturing. In recent years increasing uncertainty about the production volume of a product is accompanied by demand fluctuations over the product's life cycle [53,103,117]. To address these issues, the paradigm of the reconfigurable manufacturing system (RMS) has been postulated in research. Software reconfiguration is a key component in

1. Introduction

enabling reconfigurable manufacturing systems, which therefore benefit immensely from a modular and reconfigurable software architecture, supported by a declarative approach to the generation of execution plans. To the best of our knowledge, rtSOA is the first approach that achieves predictable and deterministic execution plans by applying distributed data processing principles in a flexible and reconfigurable service-oriented architecture.

In the following, we present basic principles of distributed data processing systems in Section 1.1 and real-time systems in Section 1.2 before giving an overview of the goals and contributions of this thesis in Section 1.3 and detailing the outline in Section 1.4.

## 1.1 Distributed Data Processing

Distributed data processing may become necessary due to different reasons: Either because the amount of data cannot be handled on a single device or because the processing of data in the network is more efficient in terms of computation time, energy efficiency or other resources, including organizational resources such as money or employee working hours. In this section we will outline several different systems which are contained under the umbrella of distributed data processing and which demonstrate certain properties or principles of DDP that are applicable to the rtSOA approach.

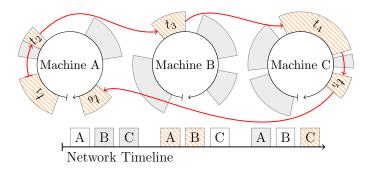

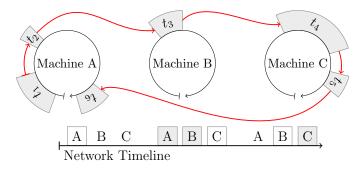

In recent years, distributed data processing has often become synonymous with processing of big data sets that cannot be contained on a single machine. One of the most successful programming paradigms in that area is MapReduce [31], which requires the programmer to specify computation in terms of a map and a reduce function. The underlying library then takes care of issues such as parallelization, inter-machine communication and fault tolerance. Efficient scheduling of network resources becomes particularly relevant when aiming for high overall system performance. Starting from the observation that the increase of computational resources has progressed at a faster pace than the increase of network communication speeds, Rödiger et al. have analyzed the impact of network scheduling on joins in distributed databases [96] and designed a network-optimized join that is based on solving two distinct optimization problems. The first of these problems is the optimal partition assignment which specifies which parts of the input data will be processed on which machine. By choosing an optimal partition assignment, the length of the network transfer phase can be minimized. The second optimization problem lies with determining a suitable communication schedule. Cross traffic and other inefficiencies can render an otherwise efficient execution plan ineffective, meaning that much time is spent idly waiting for network packets that obstruct each other during transmission. Applied to the field of industrial real-time systems, the two optimization problems solved by Rödiger et al. map to determining a suitable assignment of (computational) tasks to machines and determining an efficient overall execution plan that takes network particularities into account.

Stream processing systems are moving away from traditional database systems, which operate on stored data, towards execution semantics over data streams which operate on in-flight data, meaning data that is analyzed as soon as it is produced and may also carry a temporal component. Data for stream processing systems is often generated by distributed systems and the stream processing system may itself be a distributed system. Stonebraker et al. [105] detail eight general rules for real-time stream processing. Among these rules are performance requirements, demanding that data should be processed "in-stream" (1) without a separate storage step to achieve suitably low latency and the general requirement that the system must be able to "keep up" (2) with the amount of data generated. Rules for consistency demand that a system must process data in a repeatable and predictable (3) manner while handling stream imperfections (4) such as delayed, missing or out of order data. The stream processing systems must also be highly available and ensure data integrity under hardware failures (5). Usability requirements for a declarative stream query language (6) with easy integration of stored data (7) and support for automatic partitioning and scaling (8) are classic principles of DDP systems.

Many of the outlined principles can also be applied to industrial real-time systems, which must process sensor data as it is generated (1) while always offering guaranteed timing properties (2). Automation systems should remain deterministic (3), even when handling communication (4) and hardware failures (5). rtSOA aims to introduce some of the usability principles described by Stonebraker et al. to the area of industrial real-time systems by allowing the user to specify high-level timing constraints without manual consideration of network particularities (c.f. rules 6 and 8). Real-time in the context of the above paragraph means "a timely manner", without timing guarantees, whereas real-time in the context of this thesis always means real-time guarantees. Section 1.2 introduces our notion of the term.

Another requirement for using a declarative approach to generating execution plans is the presence of well understood and stringent semantics for the specification language. In traditional database management systems, the relational algebra [60, Chapter 8] provides the semantics and logical basis for the generation of the query execution plan. The semantics of a relational algebra expression are contained in the semantics of the individual operators used in the expression and the data flow between them. Contrastingly, rtSOA views individual services in a SOA as black-box operators and only reasons about the data flow between them. Section 3.4 defines these semantics.

The main driver for distributed data processing in embedded systems lies not in handling otherwise intractable amounts of data. Instead, achieving a balance of flexibility and efficiency in highly complex systems of systems is often the main motivation behind applying distributed data processing methods in embedded networks. One example for such a system is TinyDB [78]. TinyDB is an acquisitional query processing system that explicitly addresses, and deeply integrates with, the particularities of wireless sensor networks. Sensor networks consists of tens or hundreds of

4 1. Introduction

self-organizing battery powered nodes that operate without human intervention for months or years. Since sensor nodes are usually battery powered and severely energy constrained, optimization for energy efficiency and limiting network communication are essential for realizing a practical system. One way to realize long battery life spans is to configure sensor nodes to sleep in a low-power state for most of the time and only wake up periodically to perform data acquisition, processing and network communication. Communication often follows a multi-hop pattern to one or more gateways which act as data sinks. By performing in-network aggregation along these multi-hop communication paths, the network traffic and thus the energy usage can be greatly reduced. Acquiring sensor data and performing data aggregation and analysis is greatly simplified by using TinyDB's declarative SQL-like query interface instead of manually configuring the data acquisition and in-network aggregation behavior of each sensor node. In contrast to traditional database or stream processing systems, TinyDB can control the frequency of when sensor data is acquired instead of acting on stored data or only analyzing incoming data streams. Other issues, such as determining which sensor nodes have relevant data and in which order samples should be taken, are more closely related to traditional query optimization and stream processing.

TinyDB illustrates a flexible but specialized solution to distributed data processing in embedded (sensor) networks. Scholz et al. presented a more general solution in the form of a service-oriented middleware for embedded networks named  $\epsilon SOA$  [98].  $\epsilon$ SOA takes a data centric view on service-oriented architectures and models service interaction following a push-based communication pattern. As explained in the context of TinyDB, various data flows inside the network should be optimized in terms of the timing and frequency of the individual messages. The  $\epsilon SOA$  stream dispatcher therefore applies principles of data stream management systems to optimize the rate of all data streams in terms of energy efficiency and desired message interval. The  $\epsilon$ SOA middleware additionally tackles the service placement problem with the simulated annealing meta heuristic. Based on an abstract representation of the workflow to be executed by the devices in the embedded network,  $\epsilon$ SOA transparently applies its optimization techniques and thus hides the details of the underlying network structure from the application developer. This approach follows the same high-level structure as the MapReduce library where users are required to specify their application following certain development principles but are freed from explicit consideration of network issues because the middleware is addressing them. Users can thus reason about the implementation on a higher level of abstraction.

The examples in this section outline that distributed data processing systems may share some commonalities in their principles but have to be carefully adapted to their intended target area. In Section 1.2 we therefore give more background information about general real-time systems before detailing the system environment for our envisioned distributed data processing approach to industrial real-time automation in Section 2.

### 1.2 Background: Real-Time Systems

This short introduction to real-time systems is based on the book "Hard Real-Time Computing Systems" by Buttazzo [14]. The fundamental difference between a real-time system and other computing systems is the fact that the correctness of a computational result depends on the time at which the result is produced. The presence of a deadline thus marks a real-time system. The reason for this is that the system interacts with its environment, often meaning the physical environment, thus making real-time requirements an integral part of many embedded systems. Examples for real-time systems include automotive and avionic systems, telecommunication systems, robotics, environmental monitoring and industrial manufacturing systems, which are the main focus of this thesis.

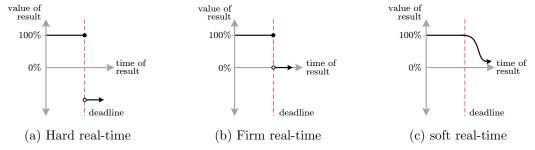

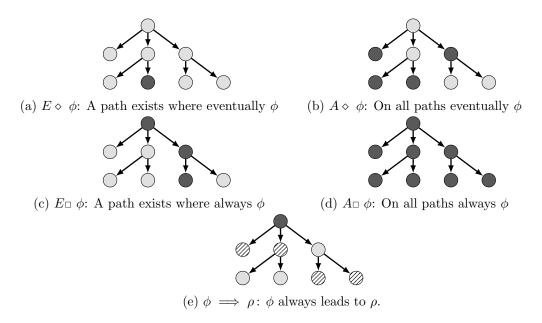

Figure 1.1 illustrates different types of real-time systems. They are classified by the value of a computational result after its expected deadline. In hard real-time systems a single missed deadline may have catastrophic consequences for the system itself, attached equipment, the environment or humans. The value of a late result is therefore negative and deadlines must be guaranteed. Examples for these kind of systems could be chemical process plants, safety critical systems in airplanes or automobiles or in general systems that incorporate sensing, actuating and control activities. In firm real-time systems deadline misses are not catastrophic. Late results are nevertheless useless and have no value. Examples would be video or audio decoding systems where frames may be dropped occasionally. In soft real-time systems a late result still has value but the performance of the system is degraded. Examples would be systems handling user input or graphical displays.

Figure 1.1: A schematic visualization of the value of a late computational result under the hard, firm and soft real-time paradigms.

An often held misconception is that real-time simply means "fast", but execution speed only relates to the average response time of a system. Hard real-time systems require guarantees for the worst case and not for the average case. These timing requirements are determined by the system's environment and the system must always react within the time frame set by the environment to be fit for its purpose. Experience with real-time systems shows that the worst case scenario can, does and will happen (c.f. the anecdotes presented by Buttazzo in the introduction of his book [14]). Buttazzo defines the following basic properties that real-time systems should possess:

6 1. Introduction

• **Timeliness:** Results must not only be correct but also be available for the consuming entity within a specific time frame.

- **Predictability:** The system must be analyzable in order to determine the consequences of any scheduling decision. For safety critical applications, timing requirements should be guaranteed before the system is put into operation.

- Efficiency: Most real-time systems are embedded devices with restricted storage, computational and energy resources. This must be taken into account when developing the system's hardware and software.

- Robustness: Real-time systems must be robust under peak-load conditions and should be designed to handle all anticipated load scenarios.

- Fault tolerance: Single failure of hardware or software should not cause the overall system to fail. Critical components of the system should therefore be designed to be fault tolerant.

- Maintainability: The architecture of a real-time system should be modular, ensuring that future system modifications are easy to perform.

To achieve these properties in distributed real-time systems, all components of the system need to be chosen accordingly. For example, fault tolerance in the area of networking may require the presence of physical duplication of the communication equipment. When writing software for these systems, developers are severely restricted in the primitives available to them. Dynamic memory allocation at run time might not be possible because this could introduce unbounded delays. Similarly, unbounded recursion or unbounded loops are often not allowable in real-time programs [14].

#### 1.3 Goals and Contributions

The overall goal of this thesis was the development of an engineering approach for distributed hard real-time systems, with a special focus on reconfigurable manufacturing systems. By following principles of distributed data processing systems the approach should reduce development time, effort and cost. The design of rtSOA was based on the following desired system properties while addressing the general properties for hard real-time systems stated at the end of Section 1.2:

- Goal 1 rtSOA systems are adaptable at run time with minimal downtime.

- **Goal 2** rtSOA systems are hard real-time systems. They have deterministic and verifiable behavior.

- Goal 3 The development of automation workflows with rtSOA is decoupled from timing and networking concerns.

- Goal 4 Development with rtSOA is iterative, visual and has short feedback cycles.

Resulting from the stated set of goals, the contribution of this thesis are:

- To the best of our knowledge, rtSOA is the first approach that achieves predictable and deterministic execution plans by applying distributed data processing principles in a flexible and reconfigurable service-oriented architecture.

- We compare the use of domain specific heuristics with a state-of-the-art linear program solver for the generation of distributed real-time workflow execution plans. This analysis is performed over a benchmark data set with 1.2 million feasible problem instances.

- We propose two new domain specific heuristics that contribute a large number of unique execution plans. Unique means that no other heuristic contributed a feasible solution for the same test case.

- We propose several adaptions of existing heuristics to increase their effectiveness for the generation of rtSOA execution plans.

- We showcase the adaption of DDP principles for industrial real-time systems with a demonstrator that is close to a real industrial system.

#### 1.4 Outline of the Thesis

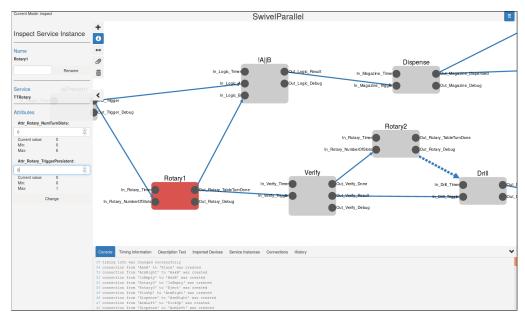

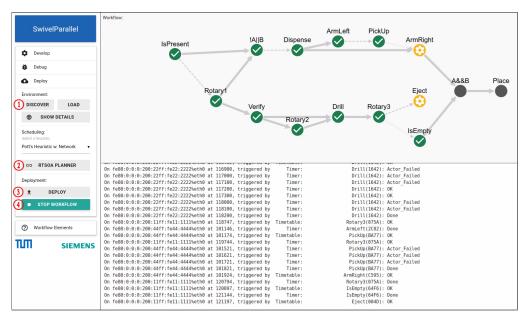

The rest of this thesis is structured in the following way: Chapter 2 expands upon the general introduction to real-time systems given in Section 1.2 by outlining past and present developments in industrial automation from a hardware and software perspective. Chapter 3 introduces our approach, named rtSOA, for real-time serviceoriented architectures from a distributed data processing perspective. It reconciles the flexibility and reconfigurability of a service-oriented architecture with the timing guarantees and determinism required to verify the correctness of hard real-time systems. rtSOA achieves these properties via cyclic execution plans for each device that participates in the execution of the automation workflow. These execution plans follow a stringent set of dataflow semantics, also defined in Chapter 3. Chapter 4 details how execution plans can be derived from an abstract representation of the workflow. The chapter includes an extensive evaluation of the alternatives. To provide confidence that a set of execution plans conforms to the required real-time properties engineers rely on verification or simulation of the overall system. Chapter 5 presents how these methods can be applied to rtSOA. In Chapter 6 we present a prototype for the overall rtSOA system that ranges from configuration of a workflow with a graphical user interface (GUI), over generation of execution plans with the methods presented in Chapter 4, to simulation, deployment, and execution on a real-world demonstration system. The thesis ends with a summary of our approach and results in Chapter 7 wherein we also point out further directions for research.

8 1. Introduction

"ANY CUSTOMER CAN HAVE A CAR PAINTED ANY COLOR THAT HE WANTS SO LONG AS IT IS BLACK." - Henry Ford

CHAPTER 2

## History and Trends in Industrial Automation

Parts of this chapter have been previously published in [64, 65, 67].

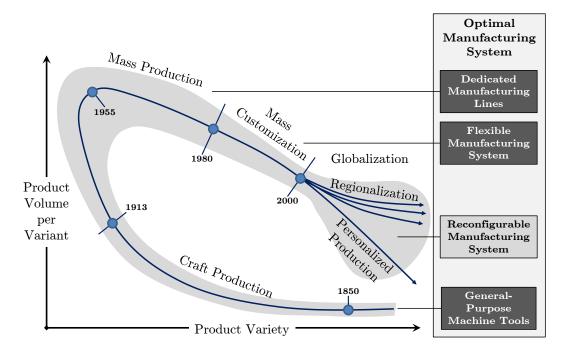

Products, markets and societies are experiencing an increasing pace of change which requires flexibility and changeability from the manufacturing industry to meet the demands of a global economy [62, 117]. Indeed, the technological and sociological conditions under which the industry has operated have constantly been changing for over 100 years. Figure 2.1 shows the changes in manufacturing paradigms in the automobile industry. In the middle and end of the 19th century the automobile (or in the beginning the carriage making) industry was following the paradigm of craft production, meaning that each product is essentially unique and hand crafted by skilled workers. In 1913 Henry Ford introduced the moving assembly line method in production of the famous Ford Model T. The assembly line ushered in the era of mass production which saw a drastic reduction in product variety while increasing the production numbers of each variant. This development in the United States' automobile industry reached its peak in 1955 [62]. From then on more product variants have been introduced to meet customers' different needs and desires. The 1980s mark the emergence of mass customization as a new paradigm in which customers are able to customize a product by choosing from different options for its individual characteristics, e.g., different accessories in their car or different components of their laptop computers. Koren observes that the 2000s have marked another paradigm shift triggered by the increased interrelations of global value chains and a worldwide customer base [62]. The customization trend may be taken to its extreme by paradigms such as personalized production which offers fully individualized products to the customer. Another trend is regionalization of products, as manufacturers have to take the cultural and legal particularities of different countries and regions

into account. A certain make and model of a car will have different components if manufactured for the European market when compared to the Chinese market. Chryssolouris remarks:

"It is increasingly evident that the era of mass production is being replaced by the era of market niches. The key to creating products that can meet the demands of a diversified customer base, is a short development cycle yielding low cost, high quality goods in sufficient quantity to meet demand. This makes flexibility an increasingly important attribute to manufacturing." [22]

Each of the manufacturing paradigms is best realized by a different manufacturing system. Craft production of one of a kind items is best realized with the most adaptable of all production systems: A skilled human worker with general purpose machine tools.

Figure 2.1: Changing manufacturing paradigms over time in the context of the automobile industry. [62]

Since the 1980s software controlled manufacturing systems have increasingly come to dominate the automation landscape, making software another key factor in the success or failure of manufacturing solutions. *Dedicated manufacturing systems* (DMS) excel at mass production of goods at high volume and quality while keeping product cost low through economies of scale. These centralized, monolithic and scan-based control systems are optimized for a given physical and network configuration allowing them to fully operate with high production rates after a long and costly setup period.

However, these dedicated lines can only be used to manufacture a narrow range of products and cannot be adapted in terms of production volume. The per-unit cost of goods manufactured on a DMS rises whenever it is not run at full capacity. There is also no quick way to increase the capacity of a DMS if demand exceeds supply. From a software perspective, the modularization and reuse of source code running on these systems is hindered by a tight coupling with their environment.

Flexible manufacturing systems (FMS) emerged as a way to handle changing customer demands within a given family of products or parts through rapid reconfiguration of their hardware and software [117]. As such, they are an enabling technology for the mass customization manufacturing paradigm [62]. Computerized numerical control (CNC) machines are an example for flexible production systems. These machines can be programmed to mill and bore work pieces from a solid block of material with high precision, granting them an unprecedented flexibility in the variety of products that they can manufacture, albeit at the cost of reduced throughput. FMSs are designed for a specific range of work pieces and often feature overprovisioning of tools or transport capabilities because retrofitting of new capabilities is expensive [117]. Section 2.1 outlines the state of the art in current industrial manufacturing from a software and networking perspective, thus showing the challenges to reconfigurability inherent in traditional architectures.

In recent years increasing uncertainty about the production volume of a product is accompanied by demand fluctuations over the product's life cycle [53, 103, 117]. To address these issues, the paradigm of the *reconfigurable manufacturing system* (RMS) has been postulated in research [36,62,117]. Koren is giving the following definition:

"A reconfigurable manufacturing system [...] is designed for rapid adjustment of production capacity and functionality [...] by rearrangement or change of its components (hardware and software)." [62]

A RMS is modular and designed to evolve both in terms of capacity and capability over its lifetime. Apart from reconfigurable hardware, software reconfiguration has been identified as a key technology for RMS [36]. This need for reconfigurability and flexibility of the control software has led to research endeavors which aim at fulfilling these requirements through implementation of service-oriented architectures (SOAs) [106] [23] [46], which encapsulate hardware behavior and software capabilities in services which can be combined in a modular way. Software capabilities also play a large role in the digitalization of the manufacturing industry. The German initiative Industrie 4.0 envisions a landscape of smart factories which are fully integrated with the manufacturer's other plants, its suppliers and its customers [53]. These smart factories also offer a detailed view of their current state to enterprise systems concerned with production planning and logistics. SOAs are likely to play a central role in realizing the capabilities envisioned under the Industrie 4.0 term [97]. In Section 2.2 we therefore give an overview of the role of service-oriented architectures in future manufacturing systems with a special focus on the Industrie 4.0 vision.

### 2.1 State of the Art in Industrial Manufacturing

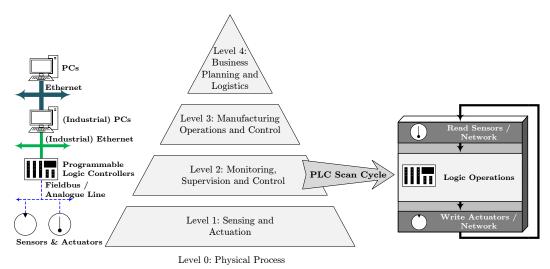

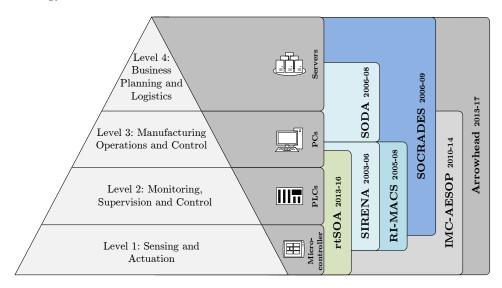

Today's manufacturing plants are usually designed following the hierarchical architecture described in the IEC 62264 standard [5] and visualized in Figure 2.2. Therein, sensors and actuators on level 1 are controlled by a control system on level 2. Communication between field devices and controllers is strictly hierarchical and follows a polling model or a cyclic publish-subscribe relation. Communication between controllers on level 2, or higher levels, may be peer-to-peer. Levels 3 and 4 are the domains of operations control and enterprise planning systems, respectively. Sensors and actuators are usually controlled by programmable logic controllers (PLCs), also following a cyclic model. At the beginning of each scan cycle an input scan is performed which obtains readings from all connected sensors. Based on these updated values, the PLC performs its logic computations, updates all outgoing communication values and sends commands to the connected actuators.

Figure 2.2: Traditional Automation Pyramid with passively queried sensors and actuators. Control programs are realized through programmable logic controllers (PLCs) following a processing architecture called a scan cycle.

IEC 61131-3 is the prevalent standard for PLC programming. This standard specifies the function block diagram (FBD) and structured text (ST) languages which are higher level and, from a software engineering perspective, should have higher productivity than the ladder diagram (LD) and instruction list (IL) languages included in the same standard. Structured text is based on, and similar to, the programming language Pascal. It can be used to define function blocks that can then be used in function block diagrams. FBDs are a graphical representation of programs consisting of (elementary) function blocks such as add, compare, logic functions, and FBs defined with structured text. Instruction list programs resemble code written in assembly. Lastly, ladder diagrams are a program representation form that resembles a notation form for electrical circuits. It is thus focused on logic relations. Although recent industry efforts target increased reusability of code blocks, the control soft-

ware is often rewritten from scratch when integrating new devices [123]. Software architectures of higher level systems mostly follow object-oriented principles with local method calls or direct data access. Services may be available, but not necessarily accessible for remote applications [5].

Networking and data acquisition between level 1 and level 2 devices are strictly hierarchical. Devices may be connected to PLCs either with analogue connections or, increasingly, over field buses or even Ethernet based solutions [5]. In most cases the communication is polling-based although cyclic publish-subscribe alternatives exist [5]. Because all input / output operations of a PLC are performed during each scan cycle, the tightest timing requirement determines the available runtime for the whole scan cycle. Additionally, the scan cycle is tightly coupled with the network cycle. Controllers on level 2 of the automation pyramid are usually able to communicate in a peer-to-peer fashion but messages are also often transmitted in a cyclic fashion. Alarms are special high-priority events which are always transmitted in an event-based fashion [5], other data may also be transmitted in an event-based manner instead of a cyclic manner. Networking between controllers also requires time determinism which is guaranteed by the utilized network protocols.

These traditional control applications offer a high degree of determinism and contribute to the high throughput of today's manufacturing systems. However, their setup and installation cost contribute up to one third of their total lifecycle costs [47]. Manufacturing strategies based on reconfigurable manufacturing systems are therefore hard to implement with the traditional automation architecture. More flexible hardware and software architectures which offer extensive interoperability and quick reconfiguration are thus needed to react to today's changing market demands. The following section outlines modern approaches to achieve these requirements.

## 2.2 Emerging Technologies

The key differences between traditional and future manufacturing systems can be summarized by two factors from a hardware perspective: Increased networking, based on a more unified protocol and hardware landscape, and ubiquitous computation resources leading to smart devices and even smart products or work pieces. These advances in hardware to support manufacturing are already evident. Industrial Ethernet is gaining traction [28] while smarter embedded devices are performing an increasing number of orthogonal tasks, for example wireless sensor networks (WSNs) monitoring machine health. Recent developments include the roll out of smart field devices, like Ethernet-equipped sensors and actuators. In the automotive and avionic industries a different process with similar results can be observed. Subsystems, that were previously separated, are consolidated through a single real-time communication network to reduce weight and costs. In both domains the result is a hardware architecture of multiple networked processing units.

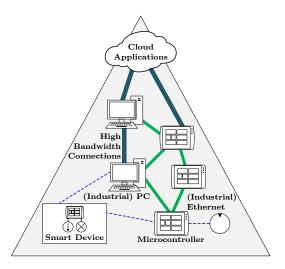

These developments lead to a more interconnected and heterogeneous automation landscape as depicted in Figure 2.3 [7,57,112]. Smart devices, consisting of sensors and actuators with direct networking and computation capabilities, are blurring the line between data acquisition and processing devices. Traditional hardware and software architectures, together with traditional approaches to software development for these systems, are not capable of addressing the challenges brought on by the heterogeneous automation landscape shown in Figure 2.3. Effectively leveraging the new capabilities offered by these interconnected systems is the topic of numerous ongoing and completed research projects. Research concerning service-oriented architectures in the industrial domain is addressing the need for interoperability between devices near the physical process and enterprise applications, which are placed several layers apart in the classical automation pyramid, thus realizing a vertical integration. Industry and research have reacted by developing the IEC 61499 standard for distributed automation systems which we introduce briefly in Section 2.2.1. SOAs are also poised to simplify the composition of multiple devices so that they may cooperate to realize an automation workflow, implementing a horizontal integration of devices. Section 2.2.2 is giving an overview of research endeavors covering the topic of SOAs for industrial automation.

Figure 2.3: The emerging automation landscape is characterized by an increasing heterogeneity and interconnectedness between devices.

The term Industrie 4.0 encompasses horizontal and vertical integration, not of individual devices in a factory but of the factory, then termed a smart factory [7], with its surroundings. Horizontal integration in the Industrie 4.0 world describes the integration of the smart factory in the value chain of the enterprise, meaning an integration with systems used in different stages of the manufacturing and business planning process, whether in-house or with external business partners. Vertical integration refers to the integration of systems on different levels of the automation process with higher level systems [53], similar to the usage of the term when applied to SOAs. Section 2.2.3 will provide further introduction to the concept of Industrie 4.0.

#### 2.2.1 Distributed Systems with the IEC 61499 Standard

The IEC 61499 standard has been proposed as a way to address distributed automation in industrial systems. Its main concept is the hierarchic encapsulation of functionality in function blocks (FBs) which offer a high level of abstraction and promise greater code reuse. An abstract example of a FB is shown in Figure 2.4. This way, "the IEC 61499 architecture exploits the familiarity among control engineers accustomed to a block-diagram way of thinking" [114]. Internally, the execution of an FB is driven by an execution control chart (ECC) state machine [122]. Multiple instances of the same function block type may exist in the same block diagram. Input and output ports are separated into event ports and (typed) data ports as shown in Figure 2.4. Signals on event ports are either present or absent, they carry no additional data but may be associated with data ports. New data is loaded and emitted from data ports whenever an associated event is present [122]. Abstract, more highlevel function blocks often interact with the underlying hardware through service interface function blocks (SIFBs), which are conceptually similar to device drivers or hardware abstraction layers in traditional embedded systems development [122]. SIFBs provide services such as sending or receiving data over the network or access to IO-pins. Algorithmic FBs may thus easily interface with different hardware.

Figure 2.4: A function block instance in the IEC 61499 standard

Function blocks can be nested arbitrarily and allow the combination of different diagram types, among them IEC 61131-3 languages other than FBDs. IEC 61499 models also include specifications of the automation workflow's infrastructure, i.e., the associated devices and the network structure. This results in an executable specification of the distributed automation system [114]. The execution semantics of IEC 61499 blocks are event-driven, they are activated whenever an event reaches one of their event inputs. It is assumed that the FB cannot be reactivated before it has finished its execution, however the standard does not specify how this should be enforced and which measures should be taken if events arrive faster than the FB is executed [114]. Encapsulation of data into FBs is another principle from software engineering that has been applied in IEC 61499. Data encapsulation was often not present in traditional PLC programming and communication between different modules often happened via shared variables [114]. The principles of encapsulation of data and functionality, together with a distributed execution of function blocks, is conceptually consistent with service-oriented architectures [27] which we discuss in detail in the next section.

#### 2.2.2 The Role of Service-Oriented Architectures

There are many definitions of the term service-oriented architecture. The author prefers the following definitions from the OASIS "Reference Model for Service Oriented Architecture":

"[Service-oriented architectures are] a means of organizing solutions that promotes reuse, growth and interoperability." [86]

and from the SIRENA EU project on SOAs in industrial manufacturing:

"A service-oriented architecture [...] is a set of architectural tenets for building autonomous yet interoperable systems." [47]

A service-oriented architecture in itself is therefore not a concrete implementation or a set of technologies, but rather an architectural style for implementing systems that achieve the conflicting goals of autonomy and interoperability. In many cases SOAs have been realized with web service standards, as is also the case in industry driven initiatives (Section 2.2.2.1) and collaborative research projects sponsored by the European Union (Section 2.2.2.2). However, this introduction will not focus on technology details of web services but instead outline the general characteristics of SOAs in the industrial context. The context in which a SOA is deployed has an influence on its characteristics. SOA as an architectural style has originally emerged as a way to organize business processes on an enterprise IT level. Owing to the particularities of the manufacturing domain, some of the original tenets of a service-oriented architecture need to be adapted for use in industrial automation scenarios [88].

The basic building block of a SOA is a service. A service encapsulates functionality, which may be either software functionality or mechatronic functionality. To outside entities, like service orchestrators or other services, the service is fully described via its service interface. Services with the same interface should be seamlessly exchangeable in classical enterprise-IT SOAs. This may not be the case in the automation domain, as the location of a service plays a role in the semantics of its execution [88]. A conveyor belt may offer the same service interface as the neighboring belt, but the correct execution of the automation task will depend on choosing the component with the right physical location for the given context. The objective of a SOA in industrial automation is therefore not distributed computation but instead the execution of a technical process [88]. A service may therefore have certain requirements for the hardware environment where it is executed, meaning that it cannot be placed freely on any device. This is already implicit in the fact that a service can encapsulate mechatronic behavior. A service that offers temperature measurements will need access to a temperature sensor. However, this does not mean that services should be defined technology centric. Instead each service should be rather coarse grained and oriented around business functions [47], meaning it should encapsulate functionality that is already useful on its own without the need to be composited with other services. When services are composited in a sequence we are referring to this composition as a *workflow*. The execution of a workflow may be controlled centrally by a service orchestrator invoking the individual services, receiving their responses and then using these responses in invocations of succeeding services, thus implementing a *service orchestration*. Workflows may also be executed decentrally with each service being aware of its successor in the workflow. This mode of workflow execution is called a *service choreography*.

Service-oriented architectures are designed to address the weaknesses, such as inflexibility and high setup costs, of traditional automation architectures. The strengths of SOA lie in its flexibility and adaptability. By encapsulating basic functionality in interchangeable services the programming of automation systems can be lifted to a higher level [47,88]. Instead of dealing with individual IO-signals, new control flows can be created by rearranging pre-existing services and rerouting the data flow between them. Our prototype implementation in Chapter 6 demonstrates this principle with a real-world system. Ideally, the interface descriptions of services are standardized and physically compatible systems would offer services that are transparently interchangeable with each other, thus allowing fully vendor independent planning and programming phases [48]. To leverage the full strength of SOAs, the hardware should therefore also be designed in a modular fashion and allow quick reconfiguration on the physical side. Reconfigurable manufacturing systems are thus an ideal fit for service-oriented architectures, and vice versa [97, 112]. In the transition phase legacy automation systems can be integrated in higher level SOAs via service facades, allowing a gentle transformation [47].

In SOAs messages between services and devices are sent in a push-based manner making more efficient use of the limited communication resources than the traditional scan or pull-based communication patterns [47]. Extensive research has been undertaken to push the performance envelope of SOA (or more specifically, web-service) technology on constrained embedded devices [123]. These endeavors have seen SOA solutions developed for lower and lower layers of the automation pyramid [46]. It is, however, difficult to verify the emergent properties of distributed event-based systems. Implementations with centralized control are therefore likely to be favored in the near future [58]. Centralized control is realized through a service orchestration which is executed by an orchestration engine that invokes each individual service in a workflow [48]. While such an orchestration represents an improvement over the traditional model, the full impact of the SOA paradigm could be realized through service choreographies providing global cooperation without central coordination [104]. In Chapter 3 we show how decentralized execution plans can be used to realize service choreographies for cyclic control tasks with real-time constraints.

The clear benefits offered by service-oriented architectures have been recognized by the industry and research communities. The remainder of this section covers the current state of SOAs in industry (Section 2.2.2.1) before presenting the research results realized in several framework programs of the European Union (Section 2.2.2.2).

#### 2.2.2.1 Industry Efforts

The automation community has long identified the need for self-describing devices and easy discovery and configuration of automation devices. For this purpose numerous standards and vendor specific implementations have been developed. We have chosen relevant examples based on their importance in industry and research as well as their relation to service-oriented principles. The two most prominent specifications concerning service orientation for industrial devices are the Devices Profile for Web Services (DPWS) [87] and the Object Linking and Embedding for Process Control Unified Architecture (OPC UA) [89]. Both are conceptually similar: They implement a SOA through web services and rely on built-in base services for discovery and service reservation. In both cases, SOAP over HTTP is the standard message binding and messages are either encoded with XML or in a binary format for increased performance. In the following we will look closer at their similarities and differences.

#### OPC UA

OPC UA is a service-oriented version of the original OPC architecture and its main mission is still to connect industrial devices to control and supervision applications [16]. It is therefore not directly aimed at the communication between the devices themselves and follows a client-server architecture. Connecting devices to monitoring and human-machine interaction (HMI) interfaces may entail a large amount of data to be transferred, as one of the roles a OPC UA client may occupy is that of a data logger. For this reason OPC UA also specifies a binding to optimized native binary protocols which may reduce network traffic and processing requirements. Typically lower-level devices take the role of OPC UA servers, as they make their information available to higher level devices [16]. OPC UA servers implement a predefined set of (web)services, which include discovery services, services for reading and writing of attributes or remote invocation of methods, as well as services for subscription to data or negotiation of secure communication channels between client and server [75]. Semantics of data exchanged via OPC UA are defined via the OPC UA meta model.

The client-server architecture as well as the predefined service sets of OPC UA make it well suited for its intended task of data export from lower layers to higher layers of the automation pyramid, especially when taking the existing model for data semantics into account. However, OPC UA is not suited for implementation of true peer-to-peer general purpose SOAs. The client-server architecture limits the communication patterns of OPC UA devices and the predefined service sets do not allow for definition of additional services that can encapsulate device behavior [16].

#### **DPWS**

DPWS is a web service middleware and profile that aims to constrain the WS-\* set of standards to make them suitable for embedded use. It is aimed directly at the devices performing the automation task and therefore supports a peer-to-peer as well as a client-server architecture [123]. DPWS defines two basic elements: the

individual devices and the services hosted upon the devices. This corresponds to our earlier observation that descriptions of services in the industrial context need to be considered together with additional information about the device which provides the service. Similar to OPC UA, DPWS also specifies a set of basic services for device discovery, publish / subscribe services for events and metadata exchange services. Additionally, DPWS allows the definition of user specified hosted services which encapsulate device functionality [16]. DPWS does not specify a meta model like OPC UA, or a similar framework for providing semantics. Semantic descriptions for DPWS services are an area of active research [42]. Efficient binary representation of messages is not part of DPWS, but the profile is open enough to allow for usage of data reduction techniques such as the Efficient XML Interchange (EXI) standard [115]. Käbisch et al. [52] showed how EXI can be applied in embedded networks.

DPWS closely fits our description of characteristics for service-oriented architectures in industrial automation. DPWS is directly aimed at constrained devices with only a few kB of RAM and ROM [123], thus allowing an integration of individual devices in the overall SOA. User defined services enable the encapsulation of the device's mechatronic capabilities. The discovery and metadata services provided by DPWS, along with the defined description format for the device itself as well as the hosted services, are a necessary component in an interoperable software architecture. The focus on peer-to-peer messaging between devices allows using DPWS services as part of control algorithms. Thus, we consider DPWS to be an enabling technology for service oriented architectures in the industrial context. The development of DPWS, as well as its use in service-oriented architectures, has been the subject of several EU research projects which we will consider next.

#### 2.2.2.2 Research Projects on Industrial SOAs

The concept of service-oriented architectures emerged during the early 2000s as a way to realize interoperable and cooperating systems in the e-business domain [13]. Research into service-oriented architectures for industrial automation started in 2003 with the "Service Infrastructure for Real-time Embedded Networked Applications" (SIRENA) project which was financed with grants from the European Union. Major progress into service-oriented manufacturing architectures has since been made in several additional EU-projects. Because much of the academic research is conducted in this context this section will focus on work performed as part of the initiatives outlined in Figure 2.5. The projects depicted therein are not following the traditional hierarchical approach, the automation pyramid is only used in this figure to convey an intuition about the relative target area of the differing projects.

The need for modular, interoperable and reconfigurable manufacturing systems was already recognized before the start of the SIRENA project or the advent of service-oriented architectures. Earlier research was focused on agent-based architectures [100], which share some similarities with SOAs. Agents encapsulate functionality and may interact with each other. In contrast to services, an agent is not invoked

but self activating. Agents are therefore often used to implement the concept of holonic manufacturing systems which are composed of self controlled modules, called holons. A holon is "an autonomous and cooperative building block of a manufacturing system" [100]. The concept of the holon can also be applied to modules in a reconfigurable or modular manufacturing system which offer appropriate software services. The remaining conceptual difference between service-oriented and agent-oriented systems lies in their activation semantics: while agents are self-activating and self-regulating, services are often activated by a central orchestrator. Another possibility for service invocation are distributed service choreographies in which services are themselves invoking their successors in a workflow. With choreographies the line between the agent-oriented and service-oriented architectural styles is blurring. For the remainder of the thesis we will continue to use the service-oriented terminology.

Figure 2.5: An overview of the rtSOA research project described in this thesis and several research projects into SOAs for industrial manufacturing financed by grants from the European Union

#### SIRENA 2003-2006

The SIRENA project was started in 2003 to examine the use of SOAs for interconnecting embedded devices in the industrial, automotive, telecommunication and home automation domain [11]. Initial development efforts still used the Universal Plug and Play (UPnP) technology, as DPWS was still being standardized. After the completion of the standardization, DPWS became the intended target technology for the project [11]. One of the major outcomes of the SIRENA effort was the first embedded DPWS-stack, which had a memory footprint of under 200kB [47]. Several tools to simplify the development of DPWS based systems, such as a generator for marshalling and demarshalling of SOAP-XML messages, have also been developed during the project. Based on this implementation an industrial demonstrator [48] was developed which consisted of a dose maker filling granules into a container.

#### SODA 2006-2008

The SIRENA follow-up project "Service Oriented Device and Delivery Architecture" (SODA) extended the SIRENA framework by providing a toolkit for manageability, orchestration and security [79]. Apart from furthering the integration of DPWS services with high-level business processes, SODA also focused on improving the performance and serviceability of the DPWS infrastructure [79]. Together, these two projects proved the feasibility of DPWS-based architectures on embedded devices.

#### RI-MACS 2005-2008

The "Radically Innovative Mechatronics and Advanced Control Systems" (RI-MACS) project is the first effort that takes real-time requirements into account, which could not be fulfilled by DPWS or other web service technologies at the time [19, 26]. DPWS is used for interaction with higher level systems which have no, or only relaxed, timing requirements. More time critical tasks are implemented through a separate communication stack which is build directly upon TCP/IP or UDP/IP instead of the HTTP / SOAP / DPWS protocols used by general services. A custom protocol stack may also be used to interact with legacy or hard real-time systems.

#### SOCRADES 2006-2009

The "Service Oriented Cross-Layer Infrastructure for Distributed Smart Embedded Devices" (SOCRADES) project built on the SIRENA and SODA results to further the vertical cross-layer integration between shop floor and enterprise systems [102]. The project also focused on the questions of how legacy devices could be integrated into a service-oriented architecture and how the evolution of existing manufacturing systems and plants towards a SOA can be accomplished [55]. When executing a stepwise transformation to a SOA, it may not always be feasible to replace legacy devices with SOA-capable devices. In these cases gateways or service mediators can be used. Gateways function as a service-facade for an individual device whereas service mediators offer a higher level view focused on functionality instead of representing an individual device. Therefore, service mediators may have internal data aggregation or composition functionality [55].

SOCRADES achieved an initial integration of constrained devices on the lower levels of the automation pyramid, but identified orchestration, determinism of the SOA run-time behavior, decentralization and effective reconfiguration as open research issues [106]. The project also focused on the engineering aspects of networks of smart devices, leading to new tools and technologies for modeling, design, implementation and operation of these new kinds of distributed embedded systems [17]. One of the major take-away messages from the project is that the effort required to add web service capabilities increases for devices further down the automation hierarchy. However, the benefits of having a service enabled device are also increasing when moving further down in the traditional automation pyramid [55].

#### AESOP 2010-2014

The SOCRADES follow-up project "Architecture for Service Oriented Process -Monitoring and -Control" (AESOP) [23] investigated the feasibility and limits of using a SOA-based approach inside control loops [46]. By implementing several prototypes, the project closely investigated the performance implications of using web services for the concurrent control of several thousand devices, thus addressing some of the open issues raised by SOCRADES. One real-world showcase included the migration of a legacy plant lubrication system to a service-oriented architecture [84], addressing issues such as SOA on low-level devices and in closed-loop control [24]. AESOP achieved cross-layer collaboration of services and devices mainly through use of an orchestration engine, which constitutes an event based model with central control through an orchestrator. Other research within the project highlighted the benefits of decentralized execution plans for service choreographies over using centralized service orchestrations for automation tasks. Starke et al. implemented an event-based choreography engine for service-oriented automation and observed a higher degree of performance and reactivity in an choreography based approach when compared to an approach based on orchestration [104].

#### Arrowhead 2013-2017

The Arrowhead project consolidates previous research into a comprehensive framework that supports the development, deployment and operation of cooperative systems in a SOA [110]. Its main contributions are design guidelines and patterns for faster engineering; documentation guidelines and templates on the levels of individual services, systems, and systems-of-systems; and a software framework build around core services which support the interaction of application specific services across different base technologies. Among the provided core set are services for discovery, authorization, orchestration and status monitoring. They address the main technical questions examined in the Arrowhead project: How can systems advertise their services and discover remote services? How can systems ensure that only authorized entities may consume its services? How can systems-of-systems be orchestrated?

#### Comparison with our approach

SIRENA, SODA and SOCRADES achieved the vertical integration of industrial control devices with higher-level enterprise systems. Arrowhead mostly focused on engineering related questions and orchestration of systems-of-systems. Since our work on rtSOA is focused on providing hard real-time guarantees on the underlying device level, RI-MACS, and especially AESOP, can be considered conceptually similar projects. AESOP showed the feasibility of integrating embedded devices in a control loop through a SOA. In our opinion, message exchange in a control loop is possible by leveraging one of the protocol stacks investigated by AESOP [46]. Additionally, work performed in the context of the AESOP project has already pointed out that a distributed choreography approach to SOA is preferable to the classical orchestration-based approach [104]. Our work focuses on the planning required to achieve performant, hard real-time execution plans for devices in a tight control loop.

Our proposal for a real-time service-oriented architecture (rtSOA) reconciles the SOA paradigm with predictable execution semantics while enabling decentralized coordination of devices. rtSOA implements decentralized execution plans for service choreographies and focuses on the temporal aspects required to offer deterministic, predictable and verifiable real-time properties, thus addressing the research questions raised by SOCRADES. The AESOP design can be united with the rtSOA approach to achieve both event-based flexibility and cyclic determinism where needed: A cyclic sub-system, scheduled with rtSOA, can periodically trigger events which are then processed by an event-based architecture on higher layers.

## 2.2.3 Industrie 4.0

Industrie 4.0 is heralded as the fourth industrial revolution, with the three previous revolutions being the mechanization of industry beginning in the 1780s, the electrification starting in the 1870s and finally the introduction of computer control in the 1970s. The unique aspect of Industrie 4.0 is seen in the advent of *Cyber-Physical Systems* (CPS) [7,53,112]. Cyber-Physical Systems are computer systems which register properties from the physical world via sensors and are often also able to affect these properties via actuators. So far, this is identical to the definition of an embedded system. The defining properties of cyber-physical systems are the aspects of networking, interconnectedness and advanced decision making and reasoning [7,53,73].

In the United States a different classification and terminology is being used: The *Industrial Internet* is seen as the third wave of innovation and productivity increase after the industrial revolution and the internet revolution. The Industrial Internet is characterized as the convergence of industrial systems with sensing and computing power, as well as networking capabilities [37]. These technical enablers are combined with an analytical and predictive evaluation of the gathered data. This description is similar to the definition of a CPS in the Industrie 4.0 context.

The Industrie 4.0 vision also calls for a horizontal and vertical integration of smart factories within a company and even with other companies along its value chain [53]. The definition of vertical integration is identical to the meaning of the term in the SOA context as it implies an interconnection between processes on the lowest layer of the production floor with enterprise planning modules. Leveraging this data effectively through analytical and predictive evaluation is the area of big-data and complex event processing systems [7,97]. Horizontal integration encompasses more than interconnection of devices within a factory or within a single enterprise. In the Industrie 4.0 model, there should be a connection between the manufacturing systems of a company, its logistics process, its suppliers, and customers. The horizontal and vertical integration is envisioned through a large scale application of serviceoriented architectures, called the *Internet of Services* [7,53]. Service-orientation of individual machines and devices is an important part of this architecture [97]. Finally, end-to-end engineering in the context of Industrie 4.0 refers to the use of modelbased techniques in an integrated engineering environment for the development and optimization of products and the associated manufacturing system [53].

To conclude, Industrie 4.0 and the Industrial Internet describe the concept of leveraging Cyber-Physical Systems for increased flexibility, awareness and data-driven decision support in several industries with the manufacturing industry at the forefront. Service-oriented architectures and model-based design, simulation and visualization are integral parts of this vision [7,37,53]. Efforts in developing a reference architecture for Industrie 4.0 name service-oriented architectures as a key component and enabler [111]. The SOA should extend down to the manufacturing process where suitable orchestration techniques are an important building block [53]. Our work inside the rtSOA project focuses at providing engineers with an easy and intuitive way to specify service compositions in a declarative way influenced by distributed data processing principles. rtSOA users can quickly evaluate the implications of their design decisions through simulation, verification and visualization of the generated execution plans. These decentralized plans can be deployed automatically to devices in a service-oriented architecture. The next chapter will introduce the rtSOA architecture and its execution semantics before we detail and evaluate the heuristics-based rtSOA planning process in Chapter 4.2. Additional challenges arise from the vision of hosting some parts of the automation logic in the cloud [56], especially when considering the lack of fault tolerance in current publish / subscribe middleware facing complex failures scenarios such as byzantine failures or selfish node behavior [80].

"I LOVE DEADLINES. I LOVE THE WHOOSHING NOISE THEY MAKE AS THEY GO BY."

- Douglas Adams

CHAPTER 3

The rtSOA Approach

Parts of this chapter have been previously published in [64–67].

This chapter introduces our approach, named rtSOA, for service-oriented architectures with real-time execution plans. It reconciles the flexibility and reconfigurability of a SOA with the timing guarantees and determinism required for hard real-time systems. The development of systems with rtSOA follows principles of distributed data processing (DDP) systems and hides much of the networking and timing issues from the engineer. The design goals and principles of the rtSOA architecture are explained in Section 3.1. Based on these principles, and the assumptions detailed in Section 3.2, Section 3.3 introduces the basic rtSOA architecture. Coherent semantics are required to generate execution plans for any distributed data processing system. Section 3.4 is therefore giving an in-depth analysis of the dataflow-driven execution semantics of rtSOA. We conclude the chapter by discussing alternative design decisions for rtSOA and placing it in context with related work in Section 3.5.

# 3.1 Design Goals and Principles

The target domain of rtSOA are distributed hard real-time systems for industrial automation. The changing realities of the manufacturing world necessitate a focus on flexibility, reconfiguration and reuse (c.f. Chapter 2). rtSOA is thus focused on applying DDP principles to modular and reconfigurable manufacturing systems in the smart factory ecosystem envisioned with Industrie 4.0. This section presents the design goals for rtSOA and the principles behind the rtSOA design philosophy. The term rtSOA refers to a service-oriented architecture for embedded real-time systems based on DDP principles. We distinguish between the rtSOA architecture and the following pieces of software:

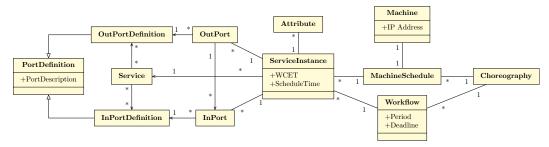

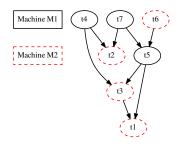

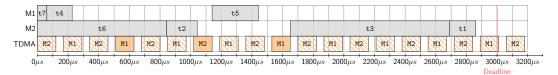

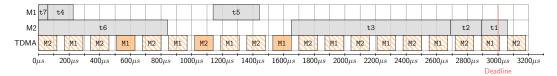

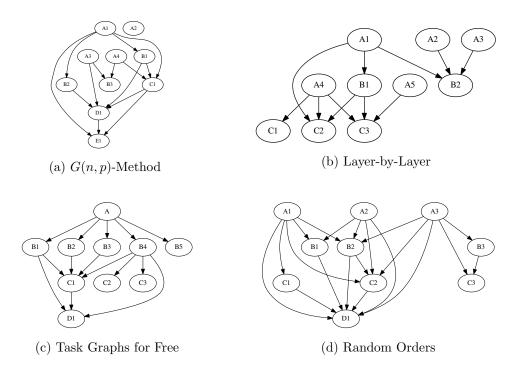

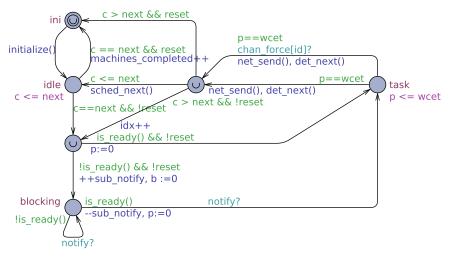

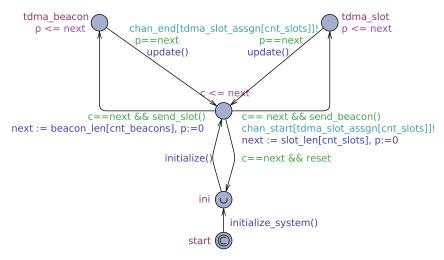

- rtSOA planner: The planner is the algorithmic core that generates rtSOA execution plans from abstract workflow descriptions. Its inputs are one or multiple workflows modeled as a task graph and a representation of the target system's infrastructure, i.e.,the available machines and the network configuration. The planner's output is a static schedule for each of the machines. These schedules constitute the rtSOA execution plan.

- rtSOA runtime: The rtSOA runtime is the software running on the individual devices partaking in the execution plan. The runtime is tasked with executing the schedule generated by the rtSOA planner by invoking the individual service instances and routing the messages between them.

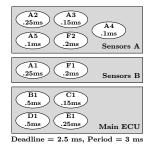

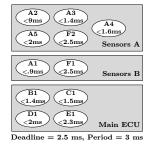

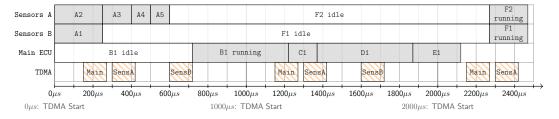

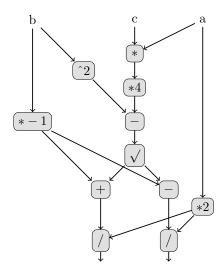

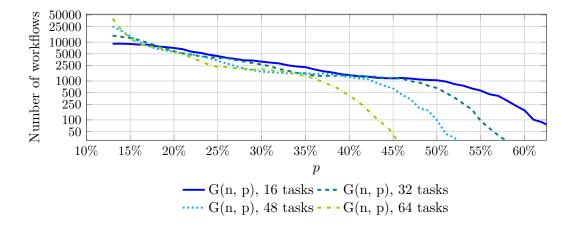

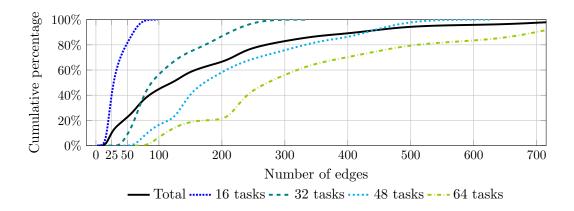

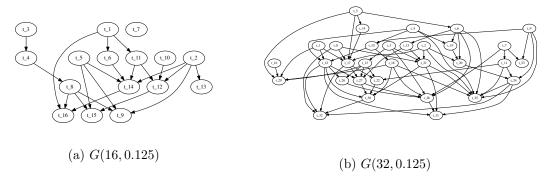

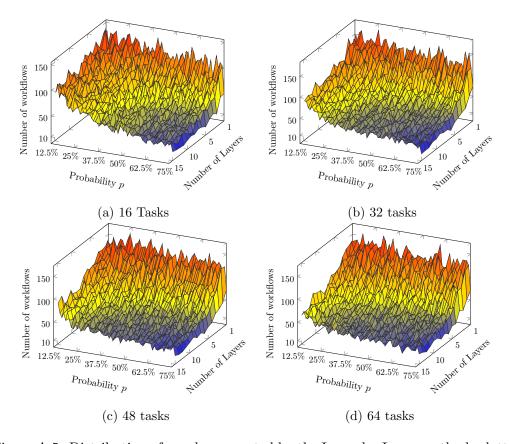

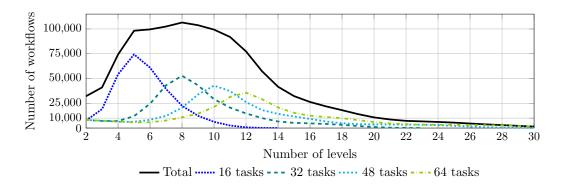

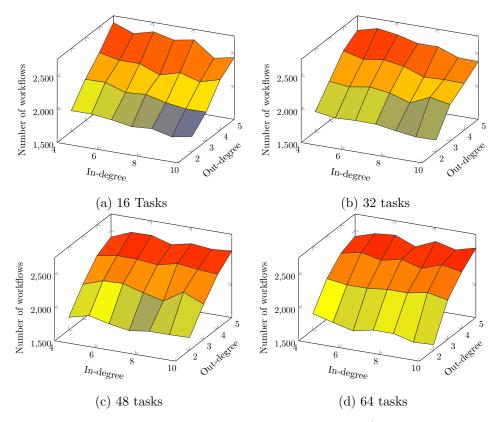

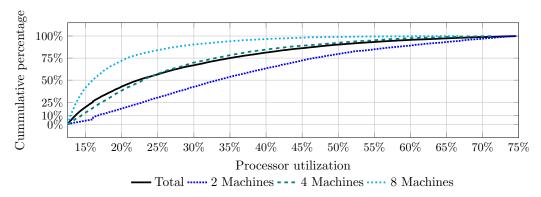

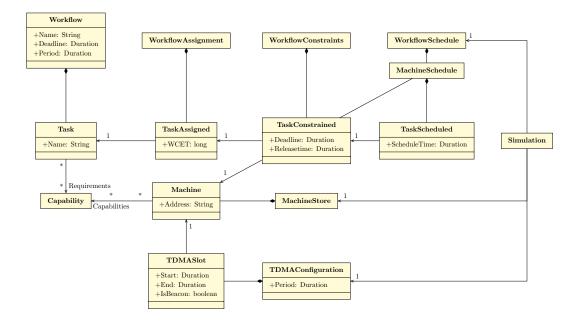

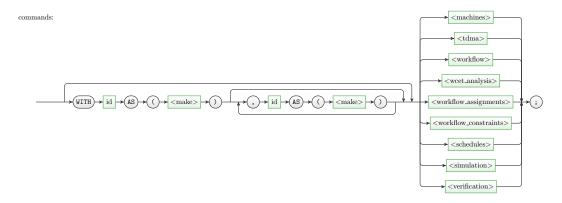

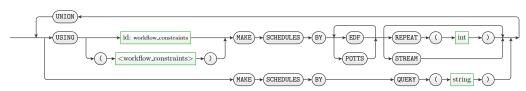

- rtSOA user interface (GUI): The rtSOA GUI is an engineering tool used to composite individual services into workflows by arranging the services in a graph through specification of the messages passed from one service instance to another. The feasibility of a workflow on a given infrastructure can be determined by the rtSOA planner, which can be triggered from the GUI. The GUI can also be used to deploy a new execution plan to the machines.