## TECHNISCHE UNIVERSITÄT MÜNCHEN Institut für Informatik Lehrstuhl für Echtzeitsysteme und Robotik

## A Model-Based Framework for System-Wide Plug-and-Play with Flexible Timing Verification for Automotive Systems

#### Hauke Stähle

Vollständiger Abdruck der von der Fakultät für Informatik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender: Prof. Dr. Hans Michael Gerndt Prüfer der Dissertation: 1. Prof. Dr.-Ing. habil. Alois Knoll

2. Hon.-Prof. Dr.-Ing. Gernot Spiegelberg,

Universität Budapest/Ungarn

Die Dissertation wurde am 12.11.2015 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 08.03.2016 angenommen.

#### **Abstract**

The integration of hardware and software components into today's vehicles from a variety of suppliers is a complex process and becomes more and more challenging. The amount of code and data as well as the number of interconnections increases rapidly and pushes the complexity of the on-board electronic systems and the involved infrastructure to new limits. This stands in contrast with the constantly growing demand for new functionalities to enhance safety, comfort, and efficiency. Integration expenses are an increasing problem during design time and the addition of hardware and software to a vehicle after sale is limited today, because the systems are developed in a static manner.

To ease the integration process and to allow the addition of functionality after sale, a model-based framework is proposed in this work that combines the plugand-play concept with an automatic timing verification to fulfill the real-time requirements of automotive systems. The idea is to divide the functionality of a vehicle into individual features that can be freely composed. Each feature consists of a set of hardware and software components as well as communication and timing requirements, which are automatically matched and verified in the resulting system setup. Addition of further features and automatic reverification is possible at any point in time with an adjustable approximation level. The approach is capable to process event-based communication patterns and is based on the data-centric design principle, i.e., data senders and receivers are loosely coupled.

The contributions of this work comprise the introduction of the system-wide plug-and-play approach, the definition of a minimal set of suitable models, transformation patterns for a mapping to exemplary technologies, and the introduction of a method to specify timing requirements for unknown setups. They further include the development of a performance verification tool based on the Real-Time Calculus framework, its enhancement for the automatic processing of cyclic resource dependencies, and the design of an approach to control the approximation of the analysis and trade tightness of the derived timing bounds for computation time.

The feasibility of the approach is shown by a running example based on the electric vehicle demonstrator (eCar) throughout this work. The performance of the extensions and approximation approaches for the verification process are examined in detail by a series of experiments.

#### Zusammenfassung

Die Integration von Hardware- und Softwarekomponenten verschiedenster Zulieferer in heutige Fahrzeuge ist ein komplexer Vorgang und wird immer schwieriger. Die Menge an Software und Daten sowie die Anzahl der Verbindungen steigt rapide an und bringt die Komplexität der Elektronik im Fahrzeug und der benötigten Infrastruktur an ihre Grenzen. Dies steht im Widerspruch zu dem stetig wachsenden Bedarf an neuen Funktionen um Sicherheit, Komfort und Effizienz zu erhöhen. Die Kosten für die Integration zur Entwurfszeit sind ein zunehmendes Problem und das Hinzufügen von neuer Hardware und Software in ein Fahrzeug ist heutzutage nach dem Kauf nur eingeschränkt möglich, weil die Systeme statisch entwickelt werden.

Um den Integrationsprozess zu vereinfachen und um das Hinzufügen von Funktionen nach dem Kauf zu ermöglichen, wird in dieser Arbeit ein modellgetriebener Ansatz erläutert, welcher den Plug-and-Play-Gedanken mit einer automatisierten zeitlichen Verifikation verknüpft, um den Echtzeitanforderungen eines Fahrzeugsystems gerecht zu werden. Die Idee besteht aus einer Aufteilung der Funktionen eines Fahrzeugs in einzelne Features, welche frei miteinander kombiniert werden können. Jedes Feature kann eine Menge von Hardware- und Softwarekomponenten beinhalten sowie Anforderungen bezüglich der Kommunikation und des zeitlichen Verhaltens, welche automatisiert verarbeitet und in der resultierenden Systemausprägung verifiziert werden. Das Hinzufügen von weiteren Features und die erneute automatisierte Verifikation sind zu jedem Zeitpunkt möglich mit einer freien Wahl des Approximationsgrades. Der Ansatz ist in der Lage, ereignisbasierte Kommunikationsmuster zu verarbeiten und basiert auf dem datenzentrischen Entwurfsprinzip, bei dem die Sender und Empfänger von Daten lose miteinander verbunden sind.

Die Beiträge dieser Arbeit umfassen die Einführung des systemweiten Plugand-Play-Ansatzes, die Definition einer minimalen Menge von geeigneten Modellen, Transformationsmuster für eine Abbildung auf exemplarische Technologien und die Beschreibung einer Methode zur Spezifikation von zeitlichen Anforderungen in unbekannten Konfigurationen. Sie beinhalten weiterhin die Entwicklung eines Werkzeugs, basierend auf dem Real-Time Calculus, zur Verifikation des zeitlichen Verhaltens und dessen Erweiterung zur automatisierten Verarbeitung von zyklischen Abhängigkeiten sowie dem Entwurf einer Möglichkeit, die Approximation der Analyse zu steuern und somit die Genauigkeit der berechneten Zeitgrenzen gegen Berechnungsaufwand einzutauschen.

Die Realisierbarkeit des Ansatzes wird mittels eines durchgängigen Beispiels innerhalb dieser Arbeit aufgezeigt, welches auf dem elektrischen Fahrzeugdemonstrator (eCar) basiert. Die Eigenschaften der Erweiterungen und Approximationsmethoden für den Verifikationsvorgang werden durch eine Reihe von Experimenten untersucht.

#### **Danksagung**

Die vorliegende Arbeit entstand während meiner Anstellungen als wissenschaftlicher Mitarbeiter am Lehrstuhl für Echtzeitsysteme und Robotik an der Technischen Universität München sowie am Forschungs- und Transferinstitut fortiss. Mein Dank geht an Professor Alois Knoll für das Ermöglichen dieser Arbeit, seine wissenschaftliche Betreuung und unterstützende Organisation. Ebenso danke ich Professor Gernot Spiegelberg für seinen Einsatz als Projektleiter von Diesel Reloaded, die vielen aufgebrachten Stunden und die Chance an seinem Weitblick teilhaben zu dürfen. Mein Dank gilt Claudia Meis und Dr. Ljubo Mercep für die gegenseitige Hilfe in unserem gemeinsamen Projekt und darüber hinaus. Dr. Christian Buckl möchte ich für die konstruktiven Ratschläge in allen Belangen danken, für die Möglichkeit, in seiner Forschungsgruppe mitwirken zu dürfen und für den stets motivierenden Umgang. Dr. Kai Huang gebührt mein Dank für seinen Optimismus, seine wissenschaftliche Kompetenz und für die hilfreichen Kommentare zu dieser Arbeit. André Gaschler und Michael Geisinger danke ich für die wertvollen Vorschläge nach dem Durchsehen dieser Ausarbeitung. Meinen Kollegen Benjamin Wiesmüller, André Leimbrock und Michael Geisinger danke ich für ihre Geduld und Verständnis, als ich mich in den letzten Schritten dieser Dissertation nur mit reduzierter Kraft unserem Vorhaben widmen konnte. Ein umfangreiches Lob gilt den von mir betreuten Studenten für ihr entgegengebrachtes Vertrauen und Engagement. Dies sind in alphabetischer Reihenfolge: Roshan Chulyada, Christian Dietz und Raphael Haase. Darüber hinaus möchte ich dem gesamten Lehrstuhl für Echtzeitsysteme und Robotik an der TUM sowie der Gruppe Cyber-Physical Systems am fortiss danken für den freundlichen und kooperativen Umgang miteinander.

Meiner Freundin gilt ein besonderer Dank für ihre entgegengebrachte Wärme, die notwendige Ablenkung und die Übernahme vieler Aufgaben, damit ich mich intensiv dieser Arbeit widmen konnte. Bei meinen Freunden bedanke ich mich für das erholende Einbringen von anderen Gedanken in mein Leben.

Zuletzt, aber nicht minder wichtig, möchte ich meiner Familie danken, welche mich aus der Ferne stets in meinen Vorhaben unterstützt und an meinen Erfolg glaubt.

München, im Oktober 2015

Hauke Stähle

# **Contents**

| Lis | st of             | figures                                                   | iii      |

|-----|-------------------|-----------------------------------------------------------|----------|

| Lis | st of 1           | tables                                                    | vii      |

| Lis | st of a           | acronyms                                                  | ix       |

| Lis | st of s           | symbols and operators                                     | xi       |

| 1   | Intr              | oduction                                                  | 1        |

|     | 1.2<br>1.3<br>1.4 | Factors increasing the complexity and amount of functions | 10<br>11 |

| 2   | Mod               | leling and timing verification background                 | 13       |

|     | 2.1               | Component-based development                               | 13       |

|     | 2.2               | Data-centric communication                                |          |

|     | 2.3               | Model-driven engineering                                  | 14       |

|     | 2.4               | Time modeling, representation, and constraints            |          |

|     | 2.5               | Timing analysis methods                                   | 20       |

|     | 2.6               | Real-Time Calculus and Modular Performance Analysis       | 23       |

|     | 2.7               | Modeling and verification background summary              | 30       |

| 3   | Con               | nbining plug-and-play and timing guarantees               | 31       |

|     | 3.1               | Requirements for a flexible verification approach         | 31       |

|     | 3.2               | Method for system-wide plug-and-play                      | 33       |

|     | 3.3               | Introduction of the running example                       | 41       |

|     | 3.4               | Combining plug-and-play and timing guarantees summary     | 44       |

| 4   |                   | quate meta-models                                         | 45       |

|     | 4.1               | Requirements for adequate meta-models                     | 46       |

|     | 4.2               | Meta-model representation                                 | 47       |

|     | 43                | FEATURE meta-model                                        | 48       |

#### **CONTENTS**

|    | 4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10 | FEATURE-SET meta-model  SYSTEM meta-model  DATA meta-model  LOGICAL meta-model  DEPLOYMENT meta-model  TIMING REQUIREMENTS meta-model  Adequate meta-models summary                                                                                                                   | 49<br>51<br>51<br>53<br>56 |

|----|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 5  |                                                | lel transformation and platform mapping  Transformation from a Feature-Set model to a combined Feature model                                                                                                                                                                          | <b>63</b> 64               |

|    | <ul><li>5.2</li><li>5.3</li><li>5.4</li></ul>  | Transformation from a combined Feature model to an Instance model Platform mapping: From an Instance model to an Analysis model Model transformation and platform mapping summary                                                                                                     | 64<br>70<br>79             |

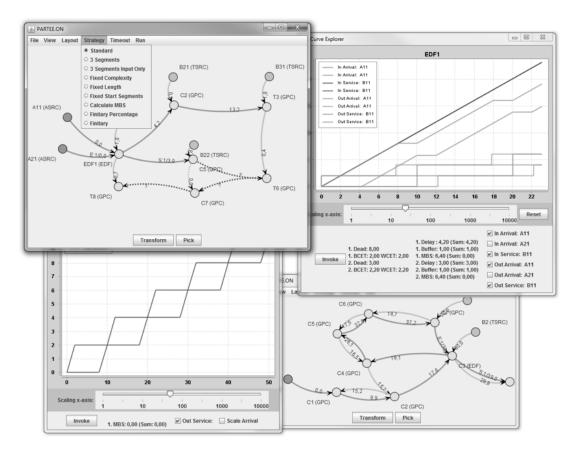

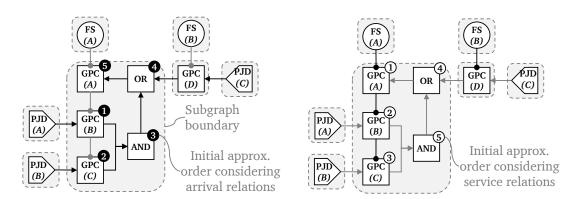

| 6  | Tim: 6.1 6.2 6.3 6.4 6.5 6.6 6.7               | ing verification framework  Refined Analysis meta-model (M)  Analysis and verification procedure  Implementation  Automatic handling of resource cycles in the system graph  Bounded buffer handling  Discussion of the verification framework  Timing verification framework summary | 82<br>84<br>90<br>92<br>98 |

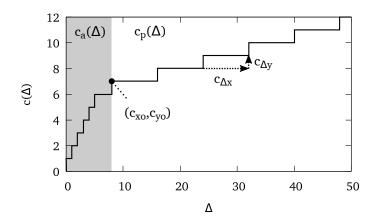

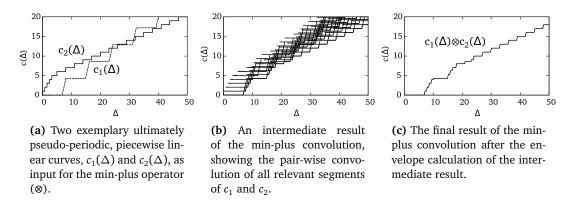

| 7  | 7.1<br>7.2<br>7.3<br>7.4                       | ptive approximate analysis  Effects on the computation time of the analysis                                                                                                                                                                                                           | 102<br>106                 |

| 8  | <b>Con</b> 8.1 8.2                             | Summary of contributions                                                                                                                                                                                                                                                              |                            |

|    | A.1<br>A.2<br>A.3<br>A.4                       | Related work                                                                                                                                                                                                                                                                          | 135<br>139<br>140          |

| Re | feren                                          | nces 1                                                                                                                                                                                                                                                                                | 143                        |

# List of figures

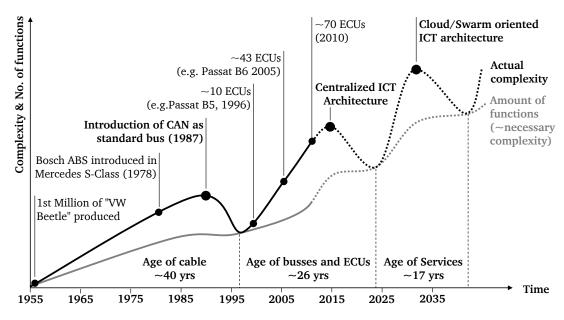

| 1.1  | Development of automotive electronic architecture complexity       | 2  |

|------|--------------------------------------------------------------------|----|

| 1.2  | Research and technology demonstrator InnoTruck                     | 3  |

| 1.3  | Sidesticks of the InnoTruck                                        | 2  |

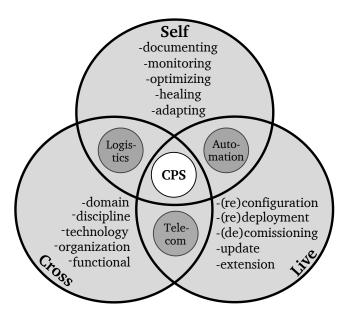

| 1.4  | Properties of smart cyber-physical systems                         | 7  |

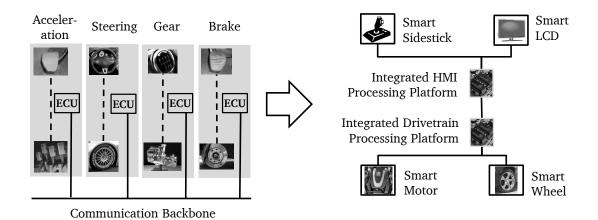

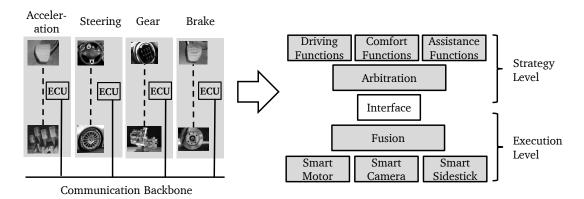

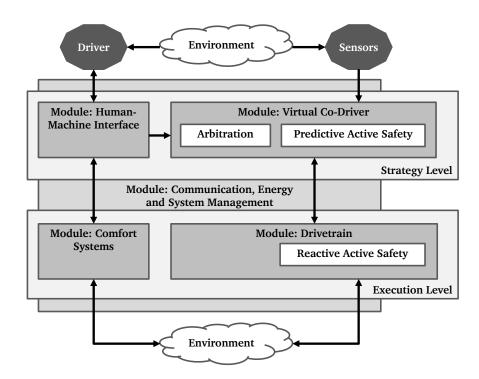

| 1.5  | Centralization of the physical architecture by integration         | 8  |

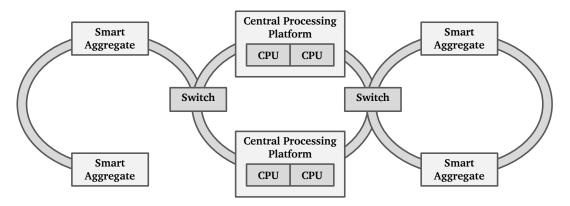

| 1.6  | RACE architecture as an example of a physically centralized design | 9  |

| 1.7  | Centralization of the logical architecture by horizontal design    | 9  |

| 1.8  | The 5-module approach                                              | 10 |

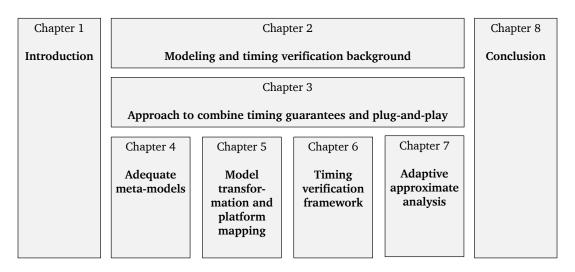

| 1.9  | Structure of this thesis                                           | 12 |

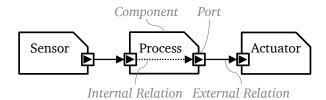

| 2.1  | Example of a component-based system design                         | 13 |

| 2.2  | Entities of the data-centric communication paradigm                | 14 |

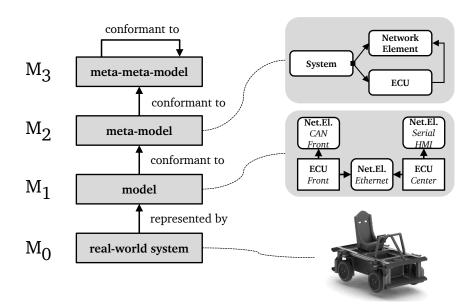

| 2.3  | Modeling layers                                                    | 15 |

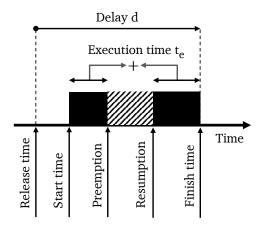

| 2.4  | Times associated with a task execution                             | 18 |

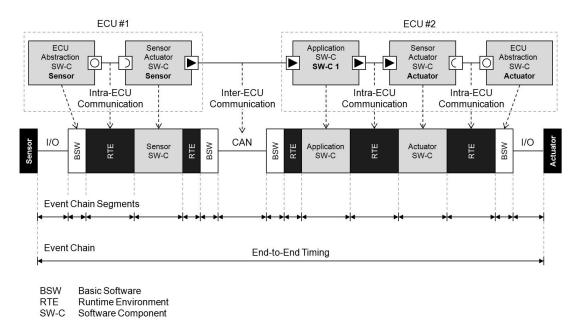

| 2.5  | Example of an event chain and the related end-to-end timing        | 19 |

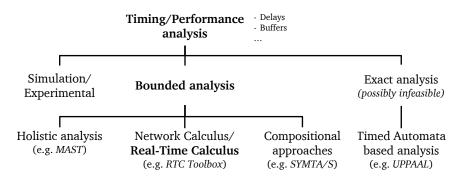

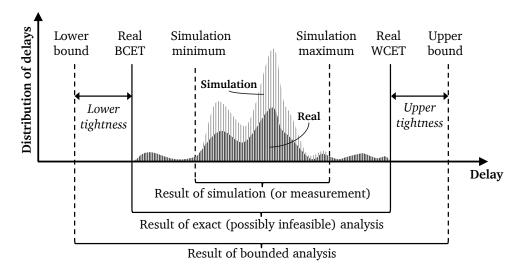

| 2.6  | Structuring of performance analysis methods                        | 20 |

| 2.7  | Comparison of bounded analysis to other analysis methods           | 21 |

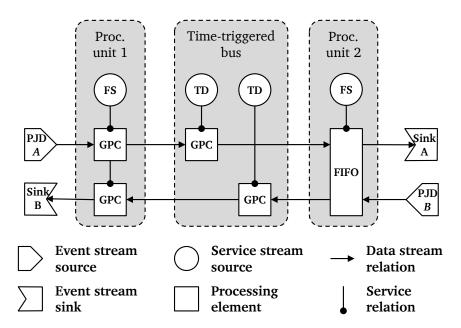

| 2.8  | Example system model of the Real-Time Calculus framework           | 24 |

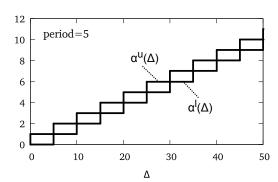

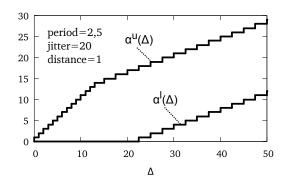

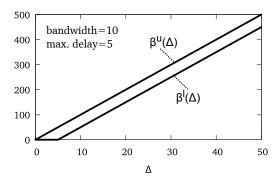

| 2.9  | Examples of arrival curves                                         | 26 |

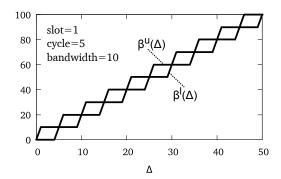

|      | Examples of service curves                                         |    |

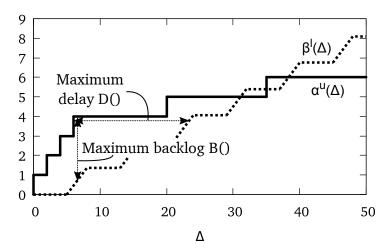

| 2.11 | Delay and backlog                                                  | 29 |

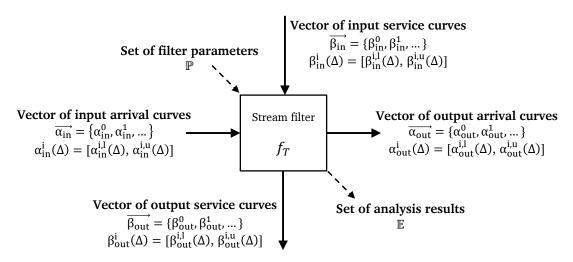

| 2.12 | Stream filter element                                              | 30 |

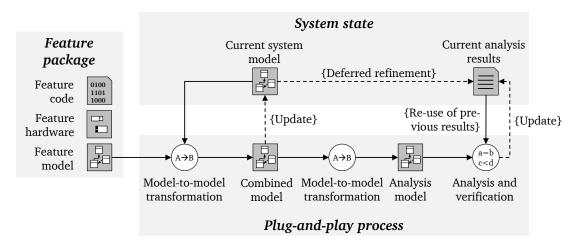

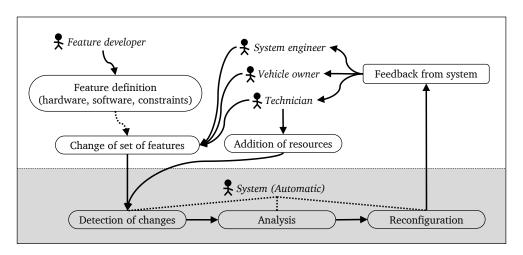

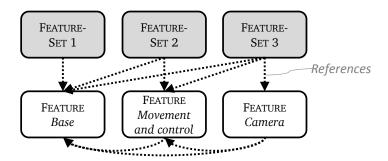

| 3.1  | System-wide plug-and-play process and involved artifacts           | 34 |

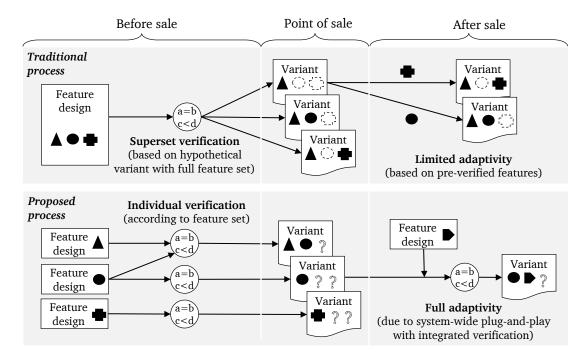

| 3.2  | Development and adaption timeline                                  | 35 |

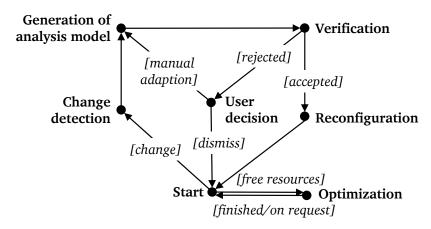

| 3.3  | Phases of the system-wide plug-and-play approach                   | 36 |

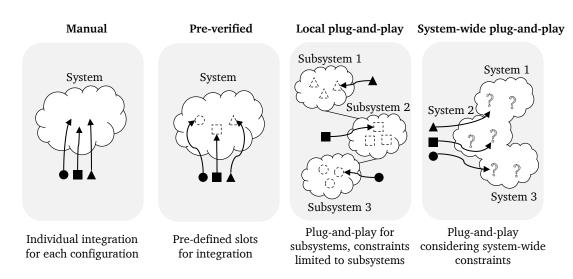

| 3.4  | Comparison of integration variants                                 | 38 |

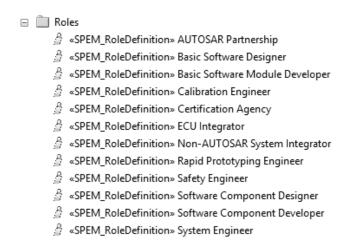

| 3.5  | Roles defined in AUTOSAR                                           | 39 |

| 3.6  | Roles within the system-wide plug-and-play approach                | 40 |

| 3.7  | Rendering of the eCar demonstrator                                 | 41 |

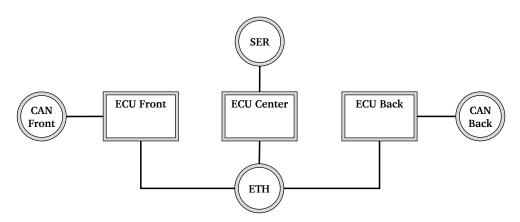

| 3.8  | The base feature of the eCar                                       |    |

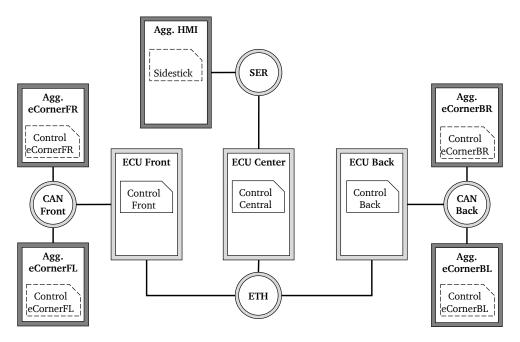

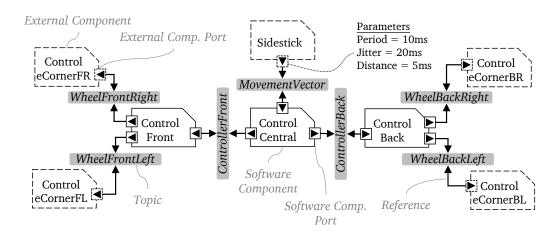

| 3.9  | The <i>movement and control</i> feature of the eCar                | 43 |

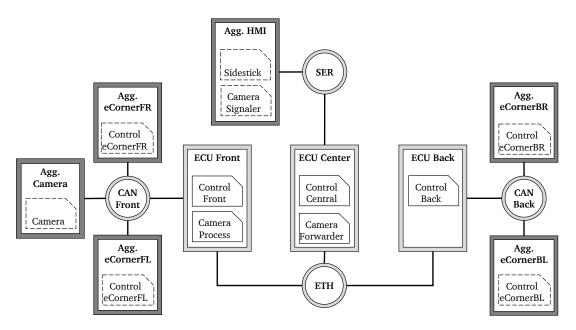

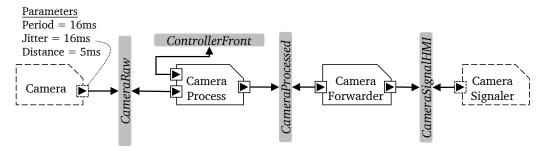

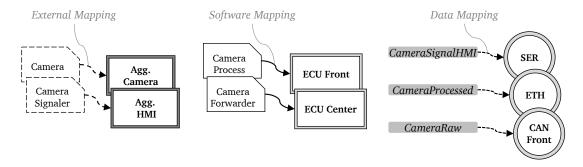

| 3.10 | The <i>camera</i> feature of the eCar                              | 43 |

#### LIST OF FIGURES

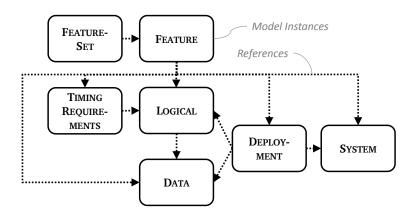

| 4.1  | Relations of the models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 46  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

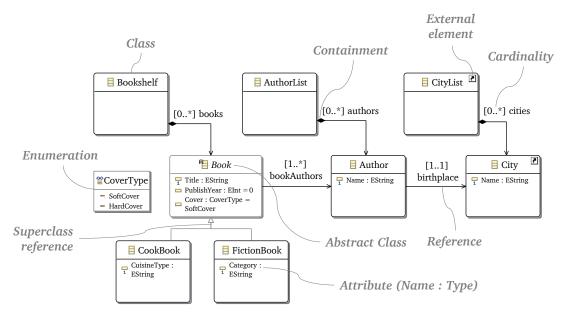

| 4.2  | Visualization of the used modeling elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 48  |

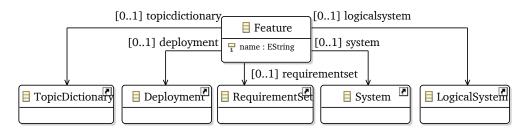

| 4.3  | Feature meta-model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 48  |

| 4.4  | Feature-Set meta-model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

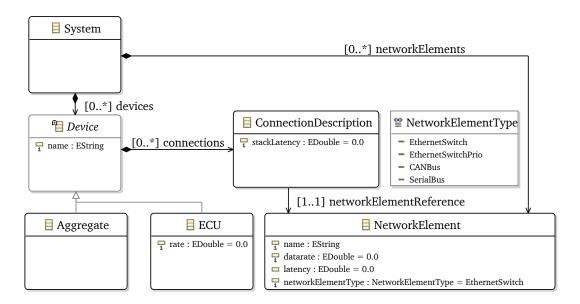

| 4.5  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 49  |

| 4.6  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 50  |

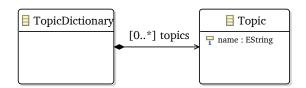

| 4.7  | Data meta-model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51  |

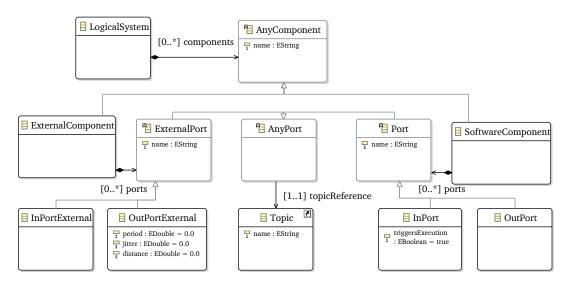

| 4.8  | LOGICAL meta-model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|      | LOGICAL model of the movement and control feature of the eCar example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53  |

|      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 54  |

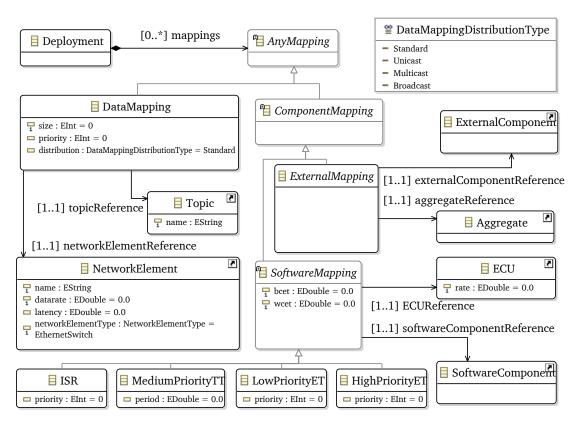

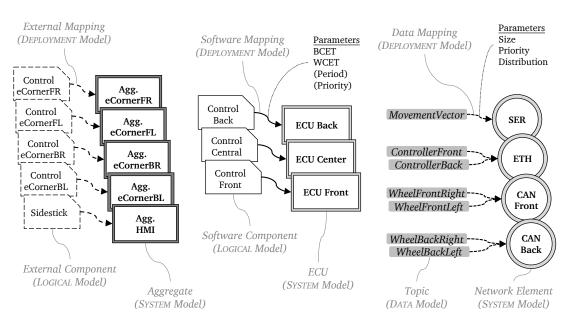

|      | DEPLOYMENT model of the movement and control feature of the eCar example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|      | <del>-</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55  |

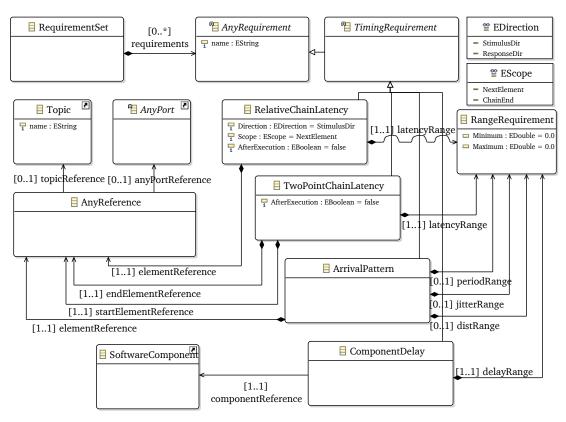

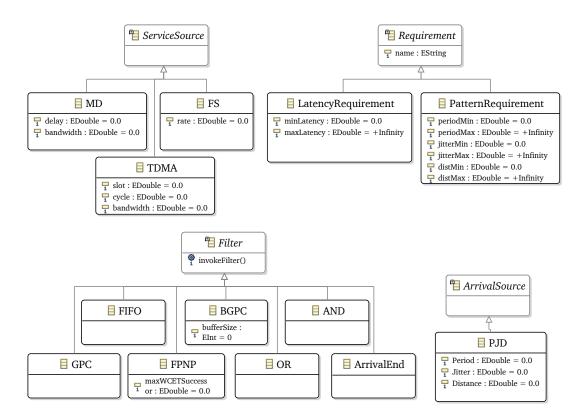

|      | TIMING REQUIREMENTS meta-model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

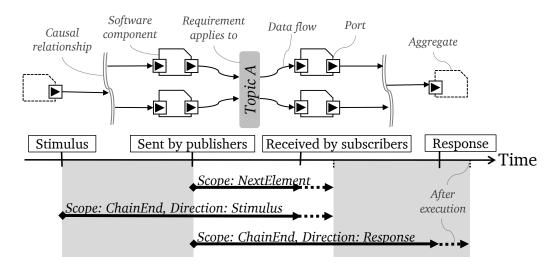

|      | Elaboration of RelativeChainLatency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

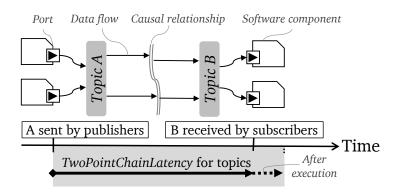

|      | Elaboration of TwoPointChainLatency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 1110 | Enabolation of two outcomes and the control of the | 0,  |

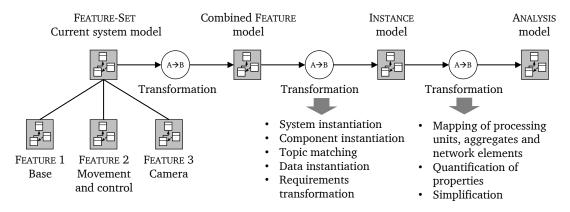

| 5.1  | Transformation steps from a Feature-Set model to an Analysis model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 63  |

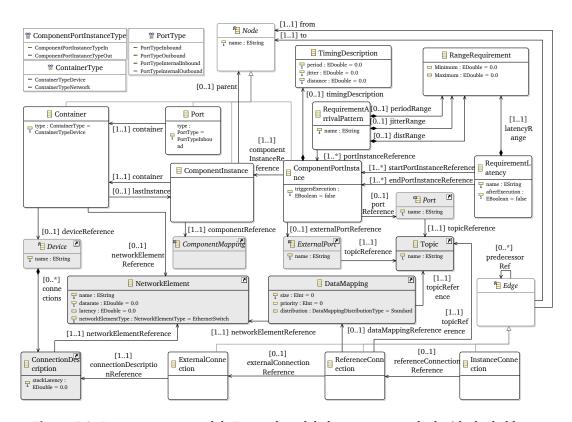

| 5.2  | Instance meta-model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 66  |

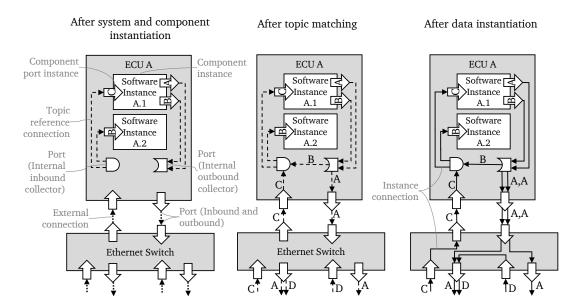

| 5.3  | Exemplary visualization of transformation chain steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 67  |

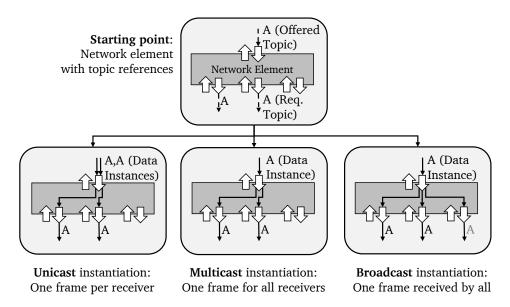

| 5.4  | Distribution variants and impact on the data instantiation process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 67  |

| 5.5  | Example for the transformation from an Instance model to an Analysis model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70  |

| 5.6  | Simplified representation of the ANALYSIS meta-model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 71  |

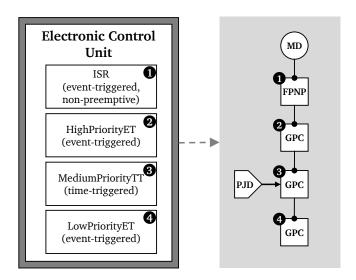

| 5.7  | Mapping of software component instances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 72  |

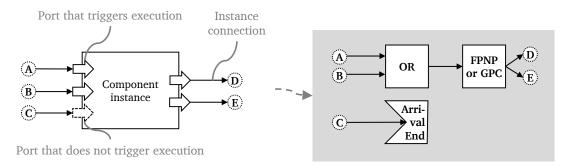

| 5.8  | Example for the handling of execution triggers and multiple outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 73  |

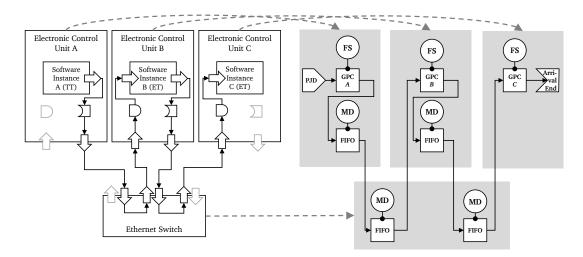

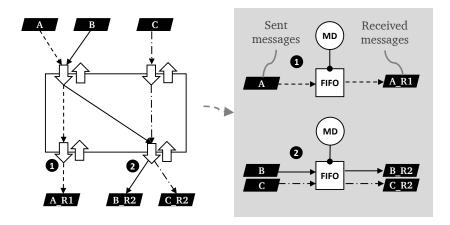

| 5.9  | Mapping of a switched Ethernet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 76  |

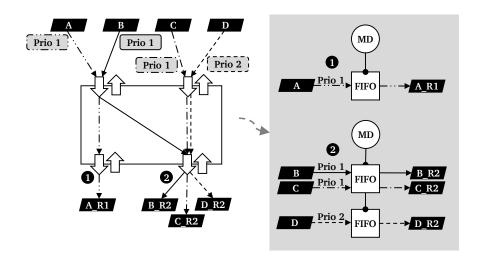

| 5.10 | Mapping of a priority-based switched Ethernet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 77  |

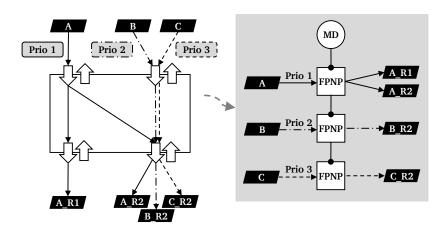

| 5.11 | Mapping of a CAN bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 78  |

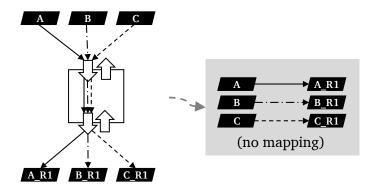

| 5.12 | Mapping of a serial bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 79  |

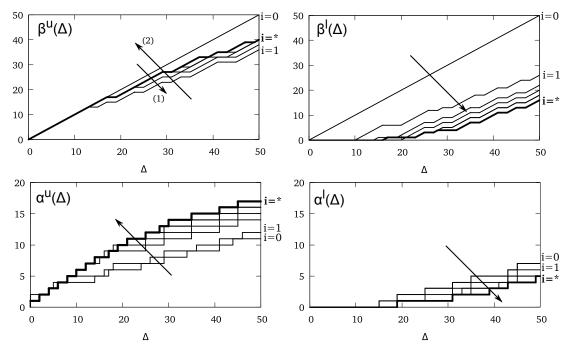

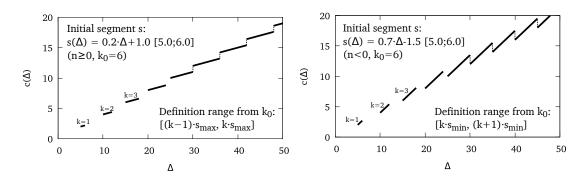

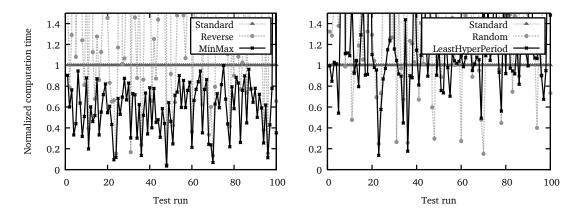

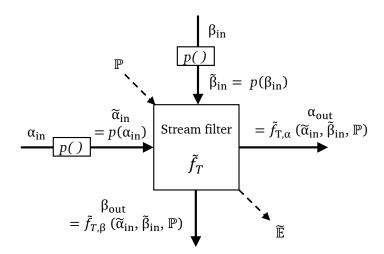

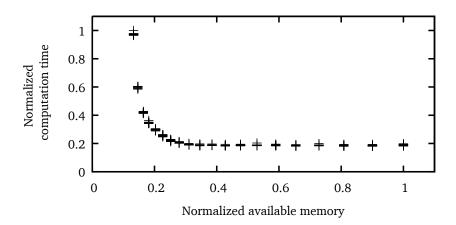

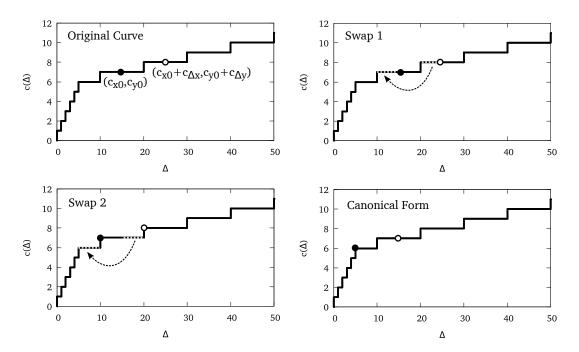

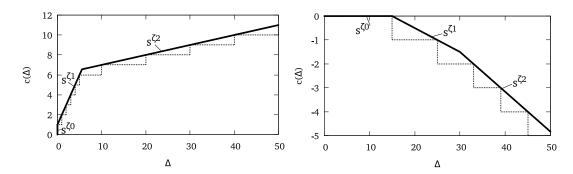

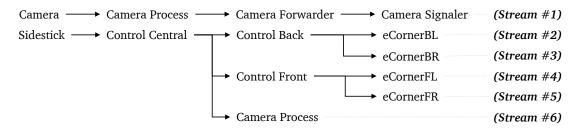

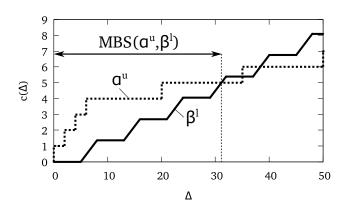

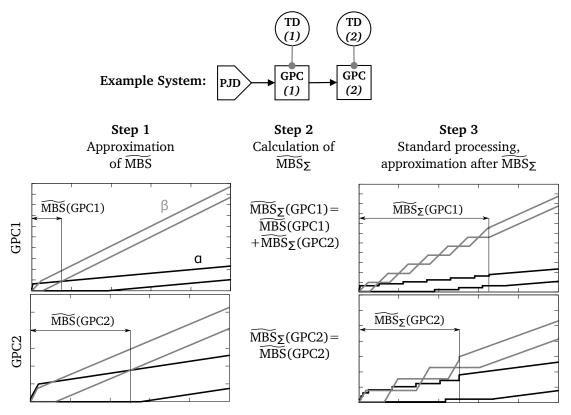

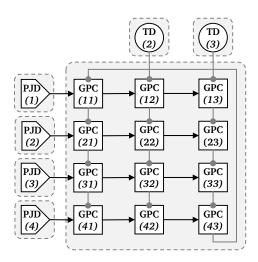

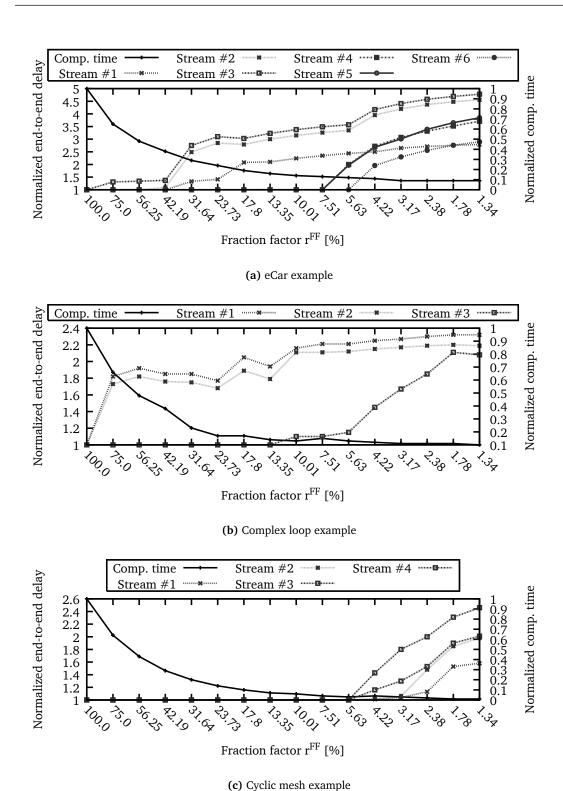

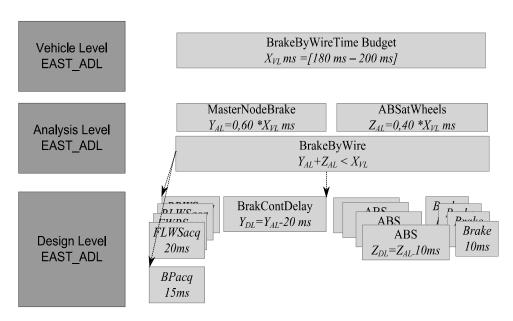

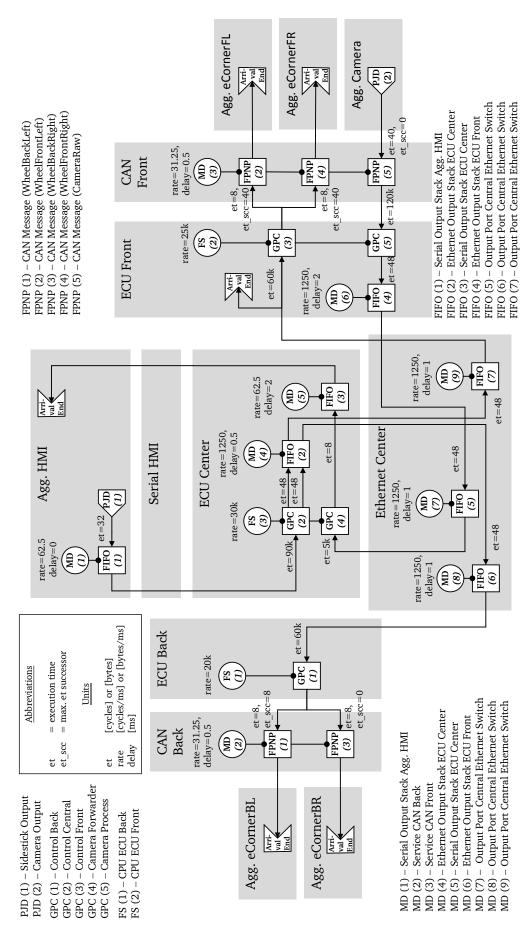

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |