### Lehrstuhl für Entwurfsautomatisierung der Technischen Universität München

## Performance Estimation in HW/SW Co-simulation

#### Kun Lu

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs**

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr.-Ing. Eckehard Steinbach

Prüfer der Dissertation: 1. Univ.-Prof. Dr.-Ing. Ulf Schlichtmann

Univ.-Prof. Dr.-Ing. Oliver Bringmann, Eberhard-Karls-Universität Tübingen

Die Dissertation wurde am 20.01.2015 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 09.11.2015 angenommen.

## Abstract

Facing the high and growing design complexity in nowadays electronic systems, the need of more efficient modeling and simulation techniques arises in the domain of virtual prototypes. In the frame of this work, two major aspects of the non-functional performance estimation in fast hardware and software co-simulation are considered. In simulating the software, a method for annotating the source code with performance modeling codes is proposed. This method features rich control-flow analysis of both the source code and the cross-compiled target binary code. Based on this, it is able to annotate the source code reliably even for an optimized target binary code. Furthermore, by considering the memory allocation principles, memory access addresses in the target binary code are reconstructed in the annotated source code. These two techniques combined lead to appropriated performance estimation in the so-called host-compiled software simulation. The second aspect concerns the simulation of transaction-level models. As a modeling technique, the transfer of a large data block can be modeled by a vary abstract transaction. This work proposes a means to extract timing profiles of the highly abstract transactions so that they can be timed appropriately. Besides that, temporal decoupling can be used for fast simulation of transaction-level models. In order to correctly estimate the durations of the concurrent processes which are simulated in a temporally decoupled way, this work proposes analytical formulas to model the delays due to access conflicts at shared resources. Together with an efficient scheduling algorithm, this analytical method can dynamically predict and adjust the durations of concurrent processes.

| A | bstra | $\mathbf{ct}$ |                                                            | iii |

|---|-------|---------------|------------------------------------------------------------|-----|

| 1 | Intr  | oducti        | ion and Background                                         | 1   |

|   | 1.1   | Motiva        |                                                            | 1   |

|   |       | 1.1.1         | Virtual Prototypes                                         | 2   |

|   |       | 1.1.2         | Benefits of Using HW/SW Co-Simulation                      | 2   |

|   | 1.2   | SW Si         | mulation                                                   | 3   |

|   |       | 1.2.1         | ISS-Based Software Simulation                              | 4   |

|   |       | 1.2.2         | Host-Compiled SW Simulation                                | 5   |

|   |       | 1.2.3         | Annotated Host-Compiled SW Simulation                      | 6   |

|   |       | 1.2.4         | Comparison of the Above Approaches                         | 8   |

|   | 1.3   | HW N          | Indeling and Simulation                                    | 9   |

|   |       | 1.3.1         | SystemC                                                    | 9   |

|   |       | 1.3.2         | Transaction-Level Modeling (TLM)                           | 10  |

|   |       | 1.3.3         | TLM+                                                       | 11  |

|   |       | 1.3.4         | Temporal Decoupling                                        | 12  |

|   |       | 1.3.5         | Transaction Level: Rethink the Nomenclature                | 13  |

|   | 1.4   | Recen         | t Development in HW/SW Co-Simulation                       | 14  |

|   |       | 1.4.1         | Academic Research and Tools                                | 14  |

|   |       | 1.4.2         | Commercial Tools                                           | 16  |

| 2 | Cha   | allenge       | s and Contributions                                        | 19  |

|   | 2.1   | The S         | cope of This Work                                          | 19  |

|   | 2.2   | Challe        | enge in Annotating the Source Code                         | 20  |

|   | 2.3   | Timin         | g Estimation for TLM+ Transactions                         | 23  |

|   | 2.4   |               | g Estimation in Temporally Decoupled TLMs                  |     |

|   | 2.5   | State         | of the Art                                                 | 25  |

|   | 2.6   | Contri        | ibutions                                                   | 32  |

|   |       | 2.6.1         | A Methodology for Annotating the Source Code               | 33  |

|   |       | 2.6.2         | Construct Timing Profiles for TLM+ Transactions            | 33  |

|   |       | 2.6.3         | Analytical Timing Estimation for Temporally Decoupled TLMs | 34  |

|   |       | 2.6.4         | Summary of Contributions                                   | 34  |

|   |       | 2.6.5         | Previous Publications                                      | 34  |

| 3 | Sou   |               | ode Annotation for Host-Compiled SW Simulation             | 37  |

|   | 3.1   |               | ural Control Flow Analysis                                 | 37  |

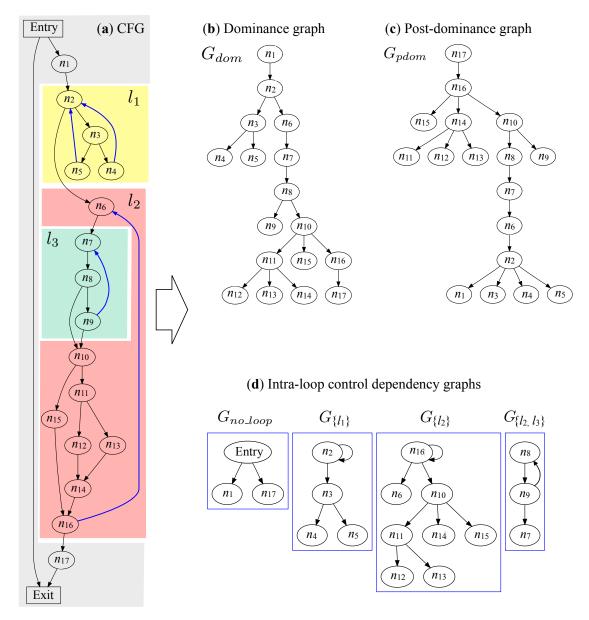

|   |       | 3 1 1         | Dominance Analysis                                         | 38  |

*Contents* vi

|   |     | 3.1.2    | Post-Dominance Analysis                                  |   | 39  |

|---|-----|----------|----------------------------------------------------------|---|-----|

|   |     | 3.1.3    | Loop Analysis                                            |   | 39  |

|   |     | 3.1.4    | Control Dependency Analysis                              |   | 40  |

|   | 3.2 | Struct   | tural Properties                                         |   | 41  |

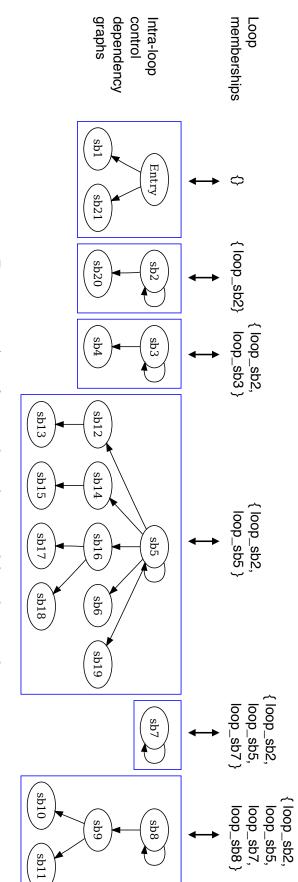

|   |     | 3.2.1    | Loop Membership                                          |   | 41  |

|   |     | 3.2.2    | Intra-Loop Control Dependency                            |   | 42  |

|   |     | 3.2.3    | Immediate Branch Dominator                               |   | 43  |

|   | 3.3 | Basic    | Block Mapping Procedure                                  |   | 44  |

|   |     | 3.3.1    | Line Reference From Debug Information                    |   | 44  |

|   |     | 3.3.2    | Matching Loops                                           |   | 44  |

|   |     | 3.3.3    | Translate the Properties of Binary Basic Blocks          |   | 45  |

|   |     | 3.3.4    | Selection Using Matching Rules                           |   | 45  |

|   |     | 3.3.5    | The Mapping Procedure                                    |   | 46  |

|   |     | 3.3.6    | Comparison with Other Mapping Methods                    |   |     |

|   |     | 3.3.7    | Consider Other Specific Compiler Optimizations           |   | 49  |

|   |     |          | 3.3.7.1 Handle Optimized Loops                           |   | 49  |

|   |     |          | 3.3.7.2 Handle Function Inlining                         |   | 51  |

|   |     |          | 3.3.7.3 Consider Compound Branches                       |   |     |

|   | 3.4 | Recon    | struction of Data Memory Accesses                        |   | 52  |

|   |     | 3.4.1    | Addresses of the Variables in the Stack                  |   |     |

|   |     | 3.4.2    | Addresses of Static and Global Variables                 |   |     |

|   |     | 3.4.3    | Addresses of the Variables in the Heap                   |   |     |

|   |     | 3.4.4    | Handling Pointers                                        |   |     |

|   | 3.5 | _        | imental Results                                          |   |     |

|   |     | 3.5.1    | The Tool Chain and the Generated Files                   |   |     |

|   |     |          | 3.5.1.1 Input Files                                      |   |     |

|   |     |          | 3.5.1.2 Performed Analysis                               |   |     |

|   |     |          | 3.5.1.3 Automatically Generated Reports                  |   |     |

|   |     | 3.5.2    | Benchmark Simulation                                     |   |     |

|   |     |          | 3.5.2.1 Evaluation of the Method for Basic Block Mapping |   |     |

|   |     |          | 3.5.2.2 Reconstructed Memory Accesses                    |   |     |

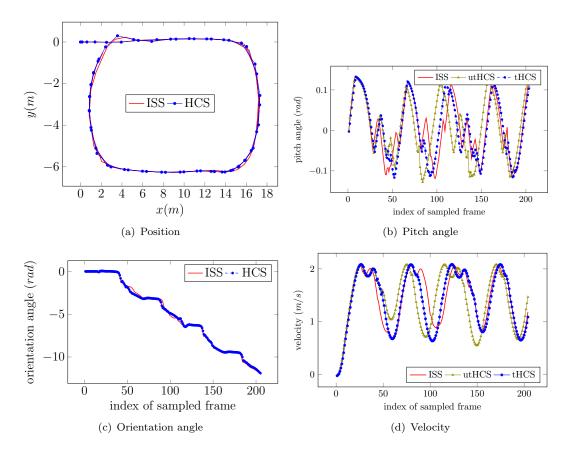

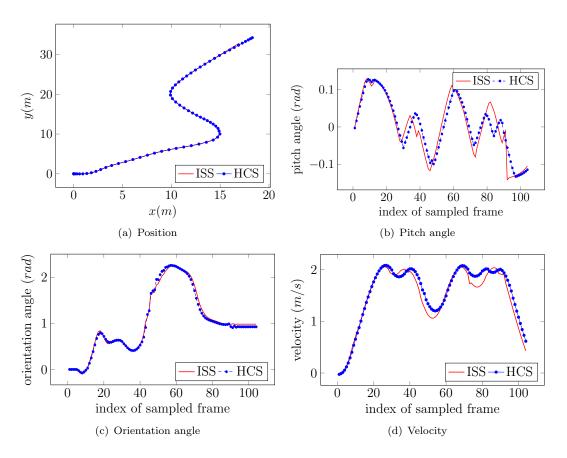

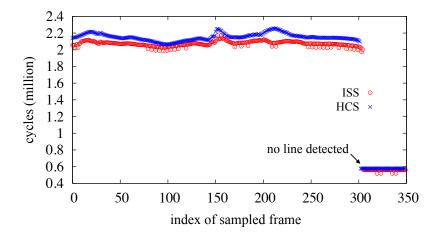

|   |     | 3.5.3    | Case Study: An Autonomous Two-Wheeled Robot              |   |     |

|   |     |          | 3.5.3.1 Simulation Results                               | • | 78  |

| 4 | Ans | alatical | l Timing Estimation for Faster TLMs                      |   | 83  |

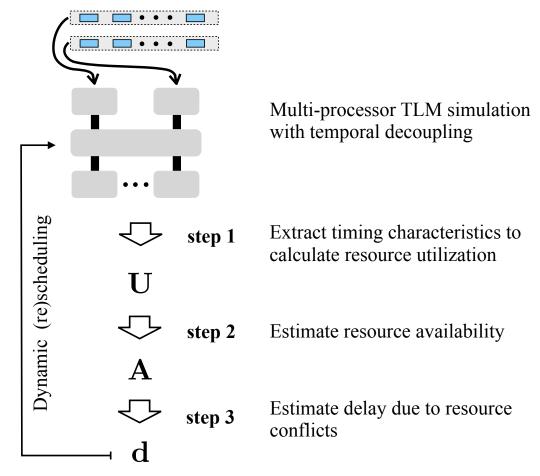

| 4 | 4.1 | •        | ibutions and Advantages                                  |   | 83  |

|   | 4.2 |          | iew of the Timing Estimation Problem                     |   |     |

|   | 1.2 | 4.2.1    | Terms and Symbols                                        |   | 84  |

|   |     | 4.2.2    | Problem Description                                      |   | 86  |

|   | 4.3 |          | lation of Resource Utilization                           |   | 88  |

|   | 1.0 | 4.3.1    | Simulation Using Bus-Word Transactions                   |   | 88  |

|   |     | 4.3.2    | Simulation Using TLM+ Transactions                       |   | 89  |

|   |     | 1.0.4    | 4.3.2.1 Extracting Timing Profiles of TLM+ Transactions  |   | 90  |

|   |     |          | 4.3.2.2 Estimated Duration of TLM+ Transactions          |   | 93  |

|   |     |          | 4.3.2.3 Compute the Resource Utilization                 |   | 93  |

|   |     | 4.3.3    | A Versatile Tracing and Profiling Tool                   |   | 94  |

|   | 4.4 |          | lation of Resource Availability                          |   | 94  |

|   | 1.1 | Carcui   | auton of response fivaliability                          | • | J-I |

Contents vii

|            |              | 4.4.1   | Arbitration Policy with Preemptive Fixed Priorities | 94                 |

|------------|--------------|---------|-----------------------------------------------------|--------------------|

|            |              | 4.4.2   | Arbitration Policy with FIFO Arbitration Scheme     | 95                 |

|            |              | 4.4.3   | Generalization of the Model                         | 95                 |

|            |              |         | 4.4.3.1 Consideration of Register Polling           | 96                 |

|            |              | 4.4.4   | Consideration of Bus Protocols                      | 96                 |

|            | 4.5          | The D   | elay Formula                                        | 97                 |

|            | 4.6          | Incorp  | orate Analytical Timing Estimation in Simulation    | 98                 |

|            |              | 4.6.1   | The Scheduling Algorithm                            | 99                 |

|            |              | 4.6.2   | Modeling Support - Integrating the Resource Model   | 103                |

|            |              | 4.6.3   | Comparison with TLM2.0 Quantum Mechanism:           | 104                |

|            | 4.7          | Exper   | imental Results                                     | 105                |

|            |              | 4.7.1   | RTL Simulation as a Proof of Concept                | 105                |

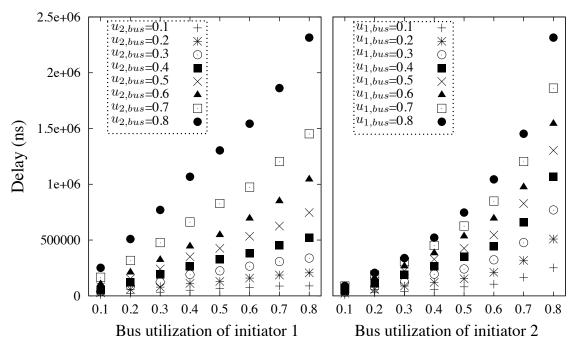

|            |              | 4.7.2   | Hypothetical Scenarios                              | 105                |

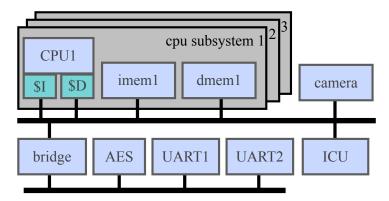

|            |              | 4.7.3   | Applied To HW/SW Co-Simulation                      | 106                |

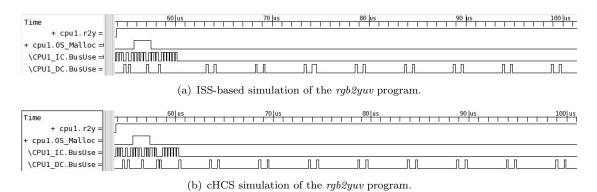

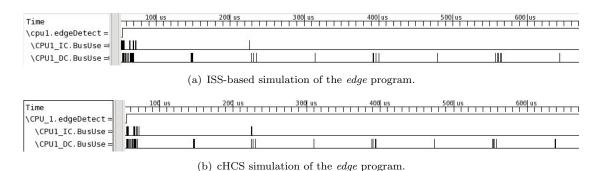

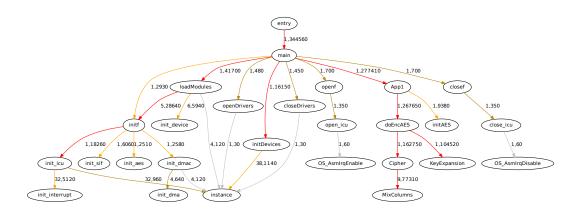

|            |              |         | 4.7.3.1 Description of the SW Simulation            | 106                |

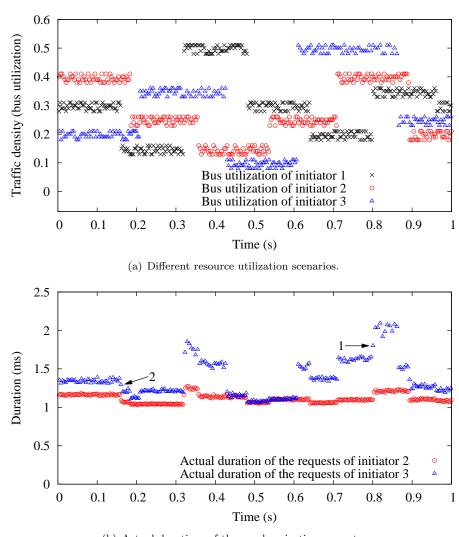

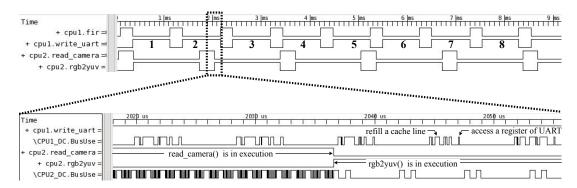

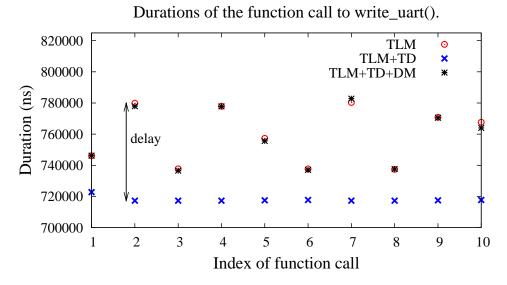

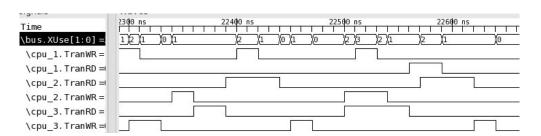

|            |              |         | 4.7.3.2 Simulation of Two Processors                | 108                |

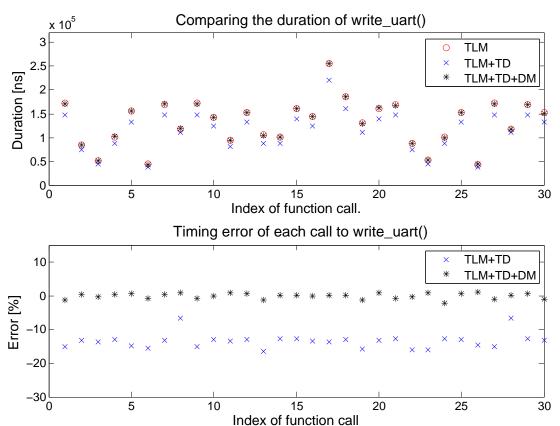

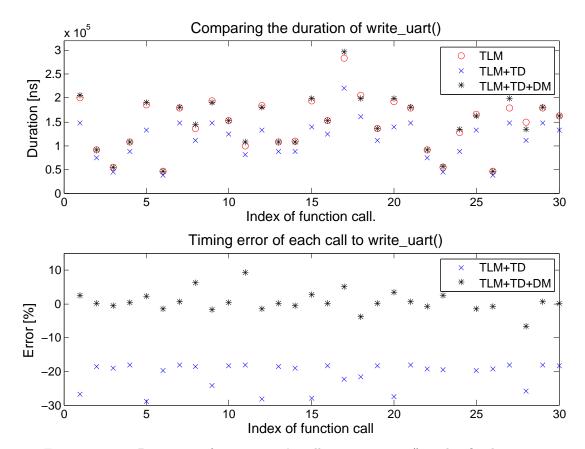

|            |              |         | 4.7.3.3 Simulation with Three Processors            | 110                |

| 5          | Con          | clusio  | 1                                                   | 113                |

| A          | Alg          | orithm  | s in the CFG Analysis                               | 117                |

| В          | Det          | ails of | the Trace and Profile Tool                          | 119                |

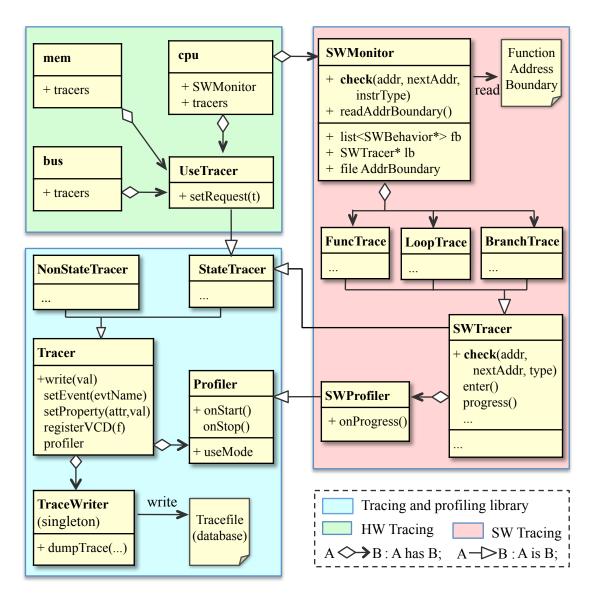

|            | B.1          | The T   | racing Mechanism                                    | 119                |

|            | B.2          | Tracin  | g the SW Execution                                  | 119                |

|            | B.3          | Tracin  | g the HW Activities                                 | 121                |

|            | B.4          | Applie  | eation of the Tracing Tool                          | 122                |

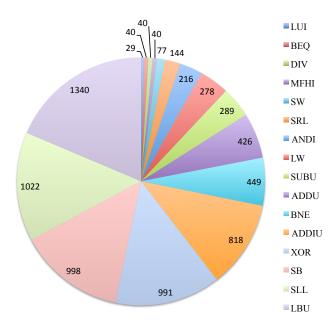

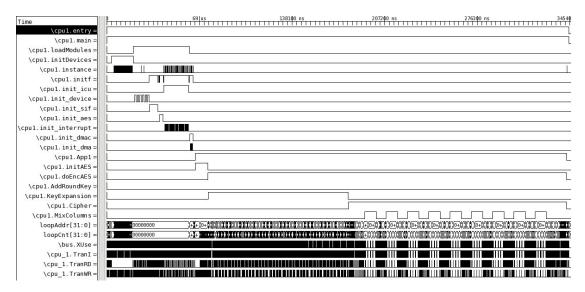

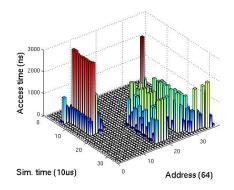

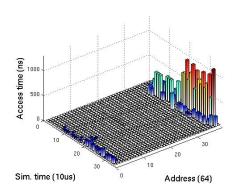

|            |              | B.4.1   | Results of Traced Software Execution                | 122                |

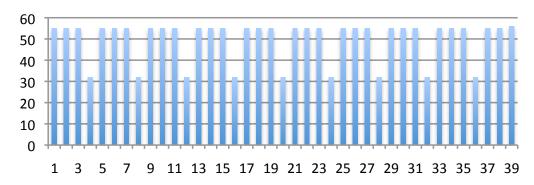

|            |              | B.4.2   | Results of Traced Hardware Accesses                 | 124                |

| <b>.</b> . |              |         |                                                     |                    |

| Li         | st of        | Figure  | es                                                  | $\boldsymbol{124}$ |

| т:         |              |         |                                                     | 124                |

| וע         | st of        | Tables  |                                                     | 128                |

|            | $_{ m ymbo}$ |         |                                                     |                    |

| Sy         |              |         |                                                     | 128                |

Remember the mistakes

## Chapter 1

# Introduction and Background

The design of electronic systems has seen ever increasing complexity for decades. With the advent of multi-processor and heterogeneous architectures, the trajectory of such growing complexity will continue for many more years to come. Traditionally, the software development task is conducted on a hardware prototype, and the techniques such as in-circuit emulation or debugging can be used. However, to handle the growing complexity, a paradigm shift has been considered necessary since the 90's of last century [1–4]. The new paradigm promotes simulation model based development, giving rise to the HW/SW co-simulation.

The following sections in this chapter are organized as follows. Firstly, Section 1.1 introduces the HW/SW co-simulation and its contribution to the design and development of nowadays embedded systems. Secondly, Section 1.2 focuses on the aspects related to SW simulation in a co-simulation environment. It compares popular techniques of simulating the SW and puts forth the challenges considered in this work. Thirdly, Section 2.5.2 focuses on the aspects related to HW modeling, especially the inter-module communication and timing estimation. It discusses the popular hardware description language SystemC and the technique of transaction-level modeling. Finally, the academic and commercial progress in the domain of HW/SW co-simulation is briefly surveyed.

#### 1.1 Motivation

According to [1], hardware and software co-simulation

"refers to verifying that hardware and software function correctly together."

As the authors further put:

"With hardware-software co-design and embedded processors within large single ICs, it is more necessary to verify correct functionality before the hardware is built."

With its popularization, the usage of HW/SW co-simulation is no longer limited to functional verification. As shall be seen, it can bolster a rich set of design tasks, including performance analysis, design-space exploration, etc. In the context of this work,

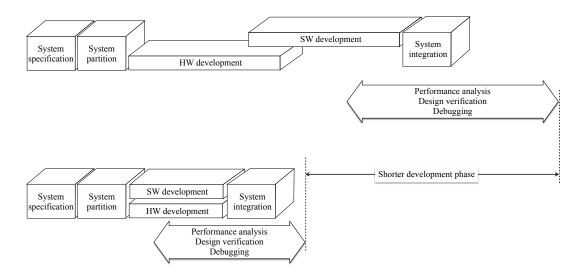

FIGURE 1.1: Co-simulation can shorten the design flow.

HW/SW co-simulation refers to the adoption of simulation platforms in aiding any design tasks of electronic systems. In the following, the benefits of using co-simulation will be discussed. Afterwards, the co-simulation tools and environments from academia and industry will be briefly outlined respectively.

#### 1.1.1 Virtual Prototypes

HW/SW co-simulation often requires the availability of virtual prototypes. A virtual prototype refers to a simulation model that is used as the target system under development. It is different from an emulative model which prototypes the target system on a hardware platform such as an FPGA board. The terminology varies in literature. For example, CoFluent Studio [5] further distinguishes the system modeling by the abstraction level, using terms such as virtual prototypes, virtual platforms or virtual systems. In the context of this work, the term virtual prototype is used in a general sense without such distinction.

#### 1.1.2 Benefits of Using HW/SW Co-Simulation

Compared to emulation, simulation-based approaches are endowed with a variety of advantages to the designers. They offer better flexibility, more cost-efficiency, higher controllability, and better system visibility. Furthermore, they are also easier and faster to develop. The multifaceted benefits of using co-simulation are broadly categorized in the following.

• It shortens the development phase:

Firstly, the hardware and software development can be carried out on a simulation platform which is available in the early development phase. Many tasks therefore

can be started earlier, such as architecture exploration, performance analysis, system validation and HW/SW co-verification. Secondly, using virtual prototypes, the HW and SW design flow can be parallelized, as shown in Figure 1.1. SW designers do not need to wait for a working HW platform to test the SW programs or port them to the HW. Instead, they could conduct a large portion of the development task using virtual prototypes in the simulation platform. As seen in industrial practice, parallelizing the HW and SW design flows indeed shortens the development cycle to a large degree.

#### • It contributes to a high design quality:

A few important reasons are listed here, as to why co-simulation can contribute to a higher design quality.

- 1. Due to increased visibility, debugging the HW and SW becomes easier and can reach a fairly fine-grained level. Mechanisms can be implemented to trace detailed system status such as the register values, events of interests, etc.

- 2. It facilitates the cooperation between the HW and SW development teams. More iterations between the HW and SW design groups can be achieved, since the effort of doing so in a co-simulation environment is much lower than that on a real product or on an emulative prototype. It also makes the full system integration easier to the HW and SW design groups. Besides, the virtual prototype can help the SW designers to better understand the HW system and develop the HW/SW interface. This eventually may reduce the design defects within a constrained development phase.

- 3. Exploration of a larger design space is made feasible, which contributes to a potentially more optimal design. This is because modeling and simulating a new system candidate can be fast. For example, to evaluate a new HW/SW partition, the designers may be able to re-run the simulation by only modifying a configuration file.

#### • It reduces the overall development cost:

Using simulation, the cost of modeling is very low. There is no need to manufacture the system. Modeling new HW and SW components may be cheap by re-using legacy codes. Verification and performance analysis can also be carried out. Therefore evaluating different design options is cheap. The cost of trial-and-error can also be greatly reduced. Further, another feature of simulation is its high flexibility. For example, it is easy to switch to new IP components, e.g. by simulating and verifying certain interface functions. This makes it easier to use new IPs and technologies which are changing fast.

#### 1.2 SW Simulation

In this work, two main variants of software simulation that can be used in a co-simulation environment are considered. The first one is the instruction set simulation (ISS) based software simulation. The second is host-compiled software simulation. If the software is annotated with performance information, the latter is then called annotated host-compiled software simulation. This section introduces the basic principles of these software simulation approaches.

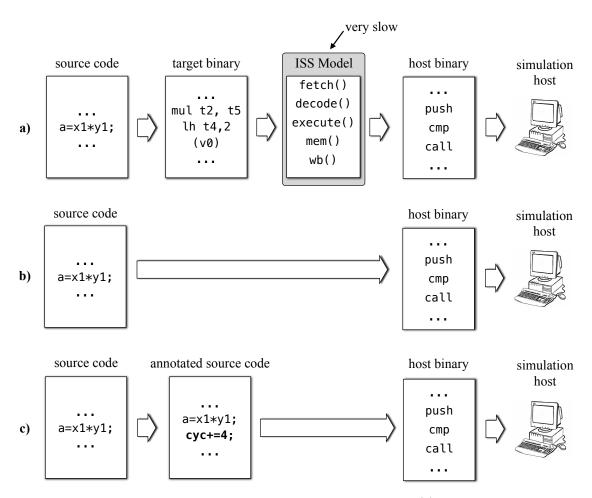

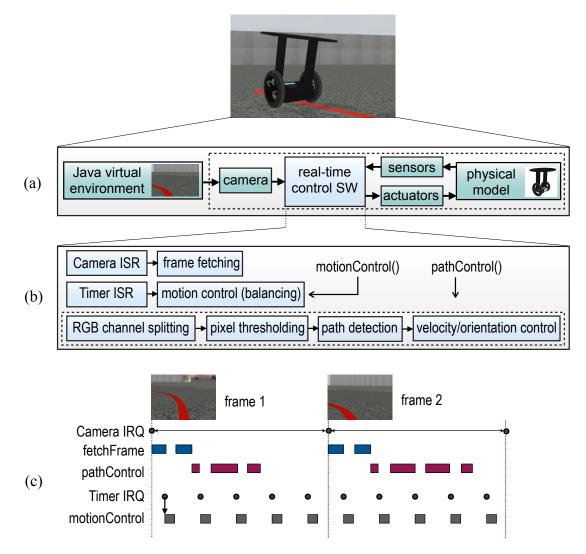

FIGURE 1.2: Basic steps in different SW simulation approaches. (a) ISS-based SW simulation; (b) Host-compiled SW simulation; (c) Host-compiled SW simulation procedure with annotated source code.

#### 1.2.1 ISS-Based Software Simulation

An instruction set simulator (ISS) is a simulation model of the target processor. It models the internal processing steps of a processor in interpreting and executing one instruction, as can be seen in Figure 1.2(a). Therefore, an ISS interprets the target binary code as the target processor would do. Being a detailed model, cycle-accurate timing can be provided by an ISS. Before the actual hardware is available, ISS-based software simulation can be used to provide relatively accurate performance estimation. Even after the target hardware platform is ready, it can still be used as an alternative, e.g. for debugging or exploring different configurations.

Several basic terms are defined in the following before a more detailed description.

The **target processor** is the processor that will be used in the HW system of the final product. Common examples of a target processor include the MIPS processor [6], the ARM processor [7], the OpenRISC processor [8], etc.

The **simulation host** or **host machine** is the machine on which the simulation is carried out. It may use a different processor and hence the instruction set architecture from the target processor. For example, the simulation host can be an Intel machine with an  $x86_-64$  processor.

**Target binary** or target binary code refers to the binary code that can be executed by the target processor.

**Cross-compilation** is the generation of the target binary using a cross-compiler installed on a simulation host. This compiler usually is different from the compiler used by the simulation host.

As is depicted in Figure 1.2(a), the following steps are performed in ISS-based SW simulation.

- **Step 1:** The source code firstly needs to be cross-compiled into the target binary. This step therefore requires the availability of the cross-compiler.

- Step 2: The ISS is provided with the target binary image.

- Step 3: The whole system model consisting of the ISS and other HW modules is compiled into a host executable.

- Step 4: Finally the simulation is performed by running the host executable. In the simulation, the ISS interprets each binary instruction of the target binary. It can model both the pipeline stages and corresponding memory accesses as would be performed by the target processor.

#### 1.2.1.1 Disadvantages of ISS-Based SW Simulation

Besides the high modeling effort, the major disadvantage of traditional ISS-based SW simulation is that the simulation speed is relatively slow, which can make it very expensive to use in some cases such as the simulation of long software scenarios. This problem also limits the application of ISS-based SW simulation in design tasks such as design space exploration or real-time simulation, where high simulation speed is required.

The simulation cost of ISS-based simulation can be roughly assessed by considering the required host machine instructions to simulate one line of the source code. Several target binary instructions can be generated from cross-compiling one source code line. Simulating each of these instruction requires the ISS model to perform a chain of tasks corresponding to the pipeline stages of the target processor. This translates to up to several thousands of host machine instructions in simulating one source code line. As a result of this high cost, usual ISS models can simulate a few millions of target instructions on a host machine with a CPU clocked at GHz. Although there exist approaches toward faster ISS models [9–12], another line of research based on host compilation has received increasing popularity.

#### 1.2.2 Host-Compiled SW Simulation

The basic steps in host-compiled SW simulation are shown in Figure 1.2(b). The source code is directly compiled to a host executable for the simulation host. A model of the target processor such as an ISS is completely by-passed. Such host-compiled simulation is very fast and yet able to verify the functional correctness of the simulated software. However, it can not provide non-functional performance estimation such as the timing information of the software. Specifically, the missing information includes the following:

• For the computation aspect of the software, the timing related to the execution time of the simulated SW becomes unknown.

• For the communication aspect of the software, the memory accesses caused by the store and load instructions become invisible, because the accessed addresses can not be statically obtained from the target binary code.

In the very early design phase, host-compiled simulation without performance estimation could be used for fast functional verification. As the design proceeds, performance estimation may become mandatory for many design tasks, including the design space exploration, timing verification, etc. To cover these design tasks, an improved version of host-compiled simulation has been proposed, which annotates performance modeling codes in the original software program. This new approach is discussed in the next section.

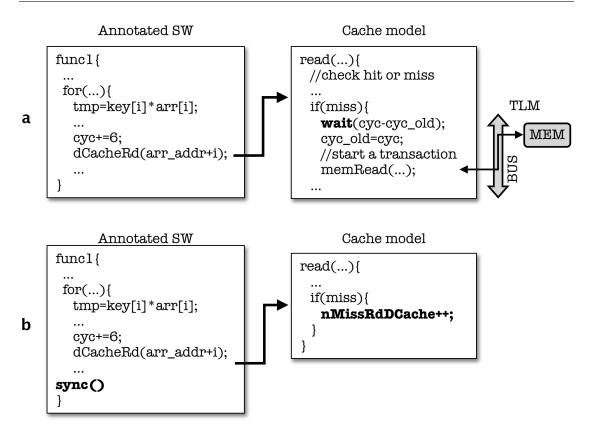

#### 1.2.3 Annotated Host-Compiled SW Simulation

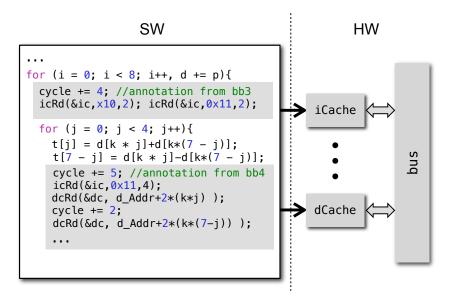

The basic principle of annotating the source code for host-compiled SW simulation is to augment the source code with performance modeling codes. It aims at providing performance analysis with sufficient accuracy while keeping high simulation speed. The annotated codes usually include execution cycles and memory accesses, corresponding to the computation and communication aspects of the target binary code, respectively. After annotation, the source code can be used as a *performance model* of the target binary. Therefore, through executing the annotated source code, performance estimation and analysis can be provided in host-compiled simulation as well.

#### 1.2.3.1 Basic Block

A basic block is the largest piece of code that has a single entry and a single exit point, between which there exits neither a branch nor a target of a branch. Once a basic block is entered, the contained code will definitely be executed until its exit point. For annotated host-compiled simulation, most existing approaches perform the annotation at the granularity of the basic blocks.

#### 1.2.3.2 Line Reference

Using the utility from the cross-compiler tool chain, debugging information such as the line reference can be obtained. The *line reference file* lists the reference line of the source code from which an instruction in the target binary is compiled. An excerpt of a sample line reference file is shown in the following:

| CU: App.c: |             |                  |

|------------|-------------|------------------|

| File name  | Line number | Starting address |

| App.c      | 125         | 0x104            |

| App.c      | 124         | 0x108            |

| App.c      | 125         | 0x118            |

| App.c      | 119         | 0x12c            |

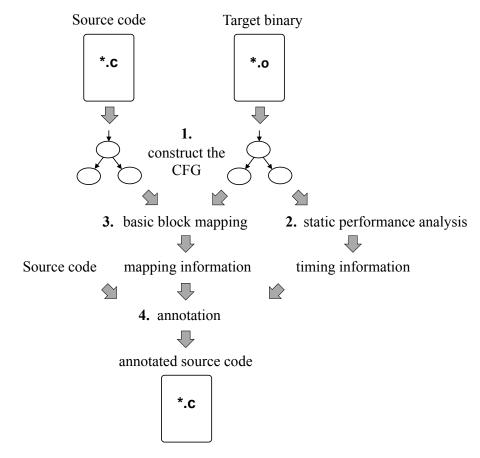

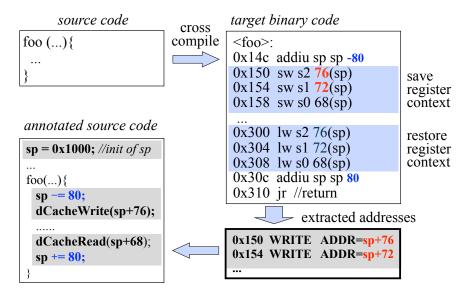

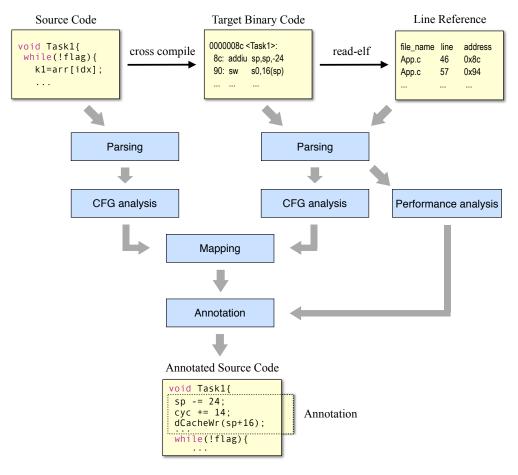

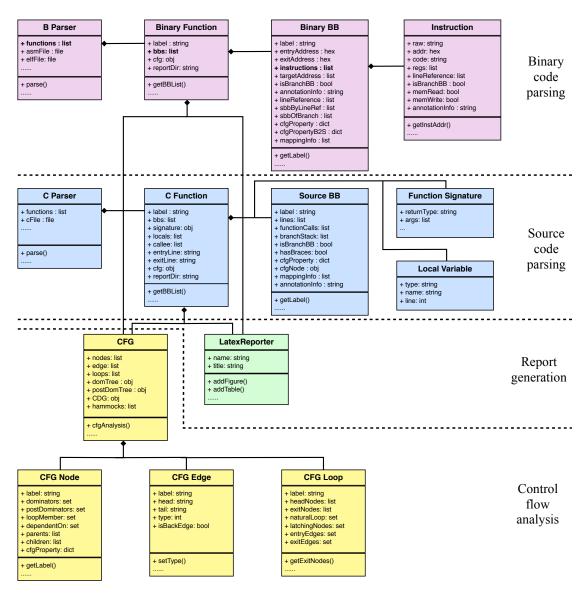

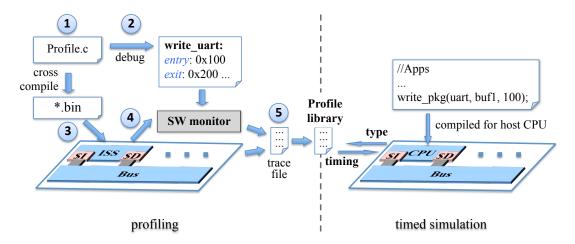

FIGURE 1.3: Basic steps in annotating the source code.

| App.c | 116 | 0x138 |  |

|-------|-----|-------|--|

|       |     |       |  |

For example, from this line reference file, it can be known that the instructions within [0x108, 0x118), i.e. 0x108, 0x10c, 0x110 and 0x114, are compiled from line 124 in the source code.

#### 1.2.3.3 The Annotation Procedure

The basic steps in annotating the source code are shown in Figure 1.3. These steps are described in the following.

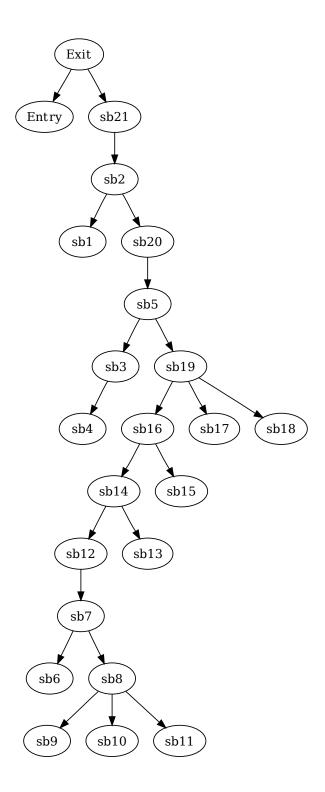

- 1. The control-flow graphs are constructed for the source code and the target binary.

- 2. For each basic block in the target binary, performance information such as the execution cycles can be extracted through static analysis.

- 3. With the line reference, the annotation process can reason about the mapping from the basic blocks in the target binary to those in the source code.

- 4. After the mapping is constructed, the statically estimated performance modeling code of a target binary basic block is annotated into its counterpart basic block in the source code.

Afterwards, the annotated source code can be directly compiled and executed on the simulation host. In the simulation, performance estimation is achieved by executing the annotated codes for performance modeling.

#### 1.2.3.4 Annotated Codes for Performance Modeling

The statically extracted codes for performance modeling cover two main aspects regarding the execution of a software. One is the computation aspect and the other is the communication aspect.

1. The computation aspect is represented by the estimated execution time or cycles of a piece of software code. For example, if the execution of a basic block is estimated to take be 8 cycles, then

can be annotated in the counterpart basic block in the source code. The variable cyc is initialized to zero.

2. The communication aspect is represented by the annotated memory accesses. For example, assume the address of the accessed instruction in a target binary basic block is 0x2100, then

#### iCacheRead(0x2100)

can be annotated in the counterpart basic block in the source code<sup>1</sup>.

Here, special attention needs to be given to the fact that the cache simulation is **non-functional**. This means that, for a given address, the cache model only checks whether the access causes a cache hit or miss, but does not cache any functional data. Upon a cache miss, a transaction can be initiated to access the memory over bus. This transaction is used to simulate the on-chip communication related to memory accesses, thus modeling the communication aspect of the target binary code. But, no functional data are actually transferred by this transaction.

Similar annotation holds for simulating data cache. However, the addresses of the data memory accesses can not be statically extracted. This problem will be detailed in Section 2.2.

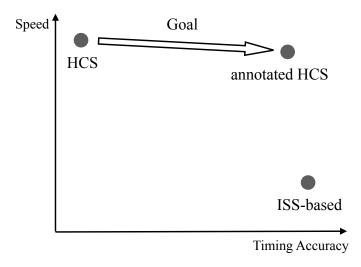

#### 1.2.4 Comparison of the Above Approaches

The main pros and cons of the previously discussed software simulation approaches can be briefly summarized in Figure 1.4. As is shown, ISS-based SW simulation offers

$<sup>^1</sup>$  If the size of a cache-line is fixed, then the sequentially executed instructions that fit in the same cache-line require the instruction cache simulation for only once. For example, assume the cache-line size is 16bytes, then for a target binary basic block with 6 instructions starting from the instruction address 0x2100, the annotation iCacheRead(0x2100, 6) suffices to simulate the instruction cache behaviour since the instructions fit in the same cache-line corresponding to the address 0x2100. This reduces the overhead of instruction cache simulation.

FIGURE 1.4: Compare different methods of SW simulation

the highest timing accuracy but relatively low simulation speed. Host-compiled SW simulation (HCS) is very fast but can not provide performance analysis. Therefore, the goal is to obtain an annotated source code that can be used as an accurate performance model of the target binary. A good annotation should preserve the correct execution order of the annotated performance modeling codes. This is hard to achieve due to compiler optimization. For optimized target binary, the line references become neither sufficient nor reliable. The concrete challenges are detailed in Section 2.2.

## 1.3 HW Modeling and Simulation

Recent hardware system modeling has witnessed the trend of moving to electronic system level (ESL), in the need of better handling the growing design complexity. Joint force from industry and academia has promoted the design shift to ESL. As a result of this effort, SystemC and transaction level modeling (TLM) have been developed and standardized. Both of them are now widely accepted. In the following, the principles of SystemC and TLM are briefly introduced. Afterwards, the often mentioned term abstraction level is discussed to clarify conceptual ambiguity.

#### 1.3.1 SystemC

SystemC was defined by the Open SystemC Initiative (OSCI) and standardized by IEEE in 2005 [13]. It is a HW description language that is developed upon C++. Specifically, as its name suggests, SystemC is suitable in design tasks such as system-level modeling, system-wide analysis, component-based modeling, etc. The core ingredients and features of SystemC are summarized in the following.

• Modular design: With a few macros, it is very easy to describe and instantiate HW modules in SystemC. The granularity of a module can vary, e.g. ranging from an adder to a processor. A module encapsulates its internal computation and reduces the complexity of modeling a whole system to modeling its components.

• Inter-module communication: In its early version, the inter-module connection is modeled by *ports*, *interfaces* and *signals*. Now, with TLM 2.0, the connection is often modeled by *sockets*. By connecting the modules in a top-down manner, it is easy to model the system in a hierarchical manner.

- Modeling of computation: SystemC abstracts the modeling of the computation in the HW modules into threads and methods. They are referred to as processes in general unless distinction is necessary. This simplifies the system modeling task when lower level details are not relevant. For example, the computation in an encryption module can be modeled by a process containing the encryption algorithm written in C++, without modeling the underlying adders and multipliers.

- **Notion of time:** Modeling of time in SystemC is straight-forward. There are two main types of *wait* statements for this purpose.

- 1. Wait on a time variable t, such as in wait(t). Supported time units include  $SC\_FS$ ,  $SC\_PS$ ,  $SC\_NS$ ,  $SC\_MS$ , and  $SC\_SEC$ .

- 2. Wait on an event e, such as in wait(e). The execution of the process that calls this wait statement will resume when the event occurs. This time can be set by notifying the event as in e.notify(t), e.g. by some other process. It is worthy of pointing out that it is possible to cancel the notified time of an event and re-notify it to a new time.

A process calling wait() without argument will stall forever and will resume only when a default event occurs that this process is sensitive to.

- **Process scheduling:** SystemC uses a central scheduler to schedule concurrent processes. Each time a *wait* statement is called, the scheduling algorithm will be performed. This scheduler inspects the queues of stalled processes and selects the next process that is ready to run.

- Timing synchronization cost: After a wait statement is issued, a context switch will be performed between the current process and the SystemC scheduler. After checking the process queues and selecting the next runnable process, another context switch will be performed from the scheduler to the next process to resume. Such context switches are computationally very expensive, therefore frequent timing synchronization can slow down the simulation to a great degree.

#### 1.3.2 Transaction-Level Modeling (TLM)

Transaction-level modeling (TLM) has been introduced to simplify the modeling of intermodule communication. To support models written in SystemC, TLM 1.0 and TLM 2.0 have been published in 2001 and 2009 respectively. The hardware virtual prototypes modeled with the TLM technique are referred to as transaction level models (TL models), or TLMs for short. This abbreviation is also often used in literature, but it ought not to be confused with the term TLM.

In TLMs, transactions are used to model the data transfer between HW modules, while the underlying complex signal protocols are abstracted away. One module can be completely agnostic to the signal interface of another module that it connects to. This not

only simplifies the modeling effort but also greatly improves the simulation speed as compared to RTL models. Therefore TLMs are suitable for fast and early SW development, system verification and design space exploration.

In essence, TLM is data-flow oriented modeling. Although the granularity of the dataflow being modeled can be arbitrary, two main categories of transactions have been used in the literature corresponding to two different abstraction levels.

- 1. Bus-word transactions: The data transferred by one transaction is a unit of datum supported by the bus protocol. For example, a bus-word transaction can transfer a byte, a word, or a burst of words. It can be regarded as a primitive transaction that transfers a basic data unit. Handshaking signal protocols, that are respected by the modules in the hardware implementation, are abstracted away.

- 2. Block transactions: The data transferred by one transaction can be increased in size. For example, a whole data block or packet can be transferred. According to the TLM 2.0 standard, a generic payload is used in implementing a transaction. Within this generic payload, a pointer is passed around that points to a data block, together with the size of the data to be transferred. One block transaction abstracts away the software protocols of the corresponding driver functions that implements the data transfer. Further details regarding such transactions are explained in the next section.

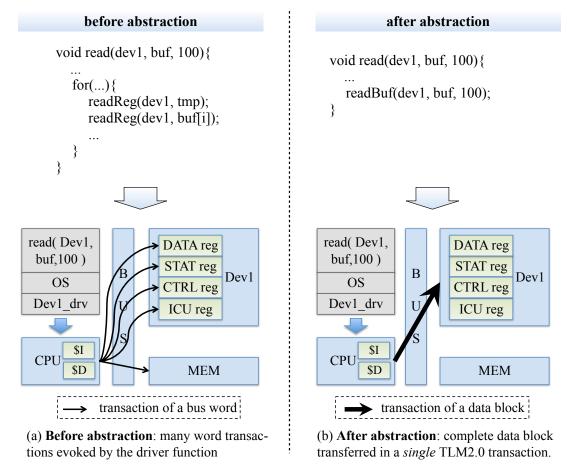

#### 1.3.3 TLM+

Initially, TLM+ [14] is proposed as a further abstraction from TLM. It regards the intermodule communication as data-flows and provides support to bypass the underlying software protocols. In terms of modeling, it introduces the following changes:

- 1. A transaction can transfer not only a bus-word, but also a large data block. This data block can have arbitrary data type and size.

- 2. The corresponding driver function in the SW is simplified in a way that it calls a single transaction to transfer a large data block. This transaction replaces a long sequence of bus-word transactions that are invoked in the original driver function for transferring the data block.

From now on, the term TLM+ transaction [14] is used when referring to a transaction that transfers a large data block. TLM+ is in fact compatible to the later TLM 2.0 standard, which implements a TLM+ transaction by passing a pointer and the data size.

In the standard TLM simulation, the transfer of a data block such as a buffer initiates a long sequence of bus-word transactions. Expensive timing synchronization needs to be performed before and during each bus-word transaction. Such effort is greatly reduced in TLM+. One TLM+ transaction abstracts the sequence of bus-word transactions into one single transaction. The changes in the driver function are exemplified using <code>write\_uart()</code> which writes a buffer to the UART module. The snippet in List 1.1 shows that, for each data word in the buffer, there is one iteration of handshaking protocol involved in the standard TLM simulation. Executing this driver function will evoke a long sequence of bus-word transactions to complete the data transfer.

```

int write_uart(buffer, size) {

1

2

3

while (i < size) {

4

get_uart_status_reg();

5

6

set_uart_txd_reg(buffer[i]);

7

8

wait_irq(...);

9

set_uart_irq_reg(0);

10

}

}

11

12

```

LISTING 1.1: Example of a driver function in standard TLM simulation

For comparison, List 1.2 shows the driver function for TLM+ simulation. The complete while loop in List 1.1 is replaced by a single transaction as shown in line 4.

```

int write_uart(buffer, size) {

get_uart_status_reg();

...

set_uart_txd_reg(buffer, size);

...

wait_irq(...);

set_uart_irq_reg(0);

}

```

LISTING 1.2: Example of a driver function in TLM+ simulation

#### 1.3.4 Temporal Decoupling

#### 1.3.4.1 Timing Simulation in Standard TLMs

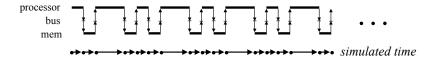

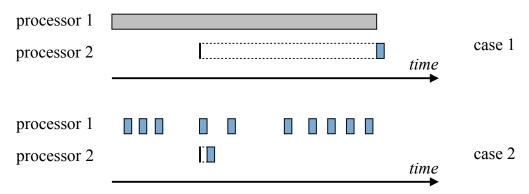

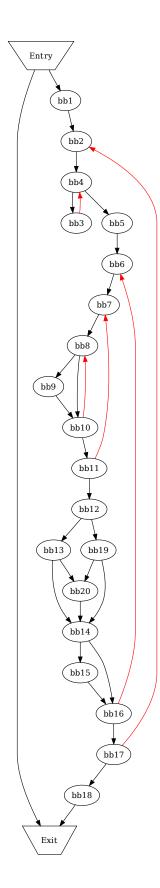

Before the introduction of TLM 2.0, functional simulation and timing simulation are intermingled with fine granularity. A process calls the *wait* statements before initiating a bus-word transaction, so that the inter-module communication is correctly synchronized. A depiction of such synchronization can be seen in Figure 1.5(a). With such fine-grained timing synchronization, all bus-word transactions are performed at the correct global time, therefore the simulation can capture access conflicts at shared HW modules in a multiprocessor simulation. During a bus-word transaction, more *wait* statements can be called when needed. For example, a bus can be cycle-accurate and contain a process that synchronizes at each clock cycle. This process can arbitrate the on-going transactions according to the bus protocols. A bus can also be un-clocked, i.e. it does not need to wait for each clock cycle. The transactions are arbitrated with estimated durations. This leads to a faster simulation than the cycle-accurate bus model, and timing can still be sufficiently accurate.

a. Standard SystemC simulation with lock-step timing synchronization

- b. Temporal decoupling: timing is synchronized at the granularity of a large quantum

- → advance of the simulated time through context switches

- advance of the local time through variable addition

FIGURE 1.5: Timing synchronization before and after using temporal decoupling.

#### 1.3.4.2 Temporal Decoupling in TLMs

Fine-grained synchronization as in Figure 1.5(a) is computationally expensive due to the incurred context switches. If the bus-word transactions need to be evoked very frequently, then the simulation is heavily slowed down due to the timing synchronization overhead. This can be the case if the simulated software requires frequent I/O communication or the cache miss rate is high.

To reduce the simulation overhead, temporal decoupling (TD) is introduced in the TLM 2.0 standard [15]. In fact, this concept has already been explored in earlier works [16, 17]. With this concept, TLM 2.0 proposes the notion of local time and global time. With temporal decoupling, the local time of a process can be larger than the global time. A process can be simulated ahead without the need to synchronize, even before it issues a transaction. In other words, timing synchronization is performed with a much coarser granularity, e.g. after the functional simulation of a large piece of code or a large quantum is reached. The basic principle of temporal decoupling is illustrated in 1.5(b). As can be seen, a local time variable is used to register the local time. If it does not exceed a pre-defined value of the global quantum, then no call to the wait statement is issued. In this way, the functional simulation is decoupled with the timing simulation. Using temporal decoupling, the number of synchronizations per thread is reduced to one within each global quantum. Setting a larger global quantum may therefore lead to more speed-up.

#### 1.3.5 Transaction Level: Rethink the Nomenclature

A transaction per se may correspond to different levels of abstraction. Therefore, the term transaction-level can cause ambiguity when describing models at different abstraction levels. In fact, since its advent, there have been opposing opinions on the appropriateness of its terminology. Some [18] hold that "TLM does not denote a single level of abstraction but rather a modeling technique", therefore it is more appropriate to name

is as transaction-based modeling. Authors in [19] suggest that transactions in essence are data-flows. They consider their modeling methodology to be data-flow abstracted or oriented virtual prototyping. Another thought provoking work [20] even challenges whether TLM is a buzz-word and whether it is useful enough in handling nowadays design task.

From the perspective of inter-module communication, an abstraction level can correspond to the granularity of data transfer being modeled. If the transferred data correspond to the values of signals, then this abstraction is at the pin level. If the transferred data correspond to a byte or word that fit the bus protocols, then this abstraction level can be said to be at the bus-word level. If the transferred data correspond to a large data block or packet, then the abstraction is at the data block or packet level. In this work, the term transaction-level modeling is still used, despite its ambiguity. But to distinguish the different abstraction levels, the data granularity is explicitly mentioned together with the transaction, such as a bus-word transaction or a block transaction.

## 1.4 Recent Development in HW/SW Co-Simulation

The last two decades have seen prevalent development and application of the co-simulation environments, both in academia and in industry. Being an important part in the design task, a good co-simulation environment should meet certain requirements to effectively aid the design process. It should cover a wide range of system configurations, in order to support various processor types and system architectures which may be required by the emerging heterogeneous systems. It should be able to simulate different applications. It should also adapt to the demands of the system designers, e.g. switching among different abstraction level. It is challenging to develop a general co-simulation environment that meets all the requirements. This section broadly surveys both the academic and industrial progress in bringing out new co-simulation environments.

#### 1.4.1 Academic Research and Tools

An early work (*Becker*, 92 [2]) proposes a co-simulation environment to enable concurrent development of software and hardware which are written in C++ and Verilog respectively. It uses Unix interprocess communication to interact software simulation with hardware simulation.

Poseidon [3] can synthesize the hardware and software components from a predefined system description. For timing simulation, clock cycles for the functional models need to be provided as input to the tool.

Ptolemy [4] is a tool that precedes and shares many similarities with SystemC. It targets the platform modeling for heterogeneous components, where the concept of modular component based modeling is raised. Computation in the modules is modeled by finite state machines. Inter-module communication is modeled by wires and ports as in SystemC.

Pia [16], developed upon Ptolemy, has several features. Firstly, it provides multiple communication models. Secondly, it proposes an advanced scheduling mechanism. Its scheduler supports the use of *global time* and *local time*. Therefore it is among the

first to propose the concept of temporal decoupling. Besides, it offers conservative and optimistic scheduling, corresponding to two modes of timing simulation. Thirdly, it enables the option of modeling the processor at different level of abstraction. This also includes host compiled simulation, in which the source code is compiled directly for the host.

The approach in [21] co-simulates HW components in VHDL and SW components in C. It adopts a so-called *multi-view* library concept to encapsulate various HW/SW implementations. This is conceptually similar to raising the abstraction level.

Miami [22] is another co-simulation environment which integrates an event driven hardware simulator with an instruction set simulator.

COSMOS [23, 24] is a co-simulation tool that features hardware and software interface generation. It supports software programs written in C and hardware models written in VHDL. Different levels of abstraction can be simulated as well. It also provides modeling and simulation support for heterogeneous multiprocessor systems.

The approach in [25] combines an instruction set simulator (ISS) with an event-based system simulator, so that the timing can be measured online instead of estimated off-line. In addition, it uses the so-called cached timing to improve the simulation speed of the ISS. This is in effect equivalent to temporally decoupling the simulation of one system component.

The approach in [26] aims to integrate different IP models using a common high level communication semantic. It can be used in a platform of a heterogeneous system, where different IP models may be configured and simulated at different abstraction levels.

Giano [27] is another HW/SW co-simulation framework. It supports the SW execution in two modes: (1) executing the target binary code using a simulated microprocessor; and (2) executing VHDL code using a simulated FPGA. The simulated target system can interact with the external environment in real time. By attaching a HW simulator, it can simulate a HW system written in Verilog, VHDL, SystemC, and C.

Authors in [28] aim to reduce the communication overhead between simulator and emulators, by avoiding communication in a period if no transactions occur in it. This period is predicted by inspecting the software and hardware modules. The problem targeted by this approach is automatically attenuated in system simulation, because the overhead is only induced when transactions take place. Therefore the prediction is not necessary any more.

A component-based simulation platform is adopted in [29]. Both the HW and the SW are abstracted as components. Bridge components are used to ease the interface the HW/SW components. The co-simulator can be configured by the specifications of the components.

The simulation in [30] can be configured to provide multi-accuracy power and performance modeling. Transaction-level modeling is used for the hardware models. The authors modify the SystemC kernel and TLM library to enable the switching among different trade-offs between simulation accuracy and speed.

The approach in [31] annotates the software program with performance modeling codes before simulating it on the hardware modeled at transaction level. It predicts the synchronization point during the simulation and uses this prediction to reduce the synchronization overhead. This technique is a common practice in host-compiled software simulation with annotated performance.

The co-simulation framework in [32] is written in SystemC. It supports the integration of a many-core architecture, with each core modeled by an instruction set simulator.

The approach in [33] also targets many-core simulation up to the scale of a thousand cores. For such computation-intense simulation, techniques are required to boost the simulation speed. Adopted techniques by the authors include host-compiled execution, distributed simulation and course-grained synchronization.

#### 1.4.2 Commercial Tools

Seamless [34] from Mentor Graphics is an early commercial co-simulation tool. It provides the possibility to switch between ISS simulation and host-compiled simulation. The HW system can be described at register-transfer level or at transaction level, depending on the design stage. In Seamless, HW/SW communication is mediated by a bus interface model, which handles the data transfer between the processor and memory or I/O ports. Timing, in terms of bus cycles, can be modeled by the bus interface model.

ModelSim [35] supports hardware design languages such as Verilog, VHDL, and SystemC. Basic debugging utilities such as signal-level tracing and code coverage measurement are provided. Another integrated feature in ModelSim is the assertion-based verification, using the IEEE Property Specification Language (PSL) [36].

Carbon [37] allows the plug-in of an accurate CPU model in an RTL environment. It emphasizes on its software debugging feature that enables the designer to interactively debug both the software and the hardware such as the processor registers.

**Gezel** [38–40] provides a co-simulation engine that supports a variety of processors, including ARM cores, 8051 micro-controllers and picoblaze micro-controllers. Users can configure multiple cores in the simulation and evaluate the design trade-offs by using coprocessors.

VMLab [41] is a co-simulation engine mainly for virtual prototyping and simulating the AVR models. It integrates the simulation of analog signals and provides SPICE-like hardware description language.

CoCentric System Studio [42] from Synopsys is a development suite for system-level design. It promotes the use of data-flow models in system modeling. The design focus of CoCentric is on two aspects. One is to produce algorithmic models that aim to verify the functional correctness in a very fast way. The other is the architecture modeling at multiple abstraction levels, from system level down to pin-accurate level.

CoFluent Studio [43] from Intel specializes itself in the very early phase of the design flow. At such an early phase, system modeling at a very abstract level can be used. For example, it uses message-level data transfer for communication modeling and ISS-free SW simulation for computation modeling. A typical application scenario with CoFluent is the modeling and simulation of use-cases, from which preliminary performance

prediction and design-space exploration could be performed. The performance metrics that can be simulated by CoFluent include timing, power, system loads, etc. An essential value proposition of CoFluent is that, through executable specifications and highly abstract modeling, design decisions can be made in the initial design phase before any HW and SW development take place, thereby shortening the overall design phase.

Platform Architect [43], previously Coware now Synopsys, features system level modeling and performance analysis. The inter-module communication is implemented using transaction-level modeling techniques. The simulation is claimed to be cycle-accurate. Adaptors are provided to interface transaction-level modules and RTL modules. It is applied in the early architectural optimization of a multi-core system, by using task-level or trace-driven simulation.

## Chapter 2

# Challenges and Contributions

In the beginning, this chapter gives an overview of the targeted challenges to tackle in the domain of co-simulation. This overview can be regarded as the scope of this work within which the proposed approaches can be applied. Details of each challenge will be described. Afterwards, related approaches are discussed. Following that, proposed solutions are summarized as the contributions of this work.

## 2.1 The Scope of This Work

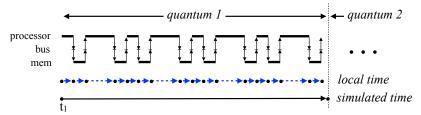

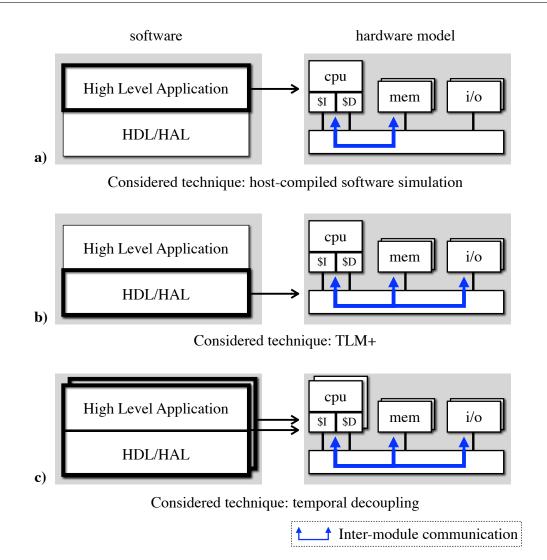

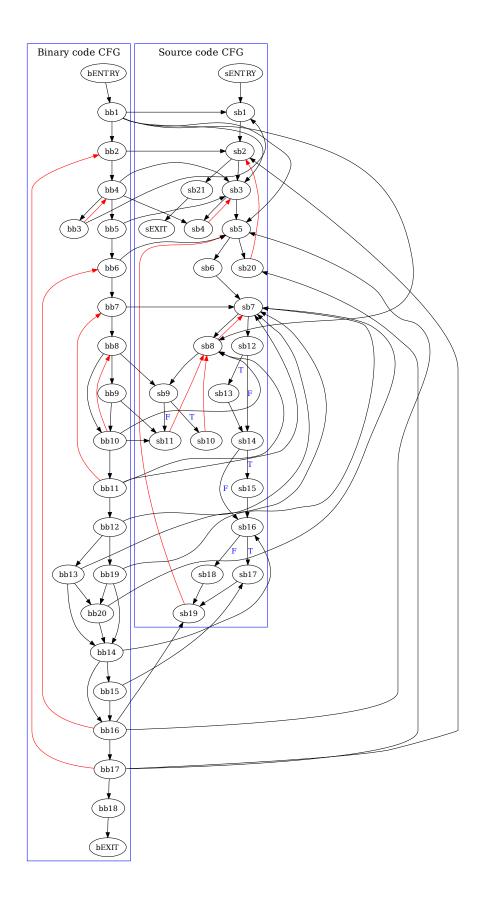

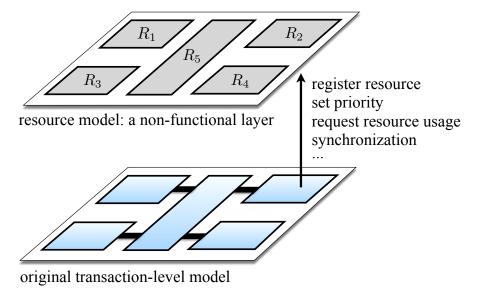

To understand the challenges that this work aims to tackle, it is helpful to consult Figure 2.1 which coherently overviews the considered cases in a co-simulation environment, together with existing techniques that have been applied by previous researchers in each case to expedite the simulation.

The first case depicts the simulation of the software codes corresponding to high-level applications. They usually reflect the computation aspect of the software. The computation is mainly performed at the target processor in interpreting the instructions and initiating memory accesses after cache misses. The technique for faster software simulation in this case is the host-compiled simulation, which has been introduced in the previous chapter.

The second case considers the codes at the hardware abstraction layer, with the emphasis on device drivers. These drivers implement the communication between the CPU and the I/O devices. In the real implementation, a driver function performs the low level software handshake protocols that transfer data among the CPU, the memory, and the registers of the corresponding I/O device. From a modeling perspective, a driver function can be implemented at a high abstraction level for fast simulation. Therefore, the technique for a faster simulation in this case is the adoption of the abstract TLM+ transactions for modeling the transfer of data blocks.

The third case relates to the simulation of a multi-processor system. Because synchronization before each bus-word transaction is expensive, thus the technique for a faster simulation in this case is to temporally decouple the simulation of the software code on each processor, so that timing synchronization is performed only once after simulating a

FIGURE 2.1: Overview of the considered cases of system modeling and simulation.

a) Simulation of high level application codes; b) Modeling and simulation of driver functions at the hardware dependent or hardware abstraction layer; c) Multi-processor simulation in which temporal decoupling can be used. For these cases, the simulation speed can be improved by using existing techniques as listed below each figure.

large piece of the software code. This technique can be used, in addition to host-compiled simulation and TLM+ transactions, to further improve the simulation speed.

Unfortunately, the above techniques applied in each case also induce several problems that lower the simulation accuracy. Describing these problems will be the subject of the following sections.

## 2.2 Challenge in Annotating the Source Code

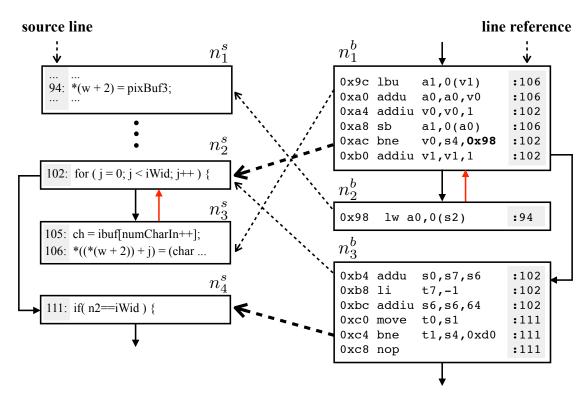

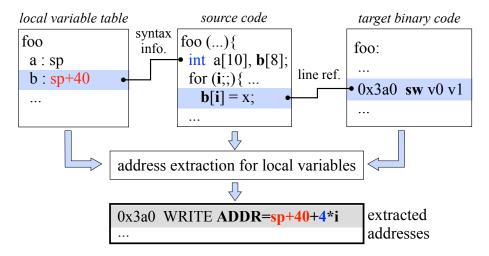

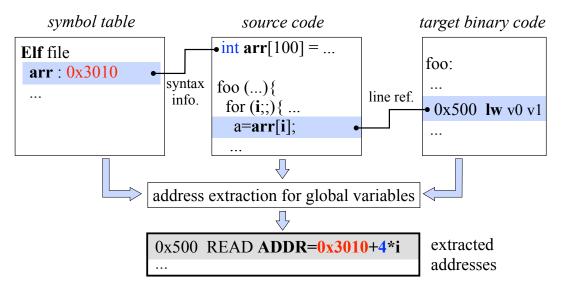

For performance estimation, host-compiled software simulation requires the source code to be annotated with performance modeling codes. The basic steps in doing this have been introduced in Figure 1.2. For a successful annotation, there are two major challenges:

The first one is to resolve the correct position in the source code, so that the performance modeling codes could be annotated in that position. In practice, this translates to mapping the basic blocks in the target binary to those in the source code. The difficulty arises as a result of compiler optimization, due to which it becomes ambiguous to determine a correct basic block mapping.

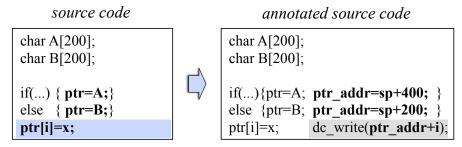

The second one is to determine the data memory access addresses, so that they can also be annotated to enable the simulation of cache and memory accesses. These addresses are obfuscated to extract because they can not be statically obtained from the target binary. Following sections will detail each challenge and point out the concrete problem to solve.

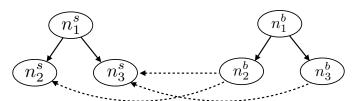

#### 2.2.1 Timing Annotation and Basic Block Mapping

The aim of the annotation is to use the annotated source code as an accurate performance model of the target binary. To achieve this, the following criterion should be met:

The annotated performance modeling codes in the host-compiled simulation should be executed in a similar order as that in the ISS-based simulation of the target binary.

Such an annotation in effect *embeds* the control flow of the target binary code into the annotated program, which then becomes a good performance model of the target binary code. In this way, directly compiling and executing the annotated source code on the simulation host will accumulate the estimated performance in a proper order. Therefore the total execution count of each part of the annotated codes will also be correct. As a result, host-compiled simulation will yield similar performance estimation as compared to simulating the target binary code with an ISS.

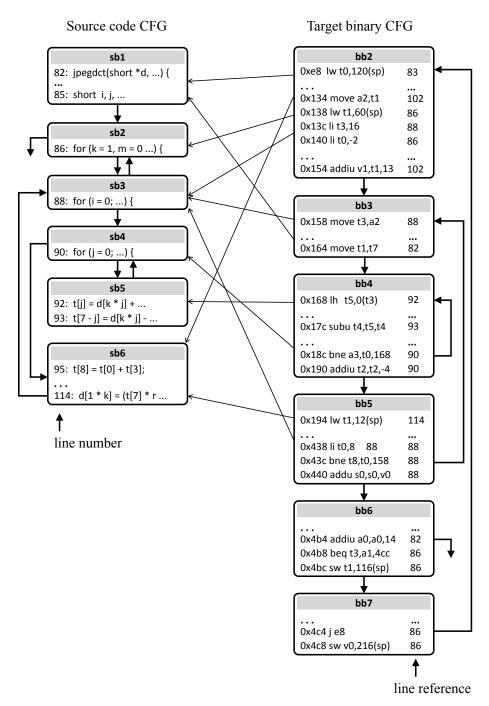

#### The Mapping Problem

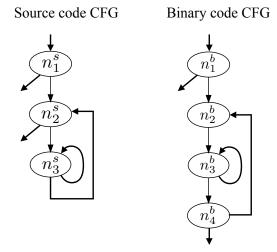

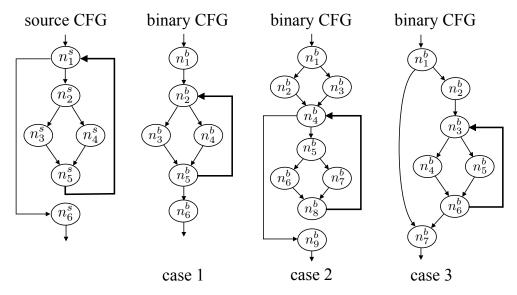

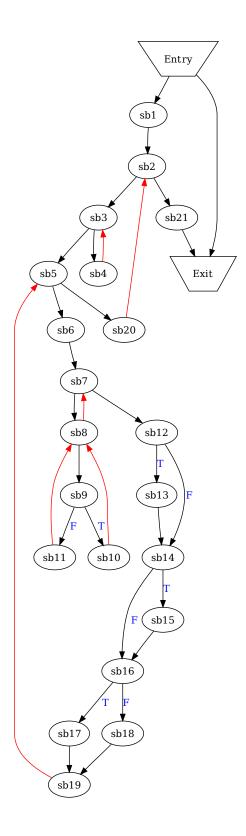

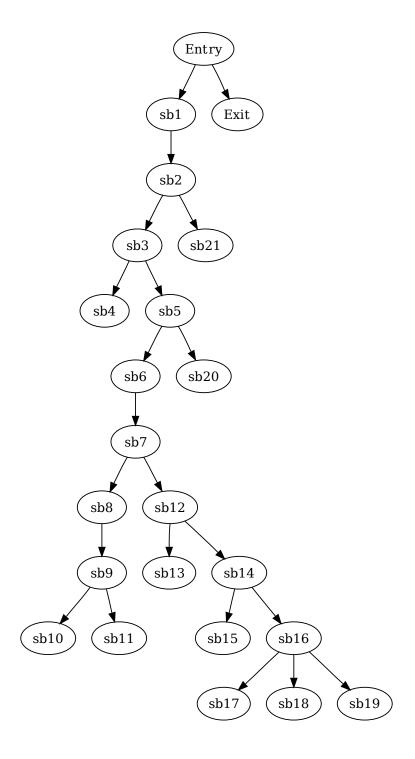

In the ideal case, the control-flow graph of the target binary resembles that of the source code, leading to a one to one mapping between the basic blocks of these two codes. In this case the annotation criterion can be largely satisfied, and the resulted annotated source code can be used as a good performance model of the target binary. However, it is very difficult to meet the annotation criterion if the target binary has been optimized by the compiler. Commonly seen optimizations include code motion, branch elimination, and loop optimization. With compiler optimization, the control-flow graphs of the source code and the optimized target binary can be very different. It becomes obscure how to map the basic blocks of the target binary to those of the source code, therefore a correct annotation position of the performance modeling codes can not be determined in a straightforward way.

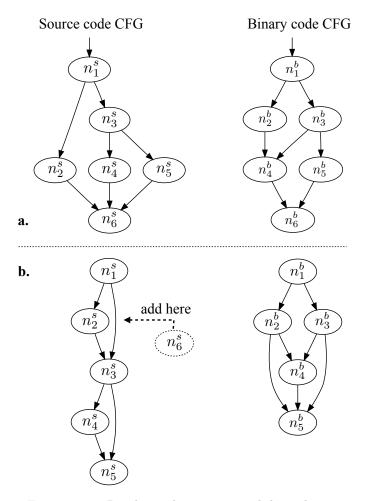

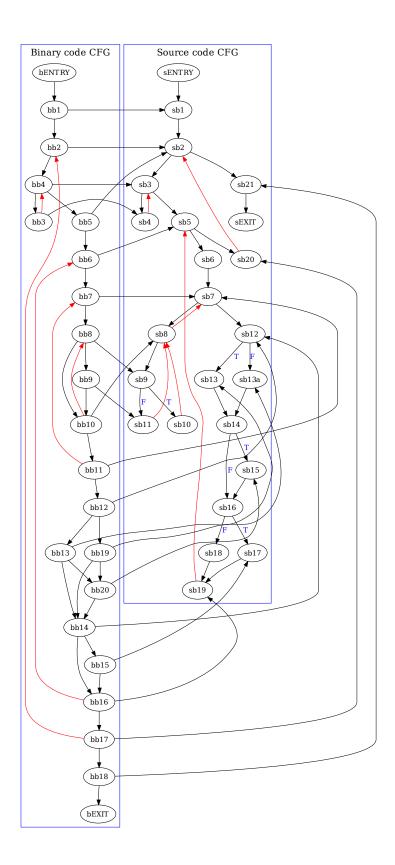

The problem of an altered control-flow in an optimized target binary can be seen in the ambiguous and erroneous line reference file. An example is shown in Figure 2.2 to illustrate the problem. According to the line reference, the instructions in the basic block bb2 of the target binary are compiled from several lines in the source code. These lines correspond to the basic block sb1, sb2, and sb3. So the question is where should the performance modeling code of bb2 be annotated in the source code? Similar problem holds for bb3. As can be seen, bb2 is the entry basic block of the outer loop in the target binary, therefore the correct counterpart for it should be sb2. But this mapping can not

FIGURE 2.2: Ambiguity problem in using the line reference for resolving an annotation position. The line number corresponding to each instruction in the target binary is the reference line from which this instruction is compiled from.

be reliably constructed by inspecting the line reference alone. Structural analysis of the control-flow is required.

#### 2.2.2 Annotate Memory Accesses

Codes related to memory accesses should also be annotated in the source code to enable realistic performance analysis. With them, cache simulation can be performed. At cache

misses, accesses to memory over bus can be simulated, e.g. by initiating transactions. Therefore, annotated memory accesses enable the simulation of inter-module communication. On one hand, this helps in achieving high timing estimation accuracy. On the other hand, it contributes to a HW/SW co-simulation and may aid certain design decisions such as the architectural exploration.

However, the addresses of data memory accesses can not be statically resolved from the target binary code. For example, consider the following instruction in the target binary:

#### sw r1 t1

The only extractable information is that it corresponds to a write memory operation to the address represented by t1. However the address can not be determined in host-compiled simulation, since it does not interpret the target binary instructions and is thus unable to compute the values of the registers. Without those addresses, data cache simulation can not be performed, leading to a lowered performance estimation accuracy. This problem has been long aware in the area of host-compiled simulation. Yet, it still remained as a major challenge.

### 2.3 Timing Estimation for TLM+ Transactions

A TLM+ transaction [14] transfers a large data block, abstracting the underlying software protocols. Fundamentals of TLM+ modeling have been introduced in Section 1.3.3. Due to the raised abstraction level, TLM+ complicates the timing estimation. The arising timing problem is twofold.

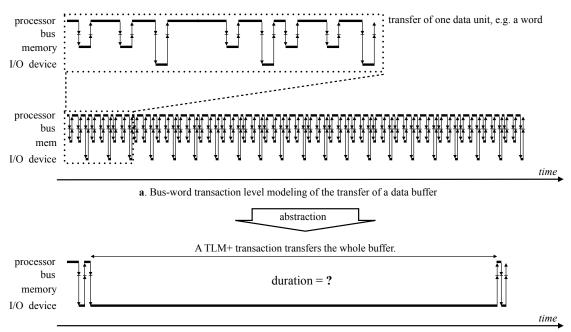

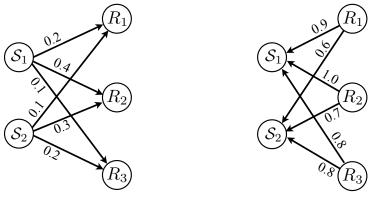

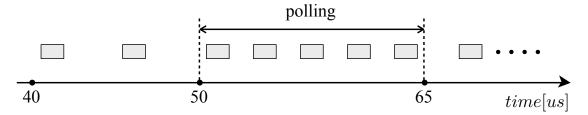

- 1. Consider the illustration in Figure 2.3. One TLM+ transaction in fact corresponds to a long sequence of bus-word transactions. But since the underlying software protocols are not represented any more after such abstraction, it is unclear how to estimate the duration of a TLM+ transaction. For example, assuming a TLM+ transaction that transfers 100 bytes to the UART module, what should be its duration? Furthermore, there are various types of driver functions and software protocols. The resulted TLM+ transactions should be timed differently for different cases.

- To tackle this problem, it is required to extract the timing characteristics of the driver functions that implement the low-level software protocols. These timing characteristics can be used later to time the TLM+ transactions.

- 2. Even if the duration of each TLM+ transaction is known, the bus-word transactions within a TLM+ transaction and their occurrence time are still unknown. These bus-word transactions may cause access conflicts with other bus-word transactions at shared modules. Therefore, it is difficult to estimate the timing of the TLM+ transactions if they overlap with other concurrent processes.

b. Modeling of the transfer of a data buffer with TLM+

FIGURE 2.3: TLM+ complicates the timing estimation. a) The transfer of a buffer by simulating a driver function that implements the low level software protocols. b) The same transfer is implemented using a TLM+ transaction. As is shown in the dashed box in a), multiple bus-word transactions are required to transfer a single unit of data in this buffer. These bus-word transactions include those for memory accesses, checking the status register of the I/O device, etc. A long sequence of bus-word transactions need to be simulated to complete the data transfer. The larger this buffer is, the more bus-word transactions are evoked.

FIGURE 2.4: Timing estimation challenge for TLM+ transactions. Long gray bar (thick line) represents a TLM+ transaction. Blue bars with dashed line represent the bus-word transactions from which the TLM+ transaction is abstracted. A white bar with dashed line represents the delay of a TLM+ transaction.

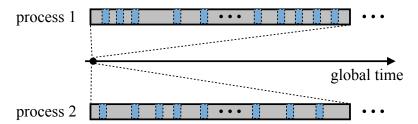

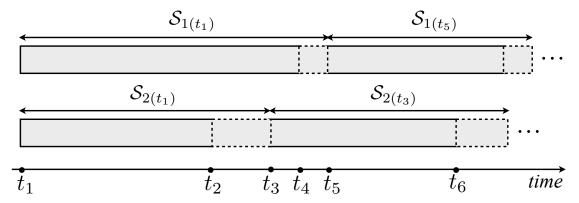

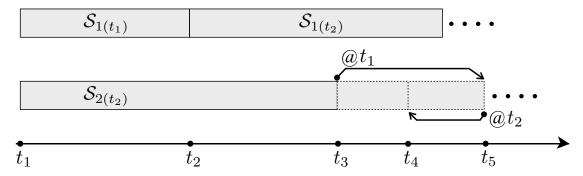

## 2.4 Timing Estimation in Temporally Decoupled TLMs

It is straightforward to see the timing problem induced by temporal decoupling. Consider the example in Figure 2.4 that shows two concurrent processes. When temporal decoupling is used, the bus-word transactions are no longer synchronized with the global time. From the viewpoint of the global time, all the bus-word transactions and the functional simulation within the same quantum occur in zero time. For concurrent processes such as in multiple processor simulation, it becomes infeasible to detect which bus-word transactions of these processes overlap e.g. at the shared bus. As a result, timing of the conflicting bus-word transactions can not be arbitrated by conventional arbitration policy. Timing simulation thus becomes inaccurate. If the transactions are initiated

more frequently, the degree of conflicts may increase and the timing inaccuracy thus becomes higher.

Additionally, using TLM+ transactions implicitly applies temporal decoupling, because timing synchronization is performed only once for a TLM+ transaction that corresponds to a very long time period. But the bus-word transactions within this period are invisible, thus it is not possible to perform standard arbitration at a shared module such as the bus. New mechanisms are required for estimating the delay induced by conflicts at shared modules.

#### 2.5 State of the Art

#### 2.5.1 Annotated Host-Compiled SW Simulation

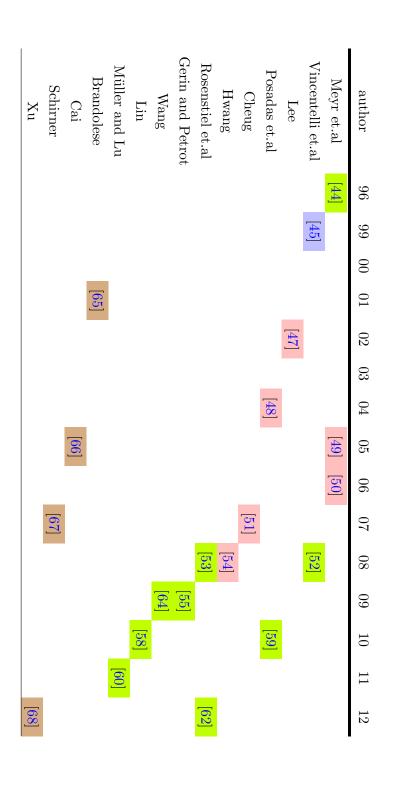

Almost two decades ago, the idea of using host-compiled software simulation was proposed by Zivojnovic and Meyr [44]. This idea has come to provide an alternative way of software performance analysis that is faster than ISS-based simulation. Since the advent, host-compiled software simulation has been continually researched [45–63].

The related work is chronologically summarized in Table 2.1. A majority of existing approaches aim at annotating performance aspects into a code that will be directly compiled for the host machine. The annotated code thus becomes a performance model of the target binary code. Depending on the format of the annotated code, there are mainly three categories of approaches: (1) binary-level annotation, (2) intermediate-level annotation, and (3) source-level annotation. Besides, there also exist profiling-based approaches. Instead of modeling a specific target binary, they use performance statistics to annotate the source code. All of these approaches are surveyed in the following.

#### 2.5.1.1 Binary-Level Annotation

Approaches using binary-level annotation directly transform the target binary into a performance model for host compiled simulation [45, 46, 69]. Usually, the following steps are involved. Firstly, the source code is cross-compiled into the target assembly instructions. Then, the assembly code is translated into a C code. This C code can be annotated and used as a performance model. Afterwards, the annotated C code can be directly simulated on the host machine. The accuracy of binary-level annotation is not affected by compiler optimization, because the performance is both extracted from and annotated to the assembly code. This is the main reason of the proposal of binary-level annotation.

#### 2.5.1.2 Intermediate-Level Annotation

Some approaches annotate intermediate codes generated by the compiler, as proposed by [47, 50, 54, 55]. The performance aspects can be estimated using the intermediate code. They can also be extracted from the target binary and annotated in the intermediate code. Because the intermediate code is partially optimized, the annotation is relatively robust against compiler optimization. However, when compiling the intermediate code to

colored pink are approaches using intermediate level annotation. Cells colored green are approaches using source level annotation. Cells colored Table 2.1: Approaches for timing estimation in host-compiled simulation. Cells colored blue are approaches using binary level annotation. Cells brown are approaches using statistical profiling.

the target assembly, the compiler can still apply target-specific optimization. Therefore there still exist mismatches in the control-flow graphs of the intermediate code and the target binary.

#### 2.5.1.3 Source-Level Annotation

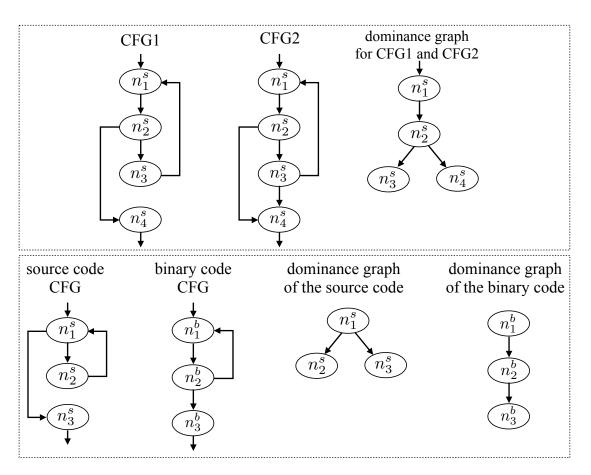

Recently, annotating performance information in the original source code has drawn increasing research effort [52, 53, 58, 60, 62]. This is also termed as source-level simulation (SLS) by some literatures. Compared to binary-level annotation or intermediate-level annotation, source-level annotation offers better transparency and is easier to analyze for software designers. It also directly shows the performance figures associated with each part of the source code. As introduced in Section 1.2.3, the annotation is usually performed at the granularity of basic blocks. The early works on source-level annotation do not perform structural analysis in mapping the basic blocks [52, 53, 58], The annotation consults primarily the line reference file. Under the presence of compiler optimization, such annotation can not preserve the correct execution order of the annotated performance modeling codes. The annotated source code thus is not an accurate performance model. To address compiler optimization, researchers have recently resorted to structural analysis [60, 62]. For example, the approach in [62] tries to preserve the dominance relation in mapping a binary basic block to a source basic block. However, compiler optimization often alters the dominance relation among the basic blocks. Therefore preservation of the dominance relation can be insufficient to provide a robust basic block mapping. Besides the dominance relation, this work also examines controldependency and loop membership of a basic block. They are more adequate in providing a constraint regarding the execution order of a basic block.

#### 2.5.1.4 Timing Extraction Based On Profiling

Besides the work above mentioned, some other approaches model the performance statistically by means of profiling [65–68, 70–72]. The profiling can be constructed at C operation level [65, 66, 71], or task level [67, 68, 72]. For example, a recent approach [68] performs task-based timing estimation. This means the timing information is extracted not from the basic blocks but from the software tasks. The authors first profile each task using Monte-Carlo simulation from which they extract the average timing for each task.

#### 2.5.1.5 Reconstruction of Memory Accesses

Despite some progress, there still lacks a reliable methodology regarding the reconstruction of the memory accesses from the target binary. The addresses for those accesses should be resolved so that data cache simulation can be evoked within the annotated source code. At cache misses, transactions can be initiated to simulate on chip communication, leading to the so-called software TLMs [51, 54, 73–75]. In [48, 60, 61, 76], this problem is alleviated by disabling the use of data cache. Approaches in [54, 58] use random cache misses. But cache miss rate is specific to the executed program and hard to predict. Using random cache misses therefore can lead to timing estimation inaccuracy. In [57], only the addresses of global data are handled. Approaches in [50, 59] use the

addresses of the simulation host to emulate the target memory accesses. However, data locality can be very different in the target binary and the host binary. For example, the stack and static variables can be compiled to very different locations for the host and target machines. Such locality discrepancy can result in large timing errors in case the cache misses are inappropriately simulated. Besides, the data types can be different as well for the host and target machine. For example, the integer may be 8 bytes for the host machine but 4 for the target machine. Therefore if an integer array is sequentially accessed, the number of estimated cache misses using host-compilation would be approximately twice as that on the target machine. Further, many data memory accesses can not be emulated by the addresses of the simulation host, because they are ISA specific and only visible in the cross-compiled binary. For example, when the register values are temporally stored at the stack as in register spilling, the corresponding memory accesses can not be emulated by host machine addresses. In [63], an abstract cache model from worst case execution time (WCET) analysis is used. It uses a range of possible addresses to annotate one data memory access, leading to pessimistic timing estimation. Resolving the memory accesses is further complicated by pointer dereference [55], especially if the pointers are passed as function arguments. To the author's best knowledge, no approach has explicitly considered the pointer dereference problem.

## 2.5.2 Faster and More Abstract HW Communication Simulation

In standard TLMs which use bus-word transactions, timing is synchronized before a transaction is evoked, so that the transactions of concurrent processes can be arbitrated properly. As the timing synchronization causes costly context switches, there have been ideas toward faster simulation of transaction-level models by means of reducing the number of timing synchronization. For a simulation with such course-grained synchronization, some approaches have been proposed to maintain the timing estimation accuracy. This section surveys the works that aim at expediting the simulation of transaction-level models and corresponding methods regarding the timing simulation.

#### 2.5.2.1 Faster Simulation of Transaction-Level Models

Generally speaking, increasing the abstraction level can be used to achieve higher simulation speed. With regard to the simulation of transaction-level models, the concept proposed in TLM+ increases the level of data-flow modeling from bus-word level to packet or data block level [14]. Conceptually similar to TLM+, other approaches [77–80] also model the hardware system at higher abstraction level. A single abstract transaction is used in [77] to implement end-to-end communication for fast simulation of wormhole switched NoC. As mentioned by the authors, timing accuracy is reduced due to abstraction, since the timing of the abstract transaction is obtained empirically. Approaches in [78–80] further abstract the models at the granularity of tasks. They use task graphs based simulation for evaluating task response times, memory utilization, etc. These approaches often target early course-grained performance estimation and architecture exploration. Usually, they can not adequately estimate the delay due to resource conflicts in TLM+ simulation or TL simulation with temporal decoupling.

In addition to increasing the abstraction level, another way to speed up the simulation is to coarsen the synchronization granularity. This is implemented in the TLM 2.0 standard [15] as a temporal decoupling technique, as introduced in Section 1.3.4.2. Readers are referred to Section 2.4 for the timing problem induced by temporal decoupling.

#### 2.5.2.2 Arbitrated Timing Simulation

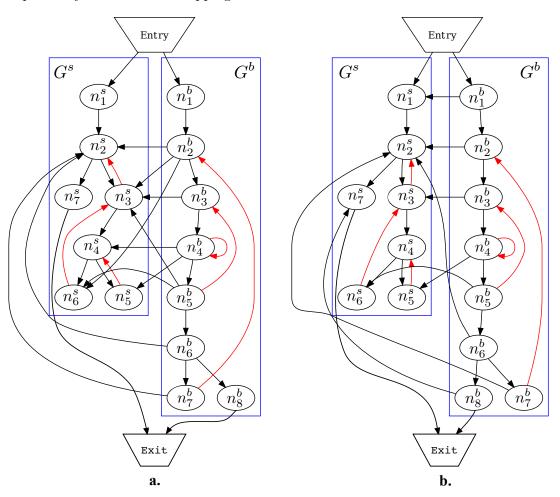

Arbitration based approaches usually trace and store the timing of individual transactions. Then they perform arbitration on long sequences of transactions, such as those occurred within the current quantum.

Schirner et al. [81] propose a concept of result-oriented modeling. A conflict-free optimistic duration is firstly used for a long transaction sequence. Afterward, retroactive timing correction is performed successively, until the actual duration is reached. Indrusiak et al. [82] apply the same concept to wormhole network-on-chip, where they store the timing of packet flows and perform timing estimation thereupon.