# TECHNISCHE UNIVERSITÄT MÜNCHEN INSTITUT FÜR INFORMATIK

# Energy-aware Computing in Embedded Systems and its Operating System Support

Andreas Barthels

Vollständiger Abdruck der von der Fakultät für Informatik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender:

Univ.-Prof. Dr. Johann Schlichter

Prüfer der Dissertation:

1. Univ.-Prof. Dr. Uwe Baumgarten

2. Univ.-Prof. Dr. Andreas Herkersdorf

Die Dissertation wurde am 08.04.2014 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 20.08.2014 angenommen.

# Abstract

The thesis presents a novel approach to establish energy-aware computing in embedded systems in an early design phase. The approach supports both explicit and implicit mechanisms. Embedded systems underlie strict criteria for functional safety, thus the design and software integration process are very intensive. The approach and techniques are formally defined and evaluated in a test bench.

The model case for the evaluation stems from the automotive domain. Modern vehicles serve as a model class of complex distributed systems with special requirements. Because of the limited capacity and dynamics of energy storage and conversion systems, the elaborated mechanisms are designed with scheduling of combined software and power in mind.

In order to be able to meet safety requirements, the modeling and the design of the mechanisms is conducted in an offline manner. This allows to formally verify the scheduling schemes in respect to voltage stability effects in the automotive power net.

The meta-model of the underlying concept is crafted with focus on implementation within current embedded systems in mind. As a reference, a corresponding scheduling paradigm was integrated into the Linux operating system kernel and tested on a modern embedded system platform.

# Kurzfassung

Die Arbeit präsentiert einen neuartigen Ansatz um energiebewusste Datenverarbeitung im Betriebssystem von eingebetteten Systemen zu ermöglichen. Der Ansatz unterstützt sowohl implizite, als auch explizite Mechanismen. Eingebettete Systeme unterliegen strikten Kriterien für funktionale Sicherheit, weswegen der Entwurfs- und Integrationsprozess der verwendeten Software sehr intensiv ist. Das Konzept wird formal definiert und in einem Prüfstand evaluiert.

Der Ansatz wurde speziell für Automobilsysteme entwickelt, die als Beispiel für komplexe verteilte Systeme mit besonderen Anforderungen dienen. Da im Automobilbereich die Kapazität und Dynamik der Energiespeicher und -wandlungssysteme begrenzt sind, wurde ein Ansatz gewählt, der bewusst Software sowie Leistungsmodi und Zeitscheiben im System koordiniert. Kerngedanke ist die Abstraktion und Ausführung gegebener Leistungspläne im Betriebssystem.

Um die Sicherheitsanforderungen erfüllen zu können, wird davon ausgegangen, dass die Modellierung und der Systementwurf offline durchgeführt werden. Hierdurch lässt sich die zeitliche Ablaufplanung im Hinblick auf Spannungsstabilität im Energiebordnetz auslegen.

Das Metamodell der zugrundeliegenden Konzepte berücksichtigt insbesondere die Implementierbarkeit in eingebetteten Systemen. Zu Demonstrationszwecken wurde das vorgestellte Planungsparadigma in den Linux Betriebssystemkern integriert und auf einer aktuellen Plattform getestet.

# Acknowledgements

First and foremost I want to thank my adviser Prof. Dr. Uwe Baumgarten for supporting me throughout my time as a researcher at the Technische Universität München (TUM). He has given me the chance to write this thesis while working on a collaboration project together with the BMW Group and the institutes for integrated systems and energy conversion technology.

I want to thank my colleagues at the mobile distributed systems group, as well as the colleagues at the collaborating institutes. Special thanks go out to the heads of these institutes, Prof. Dr. sc.techn. Andreas Herkersdorf and Prof. Dr.-Ing. Hans-Georg Herzog, for providing me the opportunity to work with them on tools for modeling and simulation, as well as for providing the test bench as part of which the evaluation of this thesis was conducted.

During my time at the TUM, I advised several theses and interdisciplinary projects. The fruitful discussions with colleagues and students, as well as with my research assistants Michael Alberter and Alexandra Buzila, have brought me forward both personally as within our disciplines.

# Contents

| Abstract |                  |         |                                                |    |  |  |  |  |  |

|----------|------------------|---------|------------------------------------------------|----|--|--|--|--|--|

| A        | cknov            | wledge  | ements                                         | v  |  |  |  |  |  |

| I.       | Fo               | undati  | ions & Theory                                  | 1  |  |  |  |  |  |

| 1.       | Introduction     |         |                                                |    |  |  |  |  |  |

|          | 1.1. Foundations |         |                                                |    |  |  |  |  |  |

|          |                  | 1.1.1.  | Power Management in Hardware                   | 4  |  |  |  |  |  |

|          |                  | 1.1.2.  | Embedded Systems Scheduling                    | 4  |  |  |  |  |  |

|          |                  | 1.1.3.  | Power Management and Interaction Paradigms     | 5  |  |  |  |  |  |

|          |                  | 1.1.4.  | Task Graphs                                    | 7  |  |  |  |  |  |

|          |                  | 1.1.5.  | Modeling                                       | 8  |  |  |  |  |  |

|          | 1.2.             |         | em Statement                                   | 11 |  |  |  |  |  |

|          | 1.3.             | Relate  | ed Work                                        | 11 |  |  |  |  |  |

|          |                  | 1.3.1.  | Power Management in Operating Systems          | 11 |  |  |  |  |  |

|          |                  | 1.3.2.  | AUTomotive Open System ARchitecture (AUTOSAR)  | 12 |  |  |  |  |  |

|          |                  | 1.3.3.  | 0, 0                                           | 13 |  |  |  |  |  |

|          |                  | 1.3.4.  | Voltage Stability                              | 14 |  |  |  |  |  |

|          |                  | 1.3.5.  | Precision Time Synchronization                 | 14 |  |  |  |  |  |

|          |                  | 1.3.6.  | Resource–Constraint Project–Scheduling Problem | 16 |  |  |  |  |  |

|          | 1.4.             |         | ibution                                        | 17 |  |  |  |  |  |

|          | 1.5.             | Struct  | ure                                            | 17 |  |  |  |  |  |

| 2.       | Ope              | erating | System Concepts                                | 19 |  |  |  |  |  |

|          | 2.1.             | Opera   | ting System Structure                          | 19 |  |  |  |  |  |

|          |                  | 2.1.1.  | Hardware Access                                | 19 |  |  |  |  |  |

|          |                  | 2.1.2.  | Memory Access                                  | 20 |  |  |  |  |  |

|          |                  | 2.1.3.  | Resource Management                            | 20 |  |  |  |  |  |

|          |                  | 2.1.4.  | Quality of Service                             | 22 |  |  |  |  |  |

|          |                  | 2.1.5.  | Adaptivity Layer                               | 23 |  |  |  |  |  |

|          |                  | 2.1.6.  | Application Program Interface                  | 25 |  |  |  |  |  |

|          | 2.2.             | Real-7  | Fime Operating Systems                         | 25 |  |  |  |  |  |

|          |                  | 2.2.1.  | Hard Real-Time Tasks                           | 25 |  |  |  |  |  |

|          |                  | 2.2.2.  | Soft Real-Time Tasks                           | 26 |  |  |  |  |  |

|          |                  | 2.2.3.  | Implementation Concepts                        | 26 |  |  |  |  |  |

|          | 2.3.             |         | ss Scheduling                                  | 27 |  |  |  |  |  |

|          |                  | 2.3.1.  | Preemption                                     | 27 |  |  |  |  |  |

|     |      | 2.3.2. Queuing                                                                    | <br>    |       | <br>. 28 |

|-----|------|-----------------------------------------------------------------------------------|---------|-------|----------|

|     |      | 2.3.3. Time Slices                                                                | <br>    |       | <br>. 28 |

|     | 2.4. | . Timing Abstractions                                                             | <br>    |       | <br>. 29 |

|     |      | 2.4.1. Clock Synchronization                                                      |         |       |          |

|     | 2.5. | 5. Summary                                                                        | <br>    |       | <br>. 32 |

| 3.  | Log  | gical/Technical Modeling                                                          |         |       | 33       |

|     | 3.1. | . Cyber-Physical Systems                                                          | <br>    |       | <br>. 33 |

|     |      | 3.1.1. Technical Abstraction                                                      | <br>    |       | <br>. 33 |

|     |      | 3.1.2. Software Abstraction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | <br>    |       | <br>. 34 |

|     |      | 3.1.3. Power Management Planning                                                  | <br>    |       | <br>. 37 |

|     |      | 3.1.4. Transducing Mechanism                                                      |         |       |          |

|     |      | 3.1.5. Response Flexibility                                                       |         |       |          |

|     | 3.2. | 2. Cybernetic Control Approach                                                    | <br>    |       | <br>. 43 |

|     |      | 3.2.1. Logical Levels $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$       | <br>    |       | <br>. 43 |

|     |      | 3.2.2. Technical Levels                                                           | <br>    |       | <br>. 43 |

|     |      | 3.2.3. Energy Distribution                                                        | <br>• • |       | <br>. 44 |

|     |      | 3.2.4. Power Distribution $\ldots \ldots \ldots \ldots \ldots \ldots$             | <br>    |       | <br>. 44 |

|     | 3.3. | 3. Summary                                                                        | <br>    | <br>• | <br>. 45 |

| 4.  | •    | stem Integration Methods                                                          |         |       | 47       |

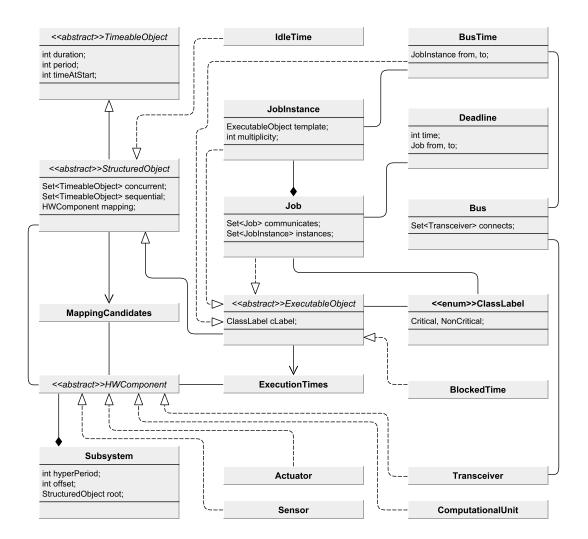

|     | 4.1. | . Satisfiability Meta Model                                                       |         |       |          |

|     |      | 4.1.1. Discretization of Time                                                     |         |       |          |

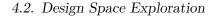

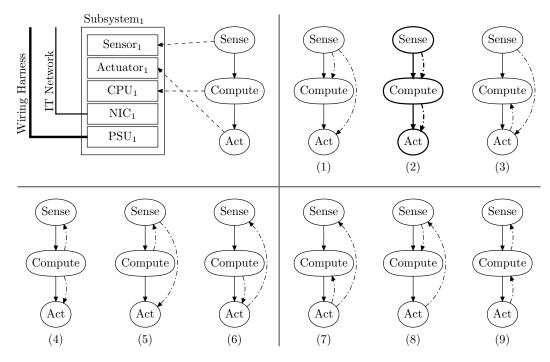

|     | 4.2. | 2. Design Space Exploration                                                       | <br>• • |       | <br>. 51 |

|     |      | 4.2.1. Single Subsystem Scheduling                                                |         |       |          |

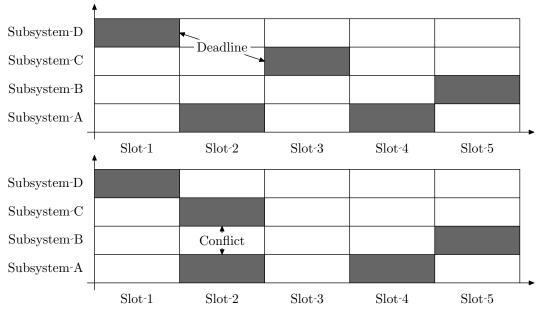

|     |      | 4.2.2. Multiple Subsystems                                                        |         |       |          |

|     | 4.3. | B. Framework                                                                      | <br>    |       | <br>. 55 |

|     |      | $4.3.1. Modeling \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$  | <br>    |       | <br>. 55 |

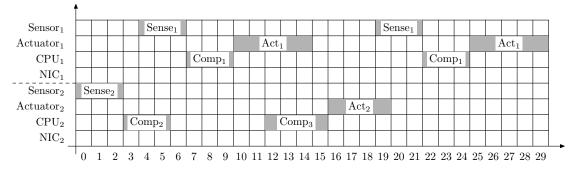

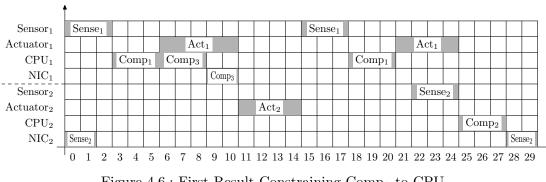

|     |      | 4.3.2. Sample Case $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$          |         |       |          |

|     |      | $4.3.3. Results \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$   |         |       |          |

|     |      | $4.3.4. Simulation \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$       | <br>• • |       | <br>. 58 |

|     | 4.4. | 4. Summary                                                                        | <br>    | <br>• | <br>. 58 |

| II. | . Im | mplementation and Evaluation                                                      |         |       | 59       |

| 5.  | Lin  | nux Implementation                                                                |         |       | 61       |

| 0.  |      | . Configuration and Virtual Filesystem                                            | <br>    |       |          |

|     |      | 2. Plan Scheduler                                                                 |         |       |          |

|     | 0.2. | 5.2.1. Idle Process                                                               |         |       |          |

|     |      | 5.2.2. Task Interface                                                             |         |       |          |

|     |      | 5.2.3. PMP Data Structure Association                                             |         |       |          |

|     |      | 5.2.4. Sequential Logic Operators                                                 |         |       |          |

|     | 5.3. |                                                                                   |         |       |          |

|     | 0.0. | 5.3.1. Dummy RT Tasks                                                             |         |       |          |

|     |      |                                                                                   |         |       |          |

|                                   | 5.4.  | Multicasting Middleware                             | 66<br>66 |  |  |  |

|-----------------------------------|-------|-----------------------------------------------------|----------|--|--|--|

|                                   |       |                                                     | 67       |  |  |  |

|                                   | 5.5.  | 5.4.2. Transducing Machines                         | 67       |  |  |  |

|                                   | 5.6.  |                                                     | 68       |  |  |  |

|                                   | 5.0.  |                                                     | 68       |  |  |  |

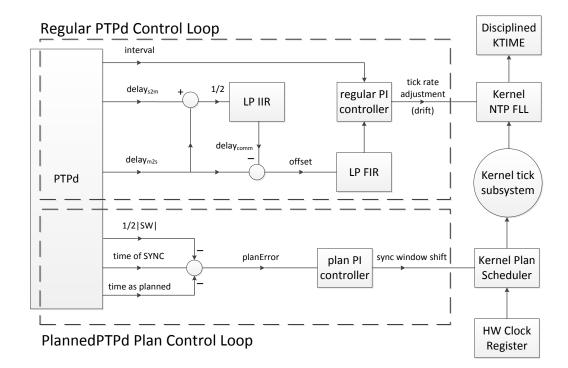

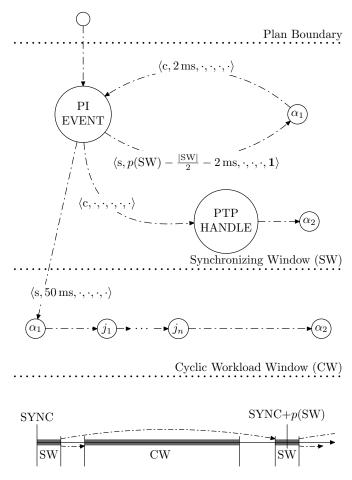

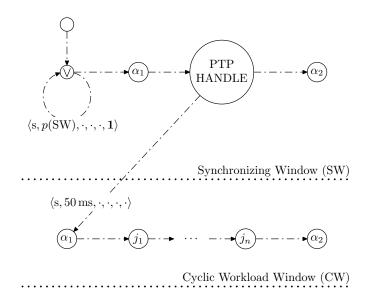

|                                   |       | 5.6.1. Implemented Control Loop                     |          |  |  |  |

|                                   | F 7   | 5.6.2. Precision Time Experiment Setup              | 69<br>74 |  |  |  |

|                                   | 5.7.  | Summary                                             | 74       |  |  |  |

| 6.                                |       | luation in a Test Bench                             | 75       |  |  |  |

|                                   | 6.1.  |                                                     | 75       |  |  |  |

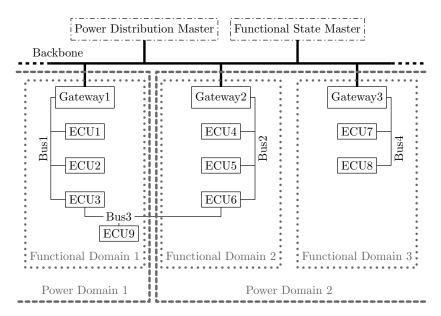

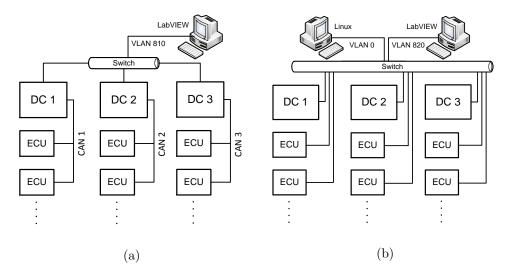

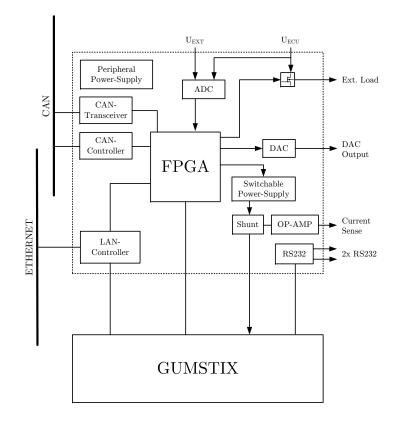

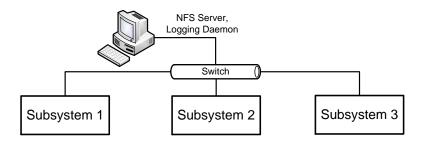

|                                   |       | 6.1.1. Hardware and Network Architecture            | 75       |  |  |  |

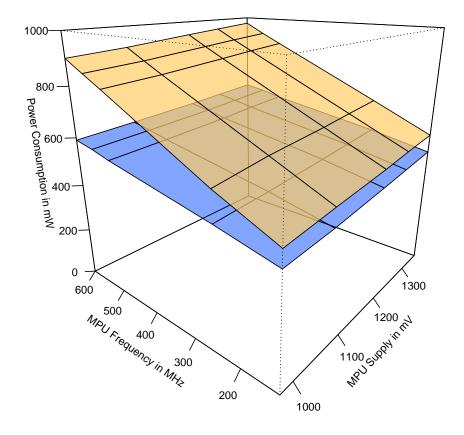

|                                   |       | 6.1.2. ECU Hardware Platform                        | 77       |  |  |  |

|                                   |       | 6.1.3. Small Scale Experimentation                  | 80       |  |  |  |

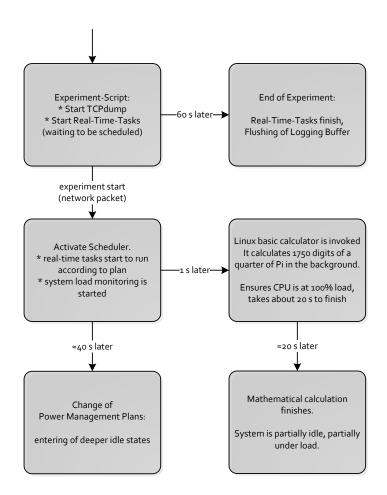

|                                   | 6.2.  | Plan Timing Experiment                              | 81       |  |  |  |

|                                   |       | 6.2.1. Experiment Script                            | 81       |  |  |  |

|                                   |       | 6.2.2. Experiment Control Network Sequence          | 81       |  |  |  |

|                                   |       | 6.2.3. Results                                      | 83       |  |  |  |

|                                   | 6.3.  | Logic Operator Performance Experiment               | 84       |  |  |  |

|                                   | 6.4.  | PTPd Experiment                                     | 86       |  |  |  |

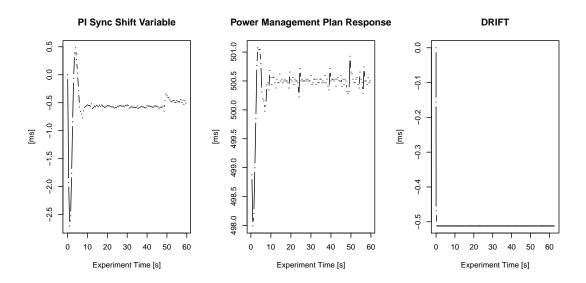

|                                   |       | 6.4.1. PTPd on Idle Subsystem and Network           | 87       |  |  |  |

|                                   |       | 6.4.2. PTPd with Presence of Real-Time Tasks        | 88       |  |  |  |

|                                   |       | 6.4.3. PlannedPTPd with Presence of Real-Time Tasks | 89       |  |  |  |

|                                   | 6.5.  | Summary                                             | 90       |  |  |  |

| 7.                                | Con   | clusion                                             | 93       |  |  |  |

| AĮ                                | open  | dix                                                 | 95       |  |  |  |

| Lis                               | st of | Figures                                             | 97       |  |  |  |

| Lis                               | st of | Tables                                              | 99       |  |  |  |

| GI                                | ossa  | ry.                                                 | 101      |  |  |  |

|                                   |       |                                                     |          |  |  |  |

| Lis                               | st of | Abbreviations                                       | 101      |  |  |  |

| List of Symbols                   |       |                                                     |          |  |  |  |

| Advised Theses, Technical Reports |       |                                                     |          |  |  |  |

| Own Publications                  |       |                                                     |          |  |  |  |

| Bibliography                      |       |                                                     |          |  |  |  |

# Part I. Foundations & Theory

# 1. Introduction

One of the major topics of the century is environment and resource awareness. This is resembled in a strive for increasing efficiency in economy. Computing has become an integral part of economy and society. Using computers to improve efficiency of complex systems (computing for green), as well as making the computing processes themselves more efficient (green computing) are major goals.

Due to the miniaturization of computing systems, there is a trend to embed them into numerous devices. Embedded systems are found in a multitude of smart devices affecting all sectors of economy, individuals' lifes and scientific experiments. Embedded systems are widely used such as in industrial control systems, household appliances, gadgets, and as personal assistance in the services sector. Last but not least, scientific studies rely on embedded computing systems for gathering data.

In the past decades, embedded systems were integrated into all sorts of transportation systems. Of special complexity are both avionic as well as automotive systems. The automotive domain serves as a model case within this thesis. This domain is rich in interconnected embedded systems.

An important issue in this domain is safe and stable operation. Automotive systems can become unstable and subsystems can be reset by so-called undervoltage lockouts. The voltage levels inherently depend on the sources and sinks for electrical energy as well as their dynamic behavior.

The sources and sinks of electrical energy can be subsumed as energy conversion components connected by a wiring harness, as depicted in BMW Technology Guide (2014). In the past, stability issues were largely tackled by adding larger lead-acid batteries, or by increasing the cross sections of the wires. Because batteries and wires have reached large sizes, the power consumption dynamics of the sinks have increasingly to be taken into focus for stable operation.

Hybrid and electric vehicles additionally have multiple voltage levels for different types of subsystems. Legacy systems work using 14 V power nets. High power electrified systems such as propulsion, steering and stability control are supplied using a higher voltage level. Together with these heterogeneous supply voltage systems, the IT network of the embedded systems is heterogeneous too.

Typically, embedded systems are low-cost and highly specialized to the task at hand. Thus, the operating systems running on these devices have to be lean in order to minimize overhead. From a standpoint of system development, system functions are provided by applications. These applications commonly also take care of power management nowadays. The applications form distributed systems which are assumed to be described using formal models. The models resemble the interaction patterns as well as the inter-dependencies of software units.

The embedded hardware platforms are becoming increasingly powerful and at the same time more versatile. Thus, new and flexible concepts are needed in order to integrate and (re-)combine different pieces of software on a platform.

# 1.1. Foundations

There is a wide range of previous and related work for energy aware computing. In this thesis, energy awareness is seeked by working on instantaneous power consumption over time. The consumption stems from hardware converting in between forms of energy. Energy aware computing started with defining different modes of operation for electronic components. These modes in general can be activated by special electronic circuitry which enables electronic systems to power manage themselves.

#### 1.1.1. Power Management in Hardware

Common operating modes of computing systems include shutting down and halting the system, or running at a certain processing speed.

Before Advanced Power Management (APM) (Microsoft Corp., 1996) and Advanced Configuration and Power Interface (ACPI) (ACPI, 2013) were introduced, the changing of operating modes or power states had to be triggered manually by the user. In the x86 architecture, until 80486, computers featured a Turbo-button and had to be turned off manually once the system was halted.

Both APM and ACPI define a set of operating modes in between full on and off, allowing different stand-by operations in between. In general it can be said that the more is turned off, the more costful in time and energy it is to turn the machine to full on again.

Because efficiency of computers have long been researched, hardware manufacturers have incorporated an increasing number of modes like different power and frequency domains for different parts of the hardware. There are a multitude of on- and offline methods for utilizing these already (Benini et al., 2000; Irani et al., 2003; Jejurikar and Gupta, 2004).

As a recent contribution, Moreno and de Niz (2012) have focused on voltage and frequency scaling for uniform multiprocessors. They present an algorithm called Growing Minimum Frequency and focus on maximizing energy efficiency. Next to being able to dynamically switch modes of computing hardware, these modes need typically to be triggered by software over time.

#### 1.1.2. Embedded Systems Scheduling

Planning resource assignment over time is called scheduling. Scheduling is done by operating systems and has seen many different variants.

Since embedded systems are often used for controlling physical processes, tasks mostly have requirements on real-time execution. On the one hand, tasks may have requirements on soft real-time, meaning they need a specific amount of bandwidth over time. They must not necessarily be run at a very specific time point, and may well be interrupted as long as the bandwidth is reached in the end. Hard real-time tasks need a resource at a given time and need to finish by some deadline.

1.1. Foundations

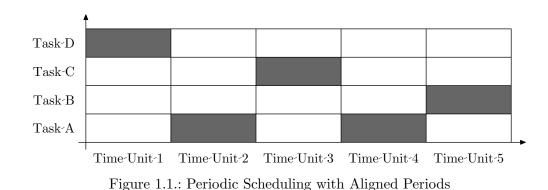

Periodic Scheduling

Periodic scheduling is used to support so-called hard real-time tasks. It is a purely time triggered scheme which has long been under investigation. Every task has a time period and a time offset which define the activation. Using this scheme, and combining it with worst-case execution times of tasks, schedules can be well created and understood offline. Using worst-case times, one can effectively preallocate execution windows for each task. Under normal operation of the software units, the schedule is well predictable despite of the actual execution time within each window.

This periodic form of resource assignment over time is important when system properties need to be guaranteed. Since the time windows meet the worst case system behavior, the resource utilization is typically significantly lower than 100 %. Thus, this paradigm typically allows for energy savings during idle phases, but it must be ensured that the system predictability is maintained.

## Aperiodic Scheduling

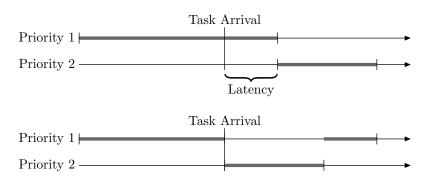

Aperiodic scheduling is less predictable in general. Both hard as well as soft real-time tasks can be aperiodic. Tasks are generally triggered by events, which can be timer expirations, or system inputs.

The nature of aperiodic systems is in general hardly predictable. Typically, tasks are assumed to be triggered according to stochastic processes. The superposition of task activations can lead to many different schedules over time. To resolve conflicts of tasks requesting the same resource at the same time, prioritization and preemption can be used.

Figure 1.2 shows an example in which a higher prioritized task arrives during the runtime of a lower prioritized task. In a system without preemption, the next task is selected based upon priority once the current task finishes. Additionally, a system may support preemption, interrupting the lower prioritized task and resuming its operation after the higher prioritized task has finished.

# 1.1.3. Power Management and Interaction Paradigms

Operating systems as well as middlewares incorporate interfaces in between distributed applications, allowing a multitude of interaction schemes. The interfaces may well be

#### 1. Introduction

Figure 1.2.: Scheduling Both Without and With Preemption

used to coordinate power management mechanisms as part of the application, as well as incorporating a management mechanism in themselves.

Eugster et al. (2003) characterize and compare common software design patterns. They distinguish the following patterns:

**Message Passing** The simplest form of interaction scheme is passing of messages as plain datagrams. Distributed systems relying on message passing can best be described as synchronous data flow graphs. As such senders and receivers are coupled in time, space, and synchronization.

In the scope of software running on top of an operating system, different services can be utilized, such as name resolution, routing, ordered delivery and queuing.

- **Message Queuing** Queuing is a common mechanism within operating systems, provided on multiple levels, e.g., by the device drivers, as well as sockets or the Transmission Control Protocol (TCP). Using queuing, senders and receivers can be decoupled in synchronization, allowing receivers to read asynchronously.

- **Remote Procedure Calls** Remote Procedure Calls (RPCs) use message passing to semantically interact among software components. A software component may provide interfaces for interaction with other components. For RPC, a mediating layer between components is needed. This layer can provide RPC synchronously as well as asynchronously, which leads to the notion of notifications.

- **Notifications** Notifications asynchronously propagate events in the system. Using RPC, notifications may be delivered by invoking specified callback procedures. Notifications are widely used to implement the observer design pattern. Using asynchronous notifications, communicating endpoints are still coupled in time and space, meaning they have to be online at the same time and need a way of communicating with each other without an intermediary component. The coupling in time and space can be lifted by adding an intermediate component such as a shared space.

- **Shared Spaces** Shared spaces form an intermediate entity between endpoints. Endpoints are decoupled in time and space; they do not address each other directly and do not need to be up and running at the same time. The shared space is filled

1.1. Foundations

Figure 1.3.: Complex Interaction Pattern for Decoupling of Endpoints

asynchronously and read synchronously. Providing additional decoupling from synchronization results in the implementation of a publish/subscribe scheme,

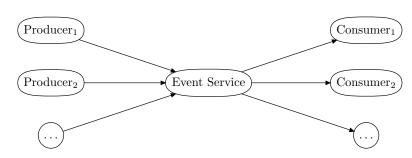

Publish/Subscribe Publish/subscribe is a means to decouple entities from time, space, and additionally from synchronization. This pattern is similar to the shared space, but subscribers are asynchronously notified of data being published by publishers. This scheme provides the most sophisticated means of decoupling interacting components and thus allowing for great flexibility in system integration and operation.

These interaction paradigms are subsumed in middlewares. As part of the software engineering process, the description of participating components enable system-wide adoption and adjustments of Quality of Service (QoS) as described by Schantz et al. (2003).

#### 1.1.4. Task Graphs

Since there is no standardized set of tasks and interaction patterns, tools for generating sets of tasks were developed. One such tool is Task-Graphs-for-Free (TGFF, Dick et al. (1998)). It randomly generates sets of independent graphs as well as dependent directed acyclic graphs of tasks. These graphs define an ordering, within which the data flow and thus execution must occur. Execution properties, like worst-case execution time as well as end-to-end deadlines and communication resources can be included.

The task graphs were initially used for synchronous aperiodic scheduling. If some deadlines are omitted or if multiple graphs are executed on the same system, it may well serve for generating asynchronous patterns.

#### Synchronous Data Flow Graphs (SDF)

Synchronous Data Flow Graphs feature cyclic input dependencies and thus are only applicable to synchronous periodic scheduling (Stuijk et al., 2006). Due to the strong coupling in time, space and synchronization, they are mostly used in integrated circuit design, e.g. for accelerating multimedia stream processing.

Thus, they allow for analysis of multicore, highly parallel multiprocessing applications. They are widely used for deadlock and consistency analysis. Consistency means all outputs of a node are being processed and the memory needed for execution is bounded. Different types of task graphs may serve as a model for the logical interaction pattern of software components, which is one aspect of modeling a distributed system such as a vehicle.

#### 1.1.5. Modeling

In order to tackle the increasing complexity, model-driven software development became the basis for interconnected embedded systems (Karsai et al., 2003).

The modeling distinguishes the following layers:

- **Requirements Level** when a function is defined, the requirements are specified first and foremost. These requirements comprise the behavior and functionality of the system. An implementation of these requirements will then touch the following, more specific levels.

- **Logical Level** describes the software from a logical point of view. Within this level, no implementation specific knowledge is modeled. Software is split up into logical units along with their communication dependencies. The logic has to fulfill the respective requirements. Using multi purpose hardware, these logical units can be deployed and implemented in various ways on the technical level.

- **Technical Level** contains the technical architecture of the system; the kinds of and numbers of embedded systems. Which is, more specifically, a description of the computing hardware and peripherals, as well as communication links. Each hardware component of such an embedded system has a set of features, and different operating modes.

- **Implementation Level** handles the implementation of the abstract logical functions to specific hardware. In here, the software is again divided into units (i.e. components), which do not have to be the same as in the logical level. Each component can be tested to meet the requirements and is often monitored during runtime to ensure correct behavior on the concrete hardware platform, which comes into play within the integration level.

- **Integration Level** ships implemented software units onto hardware units and provides scheduling and resource assignments. On the integration level, all abstract models are subsumed. This level is needed to deduce physical properties of the system, such as timing and dynamic behavior. Integrating software components onto specific hardware is done by configuring the operating system so as to meet all requirements. These requirements are typically according to static or dynamic resource allocation. Static allocation is the fixed reservation of a resource during runtime. Dynamic allocation is referring to scheduling resource usage over time.

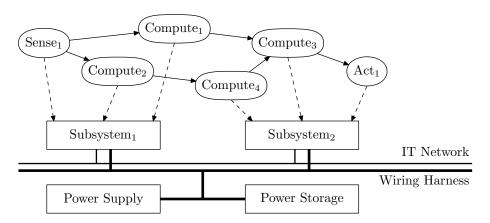

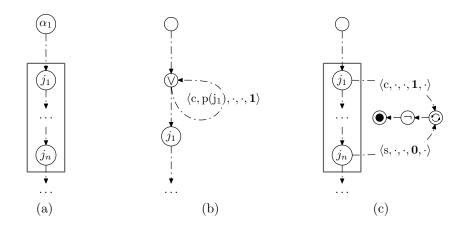

Figure 1.4 depicts an example for combining a logical and technical model with an integration view. The jobs and communication patterns stem from the logical layer, the hardware subsystems build the technical layer. Both are combined in the integration view by statically partitioning jobs to hardware components.

1.1. Foundations

Figure 1.4.: Illustration of jobs interconnected by communication patterns and distributed onto embedded subsystems. Illustration taken from Barthels et al. (2011).

### Unified Modeling Language (UML)

In the past decades, the UML was elaborated by a multitude of contributors. The language copes with all levels of modeling by, e.g., specifying requirements, such as actor, sequence, and state diagrams, as well as logical models such as class diagrams. For specific modeling domains, such as automotive systems with their special hardware equipment, special tools aiding in system development have been developed (Haberl, 2011). The UML was extended to the Systems Modeling Language (SysML), which leads to computer-aided system design.

#### Computer-Aided System Engineering (CASE)

Modeling is central to CASE-tools. The tools handle different aspects of the levels mentioned before. PREEvision by Vector Informatik GmbH (2013), e.g., copes with the requirements, logical, and technical levels. In recent versions, additional support for the implementation and integration levels was added. Depending on the target platform, specialized tools are used for the implementation and integration of components. In the early phase, disregarding actual implementation, the system can already be formally analyzed. For system analysis, so-called model checking methods are being researched. These methods require the transformation of the models into descriptions which are amenable to analysis. These models as well as their algorithmic simulation and analysis are implemented in widely adopted tool-chains, like UPPAAL (Behrmann et al., 2006). These tools can be used to model the processes in distributed embedded systems and to analyze them in terms of model checking.

## Model Checking

Common models are Timed Petri Nets (Ramchandani, 1974), and timed automata (Alur and Dill, 1994). These models can be converted into one another, as analyzed by Balaguer et al. (2012). The abstractions and tools for model checking are used for testing

the feasibility of a system design, like a control or resource allocation strategy. They are not designed for being run in the embedded systems as they are.

For modeling control systems and running them as they are, a theory of hybrid automata and abstractions for hybrid systems were developed (Tiwari, 2008). Hybrid systems grasp a mixture of continuous (physical) and discrete (IT) event-based distributed systems. Hybrid automata can be rolled out and integrated into embedded systems to actually perform the functions. They can be checked, or validated beforehand, but they are not as amenable to automated exploration of the design space, due to their expressiveness.

#### **Design Space Exploration**

Using tools for model checking, engineers naturally perform the task of design space exploration; a sensitivity analysis regarding performance of different design aspects. This can be achieved by repetitively tweaking the models and perform checks and simulation on them. The simulation can yield artificial performance measures, which again can be used to rank the solution candidates. Automating this task of exploration, and combining it with optimization was done for the task of mapping software to hardware, by Katoen et al. (2013).

The automation regards two important steps.

- 1. It is important, that solutions which are analyzed are correct. Thus an enumeration mechanism is needed which inherently produces consistent models. This can be tackled by utilizing solvers for constraint satisfaction problems, such as the one used by Katoen et al. in Microsoft FORMULA (2012).

- 2. The model has to be simulatable, be it through modeling as a stochastic process (Katoen et al., 2013), or as an accurate simulation as explained by Šimunić et al. (1999), and Walla et al. (2012c).

Once a valid configuration and integration of all components is found, the system can be shipped and runs on an operating system. This operating system abstracts and manages the resources employed by the distributed applications.

#### Testing-in-the-Loop

The development of distributed systems is often split up using a divide and conquer approach. Each subsystem model or implementation can be tested against its specification. In an early stage of the design process, only models of the subsystem exist. These are tested using the Model-in-the-Loop (MiL) approach. Using this approach, the models are deployed into a test bench and the subsystem dynamics can be analyzed.

If the models successfully pass the tests, they are being implemented and the final subsystem candidate can be tested using Hardware-in-the-Loop (HiL). The concepts presented in this thesis are designed with support for these testing processes in mind.

# 1.2. Problem Statement

The key challenge is to enable energy efficiency while maintaining safety and enabling further computing-based innovations.

Nowadays, operating systems for real-time systems hardly support dynamic power saving mechanisms. A novel power management paradigm is needed allowing to achieve energy savings as well as supporting transient reactions to system hazards. For increased flexibility and power savings, it is desirable that software units can be redeployed onto different hardware units.

For this to be feasible, suiting abstractions have to be found and services in the operating systems have to be implemented, which support a variety of hardware architectures.

# 1.3. Related Work

The field of energy aware computing has seen a long history of related work. The summary given in this chapter focuses on aspects of power management in operating systems and energy management in complex distributed systems.

Researching voltage stability effects in power nets together with operating system level scheduling is largely an open issue. In the following, important related work is presented, touching aspects relevant to the problem statement of this thesis.

## 1.3.1. Power Management in Operating Systems

The aforementioned models abstract the underlying operating system and concentrate on the functionality of the application components. There exists a long history of related work in the field of power management in operating systems. As a modern and widely used operating system, the Linux kernel functionalities are briefly sketched.

For assigning resource budgets to trees of processes Linux, e.g., annotates its process tree with control information. Processes can be assigned bandwidth values or other fixed resources, which must be respected by the scheduler.

For the Linux operating system, different real-time application patterns are supported by different extensions such as those developed by Kim et al. (2002, 2005). These extensions target adjustable QoS settings.

For very low power wireless sensor networks, an assessment of efficiency of scheduling mechanisms is given by Mazumder et al. (2012). The assessment is special in regards to applications with large sleeping times in the order of seconds, and does not account for real time properties. The implemented algorithms are inspired by the Linux scheduling subsystem. More details on these operating system concepts are given in Chapter 2.

## Quality of Service (QoS)

Related to power management is the topic of QoS. Waking up a hardware component from power saving mode, typically induces latencies. The same can apply to switching component frequencies, which may interrupt active tasks and deteriorate timer accuracy. During the switching of power states, requests can not be processed and thus deteriorate the QoS of the operating system platform to the applications.

Figure 1.5.: AUTOSAR Mechanisms for Energy Efficiency in Electronic Control Units

Linux allows to adjust QoS requirements in different hard- and soft real-time categories. Hard real-time refers to latencies induced by hardware wake-up, while soft realtime measures resource usage in bandwidth, i.e., resource amount per time unit. These bandwidth measures can refer to CPU time per second, or communication throughput. Using Linux, one may additionally assign resource budgets using resource kernels, or starting from version 2.6, by using the integrated control groups data structures.

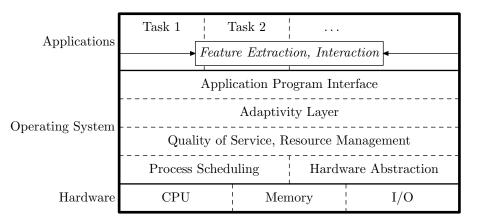

#### 1.3.2. AUTomotive Open System ARchitecture (AUTOSAR)

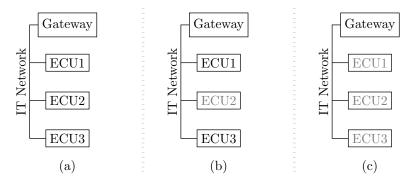

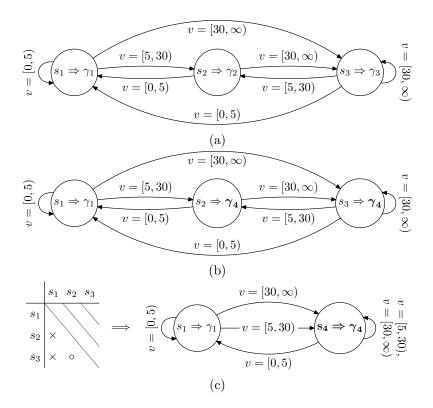

The AUTOSAR includes mechanisms for turning on and off single Electronic Control Units (ECUs), virtual function clusters, and bus systems (AUTOSAR, 2013). Figure 1.5 shows different modes of operation enabled by AUTOSAR. In 1.5.a, all embedded systems are active and running to support different automotive functions. In 1.5.b, a selected system was at least partially shut down by a notification mechanism. If the operating system and computing units are still running, this is called degradation. When in pretended networking mode, all system components are shut down and the networking capabilities are loaded off to a dedicated piece of hardware, sustaining the operation of the communication network (Schmutzler et al., 2010). In this mode, periodic signals can still be sent from the system and specific input patterns may trigger a restart of the system.

Figure 1.5.c shows the feature of partial networking. In this mode, the complete bus system can be shut down. Thus, the instantaneous power consumption can be reduced to a minimum (Fuchs et al., 2010).

The feature of partial networking is standardized in a decoupling mechanism similar to publish/subscribe. The event service serves as the master component, with which publishers explicitly request the presence of a virtual function cluster. The requests are mediated in a way, that the subscribers delivering the functionality of the cluster receive explicit notifications to turn themselves on and off.

This decoupling is very helpful in coping with the complexity of the functions and to determine the necessity of components being online. During system runtime, the standard neglects the power consumption dynamics and supply voltage stability of the vehicle as an electric system.

These effects can be taken into account not only online, but also offline, by carefully

1.3. Related Work

Figure 1.6.: Schematic Energy and Power Management

modeling the vehicle dynamics.

#### 1.3.3. Energy Flow Management

Despite the view on electronic functions from a software perspective, there is a lot of related work regarding the electrical or energy flow in an electric system.

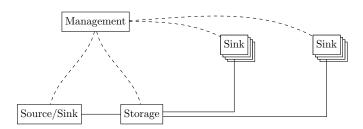

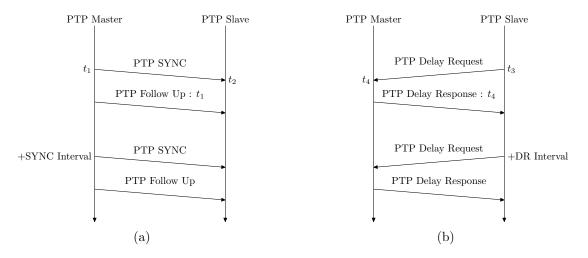

A vehicle can be seen as a network of sources, storage units, and sinks for electrical energy (Gehring et al., 2009). Figure 1.6 depicts such a network.

The network consists of at least one source of electrical energy, one storage component and different classes of sinks.

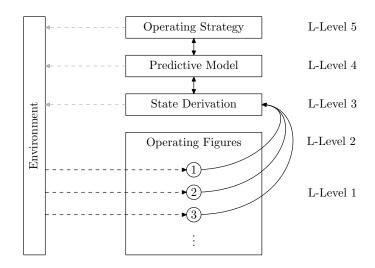

For managing this system of energy conversion components, cybernetic power distribution was proposed by Kohler et al. (2010, 2011) and subsumed in the PhD thesis (Kohler, 2013). The approach incorporates theory of cybernetic control, recombining logical and technical levels of the architecture.

There may be technical hierarchies due to the employed energy conversion processes. A group of energy sinks may be powered by a dedicated power supply line. This power supply line may be converting in between different voltage levels and may in its own depend on an extra source, like an alternator. Using the notion of technical hierarchy, arbitrary hybridization and energy distribution concepts can be described.

The logical hierarchy envisions a dedicated distribution master component in the architecture, which performs strategic decisions based upon predictions.

#### **Electric Energy Sinks**

In combustion vehicles, energy sinks are formed by assistance systems like chassis control, electric power steering or stability control, but also by all comfort and entertainment functions present nowadays.

In hybrid and electric vehicles, the drive-train poses an important component, which mostly serves as a sink, but also as a source of electrical energy upon recuperation.

The energy consumption dynamics of many such sinks may not be altered. This is due to safety requirements. Still, non-critical comfort devices may be altered, as well as the general process of controlling peripherals.

#### **Electric Energy Sources**

Depending on the type of vehicle, be it combustion, hybrid, or electric, different battery technologies are used (Ceraolo, 2000).

Battery technology has seen some progress in recent years. Combustion cars still use legacy lead-acid batteries together with an alternator for converting mechanical into electrical energy. While the lead-acid batteries feature highly dynamic capabilities due to a low inner resistance, the alternator is quite limited, because it has to be synchronized to the combustion engine.

Newer battery technology features larger capacities but worse dynamic capabilities. This can be compensated by including a mixture of battery technology or also by using capacitors to cope with transient peak power demand (Polenov et al., 2007).

Managing energy flows between vehicle components helps optimizing energy efficiency during operation.

For vehicle safety, transient processes have to be considered which leads to the topic of voltage stability.

#### 1.3.4. Voltage Stability

There are established practices to design the topology of an automotive wiring harness. One typically has a battery and an alternator close to the engine. These components power a set of consumers over relatively long distances. The consumers can electrically be considered as loads imposed on the system.

In order to research into voltage stability, it is important to understand the dynamics of the involved components. Gehring and Herzog (2009) have researched into simulation models for stability in automotive 12 V power nets. Kohler et al. (2011) have built on these results and have conducted additional experiments in a test bench.

For safe operation, different types of electrical energy sinks may be supplied on different voltage levels. Operating on higher voltage levels enable loads to draw higher amount of power with less resistance. The power net may be supported by using stabilization units operating and converting in between different voltage levels.

#### Stabilization Units

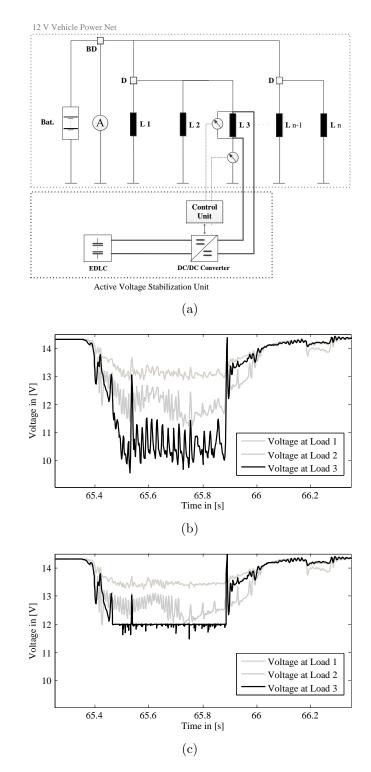

Transient loads in the electric system of the vehicle can lead to critical voltage drops. Figure 1.7a depicts a schematic of an automotive power net featuring an optional stabilization unit. Without the stabilization unit, significant voltage drops can occur in the wiring harness, due to the electrical properties of the wires. This is illustrated in Figure 1.7b. Due to the geometric nature and electric properties of the wires, the voltage drops in the system vary in significance.

In order to prevent the voltage from dropping, stabilization units may be deployed along major loads. Figure 1.7c depicts the results of such a stabilization. The voltage levels for all three loads is significantly increased by supplying Load 3 out of a short term storage and energy conversion unit.

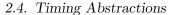

#### 1.3.5. Precision Time Synchronization

In the past decade, an IEEE standard for synchronizing clocks in distributed systems was crafted (IEEE1588). The standard was first implemented for the Linux operating system by Correll et al. (2005). They show that the level of synchronization reached by

1.3. Related Work

Figure 1.7.: Automotive power net and voltage stabilization example. Figures taken from Ruf et al. (2013b)

this software-only implementation is quite good, provided the system is idle and may prioritize the protocol above all other tasks.

Since achieving good synchronization does not work well in software-only scenarios with high load, a lot of research was put into hardware assisted implementation of the IEEE1588 (Ohly et al., 2008). For supporting PTP hardware clocks, a new Linux Subsystem was designed by Cochran and Marinescu (2010). They are using the Subsystem together with hardware support, to later-on synchronize the Linux system time (Cochran et al., 2011). Kovácsházy and Ferencz (2012) compare the use of different hardware components to assist the synchronization process. Their results also indicate that the system load significantly deteriorates the quality and speed of the synchronization in software-only implementations.

Zhu (2013) compares Phase Locked Loop (PLL) and Frequency Locked Loop (FLL) implementations for the case of Base Stations as part of a telecommunication network. The experiment was conducted on a IEEE1588 capable processor. Improvements on software-only methods which rely on operating system mechanisms are largely an open issue, especially with presence of critical tasks and high system load.

#### 1.3.6. Resource–Constraint Project–Scheduling Problem (RCPSP)

Besides scheduling for energy efficiency, as discussed by most previous work, one may want to ask for schedules which satisfy voltage stability criteria. The problem characteristic may be found similar to resource constraint project scheduling. The field of project scheduling stems from operations research (Colak et al., 2013). It is used to optimize the project in respect to different objective functions. These may be the total completion time, the number of resources used etc.

#### Multi-Mode

An extension to the simple RCPSP is to introduce multi-mode execution of jobs. This means an activity or job may be run in different modes which require different amounts of resources.

The traditional partitioning problem of software to subsystems may be tackled by introducing modes not only for operation modes of the underlying hardware, but also for the selection of a partition variant.

Voltage stable scheduling would mean to introduce additional constraints to the classic scheduling problems which may be described using the generalized notion of resources in project scheduling.

#### Resources

Resources in project scheduling may either be

- renewable, meaning at each time step, a set of resources becomes available. This kind of resources is typically labor, machines, and can be

- non-renewable, e.g. total budget for a project.

Scheduling in regards to voltage stability could be tackled using this framework by assigning a maximum amount of current draw for each time unit. The model lacks features of hard real-time scheduling problems such as end-to-end deadlines and cyclical execution within a set of jobs. These additional constraints are essential in regards to providing functional correctness of an embedded system.

# 1.4. Contribution

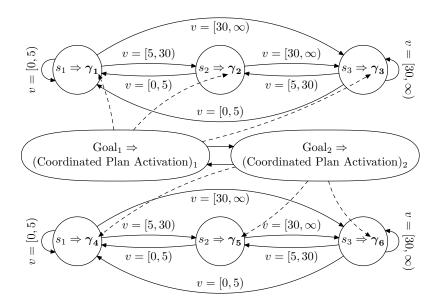

An execution model of tasks to be run in the operating system was crafted, which incorporates the active scheduling of hardware power states. This extended notion of scheduling is culminated in the definition of generalized Power Management Plans (PMPs). The formalism allows the flexible assignment of plans to arbitrary functional system states, thus transducing from system inputs to sequences of schedules.

The solution is described in a mathematical manner and implemented in prototypical embedded systems. To support the engineers in the early design-phase, assistance in model checking and exploration is given based on solving generalized constraint satisfaction problems. The problem formulation also regards constraints on voltage stabilization. Since voltage stability is a local phenomenon which in turn results from a global system behavior, time synchronization is important to enable scheduling for stability.

As a proof of concept, the methodology of PMPs is applied to a software-only implementation of the IEEE1588 Precision Time Protocol (PTP). Results show that PMPs enable the combination of critical system tasks with a lower prioritized synchronization process. The platform guarantees high QoS levels and additionally enables significant energy savings.

# 1.5. Structure

The structure of the work at hand is divided into two parts. The first part covers the concept and modeling of operating systems and distributed functions in Chapters 2–4.

- **Chapter 2** describes important operating system concepts which serve as the foundation of the concept and implementation presented in this document.

- **Chapter 3** mathematically defines the concept of an operating system mechanism which proactively transduces system inputs to sequences of Power Management Plans (PMPs).

- **Chapter 4** details an approach to construct and check power management model instances for correctness based on formal methods.

The second part copes with the implementation and the evaluation of the concepts in a prototypical testbench.

- **Chapter 5** describes the protoypical implementation of the concept in Linux version 3.0.

- Chapter 6 gives experiment setups and evaluation results.

$Chapter \ 7 \ {\rm concludes} \ the \ thesis.$

# 2. Operating System Concepts

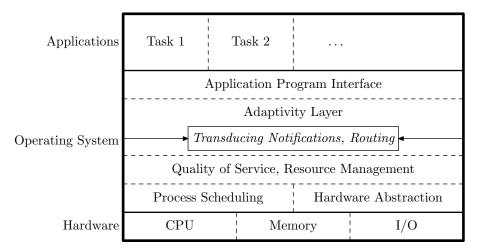

Key operating system concepts include hardware abstraction, resource management, in- and output, security and scheduling. For the operating system to support power management, all these aspects are affected.

# 2.1. Operating System Structure

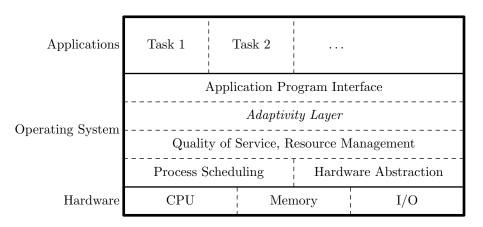

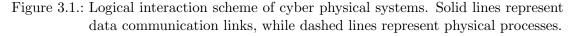

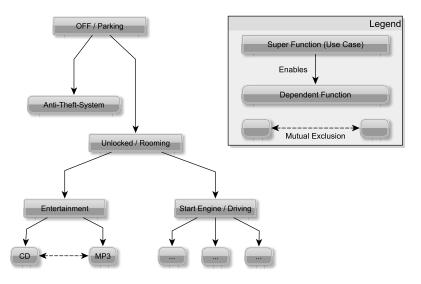

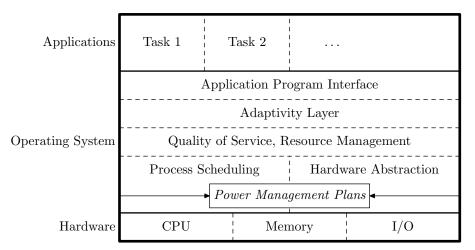

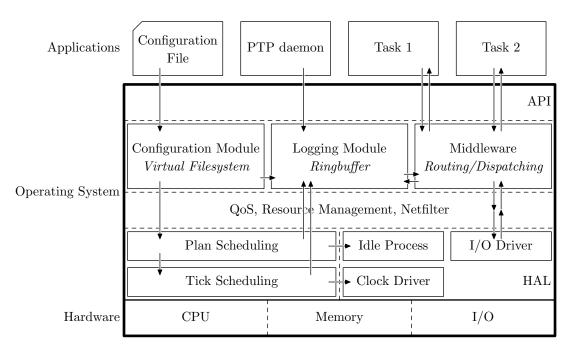

Operating systems are designed to intermediate between hardware, software and the user. To achieve this task, different concepts were developed in the past and are under investigation nowadays. To structure and compare different approaches, Figure 2.1 retypes the aspects relevant to this thesis. Similar and more general diagrams can be found, e.g., in Silberschatz et al. (2005).

Chapter 2 is organized around Figure 2.1, starting with generic operating system components and later-on details specific real-time concepts.

#### 2.1.1. Hardware Access

One key task of the operating system is to allow for heterogeneous applications to run on and share computing resources. On the lowest layer of the operating system, the access of the underlying hardware is managed.

Modern processing hardware has different levels of privilege, of which only the highest levels allow direct hardware access. The actual hardware access is always mediated by the operating system. In the so-called Hardware Abstraction Layer (HAL), device drivers provide abstract descriptions of and interfaces towards the underlying hardware.

Figure 2.1.: Operating System Modularization

#### 2. Operating System Concepts

Computing resources such as memory and computation time are typically shared in a time and object division multiplexing manner.

#### 2.1.2. Memory Access

For processes and memory access, different paradigms can be employed. In the following, the techniques of addressing memory in real and protected mode are presented

#### **Real Mode Addressing**

When programming hard real-time applications on low end hardware, resources often need to be accessed immediately and directly. For memory, this is called real mode addressing. In real mode, every process can access the whole physical memory directly. Since the access is very pure, switching processes has few overhead.

While the approach allows to fulfill very strict requirements, all knowledge has to be encoded into the application. This makes the solutions highly customized to the platform at hand. With increasing computing power and versatility of the employed hardware, the demand for flexibility of deployment and abstraction of hardware has also affected the real-time domain.

#### Protected Mode Addressing

Multipurpose operating systems running on stronger hardware introduce virtualization mechanisms. Application processes thus are typically isolated using hardware support for memory virtualization. Each process has its own virtual address space so another process' working set can not be accessed directly. Real-time tasks can be implemented using protected mode processes. Since processes may compete for access to resources, the management and locking of threads has to be kept in mind when running real-time tasks.

#### 2.1.3. Resource Management

Not all resources can be shared. When a resource is exclusive, synchronization and locking mechanisms have to be used. Since these mechanisms in combination with unknown applications can lead to deadlocks, hard real-time systems rely on offline analysis of the involved system parts.

#### Locking

Depending on the type of computing hardware and resource to lock, different locking mechanisms have proven useful.

For short interval locking in uniprocessor systems, the code can temporarily disable interrupts. In this way, the code is uninterruptible and thus guarantueed to have exclusive resource access. Due to interrupt processing latencies, in- and output operations involving peripheral hardware can be disturbed.

This can be tackled by using spinlocking in multi core or multi processor environments. Spinlocks perform active polling and testing of resource availability. Like disabling

Figure 2.2.: Resource Processing in Tasks, Prone to Deadlocking

interrupts, it should also be used only in short time frames, because polling introduces unnecessary CPU load.

If a lock has to be held for a long time frame, complex mechanisms like Mutexes or Semaphores can help improve overall system performance. If a Mutex is held by a task and requested by another one, the requesting task is put into waiting state, marked as not runnable. Thus, it does not use CPU cycles to wait for a resource. When the Mutex is released by the first task, the second task gets into the runnable state again. The latency for dispatching the tasks and assigning the resource is higher than using spin locks.

The concept of Semaphores extends the Mutex paradigm by introducing a counter. The counter specifies the number of tasks to wake up. Typically, a producer pushes items into a queue, raises the semaphore to the queue depth, and thus releases up to as many tasks as there are work items.

#### **Resource Allocation Analysis**

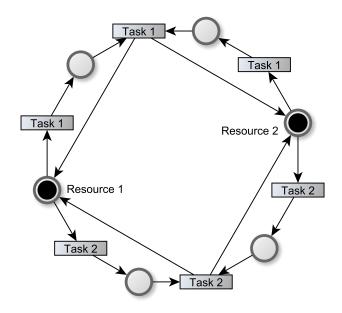

The interplay of resource allocation and their timing can be formally analyzed. A resource allocation graph is a directed graph over resources and tasks, associating locked resources with tasks and tasks with requested resources. If the allocation graph contains a cycle, deadlocks are possible and would need to be worked around by using additional locking mechanisms. Figure 2.2 depicts an example of a petri net of two tasks competing for two resources which is prone to deadlocking.

The resource allocation and processing behavior can be analyzed using (timed) petri nets, or (timed) automata. These formal models provide timing information as well as the static information present in the allocation graph. Both timed models can be checked and proven for correctness. Correctness in this case is reachability of end states without deadlocks, or exclusion of race conditions.

Measuring and affecting dynamic properties of computing systems is subsumed by the term of Quality of Service (QoS).

#### 2.1.4. Quality of Service (QoS)

QoS manages adaptive performance guarantees to applications. This is done by monitoring and observing performance figures during run time. Because applications are encapsulated by operating system processes, establishing QoS is tightly related to process scheduling and the interaction in between hardware components.

The performance guarantees comprise the measures defined according to the following topics.

#### Latency

QoS requirements on latencies for processing events are a common measure in hard real-time systems. This latency can, e.g., relate to handling an interrupt request of a device, establishing a Direct Memory Access (DMA) process, or starting a real-time task at a given time.

For guaranteeing tight latencies, it might be necessary to restrict the deepness of sleep states of hardware, due to wake-up delays. An additional measure for time division multiplex resources is making tasks and resource locking preemptible where possible. Minimizing non-preemptible code paths can be done by deferring processing of large workloads.

Jitter is another QoS measure important for tasks to control physical processes. Jitter specifies the deviation of scheduling times of periodic tasks.

#### **Resource Constraints**

Additionally to latency, resources might be constrained by total budgets. This can be a total amount of a resource for the lifetime of an object, or a bandwidth, meaning constrained resource usage per time unit.

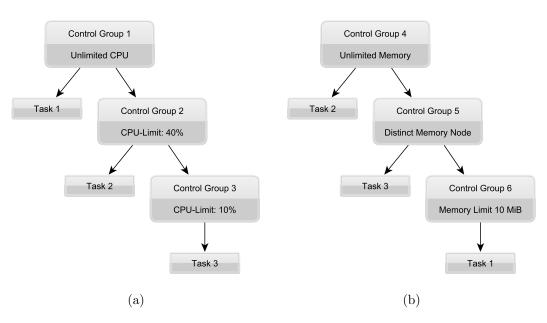

Figure 2.3 depicts two examples for hierarchical grouping and controlling of resources in the Linux operating system. The control groups can be annotated with constraints for resource allocation subsystems, like CPU accounting, or memory (Menage, 2006). Each control group can contain Linux tasks or yet more control groups.

In Subfigure 2.3a, three tasks are partitioned into control groups for CPU accounting. The root group features unrestricted resource usage for Task 1. Control group 2 restricts Task 2 and Control Group 3 to a combined maximum CPU limit of 40 %, of which Task 3 can amount at most for 10 %.

In Subfigure 2.3b, the same tasks are structured into different control groups annotated with memory allocation constraints. The root group again is unconstrained, containing Task 2 and Control Group 5. Group 5 is limited to memory allocation at a specific node of memory, i.e. a specific piece of hardware. This applies both to Task 3 as well as Gontrol Group 6, which additionally limits the total memory usage of Task 1 to 10 MiB.

Figure 2.3.: Linux Control Group Hierarchies

#### Shaping

The implementation of QoS is typically done by a combination of mechanisms (Aurrecoechea et al., 1998). Resource usage can be affected by scheduling both computing tasks as well as in- and output. Using QoS aware scheduling leads to shaping of resource usage. This can be done by adjusting the schedule in a way which affects throughput. Scheduling of in- and output is necessary to synchronize applications in a distributed system.

Despite scheduling, the QoS can be affected by manipulating queuing mechanisms. This can be done by filtering of in- and output. Queues can also be influenced by adjusting maximum depths such as the window size in TCP.

Adapting resource usage and specifying QoS levels is done in the adaptivity layer of the operating system.

#### 2.1.5. Adaptivity Layer

One important abstraction for safety and security is the separation of applications. This is established by using hardware privileges and virtual memory.

The ARM Cortex platform features several operating modes, which can be classified as **privileged** and **user** (ARM Ltd., 2010). Most notably, the operating system and device I/O happens in privileged mode and the processes running on the operating systems are running in user mode. The OS has to provide arbitration for requests from applications. This is typically the task of checking for (security) rights, or mediating QoS requests.

In this thesis, the adaptivity layer allows implicit as well as explicit statements. These types of statements are explained in the following.

### **Explicit Adaptivity**

Explicit adaptivity can be an explicit state request for a resource. Including, but not limited to:

- Locking and sharing of resources, as well as scheduling of in- and output. Applications can exclusively access locked resources. This access can be used to explicitly control resources from within an application context.

- Control of resources may be used to explicitly switch power states of hardware. An example would be to have an application execute a user request to shut down a device.

To do this kind of explicit configuration, the virtual device node representing a specific piece of hardware in the operating system, has to be opened and configured. The application doing this has to be equipped with appropriate rights and typically claims exclusive access to the resource. Thus, the management of the hardware shifts from the operating system to the application.

• Despite configuring peripherals, the applications may explicitly change operating system policies such as scheduling. This way, applications can configure mechanisms which exhibit implicit adaptivity. An example would be to tune QoS parameters which later-on get applied implicitly by the operating system.

Resorting to explicit adaptivity makes the configuration part of the application. If this configuration is spread over all applications, emergent system properties may be difficult to maintain and to verify. This is especially true if the partitioning of software components are being changed.

During the task of partitioning, the configuration of such applications would need to be adapted. This may be costly or even impossible.

Mixing different software units brings up emergent behavior as a combination of requests.

For the verification of correctness, either the exact behavior has to be specified, or, implicit approaches can be chosen.

#### Implicit Adaptivity

Implicit adaptivity is based on a rule set, translating in- and output of applications into actions, meaning for every state the adaptivity layer is in, an exact and explicit new state is known for each observed signal. That way, no arbitration time is needed and the superposition of requests can be analyzed offline.

Examples for implicit adaptivity may be:

- Enforcement of system correctness, like closing an application implicitly closes all its open files. This is related to the topics of safety and security.

- The routing of network packets in the operating system. An application typically just specifies an end-point and utilizes operating system services to handle the communication. Depending on the routing table, the operating system then implicitly handles address resolution and execution of the request.

• The execution of requests may be influenced by filtering rules and actions, such as used by the netfilter and iptables subsystems in Linux.

Resorting to implicit adaptivity implies equipping the operating system with the knowledge necessary to adapt to and execute the applications. This way, applications can be recombined, without changing or adjusting explicit requests.

#### 2.1.6. Application Program Interface

The application program interface provides all means to make software interoperable among different hardware platforms. Due to the abstraction and translation of requests, the applications typically do not work directly on I/O hardware but use handles or tokens which represent a request.

Using the interface, applications can communicate with one another and the outside world. All these actions are governed by the implicit adaptivity features. Because of this governance, the interfaces provide a feedback mechanism, indicating the state of requests.

# 2.2. Real-Time Operating Systems

Real-time operating systems are typically lean and specialized to the task at hand, especially when running hard real-time tasks.

#### 2.2.1. Hard Real-Time Tasks

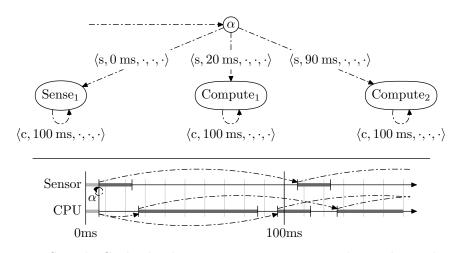

Hard real-time tasks have strict scheduling requirements, typically specifying periodic execution relative to fixed time offsets. Figure 2.4 depicts an exemplary schedule with offset o(j) and period p(j).

$$0 \quad o(j) \quad o(j) + 1 \cdot p(j) \quad o(j) + 2 \cdot p(j) \quad o(j) + 3 \cdot p(j)$$

Figure 2.4.: Fixed Cycle Scheduling of Hard Real-Time Tasks (Barthels et al., 2011)

If the worst-case execution times and the time allocation for different tasks overlap, tasks can be preempted by other tasks with higher priority. If more than one task with the same priority is runnable at the same time, e.g. the Earliest Deadline First (EDF) policy comes into place.

Hard real-time tasks typically are used to control physical processes. Since these processes have certain time evolution, the processing has to take place at exact time points.

These time points may be specified relatively to one another. An example of this is the specification of end-to-end deadlines. Additionally to specifying the exact time for running a task, one can specify bandwidths of time usable by a system task in soft real-time.

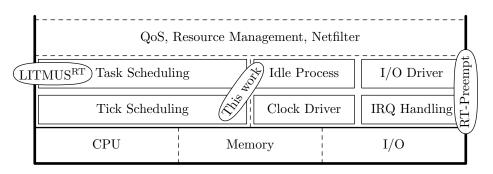

Figure 2.5.: Differentiation in LITMUS, RT-Preempt, and the Contribution of the Thesis at Hand

#### 2.2.2. Soft Real-Time Tasks

Soft real-time tasks typically do not have to be executed by time of their deadline. They only need to have a guaranteed total resource time per time unit, i.e., bandwidth. These tasks do not need to rely on latencies or accurate sleep calls. Examples for soft realtime tasks include computationally intensive processing of bulk data such as in image processing.

#### 2.2.3. Implementation Concepts

For establishing hard real-time timing properties, the I/O handling, locking, and interprocess communication is handled by small kernels which can e.g. be loaded as resource kernels into Linux. This approach is used by Xenomai (2013) and Bucher et al. (2013). Early work on resource kernels can be found, e.g. in Oikawa and Rajkumar (1998).

In recent years, the Linux kernel itself has seen strong development. More recent contributions, enrich the Linux kernel itself with features targeted at real-time processing. The kernel was, e.g., extended with an EDF–scheduling class by Faggioli et al. (2009) and by Calandrino et al. (2006) as part of the LITMUS<sup>RT</sup> environment. The approaches work on top of the task scheduling mechanism and provide a new scheduling discipline. Both approaches do not take energy awareness into account. Another train of work is to improve scheduling latencies using the RT-Preempt patch developed by Molnar (2013). The patch introduced nested and threaded interrupt handling, as well as preemptability of the kernel itself. These features were by now integrated into the kernel. The patch nowadays is a collection of changesets which mostly apply to device driver subsystems, making these preemptible were possible.

Figure 2.5 depicts the different points of application of recent related work in the Linux kernel. RT-Preempt is located on the right side, affecting interrupt handling and I/O drivers for minimizing system latencies. LITMUS<sup>RT</sup> is a framework for researching into task scheduling policies. For a comparison of LITMUS<sup>RT</sup> and RT-Preempt, please refer to Cerqueira and Brandenburg (2013).

The thesis at hand also touches task scheduling, but focuses more on energy awareness by adjusting system time slices and the system idle process.

Very small embedded systems typically do not run Linux as an operating system, since it is quite complex and may be expensive to run.

Figure 2.6.: Scheduling Classes as Being Implemented in Linux 3.0

Especially for embedded systems with limited resources, lean operating systems were developed, such as TinyOS (Levis et al., 2005). These lean operating systems handle only the smallest part of the system with leveraged privileges (kernel mode). This approach is most often referred to as Microkernel.

Despite scheduling and I/O, all other aspects of operating systems is handled in user mode. This processing mode is tightly coupled to threading and processing abstractions. These operating systems improve on timing guarantees in event handling on very small devices. Tasks are being higher prioritized as the operating system itself. Due to the constant increase in computing performance of the hardware, this thesis concentrates on Linux as a platform, which has seen increasing adoption in the field.

# 2.3. Process Scheduling

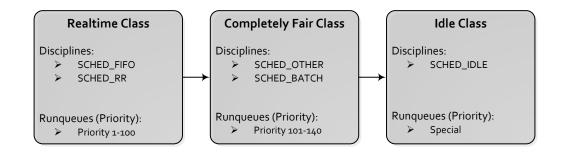

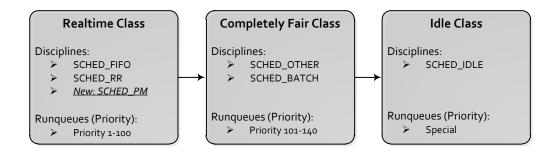

The system scheduling in modern operating systems has a profound number of aspects. Figure 2.6 depicts the scheduling classes used in the Linux kernel, as they supersede each other in priority.

Operating systems provide means of synchronization. One can synchronize to external events (interrupts), or tasks can synchronize themselves using local mechanisms and using the system scheduler.

Processes can be in waiting state. When in this state, they are not being scheduled to use the CPU. A process can be woken up by any event at any point in time. The overall system behavior then strongly depends on the current scheduling paradigm.

#### 2.3.1. Preemption

There are different forms of preemption. Preemption may be disabled, which in its strict sense also includes disabling interrupts. Preemption may be induced by timer interrupts, or also in general by locking mechanisms, which can change a task's state.

In Linux, e.g., tasks are in general not preemptible while executing code in kernel space. The kernel can be explicitly configured to allow this. Still, preemption cannot occur, when the task holds specific locks or has interrupts disabled. There are patches

to Linux, like RT-Preempt (Molnar, 2013), which ensures preemptability of tasks in almost all cases.

#### 2.3.2. Queuing

In Linux, each priority of each scheduling class has its own queue of tasks. Runnable tasks are removed from the queues in the order of their priority and are reinserted upon yielding the processor depending on the queuing discipline.

#### First-In First-Out (FIFO)

The FIFO discipline is the simplest discipline, which would typically be applied to hard real-time tasks. FIFO tasks are executed in the order in which they arrive. They are not being preempted by tasks of identical priority. Instead, they can run until yielding the CPU to the next task in the queue.

#### Round-Robin (RR)

Using the RR discipline, all tasks in each queue are multiplexed in a time division manner. In this way, even when all tasks are runnable all the time and there are fewer CPUs than tasks, all tasks with the same priority still get a share of CPU time.

#### Completely Fair Queuing (CFQ)

The average number of runnable tasks over time per CPU is defined as the CPU load. This load equals the depth of the queue of runnable tasks.

CFQ extends the notion of load to a task wise tracking. CFQ uses the exact measure of nano seconds each task has run since its creation. It aims to exactly even out the amount of runtime per task.

As in RR, this is established by using a time division manner.

#### 2.3.3. Time Slices

The time allocated to a runnable task is sliced, meaning tasks are interrupted regularly. Upon this interruption, the computing times of the processes get accounted and the tasks are scheduled. This scheduling is done according to the aforementioned policies. In Linux, the interrupt is called the system tick, marking the end of the current time slice and the start of the next. Fedorova et al. (2007) have investigated into the effect of choosing time slices in order to do load balancing among threads with equal priority on heterogeneous multi-core systems. In contrast, this thesis focuses on power management and scheduling of tasks with different priorities on lightly loaded distributed systems.

When a task of higher priority is runnable, all tasks of lower priority have to wait. Upon equal tasks with equal priority, sophisticated schemes were developed to allow for a fair distribution of computing time. Finally, in the idle class, system dependent idle code is executed, establishing partial system degradation and managing system wake up.

(c) Disabled Tick During Task and Idle (NO\_HZ Task)

Figure 2.7.: Comparison of current Linux tick scheduling. Gray intervals indicate busy times on the computing hardware. In NO\_HZ mode, the regular ticks are disabled by the idle task.

Unfortunately, due to this degradation and wake up, time is lost. This can be compensated by a novel approach to tick scheduling which is being elaborated in Chapters 3 and 5.

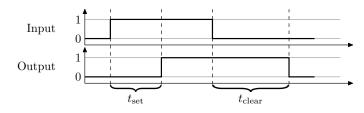

# 2.4. Timing Abstractions

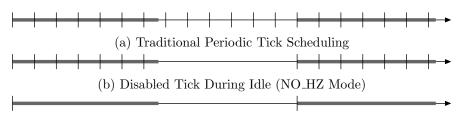

The system tick denotes the event upon indicating the end and start time of a system time slice. Traditional system tick or time slicing was provided by periodic clock sources. They were programmed to provide an interrupt signal at strictly cyclical intervals. Figure 2.7a depicts such a traditional tick period. In this case, ticks occur both when tasks are running (gray intervals), and when they are not running.

Over the traditional approach, two improvements were developed and implemented for the Linux kernel.

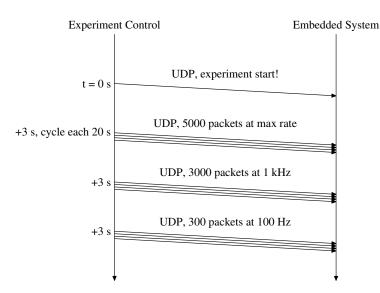

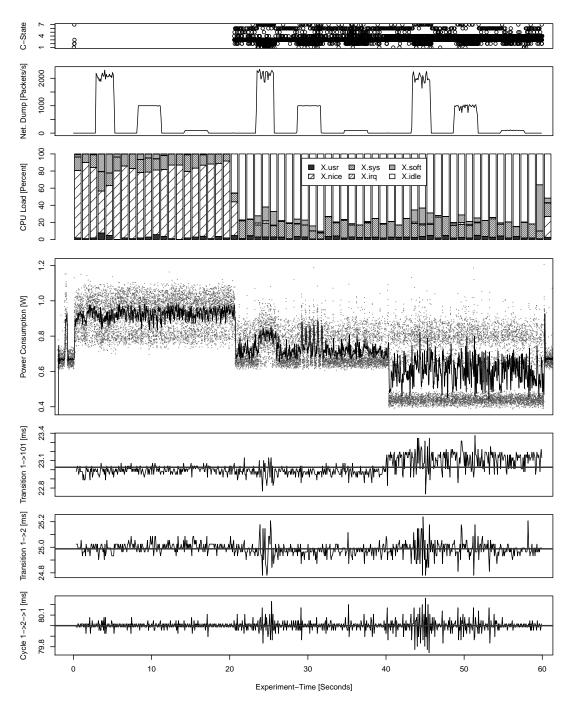

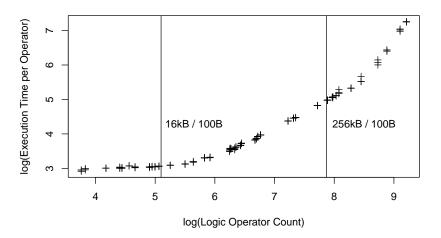

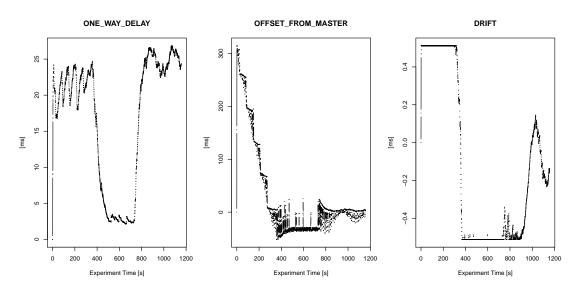

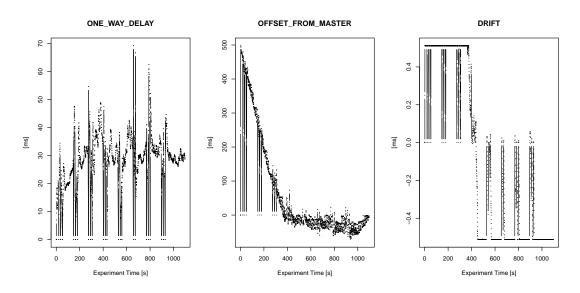

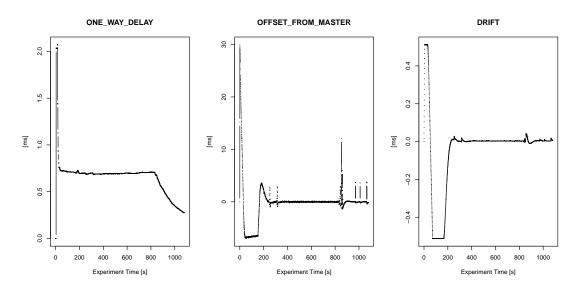

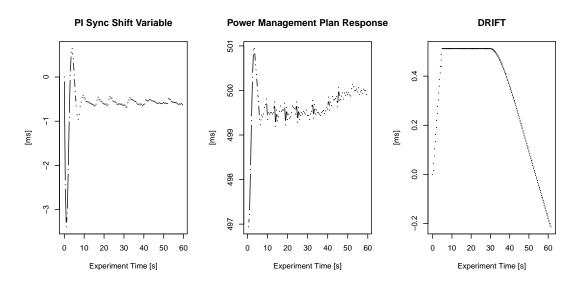

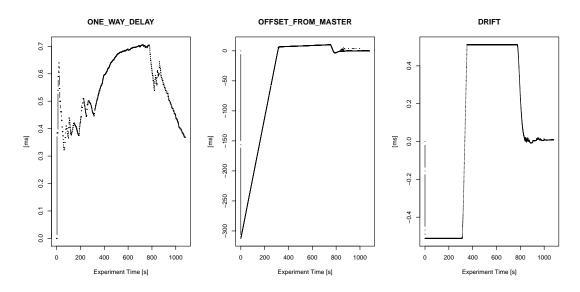

The first is called NO\_HZ and is illustrated in Figure 2.7b. It allows the system to reprogram the clock-device if possible to skip the periodic wake-up caused by ticks which are not needed for task slicing.