# TECHNISCHE UNIVERSITÄT MÜNCHEN

# Lehrstuhl für Integrierte Systeme

# FAST AND ACCURATE PERFORMANCE SIMULATION OF OUT-OF-ORDER PROCESSING CORES IN EMBEDDED SYSTEMS

# Roman Plyaskin

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

# **Doktor-Ingenieurs (Dr.-Ing.)**

genehmigten Dissertation.

# Vorsitzender:

Univ.-Prof. Dr.-Ing. Ulf Schlichtmann

# Prüfer der Dissertation:

- 1. Univ.-Prof. Dr. sc. techn. Andreas Herkersdorf

- 2. Univ.-Prof. Dr. rer. nat. Wolfgang Rosenstiel, Eberhard Karls Universität Tübingen

Die Dissertation wurde am 30.10.2013 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 23.06.2014 angenommen.

Recent embedded systems employ multiple processing cores on a single chip. Such multiprocessor system-on-chip (MPSoC) can incorporate heterogeneous processing cores with diverse internal complexity in order to offer an optimized solution in terms of performance, power consumption and dependability. Considering the growing MPSoC complexity, system architects require *fast* and *accurate* performance simulation of out-of-order processing cores to enable design space exploration (DSE) of MPSoC in reasonable time. Interpretive cycle-accurate instruction set simulators (ISS) employ detailed models of the core microarchitecture. Therefore, their use in iterative system-level DSE of MPSoC is limited because of low simulation speed. At the same time, recent approaches for fast software performance simulation leveraging annotated source code are too abstract to consider the effects of out-of-order instruction execution.

This thesis addresses the gap between interpretive cycle-accurate ISS and abstract source-level simulation and presents a novel approach for software performance simulation considering out-of-order execution. The proposed approach enables fast and accurate reproduction of the processor's out-of-order behavior and accelerates DSE at the system level. Furthermore, the thesis presents a SystemC-based simulation tool for performance evaluation of multicore architectures. The tool additionally supports trace-driven simulation of target applications and incorporates a high-level scheduler for flexible evaluation of SW partitioning in MPSoC platforms.

\_\_\_\_\_

Moderne eingebettete Systeme setzen Chips mit mehreren Prozessorkernen ein. Solche Multiprozessor Systeme-on-Chip (MPSoC) können heterogene Prozessorkerne mit diverser interner Komplexität enthalten und somit eine optimierte Lösung im Bezug auf Performanz, Leistungsverbrauch und Zuverlässigkeit bieten. Wegen der steigenden Komplexität der MPSoC benötigen Systemarchitekten eine schnelle und genaue Performanzsimulation der Out-of-Order-Prozessorkerne, um eine Entwurfsraumexploration der MPSoC in annehmbaren Zeiten zu ermöglichen. Interpretierende, zyklenakkurate Instruktionssatz-Simulatoren (ISS) enthalten detaillierte Modelle der Mikroarchitektur des Prozessorkerns und können nur kleine Simulationsgeschwindigkeiten erreichen. Aus diesem Grund ist die Nutzung dieser Werkzeuge für iterative Entwurfsraumexplorationen der MPSoC auf Systemebene begrenzt. Neueste Ansätze, die eine schnelle Software-Performanzsimulation basierend auf annotierten Quellcodes ermöglichen, sind zu abstrakt, um die Effekte der Out-of-Order-Ausführung der Instruktionen zu berücksichtigen.

Diese Dissertation stellt ein neues Verfahren für eine Software-Performanzsimulation mit Berücksichtigung der Out-of-Order-Ausführung vor und schließt somit die Lücke zwischen den interpretierenden, zyklenakkuraten ISS und einer abstrakten Simulation auf Quellcode-Ebene. Der vorgeschlagene Ansatz ermöglicht eine schnelle und genaue Wiedergabe des Verhaltens der Out-of-Order-Prozessoren und beschleunigt Entwurfsraumexplorationen auf Systemebene. Außerdem stellt diese Dissertation ein SystemC-basiertes Werkzeug für Performanzabschätzungen der Mehrkern-Architekturen vor. Das Werkzeug ermöglicht zusätzlich eine Trace-getriebene Simulation der Zielanwendungen und enthält einen Scheduler für flexible Evaluierungen der Software-Partitionierungen in MPSoC-Plattformen auf hoher Ebene.

# ACKNOWLEDGMENTS

I would like to sincerely thank Prof. Andreas Herkersdorf for supervising this thesis and providing me with the opportunity to work and do the research at the institute. I particularly appreciate our discussions on this project, which kept me motivated and helped me to gain a more comprehensive view on the research problems. I also would like to express my gratitude to Prof. Wolfgang Rosenstiel for co-examining this work and his comments which helped me to improve the dissertation.

In addition, I would like to thank Prof. Walter Stechele and Dr. Thomas Wild for their help and valuable comments on this work. Special thanks go to all present and past colleagues at the institute for integrated systems for creating a nice working atmosphere. Finally, this work wouldn't be possible without loving support of my family and my fiancée Michaela who always stood by my side during these years.

# CONTENTS

| 1 | INT | RODUC          | CTION                                           | 1   |

|---|-----|----------------|-------------------------------------------------|-----|

|   | 1.1 | Scope          | of the thesis                                   | 1   |

|   | 1.2 | Proble         | em statement                                    | 2   |

|   | 1.3 | Contr          | ibutions                                        | 3   |

|   | 1.4 | Outlin         | ne                                              | 4   |

|   |     |                |                                                 |     |

| 2 | PRI | OR ART         |                                                 | 5   |

|   | 2.1 | Instru         | action Set Simulation                           | 5   |

|   |     | 2.1.1          | Interpretive ISS                                | 5   |

|   |     | 2.1.2          | Compiled ISS                                    | 6   |

|   |     | 2.1.3          | Sampled simulation                              | 10  |

|   |     | 2.1.4          | ISS-based simulation of multicore architectures | 12  |

|   | 2.2 | Simul          | ation based on target code                      | 14  |

|   |     | 2.2.1          | Source-level simulation                         | 14  |

|   |     | 2.2.2          | Simulation based on intermediate representation | 16  |

|   |     | 2.2.3          | Instruction-level simulation                    | 18  |

|   | 2.3 | Trace-         | driven simulation                               | 20  |

|   | 2.4 | High-          | level OS modeling                               | 23  |

|   | 2.5 | Sumn           | nary                                            | 28  |

|   |     |                |                                                 |     |

| 3 |     |                | JND OF COMPILED SW SIMULATION AT BINARY         |     |

|   | LEV |                | . 11 1 .                                        | 31  |

|   | 3.1 |                | ional behavior                                  | 32  |

|   |     | 3.1.1          | Binary-to-C translation                         | 32  |

|   |     | 3.1.2          | Organization of translated code                 | 33  |

|   |     | 3.1.3          | Modeling of target memory                       | 34  |

|   | 3.2 |                | g behavior                                      | 36  |

|   |     | 3.2.1          | Annotation of timing information                | 36  |

|   |     | 3.2.2          | Modeling of caches                              | 37  |

| 4 | CON | мритер         | SW SIMULATION CONSIDERING OUT-OF-ORDER          |     |

| 4 |     |                | ION EXECUTION                                   | 41  |

|   | 4.1 |                | n-level effects of out-of-order execution       | 41  |

|   | 4.1 | 4.1.1          | Classification of out-of-order effects          | 41  |

|   |     | 4.1.2          | Limitations of conventional host-compiled sim-  | 41  |

|   |     | 4.1.2          | ulations                                        | 1.1 |

|   | 1.2 | Doriv          | ation of basic block timing                     | 44  |

|   | 4.2 |                | ISS enhancements                                | 47  |

|   |     | 4.2.1          | Identification of basic block boundaries        | 47  |

|   | 4.2 | 4.2.2<br>Conto | ext dependency of basic block timing            | 50  |

|   | 4.3 |                |                                                 | 51  |

|   |     | 4.3.1          | Concept                                         | 51  |

|   |     | 1.3.2          | Derivation of confext-dependent filming         | 53  |

|    |       | 4.3.3  | Context-aware host-compiled simulation       | 56         |

|----|-------|--------|----------------------------------------------|------------|

|    | 4.4   | Reord  | lering of memory accesses                    | 57         |

|    |       | 4.4.1  | Classification of basic blocks               | 57         |

|    |       | 4.4.2  | Simulation of memory reordering              | 59         |

|    | 4.5   | Non-l  | plocking behavior of data cache              | 61         |

|    |       | 4.5.1  | Modeling of non-blocking behavior            | 61         |

|    |       | 4.5.2  | Dependency analysis of memory instructions . | 68         |

|    | 4.6   | Optin  | nizations                                    | 69         |

|    |       | 4.6.1  | Optimization of binary-to-C translation      | 71         |

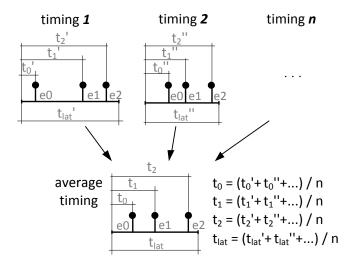

|    |       | 4.6.2  | Averaging of basic block timings             | <b>7</b> 3 |

|    |       | 4.6.3  | Static reordering of memory accesses         | <b>7</b> 4 |

| 5  | SYS   | TEM-L  | EVEL SIMULATION OF MULTICORE ARCHITEC-       |            |

|    | TUR   | ES     |                                              | 85         |

|    | 5.1   | Simul  | ation methods                                | 86         |

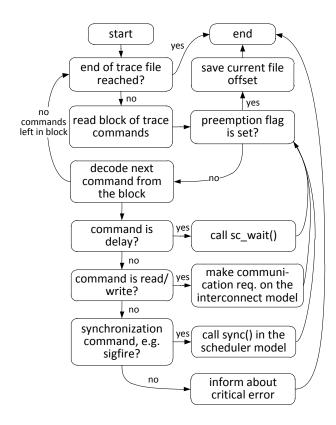

|    |       | 5.1.1  | Trace-Driven Simulation                      | 86         |

|    |       | 5.1.2  | Binary-level simulation                      | 91         |

|    |       | 5.1.3  | Summary                                      | 93         |

|    | 5.2   | High-  | level scheduler model                        | 96         |

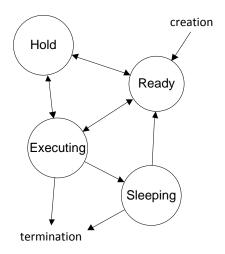

|    |       | 5.2.1  | Task model                                   | 97         |

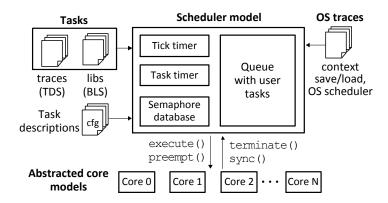

|    |       | 5.2.2  | Scheduler model                              | 99         |

|    |       | 5.2.3  | Implementation details                       | 109        |

|    | 5.3   | System | mC models of hardware components             | 115        |

|    |       | 5.3.1  | Out-of-order core                            | 115        |

|    |       | 5.3.2  | Communication infrastructure and memory      | 123        |

| 6  | EXP   | ERIME  | NTAL RESULTS                                 | 129        |

|    | 6.1   | Conte  | ext-aware host-compiled SW simulation        | 129        |

|    |       | 6.1.1  | Experimental setup                           | 129        |

|    |       | 6.1.2  | Optimization of binary-to-C translation      | 132        |

|    |       | 6.1.3  | Context-aware compiled simulation            | 135        |

|    |       | 6.1.4  | Averaging of basic block timing              | 143        |

|    |       | 6.1.5  | Consideration of a data cache                | 147        |

|    | 6.2   | Syster | m-level simulation based on SystemC          | 153        |

|    |       | 6.2.1  | Experimental setup                           | 153        |

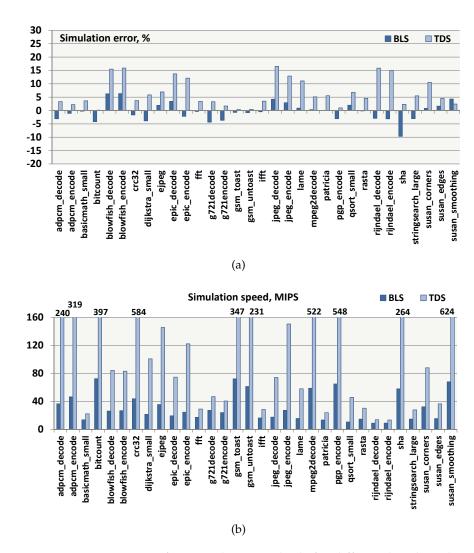

|    |       | 6.2.2  | Evaluation of BLS and TDS methods            | 155        |

|    | 6.3   | Multi  | core design space exploration: A use case    | 163        |

|    |       | 6.3.1  | Experimental setup                           | 163        |

|    |       | 6.3.2  | Results                                      | 166        |

| 7  | CON   |        | ONS AND FUTURE WORK                          | 171        |

|    | 7.1   |        | usions                                       | 171        |

|    | 7.2   | Outlo  | ok for future work                           | 175        |

| рτ | DI IO | CDADE  | IV                                           | 175        |

# LIST OF FIGURES

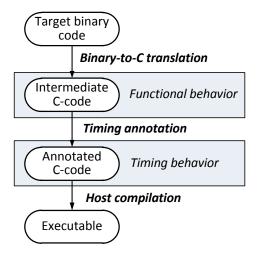

| Figure 3.1  | Workflow of binary-level SW compiled simu-     |

|-------------|------------------------------------------------|

|             | lation                                         |

| Figure 3.2  | Binary-to-C translation                        |

| Figure 3.3  | Timing annotation                              |

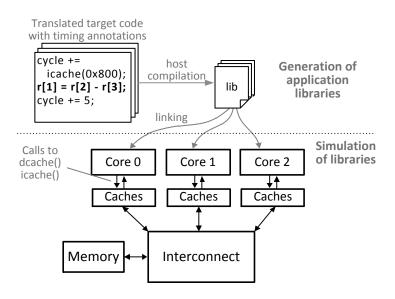

| Figure 3.4  | Calls to dynamic cache models                  |

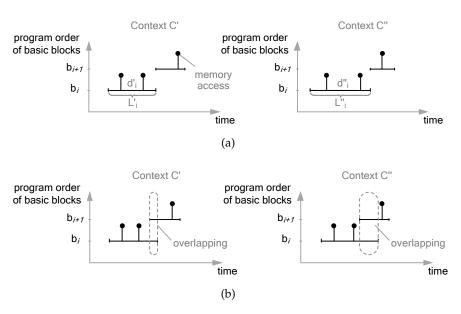

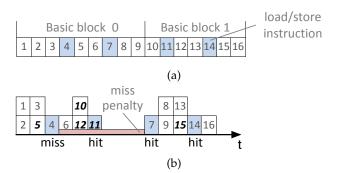

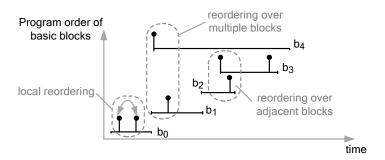

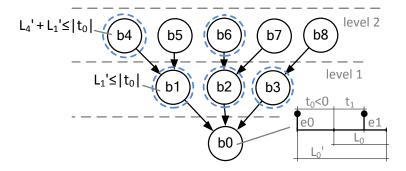

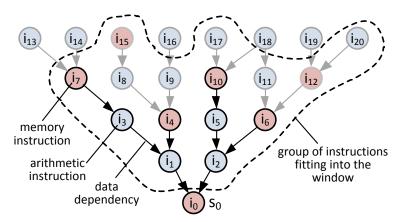

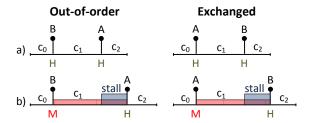

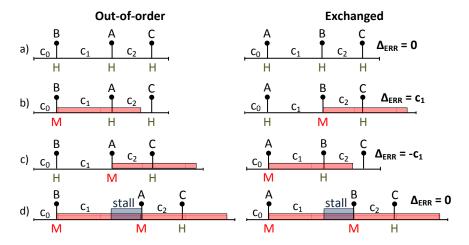

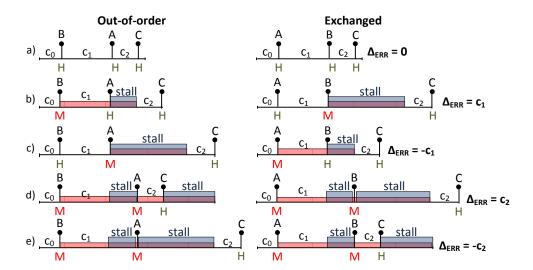

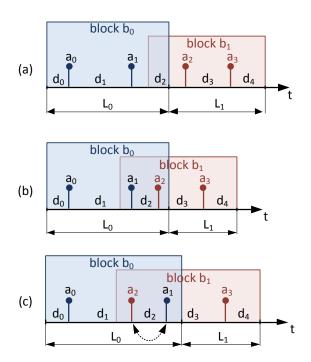

| Figure 4.1  | Context-dependent timing of basic blocks       |

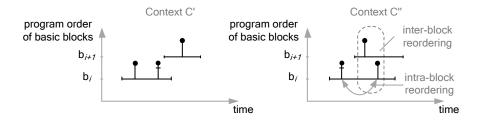

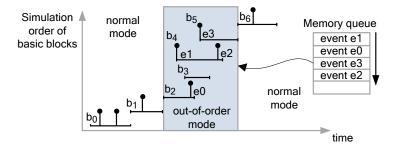

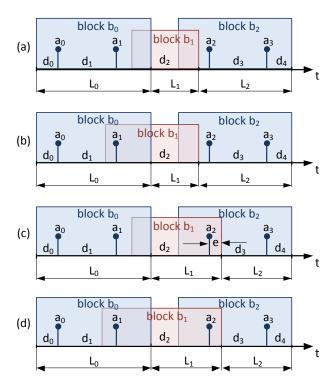

| Figure 4.2  | Reordering of memory accesses                  |

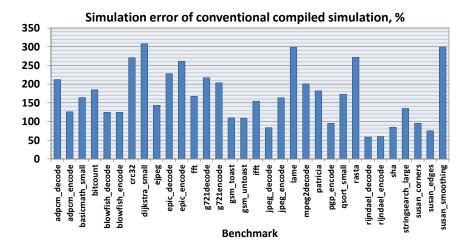

| Figure 4.3  | Error of conventional compiled simulation      |

| Figure 4.4  | Timing behavior during a data cache miss       |

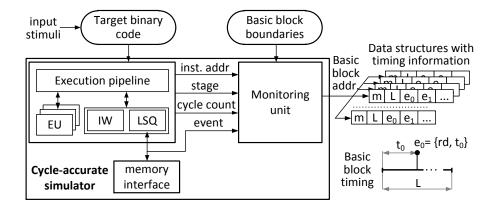

| Figure 4.5  | Derivation of basic block timing               |

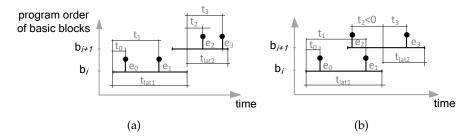

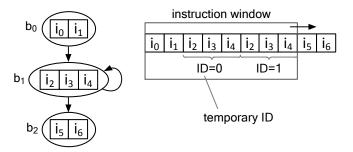

| Figure 4.6  | Consideration of overlapping of basic blocks . |

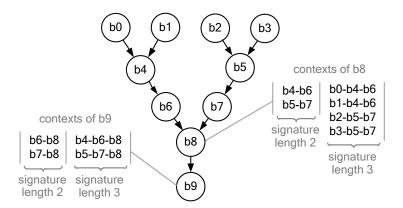

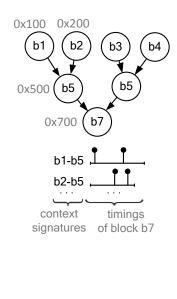

| Figure 4.7  | Contexts of basic blocks                       |

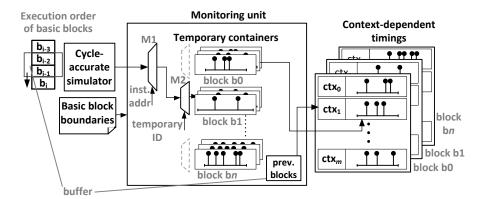

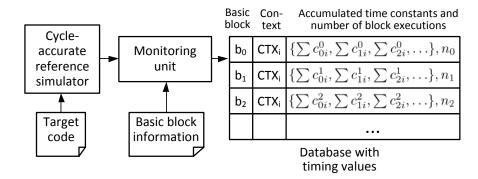

| Figure 4.8  | Context-aware measurement                      |

| Figure 4.9  | Differentiation of basic block instances       |

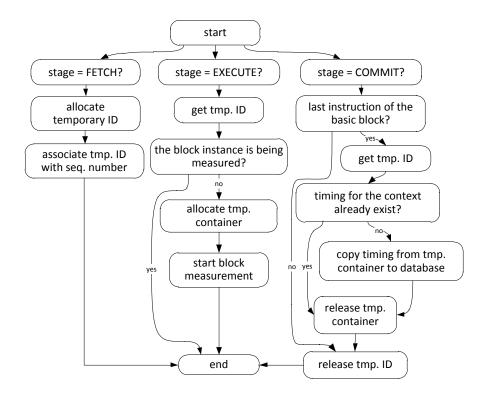

| Figure 4.10 | Algorithm for obtaining context-dependent tim- |

| _           | ing                                            |

| Figure 4.11 | Context-aware basic block function             |

| Figure 4.12 | Reordering of memory accesses                  |

| Figure 4.13 | Detection of possible memory reordering over   |

| 0 . 3       | multiple basic blocks                          |

| Figure 4.14 | Simulation of reordered memory accesses        |

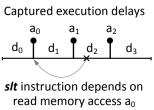

| Figure 4.15 | Example code with data dependency              |

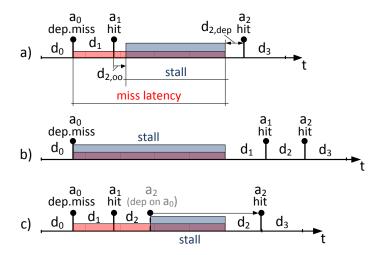

| Figure 4.16 | Hit under dependent miss                       |

| Figure 4.17 | Second miss under a dependent miss             |

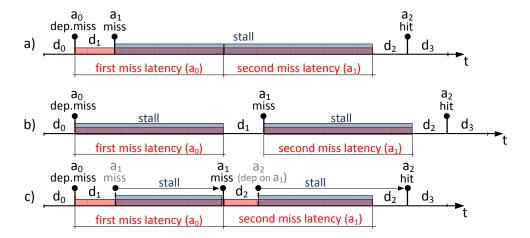

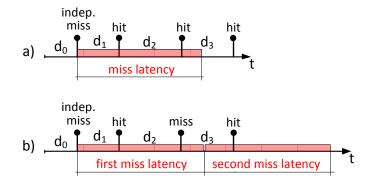

| Figure 4.18 | Simulation of independent miss                 |

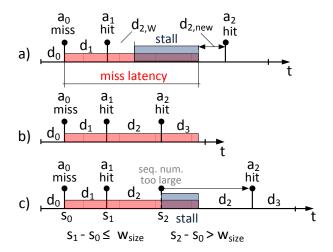

| Figure 4.19 | Consideration of instruction window            |

| Figure 4.20 | Dependency analysis                            |

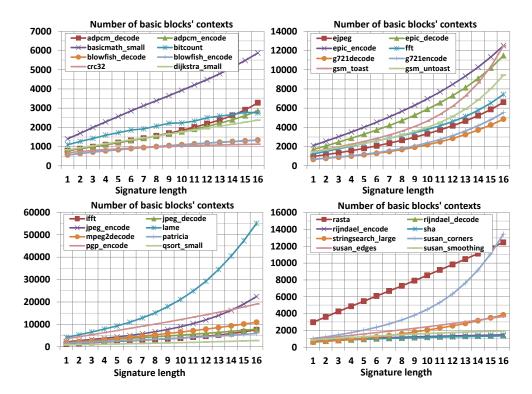

| Figure 4.21 | Total amount of basic block timings            |

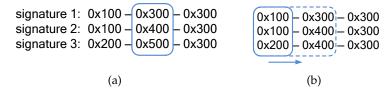

| Figure 4.22 | Optimization of context signatures             |

| Figure 4.23 | Averaging of block timings                     |

| Figure 4.24 | Simulation of exchanged accesses to the same   |

| 0           | cache line                                     |

| Figure 4.25 | Simulation of exchanged accesses to different  |

| 0 1 3       | cache lines with no dependency                 |

| Figure 4.26 | Simulation of exchanged accesses to different  |

| 0 4         | cache lines with dependency                    |

| Figure 4.27 | Static reordering of memory accesses           |

| Figure 4.28 | Types of basic block overlapping               |

| Figure 4.29 | Block overlapping without data cache accesses  |

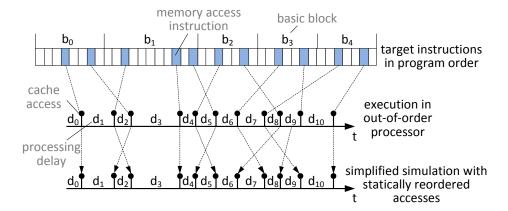

| Figure 4.30 | Measurement of basic block timings with stat-  |

| 0 4-50      | ically roordared accesses                      |

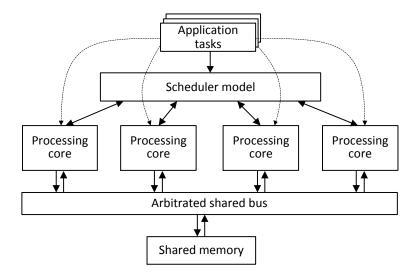

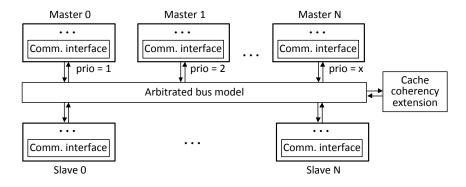

| Figure 5.1  | SystemC simulator                                | 85  |

|-------------|--------------------------------------------------|-----|

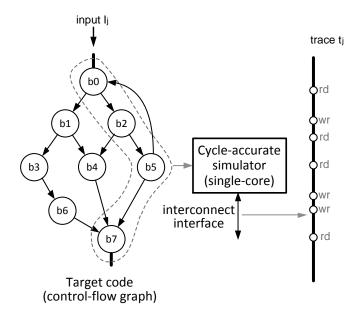

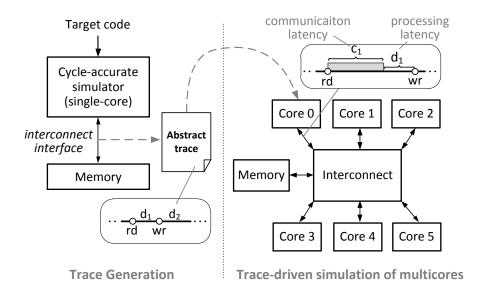

| Figure 5.2  | Generation of an abstract trace                  | 88  |

| Figure 5.3  | Trace-driven simulation of multicores            | 89  |

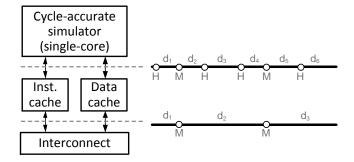

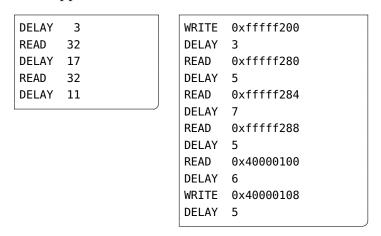

| Figure 5.4  | Different levels of trace abstraction            | 91  |

| Figure 5.5  | Different abstraction levels of traces           | 91  |

| Figure 5.6  | Binary-level compiled simulation of multicores   | 92  |

| Figure 5.7  | Comparison of TDS and BLS methods                | 95  |

| Figure 5.8  | State diagram of tasks                           | 98  |

| Figure 5.9  | Structure of the OS scheduler model              | 99  |

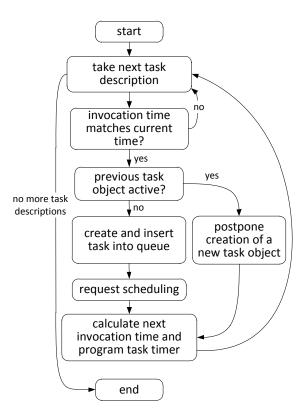

| Figure 5.10 | Algorithm for generation of instances of user    |     |

| _           | tasks                                            | 101 |

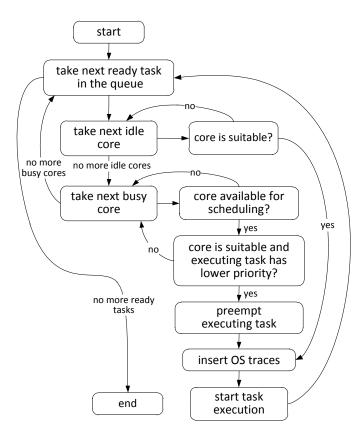

| Figure 5.11 | Algorithm for scheduling of user tasks           | 102 |

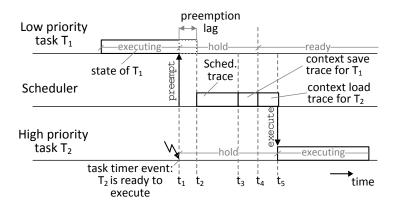

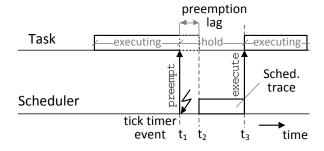

| Figure 5.12 | Preemption of user tasks                         | 103 |

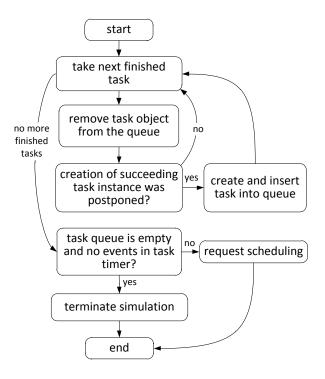

| Figure 5.13 | Termination of user tasks                        | 104 |

| Figure 5.14 | Simulation of OS ticks without task switching    | 104 |

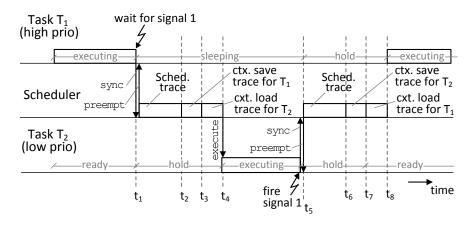

| Figure 5.15 | Synchronization of user tasks                    | 106 |

| Figure 5.16 |                                                  | 108 |

| Figure 5.17 | - ·                                              | 108 |

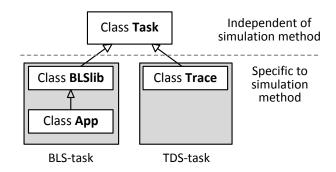

| Figure 5.18 | Class hierarchy of TDS- and BLS-tasks            | 110 |

| Figure 5.19 |                                                  | 111 |

| Figure 5.20 | Memory modeling in case of multiple target       |     |

| 0 0         | applications                                     | 113 |

| Figure 5.21 | Mapping of virtual and physical address spaces   | _   |

| Figure 5.22 |                                                  | 116 |

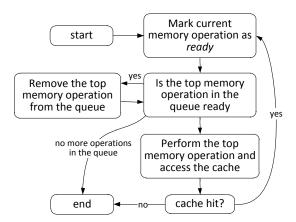

| Figure 5.23 | Queue in the non-blocking cache extension        | 117 |

| Figure 5.24 | Behavior of the non-blocking cache extension     | ,   |

| 0 0 1       | on an data access                                | 118 |

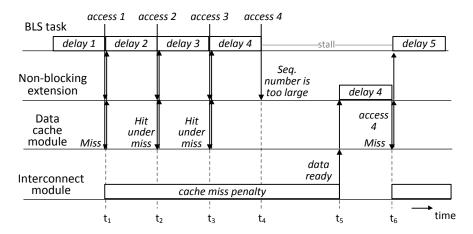

| Figure 5.25 | Behavior of the non-blocking cache extension     |     |

| 0 0         |                                                  | 119 |

| Figure 5.26 | Stalling due to the limited size of the instruc- |     |

| 0 0         |                                                  | 120 |

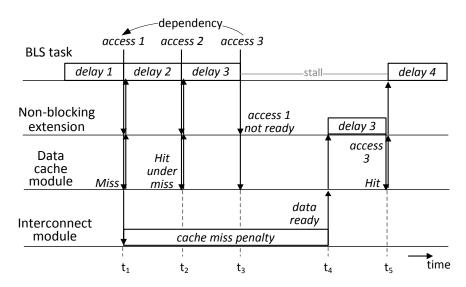

| Figure 5.27 | Stalling due to data dependency                  | 121 |

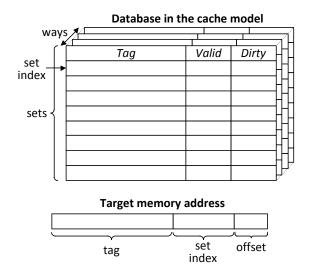

| Figure 5.28 | Database in the cache model                      | 122 |

| Figure 5.29 |                                                  | 123 |

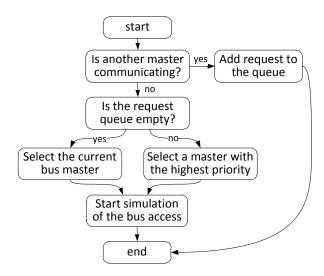

| Figure 5.30 | Bus arbitration process                          | 124 |

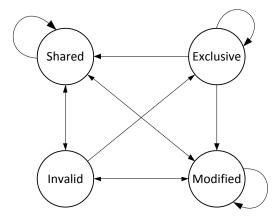

| Figure 5.31 | States in MESI protocol                          | 125 |

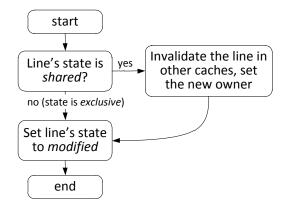

| Figure 5.32 |                                                  | 126 |

| Figure 5.33 | Operation in case of a write hit                 | 127 |

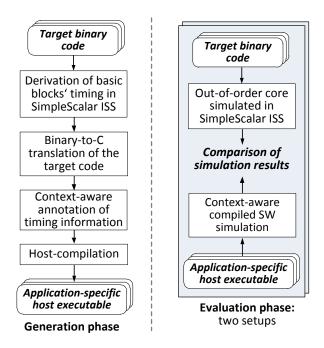

| Figure 6.1  | Workflow of experiments                          | 131 |

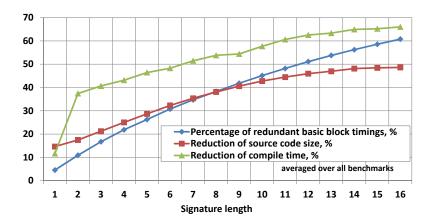

| Figure 6.2  | Optimization of binary-to-C translation          | 133 |

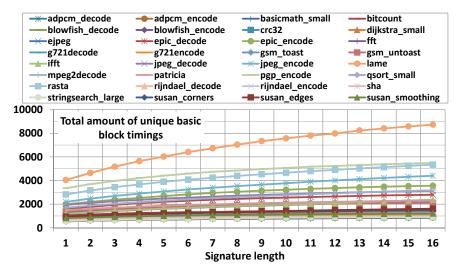

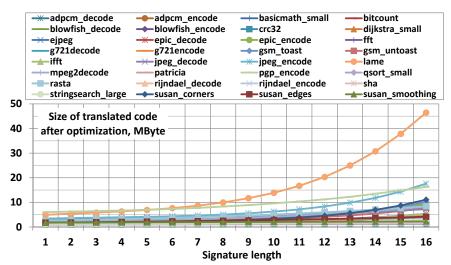

| Figure 6.3  | Amount of basic block contexts                   | 134 |

| Figure 6.4  |                                                  | 134 |

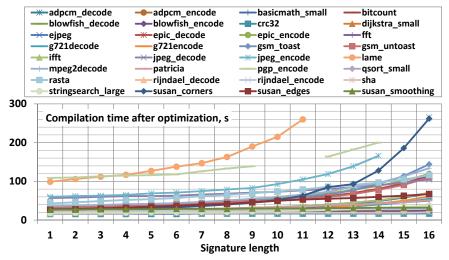

| Figure 6.5  | Compilation time                                 | 134 |

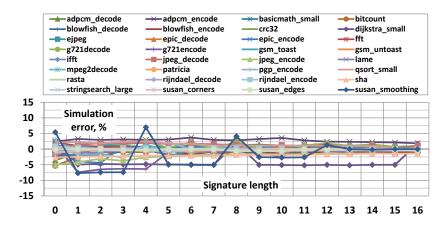

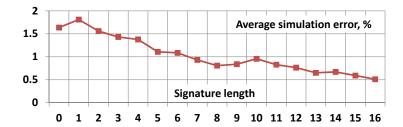

| Figure 6.6  | Timing error of context-aware simulation         | 136 |

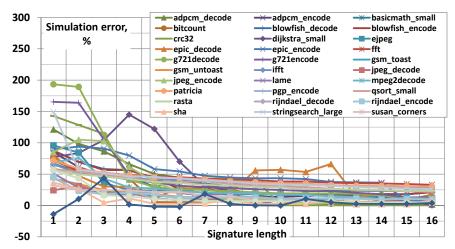

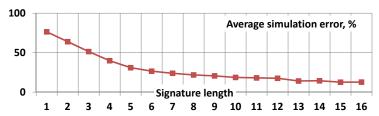

| Figure 6.7  | Average timing error                             | 136 |

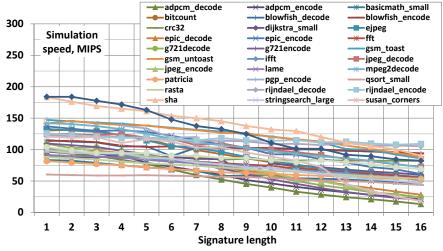

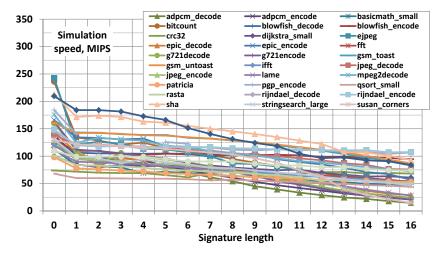

| Figure 6.8  | Speed of context-aware simulation                | 136 |

| 0           | 1                                                |     |

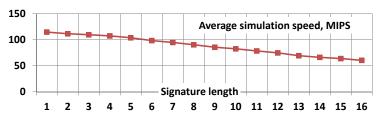

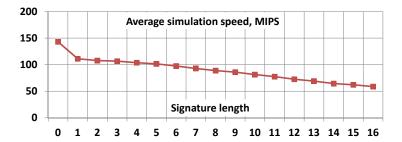

| Figure 6.9  | Average speed of context-aware simulation 13       | 6  |

|-------------|----------------------------------------------------|----|

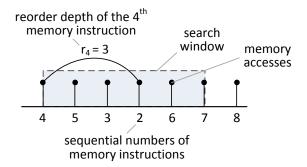

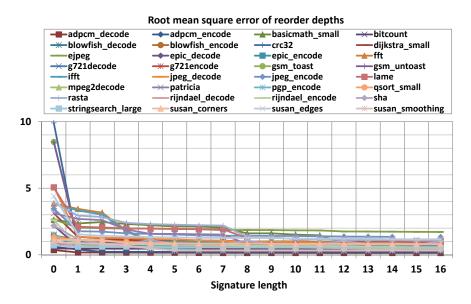

| Figure 6.10 | Reorder depth                                      | 8  |

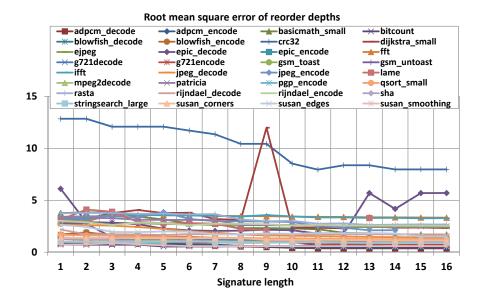

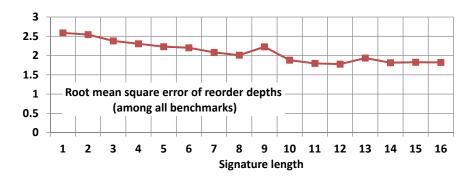

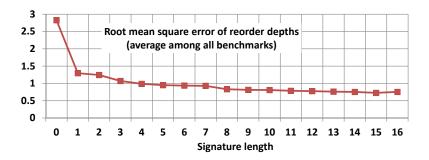

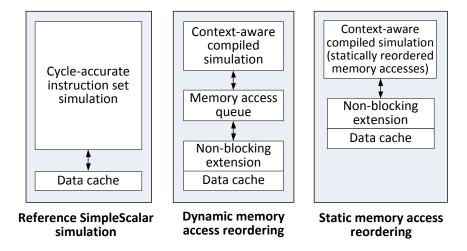

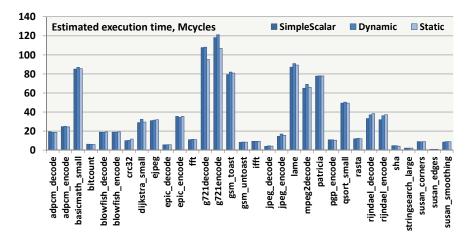

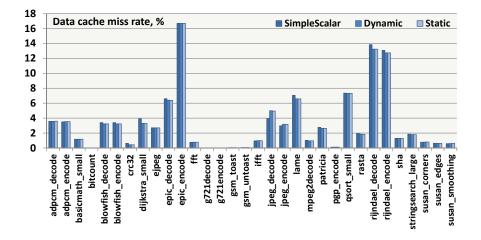

| Figure 6.11 | RMSE of reorder depth 14                           | O  |

| Figure 6.12 | Mean RMSE of reorder depths 14                     | O  |

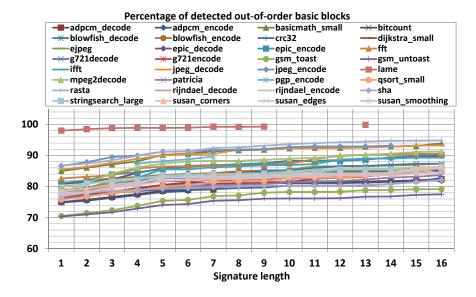

| Figure 6.13 | Percentage of out-of-order blocks 14               | .1 |

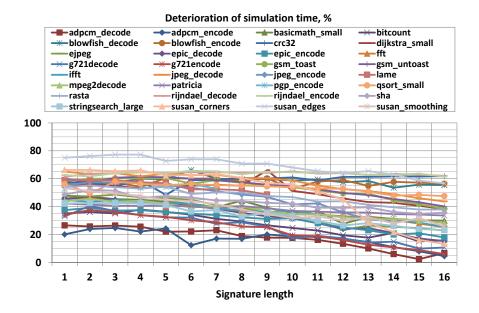

| Figure 6.14 | Deterioration of simulation time 14                | 2  |

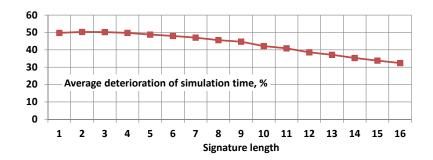

| Figure 6.15 | Mean deterioration of simulation time 14           | 2  |

| Figure 6.16 | Timing error of context-aware simulation with      |    |

|             | averaging                                          | 3  |

| Figure 6.17 | Mean timing error with averaging 14                | 4  |

| Figure 6.18 | Speed of context-aware compiled simulation         |    |

|             | with averaging                                     | 4  |

| Figure 6.19 | Mean speed of context-aware compiled simu-         |    |

|             | lation with averaging                              | 5  |

| Figure 6.20 | RMSE of reorder depths with averaging 14           | 6  |

| Figure 6.21 | Mean RMSE of reorder depths with averaging 14      | 6  |

| Figure 6.22 | Simulation scenarios with data cache 14            | 8  |

| Figure 6.23 | Accuracy of simulation with static memory re-      |    |

|             | ordering                                           | 9  |

| Figure 6.24 | Estimated miss rate of data cache 14               | 9  |

| Figure 6.25 | Simulation speed with static memory reordering 15  | O  |

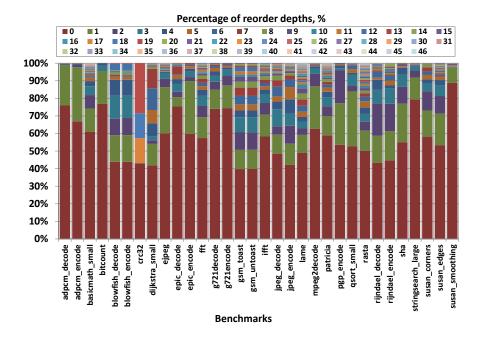

| Figure 6.26 | Percentage of reorder depths 15                    | 1  |

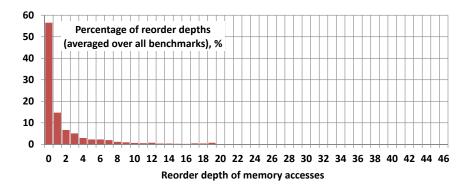

| Figure 6.27 | Average percentage of reorder depths 15            | 2  |

| Figure 6.28 | valuation of cache accesses                        | 2  |

| Figure 6.29 | Experimental setup for BLS and TDS 15              | 4  |

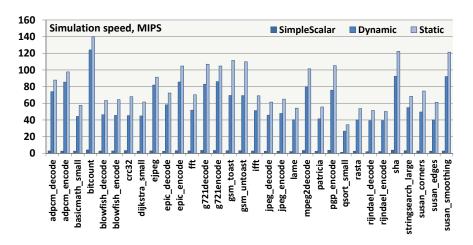

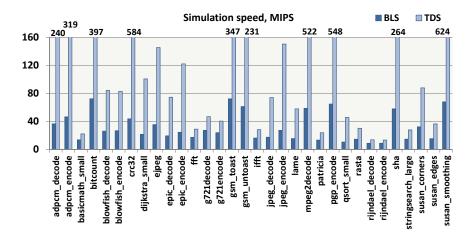

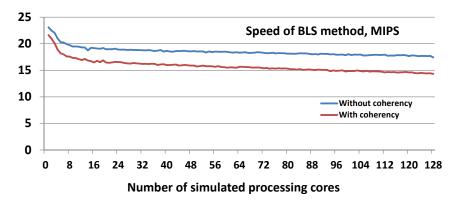

| Figure 6.30 | Speed of TDS and BLS simulation 15                 | 6  |

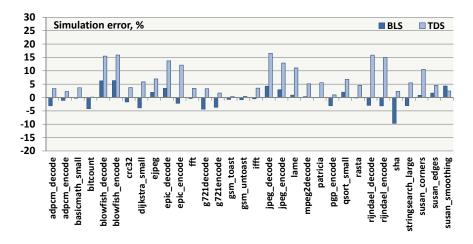

| Figure 6.31 | Simulation error of TDS and BLS 15                 | 7  |

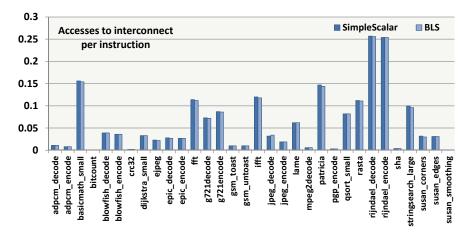

| Figure 6.32 | Rate of accesses to on-chip interconnect 15        | 7  |

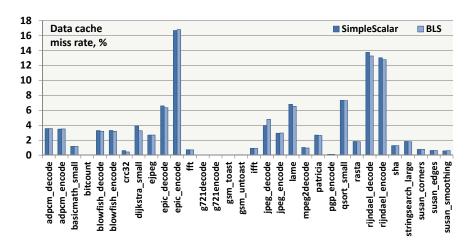

| Figure 6.33 | Accuracy of data cache simulation in BLS 15        |    |

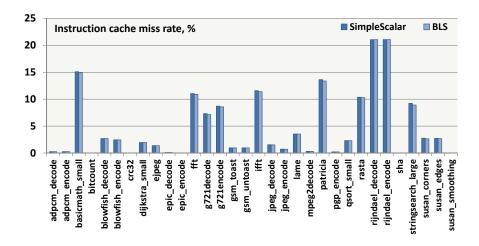

| Figure 6.34 | Accuracy of instruction cache simulation in BLS 15 | 9  |

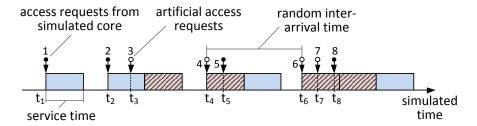

| Figure 6.35 | Simulation of random bus traffic 16                | O  |

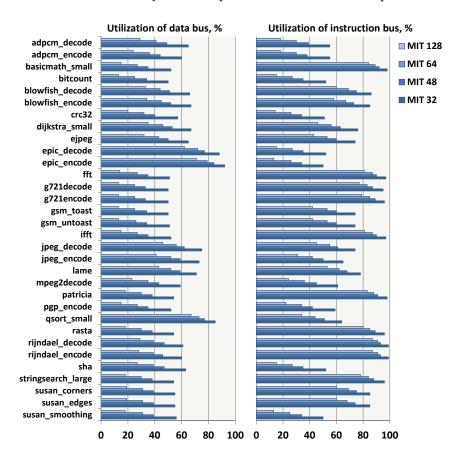

| Figure 6.36 | Utilization of data/instruction bus 16             | O  |

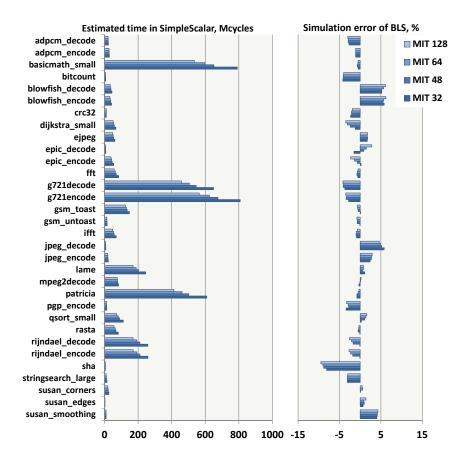

| Figure 6.37 | Estimated time and accuracy of BLS 16              | 2  |

| Figure 6.38 | Simulation speed of a multicore architecture . 16  | 3  |

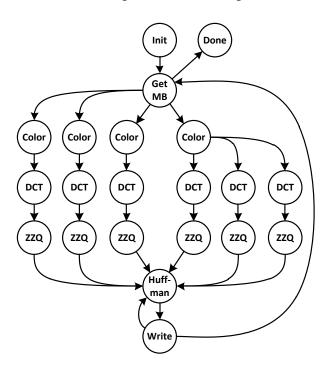

| Figure 6.39 | Task graph of JPEG encoding 16                     | 4  |

| Figure 6.40 | Pareto front                                       | 7  |

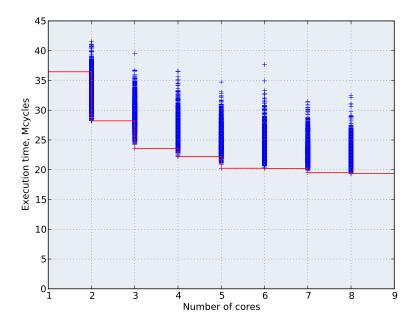

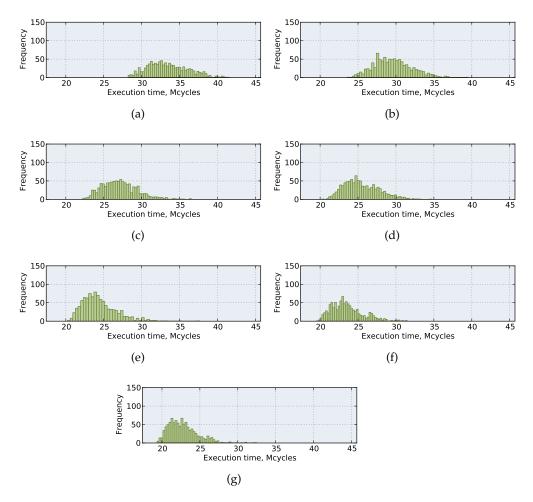

| Figure 6.41 | Distributions of execution time 16                 | 8  |

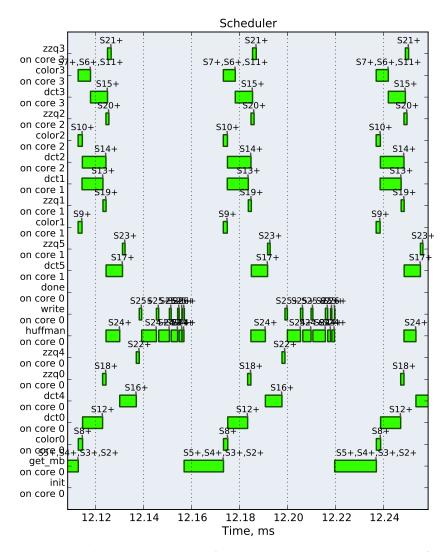

| Figure 6.42 | Scheduling diagram                                 | 9  |

| Figure 6.43 | Invalidations per bus master                       | 9  |

# LIST OF TABLES

| Table 2 | Content of the task queue                       | 107 |

|---------|-------------------------------------------------|-----|

| Table 3 | Configuration of the core simulated in the Sim- |     |

|         | pleScalar                                       | 130 |

| Table 4 | Configuration of a data cache employed in sim-  |     |

|         | ulations                                        | 147 |

| Table 5 | Evaluation results of the JPEG application      | 167 |

|         |                                                 |     |

# **ACRONYMS**

Arithmetic and Logic Unit ALU API Application Programmable Interface **BCET** Best-case Execution Time BLS Binary-Level Compiled Simulation Control-Flow Graph CFG Cycles per Instruction CPI **Dynamic Binary Translation** DBT DCT Discrete Cosine Transform DSE Design Space Exploration **EDF** Earliest Deadline First **Execution-Driven Simulation** EDS **Execution Unit** EU FIFO First In First Out GUI Graphical User Interface HDL Hardware Description Language Input/Output IO Instructions per Cycle **IPC** IR Intermediate Representation ISA Instruction Set Architecture **Instruction Set Simulator** ISS **Instruction Window** IW Load/Store Queue LSQ MESI Modified, Exclusive, Shared, Invalid MIT Mean Interarrival Time MPSoC Multiprocessor System-on-Chip

MSHR Miss Status Holding Register

# xvi acronyms

MSI Modified, Shared, Invalid

OS Operating System

RAW Read After Write

RISC Reduced Instruction Set Computer

RMSE Root Mean Square Error

RTOS Real-Time Operating System

SLS Source-Level Simulation

SMP Symmetric Multiprocessing

SoC System-on-Chip

TDS Trace-Driven Simulation

TLM Transaction-level Modeling

WAR Write after Read

WAW Write after Write

WCET Worst-case Execution Time

INTRODUCTION

#### 1.1 SCOPE OF THE THESIS

Recent embedded systems leverage chips with multiple processing cores to improve the performance of target applications and reduce power consumption. Such multiprocessor systems-on-chip (MPSoCs) can have a heterogeneous architecture and incorporate processing cores with diverse complexity to offer an optimized solution in terms of performance, power consumption and dependability. For example, a heterogeneous MPSoC may incorporate processing cores with a *simple* microarchitecture optimized in terms of chip area and power consumption. In addition, the MPSoC may contain processing cores with a *complex* microarchitecture optimized for performance. Complex cores may incorporate multiple execution units, support branch prediction and dynamic scheduling of instructions for faster execution of the software.

The heterogeneous MPSoC structure allows for more efficient distribution of software execution on the processing cores. For example, parallel software parts can be executed on multiple simple cores to efficiently exploit thread-level parallelism. In turn, sequential software parts, which are inevitable due to the limited parallelism in the target software, can be executed on fewer complex but faster cores to profit from instruction-level parallelism as much as possible. Advanced processing cores capable of out-of-order instruction execution have been recently emerged in embedded systems, e.g. Freescale e5500, ARM Cortex-R7 or Cortex-A15.

Furthermore, because of the increasing performance capabilities of MPSoCs, the complexity of target applications executed in embedded devices is steadily increasing. As as a result, design of MPSoCs involves many decisions that need to be made both on the software and hardware side. For example, a hardware designer may need to find a suitable hardware architecture with respect to allocation of processing elements and interconnect in order to meet the application requirements. Moreover, target applications can be composed of multiple communicating tasks. In this case, a software designer may need to explore various mappings of the tasks on the underlying hardware architecture, e.g. while trying to reduce the overall execution time of the target application. In this evaluation process, a key requirement is the flexibility during evaluation of SW partitioning. Different task mappings and scheduling strategies need to be studied at early stages, without the need of porting the applications to a specific im-

plementation of an operating system (OS). Consequently, the developers are faced with a large amount of possible design solutions. In order to enable exploration of design alternatives and rapidly obtain their performance characteristics at early stages, performance modeling and simulation of MPSoC architectures at the system level is necessary.

#### 1.2 PROBLEM STATEMENT

Efficient system-level simulation of multicore architectures is a contradicting problem as it requires *fast* and at the same time *accurate* performance models of processing cores. For many years, a typical approach for conducting performance simulation of the target software has been to use cycle-accurate instruction set simulation (ISS). Cycle-accurate simulators incorporate a detailed model of the processor's microarchitecture. In this type of simulators, fetching, decoding and scheduling of instructions is performed dynamically at simulation run-time. Cycle-accurate simulators are indispensable for exploration of the processor's internal microarchitecture. However, the use of these simulators during system-level design space exploration (DSE) of MPSoC is limited because of their low simulation speed. Consequently, for fast system-level performance analysis, the abstraction level of processor models must be raised.

On the other side of the spectrum are recently introduced hostcompiled source-level simulation methods. These methods are based on a native execution of the target code on the host computer. In these approaches, timing simulation of the target software is enabled by annotating pre-estimated execution delays in the target code. Sourcelevel techniques can efficiently abstract the microarchitectural details of processing cores and achieve significantly higher simulation speed compared to conventional cycle-accurate ISS. However, current approaches assume processors with in-order instruction execution only. At the moment, there is a gap in performance simulation of out-oforder processors between very accurate but slow cycle-accurate ISS and fast but very abstract host-compiled source-level simulation. To improve the efficiency of system-level DSE of multiprocessor architectures, new methodology for performance simulation is required that would consider out-of-order execution of instructions, while achieving speed higher than cycle-accurate ISS.

Moreover, one of the major goals of system-level DSE is to assess different options of SW partitioning in a multicore architecture, i.e. to investigate various task mappings and scheduling strategies, and to derive the requirements for a future OS implementation. Many recent approaches, that address high-level OS modeling at early design stages, consider the execution time of tasks at very high granularity. Particularly, they abstract hardware timing effects during a task exe-

cution, e.g. temporal behavior of coherent caches or arbitration on the shared interconnect, and model application tasks as a set of fixed processing latencies. For more comprehensive performance analysis of SW partitioning, the low-level hardware effects of the tasks' execution must be taken into consideration, e.g. cache coherency. Cycle-accurate processor simulators are not applicable for these investigations due to their low simulation speed, as mentioned earlier.

#### 1.3 CONTRIBUTIONS

The goal of this thesis is *fast* and yet *accurate* performance simulation of out-of-order processors at the system-level that enables design space exploration of multiprocessor system-on-chip in reasonable time.

Firstly, I introduce a novel approach for performing host-compiled SW performance simulation that considers out-of-order instruction execution. The proposed method is based on simulation of the target code at the binary (i.e. instruction) level. The simulation is performed on the host computer by translating target instructions into equivalent C code, which is then annotated with timing information. The thesis presents the methodology for obtaining and annotating the execution delays as well as considering the timing effects of out-of-order execution at simulation run-time. In particular, context-dependent execution time of instructions as well as reordering of memory accesses are tackled. To the best of my knowledge, it is the first approach that addresses out-of-order instruction execution in host-compiled SW simulation.

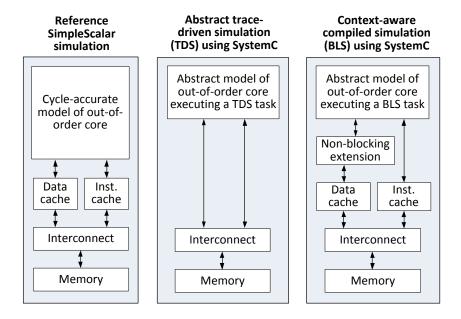

Secondly, I present a SystemC-based simulation framework for performance evaluation of multiprocessor architectures at the system level. In addition to the host-compiled binary-level SW simulation (BLS) method mentioned earlier, the framework supports trace-driven simulation (TDS). TDS completely abstracts the internal microarchitecture of processing cores. In contrast to BLS, TDS employs abstract application traces and does not require functional simulation of the target code. At the same time, TDS provides pin-accuracy of the communication requests and allows detailed evaluation of contentions in the chip interconnect. In the sequel of the thesis, we will see that out-of-order effects are exposed differently at the system level for various target applications. As a result, TDS offers a better trade-off between simulation speed and accuracy than BLS for certain target applications.

Finally, I present a high-level model of a scheduler. The scheduler model is a component of the simulation framework that enables evaluation of different SW partitioning options in multicore architectures. The scheduler model enables high-level management of application tasks and provides capabilities for inter-task synchronization. At the

same time, the workload of the application tasks is simulated with either BLS or TDS method, while considering the low-level hardware timing effects and still retaining the flexibility for high-level task management. Concepts presented in this dissertation have been published

#### 1.4 OUTLINE

in [42, 59, 60, 61, 62].

The thesis is structured as follows. Chapter 2 provides an overview of the state-of-the art techniques for SW performance evaluation. As the simulation method presented in this dissertation employs host-compiled simulation at the binary level, in Chapter 3 I briefly review the basics and the workflow of binary-level host-compiled simulation. Chapter 4 presents details of the proposed approach.

Chapter 5 describes in detail the proposed SystemC-based simulation framework. Particularly, I discuss the employment of BLS and TDS methods for system-level performance simulation of multicore architectures. Furthermore, I present implementation details of SystemC models of a high-level scheduler model, out-of-order processing cores, arbitrated on-chip bus and memory. Chapter 6 presents evaluation results of the BLS and TDS methods. In addition, it describes a use case of system-level DSE of a parallelized JPEG application on different multicore platforms. Finally, Chapter 7 concludes the dissertation with a discussion on the obtained results and presents an outlook on future work.

This chapter presents an overview of the related work in SW performance evaluation at different levels of abstraction, starting from cycle-accurate instruction set simulation (ISS) up to highly abstracted simulation of application models during system-level design. In the first part, I provide an overview of different ISS approaches and discuss recent advancements in this methodology. Afterwards, I review techniques for performance simulation at a higher abstraction level based on a native host-compiled execution of the annotated target code. Both ISS and host-compiled simulation are *execution-driven* techniques. In addition, we will retrospect estimation methods based on *trace-driven* performance simulation. Finally, I review recent approaches for the timing analysis of complex multi-tasking applications by means of a high-level model of a real-time operating system.

#### 2.1 INSTRUCTION SET SIMULATION

Instruction set simulation allows for accurate evaluation of the SW execution on a target processor and can be employed for various purposes. For example, instruction set simulators are indispensable tools for evaluating the design of processors and compilers [50, 54]. Particularly, the processor designer can assess the efficiency of specific instructions in the instruction set and make decisions on the parameters of microarchitectural components in a processor, e.g. dimensions of internal memory structures or type of branch prediction [50]. SW developers can employ ISS to validate the functionality of the target software before the actual HW implementation becomes available [5]. The review starts with *interpretive* instruction set simulation.

# 2.1.1 Interpretive ISS

In interpretive ISS, the simulation of target instructions is organized in a loop. In this loop, the processor model sequentially performs instruction fetching, decoding as well as performing the actual operation according to the semantics of the instructions [41]. A. Nohl *et al.* claimed that the simulation of the instructions in the loop "enables the highest degree of simulation accuracy and flexibility" [54].

SimpleScalar [5] is an example of interpretive ISS. The suite consists of multiple tools, which incorporate processor models at different levels of abstraction. At the highest abstraction level (*sim-fast* tool), only functional processor simulation is performed without any notion of

timing. At the lowest abstraction level (*sim-outorder*), the tool incorporates a detailed cycle-accurate model of an out-of-order processor capable of speculative execution. For accurate timing evaluation, *sim-outorder* employs performance models of internal microarchitectural components, e.g. instruction pipeline, instruction queues, branch predictor and caches. The simulator supports several instruction sets including ARM, PPC, Alpha and PISA (a slightly modified version of the MIPS-IV ISA [13]). In [14], D. Burger *et al.* presented further extensions to SimpleScalar that enable more detailed modeling of memory hierarchies and bus interconnect. The simulator has been widely adopted by computer architecture researchers as stated in [5].

Gem5 [9] (formerly M5 [10]) is a simulation framework that provides a range of processor models at different abstraction levels, including a model of a complex pipelined processing core with multiple hardware threads and capable of out-of-order execution. The processor models support multiple instruction set architectures including MIPS, ARM, Alpha and x86. In addition, the simulator allows modeling and evaluation of complex hierarchies of coherent caches and memories. The tool can perform a full-system simulation of target applications, considering IO devices and an operating system.

The major drawback of interpretive ISS is a low simulation speed, which, among other factors, results from time-intensive decoding of target instructions at simulation run-time [54].

# 2.1.2 Compiled ISS

Compiled instruction set simulators try to optimize simulation performance by moving the frequent operation of instruction decoding from run-time to compile-time. Two approaches of performing compiled simulation can be differentiated: static compilation of the target instructions and dynamic binary translation (DBT).

#### 2.1.2.1 Statically compiled ISS

The key idea behind statically compiled ISS is to translate the *complete* code of the target application into an intermediate, functionally equivalent representation. The intermediate code is then compiled and executed on the host computer.

In [50], C. Mills *et al.* suggested to employ static compilation to improve the simulation performance. The proposed method uses macrostatements and case statements of the C programming language to translate each target instruction into functionally equivalent C-operations. Afterwards, the resulting C-code is compiled and executed on the host machine at higher simulation speed than conventional interpretive ISS. The authors showed that the instruction compilation prior to simulation allows achieving a simulation speedup of 3 times compared to interpretive ISS. The suggested approach requires addi-

tional efforts for code compilation on the host. However, the associated timing overhead can be amortized if the target program must be simulated multiple times.

J. Zhu and D. Gajski in [90] proposed a statically compiled ISS based on intermediate instructions of a RISC-like *virtual machine*. In this approach, the target program is translated to virtual instructions which perform operations on a set of virtual registers. Afterwards, the virtual instructions are used to generate either host instructions or a C-code which has to be compiled on the host computer. By introducing the virtual machine, the authors address both adaptability of the simulator to different target/host platforms and the ability to directly manipulate the hardware resources of the host machine for higher simulation efficiency (e.g. by mapping virtual registers to the host registers). The authors reported that the speed of compiled ISS was only 1.1–2.5 times lower than the native execution of the target code on the host computer.

In [53], T. Nakada et al. proposed an approach in which target instructions are statically translated into a functionally equivalent Ccode. In this method, multiple target instructions belonging to one basic block are grouped into a basic block function. The basic block functions are invoked based on the value of the program counter register, which is used to select an appropriate function according to the program flow. The use of basic block functions has many benefits with respect to the final code size and simulation performance. However, such representation of the translated code does not allow simulation of *indirect* branches, i.e. the branches whose target address is calculated at run-time and cannot be determined at compile-time. In this case, the address of the target basic block function cannot be determined during the simulation. The authors solve this problem by using a second simulation mode, in which each instruction is simulated individually until the address of the known basic block function is found. At simulation run-time, the translated C-code is co-executed with the models of the processor microarchitecture to dynamically obtain the instruction execution time. In addition to the ode translation, the authors suggested optimized, workload-specific simulation of caches to further improve the simulation performance. On average, the use of static translation and compilation of the target instructions improved simulation speed by 19 times compared to the fast untimed simulator and 3.8x compared to the cycle-accurate out-of-order simulator from the SimpleScalar tool set.

Simulation methods based on static compilation require the target program code to be completely known prior to simulation. Therefore, the use of this approach may be limited if the target code changes at run-time (e.g. as in case of self-modifying codes). If the target code is not completely available prior to simulation, a more flexible approach is to translate the target instructions dynamically as discussed in the next section.

# 2.1.2.2 Dynamic binary translation

The limitations of static compiled simulation mentioned above are addressed by *just-in-time* cache compiled simulation introduced in [54]. The idea behind this approach is to pre-compile the behavioral description of the target instructions into C-functions. At simulation run-time, these functions are dynamically selected and executed on the host computer. The references to the functions are temporarily stored in a cache and subsequently reused multiple times during the simulation. If the program code has been changed, the simulator updates the cache with references to new C-functions. The authors reported that just-in-time compilation achieves 95% of the performance of conventional compiled simulation (if the size of the simulation cache is selected appropriately), while providing the full flexibility of the dynamic approach.

The Edinburgh High Speed simulator [31] supports both interpretive and DBT mode of instruction simulation. The simulation starts in the interpretive mode first. At simulation run-time, the tool profiles the program execution and dynamically translates the code of the most frequently used basic blocks. During the translation, the corresponding code sections are converted into a C-code, which is then dynamically compiled using a gcc-compiler and linked to the simulator. In the sequel of simulation, the translated basic blocks are simulated using the compiled code approximately 10 times faster than in the interpretive mode. In [31], the authors suggested that the granularity of translation units must be set either at the level of basic blocks or groups of multiple basic blocks. By using the variable size of translated code sections, an average speedup from 9.4 to 15.5 could be achieved compared to pure interpretive ISS.

Hybrid compiled instruction set simulation introduced in [65] follows a similar approach. The method employs *instruction templates* that are specific to various instruction classes of the target ISA. Based on these templates, the tool generates a custom template for each instruction of the target code. The generated code of custom templates is optimized and pre-compiled prior to simulation. The use of customized templates allows for a compact representation of the target code. At simulation run-time, a specialized decoder processes the transformed target code and then executes pre-compiled code of the respective custom templates. Thus, the authors tried to combine the benefits of statically compiled ISS and DBT. However, the approach still requires the availability of the complete target code prior to simulation. With the proposed technique, the authors achieved a speedup of 3 times compared to functional simulation in SimpleScalar.

QEMU [7] is a tool aiming at emulation of multiple target processors on different host machines. The tool enables full-system emulation of the target machine and is capable of executing unmodified target operating systems. The emulator dynamically translates target instructions into host instructions. Particularly, each target instruction is translated into a set of simpler *micro operations*, which are written in C and pre-compiled on the host platform. At simulation run-time, the micro operations are dynamically concatenated by the code generator and executed on the host machine. The translated target code is partially cached during the simulation in order to achieve better performance. The author of the tool reported a slowdown of the simulated code by 4 times (integer operations) and 10 times (floating point operations) compared to the native code execution.

The methods above focus on functional simulation only and do not consider the timing properties of software execution. Performance estimation of program execution is addressed in [11]. The paper aims at providing cycle-accurate performance modeling of an in-order processor during functional DBT-based ISS introduced in [31]. Particularly, the method employs a simplified performance model of a pipeline, which is capable of considering data dependencies among the target instructions. In this approach, the performance model is decoupled from the functional model and operates on the instruction-byinstruction and not cycle-by-cycle basis for the purpose of higher simulation efficiency. Similarly to [31], the tool translates most frequently used sections of the target code into C-code at simulation run-time. Additionally, the translated code includes functional calls to the pipeline model in order to update the microarchitecture state. Afterwards, the code is compiled as a shared library and dynamically linked to the simulator. With the proposed technique, the authors achieved a speedup of 3 times and an average simulation error of 1.4% compared to a cycle-accurate ISS.

D. Thach *et al.* [77] introduced a method for cycle count estimation by combining functional simulation in QEMU [7] with a timing analysis of the processor pipeline. In contrast to [31], the approach statically evaluates the pipeline timing prior to simulation, while making some assumptions on the status of cache accesses and branch predictions. At simulation run-time, the timing estimates are additionally adjusted to consider dynamic behavior of caches and branch prediction. The authors reported a simulation error up to 26% for an ARM processor with the average value of 10% compared to a real HW implementation. The extended version of QEMU was on average 3.37 times slower compared to functional simulation.

S. Stattelmann *et al.* [76] similarly added the capability of timing estimation to a DBT-based functional simulation in QEMU [7]. However, in this approach the execution time of basic blocks is derived using worst-case execution time (WCET) analysis of the target code

prior to simulation. The timing estimates are used during run-time of simulation to obtain an overall execution time of the target program. The proposed QEMU extension resulted in a relatively small slowdown of 1.6 times compared to the normal functional execution. However, due to the usage of the WCET values for the execution time estimation, the proposed approach still resulted in large simulation errors for some benchmarks up to 33%.

There are several commercial products currently available and aiming at fast simulation of processing cores. Synopsys CoMET [97] (formerly VaST CoMET) allows fast simulation of software on a virtual platform of the target system-on-chip. The tool includes a number of cycle-accurate models of processors from various vendors. Although there is no detailed information on the simulator available neither in the literature nor on the company's website, several recent publications [70, 66, 75] report that the tool is based on DBT technique.

OVPsim [95] from Imperas Software is a simulation tool that includes a large number of functional models of diverse processors. The simulator is based on dynamic binary translation of target instructions into x86 instructions on the host machine. The processor models are instruction-accurate and can be employed for early development and validation of the target software.

# 2.1.3 Sampled simulation

The key idea behind *sampled* simulation is to perform detailed simulation only for representative parts (or samples) of the target application<sup>1</sup>. Thus, the overall simulation time can be effectively reduced while still providing accurate simulation results.

HySim [34] is a hybrid approach that combines the native execution of annotated target code and functional instruction-accurate ISS. During the native execution, which is also denoted as fast-forwarding mode, the performance is only approximated. For this, the authors propose to statically analyze the target source code and assign execution costs to each operation in the code. Switching of the simulation mode between ISS and native execution occurs at the boundaries of target functions. The designer can manually define which functions should be executed in a particular mode. Alternatively, the switching between the modes can be performed automatically, e.g. in order to promptly reach a breakpoint set by the designer. The authors also mentioned that certain functions, e.g. calls to standard C libraries or third party libraries, for which the source code is not available, cannot be executed in the fast-forwarding mode. Simulation of these functions must be carried out in the ISS mode only. Nevertheless, the proposed method still allows achieving an average speedup of 36.6 times compared to pure ISS-based simulation. In addition, the au-

<sup>1</sup> This approach is sometimes referred to as sampling simulation.

thors reported an estimation error up to 17.6% with the average error value of 9.5%.

SMARTS framework [86] employs systematic sampling of program execution at fixed intervals. The simulation runs in two alternating modes: detailed simulation of the representative parts and fast functional simulation. During the functional simulation, the simulator updates the programmer view of the architecture only. At the same time, in detailed simulation the complete microarchitecture is updated. Furthermore, the authors showed that the state of the microarchitecture at the beginning of a detailed simulation has a significant impact on simulation accuracy. In order to reconstruct the microarchitecture state, the processor model undergoes *functional warming* of critical microarchitecture components, e.g. caches and branch predictor, before starting the detailed simulation. The approach allows achieving a very low average simulation error of 0.64% with the average speedup of 35 and 60 times depending on the considered processor microarchitecture.

Similarly to SMARTS, D. C. Powell and B. Franke [63] propose a method for accelerating performance estimation by running the processor simulation tool in two modes: slow cycle-accurate interpretive simulation and fast instruction-accurate simulation with performance prediction. However, in contrast to SMARTS, this approach employs adaptive sampling intervals. The decision on the appropriate simulation mode is made by the tool at simulation run-time. The simulation starts in the cycle-accurate mode, in which the performance prediction model is trained. If the prediction model produces accurate results relative to the cycle-accurate execution, the simulator switches to the faster instruction-accurate mode, while relying on the predicted values for performance estimation. In this mode, the tool continues evaluating the accuracy of the prediction model. If the accuracy drops below a certain threshold, the simulation is switched back to the cycleaccurate mode until the quality of prediction modeling is again improved. The authors reported an estimation error up to 19.97% with the average value of 2.36% and a speedup of 50%.

SimPoint [24] exploits the fact that target programs exhibit a repetitive behavior during an execution. This approach is based on automatic recognition of regular patterns in the program execution introduced in [72]. In SimPoint, a program's execution is divided into a set of non-overlapping intervals and the program behavior in each interval is analyzed. Intervals with a similar behavior are grouped in so called *phases*. In the next step, a representative interval is selected in each phase. The authors showed that by simulating only one representative interval per phase and extrapolating the obtained results, the overall performance of the program can be accurately estimated without the need of simulating the program completely.

## 2.1.4 ISS-based simulation of multicore architectures

Many research works employ ISS for performance evaluation of multicore architectures. For example, Gem5 [9] mentioned earlier in this chapter simulates multicore architectures by instantiating multiple ISS objects running in parallel. Simics [46, 45] can instantiate multiple instruction-level processor models to simulate a wide range of target systems, from a small embedded system to multiple complex interconnected servers. The models are simulated by translating the target instructions into an intermediate representation. The instructions in the intermediate format are then interpreted on the host machine. The processor models are instruction-accurate and do not provide accurate estimation of the cycle count. Nevertheless, the models are claimed to provide sufficient timing accuracy for simulating hardware peripherals required for full-system simulation of modern operating systems. The simulator's speed is 26 to 75 times slower compared to a native execution of the code on the host machine.

Many approaches propose to integrate multiple ISS instances into a SystemC model of a complete system-on-chip. MPARM [8] encapsulates several cycle-accurate simulators of an ARM processor into a wrapper. The wrapper is used to synchronize timing and enable data exchange between the ISS and SystemC environment, where an on-chip AMBA bus and shared memory components are simulated. The authors demonstrated an example of design space exploration of a MPSoC architecture by evaluating different cache sizes and bus arbitration policies. In a single-core architecture, the proposed approach achieved a speed of 60 Kcycles/s on a Pentium 4 2.6 GHz host computer. In a six-core architecture, the simulation speed of individual cores was reduced to 10 Kcycles/s.

Y. Yi et al. [88] improved co-simulation of multiple ISS instances by reducing the synchronization overhead and distributing the simulation over multiple processors in the host computer. In this method, each instruction set simulator generates a sequence of events, which are then transferred to a simulation backplane in the form of a trace. The trace is transferred at time points of inter-core communication. The backplane reconstructs the global timing of the supplied events under consideration of possible contentions on the interconnect. Thus, multiple instances of ISS can be co-simulated with a very small synchronization overhead. The method makes a simplifying assumption that the processors do not exhibit out-of-order behavior, i.e. the accesses latencies determined in the backplane do not impact on the time stamps of upcoming events. The authors showed that the proposed synchronization method achieves a simulation speed 8 times larger than the speed of a commercial SystemC simulator with conventional lock-step synchronization between ISS instances. Furthermore, by using the multicore architecture of the host computer, simulation performance could be further improved by 28%, resulting in a speed of 400 Kcycles/s. In addition, the simulation could be further distributed over multiple hosts. In this case, simulation performance could be approximately doubled on 4 host computers.

Sesame [58] is a simulation framework for design space exploration of embedded system-on-chip architectures. The framework allows for flexible mapping of application models to the underlying model of a HW architecture. The timing properties of the architecture components, among other methods, can be dynamically calibrated by an ISS co-simulated in the simulator. The cycle count estimated in the ISS is then used for high-level timing simulation of the HW architecture.

Hybrid simulation introduced in [19] aims at fast performance evaluation of multiprocessor architectures. This approach is based on the HySim simulator [34] that was also discussed in the previous section. Similarly to [34], the method relies on hybrid co-simulation of a cycle-accurate instruction set simulator and a native execution of the annotated target code. During the native execution, the timing of the target code is only approximated. For this, the tool statically analyzes the intermediate representation of the target code. Afterwards, the tool evaluates timing of the intermediate operations using fixed cycle costs and annotates the calculated time values back to the target source code. In addition, the approach employs dynamic simulation of data caches in order to improve the accuracy of timing estimation. Simulation of multiprocessor architectures is performed by instantiating multiple processor models in the simulator. Each of the processor model can run either in the ISS- or native execution mode and has its own local time which is then synchronized with the global time. In the experiments, the authors employed a very abstract bus model that does not consider contentions. The proposed method allowed simulation of the target application with an error of 3% at a speedup of 3–5 times compared to full cycle-accurate simulation.

O. Almer *et al.* [3] employ just-in-time DBT and parallelized simulation on the host computer to enable fast functional simulation of multicore architectures. This technique combines interpretive and compiled ISS and follows similar simulation principles introduced in [31]. The parts of the target code, which are most frequently executed during the interpretive simulation, are dynamically compiled and simulated on the host machine at a very high speed. The high efficiency of multicore simulation is achieved by simulating each individual core in a separate thread, which is then scheduled and executed in the host OS. Moreover, the authors show that the translated and compiled target code can be effectively shared among multiple simulations of individual cores. The synchronization of the cores is carried out with the support of the hardware synchronization instructions in the x86 host computer. The proposed technique was evaluated on a host machine with a 32-core Intel Xeon processor, achieving a speed

of 11982 MIPS when simulating a 2048-core target architecture. The presented approach assumes functional simulation only and does not perform evaluation of execution time.

#### 2.2 SIMULATION BASED ON TARGET CODE

A different approach for performance estimation is to employ the code of target applications. In this case, the target code is annotated with pre-estimated execution delays and then compiled and executed on the host computer. Host-compiled simulation achieves very high speed compared to cycle-accurate ISS. Consequently, host-compiled techniques have been widely used during simulation of MPSoC architectures [20], for which simulation performance is very critical. The target code can be employed at different levels of abstraction: source-level, intermediate-representation level or binary-level. We discuss each of these levels in more detail in the following sections.

## 2.2.1 Source-level simulation

Many recent research works employ simulation of the target code at source level, e.g. written in C language. The idea behind this approach is to annotate pre-estimated timing directly to the target source code. The methods reviewed in this section differentiate in the way of obtaining the timing information prior to simulation.

J. Bammi *et al.* [6] perform partial compilation of the source code in order to derive initial information on the target instructions. The instructions are then mapped to processor-independent virtual instructions. Performance estimation is enabled by assigning a cost to each virtual instruction. The costs are target-specific and represent approximated execution time of the instructions on the target processor. The authors suggested to determine the costs using either information provided in the processor's documentation or by employing ISS-based calibration. The timing estimates are then back-annotated in the original source code of the target application in order to enable its timing evaluation. This approach approximates the pipeline effects, e.g. stalls in the pipeline are not assumed, and neglects the timing effects of caches. The authors also suggested timing estimation based on the object code. This method will be discussed in the next section.

In [49], T. Meyerowitz *et al.* annotate the target source code with timing estimations obtained on a cycle-accurate virtual prototype of the target system. In this approach, the target software is executed in the cycle-accurate simulator first in order to obtain an execution trace. Afterwards, the tool analyzes the trace and calculates the timing delays of the instructions. The average execution time is then back-annotated to the source code using the debugging information. In the presented

approach, caches, memory and communication components are not simulated and the communication delays are pre-characterized and annotated in the code. The proposed method achieves a speedup of 10–1000 times with the average estimation error of 4.9% and a maximum estimation error of 17.5% .

J. Schnerr *et al.* [70] similarly employ back-annotation of timing to the original source code of the target application. The authors suggested to employ static worst-case (WCET) and best-case execution time (BCET) analysis to obtain the execution time of basic blocks prior to compiled simulation. The proposed method uses a dynamic model of an instruction cache in order to adjust the estimated cycle count at simulation run-time. The resulting annotated code is simulated using SystemC. The method increases the simulation speed up to 91% compared to conventional ISS.

SciSim [83] is a source-level simulation technique in which the execution time of target instructions is pre-estimated using static pipeline analysis prior to simulation. The approach uses debugging information to find mapping between instructions of the object code and corresponding lines in the source code. In addition to static timing annotations, dynamic models of caches and branch predictors are cosimulated to consider dynamic timing effects. To support the simulation of data caches, additional code is added for calculating the target addresses at simulation run-time. For target code, which was compiled without optimizations, the proposed approach achieves a speedup of 16 times (assuming that the branch predictor and caches are co-simulated) at the average error of 0.1% compared to a cycleaccurate ISS of a PowerPC processor.

Y. Hwang *et al.* [28] presented a technique for performance estimation based on automatic generation of annotated transaction level models of processing elements. In this method, timing estimation is carried out using generic models of pipelined processing elements under consideration of data dependencies between operations. In addition, the authors employ statistical models of caches and branch predictor to consider dynamic timing effects. The timing estimation is performed for all basic blocks of the target application. Afterwards, the approach uses the LLVM compiler infrastructure in order to generate a C code of the target application annotated with the estimated timing values. The generated code is then simulated in the scope of SystemC processes for performance evaluation of the complete architecture.

K.-L. Lin *et al.* [43] propose a similar approach that relies on static back-annotation of the timing estimates to the source code of the target application. In this method, timing estimation is performed for target basic blocks using static pipeline analysis as well. In addition, the authors consider pipeline effects between two adjacent basic blocks and add a correcting factor to the obtained timing values. Dur-

ing the timing annotation, the proposed method tries to find the basic block boundaries in the source code in order to locate the annotation points as accurately as possible. The timing effects of branch prediction are considered by using a prediction model at simulation runtime. The method makes use of a dynamic instruction cache model in order to dynamically consider the impact of miss penalties on the SW execution time. In turn, the data cache is considered by using statistic modeling because target memory addresses are difficult to obtain at the source level as mentioned by the authors. The method achieves a speedup of three orders of magnitude compared to a reference cycleaccurate ISS at the average error of 2%.

All research works presented above rely on back-annotation of preestimated instruction timing into the source code. However, there are two problems associated with this approach. The first problem occurs if the target software is compiled with compiler optimizations. The target compiler may modify the structure of the binary program without changing its functional behavior [74]. Thus, the control flow graph (CFG) of the source code does not match the CFG of the binary code. In this case, it is particularly difficult to find mapping between instructions in the object code and the corresponding statements in the source code. Secondly, for accurate simulation of data caches, SW compiled simulation requires actual target memory addresses that are used by load/store instructions. However, this information is not visible at the source level, at which computational operations are performed on the source-code variables.

Some of the recent works address the problems above. In [74], S. Stattelmann *et al.* suggested to find matching between binary- and source-level code using dominator homomorphism. This method relates the execution order of basic blocks in the source- and binarylevel code. Thus, the control flow of binary basic blocks can be reconstructed at the source level. In [75], the authors aim at accurate simulation of data caches during source-level simulations. Since the target addresses cannot be always determined correctly using the debugging information, the authors propose to use interval analysis on the target processor's registers in order to evaluate possible address ranges. Further, the authors introduce an abstract cache model that operates on the annotated address ranges and approximates the behavior of real caches. K. Lu et al. [44] address the matching problem by decomposing the CFG of the binary- and source-level code into multiple nested sub-graphs. The basic blocks in the sub-graphs are then matched using the domination principle.

## 2.2.2 Simulation based on intermediate representation

As mentioned in the previous section, the problems in matching binary- and source-level code of the target application hinder accurate timing annotations in the source code. One of possible solutions to this problem is to employ the *intermediate representation* (IR) of the target code for simulation. The IR code already considers many compiler optimizations and can be obtained during the compilation of the target software.

J.-Y. Lee and I.-C. Park in [39] employ a target-independent IR for performance simulation of the application code. Using the description of the target processor, cost of each intermediate operation is determined and annotated in the intermediate code. Afterwards, the intermediate code is compiled and executed on the host computer. In this approach, timing effects of instruction scheduling in the target processor are considered by scaling the annotated timing information by the pre-estimated value. Moreover, this method assumes cosimulation of cache models in order to determine cache access latencies at simulation run-time. To enable this, additional IR operations are added to obtain the target memory addresses.

T. Kempf *et al.* [33] use a similar approach to perform instrumentation of the target code represented at the intermediate, target-independent level. In this method, each operation in the IR is additionally instrumented with the code that accumulates the associated timing costs. The memory accesses are simulated by adding additional function calls to the communication model that adjust the simulation time accordingly. The instrumented code is then compiled and executed on the host computer for performance estimation of the target software. The proposed approach relies on approximated values of the execution time of the intermediate operations. Dynamic target-dependent timing effects, e.g. pipeline interlocks and effects of the caches and branch prediction, are not considered at this abstraction level.

A. Bouchhima *et al.* [12] employ IR-level of the target code for instrumentation and additionally introduce the concept of cross intermediate representation. The cross IR is the extended version of the original IR that considers target-specific transformations of the program control flow. The authors correspondingly extended the backend of the LLVM compiler infrastructure achieving one-to-one mapping between the cross IR and the latest stage of the target-dependent IR. The authors reported an accuracy of 100% in reconstructing the sequence of basic block execution in the native execution with respect to the execution of the target binary in the instruction set simulator.

E. Cheung *et al.* [15] use a modified version of the target compiler to generate annotated *structural models* of the target software. The structural models are derived in the GCC compiler based on the IR of the target code. In addition, these models are annotated with the execution time of the instructions obtained using the documentation of the target processor. The annotated timing considers data dependencies among the instructions in the processor's pipeline. In the next step, the structural models are wrapped into SystemC components and,

along with other components' models, are employed for MPSoC performance simulation. The proposed approach allowed a simulation speedup of three orders of magnitude compared to cycle-accurate ISS at an average error of 1%. However, such a speedup was achieved assuming a number of simplifications. Particularly, dynamic branch prediction and cache effects were not addressed in this approach. Moreover, the authors assume only coarse-grained communication between the processing cores in MPSoC.

In [82], Z. Wang and A. Herkersdorf proposed to generate a new intermediate C-code based on the IR of the target code. The resulting C code is very close to the target binary code and considers optimizations of the target compiler. The timing estimation is performed on a binary code generated from the intermediate C-code. The authors showed that in this case the source-code statements and the binary-level instructions can be matched very accurately using the debugging information of the intermediate C-code. The instructions' timing is determined prior to simulation using static pipeline analysis. In addition, cache models are employed to consider dynamic cache effects. As the target addresses are not available at the intermediate level, the authors suggested to use the host addresses of the variables in the intermediate C-code. The authors showed that simulation of the intermediate C-code produces the execution time which is very close to the execution time of the original source code. The proposed approach allowed for a simulation speed close to the native host-execution, showing the average timing error of 0.53% compared to a cycle-accurate ISS of an in-order processor.

## 2.2.3 Instruction-level simulation

At the instruction- (or binary-) level, timing simulation of the target code is performed at the granularity of instructions. The code at the binary level already contains all optimizations made by the target compiler. Therefore, the matching problem due to compiler optimizations is not relevant at this abstraction level.

J. Bammi *et al.* [6] suggested to use the modified version of the target compiler in order to produce an assembler-level C code which considers compiler optimizations. The code has a similar functional behavior as the original program and contains additional timing annotations. The timing estimates are derived using generic virtual instructions with the associated costs. The resulting assembler-level C code is then compiled and executed on the host computer in order to perform accurate performance estimation of the target software. The proposed approach allowed improvement of simulation speed by a factor of 18 times compared to a cycle-accurate ISS.

M. Lazarescu *et al.* [36] employ the assembler representation of the compiled target code to produce equivalent assembler-level C code.

The translated assembler-level C code can be co-simulated with untranslated functions of the target C code. This is enabled by using shared variables in the translated and untranslated parts and by implementing target-specific conventions of function calls. Afterwards, the resulting code is annotated with timing estimates produced by static pipeline analysis. In this approach, dynamic timing effects of instruction and data caches are abstracted. The proposed method allowed improvement of simulation speed by one order of magnitude compared to a cycle-accurate ISS.

J. Schnerr *et al.* [69] proposed an approach in which a target processor is emulated on a prototyping platform consisting of a VLIW processor and FPGAs. The execution of the target code is enabled by translating target instructions into instructions of the VLIW processor. Time estimation is then enabled by adding a pre-estimated cycle count in each basic block of the translated code. In addition, special code is inserted to simulate the timing behavior of the instruction cache and branch predictor. The annotated translated code is executed on the prototyping platform to obtain the overall execution time of the target software. The proposed approach achieved speed comparable to an FPGA emulation. At the highest level of accuracy, the authors reported a speed in the range of 3–10 MIPS, with an estimation error of 3–15% compared to the reference evaluation board.

M.-H. Wu *et al.* [85] translate target instructions into equivalent C-code annotated with timing, which is then simulated using SystemC. For simplicity reasons, the authors assume that each target instruction is executed in one cycle. Thus, the target-dependent timing, e.g. pipeline or cache effects, are not addressed. Moreover, similarly to [15], the authors simulate only coarse-grained communication requests, represented by inter-task communication using shared variables. However, the approach does not consider contentions on the shared interconnect between inter-task communication points. The simulation methodology achieves a speedup of 22–101 times compared to a cycle-accurate ISS.

In [81], Z. Wang and J. Henkel introduced a hybrid approach that combines simulation of the target code at the source and binary levels. Thus, the authors address one of the major restrictions of the source-level methods, which cannot simulate parts of the target application, for which the source code is not available, e.g. third-party libraries. In particular, this work focuses on data synchronization between the source- and binary-level code to enable functionally correct simulation. The proposed approach could double the speed of simulation compared to the pure binary-level simulation, achieving an overall speedup of 128 times compared to cycle-accurate instruction set simulator.

#### 2.3 TRACE-DRIVEN SIMULATION

Trace-driven simulation (TDS) has been widely used for performance evaluation of computing systems [71, 79]. The key idea behind this approach is to collect a trace of events using a reference computing system first. The obtained trace is then simulated on a model of the system to predict its performance in a new environment. Alternatively, the trace can be used to assess new configurations of the system.

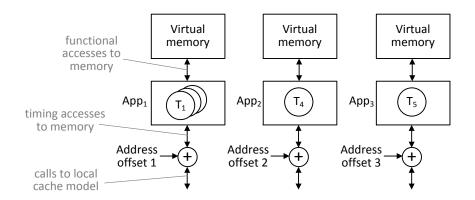

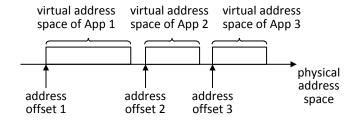

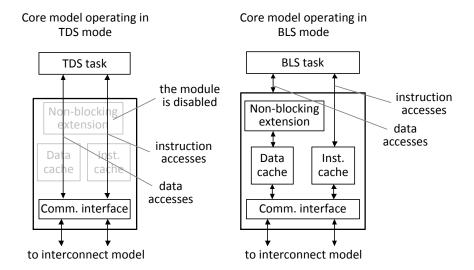

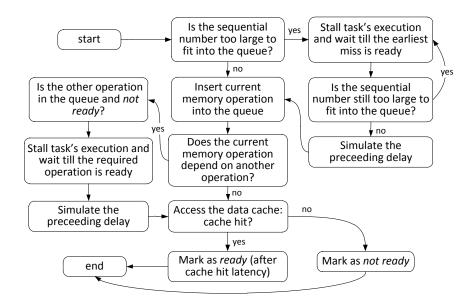

For multiple decades TDS has been applied for analysis of different aspects of computing systems. S. Sherman and J. C. Browne [71] presented an overview of trace-driven modeling techniques that were employed for evaluation of computer systems at the level of OS services. In these approaches, event-sensitive probes in the operating system were used to collect a trace of events. These events describe points when the system's resources were requested and allocated. Afterwards, performance estimation was carried out by simulating the resulting trace in a system's model. Trace-driven modeling techniques reviewed in [71] were used, among others, to evaluate algorithms for CPU scheduling, resource allocation or dynamic storage management.