#

# SCHOOL OF COMPUTATION, INFORMATION AND TECHNOLOGY - INFORMATICS

TECHNISCHE UNIVERSITÄT MÜNCHEN

Master's Thesis in Informatics

# Analysis and Implementation of AMD IBS Sample Collection for Performance Analysis Purposes

Maximilian Geitner

#

# SCHOOL OF COMPUTATION, INFORMATION AND TECHNOLOGY - INFORMATICS

TECHNISCHE UNIVERSITÄT MÜNCHEN

Master's Thesis in Informatics

#### Analysis and Implementation of AMD IBS Sample Collection for Performance Analysis Purposes

#### Evaluierung und Nutzung von AMD's IBS Sample Collection für Leistungsanalyse

| Author:     | Maximilian Geitner                |  |  |  |  |

|-------------|-----------------------------------|--|--|--|--|

| Supervisor: | Prof. Dr. rer. nat. Martin Schulz |  |  |  |  |

| Advisor:    | Stepan Vanecek, M.Sc.             |  |  |  |  |

| Date:       | 17.07.2023                        |  |  |  |  |

I confirm that this master's thesis is my own work and I have documented all sources and material used.

Munich, 17.07.2023

Maximilian Geitner

#### Acknowledgements

For the completion of this thesis, I appreciate the support I have received for working on this thesis. First, I want to thank the Chair of Computer Architecture and Parallel Systems for offering me the opportunity to work on this thesis and access to the CAPS cloud infrastructure. I appreciate the guidance I have received from Stepan very much, and I have learned a lot in half a year. Also, I want to thank Martin for his great help in finding mistakes in my thesis drafts. I also want to thank my family for their continuous support in the past few years during my studies and, of course, for this thesis.

#### Abstract

Instruction-based sampling (IBS) is a statistical profiling method developed by AMD and has been available in AMD processors since 2007. This technique features the data collection of the two event types, IBS Fetch and IBS Op. These two classes of events provide various metrics related to the front- and back-end of the pipeline. In contrast to the Intel PEBS solution with configurable programmable counters, IBS cannot choose specific metrics usually available with hardware performance counters.

IBS is implemented in the profiling interface perf\_event. Perf\_event is part of the Linux kernel since version 2.6 and developed in cooperation with hardware vendors in order to use functionalities related to the performance monitoring unit (PMU) of the processor. Perf\_event provides the system call perf\_event\_open() with the purpose of making performance metrics accessible to other profiling tools. One such tool is Mitos, which has been under development at the Lawrence Livermore National Laboratory and is now modified with new features at the Chair of Computer Architecture and Parallel Systems.

This work implements the data collection functionality utilizing IBS in Mitos. It takes a closer look at the capabilities of perf\_event with IBS, various implementation aspects, and how IBS is usable in MPI and OpenMP applications. Currently, IBS requires system-wide data collection privileges and does not support per-process monitoring. Due to the missing per-process monitoring option, monitoring all processor cores individually and filtering event samples on a higher level might be a suitable workaround method. The other workaround idea only observes processor cores executing the target application and automatically moves with the target process on change detection. However, the detection implementation has performance-related issues and requires further modifications.

### Contents

| Ac | know   | ledgements                                       | iv |

|----|--------|--------------------------------------------------|----|

| At | ostrac | t                                                | v  |

| 1. | Mot    | ivation                                          | 1  |

| 2. |        | oretical Background                              | 2  |

|    | 2.1.   | Processor Design Decisions                       | 2  |

|    |        | 2.1.1. Pipeline-Stages in Superscalar Processors | 2  |

|    |        | 2.1.2. Caches                                    | 6  |

|    | 2.2.   | Performance Monitoring on the Hardware-Level     | 6  |

|    |        | 2.2.1. Hardware Performance Counters             | 6  |

|    |        | 2.2.2. Event-Based-Sampling                      | 8  |

|    | 2.3.   | Intel Processor event-based sampling (PEBS)      | 8  |

|    | 2.4.   | AMD Instruction-Based Sampling (IBS)             | 9  |

|    |        | 2.4.1. IBS Fetch                                 | 9  |

|    |        | 2.4.2. IBS Op                                    | 10 |

|    | 2.5.   | OpenMP and OMPT                                  | 11 |

|    | 2.6.   | MPI and PMPI                                     | 11 |

| 3. | Dese   | cription of Tools                                | 13 |

|    | 3.1.   | The Tool Perf_Event                              | 13 |

|    |        | 3.1.1. The CLI of Perf_Event                     | 13 |

|    |        | 3.1.2. The perf_event_open() System Call         | 14 |

|    | 3.2.   | Mitos                                            | 16 |

|    | 3.3.   | MemAxes                                          | 17 |

|    | 3.4.   | Computation Platforms                            | 18 |

| 4. | IBS    | in Mitos                                         | 20 |

|    | 4.1.   | IBS Event Sample Data Collection                 | 20 |

|    |        | 4.1.1. Perf_Event Implementation with IBS        | 22 |

|    | 4.2.   | Mitos Implementation Changes                     | 23 |

|    |        | 4.2.1. IBS Implementation                        | 23 |

|    |        | 4.2.2. CMake Changes                             | 26 |

|    |        | 4.2.3. Mitosrun                                  | 27 |

|    |        | 4.2.4. Mitoshooks                                | 27 |

|    | 4.3.   | Evaluation                                       | 27 |

|    |        | 4.3.1. Data Collection Validation                | 28 |

|    |        | 4.3.2. Data Collection Method Evaluation         | 29 |

|     | 4.4.   | IBS Li   | mitations and Challenges                             | 30 |

|-----|--------|----------|------------------------------------------------------|----|

|     |        | 4.4.1.   | System-wide Monitoring                               | 30 |

|     |        | 4.4.2.   | Core Migration Overhead                              | 30 |

|     | 4.5.   | Future   | Considerations for Mitos                             | 31 |

|     |        | 4.5.1.   | Simultaneous Data Collection of IBS Fetch and IBS Op | 31 |

|     |        | 4.5.2.   | Issues with Dyninst and OpenMP                       | 31 |

|     |        | 4.5.3.   | Additional IBS Zen 4 Extensions                      | 31 |

|     |        | 4.5.4.   | Result Aggregation in Multi-Thread Applications      | 32 |

|     |        | 4.5.5.   | MPI + OpenMP Applications                            | 32 |

|     |        | 4.5.6.   | Per-Process Monitoring with Perf_Event               | 32 |

| 5.  | Con    | clusion  |                                                      | 34 |

|     | 5.1.   | Summ     | ary                                                  | 34 |

|     | 5.2.   |          | k                                                    | 34 |

| ١.  | Ар     | pendix   |                                                      | 36 |

| Α.  | Abb    | reviatio | ns                                                   | 37 |

|     | A.1.   | Genera   | al Terminology                                       | 37 |

|     |        |          | Terminology                                          | 37 |

|     |        |          | erminology                                           | 37 |

| Lis | t of   | Figures  |                                                      | 38 |

| Lis | t of   | Tables   |                                                      | 39 |

| Bil | bliogr | aphy     |                                                      | 40 |

# 1. Motivation

In HPC systems, looking at various aspects to improve efficiency and performance has always been important. The popular TOP500 list contains the most powerful systems in the world, the current leader in the June 2023 ranking is the Frontier supercomputer with 8,699,904 cores and power consumption of 22,703kW [Tea23]. This system uses AMD 3rd generation EPYC 64C 2GHz processors and AMD Instinct MI250X accelerators.

However, the hardware is only one aspect that needs to be considered. The software also plays a massive role in choosing a new computing platform. Compatibility and software support are often major reasons for advocating for certain systems. Although new ARM-based microarchitectures have arrived on the market and have advantageous characteristics such as high performance at relatively low power consumption, x86 processors still exist. The reason is the related software. This might be modern games, old commercial software, or software for HPC clusters using certain functionalities only available on a specific hardware and software stack.

Sometimes, the hardware alone is not the main reason to buy a certain system. It could be the toolchain that works together with the hardware. One such example is the toolkit CUDA and Nvidia accelerators in the artificial intelligence sector. The toolchain could also be a framework of profilers, compilers and other utility programs binding users to a certain vendor. The reasons might be the hype from other people, existing knowledge about the system or in the end the better software support.

Software support is also relevant in HPC and necessary for designing resource efficient applications. To analyze potential bottlenecks, finding a suitable profiling tool that can discover potential problems is necessary.

With Intel PEBS, a profiling solution is already available since the NetBurst architecture in 2000. [Int23a] The other vendor, AMD, has a similar solution with instruction-based sampling (IBS). This solution has been available since 2007 and is a response to the request for precise sampling. It is interesting to know about their data collection capabilities and their usability in practice. To answer the question, knowledge about processor design, performance monitoring, the functionality of profiling tool interfaces and their usage is necessary.

## 2. Theoretical Background

This chapter is about important basics to better understand profiling tools. It starts with processor design decisions and how to implement an efficient pipeline and memory architectures. This information is relevant for the next part about the PMU, its interaction with the pipeline, and what kind of monitoring techniques exist. The remaining parts cover Intel PEBS and AMD IBS, two different solutions for precise sampling, and profiling interfaces for two common application types in HPC and its interface for profiling tools, MPI and OpenMP.

#### 2.1. Processor Design Decisions

#### 2.1.1. Pipeline-Stages in Superscalar Processors

The concept of an instruction pipeline is essential for modern processor architectures to improve their instruction-level-parallelism (ILP) cost-effectively. A pipeline divides the workload of an instruction into multiple smaller subtasks and processes these in the corresponding number of stages. Although this approach increases the system's complecity and may increase the duration to process a single instruction, there is the benefit of performing work on multiple instructions simultaneously. [Gon11]

It is desirable to work on multiple instructions at once, but there are certain aspects pipeline design needs to consider for an efficient implementation. One primary goal is to have stages that complete their subtask in roughly the same amount of time. Slower subtasks could slow down successive stages by forcing them to wait for their next assignment and, as a result, reduce pipeline efficiency. These issues can be masked by employing multiple units to solve subtasks at potential bottleneck stages, reorder subtasks for a more efficient workflow or implement buffers between stages.

Buffers temporarily store information related to an instruction until the next stage has completed a previous assignment. Buffers might fill up if the successive stage cannot complete subtasks, such as memory accesses, as fast as previous stages in the pipeline and empty in cases where the stage is faster than its predecessor stage. Thus, buffers provide options to keep pipeline stages running and prevent them from falling into an idling state due to unavailable subtasks or by being unable to hand over subtask results to their successor stage and resume working. Technical reasons still prevent buffers from resolving problems such as cache misses or more extended periods of difficult computational tasks. Implementing larger buffers can be costly by taking away space on the processor and not improving efficiency. Also, implementing too many stages in a pipeline does not necessarily improve the pipeline's efficiency. At some point, too small subtasks make processor design increasingly complex. There is a particular trade-off between the number of stages and the increase in performance. [She13]

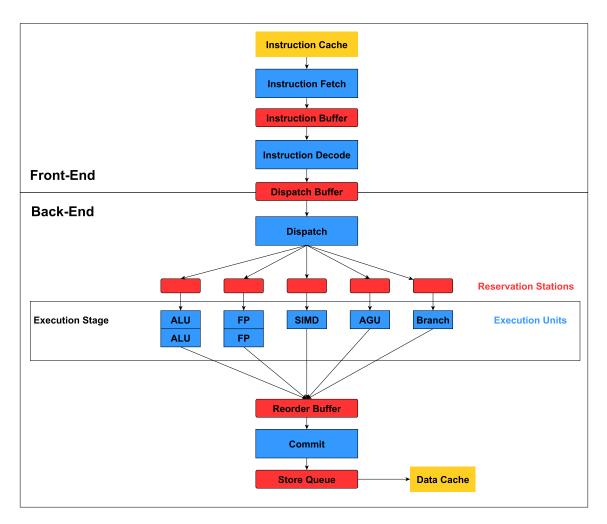

Figure 2.1.: Pipeline Overview.

The following example in Figure 2.1 shows how a small instruction pipeline could be separated into different stages. An instruction pipeline needs to handle many different kinds of instructions. Instructions are usually classified into one of the following categories:

- load/store instructions

- conditional instructions

- arithmethic and logical operations

The first stage is the instruction fetch unit, which uses the instruction pointer to determine the next instruction. This step requires an address translation involving the TLB and access to the instruction cache. In unfortunate cases, an expensive main memory access might also be necessary. Another concern is the occurrence of branches in a program. The unit's branch predictor predicts whether the branch is taken or not to continue the instruction execution. Predicting the correct fetch address involves the branch target buffer (BTB) and a branch predictor. An incorrect prediction involves a costly pipeline flushing resulting in a performance loss. [Gon11]

The next stage decodes the instruction, and this step transforms the instruction into one or multiple micro-operations depending on the complexity of the task. Micro-operations are small and simple instructions that are processed in one cycle at the following execution stage. The first two stages belong to the front-end of a pipeline, and instructions are processed in-order.

Unlike the first two stages, out-of-order execution allows the reordering of operations in order to increase performance. It is usually used on modern x86 processors and ARM-based high-performance processors. The out-of-order execution is implemented in the following stages of the pipeline and is part of the back-end of the pipeline. After the decoding stage, the microoperation is dispatched into the pipeline, issued, and the execution starts. The related dispatch stage assigns register operands and the associated resources to the micro-operation. Consecutive micro-operations might use these register operands and could cause data dependencies. Some are artificial name dependencies, and the technique register renaming removes them before the execution stage. Between the dispatch stage and the execution stage are special buffers, the so-called reservation stations, storing micro-operation-related information until the execution unit is ready. The micro-operations wait until all operands are ready and then issued to execution units.

In the execution stage, the actual micro-operation performs its specified workload. Common execution units are:

- Arithmetic Logic Unit (ALU)

- Branch Unit

- Floating-Point Unit

- SIMD unit

- Address Generation Unit (AGU)

Quite special are memory operations, they either load data from memory or store register values in the main memory. Memory operations specify the memory address with several source operands. There is a dedicated address generation unit (AGU) involved in generating the effective physical address by using a base address, an offset, and potentially other parameters. The cache is between the main memory and the processor, which stores data temporally for faster memory access. It is desirable to put often accessed data in the data cache and have cache hits in the case of future data requests to the same location, as main memory access is relatively slow. A cache miss generates a time penalty for accessing the slower main memory. All the other execution units working on non-memory-access-related tasks use register operands to compute the result. Operation results move to the reorder buffer (ROB). Its location is between the execution and the commit stage. The reorder buffer is necessary for out-of-order processors. It is part of the process to revert the micro-operation order to its original state as specified in the application.

Modern processors can decode multiple instructions per cycle. Therefore, later stages should be able to also process multiple micro-operations per cycle. The execution stage can have more than one execution unit in order to process multiple pending micro-operations. These execution units are generally divided into different types and can only handle specific operations. For example, there could be two integer units and two floating point units in the execution stage which could execute four different independent operations per clock cycle in the best-case scenario. Out-of-order execution improves the possibility of utilizing all execution units in the pipeline by finding an operation order that can be executed simultaneously. Additionally, it might reduce stalls in the pipeline due to cache misses.

The last stage, the commit stage, writes back the result to the specified register and commits the changes. After the write-back, the operation changes to the "completed"-state, and is often also declared as "retired". Memory operations need to finalize memory access changes and have a delay of a few clock cycles until they retire. A store queue or store buffer helps in reducing the time to retirement, and it stores values until they can move to the main memory.

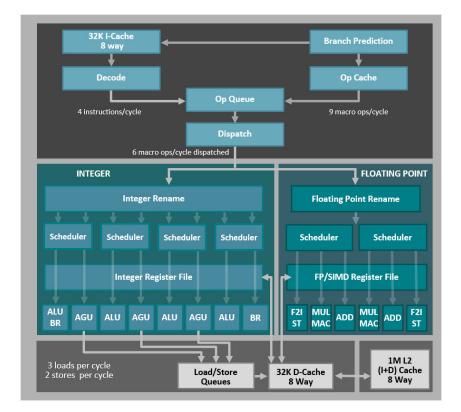

Figure 2.2.: Instruction Pipeline in Zen 4. [AMD23a]

Figure 2.2 shows an instruction pipeline implemented in the AMD Zen 4 microarchitecture. AMD defines the three following types of operations varying in complexity:

- instructions

- macro-operations

- micro-operations

One Instruction decodes to one or multiple macro-operations. The dispatch of a macro-operation is the transfer from the front-end to the back-end of the pipeline. A macro-operation may be

issued as multiple micro-operations which perform even simpler operations, such as arithmetic or load/store operations in the pipeline.  $[{\rm AMD23a},\,{\rm AMD23c}]$

#### 2.1.2. Caches

For a processor, it is desirable to have storage as fast as registers. However, registers are relatively costly and require a lot of space on the chip. Thus, using caches is a trade-off between speed and cost efficiency. Modern processors also employ several tiers of cache, the L1, L2, and L3 cache. The fastest cache is the L1 cache, which is usually a small SRAM with a size of a few KB and exclusively used by a single processor core. The L2 cache is another private cache with slower memory access timings than the L1 cache. However, it has a larger cache size in the range of a few MB. The largest cache is the L3 cache. It is typically implemented as a cache with even more available memory shared between multiple cores. The exact specification depends on the vendor and architecture. Besides the different cache tiers, it is common to separate between instruction and data caches on the fastest L1 cache. Necessary for cache locality, this separation exists on x86 processors from both vendors, Intel and AMD.

Another relevant cache is the translation lookaside buffer, also called TLB, which contains a small number of entries. Its purpose is address translation and it is designed in a fully-associative way, and allows the processor to do a fast lookup on recent entries. [She13]

#### 2.2. Performance Monitoring on the Hardware-Level

This section focuses on analyzing programs by using different techniques modern processors provide. In order to collect performance-related data, such as the number of cycles or cache misses in a program run, the processor has a dedicated hardware component called a performance monitoring unit (PMU). These low-level metrics are made available as events by the PMU and can then be analyzed by profiling tools such as PERF\_Events, Intel VTune, or AMD µProf. [Kuk15] The following subsections focus on different evaluation methods utilizing the PMU.

#### 2.2.1. Hardware Performance Counters

Performance monitoring counters (PMCs) are special registers in the PMU that increment their value when certain hardware events occur in the processor pipeline or other parts of the computer. They can also measure the duration of certain events. [AMD10] The CPUID instruction register provides information about supported features by each CPU. Other sources for finding the available events are Intel® 64 and IA-32 Architectures Software Developer's Manuals [Int23a], AMD's BIOS and Kernel Developer's Guide (BKDG) [AMD10, AMD11, AMD16], AMD's Processor Programming Reference (PPR) [AMD20, AMD21, AMD23c] and Intel's online documentation for performance monitoring events [Int23b].

Performance counters vary in the degree of software configuration and their event sources. Common are programmable counters that can select an event in software. This approach is ideal for letting the user choose a small subset of events. Modern processors have thousands of available metrics. Programmable counters are usually distributed across the pipeline to be closer to the source of the performance metrics. The locality of the counters and the complexity of wiring the counters to the information sources set limitations in the event selection of the programmable counters, some counters might only be able to record cache events, and others are limited to branch speculation events. Configuring one programmable counter requires a certain event code that activates the necessary logical unit and an umask that allows filtering events. Modern AMD and Intel x86 processors usually offer four to eight programmable counters per core. [AMD23b, Int23a]

The opposite of a programmable counter is the fixed-function counter. It continuously monitors one specific event. Suitable events for fixed-function counters are metrics regularly used in monitoring programs. Implementing these metrics in dedicated hardware, it allows the user to use the programmable counters for other purposes. Fixed-function counters on Intel systems record important metrics such as instructions retired, the number of unhalted core cycles, or the number of unhalted reference cycles. [Kuk15]

Depending on the microarchitecture, there might also be additional counters collecting information not related to a single processor core. Uncore refers to shared resources outside of the processor core. One example is the shared L3 cache. An uncore PMU is available on Intel and AMD processors. [AMD23c, Int23a, Kuk15] AMD also uses northbridge event as another name for uncore event. [Wea17]

The Intel Core 13th generation Intel Core processors are hybrid processors using a combination of performance cores and more efficiency-oriented cores, called P-core and E-core, respectively. The P-cores are based on the Golden Cove microarchitecture and offer three fixed-function counters and eight programmable counters per thread for the P-cores. There are some differences in the E-cores based on the Gracemont microarchitecture compared to the larger P-cores. They have no Hyperthreading support and cannot run two threads on one core. Additionally, the amount of programmable counters has been reduced to six.

The microarchitecture specifies which events are supported in the PMU. Intel separates events into two classes: Architectural events define metrics available across multiple microarchitectures and have the same or at least a similar specification. These types of events only relate to a small subset of events. Non-architectural events with metrics exclusive to a specific microarchitecture are the more common class. The disadvantage of non-architectural events is the missing guarantee of existence in future processor generations. [Int23a]

Compared to Intel, AMD has a similar configuration to offer for its PMC implementation. According to the AMD64 Architecture Programmer's Manual, all implementations have at least four core performance counters. The processor has special registers that indicate additional core performance counters, cache event counters, and support for other event types.. [AMD23b] The current Zen 4 microarchitecture has six core performance event counters per thread, six performance events counters per L3 complex, and sixteen Data Fabric performance events counters related to DRAM access metrics. [AMD23c] Detailed event codes are described either in the Processor Programming Reference (PPR) [AMD20, AMD21, AMD23c] or in the BIOS and Kernel Developer's Guide (BKDG) for older microarchitectures. [AMD10, AMD11, AMD16]

#### 2.2.2. Event-Based-Sampling

Event-based-Sampling is a statistical profiling technique that takes performance metrics in regular intervals of a program run. The sampling interval is decided by a dedicated counter that increases after each cycle. Suppose the counter reaches a certain threshold or a counter overflow occurs. In that case, the PMU interrupts the program execution and collects information about the current program state from the related hardware counters and related MSRs. The CPU creates samples containing data from PMUs and usually stores the data in the file system for analysis. The interval between the two samples depends on the implementation. It might be defined by the number of cycles or given as a period in milliseconds. This statistical profiling technique allows more fine-grained information gathering than simple hardware counters due to the increased amount of data. Furthermore, certain implementations make it possible to link the event sample to a specific part of the program. By aggregating the samples for each part of the program, the overview helps to find potential bottlenecks indicated by relatively many samples.

However, in non-precise interrupt routines, there is a problem in the data collection process. Until the interrupt arrives at the event source and initiates the data collection for a specific instruction, the pipeline might have moved forward, and the PMU receives information about an instruction executed a few cycles later. This delay between the request for the information and receiving an answer is called skid. [Int23a,  $W^+16$ ] Large skid values lead to a disconnect between the event samples and the instruction that caused this program state. Therefore, having either no or a very low skid is desirable while sampling applications. Section 2.3 and Section 2.4 cover vendor-specific solutions for reducing skid.

#### 2.3. Intel Processor event-based sampling (PEBS)

The Intel Pentium processors introduced model-specific registers (MSRs) as performance monitoring counters supporting non-precise data collection. Only later, the Intel NetBurst processors implemented the more precise monitoring feature, Processor event-based sampling (PEBS), to reduce skid. [Int23a] Sometimes, PEBS is incorrectly written as Precise event-based sampling due to its purpose to remove the latency between issuing the data collection for a specific instruction and retrieving the related information from the processor pipeline. [Kuk15, W<sup>+</sup>16] Significant delays could lead to incorrectly fetched values related to instructions issued a few cycles later. These special counters can be configured to select specific processor performance parameters, which are then monitored to tune the system and improve compiler performance. [W<sup>+</sup>16]

Since the Intel NetBurst microarchitecture, the processor has a debug store (DS) save area that collects information in a memory-resident buffer for further processing by debugging and profiling tools. It stores PEBS records and branch trace store records (BTS). BTS records are another type of information separate from PEBS, and they record traces about taken branches, occurring interrupts, and exceptions to determine how a certain code location has been reached. [Int23a]

Across several microarchitecture generations, Intel improved PEBS by adding more selectable events and introducing architectural events in the Intel Core Solo and Intel Core Duo generation. Architectural events, such as unhalted core cycles or instructions retired, refer to metrics available across several microarchitectures. Unfortunately, most available events belong to the group of non-architectural events, processor generation-specific metrics. A disadvantage is the missing portability across several generations and the increased workload to configure events in profiling tools. Besides introducing architectural events, several extensions of the PEBS have been implemented to improve other aspects of the data collection. To reduce the skid problem, the processor can signal an imminent counter overflow and improve trapping the correct value upon the moment of the actual data collection across all pipeline stages (Precise Distribution of Instructions Retired). Allowing the selection of non-precise events with the feature extended PEBS since Icelake makes it possible to choose from a broader range and combinations of events utilizing PEBS. [Int23a]

#### 2.4. AMD Instruction-Based Sampling (IBS)

Instruction-based sampling (IBS) is a solution by AMD and has been implemented in their processors since 2007, introduced with the AMD Family10h processors "Barcelona" (AMD Opteron Quad-Core processor). It is a statistical method and an implementation reducing skid, providing precise program performance information similar to Intel PEBS. [Dro07]

For IBS, the data collection can collect information about the front- or back-end of the instruction pipeline. These events are called IBS Fetch and IBS Op, respectively. Each IBS event type has its own model-specific registers (MSRs). These can be control registers containing the counter triggering an interrupt upon an overflow, configuration parameters, or data registers with the values collected from the pipeline. Compared to PEBS, the provided data is bound to the IBS event type and the processor specification and cannot be customized like programmable hardware counters with thousands of selectable events.

IBS has been officially supported by perf\_event since kernel version 3.2 [Gre21], but some implementation details make it more difficult to use than Intel's PEBS solution. Currently, monitoring in a per-process mode is impossible and instead requires the selection on a per-CPU basis. Besides the Linux kernel requirement, AMD systems could utilize perf\_events correctly if the event source is configured correctly. Existing folders at /sys/bus/event\_source/devices/ibs\_fetch and /sys/bus/event\_source/devices/ibs\_op indicates sampling support.

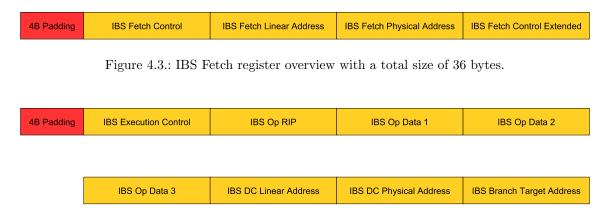

#### 2.4.1. IBS Fetch

This event type provides data related to the pipeline's instruction decoding and instruction fetch phases. The control register Core::X86::Msr::IBS\_FETCH\_CTL contains 16 bits of the internal 20-bit counter, the maximum count value of the counter, values, and flags related to the tagged fetch operation. Values such as instruction fetch latency and instruction cache L1TLB page size require multiple bits. Flags need one bit and define events describing metrics from the pipeline like L2 cache miss, instruction cache misses, or providing configuration settings about IBS Fetch. One such setting in IBS Fetch is the flag IbsRandEn which defines whether the last four bits of the fetch counter are randomized or not when starting the fetch counter. This behavior is desirable for cases where periodic instruction fetches might result in repeatedly sampling the same instruction in a computational loop. With the randomizing of the fetch counter, this pattern might be avoided, and the following sample could be related to a different instruction.

Not only the 64-bit control register belongs to the IBS Fetch MSR-registers, there are two additional 64-bit registers called Core::X86::Msr::IBS\_FETCH\_LINADDR and Core::X86::Msr::IBS\_FETCH\_-PHYSADDR containing the virtual 64-bit address and the 48-bit physical address. Sometimes, the control register indicates an invalid physical address with the IbsPhyAddrValid field set to zero.

The last register belonging to IBS Fetch is the extended control register with one single 16bit field. This metric measures the number of cycles when the fetch engine is stalled for an ITLB reload for the sampled instruction fetch. If there is no reload, then the value is zero. Microarchitectures before the AMD Zen generation (AMD Family 17h) do not have this register [AMD10, AMD11, AMD16] and therefore it is recommended to check the feature set of the processor with the CPUID command before sampling with IBS Fetch.

#### 2.4.2. IBS Op

IBS Op provides information about the backend of the instruction pipeline. Therefore event samples are generated for tagged macro operations instead of instructions as sampled by the IBS Fetch sample type. Like IBS Fetch, the event type IBS Op has its own control register Core::X86::Msr::IBS\_OP\_CTL with a 27-bit internal counter and fields for the sampling configuration. The following register Core::X86::Msr::IBS\_OP\_RIP contains only the linear address of the tagged macro-operation. Four additional registers Core::X86::Msr::IBS\_OP\_DATA to Core::X86::Msr::IBS\_OP\_DATA3 capture detailed information about the marked macro operation. These metrics describe the operation type, TLB metrics, and data cache latencies related to this event. Some fields have conditions for their validity. Examples are the fields taken branch op and mispredicted branch op, which contain relevant data when the condition branch op retired is set to one. Another case is the register Core::X86::Msr::IBS\_OP\_DATA2, which includes data source fields and is only valid for load operations without any hits in the L1 data cache or L2 cache.

The next registers Core::X86::Msr::IBS\_DC\_LINADDR and Core::X86::Msr::IBS\_DC\_PHYSADDR might contain the linear and physical address for the tagged load or store operation. The validity depends on the flags IbsDcLinAddrValid and IbsDcPhyAddrValid given by the IBS Op Data 3 register. Besides these two addresses, there is an additional field IbsBrTarget for branch operations specifying the logical address for the branch target. This register has been implemented since AMD Family 12h [AMD11], and the CPUID instruction register indicates the feature support.

Most fields have existed since the first microarchitecture implementing IBS, but there have also been modifications to IBS Op since its existence. Minor changes have been implemented over several microarchitectures adding, renaming, or removing fields in the register. A few bits in the registers are marked as reserved for future usage. Therefore it is possible to add new metrics to the event type without needing a new register for IBS. The latest Zen 4 microarchitecture uses two previously reserved bits in the OP Data 2 register to extend the DataSrc field by two additional bits, increasing the total size to four bits. Increasing the existing entry size allows a more precise evaluation of load operation samples. [AMD23c]

In the AMD Family 15h generation, IBS has introduced the OP Data 4 register to store a single bit of information in the field IbsOpLdResync. However, AMD has decided to revert the change in the following generation by removing the register and not storing this particular

information in any other register. [AMD18]

#### 2.5. OpenMP and OMPT

OpenMP is suitable for implementing parallel applications using a shared-memory model. Due to its portability and scalability, it is possible to execute applications on platforms such as embedded systems, multicore systems, and even hardware accelerators. The standard is controlled by the architecture review board (ARB). Members are CPUs and GPU vendors, research laboratories, universities, OEMs, and other companies supporting the standard. [Ope23]

To use first-party tools with OpenMP-applications, OpenMP provides the OMPT-interface with mechanisms to initialize the tool and examine the OpenMP state of OpenMP threads. The tool can receive notifications of OpenMP events from the OpenMP application by implementing callback functions. It is also possible to monitor the activity on OpenMP target devices or to evaluate implementation-specific details of an OpenMP application.

OpenMP version 5.0 introduced the new interface OMPT support in November 2018. [Ope18] The LLVM/clang compiler version 16.0 supports most OpenMP 5.0 features, and the OMPT interfaces are considered "mostly done" according to the documentation. [Cla23] However, OMPT is still not supported on all compilers. The GCC 13 compiler still lacks the OMPT interface support and a few other OpenMP 5.0 features. [GCC23]

A tool implementing the OMPT-interface must declare and implement the initialization function <code>ompt\_start\_tool()</code>. This function defines a struct of the type <code>ompt\_start\_tool\_result\_t</code> and requires two functions usually called <code>ompt\_initialize()</code> and <code>ompt\_finalize</code>. The type definition are specified in the header file omp-tools.h and requires the availability of the OMPT-interface. These functions are called before the OpenMP-application starts and after the program has terminated. The defined struct is then returned by the <code>ompt\_start\_tool()</code> function. Linking the tool to an OpenMP-application works by compiling the tool and either linking it statically to the OpenMP-program or linking it to the application by specifying the environment variable OMP\_TOOL\_LIBRARIES with the path of the library. [Ope18]

#### 2.6. MPI and PMPI

The Message Passing Interface (MPI) is a message-passing library interface specification first published in 1994 and designed for parallel and distributed programming purposes. The goal of MPI is the development of a standard for message-passing applications with a focus on portability, efficiency, and the establishment of a flexible standard for message passing. All MPI operations are defined as functions, subroutines, or methods with the appropriate programming language bindings. The bindings for C and Fortran are part of the MPI specification. [Mes21] The application runs on MPI nodes and might be distributed across multiple machines. Therefore, the communication between nodes is more complex than OpenMP and requires communication via messages. MPI provides functions for sending and receiving data. Examples are MPI\_Send, MPI\_Recv, and MPI\_Bcast.

MPI has a profiling interface called PMPI for profiling tools. The MPI functions can be called

with either the MPI\_ or the PMPI\_ prefix. For example, the profiling tool could implement its own MPI\_Init() function in which it calls PMPI\_Init(). This approach allows the tool to keep the original MPI behavior as intended and additionally perform its own tasks. The original MPI application then uses the re-implementation from the tool.

## 3. Description of Tools

This work is about the profiling tool Mitos and its implementation of IBS. The data collection of IBS samples uses the perf\_event profiling interface of the Linux kernel. Related to Mitos is the Visualization Tool MemAxes, which uses the post-processed data from Mitos as input data. Currently, it is designed to display information about PEBS. Both tools were originally developed by Alfredo Gimenez at the Lawrence Livermore National Laboratory and are distributed under the Apache-2.0 license with the LLVM exception. [Gam15] The following work covers modified versions of both tools from the Chair of Computer Architecture and Parallel Systems at TUM. The last part of this chapter covers the systems used in this work.

#### 3.1. The Tool Perf\_Event

The tool perf began as part of the Linux subsystem for utilizing CPU performance counters. In later versions, it also supported tracepoint events, kprobes, and uprobes. This tool is also known under the names perf\_events, Performance Counters for Linux (PCL), or Linux perf events (LPE). As part of the Linux kernel, perf\_event is included under tools/perf. Perf\_events is a lightweight profiling tool and provides many configuration options as a command line tool and via the perf\_event\_open() system call. Despite the deep integration into the Linux system and the importance of its functionality, the official documentation [Lin23] does not provide much information about implementation details. Some additional sources related to perf\_events are Brendan Gregg's perf website [Gre23] and Vince Weaver's unofficial perf\_events website [Wea23].

#### 3.1.1. The CLI of Perf\_Event

Table 3.1 shows common options that the perf\_event command line tool provides. Perf\_event is quite helpful for performing a Top-Down Analysis [per22, Yas14], an approach to discover software performance bottlenecks. For this purpose, the command perf stat collects hardware event counters and tries to identify the bottleneck type. After identifying the general bottleneck type with hardware counters, the perf record command takes event samples containing data related to the bottleneck type during the program run, and perf report analyzes which specific functions are the related bottlenecks.

| 3. | Description | of | Tools |

|----|-------------|----|-------|

|----|-------------|----|-------|

| perf_event command | Description                                   |

|--------------------|-----------------------------------------------|

| perf stat          | Collect performance counter statistics        |

| porf record        | Record events for reporting and write to file |

| perf record        | perf.data                                     |

| nouf von out       | Read file perf.data and display event samples |

| perf report        | by process, function, etc.                    |

| norf annotato      | Read file perf.data and annotate assembly or  |

| perf annotate      | source code with event counts                 |

| perf top           | Display live event counts                     |

| perf bench         | Run different kernel microbenchmarks          |

|                    | 1                                             |

Table 3.1.: Overview of common perf\_event commands.

Data mainly taken from: https://perf.wiki.kernel.org/index.php/Tutorial

To configure perf\_event to collect the correct data, the command perf record has various parameters for customizing the profiling routine. The flag -e specifies the PMU event, and some common options are available with the command perf list and not vendor-specific metrics. Specifying raw events from processors or features such as IBS Fetch or IBS Op is also possible. Besides the event selection, parameters might specify recording in a per-thread, per-process, per-CPU, or system-wide monitoring mode. Also relevant for the data collection routine is the correct choice for the event sample period that is adjustable with the -c flag. Shorter event periods are helpful for collecting enough data in shorter program runs, but there are also disadvantages. Lower sample periods in more extended program runs lead to large record files and may not be necessary for a sufficient analysis. Additionally, the overhead from the profiling tool increases with the higher frequency of interrupt routines caused by the data collection. An overview of perf record parameters is available in Table 3.2. [per23a]

| perf record $\operatorname{Flag}$ | Description                                                    |

|-----------------------------------|----------------------------------------------------------------|

| -a                                | System-wide monitoring mode                                    |

| -C                                | Per-CPU monitoring mode and requires a list of core ids        |

| -с                                | Event sample period                                            |

| -е                                | Event selection                                                |

| -р                                | Per-process monitoring mode with pid value                     |

| -t                                | Per-thread monitoring mode with tid value                      |

|                                   | Verbose command line output providing errors and configuration |

| -V, -VV                           | of internal states and the perf_event_open() system call       |

Table 3.2.: Overview of perf record parameters. [per23a]

#### 3.1.2. The perf\_event\_open() System Call

Before the perf\_event\_open() system call happens, it needs to know which event must be monitored, the selected sampling frequency, and many other settings. The system calls requires a parameter with type perf\_event\_attr, and the type definition is available in the header file perf\_events.h from the perf\_event tool and part of the Linux kernel. One important field in the perf\_event\_attr struct is the attribute type that specifies which kind of event is selected. The documentation defines following constants:

- PERF\_TYPE\_HARDWARE

- PERF\_TYPE\_SOFTWARE

- PERF\_TYPE\_TRACEPOINT

- PERF\_TYPE\_HW\_CACHE

- PERF\_TYPE\_RAW

- PERF\_TYPE\_BREAKPOINT

- Dynamic PMU

For example, PERF\_TYPE\_HARDWARE and PERF\_TYPE\_SOFTWARE are constants from perf\_event for common events available on systems regardless of the vendor. Events from the *Dynamic PMU* type are available depending on the system, and a hint about supported events gives the subdirectory /sys/bus/event\_source/devices. This directory contains folders specifying PMU instances. [per23b]

Two other relevant parameters besides the type field are the attributes sample\_type and precise\_ip. The sample\_type defines which information is present in the event sample. Each bit in the sample\_type field corresponds to a specific field, and setting the bit to 1 enables the collection. Table 3.3 shows most relevant fields for the perf\_event configuration in Mitos. The other attribute precise\_ip is relevant for enabling precise sampling with PEBS or IBS. The attribute accepts values between 0 and 3. 0 is for non-precise data collection, and higher values require more precise sampling conditions.

| <pre>sample_type Constant</pre> | Description                                                  |

|---------------------------------|--------------------------------------------------------------|

| PERF_SAMPLE_IP                  | Records the instruction pointer                              |

| PERF_SAMPLE_TID                 | Records the pid and tid                                      |

| PERF_SAMPLE_TIME                | Records a timestamp                                          |

| PERF_SAMPLE_ADDR                | Records an address, if applicable                            |

| PERF_SAMPLE_CPU                 | Records CPU number                                           |

| PERF_SAMPLE_RAW                 | Records raw data (such as IBS register fields) if applicable |

Table 3.3.: Overview sample\_type field. [per23a]

The system call also needs additional parameters for the fields pid, cpu, group\_fd, and flags. Combinations of the fields pid and cpu determine the monitoring mode. The system call supports running in the per-CPU mode on a specific processor core or in a per-process mode returning event samples for a given pid. The per-CPU mode refers to the monitoring of one logical core as seen by the operating system, and in perf\_event, the numbering of the core ids starts at zero. The system call returns on success an integer specifying the file descriptor, which is used for setting up mmap buffers and collecting perf\_event data from the PMU of the processor. Not only memory needs to be configured, but also signal handlers that write the data from the mmap buffer to disk when a buffer overflow occurs. After everything has been configured, an ioctl() command starts the sampling routine, and another ioctl() command is used to stop the perf\_event routine.

#### 3.2. Mitos

The tool Mitos allows profiling of applications utilizing Intel PEBS. Sampling with PEBS enables perf\_event to monitor applications by specifying the pid. There are two entry points to Mitos: The first one is Mitosrun and works as a command line tool that requires the executable path, configures the sampling routine, interacts profiling with Mitos, take event samples and write them to disk while the application runs and postprocesses the sample data after the monitored program has terminated. The second entry point is Mitoshooks and is specially designed for MPI-applications running on several different nodes. In this case, each node runs its own Mitos instance with preprocessing, sampling and postprocessing. Due to its strict separation between nodes, each process creates its own result folder containing hardware specifications and event sample data. This means the results from one MPI application run still require a manual merging of the data and is a feature desirable to be implemented within Mitoshooks.

Mitos has a few requirements such as CMake, OpenMP, MPI, Dyninst and hwloc. OpenMP and MPI dependencies are necessary for profiling applications requiring using one of these interfaces. Dyninst is used for matching perf\_event samples and their related instruction in the source code. Finally, the hwloc dependency is used in the initial phase of Mitos for collecting information about the hardware configuration of the system.

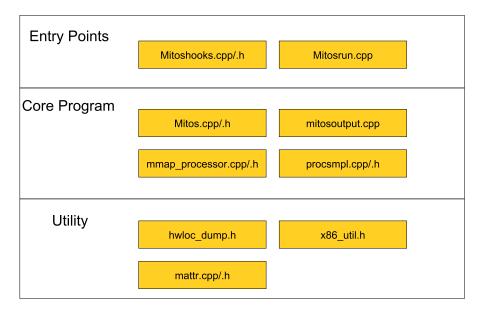

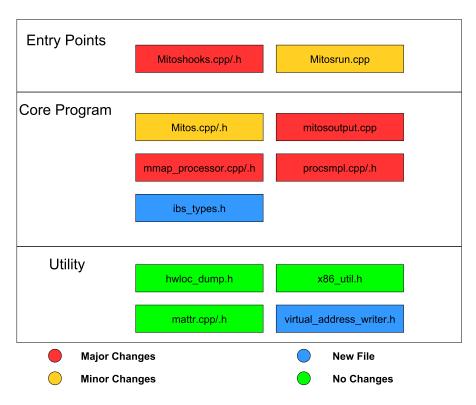

Figure 3.1.: Mitos Program Structure Overview.

Figure 3.1 shows the Mitos program structure. These files belong to either the utility functions, core program, or are entry points using Mitos. Utility files define helper functions used for interacting with the dependency hwloc in hwloc\_dump.h or in the post-processing routine on event samples such as mattr.cpp/.h and x86\_util.h.

Essential to Mitos are files from the core program. These files contain struct definitions used in the profiling tool's lifecycle, accessing the file system to read and write event sample data and hardware-related information (mitosoutput.cpp), functions to process raw event samples from perf\_event (mmap\_processor.cpp/.h) or provide an interface interacting with entry points (Mitos.cpp/.h). The core program and entry points interact in the pre- and post-process phases. The source file Mitos.cpp contains the implementation of most Mitos functions interacting with entry points and always start with the prefix Mitos\_, some of these functions are I/O related Mitos functions and are implemented in mitosoutput.cpp. Entry points need to specify values such as the event sample period, the pid of the profiled application, how to process event samples during the profiling phase, and other settings before the profiling begins. The last pre-processing step is starting the sampling process. After the profiled application terminates, the entry point signals Mitos to stop the profiling, initiate the post-process routine evaluating the collected raw samples, and terminate the profiling tool.

As mentioned, Mitos defines its own structures to handle event samples and its internal state. The struct definitions for event samples and data related to I/O operations are specified in Mitos.h. The struct perf\_event\_sample contains raw values returned by perf\_event and a few other processed values that are later written to disk for usage with MemAxes. The struct mitos\_output contains folder paths and file streams. It is first initialized in the pre-processing phase, collects hardware specification and topology with the help of hwloc, and initializes the raw\_samples.csv file for collecting perf\_event samples. During the profiling phase, mmap buffers are filled with perf\_event samples until they are full, then an interrupt signals Mitos to process the data and write it to disk. After the profiled application has terminated, Mitos transforms the raw data to its final state. Each line in the raw data is copied to the actual samples output file called samples.csv. Additionally, the instruction pointer value is used to find the source code's actual position and instruction with the Dyninst package's help and added to the result data of a perf\_event sample. So far, Mitos can only collect perf\_event samples with PEBS, and one goal of this work is to implement similar routines for AMD IBS.

The essential part of Mitos is configuring the perf\_event tool with the perf\_event\_open() system call, collecting and writing the samples to an output file, and finally stopping the profiling activity. The related data is stored in several different structs defined in procsmpl.h, the first one is called perf\_event\_container and stores information for one perf\_event\_open() system call. For Intel PEBS, there exists exactly one such struct at runtime, which collects performance data for one process on all threads of the system. The other structs procsmpl and threadsmpl store information for one process and a single thread, respectively. In the thread-related data, there is an array of perf\_event\_container which is initialized by the method call of Mitos\_init() and configures all requirements for perf\_event\_open().

#### 3.3. MemAxes

The visualization tool MemAxes uses output data from Mitos and displays data from event samples, primarily information about memory accesses. This tool requires CMake, Qt5, and VTK. The latest MemAxes version from the Chair of Computer Architecture and Parallel Systems at TUM also requires the sys-sage companion tool. [GV22] Sys-sage is a library currently under

development at TUM, and its purpose is to record and manipulate hardware topology information of compute systems. The library is licensed under LGPL-2.1 and available on spack or accessible via Github. [Van23]

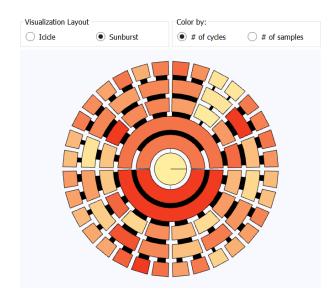

Besides the system requirements, MemAxes also requires sampling data. The current version works with Mitos results with samples using Intel PEBS. The plan is to extend the feature set with the support of AMD IBS event samples. Figure 3.2 shows a screenshot from MemAxes and a visualization of the hardware topology in a hierarchical structure. This hierarchy structure represents existing NUMA nodes and caches, and its coloring indicates the resource usage. [GV22]

Figure 3.2.: Hardware Topology Vizualisation in MemAxes. [GV22]

#### 3.4. Computation Platforms

Mitos has two entry points, Mitosrun, and Mitoshooks. On the one hand, Mitosrun is a profiling tool for general applications running on one or multiple threads. Thus, it is generally suitable for single-node applications. Mitoshooks, however, is designed to work with MPI programs and OpenMP applications. The support for MPI makes this suitable for profiling on MPI nodes and, therefore, compute clusters.

In this work, the focus lies on systems with an AMD processor. The first system is an AMD Zen 3 system and runs the evaluations in Section 4.3. It is a consumer system from the Ryzen 7-series with a modest amount of memory and eight cores with 16 threads. The second system is the time-x system, a single node in the CAPS cloud. CAPS cloud is a collection of servers, workstations, and other machines with highly configurable settings. Compared to the first system, it has double the amount of cores and threads but is from the previous Zen 2 generation. [CAP23] This system is relevant for testing the deployment in environments comparable to HPC systems with only limited administrative privileges. The CAPS cloud is a collection of servers, workstations, and other machines with highly configurable settings. Table 3.4 shows the hardware specifications

of both systems.

| Feature              | Zen 3             | time-x                                                     |

|----------------------|-------------------|------------------------------------------------------------|

| Number of Nodes      | 1                 | 1                                                          |

| Processor            | AMD Ryzen 7 5800X | AMD Ryzen Threadripper<br>PRO 3955WX 16-Cores<br>("Zen 2") |

| Cores per Node       | 8                 | 16                                                         |

| Threads per Core     | 2                 | 2                                                          |

| Base Frequency [GHz] | 3.8               | 3.9                                                        |

| L1-cache [KB]        | 512               | 1024                                                       |

| L2-cache [MB]        | 4                 | 8                                                          |

| L3-cache [MB]        | 32                | 64                                                         |

| RAM per Node [GB]    | 32                | 32                                                         |

Table 3.4.: Overview of the technical details of the used platforms. [CAP23]

# 4. IBS in Mitos

Implementing IBS requires a few considerations: The solution must run on various AMD systems, including future processors. A practical solution provides an extraction mechanism for IBS event samples, has official AMD development support, and accessible documentation. A suitable candidate is the profiling interface perf\_event that is available in the Linux kernel. This work focuses on how perf\_event and the system call perf\_event\_open() is used for collecting IBS data and analyzes the potentials and pitfalls of the current implementation. Furthermore, a dedicated part shows new Mitos features such as OpenMP in Mitoshooks, merging results from several folders, and writing virtual offsets to disk for the Dyninst analysis in the post-processing phase.

#### 4.1. IBS Event Sample Data Collection

There are several ways to collect IBS samples, suitable approaches seem to be software profiling analysis tool AMD  $\mu$ Prof, directly extracting data from IBS-MSRs and the profiling interface perf\_event integrated into the Linux kernel since version 2.6. Essential requirements are collecting event sample data, code portability, and low code change requirements for later IBS revisions. Aggregated data is insufficient as the tool MemAxes works on the actual event sample data.

The probably most user-friendly option to experience IBS is the tool AMD  $\mu$ Prof ("MICRO-prof") for x86 applications. There are versions available for Windows, Linux, and FreeBSD operating systems. Not only is the tool usable in a GUI without much difficulty, but it also offers CLI support and a variety of parameters to configure data collection and reporting. [AMD22] Despite its rich feature set, such as profiling analysis, system analysis, and energy analysis, it is unsuitable for Mitos and its purpose to supply event samples to the companion tool MemAxes. AMD  $\mu$ Prof can collect raw information and save them in binary form. Still, the data is only used for generating reports aggregating samples by their respective processes, threads, load modules, functions, and instructions. There is no documentation available on how to parse  $\mu$ Prof binary data to a Mitos-compatible samples output file.

The next option is to access the IBS-MSRs and extract the data directly. This concept is implemented in the AMD Research Instruction Based Sampling Toolkit Github repository by installing a special driver to extract IBS samples. [Gre21] The toolkit provides example programs collecting and processing IBS event samples. Also, some header files contain structure definitions specifying the correct order of the IBS attributes in the relevant registers. However, the author states it is only an experimental solution and does not recommend this approach in the long term. The author refers to the official AMD implementation in perf\_event should as a long-term solution.

The probably best option is to collect IBS samples with perf\_event due to its official support by AMD and the availability on modern linux systems. It allows to select either IBS Fetch or IBS Op

4. IBS in Mitos

| PROFILE SUMI      | MARY ANALYZE                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                           |                                                                                             |                                                                                                                                                                                                                                                                        |                                                                            |                                                                      |                                                                                |                                                                                                  |                       | ٠         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------|-----------|

| Function Hotspots | Select View All Events                                                                                                                                                                                                                                                                                                                                                  | ¥                                                                                                                                                                                                                                                                                                                  | Grou                                                                                                                                                      | p By Proces                                                                                 | s 💌                                                                                                                                                                                                                                                                    | Value Type E                                                               | event Count 🔹                                                        | Syste                                                                          | m Modules                                                                                        | Include Exclude       |           |

| Metrics           | Process                                                                                                                                                                                                                                                                                                                                                                 | IBS_TAG_TO_RET                                                                                                                                                                                                                                                                                                     | IBS_ALL_OPS                                                                                                                                               | IBS_FETCH                                                                                   | IBS_FETCH_KILLED                                                                                                                                                                                                                                                       | IBS_FETCH_ATTEMPT                                                          | IBS_FETCH_COMP                                                       | IBS_FETCH_ABORT                                                                | IBS_L1_ITLB_HIT                                                                                  | IBS_ITLB_L1M_L2H      | IBS_ITU   |

|                   | 🔽 matmul (PID 4045)                                                                                                                                                                                                                                                                                                                                                     | 4517286                                                                                                                                                                                                                                                                                                            | 51683                                                                                                                                                     |                                                                                             | 133                                                                                                                                                                                                                                                                    | 17542                                                                      | 17538                                                                |                                                                                | 4 0                                                                                              |                       |           |

| ліх               | <ul> <li>Load Modules</li> </ul>                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                           |                                                                                             |                                                                                                                                                                                                                                                                        |                                                                            |                                                                      |                                                                                |                                                                                                  |                       |           |

|                   | matmul                                                                                                                                                                                                                                                                                                                                                                  | 4498188                                                                                                                                                                                                                                                                                                            | 51494                                                                                                                                                     | 17558                                                                                       | 120                                                                                                                                                                                                                                                                    | 17438                                                                      | 17434                                                                | 4                                                                              | 4 0                                                                                              |                       | )         |

|                   | libc.so.6                                                                                                                                                                                                                                                                                                                                                               | 18358                                                                                                                                                                                                                                                                                                              | 139                                                                                                                                                       | 92                                                                                          | 12                                                                                                                                                                                                                                                                     | 80                                                                         | 80                                                                   |                                                                                | 0 0                                                                                              |                       | )         |

|                   | libgomp.so.1.0.0                                                                                                                                                                                                                                                                                                                                                        | 641                                                                                                                                                                                                                                                                                                                | 48                                                                                                                                                        | 25                                                                                          |                                                                                                                                                                                                                                                                        | 24                                                                         | 24                                                                   |                                                                                | 0 0                                                                                              |                       |           |

|                   | ld-linux-x86-64.so.2                                                                                                                                                                                                                                                                                                                                                    | 99                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                           | 0                                                                                           |                                                                                                                                                                                                                                                                        |                                                                            | 0                                                                    | (                                                                              | 0 0                                                                                              | C                     | )         |

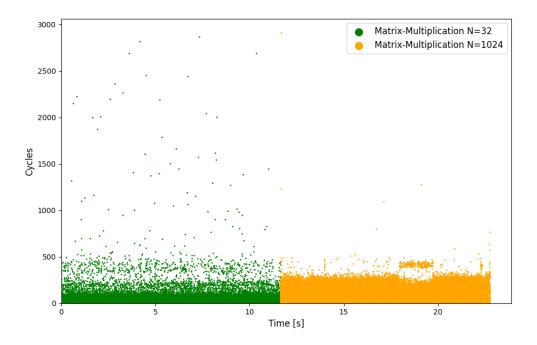

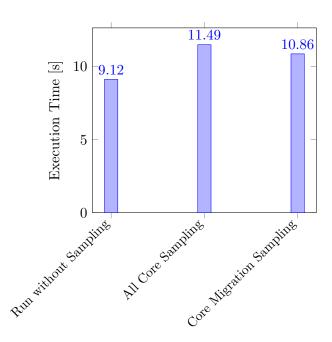

|                   | ▼ Threads                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                           |                                                                                             |                                                                                                                                                                                                                                                                        |                                                                            |                                                                      |                                                                                |                                                                                                  |                       |           |