Technische Universität München TUM School of Computation, Information and Technology

# Model-based Generation of Highly Configurable RTL Designs

Johannes B. Schreiner

Vollständiger Abdruck der von der TUM School of Computation, Information and Technology zur Erlangung eines

Doktors der Ingenieurwissenschaften (Dr.-Ing.)

genehmigten Dissertation.

Vorsitz:

Prof. Dr.-Ing. Ralf Brederlow

Prüfer\*innen der Dissertation:1.Hon.-Prof. Dr.-Ing. Wolfgang Ecker2.Prof. Dr.-Ing. Robert Wille

Die Dissertation wurde am 24.04.2023 bei der Technischen Universität München eingereicht und durch die TUM School of Computation, Information and Technology am 23.11.2023 angenommen.

# Acknowledgements

This research has been made possible by Infineon Technologies AG and the EDA Chair at Technical University of Munich. I would like to express my sincere gratitude for the opportunity to conduct research with them.

Above all else, I would like to thank Prof. Dr.-Ing. Wolfgang Ecker for his constant support, guidance, and valuable inputs – not only throughout my work on this thesis but also during my entire career at Infineon. Despite his busy schedule, he was always available for thoughtful discussions, creative ideas, and valuable feedback. In countless meetings and alignments, he pushed me in the right direction and exhibited incredible patience. I deeply value his ability to motivate and push me by showing true appreciation and enthusiasm for my work and results. If there is one thing that I hope to learn from him and be able to carry forward through my professional life, it is this ability to motivate and drive others by feeling and showing the same honest fascination and appreciation for their work. Without his patience, persistence, and encouragement I would have never been able to come to these results. I am aware of how extraordinary the opportunities that he opens up to me are and I cannot express how thankful I am. I will do my best to make sure that my future contributions at Infineon Technologies AG provide a return on his investment.

Further, I want to thank my mentor Prof. Dr.-Ing. Ulf Schlichtmann. I am very thankful that he decided to mentor me personally and I want to express my deepest gratitude for his feedback and the essential support that helped me finalize this work.

A special thank you goes to all the students who contributed key elements to the development and research conducted as part of this thesis: Felix Willgerodt, Bastian Koppermann, Yurun Wu, Andreas Neumeier, and Vasundhara Raje Gontia. I would also like to thank all Ph.D. candidates who based their work on the foundations set by this thesis and all Infineon employees working in the Infineon Metamodeling Group. They evolved the interpretation of the MDA flow developed in this thesis into what came to be Infineon's MetaX initiative. In this context, I want to particularly mention Keerthikumara Devarajegowda, Stefan Gerstendörfer, Paritosh Kumar Sinha, Andreas Neumeier, and Christian Lück who offered their guidance, support, and honest opinions. The motivation their feedback provided is invaluable to me. I also want to thank Sebastian Prebeck and Michael Werner – their Ph.D. work has inspired, guided, and motivated me. My special thank you for all the insightful and incredibly motivating conversations that allowed me to finalize this thesis.

A big thank you also goes to my line managers Jens Eckardt and Anshuman Anand for supporting me and providing the flexibility I needed to work on and finish this thesis.

Finally, I would like to thank my wife Ronja, my friends, and my family for the support and the distraction they offered me during the more challenging stages of my work on this thesis.

#### Abstract

The exponential growth in the capabilities of integrated circuits (ICs) has massively increased the complexity and cost of their development. To manage this complexity, a high degree of specialization, tool support, and reuse of intellectual property (so-called IP-reuse) between different integrated circuits are critical. Code generators can automatically provide artifacts for software and hardware development such as synthesis models on Register Transfer Level (RTL) or software code for device firmware. In areas where code generation can be applied, the replacement of manual coding with automated generation has shown significant productivity increases.

The applicability of code generation is limited by the complexity inherent in developing generators. This thesis provides a novel methodology for developing generators for digital hardware that significantly reduces the complexity of generator development and the cost of generator development along with it. The reduced complexity further facilitates the development of generator-based automation for digital design tasks which previously required manual work.

The new methodology is based on the vision of Model Driven Architecture (MDA) which has been developed in the field of software engineering and is successfully applied there. Model Driven Architecture aims to automate the generation of target views through a series of models with different levels of abstraction and Model-to-Model transformations that automatically provide more refined models from more abstract specification models and eventually automatically generate the final view.

This thesis adapts, transfers, and extends the vision of Model Driven Architecture for use in the field of digital hardware design. It identifies key Metamodels and Model-to-Model transformations and implements an end-to-end generation flow for digital designs. The framework developed in the context of this thesis puts particular focus on Metamodel-based automation to reduce the manual effort required to develop generators.

The new framework enables a shift from the development of static instances of digital hardware in hardware description languages such as SystemVerilog and VHDL to the development of highly configurable generators in a general-purpose software programming language. This thesis demonstrates how the capabilities of this general-purpose programming language and the MDAinspired modeling environment can be applied for generator reuse and to solve complex Systemon-Chip (SoC) infrastructure problems.

The results of this thesis are the foundation of MetaX, a full chip generation framework that is already used in a productive industrial context to automate chip design, verification, and embedded software development where it is able to reduce the overall development effort significantly.

| 1. | Intro | oduction                                                                                                                                                    | 15              |

|----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|    | 1.1.  | Growing Complexity of Integrated Circuits                                                                                                                   | 15              |

|    | 1.2.  | Management of Complexity in IC Design                                                                                                                       | 16              |

|    |       | Management of Complexity Through Generation                                                                                                                 | 17              |

|    | 1.4.  | Outline                                                                                                                                                     | 18              |

| 2. | Lang  | guages, Models, Metamodeling and Model Driven Architecture (MDA)                                                                                            | 21              |

|    |       | Evolution of Languages and their Productivity Impact                                                                                                        | 21              |

|    |       | 2.1.1. Software Programming Languages Generations                                                                                                           | 21              |

|    |       | 2.1.2. Mapping of Programming Language Generations to Digital Design                                                                                        | 23              |

|    |       | 2.1.3. Common Observations about Software and Hardware Languages                                                                                            | 24              |

|    | 2.2.  | Model-based and Language-independent Approaches                                                                                                             | 25              |

|    |       | 2.2.1. The Modeling Spectrum                                                                                                                                | 26              |

|    | 2.3.  | Metamodeling and Metamodeling-based Code Generation                                                                                                         | 28              |

|    |       | 2.3.1. Simple Code Generation without Metamodeling                                                                                                          | 28              |

|    |       | 2.3.2. Metamodeling Concept                                                                                                                                 | 29              |

|    |       | 2.3.3. Capabilities and Advantages of Metamodeling Frameworks for Code Gen-                                                                                 |                 |

|    |       | eration                                                                                                                                                     | 30              |

|    |       | 2.3.4. Application in Software Engineering                                                                                                                  | 32              |

|    |       | 2.3.5. Application in IC Design                                                                                                                             | 33              |

|    |       | 2.3.6. Limitations of Model-based Generation Approaches                                                                                                     | 34              |

|    | 2.4.  | Model Driven Architecture (MDA)                                                                                                                             | 36              |

|    |       | 2.4.1. The Model Driven Architecture Vision                                                                                                                 | 36              |

|    |       | 2.4.1.1. CIM, PIM, and PSM Models and Metamodels                                                                                                            | 36              |

|    |       | 2.4.1.2. Model-to-Model Transformations and Transformation Specifica-                                                                                       | 20              |

|    |       | $\operatorname{tions} \ldots \ldots$ | 38              |

|    |       | 2.4.2. Application in Software Engineering                                                                                                                  | 39              |

|    | 2.5.  | 2.4.3. Application in IC Design                                                                                                                             | $41 \\ 42$      |

|    | 2.0.  | Thesis Goal and Envisioned Approach                                                                                                                         | 42              |

| 3. |       | ted Work                                                                                                                                                    | 45              |

|    | 3.1.  | VHDL, Verilog, and SystemVerilog for Configurable Designs                                                                                                   | 46              |

|    |       | 3.1.1. Preprocessors                                                                                                                                        | $46 \\ 47$      |

|    |       | 3.1.2. Parametrization and Language Generation Constructs                                                                                                   | 47<br>48        |

|    |       | 3.1.3. Limitations                                                                                                                                          | $48 \\ 49$      |

|    | 30    | Enhanced Preprocessing and Script-based Generation                                                                                                          | $\frac{49}{50}$ |

|    |       | Embedded Domain-Specific Languages for Hardware Design and Generation                                                                                       | 50<br>51        |

|    | 3.4.  |                                                                                                                                                             | 53              |

|    | 0.4.  |                                                                                                                                                             | 00              |

|    | 3.5. | Synthesis-centric Languages as Embedded DSLs                                                                                                                       | 55         |

|----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|    |      | 3.5.1. Chisel and SpinalHDL                                                                                                                                        | 56         |

|    |      | 3.5.1.1. The Semantics of Chisel                                                                                                                                   | 57         |

|    |      | 3.5.1.2. Advantages and Limitations                                                                                                                                | 60         |

|    |      |                                                                                                                                                                    | 63         |

|    |      |                                                                                                                                                                    |            |

| 4. | Moo  | ·                                                                                                                                                                  | 65         |

|    | 4.1. |                                                                                                                                                                    | 65         |

|    | 4.2. |                                                                                                                                                                    | 68         |

|    |      | · · · ·                                                                                                                                                            | 68         |

|    | 4.3. | The Model-of-Design Layer and the MetaRTL Metamodel                                                                                                                | 70         |

|    |      | 4.3.1. Semantics of MetaRTL                                                                                                                                        | 70         |

|    |      | 4.3.2. The MetaRTL Metamodel                                                                                                                                       | 72         |

|    |      | 4.3.2.1. Compatibility with all Naming Conventions                                                                                                                 | 73         |

|    |      | 4.3.2.2. Registers $\ldots$                                                                                                                                        | 74         |

|    |      | $4.3.2.3. Memories \ldots \ldots$                         | 75         |

|    |      | $4.3.2.4.  \text{Primitives} \ldots \ldots$ | 76         |

|    |      | 4.3.2.5. Higher-level design patterns as MetaRTL Components                                                                                                        | 77         |

|    |      | 4.3.2.6. Compatibility and Hardmacro Components                                                                                                                    | 78         |

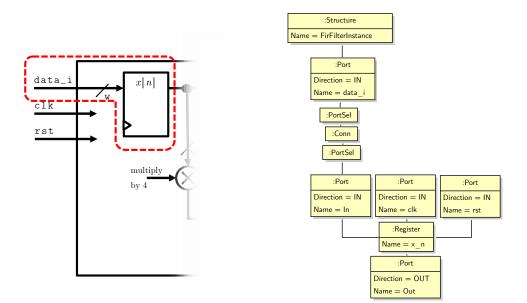

|    |      | 4.3.3. Sample MoD Layer for Digital Filters                                                                                                                        | 78         |

|    | 4.4. |                                                                                                                                                                    | 79         |

|    | 4.5. | • •                                                                                                                                                                | 82         |

|    |      |                                                                                                                                                                    | 83         |

|    |      | 4.5.1.1. Application Example                                                                                                                                       | 84         |

|    |      |                                                                                                                                                                    | 85         |

|    |      | 4.5.2.1. Usage in Expression Metamodel                                                                                                                             | 86         |

|    |      | 8                                                                                                                                                                  | 86         |

|    |      | 4.5.2.3. Usage as MetaRTL Primitive Components                                                                                                                     | 88         |

| _  | -    |                                                                                                                                                                    | ~ 1        |

| 5. |      | •                                                                                                                                                                  | <b>91</b>  |

|    | 5.1. |                                                                                                                                                                    | 92         |

|    |      |                                                                                                                                                                    | 92         |

|    |      |                                                                                                                                                                    | 95         |

|    |      |                                                                                                                                                                    | 95         |

|    |      | 5.1.4. Development Environment: Package, Dependency and Environment Man-                                                                                           | 07         |

|    | 5.0  | 0                                                                                                                                                                  | 97         |

|    | 5.2. | 8                                                                                                                                                                  | 99         |

|    | 5.3. |                                                                                                                                                                    | .02        |

|    |      | · 0 0                                                                                                                                                              | .03        |

|    |      |                                                                                                                                                                    | .03        |

|    |      |                                                                                                                                                                    | .08<br>.00 |

|    |      |                                                                                                                                                                    | .09        |

|    |      |                                                                                                                                                                    | .10        |

|    |      |                                                                                                                                                                    | .12        |

|    |      |                                                                                                                                                                    | .14        |

|    |      | 5.3.3.3. Flexible Support for Constructor Parameters                                                                                                               | 14         |

|              |          | 5.3.3.4. Library Routines for Efficient Connectivity                            | 115 |

|--------------|----------|---------------------------------------------------------------------------------|-----|

|              |          | 5.3.3.5. Automated Clock and Reset Connectivity                                 | 115 |

|              |          | 5.3.3.6. Object Property Propagation                                            | 115 |

|              |          | 5.3.3.7. Results                                                                | 116 |

|              |          | 5.3.4. Transformation of Model-of-Things Input Models                           | 117 |

|              |          | 5.3.5. The Language and Modeling Nature of the Template-of-Design               | 119 |

|              | 5.4.     | View Language Description and Automated View Generation                         | 120 |

|              |          | 5.4.1. The View Language Description Format                                     | 122 |

|              |          | 5.4.2. Target Code Indentation and Tabular Alignment                            | 125 |

|              |          | 5.4.3. Template-of-View Transformations                                         | 126 |

|              |          | •                                                                               |     |

| 6.           |          | lication and Subsequent Work                                                    | 129 |

|              | 6.1.     | Application of Generators in Commercial Designs                                 | 129 |

|              | 6.2.     | Architecture Exploration using MetaX                                            | 131 |

|              | 6.3.     | Subsequent Work                                                                 | 131 |

| _            | _        |                                                                                 |     |

| 7.           |          | erator IP-reuse and Automated Infrastructure Generation                         | 135 |

|              | 7.1.     | Detailed Problem Statement                                                      | 136 |

|              |          | 7.1.1. Limitation 1: Decentralized Handling of Infrastructure Needs             | 137 |

|              |          | 7.1.2. Limitation 2: Provisioning and Configuration of Infrastructure Resources | 140 |

|              | 7.2.     | Root Cause Analysis                                                             | 141 |

|              |          | 7.2.1. The Single-Pass Generator Pattern                                        | 141 |

|              |          | 7.2.2. Benefits of Single-Pass Generation                                       | 144 |

|              |          | 7.2.3. Multi-Pass Generation                                                    | 144 |

|              | 7.3.     | Implementation of Multi-Pass Generation                                         | 146 |

|              |          | 7.3.1. Definition of Interfaces for Communication between Generators            | 148 |

|              |          | 7.3.2. Application of the Dependency Inversion Principle                        | 148 |

|              |          | 7.3.3. Management of Multiple Passes                                            | 149 |

|              |          | 7.3.4. Resolution of Circular Dependencies                                      | 150 |

|              |          | 7.3.5. Example of a Multi-Pass ToD                                              | 151 |

|              | 7.4.     | Application and Results                                                         | 152 |

|              |          | 7.4.1. Key Achievements                                                         | 155 |

|              |          | 7.4.2. Challenges                                                               | 155 |

|              |          | 7.4.2.1. Adaptation to Software Thinking and Software Methodology .             | 155 |

|              |          | 7.4.2.2. Definition of Reusable and Stable Interfaces for Infrastructure        |     |

|              |          | Requests                                                                        | 156 |

| 0            | <b>C</b> | many and Kay Cantuibutiana                                                      | 157 |

| ð.           |          | mary and Key Contributions                                                      | 157 |

|              |          | Key Contributions                                                               | 157 |

|              | ð.2.     | Publications                                                                    | 160 |

| Bibliography |          |                                                                                 |     |

|              |          |                                                                                 |     |

# List of Figures

| 2.1.   | The Modeling Spectrum [23]                                                    | 26  |

|--------|-------------------------------------------------------------------------------|-----|

| 2.2.   | Model-centric generation of multiple outputs                                  | 27  |

| 2.3.   | Illustration of a simple, unstructured script-based generator                 | 28  |

| 2.4.   | Metamodeling, Hierarchies of Models as defined by OMG [21]                    | 29  |

| 2.5.   | Sample diagram of a Code Generation Framework based on Metamodeling           | 31  |

| 2.6.   | The Generator Gap in Simple Metamodeling Approaches                           | 34  |

| 2.7.   | Model Driven Architecture with its Model Transformations and Transformation   |     |

|        | Hierarchies as defined by OMG [23]                                            | 37  |

| 2.8.   | Y-Chart Visualization of Model Driven Architecture                            | 39  |

| ~ .    |                                                                               |     |

| 3.1.   | Hardware Models Generated by Chisel Listing 3.8                               | 58  |

| 3.2.   | Hardware Models Generated by Chisel Listing 3.9                               | 60  |

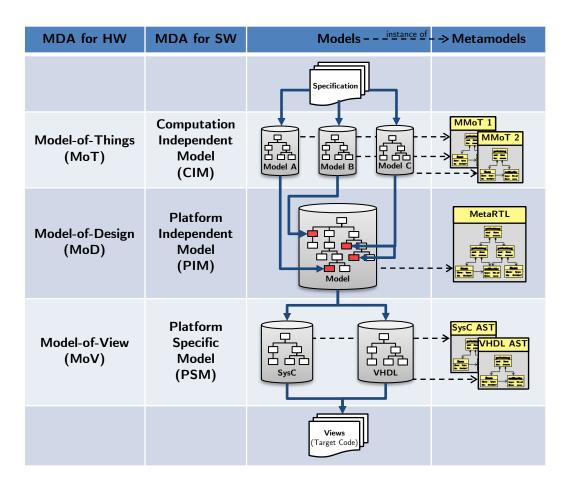

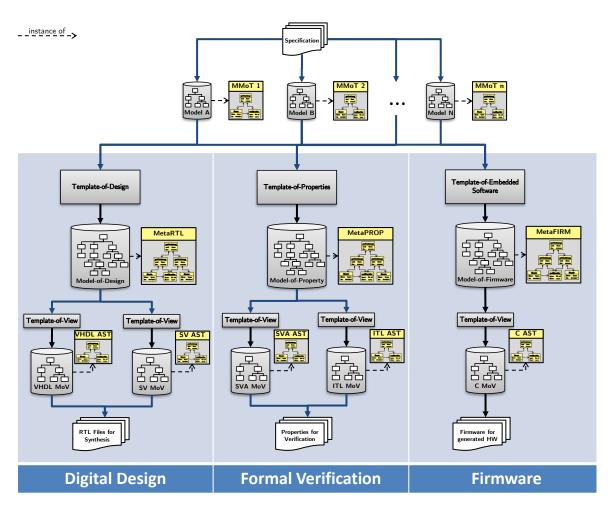

| 4.1.   | Abstraction Layers in MDA for Hardware Generation – Models and Metamodels     | 66  |

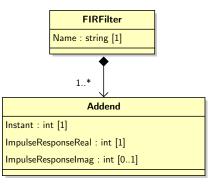

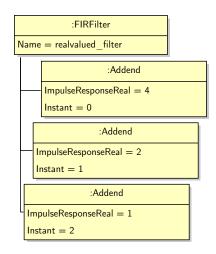

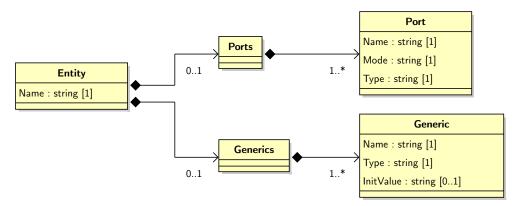

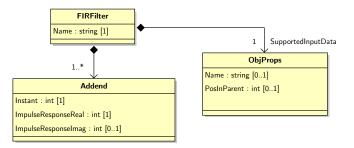

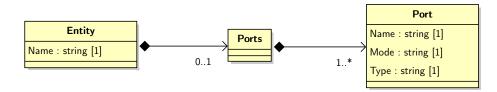

| 4.2.   | Metamodel-of-Things for an MDA-based generator for FIR Filters                | 69  |

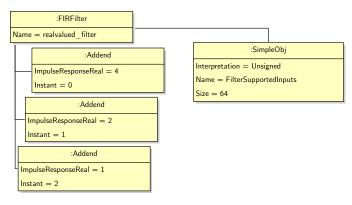

| 4.3.   | Example Model-of-Things instance of FIR Filter MMoT                           | 70  |

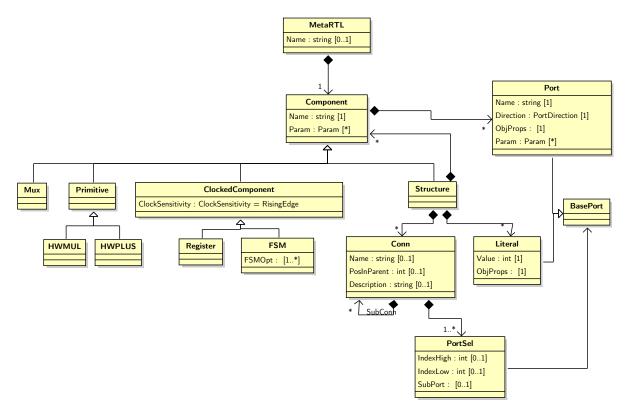

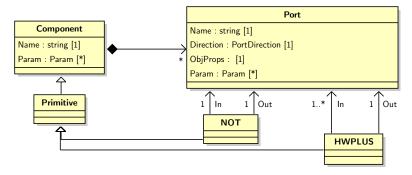

| 4.4.   | MetaRTL: Metamodel-of-Design (simplified)                                     | 72  |

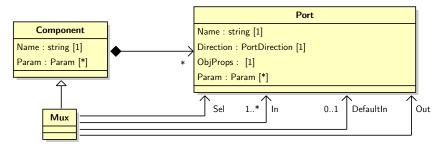

| 4.5.   | Mux Component with associations to describe Port roles independent of their   | . – |

| 1.0.   | names                                                                         | 73  |

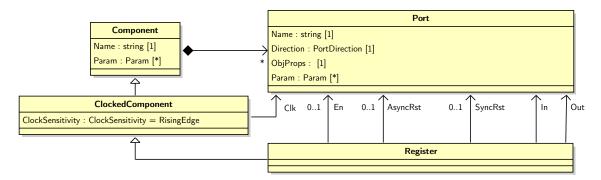

| 4.6.   | The MetaRTL Register Component                                                | 75  |

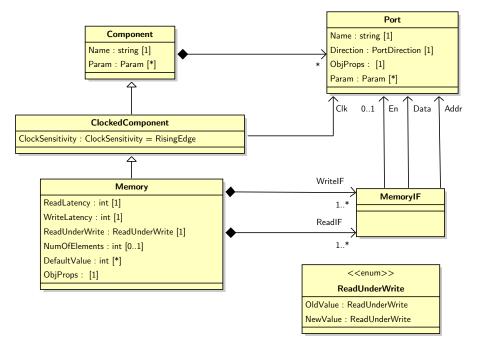

| 4.7.   | The MetaRTL Memory Component                                                  | 75  |

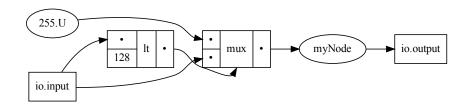

| 4.8.   | Two sample Expression Operands with their Mapping to Primitives               | 76  |

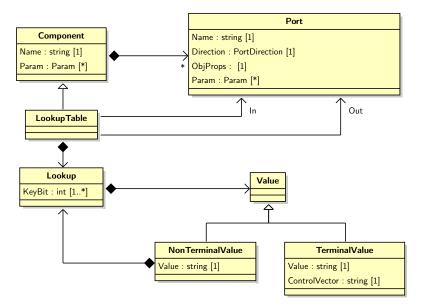

| 4.9.   | The MetaRTL Lookup Table                                                      | 77  |

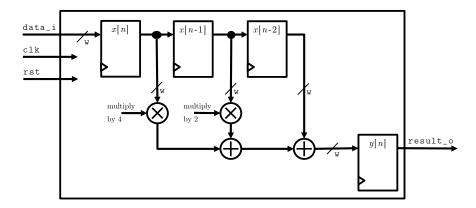

| -      | Block diagram of MoD generated from the MoT in Figure 4.3 without Clock and   |     |

| 1.101  | Reset Connectivity                                                            | 78  |

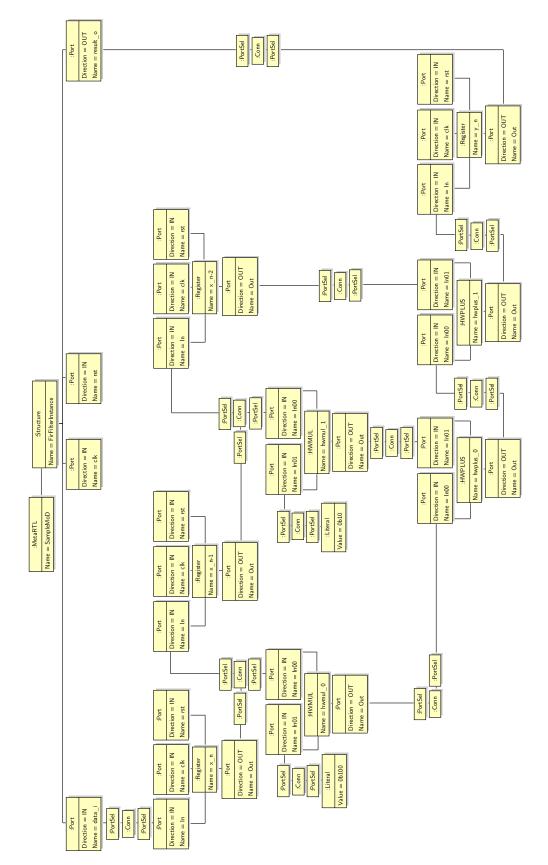

| 4 11   | MetaRTL MoD for Figure 4.10 without Clock and Reset Connectivity (simplified) | 80  |

|        | Small Subset of Model-of-View for VHDL                                        | 81  |

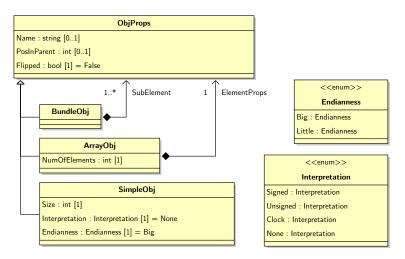

|        | Orthogonal ObjectProperties Metamodel                                         | 83  |

|        | Metamodel-of-Things for FIR Filters using the Orthogonal Object Properties .  | 84  |

|        | Model-of-Things for FIR Filters using the Orthogonal Object Properties        | 85  |

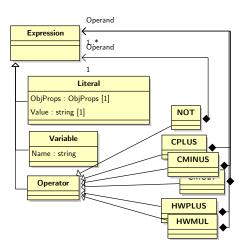

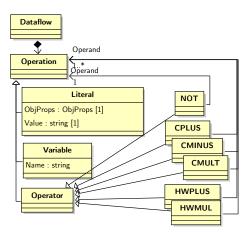

|        | Orthogonal Expression Metamodel with a subset of the available Operators      | 88  |

|        | Orthogonal Dataflow Metamodel with a subset of the available Operators        | 88  |

| 1.1.1. |                                                                               | 00  |

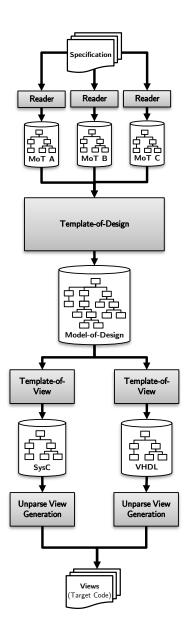

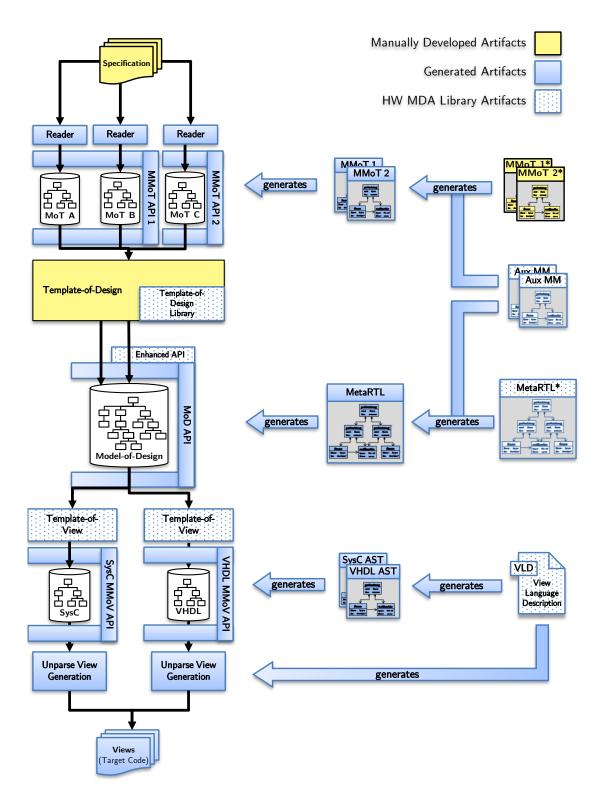

| 5.1.   | Readers, Model-to-Model Transformations and View Generation                   | 91  |

| 5.2.   | Abstraction Layers in MDA for Hardware Generation – Models and Metamodels     | 96  |

| 5.3.   | Abstraction Layers in MDA for Hardware Generation – Models and Metamodels     | 100 |

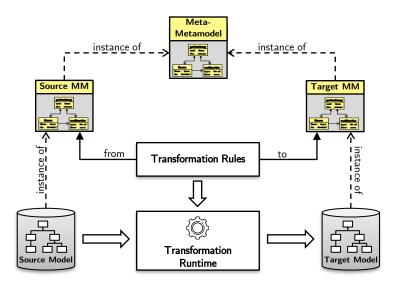

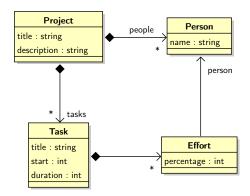

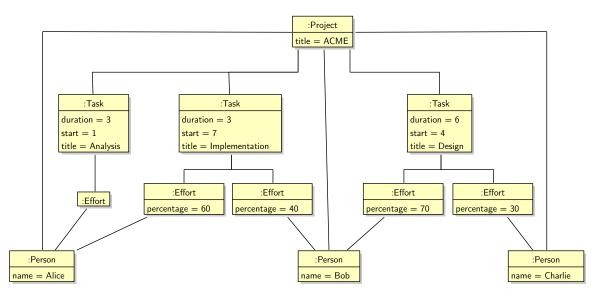

| 5.4.   | Metamodel-based Model-to-Model Transformations [18]                           | 102 |

| 5.5.   | I L J                                                                         | 105 |

| 5.6.   | Example Source Model for ETL transformation [101]                             | 105 |

|        |                                                                               |     |

| 5.7.  | Example Target Metamodel for ETL transformation [101]                      | 106 |

|-------|----------------------------------------------------------------------------|-----|

| 5.8.  | Example Target Model for ETL transformation [101]                          | 108 |

| 5.9.  | Python Model-to-Model transformation based on Metamodels and Metamodel     |     |

|       | APIs                                                                       | 111 |

| 5.10. | Excerpt from MoD used in Section 4.3.3                                     | 112 |

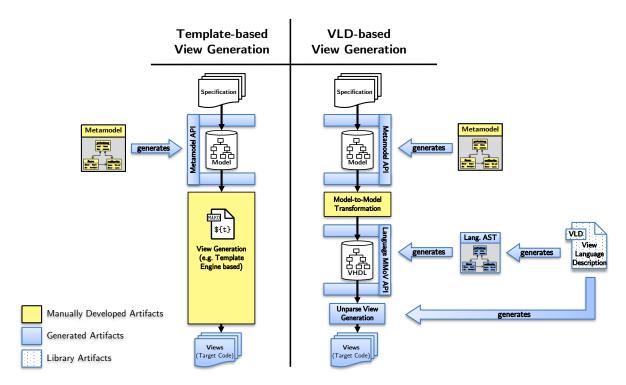

| 5.11. | Template-based and VLD-based View Generation Compared                      | 122 |

| 5.12. | Metamodel Generated from the VLD in Listing 5.7                            | 125 |

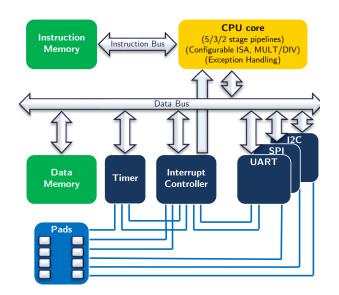

|       | Sample SoC generated with MetaX generator framework                        |     |

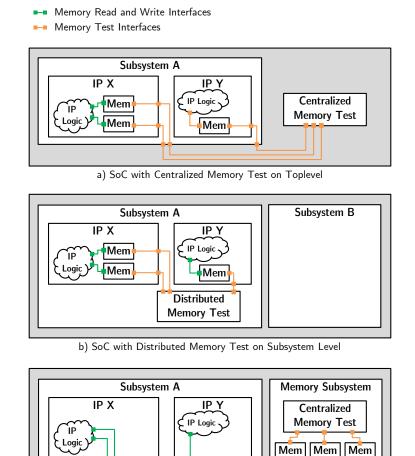

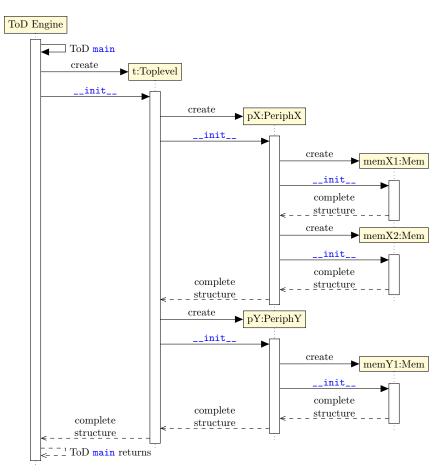

| 7.1.  | Example for different Memory Architecures                                  | 139 |

| 7.2.  | UML Sequence Diagram of Template-of-Design in Listing 7.1 with single-pass |     |

|       | creation of nested structures                                              | 142 |

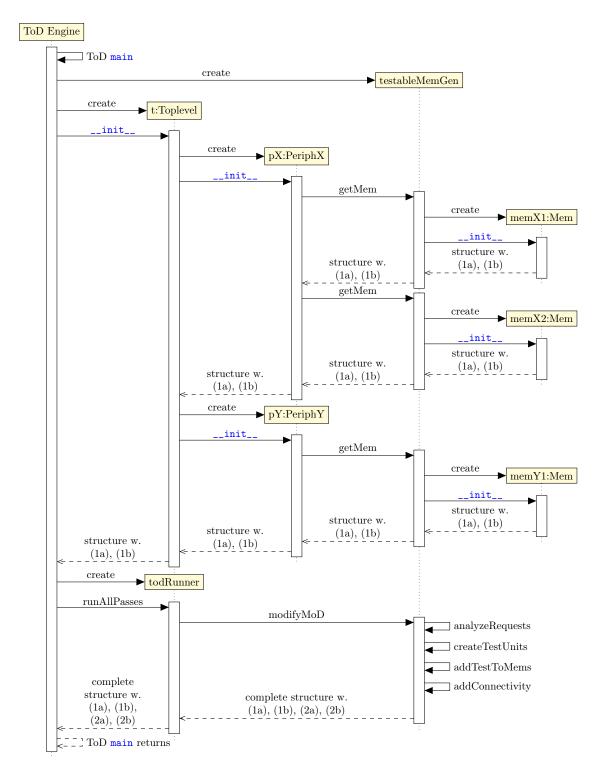

| 7.3.  | UML Sequence Diagram of Template-of-Design in Listing 7.6 with Multi-pass  |     |

|       | Generation                                                                 | 154 |

# List of Listings

| 3.1.  | Example of an `ifdef pragma to alter simulation behavior                                        | 46  |

|-------|-------------------------------------------------------------------------------------------------|-----|

| 3.2.  | Example of an `ifndef pragma combined with a `define as include guard                           | 47  |

| 3.3.  | Consistent logging of error messages with date and source location [57]                         | 47  |

| 3.4.  | Example of a generate statement in SystemVerilog                                                | 49  |

| 3.5.  | Example of Script-based Preprocessor from the Original Research Developing                      |     |

|       | Genesis2 [93]                                                                                   | 51  |

| 3.6.  | Verilog (left) and Verischemelog (right) Example of a Half-Adder [16]                           | 53  |

| 3.7.  | Implementation of the Code from Listing 3.4 in Verischemelog                                    | 54  |

| 3.8.  | Sample of a Chisel Module with conflicting connection statements                                | 58  |

| 3.9.  | Sample of a Chisel Module with Multiplexer Connection                                           | 59  |

| 3.10. | Sample of a Chisel Register and Port (Nodes) without Driver                                     | 61  |

| 5.1.  | Syntax of an Eclipse Transformation Language (ETL) Transformation Rule [80,                     |     |

|       | 45]                                                                                             | 104 |

| 5.2.  | Example Transformation in ETL [80]                                                              | 107 |

| 5.3.  | Creation of static MoD excerpt shown in Figure 5.10 using default API                           | 113 |

| 5.4.  | Supported Notations for Object Creation                                                         | 114 |

| 5.5.  | Creation of static MoD excerpt shown in Figure 5.10 using extended API $\ldots$                 | 117 |

| 5.6.  | Template-of-Design example for the generation of n-th order FIR filter from                     |     |

|       | Model-of-Things                                                                                 | 118 |

| 5.7.  | Simplified Snippet from View Language Description of the VHDL MoV [5]                           | 123 |

| 5.8.  | VHDL entity declaration from VHDL'93 [92]                                                       | 123 |

| 5.9.  | Sample Entity showing the effect of indent and ta functionality                                 | 126 |

|       | Template-of-View Excerpt to Visualize the Benefit of VLD-based View Generation                  | 127 |

| 5.11. | . View Generation based on the Mako template engine [98] using input equivalent to Listing 5.10 | 127 |

|       |                                                                                                 |     |

| 7.1.  | Sample Template-of-Design with single-pass creation of nested structures                        | 143 |

| 7.2.  | Definition of Memory Generator Interface                                                        | 148 |

| 7.3.  | Application of Dependency Injection for Infrastructure Generators                               | 149 |

| 7.4.  | •                                                                                               | 150 |

| 7.5.  |                                                                                                 | 151 |

| 7.6.  | Sample Template-of-Design with Multi-pass Generation                                            | 153 |

$List \ of \ Listings$

# 1. Introduction

# 1.1. Growing Complexity of Integrated Circuits

The computer age started with the use of vacuum tubes as switches in calculating machines. The world's first programmable, fully automated computer based on vacuum tubes is the Z3 with its 2,600 tubes. It was developed in 1939. The end of the relatively short history of the development of vacuum tube based computers is marked by the initial delivery of the AN/FSQ-7, the largest and most powerful vacuum tube based computer in 1957. This computer was built from 49,000 vacuum tubes, required more than 2,000 m<sup>2</sup> of floor space, and weighed 275 tons at a power usage of up to three megawatts. These dimensions still make it one of the largest computers ever built – measuring up to today's supercomputers [91, 9, 19].

It was clear that the fundamental boundaries were limiting the evolution of vacuum tube based computers. At the time, it was easy for engineers to design systems with a complexity much higher than what could possibly be built: if those systems had been realized on vacuum-tube technology, they would not have been economically feasible because of manufacturing and operation costs and a lack of reliability of the countless discrete components required to build them [19].

The key invention that eliminated this bottleneck to evolution and imagination is the transistorbased integrated circuit (IC), colloquially referred to as "computer chip". The inventor of the integrated circuit, Jack St. Clair Kilby, noted at his Nobel Lecture how remarkable the evolution that followed this keystone invention was: "The reality of what people have done with integrated circuits has gone far beyond what anyone – including myself – imagined possible at the time" [19]. This reality of what people have done with integrated circuits is nicely described by Moore's law. Gordon Moore, the co-founder of Intel, forecast that from 1965 onward, the number of transistors on a leading-edge integrated circuit would at least double every two years. While Moore's law cannot continue indefinitely – it has been an accurate pacemaker of the industries' development of the last 50 years – much longer than what Moore expected [13].

The increase in the number of transistors has enabled an increase in performance, capabilities, and a significant reduction in cost – at the cost of significant complexity. In the context of System-on-Chip (SoC) development, complexity refers to the number of components, the number of interactions between those components, and the difficulty of understanding and working with the models or code describing the artifacts underlying the components. Today's SoC designs consist of billions of transistors and hundreds of heterogeneous components – embedded into a single chip. These elements are all required to enable the development of smaller, faster,

#### 1. Introduction

smarter, and more energy-efficient electronic devices as demanded by the market.

Seeing the growth in complexity and the progress that came with it, it is easy to intuitively infer progress from complexity. Increasing complexity and progress are however not the same thing. Complexity is a necessary evil for making progress, and the complexity that arises from this progress hinders future progress. The drawback of increasing complexity in the design task can be clearly seen in today's semiconductor landscape where the high level of complexity in integrated circuits slows innovation and progress. An analysis by Collet et al. in the 2013 McKinsey study on semiconductors analyzes the previous decade with respect to changes in design complexity and design productivity. The analysis finds that in this period, the number of transistors that can be manufactured increased by a factor of 100x, yet the productivity of design increased only by a factor of 20x. It thus shows a further widening of the design productivity gap by a factor of about 5x in one decade [61, 46, 4].

# 1.2. Management of Complexity in IC Design

To tackle the growing complexity of IC design and the cost and time-to-market challenges associated with it, the semiconductor industry has developed a wide range of approaches which can be summarized in the following categories:

- **Specialization** An increased level of specialization is applied to maintain high productivity and to provide the short cycle times demanded by increasingly challenging time-to-market requirements. The distribution of the overall design tasks onto specialized teams which can execute the individual steps more productively and the parallel execution of design tasks by different teams has resulted in the reduction of time-to-market and the ability to handle more complex designs, without however addressing the increasing design cost and the need for synchronization of common concerns.

- **Tools** The introduction of new languages and tools to increase efficiency and productivity throughout the development workflow. The last disruptive productivity increase in this field has been achieved by RTL synthesis tools. RTL synthesis managed to raise the level of abstraction and completely automate the construction of the lower-level implementation. Other technologies which promised to deliver disruptive improvements for the entirety of the digital design domain, for example, the introduction of Transaction-Level Modeling (TLM) or High-Level Synthesis (HLS) have not been able to deliver on their promises. It is theorized that disruptive levels of improvement were not seen with TLM as it does not manage to define one agreed-upon level of abstraction – an obvious contrast to what RTL Design (synchronous design, time discretization) and Gate-Level Design (digital design, value discretization) deliver [4]. While HLS came with an increase in productivity in a limited sub-domain of digital design, it failed to raise the abstraction of the entire domain [52]. Further noteworthy examples which bring similar benefits to limited areas of the IC development task are formal methods for verification and more powerful tools for design space exploration. These specialized tools and approaches however also increase the

complexity needed to synchronize common concerns across heterogeneous development environments.

IP-reuse The reuse of existing components and artifacts across different designs. Since the early days of the semiconductor industry, the basic building blocks of digital designs were implemented once and then reused multiple times in the same or in different designs. Although IP-reuse brought a big initial leap in productivity, its continuous benefit is often overestimated [61]. While reuse can significantly reduce the cost of designs, it limits the ability to change and innovate on existing components and often requires the design of library components that exceed what is needed for any individual device – resulting in higher design and manufacturing costs.

All three pillars are essential and their application has kept the growing productivity gap in check. Their application however comes with its own challenges. As mentioned above, a high degree of specialization and increasingly large, heterogeneous tool landscapes cause significant effort for the synchronization of single source data. IP-reuse in turn has limited the ability to adapt individual components to their concrete needs. The following section describes how code generation can both address these challenges and provide an important additional component for managing complexity.

# 1.3. Management of Complexity Through Generation

Code Generation is an important orthogonal component to the pillars described in Section 1.2 and addresses many of the shortcomings and problems caused by their application.

- **Specialization and Tools** Code generation plays an important role in IC development flows which rely on a high degree of specialization and make use of heterogeneous tools for different specific domain tasks. In modern, highly distributed development flows, generation can provide artifacts for different specialized tasks across different design steps and environments used by different teams and across different domains such as hardware, software, and verification. This is especially true in an environment where different tools, provided by different vendors require the same artifacts in often non-standardized or nonstandard-compliant formats. Automated generation guarantees consistency and flawless synchronization and ensures that all tool-based workflows can be performed on correct and consistent data without the need for manual adaptation.

- **IP-reuse** Generation can overcome a key limitation of IP-reuse: it addresses the limited ability to change and innovate based on existing library components by making them more configurable and adaptable.

Ecker et al. [63] reported a productivity increase by a factor of 20 in special design tasks and up to three times higher productivity in design implementation from specification freeze to tape-out through the use of Metamodeling and code generation. The replacement of ad-hoc script-based

#### 1. Introduction

approaches with a more structured approach and the link to formalized specification data have been mentioned as key to this improvement.

This thesis strives to establish the vision of generation as part of a new approach to designing chips as postulated by Nicolic [67] and Shacham et al. [56]. Following this vision, generators should not only be used to make simpler and more efficient designs but also to generate different alternatives, thus enabling exhaustive architecture analysis. The use of generators [4] instead of models has also been claimed by Bachrach et al. [58].

Besides controlling and configuring generation, the development of generators is the most timeconsuming effort to enable automation. To achieve the vision of generation as part of a completely new approach to designing ICs, this thesis makes heavy use of the research and achievements in the field of software engineering regarding Modeling, Metamodeling and Model Driven Architecture (MDA) and provides a transfer of these achievements into the domain of IC design. With MDA, the Object Management Group (OMG) offers a vision for target code generation from specification via a set of models and a set of transformations, each deriving a model from the adjacent model [69, 42, 4].

## 1.4. Outline

**Chapter 2** describes how advances in development languages have increased productivity and abstracted complexity in both software and hardware development. It details the shortcomings and limitations of language-based approaches and shows how model-centric development approaches can be seen as the next step to managing complexity and raising the level of abstraction of the design process. In this context, the chapter also introduces the theory underlying the Metamodeling-based code generation that has replaced the ad-hoc script-based approaches – eventually leading to the 20x improvement in some areas of the design space [63, 4].

Based on this theoretical foundation, the thesis introduces the vision of Model Driven Architecture (MDA) as postulated by the Object Management Group (OMG). It shows how the realization of this vision in the field of Software Engineering has delivered on its promise of productivity improvement. This leads to a key observation of this thesis: the vision of Model Driven Architecture has not yet been fully realized in the domain of IC design. This realization is the basis for the envisioned approach described in Section 2.5 of this thesis: this work applies the vision of Model Driven Architecture to digital hardware design and provides a wider framework for the application of Model Driven Architecture to different environments in the domain of IC design. Based on the background of this chapter, Section 8 gives an overview of the key contributions made by this thesis.

**Chapter 3** presents related work. The high-level goal of this transfer is to provide more powerful automated code generation to increase productivity and handle the growing complexity in the domain of IC development with an application to digital hardware design. The chapter

thus describes related work applying and improving code generation in the field of digital hardware design. It also identifies the shortcomings that even the most advanced of these approaches cannot overcome.

Chapters 4 and 5 describe in detail the key contributions made by this thesis.

Chapter 4 shows the transfer of the formal structure of the Model Driven Architecture Vision onto the field of IC design. This includes an adaptation of the vision and its terminology for the world of IC design and the development of models and Metamodels for the Model Driven Architecture flow for digital hardware design. It is important to note that Chapter 4 provides this entirely in the context of models and Metamodels. The transfer provided here is agnostic of any concrete hardware or software development language or the concrete implementation of any framework.

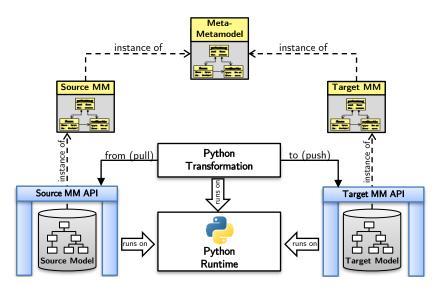

Chapter 5 then describes the Python-based implementation of the proposed MDA framework. Here, it is described how automation and code generation can be used to make the development of an MDA framework and the application of this framework for the development of new generators as easy as possible. This chapter also describes what can be seen as the *heart and soul of any model-driven development approach* [45, 26]: the Model-to-Model transformations as central components of generators built on MDA.

**Chapter 6** shows how the work in this thesis has been applied and extended.

Section 6.1 shows how the methodology developed in this thesis has been applied to develop generators for digital designs. It describes the commercial development projects that have been started based on the methodology developed in this thesis and shows how it is integrated into Infineon's design flow and development at Infineon Technologies AG. Section 6.2 describes how the configurable generators can be used for design space exploration. Section 6.3 shows how the methodology has been further extended outside of the scope of digital hardware design for hardware verification and the development of embedded software.

**Chapter 7** demonstrates how the application of the proposed MDA flow allows users to benefit from established software development methodology and use it to solve problems in the domain of digital design.

**Chapter 8** summarizes this thesis, points out its key contributions, and lists the key publications made as part of the work on this thesis.

# 1. Introduction

This chapter introduces the concepts of models, Metamodels, and Model Driven Architecture and describes their role in the modern software engineering landscape. It explains how these methods have demonstrated to handle complexity, and increase productivity and why they are considered a vital component of any present and future development ecosystem by many in the software engineering community. To do this, this section first summarizes the history of software engineering and describes how modeling needs arose in this domain. Next, this chapter shows how these methods are applied in software engineering where they show benefits.

Based on this understanding of the existing software engineering methods, this section identifies approaches used in the field of IC design which resemble those of software engineering – either inspired by them or developed independently with the same objectives.

This juxtaposition of model-based software engineering and IC design methods eventually leads to the main goals of this section: It identifies the Model Driven Architecture concepts that do not yet have a parallel in the domain of IC design and describes the approach envisioned in this thesis: applying the full vision of Model Driven Architecture – a concept targeted at the development of complex enterprise software landscapes – in the domain of IC design.

# 2.1. Evolution of Languages and their Productivity Impact

This section presents a common taxonomy of software programming languages that emphasizes the historical evolution of these languages towards higher productivity: the grouping of languages into *Programming Language Generations*. It then shows that the steps in the evolution of digital hardware design permit a grouping into categories that are similar in their definition to the Programming Language Generations defined for software programming languages.

Based on this grouping, it identifies a shortcoming shared by both hardware and software development landscapes.

# 2.1.1. Software Programming Languages Generations

The history of programming computers – which is now the vast field of software development – shows a clear trajectory towards increasing efficiency and handling complexity through an

increase in abstraction.

The evolution of programming languages is a good example of this. Programming languages are the main tool for creating software and have undergone a significant evolution since the development of the first computers. A commonly used grouping is the assignment of languages to *programming language generations*.

- **First-generation languages (1GL)**, also referred to as *machine languages* and represent the most primitive form of language with the lowest level of abstraction. Programs written in first-generation languages are directly recognized by a processor. They are therefore highly machine-dependent and hard to write and understand as the numerical notations of these languages are equivalent to the instruction set supported by the processor running the program. This instruction set is optimized for the fast and easy execution of a program and not to simplify the development of programs.

- Second-generation languages (2GL), also referred to as assembly languages are the first level of abstraction in the domain of programming languages. The structure of assembly languages still closely matches the instruction set of the underlying computer. Assembly language instructions typically map one-to-one to the instructions in the instruction set. The benefit of assembly languages is their support for symbolic names (mnemonics) for operations, addresses, registers and sections of instructions.

- Third-generation languages (3GL), also referred to as *higher-order languages* are the last commonly established level of abstraction. This category is significantly wider than that of first- and second-generation languages. It contains all languages that provide a degree of abstraction of the instruction set that allows developers to write programs with little knowledge of the instruction set of the underlying computer. In addition to the use of symbolic names, they can be translated to different instruction sets and therefore run on different machine types. This field ranges from very low-level languages such as Algol and C to high-level languages such as Java, C# or dynamic languages such as Python. Nowa-days, third-generation languages have displaced first- and second-generation languages in all but a few highly specialized corner cases. A lot of development is still happening on improving and making third-generation languages more powerful. Still, the above taxonomy defining what is first- and second-generation language and what is third-generation language or higher is widely accepted and established.

- Fourth- and fifth-generation languages (4GL and 5GL) describe abstractions above of what currently exists in the category of third-generation languages. The definition of the groups of fourth- and fifth-generation languages is more ambiguous to date. Some sources place languages such as Python into the 4GL bin and differentiate from the 3GL category on attributes such as their ease of use and similarity to human language [82]. Others define fourth-generation languages as domain-specific languages [28] or define the category based on the ability of languages to make programming accessible to non-programmers (using features such as a graphical query generator, spreadsheet capabilities, and graphical screen definition) [54].

#### 2.1. Evolution of Languages and their Productivity Impact

The same applies to the 5GL category which is sometimes described as the category of declarative programming (i.e. that of constraint-based programming) [82], while in other cases being equated with the field of visual development and no-code and low-code approaches [54].

In the context of this thesis, the groups of 1GL, 2GL, and 3GL are treated as closed and defined groups where 3GL includes all high-level multi-paradigm programming languages. [54, 82]

#### 2.1.2. Mapping of Programming Language Generations to Digital Design

The terminology of *Generations of Programming Languages* is one that has been established exclusively for the field of software engineering. The characteristics of this taxonomy can however also be used to evaluate the developments in the history of digital design.

- **First-generation Digital Design** can be matched to transistor-level, the lowest level of abstraction in digital design. On this level, individual transistors and specialized transistor structures are used to build higher-level functions such as e.g. multiplexers or logic gates. Development on transistor-level provides the lowest level of abstraction, yet allows for the highest level of optimization. Using specialized transistor circuit structures such as transmission gates, it is for example possible to develop a one-bit multiplexer with only six transistors [11]. The formalized, Fortran-based input format used to program initial versions of the SPICE simulator is an example of the languages used in the context of first-generation digital design [7].

- Second-generation Digital Design can be matched to gate level, the next higher level of abstraction in digital design. On this level, functionality is not compiled from individual transistors but from pre-assembled building blocks. The level of optimization possible on this level is already reduced - compiling a multiplexer from library logic gates would require at least 14 transistors. Similar to the second-generation software languages, assembling a design using gate-level design requires the engineer to himself pick the individual library blocks and connect them together – this requires an awareness of the exact combinational logic that is instantiated in the design [11]. The Electronic Design Interchange Format (EDIF) or a subset of the Verilog language that corresponds to the capabilities of EDIF are languages that are used to describe artifacts of second-generation digital design [8].

- Third-generation Digital Design can be matched register-transfer level (RTL). RTL design is today's standard approach to the design of digital circuits. The standard languages that are nowadays used for digital design are on the level of abstraction of RTL. In RTL design, the level of abstraction is raised to registers and the definition of the logic function between registers. RTL synthesis tools handle the translation from logic and register definition onto the gate-level representation of a design. The established languages in this area are VHDL, Verilog, and SystemVerilog, with SystemVerilog developing into the defacto industry standard and VHDL and Verilog-only designs being slowly phased out. For simplicity,

this thesis treats Verilog as a subset and predecessor of SystemVerilog. Similar to the development of software languages belonging to the category of third-generation language, the languages in this field are still undergoing continuous evolutionary development – admittedly at a much slower pace than the developments in the field of third-generation software languages [11].

Fourth-generation Digital Design can be matched to all design approaches above traditional RTL design. The most well-known candidate for such an approach is high-level synthesis (HLS). The languages used to describe high-level synthesizable hardware models are typically a subset of C or C++ and SystemC. The supported libraries and language subsets are highly vendor-dependent and there is no commonly agreed definition of a high-level synthesizable language subset. When comparing high-level or behavioral synthesis approaches to levels of abstraction in software development, a resemblance between imperative and declarative programming on the software side and RTL design and highlevel synthesis on the hardware side becomes apparent. In both domains, feasible and helpful approaches exist – yet their commercial applicability is currently limited to very narrow fields. For high-level synthesis, a clear benefit of the technology is visible only for datapath-driven designs with an ability to benefit pipeline-based approaches to data processing. The first generation of HLS tools was applied for IC design in the 1980s. Despite this 40-year-long history and significant development steps in the technology, it is not foreseeable that HLS becomes the next common level of abstraction that might replace the register transfer level. It is therefore also not clear whether HLS is what will fill the role of *fourth-generation* digital design [52]. The Bluespec languages (Bluespec System Verilog and Bluespec Haskell) can further be considered as fourth-generation digital design languages in the context of this thesis. The definition of state as registers and memories is clearly still a part of the Bluespec concept, it therefore still meets an important characteristic of RTL design and differentiates itself from HLS. Moreover, the Bluespec approach relies on describing the change to those stateful elements on RTL level. What Bluespec however does not need is the definition of actual RTL connectivity or scheduling. It is the compiler of the Bluespec language that takes care of all synchronization, the generation of state machines, and synchronization. This is a significant level of abstraction over the RTL level, leading to the categorization performed here [55, 30, 79].

#### 2.1.3. Common Observations about Software and Hardware Languages

Grouping approaches to Digital Design into the same categories that are used for software development languages allows us to come up with important common observations about both fields:

1. For both hardware and software development, there is noteworthy ongoing development in the category of third-generation languages. These new third-generation languages have drastically reduced the complexity of development tasks and allowed developers to tackle problems of a complexity that was undreamed of in the days of first-generation programming languages and initial hardware description languages [21].

- 2. All these new developments of efficient third-generation languages are however an evolutionary approach that has a known upper boundary: In both hardware and software domains, the law of diminishing returns manifests: ever more complex and powerful languages (which are therefore harder to learn) provide ever smaller returns in developer productivity. Examples in the domain of software engineering are the increased complexity of the C++ language and the sheer amount of different languages with relatively small developer communities. In the domain of IC design, the complexity of SystemVerilog is an example of the limits of productivity which can be obtained by improvements in third-generation languages.

- 3. The abstraction the third-generation languages provide is sufficient for simple software and smaller IC design projects. For the complexity of large, state-of-the-art products in both IC design and software development, it is clear that both the current third-generation languages and the discernible upper threshold of productivity a potential future thirdgeneration language can provide are insufficient [23]. One of their key issues is their inability to provide human and machine-readable views of complex systems, their complex structure, and their complex interdependencies. In neither of the domains, a clear path to a *fourth-generation* approach can be identified and the replacement of third-generation languages is not anticipated.

We can derive a growing productivity gap from these observations: improvements in thirdgeneration languages increase productivity at a decelerating rate while the complexity of designs is increasing at an accelerating rate. The following sections show how model-based, languageindependent approaches can contribute to reducing this gap.

#### 2.2. Model-based and Language-independent Approaches

The ambiguity regarding language categories above *third-generation languages* highlights the need for and the importance of model-based approaches. Model-based approaches are able to address the shortcomings of third-generation languages described in the previous section and can be seen as language-independent continuation of the raising levels of abstraction the language generations provide.

This section details modern model-based development approaches and demonstrates how they already provide the first answers to the question of what comes above the third-generation languages. To do this, it first broadly categorizes the levels of modeling which are applied to industry development tasks into a spectrum of modeling. It then introduces Metamodeling as the state-of-the-art for efficient modeling and code generation. Based on this theoretical underpinning, it shows how the technology is used as part of software and hardware development and details its benefits and weaknesses.

#### 2.2.1. The Modeling Spectrum

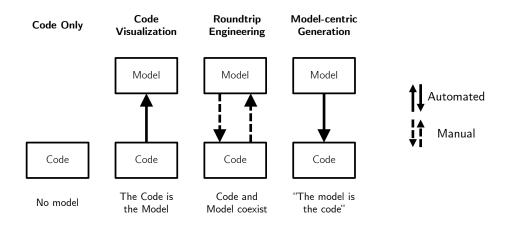

The application of modern model-based approaches differs depending on the domain and complexity of the problem at hand. This section presents a view of the modeling spectrum as defined by Kleppe et. al. [23]. Figure 2.1 describes the different categories of modeling used.

Figure 2.1.: The Modeling Spectrum [23]

**Code Only** development does not utilize any modeling and relies only on code as the primary artifact to define a software or hardware product. Any abstractions of the code only exist in the developer's mental model of the implementation.

**Code Visualization** approaches use models to reduce one of the main weaknesses of Code Only approaches: it extracts modeling artifacts from the code that can be used by humans to get a better view of the structure and interdependencies inside these systems. In this scenario, the code acts as a model and it is only possible to visualize model artifacts that are captured in the code itself. Higher-level modeling artifacts like ownership of objects, which may not have a counterpart in the language used to implement the code cannot be captured in code and therefore not be visualized. The extraction of models from the code is commonly done automatically which ensures consistency and reduces effort.

**Roundtrip Engineering** describes an approach where a formal, code-independent model is maintained by the engineering team. This model is manually kept in sync with the code that it describes. Any changes to the model that impact the code require corresponding changes in the code and vice-versa.

The main benefit of this approach is that the model can contain additional modeling artifacts that need not be supported by the language of the code. Because of these additional artifacts, it is however no longer possible to automate the generation of the model from the code.

#### 2.2. Model-based and Language-independent Approaches

Moreover, while many approaches support initial code generation from the model, the generated code artifacts are intentionally loosely coupled to the model. It is intended that they are extended and modified by the developers. As a result of this intentionally loose coupling, an automated change to the code after a change in the model is not possible in the practical incarnations of this approach.

Roundtrip engineering helps with the understanding of the complexity in the underlying code and provides a better abstraction than Code Visualization – it however does not remove the complexity from the development task. This can be compared to how assembly language behaves towards machine code: assembly language abstracts addresses and bit codes and therefore simplifies writing and understanding code – it however does not remove the burden to understand the intricacies of the instruction set of the underlying machine.

**Model-centric Generation** is the first automated, fully model-based generation approach. When this approach is applied, a certain aspect of a software or hardware system is fully described by a model. From this model, a fully automated generator will provide the code.

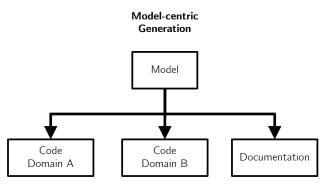

Similar to Roundtrip Engineering, this approach allows models to contain additional artifacts that may not be supported by a particular generated code view. This enables the scenario depicted in Figure 2.2: a model can contain the superset of all artifacts required to generate target views of different domains (e.g. code of different languages, for hardware development and software development, for software or hardware verification activities, hardware validation or documentation).

"The model is the hardware, software, documentation  $\ldots$  "

#### Figure 2.2.: Model-centric generation of multiple outputs

The most noteworthy difference to Roundtrip Engineering is the fact that – when the philosophy of Model-centric Generation is followed – any generated artifact must not be manually modified. As a consequence, for any change in the model, a new target view can automatically be generated.

Model-centric generation can take the next step to both ease the understanding and analysis of

complex systems and remove complexity from the development task. The development teams can rely on the generator and no longer need to carry the burden of understanding the intricacies of the generated code. This leaves the development teams with a view that is significantly more abstract and less complex than what can be achieved with code developed in a third-generation programming language.

It is important to note that modern software and hardware development projects do not just rely on one of the approaches described above. For any reasonably large, heterogeneous development project, a combination of all approaches from the Modeling Spectrum is applied. Productivity benefits can be obtained by moving more and more development tasks toward Model-centric generation. This can be achieved by either identifying coding tasks that can be solved with existing Model-centric Generation methodologies or by developing new generation methodologies.

The state-of-the-art of existing Model-centric generation methodologies is described and their existing applications are described in Section 2.3. Model Driven Architecture as a more advanced and significantly more powerful methodology with a wider field of application is described in Section 2.4.

## 2.3. Metamodeling and Metamodeling-based Code Generation

Based on the overview of model-centric development provided in the previous section, this section will detail the state-of-the-art of Metamodeling, a structured and clean approach to model-centric automation.

#### 2.3.1. Simple Code Generation without Metamodeling

Developing generators that generate views from input models can be achieved with simple scripting approaches – a practice that is common in both the software and hardware industry [16]. In the following, these scripts are referred to as point-solution generators.

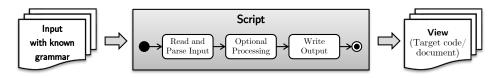

Figure 2.3.: Illustration of a simple, unstructured script-based generator

The only prerequisite for a point solution script is structured input data that follows an explicitly or implicitly defined grammar. Figure 2.3 shows how such a script typically generates its outputs: it reads a known input file and parses its content, applies some optional, simple processing on the data, and then uses either file I/O or standard output to write the view information.

This simple approach lacks many important requirements for a structured, re-usable and extendable model-centric automation framework:

- 1. A language and data format independent definition of a model's structure.

- 2. An automated and reusable approach to checking correct model structure.

- 3. An automated and reusable approach to serializing and deserializing models for storage.

- 4. A method to facilitate the visualization and entry of models and model structure.

- 5. A re-usable and structured approach to define mappings from models to views.

These requirements are met by state-of-the-art Metamodeling as detailed in the rest of this chapter [21].

#### 2.3.2. Metamodeling Concept

Metamodeling is an important theoretical foundation for a structured approach to code generation. The prefix "meta" can be loosely translated to "after" or "beyond". In the term Metamodeling, it is used to highlight that a Metamodel is a *model of a model*. A Metamodel is an abstraction of a set of models, defining the model's properties and specifying the relationships between its elements [60, 53].

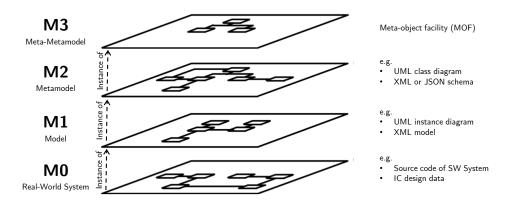

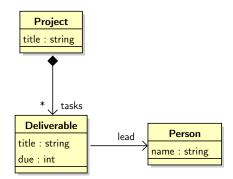

Figure 2.4.: Metamodeling, Hierarchies of Models as defined by OMG [21]

The relationship between a model and its Metamodel does not only exist on a single level: A Metamodel can in turn be conceptualized as a model, which then will have its own Metamodel. The Object Management Group (OMG) is a standardization consortium that has developed a standard formalization of these *model of a model* hierarchies. Figure 2.4 illustrates these hierarchies using the OMG standardized terminologies. For each of the layers in the figure, the model in the lower layer is in an *instance of* the model in the layer directly above it. The following will describe the characteristics of the individual layers from bottom to top.

- 2. Languages, Models, Metamodeling and Model Driven Architecture (MDA)

- **M0** contains the *Real-World System* subject to the Metamodeling based automation. Elements on this layer are for example the source code of a software tool or library or design artifacts such as hardware description language or schematic data in the IC design process.

- **M1** holds the *Model* of the real-world system subject to automation. This layer is what is typically read or generated by a framework that generates views for use in the design process. The input data handled by the typical users of automation tools resides on this layer.

- M2 holds the *Metamodel* of the M1 model. This layer defines the M1 model's properties and specifies the relationships between its elements. It is the layer that has to be handled by the developers of automation tools.

- M3 holds the Meta-Metamodel, referred to as Meta Object Facility in OMG terminology. Any M2 Metamodel can be described as an instance of the Meta-Metamodel, however, also the Meta-Metamodel can be described as an instance of itself. This self-describing property of Meta-Metamodels is called metacircular. The Meta-Metamodel layer is not used by developers of automation tools but by developers of the framework for automation tools to develop tooling that can be utilized for all M2 Metamodels. These approaches are further described in Section 2.3.3.

This theoretical foundation provides a solid, language-independent view of models and the data they contain. When this theoretical foundation is used for the implementation of a Metamodeling framework, it is guaranteed that all available models are easily accessible and compatible. The theoretical foundation also permits further analysis and mathematical formalization which has been developed as part of this thesis work and is published in [3].

The next section details the practical benefits that the theoretical Metamodeling framework has for the structured development of generators.

# 2.3.3. Capabilities and Advantages of Metamodeling Frameworks for Code Generation

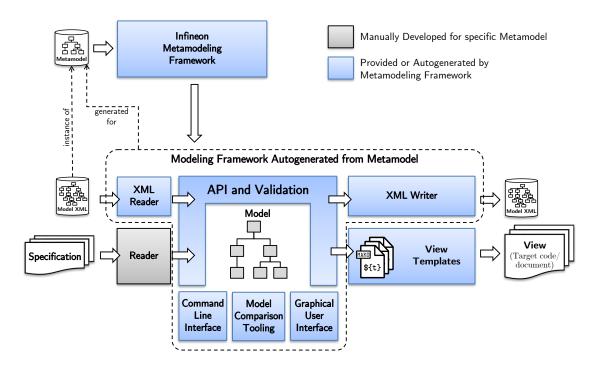

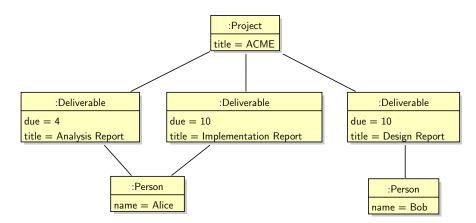

This section describes the structure and features a generic, language-independent Metamodeling framework has. The described structure and features match those of the Metamodeling framework implemented at Infineon Technologies AG and used for the work of this thesis, the descriptions are however deliberately kept generic and will apply to any metamodeling framework, regardless of the concrete implementation.

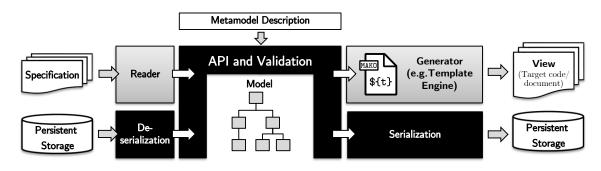

Figure 2.5 shows an overview of the components such a Metamodeling framework provides for a given Metamodel. The arrangement of the blocks visualizes the data flow through the framework from left to right. The white boxes describe the input or output of the metamodeling framework. Possible inputs are either an M1-layer model used to generate the views (boxes "Specification" or "Persistent Storage") or an M2-layer Metamodel ("Metamodel Description")

### 2.3. Metamodeling and Metamodeling-based Code Generation

used to generate and configure the framework itself. Possible outputs are in turn M1-layer models "Persistent Storage" or generated target views such as software code, hardware description code, or documents ("View" or M0-layer)). The elements depicted in solid black ("Deserialization", "API and Validation" and "Serialization") are components that are typically provided by the framework out of the box, and the elements depicted in light gray ("Reader" and "Generator") are elements that need to be manually developed as extensions to the framework. They provide the ability to read data from data formats custom to a certain M2-layer Metamodel or to write data to such a format.