Research Paper

## International Journal of HIGH PERFORMANCE COMPUTING APPLICATIONS

# A massively parallel semi-Lagrangian solver for the six-dimensional Vlasov-Poisson equation

The International Journal of High Performance Computing Applications 2019, Vol. 33(5) 924–947 © The Author(s) 2019

Article reuse guidelines: sagepub.com/journals-permissions DOI: 10.1177/1094342019834644 journals.sagepub.com/home/hpc

Katharina Kormann 6, Klaus Reuter and Markus Rampp 2

#### **Abstract**

This article presents an optimized and scalable semi-Lagrangian solver for the Vlasov-Poisson system in six-dimensional phase space. Grid-based solvers of the Vlasov equation are known to give accurate results. At the same time, these solvers are challenged by the curse of dimensionality resulting in very high memory requirements, and moreover, requiring highly efficient parallelization schemes. In this article, we consider the 6-D Vlasov-Poisson problem discretized by a split-step semi-Lagrangian scheme, using successive I-D interpolations on I-D stripes of the 6-D domain. Two parallelization paradigms are compared, a remapping scheme and a domain decomposition approach applied to the full 6-D problem. From numerical experiments, the latter approach is found to be superior in the massively parallel case in various respects. We address the challenge of artificial time step restrictions due to the decomposition of the domain by introducing a blocked one-sided communication scheme for the purely electrostatic case and a rotating mesh for the case with a constant magnetic field. In addition, we propose a pipelining scheme that enables to hide the costs for the halo communication between neighbor processes efficiently behind useful computation. Parallel scalability on up to 65,536 processes is demonstrated for benchmark problems on a supercomputer.

#### **Keywords**

Vlasov-Poisson, fully kinetic simulation, semi-Lagrangian method, high-dimensional domain decomposition, hybrid parallelization

#### I. Introduction

Numerical simulations are of key importance for the understanding of the behavior of plasmas in a nuclear fusion device. The fundamental model in plasma physics is a kinetic description by a distribution function in six-dimensional (6-D) phase space solving the Vlasov–Maxwell equation

State-of-the-art kinetic simulations for magnetic confinement fusion are built upon the so-called gyrokinetic model, a reduced model in a 5-D phase space. Since the increase in parallel computing power renders the solution of the fully kinetic Vlasov equation in 6-D phase space possible, corresponding interest has arisen recently (cf. e.g. Muñoz et al. (2015); Grošelj et al. (2017); Kuley et al. (2015); Miecnikowski et al. (2018) for physical studies of the kinetic model with particle codes). For the solution of the Vlasov equation, both grid-based and particle-based methods are commonly used; however, simulations in the full 6-D phase-space are as yet mostly based on the particle-in-cell method. We distinguish two classes of grid-based methods, Eulerian solvers based on finite volume or discontinuous Galerkin on the one hand,

and, on the other hand, semi-Lagrangian methods that update the solution by evolution along the characteristics using interpolation. The latter class of methods has the advantage that usually no time step restriction by a Courant–Friedrich–Levy (CFL) condition needs to be imposed. Typically, particle-in-cell methods are used for high-dimensional simulations due to their favorable scaling with the dimensionality. Moreover, the particle pusher part is embarrassingly parallel. Aspects of memory layout and parallelization strategies for the 6-D kinetic model with the particle-in-cell method have for instance been reported by Hariri et al. (2016). On the other hand, particle-in-cell methods suffer from numerical noise, and grid-based

#### Corresponding author:

Katharina Kormann, Max Planck Institute for Plasma Physics, Boltzmannstr 2, 85748 Garching, Germany.

Email: katharina.kormann@ipp.mpg.de

<sup>&</sup>lt;sup>1</sup> Max Planck Institute for Plasma Physics, Garching, Germany & Department of Mathematics, Technical University of Munich, Garching, Germany

<sup>&</sup>lt;sup>2</sup> Max Planck Computing and Data Facility, Garching, Germany

methods are therefore an interesting alternative. Grid-based solvers for the 6-D Vlasov equation have already been considered in the space plasma community. In particular, Yoshikawa, Yoshida, Umemura, and coworkers have presented Vlasov-Poisson and Vlasov-Maxwell solvers in 6-D phase space based on semi-Lagrangian methods (Tanaka et al., 2017; Yoshikawa et al., 2013). Another example is the hybrid Vlasov-Maxwell (HVM) code based on finite differences (Cerri et al., 2018). Scalability of these codes on 5-D meshes have been reported in Umeda and Fukazawa (2014) and Mangeney et al. (2002), respectively; however, no detailed performance tuning has been reported. Another area of active research is the development of grid-based solvers with compression based on sparse grids (Guo and Cheng, 2016; Kormann and Sonnendrücker, 2016) or lowrank tensors (Ehrlacher and Lombardi, 2017; Einkemmer and Lubich, 2018; Kormann, 2015). These techniques are still experimental and require some structure in the underlying problem that allows for compression.

Kinetic simulation of fusion plasma is a very demanding task. Numerical runs with the state-of-the-art semi-Lagrangian solver GYSELA are typically performed on 1k-16k cores (cf. Latu et al. (2016)). However, these simulations are limited to the core of the device, a simplified model for the electrons, and a 5-D gyrokinetic model. Simulations that include the edge and scrape-off layer as well as a fully kinetic model will therefore require exascale computing facilities. In this article, we focus on efficient parallelization schemes for a semi-Lagrangian discretization of the Vlasov-Poisson equation in 6-D phase space. For a Vlasov-Poisson equation on a 4-D phase space, two parallelization schemes have been discussed in the literature: a domain partitioning scheme with patches of 4-D data blocks (Crouseilles et al., 2009) as well as a remapping scheme (Coulaud et al., 1999). The idea of the remapping scheme is to work with two different domain partitions which both keep a partition of the dimensions sequential on each processor. The latter strategy is very well adapted to a semi-Lagrangian method combined with dimensional splitting; however, its parallel scalability is hampered by an all-to-all communication pattern. While domain decomposition methods are wellestablished for 2- and 3-D problems, higher dimensional decompositions are less well studied.

This article addresses the particular technical challenges posed by the high dimensionality and presents a number of unique optimizations for tackling them in a 6-D domain decomposition approach. Specifically, the surface-to-volume ratio of a domain increases with the dimensionality, and the number of grid points per dimension that can be stored on a single compute node is dramatically reduced compared to the low-dimensional case. For instance, working with a hypercube of only 32 points per dimension already requires around 10 GB of memory in 6-D. Hence, the key property of an implementation is its ability to use an as-large-as-possible amount of distributed memory, and weak scalability is the most relevant metric for the

efficiency of the application. As a consequence of the high surface-to-volume ratio, the number of "halo" grid points that need to be communicated between domains is large compared to the number of inner points, an effect that is aggravated in our application scenario since high-order interpolation schemes are necessary due to accuracy requirements of the semi-Langrangian method (as shall be demonstrated in Section 6). To reduce the burden of the high-volume data exchange, we propose a blocking scheme to overlap communication and computations in the advection steps. In passing we note that concerning parallel scalability, a fully kinetic description in 6-D is considerably more challenging than the gyrokinetic model, as the latter not only involves one dimension less but also the fifth dimension of the gyrokinetic model acts merely as a parameter and thus communication is effectively restricted to along four dimensions (cf. Grandgirard et al., 2016; Latu et al., 2016). In principal, semi-Lagrangian methods allow for delocalized interpolation stencils and hence for large time steps. Such a delocalization is, however, problematic in combination with a domain decomposition method and typically time step restrictions need to be introduced (cf. also Yoshikawa et al., 2013, section 2.4; Crouseilles et al., 2009). We demonstrate that the restriction can be alleviated by an asymmetric communication scheme. This problem is particularly severe in simulations of magnetized plasmas in a strong guide field where particles perform a fast gyromotion around the magnetic field lines. To mitigate this problem, we propose the use of a rotating velocity grid.

The outline of the article is as follows: In the next section, we introduce the physical model, the semi-Lagrangian method including the rotating mesh for the background magnetic field, and the parallelization schemes. Moreover, in Section 3, we discuss the impact of the parallelization on the interpolation step in the semi-Lagrangian scheme. In Section 4, we describe our implementation of the domain partitioning scheme, followed by Section 5 with a discussion of our performance optimizations. Section 6 compares Lagrange interpolation of various orders and demonstrates the effectiveness of the rotating grid followed by a numerical demonstration of the scalability of our new implementation in Section 7. Finally, Section 8 concludes the article.

#### 2. Algorithmic background

#### 2.1. Vlasov-Poisson equation

The Vlasov-Poisson equation describes the motion of a plasma in its self-consistent electric field for lowfrequency phenomena. The Vlasov equation for electrons in dimensionless form is given as

$$\begin{split} \partial_t f(\mathbf{x}, \mathbf{v}, t) + \mathbf{v} \cdot \nabla_{\mathbf{x}} f(\mathbf{x}, \mathbf{v}, t) \\ - (\mathbf{E} + \mathbf{v} \times \mathbf{B}_0)(\mathbf{x}, t) \cdot \nabla_{\mathbf{v}} f(\mathbf{x}, \mathbf{v}, t) &= 0 \end{split}$$

The self-consistent field for electrons in a neutralizing ion background can be computed by the following Poisson equation

$$-\Delta \phi(\mathbf{x}, t) = 1 - \rho(\mathbf{x}, t), \quad \mathbf{E}(\mathbf{x}, t) = -\nabla \phi(\mathbf{x}, t),$$

$$\rho(\mathbf{x}, t) = \int f(\mathbf{x}, \mathbf{v}, t) d\mathbf{v}$$

(1)

Here, f denotes the probability density of a particle in phase space defined by position  $\mathbf{x} \in D \subset \mathbb{R}^3$  and velocity  $\mathbf{v} \in \mathbb{R}^3$ ,  $\mathbf{E}$  denotes the electric field,  $\phi$  the electric potential, and  $\rho$  the charge density. The magnetic field  $\mathbf{B}_0$  is supposed to be either zero or a constant background field aligned with the  $x_3$  axis. Generally, the spatial domain is defined by the geometry of a tokamak or a similar fusion device. In this article, we restrict ourselves to common benchmark problems on a periodic box. The distribution has a Maxwellian shape in velocity such that it follows an exponential decay for large values of the velocity. We therefore truncate the computational domain in velocity space to a box and close the system with (artificial) periodic boundary conditions.

The characteristic curves of the Vlasov equation can be defined by the following system of ordinary differential equations (ODE)

$$\frac{\mathrm{d}\mathbf{X}}{\mathrm{d}t} = \mathbf{V}, \quad \frac{\mathrm{d}\mathbf{V}}{\mathrm{d}t} = -\left(\mathbf{E}(\mathbf{X}, t) + \mathbf{V} \times \mathbf{B}_0\right) \tag{2}$$

Let us denote by  $\mathbf{X}(t; \mathbf{x}, \mathbf{v}, s)$ ,  $\mathbf{V}(t; \mathbf{x}, \mathbf{v}, s)$  the solution of the characteristic equation (2) at time t with initial conditions  $\mathbf{X}(s) = \mathbf{x}$  and  $\mathbf{V}(s) = \mathbf{v}$ . Given an initial distribution  $f_0$  at time  $t_0$ , the solution at time s > 0 is given by

$$f(\mathbf{x}, \mathbf{v}, s) = f_0(\mathbf{X}(t_0; \mathbf{x}, \mathbf{v}, s), \mathbf{V}(t_0; \mathbf{x}, \mathbf{v}, s))$$

(3)

since the distribution function is constant along the characteristic curves.

#### 2.2. The semi-Lagrangian method for Vlasov–Poisson

To numerically compute the solution of the Vlasov equation, we use the so-called semi-Lagrangian method. We introduce a 6-D grid to discretize the phase space. In each time step, the equations for the characteristics are solved for each grid point backward in time from time  $t_{m+1}$  to time  $t_m$  with  $\Delta t = t_{m+1} - t_m$  small. Then equation (3) is used with  $s = t_{m+1}$  and  $t_0 = t_m$  to find the solution at time  $t_{m+1}$  for each grid point. Since  $f^{(m)}$  is only known on the grid points, some interpolation method is needed to approximate the value of  $f^{(m)}\left(\mathbf{X}(t_m; \mathbf{x}, \mathbf{v}, t_{m+1}), \mathbf{V}(t_m; \mathbf{x}, \mathbf{v}, t_{m+1})\right)$ . In this general form, the solution with a semi-Lagrangian method requires the solution of a system of ODE as well as interpolation.

To efficiently solve the characteristic equations, Cheng and Knorr (1976) proposed a splitting method for the Vlasov–Poisson equation ( $\mathbf{B}_0 = 0$ ) reduced to a 2-D ( $1\mathbf{x} - 1\mathbf{v}$ ) phase space that splits the  $\mathbf{x}$  and  $\mathbf{v}$  advections. This yields the following algorithm: given  $f^{(m)}$  and  $\mathbf{E}^{(m)}$  at time  $t_m$ , we

compute  $f^{(m+1)}$  at time  $t_m + \Delta t$  for all grid points  $(\mathbf{x}_i, \mathbf{v}_j)$  as follows:

- 1. Solve  $\partial_t f \mathbf{E}^{(m)} \cdot \nabla_{\mathbf{v}} f = 0$  on half time step:  $f^{(m,*)}(\mathbf{x}_i, \mathbf{v}_j) = f^{(m)} \left( \mathbf{x}_i, \mathbf{v}_j + \mathbf{E}_i^{(m)} \frac{\Delta t}{2} \right)$

- 2. Solve  $\partial_t f + \mathbf{v} \cdot \nabla_{\mathbf{x}} f = 0$  on full time step:  $f^{(m,**)}(\mathbf{x}_i, \mathbf{v}_j) = f^{(m,*)}(\mathbf{x}_i \mathbf{v}_j \Delta t, \mathbf{v}_j)$

- 3. Compute  $\rho(\mathbf{x}_i)$  and solve the Poisson equation for  $\mathbf{F}^{(m+1)}$

- 4. Solve  $\partial_t f \mathbf{E}^{(m+1)} \cdot \nabla_{\mathbf{x}} f = 0$  on half time step:  $f^{(m+1)}(\mathbf{x}_i, \mathbf{v}_j) = f^{(m,**)} \left( \mathbf{x}_i, \mathbf{v}_j + \mathbf{E}_i^{(m+1)} \frac{\Delta t}{2} \right)$

Note that the electric field is constant for the  $\mathbf{v}$  advection step. Therefore, the advection coefficients are independent of  $\mathbf{v}$  for the  $\mathbf{v}$  advection and independent of  $\mathbf{x}$  for the  $\mathbf{x}$  advection and the characteristics are therefore given analytically.

To avoid 3-D interpolation, we use a cascade interpolation scheme replacing the 3-D interpolation by three successive 1-D interpolations. Moreover, we can use a first-same-as-last implementation that clusters step 4 of time step m with step 1 of time step m + 1.

As a consequence the main building block of the splitstep semi-Lagrangian discretization of the Vlasov–Poisson problem is 1-D interpolation on 1-D stripes of the 6-D domain. Moreover, the interpolation step on the individual stripes has a special form: The function needs to be interpolated at a shifted value of each grid point and the value of this shift is constant for the whole stripe. For a stripe of length n with grid points  $x_i$ , i = 1, ..., n, we compute

$$g^{(m+1)}(x_i) = g^{(m)}(x_i + \alpha), \quad i = 1, \dots, n$$

(4)

Since  $\alpha$  is independent of  $x_i$ , the interpolation formula is the same in each grid cell that can be exploited for vectorized implementation.

Advections can also be reduced to 1-D interpolation for the Vlasov—Maxwell equation using the backward substitution method introduced by Schmitz and Grauer (2006). In this article, we focus on the Vlasov—Poisson problem. However, we include strong background magnetic fields and discuss in the next section how they can be integrated into the split-step semi-Lagrangian scheme.

### 2.3. Split-step semi-Lagrangian method on a rotating mesh

In a magnetic confinement fusion device, the background magnetic field is strong compared to the self-consistent fields and causes a rapid motion around the field lines, the so-called gyromotion. Often the time scale of the gyromotion is the fastest so that we do not want to accurately resolve this time scale. On the other hand, the rotation around the magnetic axis (here the  $x_3$  axis) causes non-locality in the perpendicular velocity plane (the  $(v_1, v_2)$

plane) which is difficult to handle when working with distributed grids.

We therefore propose the use of a rotating grid that follows the circular motion of the characteristics given by

$$\frac{\mathrm{d}\mathbf{V}}{\mathrm{d}t} = \mathbf{V} \times \mathbf{B}_0 \tag{5}$$

Moving grids for Vlasov simulations have previously been discussed by Sonnendrücker et al. (2004), however, not in the context of parallelization.

To this end, we define a logical grid equivalent to the physical grid at initial time. Let us define the rotation matrix

$$D(t) = \begin{pmatrix} \cos\left(B(t-t_0)\right) & \sin\left(B(t-t_0)\right) & 0\\ -\sin\left(B(t-t_0)\right) & \cos\left(B(t-t_0)\right) & 0\\ 0 & 0 & 1 \end{pmatrix} \tag{6}$$

where  $\mathbf{B}_0 = B\hat{\mathbf{x}}_3$ . The logical grid then follows the fast gyromotion with rotation frequency  $\omega_c = \frac{2\pi}{R}$ .

For a velocity  $\mathbf{w}$  on the logical grid, the physical value of the velocity at time  $t_m$  is given by  $\mathbf{v}(\mathbf{w}) = D(t_m)\mathbf{w}$ . Furthermore, let us denote by  $f^{(m)}$  the distribution function on the physical grid at time  $t_m$  and by  $g^{(m)}$  the distribution function on the logical grid at time  $t_m$ , that is

$$f^{(m)}(\mathbf{x}, D(t_m)\mathbf{w}) = g^{(m)}(\mathbf{x}, \mathbf{w})$$

(7)

In the advection steps, we always solve the characteristic equations in physical coordinates and then transform the resulting velocity coordinates to the logical grid.

We again split the  $\mathbf{x}$  and  $\mathbf{v}$  advections. Then, the solution at time t of the separate characteristic equations starting at  $(\mathbf{x}, \mathbf{v})$  at time  $t_0$  is given as

$$X_i(t; t_0, x, v) = x_i + (t - t_0)v_i, i = 1, 2, 3,$$

(8)

$$V(t;t_{0},v) = \begin{pmatrix} \cos((t-t_{0})B) & \sin((t-t_{0})B) & 0 \\ -\sin((t-t_{0})B) & \cos((t-t_{0})B) & 0 \\ 0 & 0 & 1 \end{pmatrix} v + \frac{1}{B} \begin{pmatrix} \sin((t-t_{0})B) & 1-\cos((t-t_{0})B) & 0 \\ \cos((t-t_{0})B) - 1 & \sin((t-t_{0})B) & 0 \\ 0 & 0 & B(t-t_{0}) \end{pmatrix} \mathbf{E}(\mathbf{x},t)$$

(9)

This yields the following advection steps on the rotating grid:

v advection: Defining

$$A(t) = \frac{1}{B} \begin{pmatrix} \sin\left((t - t_0)B\right) & 1 - \cos\left((t - t_0)B\right) & 0\\ \cos\left((t - t_0)B\right) - 1 & \sin\left((t - t_0)B\right) & 0\\ 0 & 0 & B(t - t_0) \end{pmatrix}$$

$$(10)$$

for given  $\mathbf{v}$  at time  $t_{m+1}$  the origin of the characteristic (9) at time  $t_m$  is given by  $\mathbf{V}(t_m; t_{m+1}, \mathbf{x}, \mathbf{v}) = D(t_m - t_{m+1})\mathbf{v} + A$   $(t_m - t_{m+1})\mathbf{E} = D(t_{m+1} - t_m)^{-1}\mathbf{v} + A(t_m - t_{m+1})\mathbf{E}$ . For the  $\mathbf{v}$  advection, we work with different physical grids at time  $t_m$  and  $t_{m+1}$ , namely

$$f^{(m)}(\mathbf{x}, D(t_m)\mathbf{w}) = g^{(m)}(\mathbf{x}, \mathbf{w}),$$

$$f^{(m+1)}(\mathbf{x}, D(t_{m+1})\mathbf{w}) = g^{(m+1)}(\mathbf{x}, \mathbf{w})$$

(11)

To find the representation of  $g^{(m+1)}$  at a point **w** of the logical grid, we first transform to the representation on the physical grid, use the characteristic equation to express it in terms of the solution at time  $t_m$  and finally transform back to the logical grid at time  $t_m$

$$g^{(m+1)}(\mathbf{x}, \mathbf{w}) = f^{(m+1)}(\mathbf{x}, D(t_{m+1})\mathbf{w})$$

$$= f^{(m)}(x, D(t_{m+1} - t_m)^{-1}D(t_{m+1})\mathbf{w} + A\mathbf{E})$$

$$= g^{(m)}(\mathbf{x}, D(t_m)^{-1}(D(t_m)\mathbf{w} + A\mathbf{E}))$$

$$= g^{(m)}(\mathbf{x}, \mathbf{w} + D(t_m)^{-1}A\mathbf{E}).$$

(12)

Note that the displacement  $D(t_m)^{-1}A\mathbf{E}$  on the logical grid is not dependent on **w**. In our implementation, we compute  $D(t_m)^{-1}A\mathbf{E}$  and then use successive 1-D interpolations along the three velocity coordinates axes of the logical grid.

**x** advection: In this step, the transformation between the physical and the logical grid does not change. We therefore have

$$g^{(m+1)}(\mathbf{x}, \mathbf{w}) = f^{(m+1)}(\mathbf{x}, D(t_m)\mathbf{w})$$

$$= f^{(m)}(\mathbf{x} - \Delta t D(t_m)\mathbf{w}, D(t_m)\mathbf{w})$$

$$= g^{(m)}(\mathbf{x} - \Delta t D(t_m)\mathbf{w}, \mathbf{w})$$

(13)

Compared to the case with fixed grid, the displacements in  $x_1$  and  $x_2$  are now dependent on both  $v_1$  and  $v_2$  and on time. On the other hand, we still have displacements independent of  $\mathbf{x}$ , and we can use successive 1-D interpolations along the three coordinate axes.

#### 2.4. Domain partitioning

Due to the curse of dimensionality, the memory requirements of a grid in the 6-D phase space are rather high already for coarse resolutions. Therefore, a distributed numerical solution of the problem is inevitable. Two choices of domain partitioning are considered in this article:

Domain decomposition (Crouseilles et al., 2009): The domain is decomposed into patches of 6-D data blocks, each representing a separate part of the domain. The patches are mapped to a 6-D logical grid of processors. For interpolations next to the domain boundary, halo cells with a width determined by the interpolation stencil have to be introduced and filled in advance with data from neighboring processors. This classical approach is widely used in parallelizations of lower dimensional physics and engineering problems, e.g. 2-D or 3-D computational fluid dynamics.

• Remap (Coulaud et al., 1999): Two decompositions of the domain are introduced, the first one distributing the domain only over the velocity dimensions (keeping the spatial dimensions local to each processor) and the second one distributing the domain only over the spatial dimensions (keeping the velocity dimensions local to each processor). For x advection steps, we use the first decomposition and for the v advection steps the second. In between the steps, the data are redistributed between the two decompositions using an all-to-all communication pattern.

The first strategy has the clear advantage over the remap method that the complexity of the communication pattern is reduced dramatically. On the other hand, the remap scheme is very well adapted to the split-step semi-Lagrangian method since the 1-D interpolations can be performed locally once the remapping has been applied. For the domain decomposition method, the 1-D stripes are usually distributed over separate domains. This makes the implementation more complicated and introduces an artificial time-step restriction (similar to a CFL condition) since the interpolation needs information of the function around the shifted data point  $x_i + \alpha$  in equation (4).

#### 2.5. Solution of Poisson's equation

The focus of this article is on the distributed solution of the 6-D Vlasov equation. However, in addition, we need to solve the 3-D Poisson problem (1). Since the problem is only 3-D, the compute time spent on its solution is almost negligible. For this reason, we use a pseudo-spectral solver based on fast Fourier transforms (FFTs) for the solution of the Poisson equation and remap the solution between domain decompositions that are local along the direction where FFTs are performed. In case a full 6-D domain decomposition is used (i.e. when the widths of all dimensions of the logical grid of processors are greater than 1), there are several subgroups of processors that span the whole x or v domain, respectively. As a first step, we compute the charge density by a reduction along the velocity dimension. This involves an all-to-all communication among groups of Message Passing Interface (MPI) processes of equal spatial domain. Then, the Poisson equation is solved on each subgroup of processors that span the whole x domain. By solving the same Poisson problem in each subgroup, we avoid another communication step for redistribution of the computed electric field.

Finally, we also include a diagnostic step in our stimulations that computes scalar quantities like mass, momentum, and energy, thus containing reduction steps over the full 6-D array.

#### 3. Interpolation on distributed domains

To compute the interpolated values, we can either use nodal interpolation formulas like Lagrange interpolation or global interpolants like spline interpolation. For simulations of the Vlasov–Poisson problem, cubic spline interpolation is most popular since it is well balanced between accuracy and efficiency. In combination with a domain decomposition, we however have to deal with the fact that the stripes are distributed between several processors, rendering a global interpolant impractical due to the required data exchange. Local splines as example considered for the 4-D Vlasov–Poisson equation by Crouseilles et al. (2009) are an interesting alternative. However, in this article, we focus on local Lagrange interpolation.

Let us recall the special structure of the interpolation task arising from our 1-D advections: The new value at grid point  $x_i$  is given by the interpolated value at  $x_i + \alpha$  for some displacement  $\alpha$  that is constant over the whole stripe. Let us decompose the displacement  $\alpha$  into a multiple  $\gamma \in \mathbb{Z}$  of  $\Delta x$  and a remainder  $\beta \in [0, 1]$ , that is

$$\alpha = (\gamma + \beta)\Delta x \tag{14}$$

Depending on the sign of  $\alpha$ , the origin of the characteristics for points close to the boundary of the local domain are displaced into a part of the domain that is stored on a neighboring process. Since the interpolation formula needs to be centered around  $x_i + \alpha$ , this yields an additional need for halo data points on one side of the domain. To keep the data transfer limited and regular, we need to impose a CFL-like condition to restrict the displacement. The number of additional halo points needs to be kept small since each additional halo point requires the exchange of a 5-D facet of the 6-D hyperrectangle.

#### 3.1. Fixed-interval Lagrange interpolation

Lagrange interpolation with a stencil that is fixed around the original data point  $x_i$  is a very simple interpolation formula for distributed domains. In this case, the interpolation formula with an odd number q of points is given by

$$f(x_j + \alpha) \approx \sum_{i=j-(q-1)/2}^{j+(q-1)/2} \ell_i(\alpha) f(x_i)$$

(15)

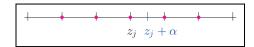

where  $\ell_i(\cdot)$  denotes the Lagrange polynomial centered at *i*. Figure 1 illustrates on which data points a five-point stencil is based. In this case, we have a static data exchange pattern where  $\frac{q-1}{2}$  points are needed from the processors on the left and on the right. On the other hand, we need to require  $|\alpha| \leq \Delta x$  for stability, that is, the scheme is rather restrictive on the time step.

**Figure 1.** Fixed-interval Lagrange interpolation based on a five-point stencil. The red dots indicate the points necessary to calculate the value at  $z_i + \alpha$ .

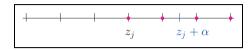

**Figure 2.** Centered Lagrange interpolation based on a four-point stencil. The red dots indicate the points necessary to calculate the value at  $z_i + \alpha$ .

#### 3.2. Centered Lagrange interpolation

As an alternative, we consider the Lagrange interpolation for an even number q centered around the displaced point  $x_i + \alpha$ . Then, the interpolated values are given as

$$f(x_j + \alpha) = f(x_{j+\gamma} + \beta) = \sum_{i=j+\gamma+q/2-1}^{j+\gamma+q/2} \ell_i(\beta) f(x_i)$$

(16)

The choice of the data points for the interpolation stencil is illustrated in Figure 2 for a four-point-formula. In this case, we need to exchange a layer of  $\max(\frac{q}{2} - \gamma, 0)$ points for the processor on the left and a layer of  $\max(\frac{q}{2} + \gamma - 1, 0)$  points to the right. As long as  $1-\frac{q}{2} \le \gamma \le \frac{q}{2}$ , that is  $|\alpha| \le \frac{q}{2}\Delta x$ , the total number of points that need to be exchanged per stripe is always q + 1. However,  $\gamma$  changes depending on the value of the other coordinates—and for v advections also with time. Therefore, the communication pattern is different for different stripes. On the other hand, for Vlasov-Poisson, the largest displacements usually appear for the x advections on grid points with high velocities. For an  $x_d$  advection, d=1,2,3, the displacement  $\alpha=\Delta t v_d$  is very simple and—for constant time steps—constant in time. In case we require  $|\alpha| \leq \frac{q}{2}\Delta x$  (to retain the minimal communication), the domain can be split in q blocks of different ranges of  $v_d$  with the same interpolation stencil and, hence, the same data exchange pattern. This way, we can relax the time step restriction but at the same time keep a regular pattern of both data exchange and computations for the advections. Note that this is only true for the case without background magnetic field. The rotation of the grid with the magnetic field changes the displacement of the x advection steps on the logical mesh.

Having detailed on the mathematical background, we now turn toward a discussion of the aspects and challenges of an efficient implementation and parallelization.

#### 4. Implementation and parallelization

Representing the 6-D distribution function on a grid requires a large amount of memory. Thus, it is of primary

importance that an implementation can be efficiently distributed over a sufficiently large number of compute nodes to make use of the aggregate memory provided by the nodes. For the same reason, the problem is not very well suited to be solved on GPUs due to their scarce memory resources.

For our implementation, we use object-oriented Fortran 2008, the MPI for distributed-memory parallelism, and OpenMP directives and runtime functions to add shared-memory parallelism. The developments were made within the framework of the library SeLaLib. The 6-D distribution function is discretized on a 6-D Fortran array. Since a central idea of our method is dimensional splitting, the advection algorithms exclusively work on 1-D stripes of the 6-D data. Since these stripes are non-contiguous in memory for any direction but the first dimension, non-contiguous 1-D slices are copied from the 6-D array into a contiguous buffer before the interpolated values are computed. The performance of these strided memory accesses can be greatly improved by cache blocking as is discussed in Section 4.2.

For the domain-decomposition-based parallelization approach, the 1-D stripes are distributed over multiple processes. The following section discusses how the halo data are stored to perform the interpolations.

#### 4.1. Distributed-memory parallelism

The domain decomposition approach requires a layer of halo cells around the processor-local data points to be able to conveniently compute the interpolants. In the discussion below as well as in our Fortran-based implementation, we consider global indices used locally in each MPI process.

A straight-forward way to handle the halos would be to include the cells into the 6-D array of the distribution function. Synonymously, this can be regarded as to work with 6-D arrays that overlap between neighboring processors. Padding the 6-D array with the halo cells has the advantage that the data are laid out contiguously in memory in the first dimension stripe-by-stripe, that is, the interpolation routines can work directly on the array in this special case. Stripes along higher dimensions are conveniently accessed via Fortran-style linear indexing, however, one has to keep in mind that the elements are laid out in memory in a strided fashion. It is important to avoid Fortran array slicing operators which cause temporary arrays to be used. Performance can be improved dramatically by implementing a cache blocking scheme using 2-D buffer arrays, see below. Moreover, using halos, there is no need for special treatment of periodic boundary conditions during the advection

A second possibility is to allocate the halo cells separately from the 6-D array of the distribution function, that is, there is no index overlap on the 6-D array between neighboring processes. Note that in this situation the halo buffers are identical to the MPI receive buffers.

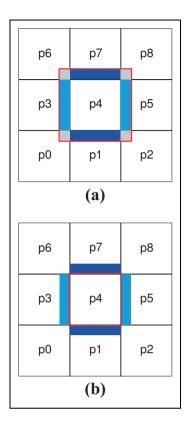

Figure 3. Schematic diagram of a data layout example, simplified to two dimensions and distributed over nine MPI processes labeled p0...p8. The square tiles represent the processor-local parts, the blue and cyan blocks the halo data needed for the advections along the first and the second dimension. The red square shows the data array stored by processor p4 for the two different data layouts. Layout (a) allocates the halo cells as part of the data array. Layout (b) allocates the halos as independent arrays. For layout (a), the gray blocks in the corners are unused. (a) Local arrays with indices that overlap between different processes and (b) local arrays with indices that do not overlap between different processes. MPI: Message Passing Interface.

Figure 3 shows these two possibilities. In a 6-D array which includes the halo cells, one also has to allocate the corner points (displayed gray in Figure 3(a)) as well, even though they are not used by any of the 1-D interpolators. As is well-known, the volume of a hypercube mostly concentrates in the corners, therefore it is desirable to avoid memory allocation there. Moreover, in case the algorithm uses a different number of halo cells on different blocks of data, the 6-D array has to include the maximum number of halo cells in any direction. Therefore, we have chosen the second approach, using halo cells allocated separately from the 6-D array of the distribution function. It avoids the aforementioned disadvantages and is in particular superior with respect to memory efficiency. Moreover, we can also exploit the fact that we only need the halo cells along one dimension at a time. Once allocated, the halo buffers can be reused.

If we assume a MPI-process-local grid of size  $N^6$  and a halo width of w cells on each side of the domain, the basic memory requirements for the domain decomposition scheme are  $N^6 + 2wN^5$  (for the core 6-D array and two

**Table 1.** Comparison of the theoretical minimum memory requirements per MPI process for both algorithms under consideration.<sup>a</sup>

|    | Allocated n | nem. (GB) | Communicated mem. (GB) |        |  |

|----|-------------|-----------|------------------------|--------|--|

| N  | remap       | d.d.      | remap                  | d.d.   |  |

| 16 | 0.25        | 0.17      | 0.5                    | 0.28   |  |

| 32 | 16.00       | 9.50      | 32.00                  | 9.00   |  |

| 40 | 61.04       | 35.10     | 122.08                 | 27.47  |  |

| 64 | 1024.00     | 560.00    | 2048.00                | 288.00 |  |

MPI: Message Passing Interface.

<sup>a</sup>A distribution function at a resolution of  $N^6$  local points is considered, in addition we assume for the domain decomposition case (d.d.) two halo buffers with a width w=3 points each. Note that additional buffers which may be required, for example, by the MPI library, are not accounted for. Moreover, the table shows for each resolution the data volume that is communicated per time step per process ( $p \to \infty$  for remap).

halo buffers of size  $wN^5$  on each side). Note that an additional send buffer of the size of a single halo buffer is needed. In a neighbor-to-neighbor communication, two data blocks of size  $wN^5$  need to be communicated for each 1-D advection step. For the remap scheme, on the other hand, two copies of the local  $N^6$  buffer are needed and, in addition, MPI send and receive buffers. Between each block of  $\mathbf{x}$  and  $\mathbf{v}$  advections, data blocks of size  $\frac{1}{p}N^6$  have to be communicated to each of the p-1 other MPI processes, that is, a total fraction of  $\frac{p-1}{p}$  of the local data block is sent. In practice, the actual memory requirements may be even higher due to MPI-internal buffers.

Table 1 compares the theoretical memory requirements for a typical process-local number of points per dimension for the two memory layouts. Note that the remap parallelization uses two 6-D data arrays for the two remap data layouts. The comparably low memory consumption of the domain decomposition implementation is especially advantageous on systems where fast memory is a scarce resource, for example, on certain manycore chips.

Moreover, based on the numbers from Table 1, one can give a straightforward estimate of the resolution possible on a cutting-edge high-performance computing (HPC) system with approximately 100 GB memory per two-socket node. Considering the domain decomposition algorithm and putting two MPI processes per node with  $32^6-40^6$  points each, a grid size of  $128^6-160^6$  would fit on 2048 nodes. Further increasing the resolution, for example, in velocity space, the problems of size  $128^3 \cdot 256^3 - 160^3 \cdot 320^3$  would fit on 16,384 nodes.

#### 4.2. Data access for I-D interpolations

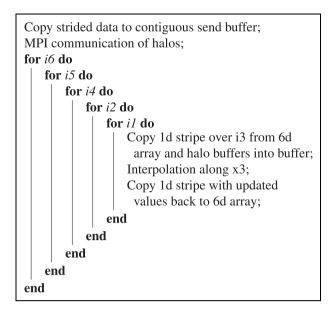

On the distributed domain, the advection along a dimension takes the form shown in Algorithm 1 at the example of  $x_3$ . Note that for advections along the dimensions 2 to 6, we have to deal with increasingly large strides when the 1-D interpolation buffers are filled, causing a severe performance penalty due to cache misses as confirmed by profiling.

**Algorithm 1.** Advection along  $x_3$  without cache blocking.

The cache efficiency and the resulting performance can be greatly improved by a cache-blocking scheme similar to the schemes used to accelerate, for example, dense linear algebra operations. The blocking is based on a 2-D buffer array. Interpolations are performed along the first (contiguous) dimension. In the second dimension, the array is large enough to store at least a cache line of data. Algorithm 2 summarizes the loop rearrangements. A similar blocking has been implemented for all advection steps. For the advections along  $x_2$  to  $x_6$ , we extract the 1-D stripes in blocks along the first dimension.

#### 4.3. Shared memory parallelization

Both implementations, remap and domain partitioning, are carefully parallelized using OpenMP directives and runtime functions to exploit the shared-memory architecture of prevalent multicore CPUs using threads, in addition to the distributed-memory parallelization which employs MPI processes.

A significant advantage of introducing a hybrid parallelization in addition to MPI is that it allows to reduce the memory consumption and the communication volume significantly. Instead of running one MPI process per available processor core, each allocating and exchanging halo cells, it is superior to launch only one or two MPI processes per socket, each with a proportionate number of threads pinned to the cores of that socket. All threads thereby share the halo cells.

Let us illustrate this effect by giving a simple numerical example. Consider a 64<sup>6</sup> simulation using seven-point Lagrange interpolation that shall be run on 64 compute nodes with 64 cores each, implying a grid size of 32<sup>6</sup> points per node. If a plain MPI setup is chosen, each node would run 64 MPI processes with a local grid size of 16<sup>6</sup> points, totaling up to 4096 MPI processes. On the other hand, we

**Algorithm 2.** Advection along  $x_3$  with cache blocking.

might consider an (extreme) hybrid setup running only 1 MPI process per node with a local grid size of 32<sup>6</sup> points. The 64 processes of the plain MPI setup would allocate 11 GB of memory per node for the distribution function and the halo cells and communicate 36 GB per time step, 18 GB of which beyond the node over the network. In contrast, the hybrid setup would require 9.5 GB per node and communicate 18 GB over the network.

We conclude that, first, it may be advantageous to use as few MPI processes as possible from the memory and communication point of view. Second, while the hybrid setup eliminates intra-node communication, the internode communication volume stays the same compared to the plain MPI case, with larger message sizes though.

A potential disadvantage of a naive hybrid approach is due to the fact that a significant fraction of the threads would be idle during the data-intense halo exchanges; however, by introducing an advanced pipelining scheme, we are able to hide the communication times to a large extent as is discussed in the following section.

#### 5. Performance optimization

Performance optimization work aims at maximizing the node-level performance simultaneously with the parallel scalability that are conflicting goals to some degree. In the

| System    | SuperMUC                              | DRACO                               | KNL node                               | Marconi-KNL                            |

|-----------|---------------------------------------|-------------------------------------|----------------------------------------|----------------------------------------|

| CPU       | Intel SandyBridge 2 ×<br>Xeon E5-2680 | Intel Haswell 2 ×<br>Xeon E5-2698v3 | Intel Knights Landing Xeon<br>Phi 7210 | Intel Knights Landing Xeon<br>Phi 7250 |

| Cores     | 2×8                                   | 2×16                                | 64                                     | 68                                     |

| Threads   | up to 2 per core                      | up to 2 per core                    | up to 4 per core                       | up to 4 per core                       |

| Frequency | 2.7 GHz                               | 2.3 GHz                             | I.3 GHz                                | I.4 GHz                                |

| Memory    | 2 × 16 GB (50 GB/s)                   | 2 × 64 GB (68 GB/s)                 | 16 GB MCDRAM (450 GB/s)                | 16 GB MCDRAM                           |

| ,         | ,                                     | ` ,                                 | 96 GB (90 GB/s)                        | 96 GB of DDR4                          |

| SIMD      | AVX                                   | AVX2                                | AVX-5Ì2                                | AVX-512                                |

| Network   | Mellanox FDR10 (40 GB/s)              | M'x FDR14 (56 GB/s)                 | _                                      | Intel OmniPath (100 GB/s)              |

Table 2. Specification of the hardware used for performance evaluation.<sup>a</sup>

<sup>&</sup>lt;sup>a</sup>On the KNL node, only the fast on-chip MCDRAM was used as indicated by the underline.

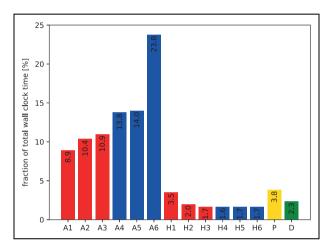

**Figure 4.** Profile of the domain decomposition implementation running a 32<sup>6</sup> case with seven-point Lagrange interpolation on a single Haswell core, where the letter "A" denotes advection, the letter "H" denotes a halo-exchange operation, the letter "P" denotes the Poisson solve operation, the letter "D" denotes the diagnostic computation, and the direction is given by its number.

scope of this article, we target recent x86\_64 systems with multicore or many-core CPUs as found in the vast majority of today's HPC systems. Details on the systems under closer consideration are given in Table 2 in the following section where performance results will be discussed.

#### 5.1. Performance profile

Figure 4 shows a breakdown of the costs of the various operations involved during a time step of the domain decomposition solver running on a single core without any parallelism. The profile is clearly dominated by the advection computations ("A") including the Lagrange interpolation. Going from the direction of the first to that of the sixth dimension, the cost of the advection monotonically increases. This effect is caused by the fact that memory accesses become more and more strided. It is important to note that the effects of the striding are already mitigated by the cache blocking scheme that preserves a cache line, once loaded. Moreover, the prefetch efficiency of the processor appears to deteriorate with increasing strides. The

preparation of the halo buffers ("H"), which also involves copies from strided into contiguous memory (however of much less data compared to step "A"), is by far less time-consuming. However, neighbor-to-neighbor MPI communication is included in "H" which becomes important when the parallelization spans multiple nodes. Finally, the Poisson-solve step and the diagnostics account for roughly 4% and 2% of the total runtime, respectively.

In addition to simple and lightweight timing facilities, we used the tools Amplifier and Advisor from the Intel Parallel Studio XE package to obtain low level information on the performance and limitations of various parts of the code. Based on that information, code improvements were implemented, the most important of which are detailed below.

#### 5.2. Single-core performance

Without considering MPI communication, the major factors limiting performance of both the 6-D Vlasov implementations, the remap and the domain decomposition, are due to the fact that the vast majority of the memory accesses—except the ones along the first dimension—are strided. A cache blocking scheme mitigates this issue significantly, as illustrated by performance numbers below. Nevertheless the code remains memory bound. The increase in runtime from "A1" to "A6" in Figure 4 reflects the aspect of the increasingly strided memory accesses.

In addition, single instruction, multiple data (SIMD) vectorization is a key factor to achieve performance on modern CPUs. While in early days (SSE2) only a factor of two was lost when vectorization was ignored for double-precision operations, the potential loss has grown to a factor of 4 (AVX) or 8 (AVX512) on more recent CPU models. We have implemented Lagrange interpolation routines such that the compiler is able to generate vectorized code that we verified carefully using compiler reports and performance tools. Arrays are aligned to 64 byte boundaries, though the large 6-D array of the distribution function is not padded in order not to waste memory. In general, the compiler is able to generate vectorized code for most of the loops.

Running 100 time steps of a 16<sup>6</sup> (32<sup>6</sup>) case with sevenpoint Lagrange interpolation on a single Skylake core, the

domain decomposition code achieves a floating point operation rate of 3.9 (2.8) GFLOP/s, which translates to 2.5 (2.5) GFLOP/s on the Haswell core. This value represents about 6.8% of the Haswell core's theoretical peak performance. Note that the smaller setup is relatively faster on the Skylake CPU. We measured the FLOP rates using performance counters on Skylake and converted the result to Haswell using the runtime ratio. Note that the measurement covers the complete run including startup and shutdown phases and includes inevitable memcopy operations that do not perform any FLOPs at all. Around 90% of the floating point instructions issued are vectorized. These numbers once more illustrate the main performance challenge of 6-D Vlasov codes resulting from memory boundedness due to strided memory accesses in combination with a moderate arithmetic intensity.

Finally, to quantify the effect of the cache blocking algorithm, the aforementioned test runs with 100 time steps take on the Haswell core in total about a factor of 2.4 longer for both cases with the cache blocking disabled. The higher the dimension to be interpolated along, the more effective and important the cache blocking becomes in general, accelerating certain parts of the code such as the loop over  $x_6$  by up to a factor of 20, as measured using performance profilers.

#### 5.3. Node-level performance

A modern compute node provides several cores that are organized in non-uniform memory access (NUMA) domains such that groups of cores share L3 caches and memory channels these cores can access fastest. Optimizing for the NUMA domains by careful process and thread pinning at runtime turns out to be important. Typically, MPI processes are pinned to sets of cores on sockets, and threads are pinned to individual physical cores from these sets. When overlapping communication and computation as introduced in the following subsection, it turns out to be advantageous only to pin the processes to constrain the threads within NUMA domains, and in addition, to use hyperthreads.

As the typical structure of the code are six-fold nested loops, a standard loop-based OpenMP parallelization strategy proved rather successful. From benchmark measurements at various resolutions, it was concluded that the runtime is minimized when the outer two loops are collapsed into a single one to increase the granularity of the parallel workload and when static loop iteration scheduling is used. Each thread is able to benefit from cache blocking and vectorization in the inner loops. Virtually any workload in the code is parallelized using that technique. As a result, the application scales well over a single node in pure OpenMP as shown in Section 7.

#### 5.4. Distributed-memory performance

Semi-Lagrangian 6-D Vlasov solvers are unavoidably intense in terms of memory and data communication volume

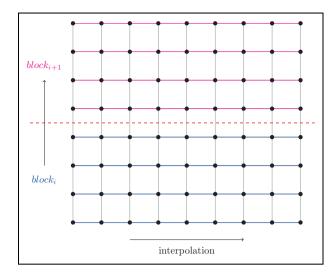

**Figure 5.** Blocking of a 2-D example grid, perpendicular to the direction along which is to be interpolated.

(cf. Section 4.1). For the domain decomposition approach, typical sizes of single MPI messages are in the range of  $\mathcal{O}(0.1)$ – $\mathcal{O}(1)$  GB, while modern interconnects achieve a bandwidth of up to approximately 10 GB/s per node. It is therefore important to mitigate the cost of the data transfers as much as possible, firstly by careful planning of the process grid, by overlapping communication and computation, and in addition by means of data reduction.

As outlined in Algorithm 2, each advection step starts with MPI communication to fill the halo buffers in the neighbor processes, before the interpolations are performed. We use standard blocking point-to-point MPI communication, in particular the MPI sendrecv() call, which has proven to be fastest when compared to non-blocking communication in early tests. For lower dimensional domain decomposition codes, MPI 3 neighborhood collectives are typically used to implement these halo exchanges efficiently, in particular the MPI\_Neighbor\_alltoall() call. However, in 6-D, we cannot afford to allocate all the halo buffers at the same time that would be necessary to use such neighborhood collectives. In fact, as explained previously in Section 4.1, we use dynamic halos that are reused for the different directions, one at the time. Therefore, conventional point-to-point communication is the preferred way to exchange the data in 6-D.

In hybrid-parallel setups the initial MPI communication would only keep a single thread busy while all the other threads were idle. The trend toward systems with increasingly more cores per socket suggests to use multiple threads per MPI process to overlap ("pipeline") the communication with useful computation.

5.4.1. Simultaneous communication and computation. To implement pipelining of communication and computation, we block the data along a dimension different from the one we intend to interpolate along and perform data exchange

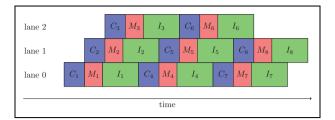

**Figure 6.** Schematic showing the temporal overlap of the copy operation (C), the MPI communication (M), and the interpolation (I) for a single MPI process at the example of an eight-fold blocked advection.

and computation simultaneously on the resulting independent blocks, as illustrated in Figure 5.

Here, we consider the Lagrange interpolation with fixed interval because in this case we do not have to handle additional blocking due to asymmetric data exchange. Moreover, to avoid a second layer of blocking, we do not consider blocks with different halo patterns. Anyway, the overhead introduced by not minimizing the halo widths for some blocks is less problematic when the communication is overlapped with computations.

For each data block, the advection computation consists of three steps: copy (generally non-contiguous 6-D) data into coherent buffer (C); MPI\_sendrecv() communication (M); and computation of interpolated values (I).

For each data block, these three steps need to be performed in the given order, but there is no dependency between different blocks. Nevertheless, we have to enforce some ordering to avoid a capacity overload of resources such as the maximum number of simultaneous hardware threads. Given the three-fold structure of the advection, we propose a straight forward pipelining scheme using three lanes as shown in Figure 6.

To keep the overhead of the start-up and the final phase as small as possible, we overlap communication and computation of advections for different dimensions as well. To give an example, let us start with the  $x_1$  advection. Once we have reached the communication step (M) of its last block, we can already start to copy (C) and communicate (M) the data needed for the following  $x_2$  advection in the first data block—provided that the  $x_2$  dimension is contiguous in each block.

5.4.2. Implementation details on the pipelining scheme. Our pipelining implementation relies on a thread-safe MPI library and on OpenMP threads—requirements that are provided by most modern compilers and libraries. The steps C, M, and I can be regarded as tasks with interdependencies.

In the following, we provide details on the implementation, referring to Algorithm 3. Initially, a list of all blocks is built, where each list element contains metadata such as block indices, the number of nested threads for the steps C and I, and two OpenMP locks, one for the C step and one for the M step. In the scheme proposed in the following, the orchestration of the tasks is explicitly controlled using a

```

Build list of N blocks, add dummy block, initialize

OpenMP locks:

Enter OpenMP parallel region with 3 threads;

for i (OpenMP: schedule static, chunk size 1) \leftarrow 1 to

N do

Set lock of C(i+1);

Set lock of M(i+1):

end

for i (OpenMP: schedule static, chunk size 1) \leftarrow 1 to

N do

Set lock of C(i);

C†(i);

Unset lock of C(i);

Unset lock of C(i+1);

Set lock of M(i);

M(i);

Unset lock of M(i):

Unset lock of M(i+1);

I†(i);

end

Leave OpenMP parallel region;

Destroy locks;

```

**Algorithm 3.** Control layer of the pipelining algorithm implemented using OpenMP directives and runtime functions. The symbol † indicates the use of nested parallelism in the worker functions C and I.

parallel region with a fixed number of three threads which uses internal loops with static scheduling and a chunk size of one such that the ordering is deterministic. For N blocks, thread i, with i = 0, 1, 2, manages the work on the blocks  $\ell = i + 1 + 3k$ ,  $k = 0, \dots, \frac{N-i-1}{3}$ , performing the steps C, M, and I one after the other. In the steps C and M, we use nested OpenMP parallelism to make use of all the available threads. Apart from managing locks and calling the tasks, the outer loop does nothing. To make best use of the network resources, we ensure that the resources are dedicated to one C and one M operation at a time, that is, only a single communication M is allowed to take place at a time. Therefore, thread i initially locks all the C and M operations of thread mod(i + 1, 3) and only releases the lock on  $M_{\ell+1}/C_{\ell+1}$ , when it has finished  $M_{\ell}/C_{\ell}$ . As a result, the pipelining scheme with overlapping tasks as shown in Figure 6 arises.

At runtime, we have to specify two parameters that influence the performance of the implementation: the number of blocks and the number of threads used by each of the C and I tasks. The smaller the blocks are chosen the shorter the start-up and finishing phases become during which communication and computation cannot be overlapped. On the other hand, the blocks should not be chosen too small to keep the overhead low. As the second parameter, one needs to decide how to assign the available threads to the C and I steps. Note that the first C and the last I step may use more threads since they do not fully overlap with other

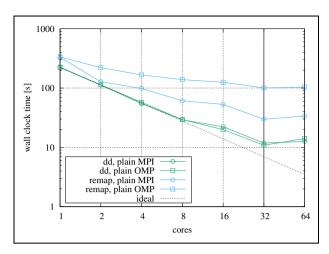

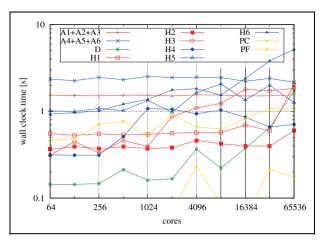

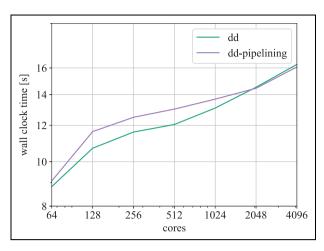

operations. It turns out that the use of simultaneous multithreading (hyperthreading) is beneficial in concert with the pipelining scheme. The implementation assures that not more than the maximum available number of hardware threads are used to avoid congestion. The cost induced by the lock management is negligible compared to the computation, for example, for a typical number of four blocks per direction as shown in Figure 15 for real run data. In particular, the benchmark numbers show that the pipelined code is as fast as the non-pipelined code for small core numbers (cf. Figure 13) and is strongly superior when going to larger core numbers in a weak-scaling scenario (cf. Figure 14). A detailed discussion including benchmark results is presented in Section 7.

An obvious choice for the advections in  $\mathbf{x}$  is to block the 6-D distribution function along the 6th dimension  $v_3$  that corresponds to the slowest varying loop index resulting in blocks that are laid out contiguously in memory. Thus, our pipelining scheme combines the three  $\mathbf{x}$  advection steps without any inner global synchronization point. In the same way, the  $\mathbf{v}$  advection block can be combined. Here, the blocking of the data is performed along  $x_3$ .

An alternative implementation based on OpenMP 4.0 tasks with an explicit dependency graph for the steps C, M, and I, in combination with non-blocking MPI communication had also been evaluated. However, this line of work was finally abandoned due to inferior performance. The major issue with this implementation was that the timing of the execution of the tasks differed strongly between different MPI processes, decided internally by the OpenMP task runtime. Using the tightly controlled loop-based scheme presented above, it was found that conventional blocking MPI communication in dedicated threads provides superior performance, reproducibility, and, moreover, has lower memory requirements.

5.4.3. Optimization of the halo-exchange communication. As pointed out before, the 6-D Vlasov solver is a highly communication intensive application, rendering good large-scale parallel scalability a difficult goal to achieve. From our experiments, we find that the implementation can scale well even when spanning multiple islands on a HPC system, if the process grid is laid out in an optimum way and communication and computation are pipelined.

The HPC systems under consideration have the network topology of a pruned fat tree. An island of the system is designed such that each node of the left half of the island is theoretically able to communicate with the corresponding node of the right half of the island simultaneously at the same bandwidth, termed the bisectional bandwidth. Going beyond an island, the bisectional bandwidth is reduced. Here, the blocking factor is decisive, which is, for example, 1:4 on a system used below, meaning that the interisland bisectional bandwidth is only a quarter of the intraisland one. We are therefore challenged with at least four levels of interconnection speeds between MPI processes, namely communication via shared memory on the same socket,

intra-node communication via shared memory between different sockets, intraisland and interisland communication via the network.

In addition to the pruned fat tree topology, there are other topologies, for example, high dimensional torus interconnects. We would expect the 6-D domain decomposition algorithm to benefit highly from such networks because a reduced bisectional bandwidth is avoided, whereas on a pruned fat tree it turns out to be one of the major challenges to scalability.

It is crucial to optimize the Vlasov solver and also choose the problem setup for the network topology of the machine as well as possible to prefer fast communication paths for the largest messages, which is discussed in the following.

5.4.4. Process grid optimization. The ordering of the 6-D process grid can be chosen such that communication between remote processes is kept as small as possible. A batch system lays out the MPI processes in a certain pattern, often placing the ranks consecutively on the nodes, one island after the other. When constructing the 6-D process grid, the MPI ranks are placed in row-major (C) order, indexing processes p like p[i, j, k, l, m, n], with n being the fastest varying index. Consequently, the neighboring processes are closest in  $x_6$ , direction n, whereas they are separated increasingly on the network when going to the  $x_1$ , direction i. Depending on the shape of the process-local part of the 6-D grid and on the (potentially different) interpolation orders along x and v, the process grid layout can be chosen such that interisland communication is minimized. Despite this optimization, certain directions still communicate mainly between islands. In our experiments, it turned out to be beneficial to transpose the grid such that neighboring processes are closest in  $x_1$ . In this case, the processor groups that solve the Poisson problem are close. On the other hand, the reductions over velocity to compute  $\rho$  combine more remote processes. When overlapping communication and computations, this ordering is especially advantageous since the communication is more expensive the larger the stripe, that is, the longer it takes to gather the data for the advection.

To go one step further, we have experimented with communication patterns between islands that are more balanced in the time dimension. This is done by mapping consecutive MPI ranks onto blocks of 2<sup>6</sup> processes, that is, by rearranging the 6-D process grid completely. Our implementation uses known hostname schemes of HPC systems to perform the rearrangement. As the consequence of such rearrangement, the advection in each direction would perform interisland communication to some fraction, which would be useful to mitigate situations without rearrangement when only one or few directions are communicated between islands not hiding well behind computation. However, within the scope of this article, we did not enable such blocking because it did not turn out beneficial, the reason being that the per-process computational workload (the

local partition of the 6-D hypercube) was typically too small in relation to the halos.

It is important to point out that these process grid optimizations do not reduce the total amount of data that is to be communicated. We will turn toward possibilities to reduce the communicated data volume in the following section.

5.4.5. Reduction of the communication volume. The MPI messages sent between neighbor processes to fill the halos use by default 8 byte-wide double precision numbers. We have implemented the option to halve the communication volume and time by sending these messages in single precision, leading to an improved parallel scalability especially in interisland scenarios. However, one has to keep in mind that an additional error is introduced into the computation which requires careful validation. We therefore consider single precision messages an experimental tool.

When running the pipelined code in a hybrid fashion it turns out that—depending on the balance between threads and processes—a fraction of the threads is idle waiting for communication to finish. To continue along the lines of single precision messages, we have therefore experimented with floating point compression to further reduce the communication volume and time while utilizing the threads that would otherwise be idle. Naturally, a simple stream compression algorithm is not suitable to compress floating point data, rather a lossy algorithm tailored toward numerical data is required. The ZFP floating point compression algorithm, of which an implementation is freely available as a library, compresses blocks of 64 double precision numbers, taking the desired precision as a parameter (Lindstrom, 2014). The compression ratio achieved depends on the similarity of the numbers in the blocks. Adjusting the precision to match single precision, we typically observe a compression factor of approximately 4 for the halo data, improving parallel scalability over islands significantly. In particular, the compression step is rather expensive as will be shown briefly in the following. The compression option might become more relevant in the future when the pernode computational power continues to grow faster than the network bandwidth.

In Section 7, we present performance studies, detailing on the various challenges and the respective optimization approaches to tackle them.

#### 6. Numerical experiments

Before we benchmark our implementation and demonstrate the scalability of the code, we consider representative test problems with and without a background magnetic field and discuss accuracy and time-step restrictions (CFL-like conditions) for the various Lagrange interpolations on distributed grids. For the tests we look at the electric energy,  $H_e(t) := \frac{1}{2} \parallel \mathbf{E} \parallel_2^2$ , and how it evolves over time. The errors reported are absolute error, and we are only interested in the qualitative behavior of the error of the integrators of

various order around the CFL-like condition. Testing the accuracy of the various integrators at the CFL-like condition imposed by the domain-decomposition parallelization scheme will demonstrate that relatively high-order is needed to accomplish efficiency. However, this will cause a relatively large halo cells which are challenging for the distributed solution as we will see in the subsequent section.

#### 6.1. Vlasov-Poisson simulations

We first consider two test problems with no magnetic field, weak Landau damping, where the chosen resolution yields rather good accuracy, and a bump-on-tail instability with larger phase-space error, and compare the accuracy of the Lagrange interpolators of various order.

The initial value of the weak Landau damping problem is given as

$$f_0(\mathbf{x}, \mathbf{v}) = \frac{1}{(2\pi)^{3/2}} \exp\left(-\frac{|\mathbf{v}|^2}{2}\right)$$

$$\left(1 + 0.01 \sum_{\ell=1}^{3} \cos(0.5x_{\ell})\right)$$

(17)

The grid resolution is chosen to be  $16^3 \times 64^3$ , and we consider the error in the electric energy in the time interval [0,30] compared to a reference simulation on a grid with  $20^3 \times 80^3$  points and a time step of  $\Delta t = 0.005$  with Lagrange interpolation of order 8 in space and 7 in velocity.

The bump-on-tail test case has the initial value

$$f_0(\mathbf{x}, \mathbf{v}) = \frac{1}{(2\pi)^{3/2}} \left( 0.9 \exp\left(-\frac{v_1^2}{2}\right) + 0.2 \exp\left(-2(v_1 - 4.5)^2\right) \right)$$

$$\exp\left(-\frac{(v_2^2 + v_3^2)^2}{2}\right) \left(1 + 0.03 \sum_{\ell=1}^3 \cos(0.3x_\ell)\right)$$

(18)

and is solved on a mesh with 32 points per direction until time 15. The reference solution is simulated on a mesh with 40 points per direction, a time step of  $\Delta t = 0.0125$ , and Lagrange interpolation of order 8 in space and 7 in velocity.

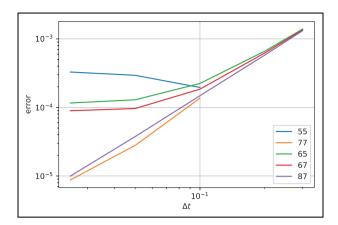

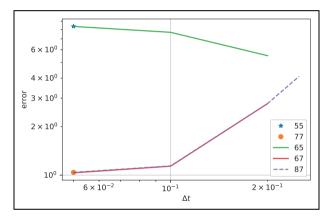

Figure 7 shows the error in the electric energy as a function of the time step for various orders of the Lagrange interpolator for the weak Landau damping example. Comparing the curves, we see that the error for the largest time step  $\Delta t = 0.3$  is almost the same for all considered interpolation formulas, that is, the temporal error dominates. Since we use a second-order Strang splitting method, the error reduces proportional to  $\Delta t^2$  as we reduce the time step until the interpolation error starts to dominate. The lower the order of the interpolation stencil the earlier this happens. Note that, once we have reached a time step where interpolation errors dominate, a further reduction of the time step may even yield an increase of the error.

**Figure 7.** Landau damping: error in electric energy as a function of the time step for various interpolators. The numbers indicate the stencil widths of the **x** and the **v** interpolations, respectively.

**Figure 8.** Bump-on-tail: error in electric energy as a function of the time step for various interpolators. The numbers indicate the stencil widths of the  $\mathbf{x}$  and the  $\mathbf{v}$  interpolations, respectively.

For this example, the displacement of the x advection exceeds one cell size for a time step above 0.13. Therefore, fixed Lagrange interpolation (odd order) is only stable for time steps smaller than 0.13. On the other hand, centered Lagrange interpolation shows good results for time steps beyond this. The results also show that for accuracy reasons, the time step should be chosen such that the displacement is on the order of the cell size or a bit above. Hence, a combination of centered Lagrange interpolation with blocked communication as described in Section 3.2 for the x advections and fixed Lagrange interpolation for the v advection is an efficient choice for the Vlasov–Poisson equation.

Figure 8 shows the results for the bump-on-tail test case. In this case, the spatial error is larger which is why larger time steps compared to the value of  $\Delta t \approx 0.073$  (which corresponds to the maximum time step where the displacement is bounded by one cell size) are advantageous. As in the previous case, we see that order 5 does not give satisfactory results and the use of Lagrange interpolation of order 6 in  $\bf x$  and 7 in  $\bf v$  gives best results. Note also that the absolute error is shown in the figure and the maximum

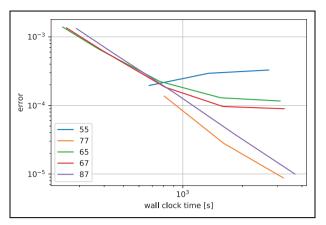

**Figure 9.** Landau damping: error in electric energy as a function of the wall clock time for various interpolators. The numbers indicate the stencil widths of the **x** and the **v** interpolations, respectively.

value of the electric field energy in the considered interval [0, 15] is about 205.

Figure 9 shows the accuracy as a function of the wall clock time for a simulation on a single node of the DRACO cluster with 32 MPI processes for the Landau case. We can see that the computing time increases with the order but the increase is very small. On the other hand, the increasing halo cells for increasing order will impact the performance more strongly when MPI communication between nodes is involved.

We conclude that the time step should be chosen around the CFL-like condition or even somewhat above it (enabled by the use of one-sided halo blocks as described in Section 3.2) and that an integrator of order five and below does not yield the necessary accuracy at that temporal resolution.

#### 6.2. Simulations with rotating mesh

As an example of a simulation with a strong background magnetic field  $\mathbf{B}_0$ , let us consider a simulation with initial value given as

$$f(\mathbf{x}, \mathbf{v}) = \left(1 + \alpha \cos(k_{\perp} x_1) \cos(k_{\parallel} x_3)\right) \exp\left(-\frac{\parallel v \parallel^2}{2}\right) \quad (19)$$

In this case, the gyrofrequency is given by  $\omega_c = \frac{2\pi}{B}$ . To understand the time-step restrictions of our distributed memory parallelization with the rotating grid, we estimate the maximum displacement in the various advection steps. The displacement of an  $x_1$  advection at time t is given by

$$|\Delta t \Big( \cos(Bt) v_1 + \sin(Bt) v_2 \Big)|$$

$$\leq \Delta t \Big( |\cos(Bt)| v_{1,\max}| + |\sin(Bt)| v_{2,\max} \Big)$$

$$\leq \Delta t \sqrt{2} \max_{\{v_1, \dots, v_2, \dots, v_n\}} (20)$$

Here, we use  $v_{i,\text{max}}$  to denote the (in modulus) largest value of the velocity on the computational grid. For the displacement of the  $x_2$  advection, the same estimate can be derived.

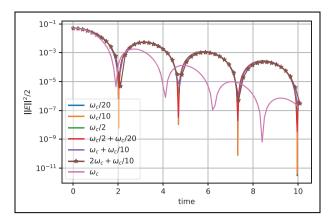

Figure 10. Simulation with rotating velocity grid: electric energy as a function of time for various time steps (given in the legend).

The displacement of the  $x_3$  advection is given by  $\Delta t v_3$  and can thus be estimated by  $v_{3,\max} \Delta t$ .

The displacement of the velocity advections depends on the electric field. The electric field induced by the initial condition is given as

$$\mathbf{E} = -\frac{\alpha}{k_{\perp}^{2} + k_{\parallel}^{2}} \begin{pmatrix} k_{\perp} \sin(k_{\perp} x_{1}) \cos(k_{\parallel} x_{3}) \\ 0 \\ k_{\parallel} \cos(k_{\perp} x_{1}) \sin(k_{\parallel} x_{3}) \end{pmatrix}$$

(21)

If the electric field is damped in time, we can estimate the electric field by  $\frac{\alpha k_{\perp}}{k_{\perp}^2 + k_{\parallel}^2}$  for the perpendicular and  $\frac{\alpha k_{\parallel}}{k_{\perp}^2 + k_{\parallel}^2}$  for the parallel direction.

Let us consider the following parameters,  $B=20\pi$  ( $\omega_c=0.1$ ),  $k_\perp=k_\parallel=0.5$ ,  $\alpha=0.01$ . Using 16 grid points along each spatial dimension and 32 points along the velocity dimensions as well as a velocity domain limited to [-6,6], the grid spacing takes the values of  $\Delta x_i=\frac{4\pi}{16}=\frac{\pi}{4}$  and  $\Delta v_i=\frac{12}{13}=0.375$ .

The maximum displacement along  $x_1$  and  $x_2$  direction is given by  $\Delta t 6\sqrt{2}$  and hence the displacement is restricted to one cell size if  $\Delta t \le 9.256 \cdot 10^{-2}$ , that is, slightly below one period of the gyration. On the other hand, the displacement of the velocity advections is bounded by  $0.01\Delta t$  such that the displacement is smaller than the grid size for all  $\Delta t < 37.5$ . Figure 10 shows the electric energy as a function of time from simulations with various time steps. In the x advection steps, we use centered Lagrange interpolation with six points and in the v advections a fixed seven-point Lagrange interpolation formula. Note that we use symmetric halo cells of sufficient size for the  $x_1, x_2$  directions since a static blocking as in the pure Vlasov-Poisson case is not possible on the rotating mesh. Comparing the evolution of the electric energy for the various time step sizes, one can see that deviations from the reference run with a tiny time step at  $\Delta t = \omega_c/20$  are rather small, that is, rather good results can be obtained for time steps above the gyrofrequency. In particular, we can use time steps close to  $\omega_c/2$  that would yield a completely nonlocal stencil if we would not rotate the mesh. However, the time step cannot be a multiple of  $\omega_c$  (as clearly visible in Figure 10) since then the magnetic field cancels out in the propagator on the rotating mesh, and the simulation completely neglects the magnetic field.

#### 7. Performance benchmarks

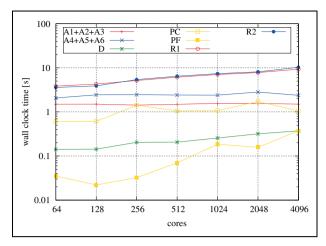

To systematically compare and evaluate the performance and the scalability of the remap and the decomposition implementations, a series of runs was performed, going from a single compute node to a HPC cluster and further up to multiple islands on a supercomputer. For most of our basic tests and during iterative performance optimization work, we used a two-socket Intel Haswell-type node, the building block of the DRACO HPC cluster at MPCDF.<sup>3</sup> Moreover, an Intel Xeon Phi KNL node was available, running in "flat" mode with the 16 GB of MCDRAM available as a separate memory domain. All the runs performed on the KNL used the fast MCDRAM exclusively. Finally, we present large-scale runs performed on the SandyBridge partition of the SuperMUC HPC system of the Leibnitz Supercomputing Center, covering up to eight islands with 64k physical cores. Table 2 provides details on the specifications of the compute nodes.

The Landau damping test case was chosen in each run. We consider a seven-point Lagrange interpolation for both **x** and **v** advections, since it proved to be a good choice in terms of accuracy and flexibility according to the numerical comparison presented in the previous section. Note that the six-point centered Lagrange interpolation has the same halo width and therefore shows a similar performance. Any wall clock time given refers to the computation of five time steps. The initial time step is excluded from the time measurement to compensate for the initialization overhead of the MPI library that can be significant.

To compile and link the code, recent versions (16 and 17) of the Intel compiler were used throughout this work, with the optimization flags set to -O3 -xHost -ipo-separate -qopenmp. On DRACO and on the Xeon Phi node, Intel MPI is used whereas on SuperMUC, IBM PE is used. We first look at the performance on a single node, focusing on both process (MPI) and thread (OpenMP) parallelism.

#### 7.1. Node-level performance

To evaluate the performance of the OpenMP-based parallelization in comparison to MPI, we present scalings on a single compute node in this section.

Each run was repeated five times to average out small variations between individual runs that were found to be on the order of up to 5%. A problem size of 32<sup>6</sup> was chosen since it is quadratic and represents a reasonable (though moderately large) size for a per-socket workload on the relevant systems, the net size of the distribution function being 8 GB in double precision.

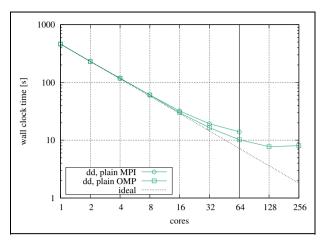

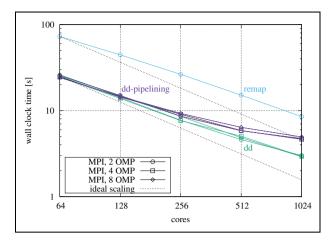

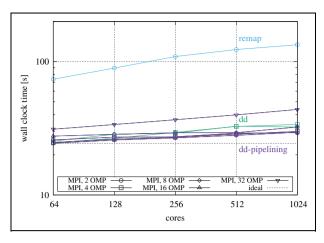

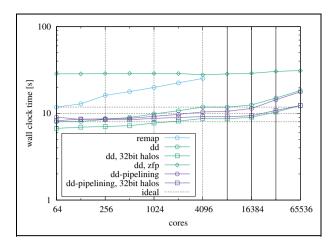

**Figure 11.** Strong scaling in pure MPI and pure OpenMP on the Haswell node, comparing the domain decomposition code with the remap implementation, running five time steps of a 32<sup>6</sup> case with seven-point Lagrange interpolation. The vertical line indicates the transition to simultaneous multithreading. MPI: Message Passing Interface.