#### Technische Universität München Fakultät für Elektrotechnik und Informationstechnik Lehrstuhl für Integrierte Systeme

# Redundanzfreie Fehlerbehandlung in echtzeitfähigen FPGA Schaltungen

Dipl.-Ing. Michael Frischke

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines Doktor-Ingenieurs genehmigten Dissertation.

Vorsitzende: Univ.-Prof. Dr. rer. nat. Doris Schmitt-Landsiedel

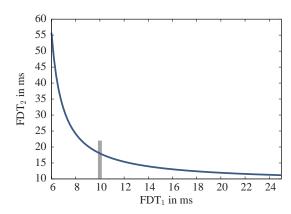

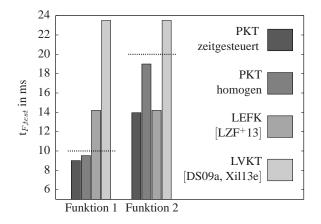

Prüfer der Dissertation:

1. apl. Prof. Dr.-Ing. habil. Walter Stechele

2. Univ.-Prof. Dr.-Ing. Georg Sigl

Die Dissertation wurde am 24.04.2015 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 13.10.2015 angenommen.

## Kurzdarstellung

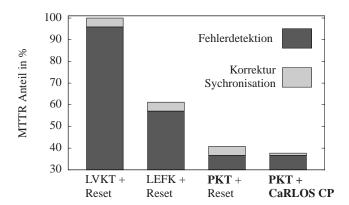

In sicherheitsrelevanten oder hochverfügbaren Anwendungen kann je nach Funktionsanforderung flexible Hardware eingesetzt werden. Traditionell werden dazu zusätzliche Redundanzmechanismen zur Fehlerdetektion und ein Reset zur Fehlerkorrektur flüchtiger Fehler verwendet. Für den wettbewerbsfähigen Einsatz flexibler Hardware bei hohem Produktionsvolumen sind jedoch kostengünstige Mechanismen zur Fehlerbehandlung im Bereich von wenigen Millisekunden notwendig. Speziell in echtzeitfähigen Kraftfahrzeug Steuergeräten mit programmierbarer Hardware in Form von Field Programmable Gate Arrays (FPGAs) können diese Mechanismen zu einer reduzierten Mittleren Fehlerdetektions- und Reparaturzeit (MTTR) und somit höheren Verfügbarkeit beitragen. Hierzu wird die redundanzfreie Fehlerdetektion, Fehlerkorrektur und Echtzeit-Synchronisation innerhalb des FPGAs ohne große Einflüsse auf das Gesamtsystem verbessert und optimiert.

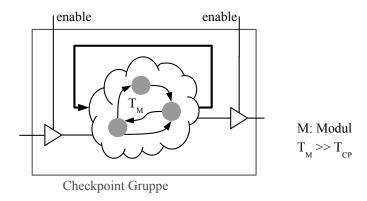

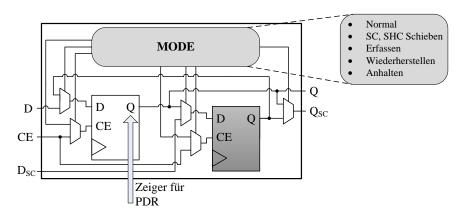

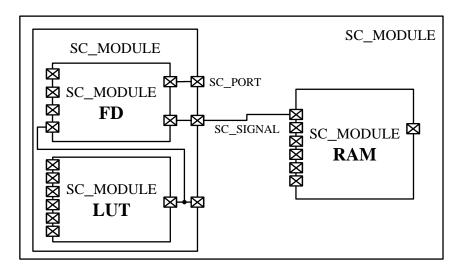

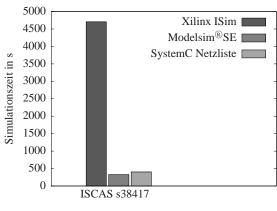

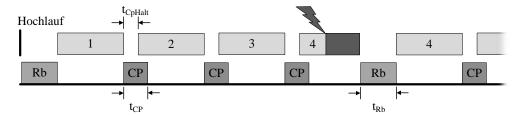

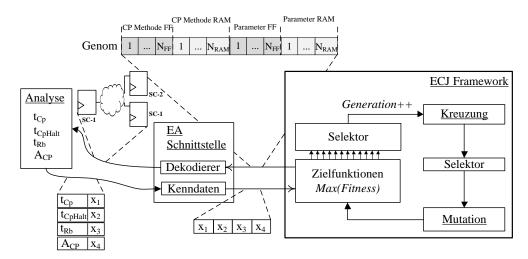

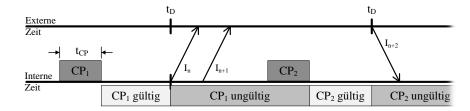

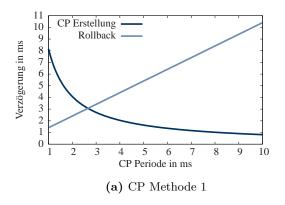

Kurze Synchronisationszeiten mit dem Gesamtsystem sind eine Anforderung zum Erreichen einer hohen Verfügbarkeit der der FPGA Schaltung. Klassische Reset Konzepte erreichen diese Zeiten nicht und können durch Zustandssicherung (Checkpoint) und Zustandswiederherstellung (Rollback) teilweise ersetzt werden. Hierfür wird ein Analyseframework auf Netzlisten- und Verhaltensebene eingeführt. Checkpoint Methoden für sequentielle Schaltungen werden in Bezug auf Zeitanspruch und Mehraufwand optimiert und zyklenakkurat simuliert. Die dafür notwendige Simulationsumgebung wurde auf Basis von SystemC in der Netzlistenebene etabliert und die Simulationsgeschwindigkeit evaluiert. Nach der Bestimmung der dedizierten Checkpoint und Rollback Methode wird die Schaltung durch eine neue Analyseumgebung auf relevante Echtzeitverletzungen untersucht. Mittels diesem teilautomatisierten Framework mit Schnittstelle zur Systemsimulation wird letztlich die Strategie der Zeitpunkte von Checkpoint Erstellungen ermittelt.

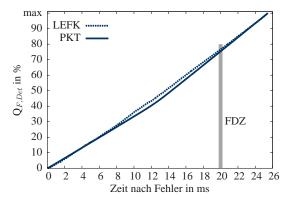

Aus den Untersuchungen zu der Verfügbarkeit und der Zustandswiederherstellung von FPGA Schaltungen ergibt sich notwendigerweise eine kurze Fehlerdetektionszeit der Funktionen. Diese Zeit wird bisher durch langsame Tests des fehlersensitiven Konfigurationsspeichers dominiert. Durch den redundanzfreien Ansatz des Priorisierten Konfigurationsspeicher Tests (PKT) kann diese Fehlerdetektionszeit von flüchtigen und permanenten Fehlern im Konfigurationsspeicher häufig deutlich verkürzt werden. Hierfür werden auf Error-Correcting Code (ECC) basierende Testmethoden mittels zusätzlichen Datenfluss- und Platzierungsinformationen verfeinert. Das daraus folgende Scheduling von Tests in partiellen Speicherbereichen reduziert die Testzeit einzelner programmierter Hardwarefunktion.

Sowohl die optimierte Checkpoint Methodik als auch der verfeinerte Konfigurationstest werden anhand von echtzeitfähigen Schaltungen evaluiert. Die Ergebnisse zeigen eine kürzere Testzeit nach Fehlern im Konfigurationsspeicher sowie eine kürzere Korrekturzeit für flüchtige Fehler im Zustandsspeicher der Schaltung. Beide Resultate führen zu einer kürzeren MTTR und somit erhöhten Verfügbarkeit der FPGA Schaltung im Vergleich zu klassischen Testmethoden mit anschließendem Reset. Gleichzeitig wird die Verwendung der entwickelten Methoden im industriellen Umfeld durch eine kurze Anwendungszeit in der Produktentwicklung gezielt unterstützt.

#### Abstract

Nowadays, flexible hardware is applicable in a wide range of safety relevant and high-available applications. In order to meet the requirements in terms of reliability we often use redundancy for error detection and reset concepts for corrections of soft errors. Yet, to become more competitive on high-volume markets, the approaches for error handling at configurable hardware have to be more cost-efficient without lack in speed. Focusing on real-time electronic control units the required approaches shall reduce the Mean Time To Repair (MTTR) in commercial FPGAs. Hence, this work aims on a reduced MTTR by redundancy-free error detection, correction and synchronization within the FPGA. The methods shall comply with the real-time property of the embedded system.

Firstly, shortening the time for global synchronization after an error is a major issue because state of the art reset concepts lack in a synchronization manner. Instead, checkpoint and rollback approaches are analyzed by a novel framework dealing with netlist- and system behavior. This work does optimize and simulate checkpoint measures in sequential circuits with focus on little overhead in time and hardware. A System-C based netlist simulation is therefore introduced and evaluated. Further, a novel behavior analysis tool based on interaction monitoring reveals the missed real-time deadlines. Finally, a strategy for times gathering the checkpoints is extracted from the easy-to-use frameworks.

Upon the investigations of the increased availability via checkpoint and rollback, a short fault detection time (FDT) is mandatory. Until now, the FDT is kept high due to slow tests of the vulnerable configuration memory in the FPGA. By introducing the fast prioritized configuration memory test the FDT is reduced significantly. Together with data flow and layout information mature error correcting codes are used. Memory areas are scheduled into a test sequence in order to reduce the test time of dedicated hardware functions.

Either the optimized checkpoint approach or the refined test of the configuration memory are evaluated with real-time circuits. Almost all results show a shorter FDT for the memory as well as a very short error correction time after soft errors. The results propose a short a MTTR and, in fact, they increase the availability compared to state of the art redundancy-free fault detection and reset methods. Finally, all presented tools are intended to provide a fast product development phase by easy-to-use handling.

### Danksagung

Diese Arbeit entstand während meiner Tätigkeit bei der Robert Bosch GmbH in Zusammenarbeit mit dem Lehrstuhl für Integrierte Systeme der Technischen Universität München. Somit geht mein besonderer Dank an Prof. Dr.-Ing. Walter Stechele, der diese Arbeit ermöglichte und mich in vielen fachlichen Diskussionen inspiriert und gefordert hat. Ein weiterer Dank gilt Prof. Dr.-Ing. Sigl für sein wertvolles Feedback.

Seitens der Robert Bosch GmbH möchte ich mich zuerst bei Andreas Jürgen Rohatschek für seine Unterstützung, Ratschläge und auch seine Geduld bedanken. Ferner danke ich allen Mitarbeitern und Freunden der Forschungsgruppe für digitale Hardware, insbesondere auch Jürgen Schirmer für seine Unterstützung. Für die besondere und kreative Stimmung im Team danke ich zudem René Guillaume, Simon Roth, Dr. Simon Hufnagel, Dr. Hendrik Post, Dr. Tobias Kirchner, Dr. Nico Bannow, Dieter Thoss und Stoyan Todorov.

Ein großer Dank geht an meine Eltern und an meine Schwester, die mich großartig unterstützt haben.

Zuletzt schulde ich vor allem meiner Frau Kerstin größten Respekt und Dank für ihr Verständnis, ihre Unterstützung und Liebe während der letzten Jahre.

Für Elisa

"Drei Dinge sind uns aus dem Paradies geblieben: die Sterne der Nacht, die Blumen des Tages und die Augen der Kinder" (Dante Alighieri)

# Inhaltsverzeichnis

| Kı | urzda         | arstellung                                                                                   | 111          |

|----|---------------|----------------------------------------------------------------------------------------------|--------------|

| Αl | bstra         | act                                                                                          | $\mathbf{v}$ |

| In | $_{ m halts}$ | sverzeichnis                                                                                 | ix           |

| 1. | Einl          | leitung und Ziel                                                                             | 1            |

|    | 1.1.          | Motivation                                                                                   | 2            |

|    | 1.2.          | Ziele und Beiträge                                                                           | 2            |

|    | 1.3.          | Gliederung der Arbeit                                                                        | 4            |

| 2. | Auf           | bau, Fehler und Wiederherstellung von programmierbaren Logikschaltungen                      | 5            |

|    | 2.1.          | Grundlagen des Schaltungsdesigns mit FPGAs                                                   | 6            |

|    |               | 2.1.1. Architekturen und Eigenschaften                                                       | 6            |

|    |               | 2.1.2. Entwicklungsablauf                                                                    | 10           |

|    | 2.2.          | Überblick der Ausfallsicherheit des FPGA auf Logikebene                                      | 11           |

|    |               | 2.2.1. Defektquellen und Fehlerausbreitung                                                   | 11           |

|    |               | 2.2.2. Fehlertoleranz zur Reduzierung der Fehlerauswirkung                                   | 14           |

|    | 2.3.          | Beschreibung von flüchtigen Fehlern im Konfigurationsspeicher                                | 16           |

|    |               | 2.3.1. Fehlerwahrscheinlichkeiten für flüchtige Fehler                                       | 17           |

|    |               | 2.3.2. Funktionale Fehlermodelle                                                             | 18           |

|    |               | 2.3.3. Detektions- und Korrekturmaßnahmen                                                    | 19           |

|    | 2.4.          | Analyse von Methoden zur Zustandswiederherstellung                                           | 22           |

|    |               | 2.4.1. Varianten des Checkpoint und Rollback                                                 | 22           |

|    |               | 2.4.2. Methoden zur Sicherung des Zustandsvektors in sequentiellen Schaltungen               | 24           |

|    |               | 2.4.3. Anwendungsdomänen von Methoden der Zustandswiederherstellung                          | 25           |

| 3. | Red           | lundanzfreie Methoden für verfügbare und sicherheitsrelevante Echtzeit-Designs               | 27           |

|    | 3.1.          | Abgeleitete Anforderungen an die Fehlerdetektion der Konfiguration gemäß ISO 26262 $ \dots $ | 28           |

|    |               | 3.1.1. Kurzdarstellung Standard ISO 26262 mit FPGA                                           | 28           |

|    |               | 3.1.2. Beurteilung der CRAM-Detektionsmethoden unter ISO 26262                               | 29           |

|    | 3.2. | Beschreibung von Verfügbarkeit in FPGA Systemen                                       | 32 |

|----|------|---------------------------------------------------------------------------------------|----|

|    |      | 3.2.1. Metrik und Bestimmungen der Verfügbarkeit                                      | 32 |

|    |      | 3.2.2.Beitrag der Fehlerdetektion und Zustandswiederherstellung auf die Verfügbarkeit | 34 |

|    | 3.3. | Beschränkungen durch validierten Entwicklungsfluss                                    | 34 |

| 4. | Ech  | tzeitfähige Zustandswiederherstellung in sequentiellen Schaltungen                    | 37 |

|    | 4.1. | Grundlegende Auslegung der Checkpoint Virtualisierung                                 | 38 |

|    |      | 4.1.1. Größe des Zustandsvektors                                                      | 38 |

|    |      | 4.1.2. Schaltungs- und Betrachtungsgrenzen                                            | 39 |

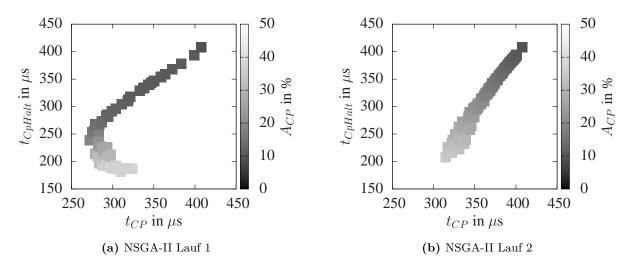

|    | 4.2. | Checkpoint-Analyse auf der Netzliste                                                  | 41 |

|    |      | 4.2.1. Modellierung von Methoden und Schaltungen                                      | 41 |

|    |      | 4.2.2. Simulation der applizierten Methoden                                           | 42 |

|    |      | 4.2.3. Analyse der applizierten Methoden                                              | 44 |

|    |      | 4.2.4. Minimierung der Methoden-Auswirkungen                                          | 46 |

|    | 4.3. | Dynamische Analyse der Schaltung auf der Ebene von Register Transfer Level            | 48 |

|    |      | 4.3.1. Checkpoint Gültigkeiten                                                        | 48 |

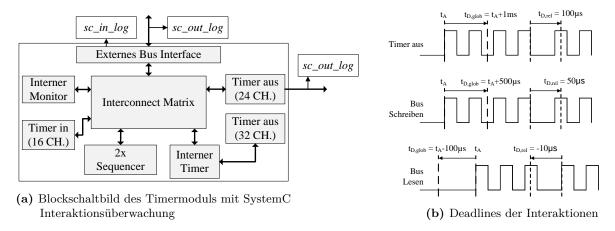

|    |      | 4.3.2. SystemC basierte Evaluation der Interaktionen                                  | 51 |

|    | 4.4. | Analysetool und Anwendungsergebnisse für ein Echtzeitsystem                           | 54 |

|    |      | 4.4.1. Anwendung 1: Microcontroller System                                            | 54 |

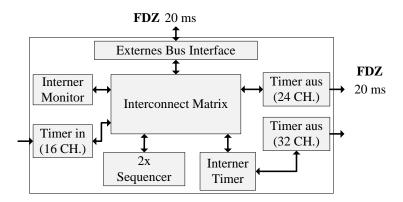

|    |      | 4.4.2. Anwendung 2: Echtzeit Timermodul                                               | 57 |

|    | 4.5. | Zusammenfassung und Erweiterungen                                                     | 64 |

| 5. | Pric | orisierte und datenflussorientierte Fehlerdetektion im Konfigurationsspeicher         | 67 |

|    | 5.1. | Grundlegende Auslegung                                                                | 68 |

|    |      | 5.1.1. Priorisierter Konfigurationstest                                               | 68 |

|    |      | 5.1.2. Datenfluss-Varianten                                                           | 69 |

|    |      | 5.1.3. Partitionierung von Testbereichen                                              | 70 |

|    | 5.2. | Datenflussorientierte Schaltungsanalyse und Erstellung der Testbereiche               | 70 |

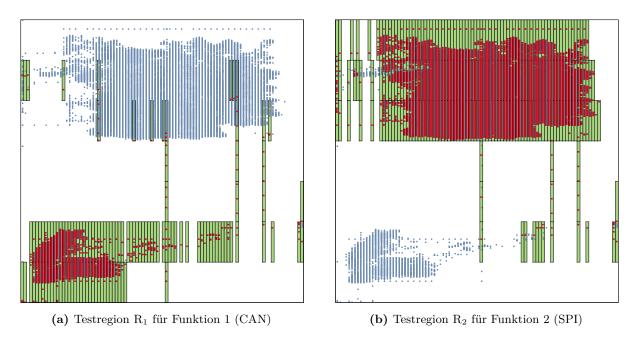

|    |      | 5.2.1. Korrelation der Funktionen zum Layout und zu Testregionen                      | 71 |

|    |      | 5.2.2. Abdeckung der CRAM Fehlermodelle                                               | 75 |

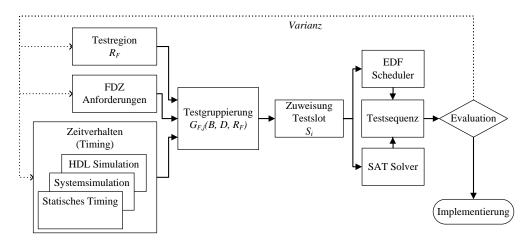

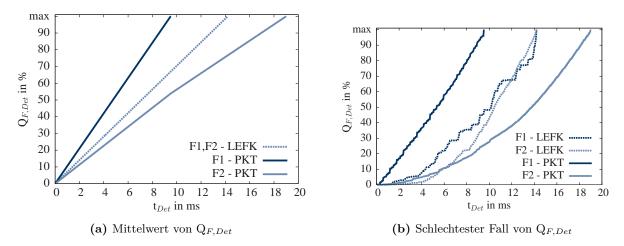

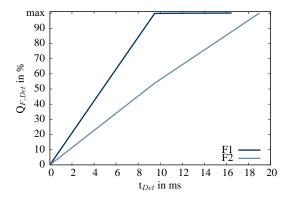

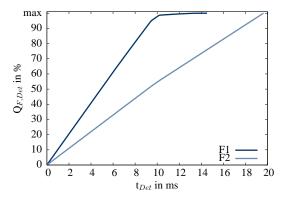

|    | 5.3. | Zeitgesteuerte Testverteilung                                                         | 77 |

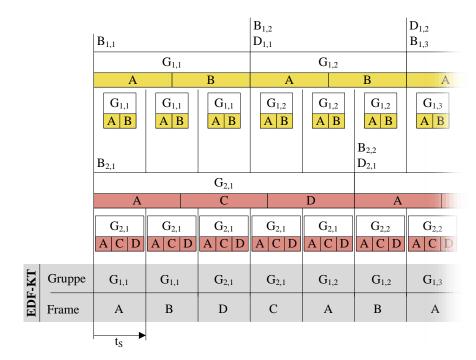

|    |      | 5.3.1. Gruppierung der Testanforderung und Verteilung auf Testslots                   | 79 |

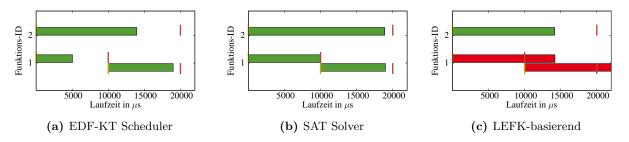

|    |      | 5.3.2. EDF Scheduling                                                                 | 79 |

|    |      | 5.3.3. Scheduling mit SAT                                                             | 80 |

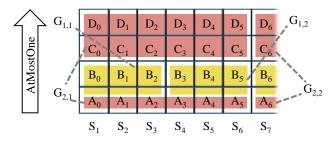

|    | 5.4. | Homogene Testverteilung                                                               | 82 |

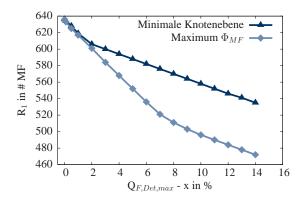

|    |      | 5.4.1. Verteilungsalgorithmus                                                         | 83 |

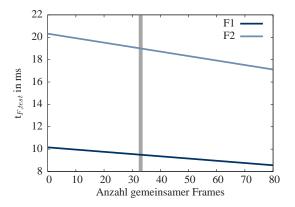

|    |      | 5.4.2. Optimierung der Testzeit                                                       | 85 |

|           |       | 5.4.3. Abhängige Testzeit bei gemeinsamen Ressourcen                                                            | 88  |

|-----------|-------|-----------------------------------------------------------------------------------------------------------------|-----|

|           | 5.5.  | Realisierung des Testsequenzers im FPGA                                                                         |     |

|           |       | 5.5.1. Detektions- und Korrektureinheit                                                                         | 90  |

|           |       | 5.5.2. Speicherbedarf                                                                                           | 91  |

|           |       | 5.5.3. Empirischer Nachweis der PKT Fehlerabdeckung                                                             | 91  |

|           | 5.6.  | Anwendungsergebnisse für verteilte und einzelne FPGA Funktionen                                                 | 93  |

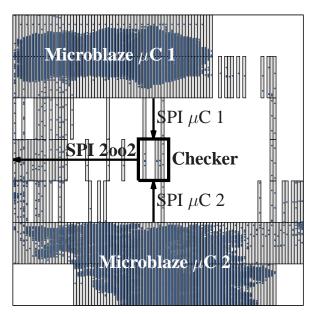

|           |       | 5.6.1. Dual Microcontroller Schaltung                                                                           |     |

|           |       | 5.6.2. Redundanzschaltung mit Überprüfer                                                                        | 99  |

|           |       | 5.6.3. Echtzeit Timermodul                                                                                      | 100 |

|           | 5.7.  | Zusammenfassung und Erweiterungen                                                                               | 104 |

|           |       |                                                                                                                 |     |

| 6.        |       | ammenfassung und Ausblick                                                                                       | 107 |

|           |       | Zusammenfassung und Diskussion                                                                                  |     |

|           | 6.2.  | Ausblick                                                                                                        | 108 |

| Α.        | Anh   | nang                                                                                                            | 111 |

|           | A.1.  | Code Templates                                                                                                  | 112 |

|           | A.2.  | Design Dateien                                                                                                  | 113 |

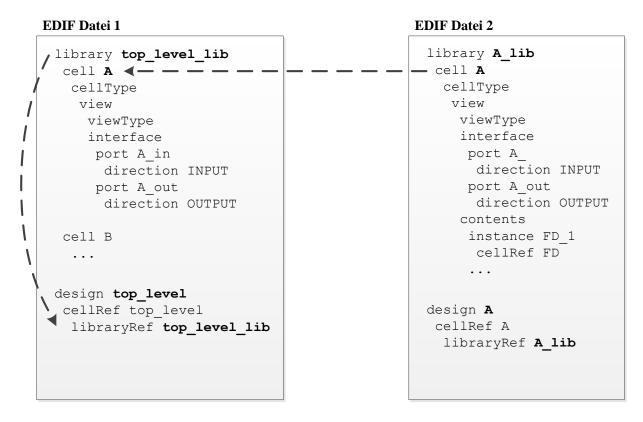

|           |       | A.2.1. EDIF Netzlistenformat                                                                                    | 113 |

|           |       | A.2.2. XDL Platzierungsformat                                                                                   | 114 |

|           | A.3.  | Checkpoint und Rollback                                                                                         | 115 |

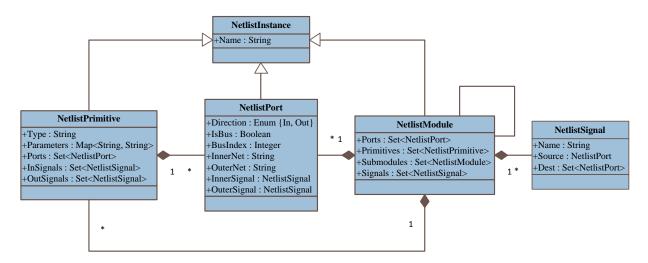

|           |       | A.3.1. Netzlistenrepräsentation                                                                                 | 115 |

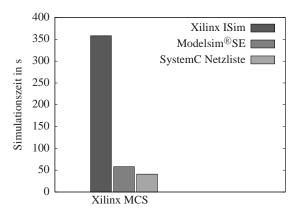

|           |       | A.3.2. Ergebnisse Fallbeispiel MicroBlaze MCS                                                                   | 116 |

|           | A.4.  | Priorisierter Konfigurationstest                                                                                | 117 |

|           |       | A.4.1. Kombinatorische Testbereiche                                                                             | 117 |

|           |       | A.4.2. Herleitung der mittleren Testdauer eines Major Frames der Xilinx 7 Serie                                 | 117 |

|           |       | A.4.3. Aufbau der Frameadressen der Xilinx 7er Serie                                                            | 118 |

|           |       | A.4.4. Frame auslesen mittels ICAP                                                                              | 119 |

|           |       | A.4.5. Frame schreiben mittels ICAP                                                                             | 120 |

|           |       | ${\rm A.4.6.\ \ Detaillierte\ Ergebnisse\ der\ homogenen\ Testverteilung\ f\"ur\ Dual\ Core\ Microcontroller}.$ | 123 |

|           |       | A.4.7. Detaillierte Ergebnisse der homogenen Testverteilung für den Echtzeit Timer $\ \ldots \ \ldots$          | 124 |

| Αl        | obild | ungsverzeichnis                                                                                                 | 125 |

| Li        | terat | urverzeichnis                                                                                                   | 127 |

| ${f A}$ l | okürz | zungsverzeichnis                                                                                                | 139 |

|           |       |                                                                                                                 |     |

### 1. Einleitung und Ziel

Im Bereich der digitalen Elektronik stellte die Erfindung des Field Programmable Gate Array (FPGA) in den 1980er einen enormen Fortschritt dar. Erstmals wurden programmierbare Speicherzellen Programmable Read Only Memory (PROM) mit veränderbaren Verdrahtungen (engl. Routing) verknüpft [Fre89] und mit dem ersten FPGA XC2064 kommerziell vertrieben. Die Firma Xilinx startete damit 1985 einen Markt, der heute einen Umsatz von über 4 Milliarden Dollar hat [Sou13]. Die technische Entwicklung schritt rasant voran, getrieben von den schrumpfenden Strukturbreiten in Halbleitern. Ende der 1980er und Anfang der 1990er Jahren führten nach und nach mehrere Firmen Integrated Circuit (IC)s mit programmierbarer Logik ein, darunter Actel und Altera. Im Jahre 2012 teilen sich Xilinx und Altera einen Marktanteil von ca. 90 % [Sou13]. Während FPGAs im Bereich der Telekommunikation und Netzwerktechnik reiften, sind heute weitere Domänen wie Luft- und Raumfahrt, Automotive, Medizintechnik, Audio- und Videoverarbeitung abgedeckt. In vielen Applikationen kann ein FPGA als technische Alternative zu einer Graphics Processing Unit (GPU), Central Processing Unit (CPU) [CWFH12] oder Application Specific Integrated Circuit (ASIC) [Kot06] eingesetzt werden.

Im Automotive Umfeld hat der FPGA erst in den 2000er Einzug gehalten [GNW+06]. Bereits im Jahr 2007 sind 18 Xilinx FPGAs in einer vollausgestatteten S-Klasse enthalten [Mar07]. Die Applikationen sind zu dieser Zeit auf Komfortfunktionen wie Fensterheber bis zu Fahrerassistenz Systemen [Hau08] beschränkt. Zugleich steigen der Anteil und die Kosten der Elektronik im Fahrzeug immer weiter an [Kru08]. Es ist absehbar, dass durch zukünftige Systemanforderungen in einem Kfz Steuergerät der Anteil der FPGAs zunehmen wird, auch für sicherheitsrelevante Bereiche. Zum einen muss die Zeit bis zur Markteinführung eines Steuergerätes (time-to-market) von ein bis drei Jahren reduziert werden, um wettbewerbsfähig zu bleiben. Zum anderen sind leistungsfähige Verarbeitungseinheiten notwendig, sowohl für teil-automatisiertes Fahren als auch für voll-automatisiertes Fahren. Gepaart mit Flexibilität in der Entwicklung und durch Reduktion der Variantenvielfalt ergibt sich ein breites Anwendungsfeld für aktuelle und zukünftige FPGA Generationen.

In der Zukunft ist absehbar, dass auf einem FPGA implementierte Funktionen teilweise vital für eine Applikation werden. Beispielsweise können Funktionen wie Sensor-Daten-Fusion oder Gateway Funktionalitäten sicherheitsrelevante Informationen in Echtzeit bereitstellen. Dabei müssen sowohl der enthaltene FPGA als auch weitere Microprocessor Control Unit (MCU) die funktionalen Sicherheitsanforderungen und die von der Qualitätssicherung geforderte Verfügbarkeit erfüllen. In ersten Systemansätzen wird der FPGA als Überwacher-IC oder physikalisch doppelt ausgelegt, um die entsprechende Sicherheitseinstufung zu erhalten [BBD+08, Chu02]. In dieser Arbeit sollen Methoden erarbeitet werden, welche die Systemrelevanz der FPGA-Schaltung durch erhöhte Verfügbarkeit mittels redundanzfreier Lösungen erhöhen können.

2 1 Einleitung und Ziel

#### 1.1. Motivation

Für den Einsatz von FPGAs in automobilen Echtzeitanwendungen sprechen mehrere Gründe. Während der Entwicklung profitieren die Anwender von schnellen Prototypen und kürzerer Zeit bis zur Markteinführung. Zudem bietet die Eigenschaft der Parallelisierung von Hardware (HW) Aufgaben eine reduzierte Latenzzeit [CWFH12]. Infolge der Reprogrammierbarkeit lassen sich Fehler im Feld gut korrigieren. Aus betriebswirtschaftlichen Gründen werden FPGAs zur Reduzierung von Aufbauvarianten eines Produktes eingesetzt. Ferner ergibt sich eine Unabhängigkeit von Spezialhardware durch die Möglichkeit, dedizierte Intellectual Property (IP)s oder HW Beschleuniger zu implementieren. Im Jahr 2012 sind für Strukturgrößen von 28 nm Maskenkosten von zwei bis drei Millionen US-Dollar [Cad12] einzuplanen. Diese Einmalkosten (Non Recurring Engineering (NRE)) müssen für dedizierte Hardware eingeplant werden, sofern nicht frei programmierbar Hardware eingesetzt wird. Somit ist der FPGA unter Randbedingungen wie Stückkosten bei mittleren Volumen von 1.000 bis 100.000 Stück und kleinen NRE [Kot06]eine sinnvolle Alternative.

In dieser Arbeit soll durch kostengünstige Lösungen zur Fehlerdetektion und Fehlerkorrektur der Eintritt in hochvolumige automobile Anwendung (Automotive Anwendungen) erleichtert werden. Eine technische Voraussetzung für den Einsatz eines FPGAs in einem echtzeitfähigen und sicherheitsrelevanten Bereich der Fahrzeugelektronik ist die funktionale Sicherheit. Der für die Automobilindustrie geltende Standard im Sinne der funktionalen Sicherheit in Kraftfahrzeugen ist die Norm ISO 26262 der International Organization for Standardization [ISO11a]. In dieser Norm stellt die Fehlertoleranz einen Aspekt dar, die sich aus Fehlerdetektion und Erreichen des sicheren Zustandes zusammensetzt. Die Vorgaben für die Fehlerdetektion zielen darauf ab, die Fehlerausbreitung im System lokal begrenzt zu halten und somit die für den Fahrer spürbaren Auswirkungen zu unterbinden. Diese Zeit der Fehlerbehandlung kann von mehreren 100 ms bei einer Motorsteuerung bis zu 1 ms für das Antiblockiersystem (ABS) oder für die elektrische Lenkung reichen [Ren12]. Somit ist für den FPGA die schnelle Fehlerdetektion unter akzeptabler Fehlerabdeckung eine Bedingung für den Einsatz in heutigen echtzeitfähigen und sicherheitsrelevanten Bereichen des Automobils.

Ein weiteres Qualitätsmerkmal eines (FPGA-basierten) Steuergerätes ist eine hohe Verfügbarkeit trotz flüchtiger und nichtflüchtiger Speicherfehler. Eine hohe Verfügbarkeit meidet Rückläufer aus dem Feld und verhindert unangenehme oder spürbare Leerlaufzeiten des Systems. Nur wenn Fehler im System toleriert oder schnell behoben werden, ist eine hohe Verfügbarkeit denkbar. Da Toleranz in den meisten Fällen eine Kostenerhöhung in Form von Redundanzen bedeutet, ist eine schnelle Fehlerreaktion und Behebung unterhalb der Wahrnehmschwelle oder innerhalb der Fehlertoleranzzeit erstrebenswert. Zunehmend komplexe Systeme und Schaltungen verursachen nach einer Fehlerdetektion eine nicht zu unterschätzende Ausfallzeit durch einen Reset. Daher sind Konzepte notwendig, welche eine FPGA Schaltung sowohl während des Hochlaufs als auch nach einer Detektion von Zustands- und Konfigurationsspeicherfehlern innerhalb kürzester Zeit wieder bereitstellen und mit der Umgebung synchronisieren.

#### 1.2. Ziele und Beiträge

Mit den in dieser Arbeit vorgestellten Methoden soll die mittlere Fehlerdetektions- und Reparaturzeit (Mean Time To Repair (MTTR)) einer echtzeitfähigen eingebetteten FPGA Schaltung merklich reduziert werden. Durch eine reduzierte MTTR wird die Verfügbarkeit im Sinne der Produktqualität erhöht. Zudem können bei

verkürzter MTTR komplexere Anwendungen die Anforderungen an die Fehlertoleranzzeit nach International Organization for Standardization (ISO) 26262 [ISO11a] erfüllen.

Als konkrete Maßnahmen zur Reduzierung der MTTR wird zum einen die kostengünstige und schnelle Fehlerdetektion im Konfigurationsspeicher untersucht und implementiert. Zum anderen wird eine redundanzfreie Methode zur Zustandswiederherstellung und somit zur Fehlerkorrektur auf Basis von Checkpoint und Rollback präsentiert. Mit diesen zwei Ansätzen lassen sich bestehende Konzepte für "fail safe" FPGA Steuergeräte von Chujo et al. (2002) [Chu02] oder Beckschulze et al. (2008) [BBD+08] auf komplexe FPGA Anwendungen erweitern. Ferner müssen die Methoden sowohl industriell und kostengünstig nutzbar als auch normkonform einsetzbar sein.

Für die Fehlerdetektion im Konfigurationsspeicher werden folgende Beiträge präsentiert.

- 1. Verknüpfung von Teilbereichen des Konfigurationsspeichers mit dedizierten Funktionen der Anwendung

- 2. Gewichtung und Priorisierung von Teilbereichen des Konfigurationsspeichers nach der Anzahl der verwendeten Bits. Mit dieser Gewichtung lassen sich Testsequenzen homogener erstellen.

- 3. Anwendung von Scheduling Verfahren auf den Testablauf im Konfigurationsspeicher innerhalb von FPGAs.

- 4. Anpassung der Testdauer einer Funktionalität an deren Kritikalität. Dazu sind Testanforderungen und Speicherregionen zu einem Testablauf adaptiert.

- 5. Nachweis der Fehlerabdeckung des partiellen Konfigurationstests.

Nach der Fehlerdetektion soll die Fehlerbehebung von flüchtigen Fehlern ohne die Verwendung eines klassischen Schaltungsreset oder der Verwendung von redundanten Modulen durchgeführt werden. Es werden Konzepte für Zustandssicherung (Checkpoint) und Zustandswiederherstellung (Rollback) untersucht und an der Echtzeitfähigkeit gemessen. Gegebene Schaltungen sollen auf diese Konzepte untersuchbar sein und der Entwickler soll die Auswirkungen auf die Schaltung und die Applikation durch folgende Beiträge einschätzen können.

- 1. Schnelle und teil-automatisierte Beurteilung von Methoden der Zustandswiederherstellung durch hybride Schaltungsanalyse und Verhaltenssimulation.

- 2. Anwendung und Optimierung von Methoden zur Zustandswiederherstellung verschiedener Abstraktionsebenen auf ein Netzlistenmodell.

- 3. Erstellung von Anwendungskriterien und die Etablierung von interaktionsabhängigen Gültigskeitsmetriken für unterschiedliche Szenarien mit Zustandswiederherstellung in echtzeitfähigen Schaltungen.

- SystemC-basierter Nachweis der Checkpoint Strategie mit anschließenden Deadline Analysen und Anwendungs-Performance Einschätzungen.

Mit Hilfe dieser Maßnahmen ist der Schaltungsentwickler in der Lage, effiziente Methoden und Strategien zur Zustandswiederherstellung durch Checkpoint und Rollback zu finden. Es werden die dafür notwendigen Schritte und Anwendungskriterien abgeleitet.

4 1 Einleitung und Ziel

#### 1.3. Gliederung der Arbeit

Im folgenden Kapitel wird ein Überblick über den generellen Aufbau eines FPGA und dessen Fehlerbilder gegeben. Darauf aufbauend zeigt dieses Kapitel dedizierte Testmethoden für den Konfigurationsspeicher sowie Möglichkeiten zur Fehlerkorrektur flüchtiger Fehler auf. Kapitel 3 zeigt nun die Herausforderungen eines FPGA Designs mit Hinblick auf die in der Automobilbranche angewendete ISO 26262. Ferner wird die Verfügbarkeit von FPGA Systemen eingeführt und die Einflüsse einer schnellen Fehlerdetektion und Fehlerkorrektur herausgestellt. Ein häufig unterschätzter Aspekt des normgerechten und validierten Entwicklungsflusses wird hier ebenfalls erläutert.

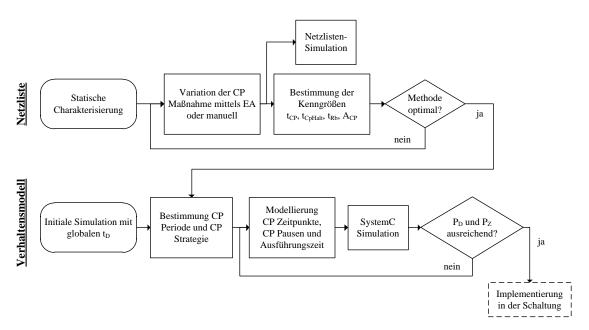

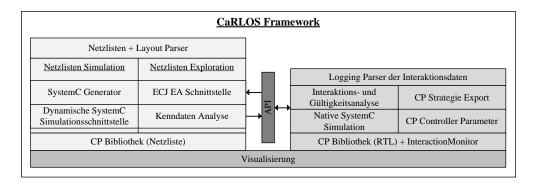

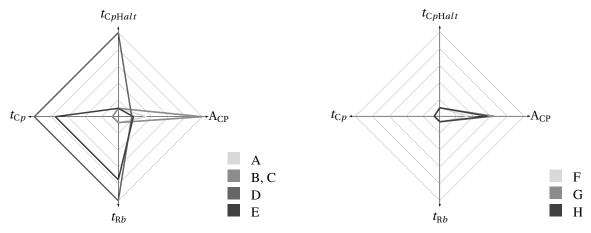

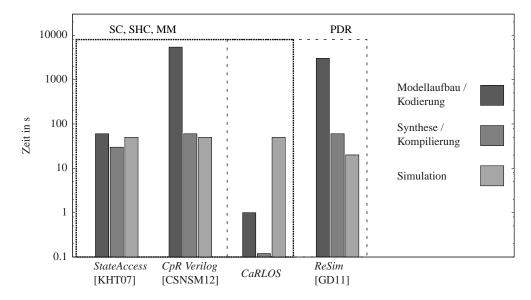

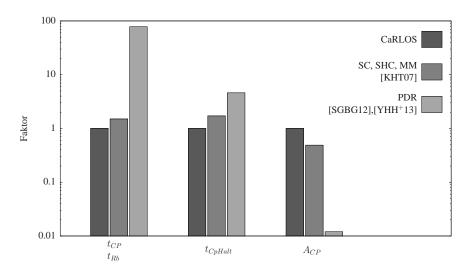

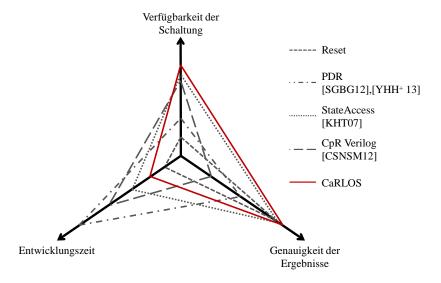

Das für industrielle Zwecke einsetzbare Checkpoint and Rollback Evaluation, Optimization, Simulation (CaRLOS) Framework zur Beurteilung von Checkpoint und Rollback Methoden in echtzeitfähigen FPGA Schaltungen wird in Kapitel 4 vorgestellt. Hier werden die drängenden Fragen bei einer rückwärts gerichteten Fehlerkorrektur herausgestellt und aggregiert durch Analysen und Simulationen beantwortet. Das Kapitel wird mit zwei Beispielanwendungen abgeschlossen.

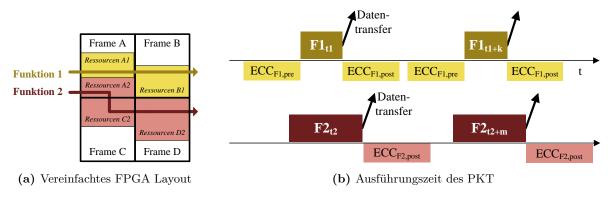

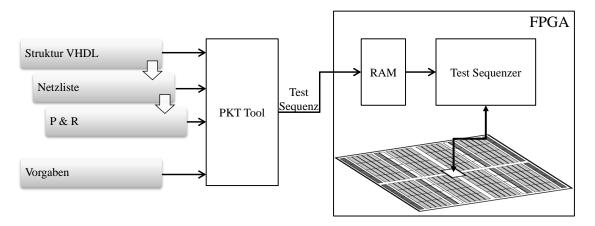

Anschließend wird der grundsätzlich neue Ansatz des Priorisierten Konfigurationsspeicher Tests vorgestellt (PKT). Anstelle von linearen Tests wird nun eine zeitliche Abfolge in den ECC-basierten Test von Bereichen des Konfigurationsspeichers gebracht. Es wird der theoretische Ansatz, die Umsetzung und die Anwendung präsentiert.

Die Arbeit schließt in Kapitel 6 mit einer Zusammenfassung des CaRLOS Framework und des PKT inklusive einem kurzen Ausblick.

# 2. Aufbau, Fehler und Wiederherstellung von programmierbaren Logikschaltungen

Dieses Kapitel befasst sich mit der Einführung der programmierbaren Logik, speziell des FPGAs. Wie bereits dargestellt, eignet sich ein FPGA vor allem für parallele Datenverarbeitung [CWFH12]. Zudem sind schnelle HW Prototypen (rapid prototyping) und Serienprodukte mit volatilen Anforderungen während und nach der Entwicklungszeit möglich. Ein Beispiel für diese Kleinserien mit wechselnden Kundenanforderungen ist die Motorsteuerung für Rennfahrzeuge [Bos13]. Hier werden FPGAs seit 2008 verwendet, um die Leistungsfähigkeit und Flexibilität zu erhalten, die ein einzelner Microcontroller nicht bietet.

Im Gegensatz zu grob granularen programmierbaren Strukturen (engl. coarse grain) nach Hartenstein (2001) [Har01] muss bei der FPGA Anwendung der Datenfluss nicht bereits mit Bitbreite und Rechenoperationen spezifiziert sein. Daher liegt, trotz des größeren Flächen- und Verdrahtungsbedarfs, der Fokus dieser Arbeit auf programmierbaren fein granularen (engl. fine grain) Logikstrukturen.

Aktuelle Static Random Access Memory (SRAM) basierende FPGA Generationen werden mit dem 28 nm Halbleiter Technologieknoten in Serie gefertigt. Der damit verbundene Vorsprung in der Leistungsfähigkeit gegenüber einem vor mehreren Jahren entwickelten ASIC führt zu einem Preisverfall pro Gatter, der den FPGA auch für zeitnahe Serienprodukte mittleren oder hohen Volumens attraktiv machen kann. Durch die Flexibilität der Schaltung mittels Programmieren des Bausteins eröffnen sich auch für sicherheitsrelevante Anwendungen vielfältige Optionen. Der Ausbau und die Erweiterung von Sicherheitskonzepten für eine Schaltung ist ebenso schnell wie die Integration dedizierter IPs möglich.

Die Flexibilität wird mit einem Überschuss an verwendeter Si-Fläche gewonnen. Die regulären Strukturen und konfigurierbaren Verbindungspunkte (routing) verursachen eine ca. 20 bis 30 fach größere IC Fläche gegenüber einem kundenspezifischen ASIC [WBR11]. Durch die schaltbaren Verbindungsstrukturen vergrößern sich ferner die Signallaufzeiten (delay) um das etwa 10 bis 20 fache [KR09]. Zudem steigt die dynamische Leistungsaufnahme des FPGAs auf das 5 bis 10 fache im Vergleich zu einem ASIC. Diese Daten sind für Technologieknoten von 60 nm mit Xilinx ICs und für 90 nm mit Altera ICs erhoben.

Das Kapitel erläutert die Grundlagen der FPGA Technologie und des Schaltungsdesigns. Danach werden die wichtigsten Fehlermodelle und deren Einfluss auf die Verfügbarkeit angeführt. Neben Fehlerquellen und Fehlerarten werden auch Gegenmaßnahmen erläutert, die eine funktionale Sicherheit gewährleisten und die Verfügbarkeit erhöhen. Hierbei liegt der Fokus auf dem Konfigurationsspeicher und der Zustandswiederherstellung.

#### 2.1. Grundlagen des Schaltungsdesigns mit FPGAs

Moderne programmierbare Logik kann mit drei Technologien konfiguriert werden: SRAM, Flash und Antifuse [KTR08]. Eine Konfiguration mittels Antifuse ist einmal programmierbar durch das Durchbrennen einer Isolationsschicht. Sie bietet zwar eine große Packungsdichte gegenüber SRAM Technologien gleicher Strukturbreite, wird aber aufgrund der Strukturbreiten über 100 nm und der fehlenden Flexibilität in dieser Arbeit nicht weiter betrachtet. Im Vergleich zur SRAM Technologie ist die Konfiguration mittels Flash Zellen bei einem Verlust der Versorgungsspannung nicht flüchtig und hat eine geringere statische Leistungsaufnahme [Dri11]. Dagegen steht der um mehrere Generationen zurückliegende Technologieknoten von aktuell 65 nm für Flash basierende FPGAs [Mic13] im Gegensatz zu 28 nm bei SRAM basierenden FPGAs [Xil14], [Alt14]. Dadurch verringert sich die Leistungsfähigkeit der Flash FPGAs, was sich in reduzierter Taktfrequenz und reduzierter Anzahl von Konfigurationsblöcken zeigt. Ferner haben diese IC höhere Stückkosten. Der Fokus dieser Arbeit liegt somit auf SRAM basierten FPGAs.

#### 2.1.1. Architekturen und Eigenschaften

Am Grundaufbau von FPGAs hat sich von den 1990er bis heute wenig geändert. Für eine beliebige sequentielle Schaltung werden kombinatorische Logikelemente, Zustandsspeicher und Verbindungen zwischen den Elementen benötigt. Um diese Komponenten flexibel nutzen zu können, gibt es drei Standard-Aufbauvarianten: island-style, row-based und hierarchical [BRM99] [FMM12]. Bei allen Aufbauvarianten bilden konfigurierbare Eingangs- / Ausgangsblöcke (Input / Output Block, IOB) den Randbereich. Intern liegt ein regelmäßiges Gitter der Leitungs- und Verdrahtungsebene zwischen den eigentlichen Logikblöcken, genannt Routing oder Interconnect. Je nach Aufbauvariante unterscheidet sich der Aufwand für die Verdrahtungsebene. Frühere Bausteine der Firma Altera waren mit hierarchischer Architektur verfügbar. Diese setzte sich aber aufgrund des erhöhten Leitungs- und Verbindungsbedarfs, bestehend aus globalen Verbindungen und abgeschotteten lokalen Verbindungen, nicht durch. Bei der row-based Architektur lassen sich Logikblöcke innerhalb einer Reihe bzw. Spalte verbinden. Die Verdrahtungsebene wird reduziert, bietet jedoch nicht die volle Flexibilität bei großen Schaltungen. Diese Architektur findet sich bei FPGAs mittlerer Leistungsfähigkeit und Größe wieder [Mic13].

#### 2.1.1.1. Aktuelle Island-Based Architektur

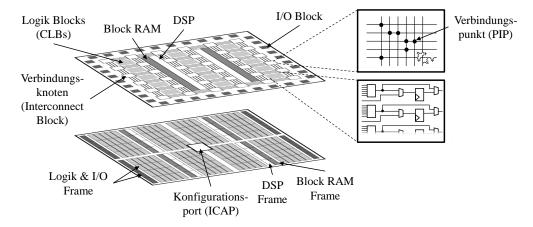

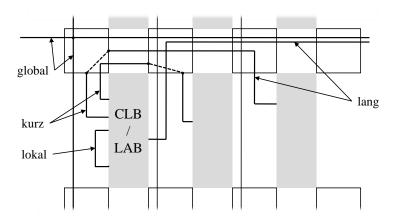

Aktuell verfügbare FPGAs der Marktführer Altera und Xilinx verfolgen die island Architektur [Xil13a] [Alt14] nach Abbildung 2.1. Die Logikblöcke lassen sich sehr regulär anordnen und die Bausteinfamilien sind somit skalierbar. Zudem vereint das Verbindungsgitter lokale, lange und globale Leitungen. Mit lokalen Leitungen lassen sich Logikblöcke verknüpfen, die nah beieinander liegen. Weiter entfernte Blöcke über mehrere Gitterabstände hinweg werden über lange Leitungen verbunden. Je nach FPGA Hersteller variiert die Länge und Anzahl der lokalen und langen Leitungen. Taktsignale werden über globale Leitungen verteilt, getrieben von speziellen Treibern mit hohem Lastfaktor (Fan-Out). Die Flexibilität in den Verbindungen beruht seit den 1980er auf dem Prinzip der konfigurierbaren Verbindungspunkte [Fre89]. Die Art der Verbindungspunkte werden Programmable Interconnect Point (PIP) genannt und sind sowohl bei FPGAs von Altera als auch von Xilinx zu finden, bei denen mittels Pass-Transistoren Leitungen verknüpft werden. Die Bit-Information

Abbildung 2.1.: Grundstruktur der Island-Based Architektur mit Konfigurationsspeicher

über einen hochohmigen (offen) oder niederohmigen (geschlossen) PIP liegt im Konfigurationsspeicher. Die PIPs werden in dem Gitter an den Verbindungsknoten gebündelt und stellen jeweils einen programmierbaren Interconnect Block dar. Die Leitungen und PIPs beanspruchen etwa 80% bis 90% der FPGA Si-Fläche [FMM12].

Das Verbindungsgitter besteht aus multiplen Leitungsarten. Zunächst werden Leitungen für Logik, Takt und statische Signale wie VCC und Masse (GND) unterschieden. Gemäß Abbildung 2.2 sind alle Leitungen von Logiksignalen Punkt-zu-Punkt Verbindungen zwischen Verbindungsknoten oder Logikblöcken, jedoch mit unterschiedlicher Länge. Dagegen verbreiten sich die Taktleitungen als verteiltes Netz mit wenigen globalen Treibern und mehreren Senken. Die Anbindung an eine Instanz erfolgt hier über die Verbindungsknoten. Die statischen Signale VCC und GND sind ebenfalls verteilte Netze, jedoch weitaus lokaler begrenzt. Die lokalen Grenzen resultieren aus den verteilten Quellen für die statischen Signale, wohingegen das Clock Netz nur wenige Quellen aber viele Treiber hat.

Abbildung 2.2.: Typische Leitungsarten zur Verbindung von Logikblöcken

Das Zentrum in den Zellen des Verbindungsgitters bilden die Logikblöcke. Je nach FPGA Anbieter werden diese Logikblöcke Configurable Logic Block (CLB) [Xil13a] oder Adaptive Logic Module (ALM) [Alt14] bezeichnet und basieren auf einer Grundkomposition aus dem Jahr 1984 [Car89]. Innerhalb der Logikblöcke decken die Lookup Table (LUT) beinahe vollständig alle kombinatorischen Anteile einer Schaltung ab. Eine LUT spiegelt die logische Wahrheitstabelle als Multiplexerstruktur wider, wobei die Konfiguration die Wahrheitswerte jeder möglichen Eingangskombination enthält. Aktuelle FPGA Generationen halten mehrere LUTs innerhalb der Logikblöcke vor, wobei jede LUT bis zu 6 Eingänge verarbeiten kann. Ferner

sind 4 bis 8 Zustandsspeicher Flip-Flop (FF) und dedizierte Elemente für mathematische Operationen, z.B. Übertragsketten (Carry Chain) oder Volladdierer, pro Logikblock enthalten. Der Konfigurationsspeicher einer LUT kann vielmals auch als Arbeitsspeicher konfiguriert und verwendet werden und wird in diesem Fall als LUT-Random Access Memory (RAM) oder Distributed RAM bezeichnet. Optional kann anstelle eines LUT-RAM auch ein Schieberegister in einem Logikblock instanziiert werden, bestehend aus den 32 Bit einer 6-Eingänge-LUT und dem Übertrag zur nächsten LUT.

Im Zuge der kleiner werdenden Transistorstrukturen und der daraus resultierenden Verfügbarkeit von Siliziumfläche im Die wurden fest implementierte IP Blöcke Bestandteil in FPGAs. Diese fest strukturierten und platzierten Blöcke werden als *Hard-IP* oder *Hard-Macro* bezeichnet. Standardmäßig werden Digital Signal Processor (DSP) Einheiten und Block Random Access Memory (BRAM) Blöcke in aktuellen FPGAs implementiert. Zurzeit stehen pro BRAM Block 20 Kb [Alt14] oder 36 Kb [Xil14] zur Verfügung, wobei die Anzahl von der FPGA Familie und Größe abhängt. Diese Blöcke lassen sich als Single-port, Simple dual-port, True dual-port, Schieberegister, Read Only Memory (ROM) oder First In - First Out (FIFO) konfigurieren und nutzen. Neben 48x48 DSP Einheiten stehen zum Teil noch einige weitere Hard-Macros zur Verfügung, wie Ethernet-IP, PCIe, Serializer-Deserializer, High-Speed Transceiver, Konfigurationsports, ECC Macros, AES-256 Verschlüsselungsmacros und Weitere.

#### 2.1.1.2. Konfiguration und Schnittstellen zur Technologie

Wie in Abschnitt 2.1.1.1 gezeigt, beruht der Unterschied zu Standardzellen ICs in der Konfigurationsebene. Nach Abbildung 2.1 besteht der Configuration Random Access Memory (CRAM) aus Frames unterschiedlicher Art. Ein Frame ist ein Teilbereich des CRAM mit eigener Adressierung und lokalen Einstellungen. Jeder Frame speichert die Konfigurationsbits eines Logiktypes: CLB, DSP, BRAM, I/O, globaler Clock (GCLK) oder weiterer FPGA Einstellungen. Je nach FPGA Typ hat der Konfigurationsspeicher eine Größe von ca. 2 MB bis 37 MB mit mehreren tausend Frames [Xil13b]. Bei aktuellen Xilinx FPGAs werden die Frames als "Minor Frame" bezeichnet und haben eine Größe 101 Wörter x 32 bit. Je nach Bedeutung werden 30 bis 42 Minor Frames zu einer Spalte zusammengefasst. In der Literatur wird diese Spalte als *Major Frame (MF)* bezeichnet.

Bei flüchtigen SRAM-basierten Speichern muss der Inhalt während der Startsequenz geladen werden. Der CRAM wird nach dem Einschalten der Betriebsspannung (Power Up) und anschließenden Power-On Reset beschrieben. Bei nichtflüchtigen FPGAs entfällt dieser Konfigurationsschritt, der je nach Datenrate und Größe des FPGA länger als eine Sekunde werden kann. Gleichung 2.1 zeigt die Abhängigkeit der Ladezeit von der Datenrate und der Größe des Konfigurationsspeichers. Aktuelle Bausteine lassen bei serieller oder 32 Bit paralleler Datenübertragung Konfigurationstakte von 100 MHz [Xil13f] bis 133 MHz [Alt14] zu. Diese Übertragungsraten sind durch die kurzen Leitungswege vom externen Speicher bis zum FPGA erreichbar. Bei längeren Distanzen oder Busstrukturen sinkt auch die Übertragungsgeschwindigkeit.

$$t_{Konfiguration} = \frac{Bitzahl_{Konfiguration}}{Datenbreite_{Interface} \times f_{Konfiguration}}$$

(2.1)

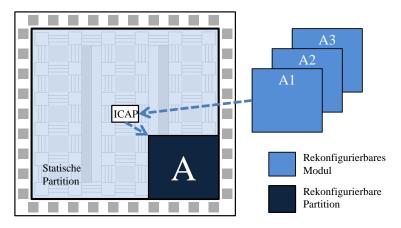

Aufgrund der nicht beschränkten Schreibzyklen von SRAM Zellen lassen sich auch Schreibverfahren zur Laufzeit einsetzen. Üblicherweise wird diese Methode als Dynamische Rekonfiguration bezeichnet. Eine

|                                       | Vollständiges FPGA         | Untermenge des FPGAs                          |

|---------------------------------------|----------------------------|-----------------------------------------------|

| Im Betrieb                            | Dynamische Rekonfiguration | Partielle Dynamische<br>Rekonfiguration (PDR) |

| Außerhalb des funktionalen<br>Betrieb | Statische Konfiguration    | Partielle Rekonfiguration (PR)                |

Tabelle 2.1.: Rekonfigurationsarten des FPGAs

Einordnung der Arten von Rekonfigurationen ist in Tabelle 2.1 dargestellt. Hier ist besonders die Partielle Dynamische Rekonfiguration (PDR) interessant, da sich zur Laufzeit Teilfunktionalitäten austauschen lassen. Das Prinzip von PDR ist in Abbildung 2.3 dargestellt. Ursprünglich ist diese Funktionalität im Jahr 2004 mit der Intention des zeitlichen Multiplex von Teilfunktionen in Xilinx FPGAs integriert worden [Xil09]. PDR hat sich nun auch in aktuellen Altera Bausteinen verbreitet [Alt14] und eine Vielzahl weiterer Forschungsaktivitäten inspiriert. Ein Schwerpunkt ist die Verkürzung der Konfigurationszeit durch sequentielles Laden von Teilschaltungen [HMS+10] mittels einer verkleinerten statischen Partition. Nach Gleichung 2.1 reduziert sich die statische Konfigurationszeit zum Starten des Systems linear mit der Größe der statischen Region. Somit lassen sich zeitkritische Spezifikationen wie die PCIe®Transfer Anforderung mit 100 ms nach Anlegen der Versorgungsspannung [TK10] erfüllen. Der Aufwand und Nutzen der PDR muss in der Applikation über Modellbildung erörtert werden [PDH11], jedoch ist hier die Speicheranbindung des externen Speichers der limitierende Faktor für die Konfigurationsgeschwindigkeit. Die interne Datenrate der Konfiguration liest mit maximal 400 MB / s (100 MHz bei 32 Bit Datenbreite) [Xil13b] über der möglichen Geschwindigkeit durch den kommerziell vertretbaren Quad-Serial Peripheral Interface (SPI) Bus von 50 MB/s (100 MHz bei 4 Datenbit).

Abbildung 2.3.: Grundprinzip Partielle Rekonfiguration

#### 2.1.1.3. Automotive Eigenschaften

Die zunehmende Datenverarbeitung im Kraftfahrzeug (Kfz) bringt auch die FPGAs in die hochvolumigen und niedrigpreisigen Steuergeräte. Vor allem Fahrerassistenzsysteme wie Rückfahrkamera, Frontkamera, Radar- und Ultraschallauswertung sowie zunehmend Sensor-Daten-Fusion benötigen die Leistungsfähigkeit und Time-To-Market von FPGAs. Daher sind bei allen großen Herstellern von FPGAs auch Produktlinien verfügbar, die für den Automobilmarkt durch den Standard AEC-Q100 [AEC07] qualifiziert sind. Hier werden Stichproben eines Quartals gegen Elektrostatische Entladung (engl. Electrostatic Discharge) (ESD), Elektromagnetische Verträglichkeit (EMV) und Halbleiterstress geprüft. Interessant für FPGAs in sicherheits-

relevante Echtzeitsystemen ist die Temperaturverträglichkeit, d.h. die Zuverlässigkeit bei hohen und niedrigen Temperaturen. Aktuell verfügbare Bausteine der Xilinx XA Familie, Altera 5er Serie und Lattice FPGAs sind bis zur Kerntemperatur  $T_j = -40^{\circ}$ C bis  $+125^{\circ}$ C qualifiziert. Das entspricht etwa dem Grad 2 des AEC-Q100 Temperaturgrad mit einer Umgebungstemperatur  $T_a = -40^{\circ}$ C bis  $+105^{\circ}$ C. Flash-basierte FPGA der Firma Microsemi sind aufgrund der ausgereiften und älteren Prozesstechnologie bis  $T_j = 135^{\circ}$ C qualifiziert und auch bei höheren Temperaturen erprobt [BMVBK10]. Somit sind frei programmierbare ICs technologisch für den Automobilmarkt geeignet, wenn auch nicht in besonders rauen Umgebungen im Motorraum.

#### 2.1.2. Entwicklungsablauf

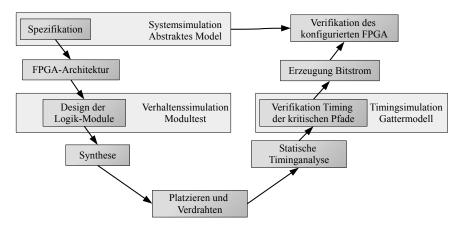

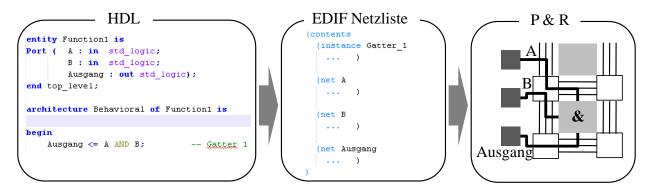

Die Entwicklung einer FPGA Schaltung läuft in ähnlichen Schritten wie die Entwicklung eines ASIC ab [Sau10], jedoch unterscheidet sich das Resultat der Abläufe. Nach der Konzeptphase beginnen die Entwicklungsumgebungen der Hersteller bei der Beschreibung der Funktion mittels einer Hardwarebeschreibungssprache wie Very High Speed Integrated Circuit Hardware Description Language, VHSIC Hardware Description Language (VHDL) [IEE09] oder Verilog Hardware Description Language (HDL) [IEE06a]. Danach wird die Beschreibung durch die Synthese in eine elektrische Netzliste umgewandelt. Hier werden die in der HDL beschriebenen Architekturen und Makros interpretiert und in eine Abbildung aus FPGA spezifischen Instanzen wie LUT, FD FF oder RAM Blöcke umgewandelt. Anschließend wird im Map Prozess die erzeugt Netzliste zusammen mit weiteren IP Schaltungen auf die verfügbaren Ressourcen des spezifischen FPGA abgebildet und vorläufig platziert. Im anschließenden Schritt des Place and Route (P&R) erfolgt die finale Belegung der Ressourcen sowie die Zuweisung der Leitungen auf die konfigurierbaren Verbindungspunkte. Das Resultat nach dem nächsten Schritt ist ein Bitstrom (engl. Bitstream), mit dem die Konfigurationsbits nach dem Laden gesetzt werden. Während die Synthese noch mit Programmen von Drittanbietern durchgeführt werden kann, z.B. Mentor Graphics® Precision oder Synopsys® Synplify, muss der Map Prozess und nachfolgende Prozesse mit den Programmen der FPGA Hersteller ausgeführt werden.

In Industrieanwendungen muss dieser Ablauf ebenfalls eingehalten werden, jedoch um Verifikationsschritte erweitert. In Abbildung 2.4 wird der Entwicklungsfluss gemäß des V-Modells aus der ISO 26262 [ISO11b] dargestellt. Aktuelle Entwicklungen beginnen mit einem abstrakten Verhaltensmodell, erzeugt in SystemC [IEE06b], Matlab® [Mat12] oder OpenCL [Khr14]. Diese abstrakten Modelle dienen der Systementwicklung und Gesamtsystem-Simulation und werden daher mit Anwendungsfällen simuliert (Use-Case Simulation). Aus dem abstrakten Modell wird mittels High Level Synthese (HLS) oder händisch eine HDL Beschreibung erzeugt, die danach den bekannten Entwicklungsablauf fortführt. Die Verifikation der HDL Verhaltensbeschreibung wird mit Einzelfunktionstests (engl. Unit Tests) durchgeführt, da eine Simulation von Anwendungsfällen auf dieser Abstraktionsebene mehrere Tage in Anspruch nehmen würde. Nach der Synthese und dem P&R wird eine statische Timing Analyse durchgeführt, bei der unter anderem Signallaufzeiten, Taktausbreitung und Sample and Hold Zeiten von FFs unter definierten Bedingungen (Timing Constraints) überprüft werden. Allenfalls in seltenen Fällen wird hier noch eine Einzelfunktion mit Timing Informationen simuliert. Die endgültige funktionale Verifikation findet aufgrund der Reprogrammierbarkeit an realer FPGA Hardware statt.

Abbildung 2.4.: FPGA spezifisches V-Modell in Industrieapplikationen

#### 2.2. Überblick der Ausfallsicherheit des FPGA auf Logikebene

Die in Abschnitt 2.1 dargelegte FPGA Technologie muss für sicherheitsrelevante Applikationen einer ausführlichen Fehleranalyse standhalten. In diesem Abschnitt sind grundlegende Effekte und Toleranzmechanismen beschrieben, die auch im Rahmen einer für den Automobilbereich wichtigen ISO 26262 Qualifizierung in den Fokus rücken. Jedoch sind auch Applikationsbereiche wie Luftfahrt und Raumfahrt, Kraftwerktechnik und Eisenbahntechnik von Fehlern mit kritischen Ausmaßen betroffen. Bei den Gegenmaßnahmen muss unterschieden werden, ob der FPGA Anwender bzw. Programmierer oder der FPGA Hersteller wirksam einen Fehler unterdrücken oder die Fehlerwahrscheinlichkeit reduzieren kann [Sut13] [SSC08]. Hierbei wird zwischen Detektion und Toleranz von Fehlern unterschieden. Wobei für die Gewährleistung der funktionalen Sicherheit nicht beide Methoden gleichzeitig notwendig sind.

#### 2.2.1. Defektquellen und Fehlerausbreitung

Wie bei jedem Very Large Scale Integration (VLSI) IC treten auch beim FPGA zur Fertigungszeit und zur Laufzeit Defekte (engl. fault) auf [SSC08]. Ein Defekt bezeichnet eine veränderte Bedingung oder Situation, die zu einem Fehler führen kann. Beispiele für einen Defekt in einem IC kann ein Oxiddurchbruch, ein ESD Impuls auf einer leitenden Struktur oder ein Strahlungseffekt sein. Ein Fehler (engl. error) resultiert aus einem Defekt oder aus einer systematischen Ursache und bezeichnet die Abweichung von einem Soll-Zustand oder einer Soll-Bedingung. Dies kann zum Beispiel ein falscher Ausgang einer Arithmetikeinheit oder ein falscher Zustandswert in einem FF sein. Letztendlich mündet der Fehler wiederum in einem Schadensereignis (engl. failure) des Gesamtsystems. Die Begriffe Defekt, Fehler und Schadensereignis müssen unterschieden und teilweise getrennt betrachtet werden. Für eine Quantisierung der Ausfallrate  $\lambda$  durch Defekte wird die irreführende Einheit Failure In Time (FIT) verwendet mit 1 FIT = 1 Ausfall pro  $10^9$  Stunden. Dabei gilt für die mittlere Zeit bis zu einem Defekt oder Fehler die  $Mean\ Time\ Between\ Failures\ MTBF = \frac{1}{\lambda}$ .

#### 2.2.1.1. Permanente und flüchtige Fehler

Fehler innerhalb des FPGAs lassen sich in die Kategorien permanent und nicht-permanent, genannt flüchtig, einordnen. Neben mechanischen Fehlern resultieren permanente Fehler hauptsächlich aus der Degradation

| Einteilung               | Defekt                                 | Beschreibung                                                                                                          |

|--------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Flüchtig<br>(Soft Error) | Single Event Upset (SEU)               | Eine Speicherzelle kippt ungewollt von 0 auf 1 oder von 1 auf 0.                                                      |

| (Soft Effor)             | Multi-Bit Upset (MBU)                  | Mehrere Speicherzellen kippen ungewollt aufgrund des gleichen Strahlungsdefektes.                                     |

|                          | Single Event Transient (SET)           | Transienter Ladungsüberschuss in der Logik.                                                                           |

| Pseudo-<br>Permanent     | Soft Error Functional Interrupt (SEFI) | Ein Fehler in der Logik, z.B. undefinierter Zustand oder falscher Zustand. Kann meist nur durch Reset behoben werden. |

|                          | Single Event Latch-up (SEL)            | Durchschalten eines parasitären PNPN-Thyristors in CMOS Strukturen.                                                   |

| Permanent                | Single Event Burnout (SEB)             | Durchschalten einer parasitären Transistorstruktur in Leistungs-MOSFET.                                               |

|                          | Single-Event Gate Rupture (SE-GR)      | Durchbruch des Gate-Oxids durch hohe Spannungen am Gate in Leistungs-MOSFET oder Flash-Zellen.                        |

Tabelle 2.2.: Fehlerarten aus Neutronen- und Alpha Strahlungsdefekten [NYKB08] [KPCC97]

der Halbleiter Prozessstrukturen wie etwa durch freie Ladungsträger in der Gate-isolierenden Schicht des Metall-Oxid-Halbleiter Feldeffekttransistor (MOSFET)s oder durch Elektromigration in den Metalllagen [SKM<sup>+</sup>08]. Die degradierenden Defekte wie Hot Carrier (HC), Negative Bias Thermal Instability (NBTI) und Time-Dependent Dielectric Breakdown (TDDB) reduzieren maßgeblich die Lebensdauer, lassen sich aber auf Zuverlässigkeiten von größer 10 Jahre abmildern [SWC10] [HAP<sup>+</sup>07]. Für eine Zuverlässigkeitsanalyse im Zuge der Automobilqualifikation werden diese Defekte mit FIT Werten versehen [AEC07]. Ferner resultieren diese Defekte in einer Sicherheitsanalyse zu Fehlermodellen wie Haftfehlern (Stuck-At-0 und Stuck-At-1), Kurzschlüssen (Bridging oder Short) und Fehlern im Signallaufzeiten (Path-Delay). Von diesen Fehlern sind FPGAs ebenso betroffen wie ASICs im gleichen Technologieknoten.

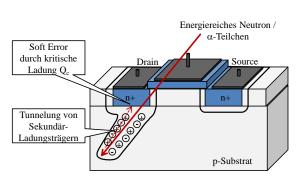

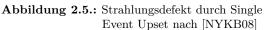

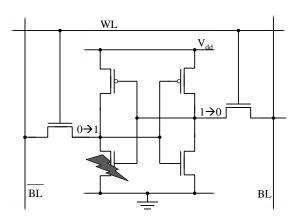

Als flüchtige Fehler bezeichnet die Literatur diejenigen Fehler, deren ursächliche Defekte nicht dauerhaft anhalten und somit nur temporär vorhanden sind. Neben EMV sind Strahlungsdefekte eine Hauptursache für flüchtige Fehler in VLSI Schaltungen [NYKB08]. Die Strahlung wird vornehmlich durch schwere Ionen  $(\alpha$ -Teilchen) aus der Mouldmasse sowie durch Neutronenstrahlung aus der Atmosphäre erzeugt. Hierzu zeigt Tabelle 2.2 eine Übersicht der aus Strahlungseffekten resultierenden Fehler, die unter dem Oberbegriff Single Event Effect (SEE) einzuordnen sind. Neben den flüchtigen Fehlern reduzieren auch permanente Strahlungsfehler die Zuverlässigkeit von FPGAs. Die Metrik für die Strahlungsdefekte SEE wird als Soft Error Rate (SER) bezeichnet. Bei SEEs liegt dabei ein physikalischer Vorgang der Ladungserzeugung durch hochenergetische Strahlung zugrunde, dargestellt in Abbildung 2.5. Hier erzeugt ein energiereiches Neutron oder ein  $\alpha$ -Teilchen sekundäre Teilchen und Elektron-Loch Paare nahe der Raumladungszone einer Complementary Metal Oxide Semiconductor (CMOS) Struktur. Diese Ladungsträgern tunneln in die Strukturknoten und erzeugen eine kritische Ladung  $Q_c$ . Abbildung 2.6 zeigt eine einfache SRAM Zelle ohne Härtungsmaßnahmen, wobei  $Q_c$  den nMOS Transistor der negierten Bitline BL kippt. Tritt das SEE an anderer Stelle im Si auf, kann  $Q_c$  transient weiter in der Logik propagieren (SET). In den in dieser Arbeit betrachteten echtzeitfähigen Automobilanwendungen mit Taktraten von maximal 300 MHz überwiegt die Wahrscheinlichkeit für SEU  $P_{SEU}$  der Wahrscheinlichkeit für SET  $P_{SET}$  und weiteren SEE Effekten [GEBT05]. Für einen 180 nm Technologieknoten liegt die Schwelle für  $P_{SEU}$  größer als  $P_{SET}$  bei circa 900 MHz aufgrund der erhöhten zeitlichen Maskierung. Zudem weisen FPGAs eine um Faktor 10 höhere Leitungskapazität gegenüber technologisch gleichen ASIC auf und sind demnach um ein vielfaches unempfindlicher gegenüber SET  $[LDF^+05]$ .

Abbildung 2.6.: SEU in SRAM Zelle

#### 2.2.1.2. Fehlerpropagation

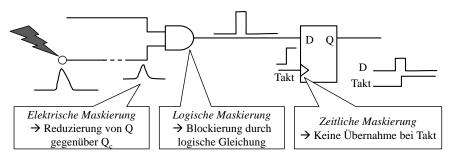

Einmal aufgetretene flüchtige SEE verteilen sich als Fehler über die elektrischen Netze und kombinatorischen Elemente in die Zustände der Schaltung [NYKB08]. Dieser übertragene Fehler im Zustandsspeicher wird persistenter Fehler genannt [MCG<sup>+</sup>05]. Persistente Fehler können nicht durch eine erneute Konfiguration des FPGA behoben werden, da bereits der Zustandsspeicher der Schaltung korrumpiert wurde. Der Übergang in die Persistenz wird jedoch durch drei wichtige Arten der Fehlermaskierung abgeschwächt. Die erste Hürde für die Fehlerpropagation wird als  $Elektrische\ Maskierung$  bezeichnet. Hierbei wird die erzeugte Ladung Q durch Leitungs- und Gatterkapazitäten unter das Niveau von  $Q_c$  verringert und nicht mehr als falscher boolescher Wert interpretiert 2.7. Bei SETs liegt der falsche Wert nur für einige Picosekunden an und zeigt somit eine kleine Wahrscheinlichkeit, an einem Flankenwechsel des Taktes in einen Zustandsspeicher übernommen zu werden. Diese zeitliche Beschränkung der Auswirkungswahrscheinlichkeit wird als Zeitliche Maskierung (engl. Timing Derating) bezeichnet und ist umgekehrt proportional zur Taktfrequenz. Ein weiterer limitierender Faktor für die Fehlerausbreitung liegt in der Beschränkung durch die Logikfunktion selber und gilt sowohl für SET als auch für SEU. Diese Logische Maskierung wird als auch als Logic Derating bezeichnet und verhindert aufgrund der booleschen Funktion des Gatters die Propagation eines fehlerhaften Signals an einem kombinatorischen Ausgang. Beispielsweise wird ein fehlerhafte "0" an einem Eingang eines UND-Gatters nicht propagiert, wenn an weiteren Eingängen Nullen anliegen. Die benannten Maskierungen gelten sowohl für ASIC Bausteine als auch für FPGAs. Da jedoch in FPGAs der Konfigurationsspeicher die Netzliste abbildet, wird bei einem SEU in diesem Speicher die logische Maskierung in der Netzliste nicht mehr vorhersagbar. Somit kann eine von der logischen Maskierung unabhängige Fehlerpropagation stattfinden.

Abbildung 2.7.: Fehlerausbreitung und Fehlermaskierungen nach SEE in der Logik

| Physikalische Veränderung                                | Simulation                                                                                                     | Emulation                                                                         |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| • Definierte Neutronenstrahlung<br>([FPV10])             | • Vorwärtsgerichtete Fehlerinjektion in der Netzliste ([KSL <sup>+</sup> 06], [MWE <sup>+</sup> 03]) ([FPV10]) | • Initiale oder laufzeitfähige Bitstrom-Manipulation ([LBN10], [DASS09], [SKK11], |

| • Energieeintrag mittels Laser ([PMN <sup>+</sup> 09])   | • Rückwärtsanalyse der Fehlerausbreitung ([HRSH11])                                                            | [MCG <sup>+</sup> 05])  • Statische Zusatzelemente                                |

| • Elektromagnetische Interferenz ([VCG <sup>+</sup> 05]) | additionally ([IIIdditii])                                                                                     | in der Schaltung zur Feh-<br>lereinspeisung zur Laufzeit<br>([LOGVPGEA05],[MS13]) |

Tabelle 2.3.: Schwachstellen (SEFI) Analyse

#### 2.2.2. Fehlertoleranz zur Reduzierung der Fehlerauswirkung

Die Propagation der in Abschnitt 2.2.1.1 erläuterten Fehler auf Systemebene müssen so weit verhindert werden, dass kein Schadensereignis (engl. failure) auftritt. In diesem Abschnitt werden ausschließlich Toleranzmechanismen innerhalb des FPGAs angeführt. In einem Steuergerät mit weiteren ICs können neben den FPGA-internen Maßnahmen auch systemweite Fehlertoleranzen implementiert werden. Diese sind jedoch nicht im Fokus dieser Arbeit. Für fehlertolerante FPGA Schaltungen werden drei Schritte erläutert. Zudem ist es für einen Schaltungsentwickler entscheidend, ob eine Maßnahme durch den FPGA Hersteller oder durch den Anwender implementiert werden kann. Mechanische und degradierende Defekte der CMOS Strukturen müssen ebenso wie im ASIC adressiert werden [SKM<sup>+</sup>08].

#### 2.2.2.1. Schwachstellenanalyse

Neben der Reduzierung der Defektwahrscheinlichkeit durch Technologie- und Prozessmethoden muss die Schwere der Auswirkungen der Fehler beurteilt werden. In einer Digitalschaltung auf dem FPGA hat nicht jedes transient fehlerhaftes Konfigurationsbit oder jedes transient fehlerhaftes Gatter ein Schadensereignis zur Folge [MCG<sup>+</sup>05] [MWE<sup>+</sup>03]. Permanente Defekte und somit statische Fehler wirken sich über die Lebensdauer der Schaltung immer auf den Ausgang aus, insofern keine redundanten oder schlafenden Schaltungsteile existieren. Somit zielen die Schwachstellenanalysen aus Tabelle 2.3 in erster Linie auf flüchtige Fehler oder das Finden von kritischen Speicherelementen ab. Genauer gesagt werden dabei die Propagation von flüchtigen Fehlern und die Laufzeit von permanenten Fehlern untersucht und Gegenmaßnahmen evaluiert.

Die Methoden für die SEFI Analyse lassen sich in drei Prinzipien gliedern. Durch direkte physikalische Veränderungen in der Si-Struktur lassen sich Defekte meist ungezielt aber realistisch nachstellen. Zudem kann die Fehlerpropagation zur Laufzeit untersucht werden. Im Gegensatz dazu können mittels simulativer Methoden dedizierte Defektstellen nachgestellt und der Propagationsweg genauestens beobachtet werden. Nachteilig wirken sich hier die lange Rechenzeit, die Abhängigkeit von Eingangspattern und die Annahme einer korrekten Netzliste im CRAM aus. Durch Emulation von Fehlern kann zur Laufzeit eines FPGA Systems ein Fehler injiziert werden. Hier sind die Fehlermodelle jedoch sehr stark auf SEUs eingeschränkt. In Tabelle 2.3 werden mit den physikalischen Veränderungen des ICs und der Manipulation des Bitstromes zudem bereits Methoden der Fehlerinjektion in den Konfigurationsspeicher aufgezeigt. Diese Fehler im CRAM werden im späteren Abschnitt 2.3 eingeführt und genauer untersucht.

#### 2.2.2.2. Detektion und Korrektur von Fehlern in der Logik

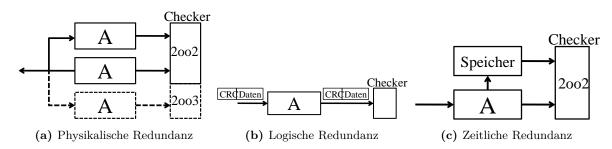

Die Defektwahrscheinlichkeit bleibt bei jedem VLSI IC immer größer als Null. Die Annahme der zufälligen Hardwarefehler in dem Standard ISO 26262 ist dieser Tatsache geschuldet [ISO11a]. Somit müssen gegen permanente Fehler und auch gegen die Fehlerausbreitung aus den ermittelten Schaltungsteilen der Schwachstellenanalyse Toleranzmechanismen eingefügt werden. In der Praxis haben sich physikalische, logische und zeitliche Redundanzen als wirksam erwiesen [Sut13]. Physikalische Redundanzen nach Abbildung 2.8a werden als Double Checker Redundancy (DCR) doppelt mit einer Zwei-aus-Zwei Prüfinstanz (2002) oder als Triple Modular Redundancy (TMR) dreifach mit einem Zwei-aus-Drei Entscheider (2003) eingesetzt. Diese Art der Redundanz lässt sich auf vielen Abstraktionsebenen einfügen. Auf der CMOS Strukturebene sichern doppelte p- und n-Kanal MOSFETs einen Ausfall ab [NYKB08]. Eine Abstraktionsebene höher verwenden die Hersteller verschiedene Aufbauarten für FF, LUT und SRAM Zellen mit zusätzlichen Transistoren und Leitungen. Bis zu dieser Ebene hat der Endanwender keine Möglichkeit zur Optimierung der Fehlertoleranz. Ab der Implementierungsebene mit der Netzliste können feingranulare Redundanzen eingefügt werden [NSB12], bei der einzelne Gatter verdoppelt oder verdreifacht werden. Diese Art der physikalischen Redundanz in der Schaltungsentwicklung ist skalierbar und vielseitig [CB09]. Daher bieten Hersteller wie Xilinx mit dem TMRTOOL [Xil12b] oder Mentor Graphics mit Precision Hi-Rel [PM11] vollwertige Lösungen für VHDL Modul- und Netzlistenredundanzen. Zudem gibt es weitere Optimierungen für das automatisierte Einfügen von TMR und DCR mit Hinblick auf Flächenverbrauch, Leitungsredundanzen, Timing und Anwendung der PDR zum Modultausch [BMS11] [KFC06] [JW10] [RMR09] [Ste09]. Neben der Logik lassen sich auch die RAM Blöcke redundant auslegen. Nachteilig bei allen physikalischen Redundanzstrukturen ist der Entscheider (engl. Voter) oder Überwacher (engl. Checker), der ebenfalls redundant oder extern ausgelegt werden muss [FPV10]. Ferner widerspricht der erhöhte Flächenbedarf einer kostenoptimalen Lösung.

Abbildung 2.8.: Redundanzen zur Fehlerdetektion und Fehlertoleranz

Bei logischen Redundanzen werden interne Zustände oder Kommunikationen gesichert ausgelegt, beispielsweise über zusätzliche Cyclic Redundancy Check (CRC) Prüfsummen im Datenstrom aus Abbildung 2.8b. Zustandsautomaten werden mittels *Hot-One* Verfahren oder durch Definition von Alternativzuständen gesichert [PM11]. Ferner kann der interne Datenfluss logisch redundant ausgelegt werden, wenn die CRC Prüfsumme für die Daten eines Busses oder eines Signalbündels mit übertragen wird [LBN11]. Interne RAM Blöcke können über ECC Paritätsbits abgesichert werden [RFW10]. Hierzu werden zu je 64 Datenworten weitere 8 Paritätsbits hinzugenommen. Mit einer zeitlichen Redundanz kann der Zeitpunkt eines Fehlerauftritts bestimmt werden, da hier derselbe Algorithmen zeitlich nacheinander zweimal durchlaufen wird [YM01] (Abbildung 2.8c).

Fehlertolerante Systeme im Bereich des automatisierten Fahrens oder elektrische Lenkung müssen auch im Fehlerfall weiter operieren (engl. fail operational). In vielen Fällen genügt nach einem Fehler jedoch die korrekturunabhängige Erreichung eines sicheren Zustandes mit anschließender Korrektur (engl. fail safe).

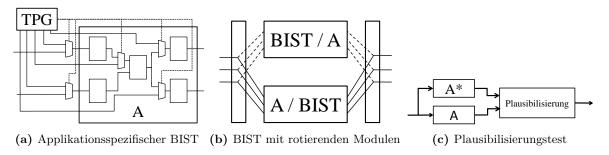

Hierfür müssen permanente und flüchtige Fehler detektiert werden. Mittels eines Applikationsspezifischen Selbsttest (engl. application specific Build-In Self-Test (BIST)) können Haftfehler und Kurzschlüsse auf den verwendeten FPGA Ressourcen erkannt werden [Tah06]. Durch Anpassung der Schaltung mit Zusatzgattern wie ODER und AND-Verknüpfungen können dedizierte Pfade getestet werden und die Testabdeckung steigt (Abbildung 2.9a). Ferner können FPGA Ressourcen durch einen BIST belegt werden während die funktionale Schaltung durch PDR umplatziert wird (engl. roving) [SSC08] (Abbildung 2.9b). Im Falle von detektierten permanenten Fehlern werden Alternativplatzierung aus der Designphase verwendet [WJW<sup>+</sup>13]. Eine weitere Möglichkeit zur Fehlerdetektion zeigt die Plausibilisierungsprüfung (Abbildung 2.9c). Hier wird der Algorithmus A formalisiert und es werden kritische Parameter alternativ berechnet (engl. Concurrent Error Detection (CED))[LCR03]. Die Plausibilisierung deckt latente Fehler nicht ab, aber es werden alle sicherheitskritische Parameter zur Laufzeit evaluiert. Dabei kann der ursprüngliche Datenfluss durch zeitliche Redundanz nochmal codiert durchlaufen werden oder durch physikalische Redundanz jeweils codiert und uncodiert berechnet werden. Alternativ kann durch codiertes Prozessieren (engl. encoded processing) ein Berechnungsfehler entdeckt werden [SFRB05].

Abbildung 2.9.: Fehlerdetektion in der Logik einer FPGA Schaltung

# 2.3. Beschreibung von flüchtigen Fehlern im Konfigurationsspeicher

Wie bereits in den Ausführungen über Fehlerarten erwähnt, sind SRAM Zellen besonders anfällig für SEUs. Die Gründe für die Fokussierung auf SEUs anstelle von SET sind in Abschnitt 2.2.1 erklärt. Ein Großteil dieser Arbeit zielt aufgrund der hohen Dichte von SRAM-Zellen auf den Konfigurationsspeicher kommerzieller FPGAs, exemplarisch der Firma Xilinx. Da die FPGAs der Firma Altera technologisch ähnlich aufgebaut sind und auch bei der Taiwan Semiconductor Manufacturing Company (TSMC) gefertigt werden, treffen folgende Aussagen auch für diese Bausteine zu. Im Weiteren wird der SRAM des Konfigurationsspeichers als CRAM bezeichnet. Moderne große Bausteine haben ein CRAM von ca. 300 Mbit [Xil13b, Alt13b]. Es zeigt sich zudem in den folgenden Ausführungen, dass der Konfigurationsspeicher eine bis zu vierfach höhere Wahrscheinlichkeit für flüchtige Fehler gegenüber Logik-FF innerhalb eines FPGA hat. Flüchtige Fehler können als Einzelbitfehler gewertet werden. In diesem Abschnitt werden nichtflüchtige Fehler nicht separat behandelt, da diese zum großen Teil in der Fehlerdetektion enthalten sind.

#### 2.3.1. Fehlerwahrscheinlichkeiten für flüchtige Fehler

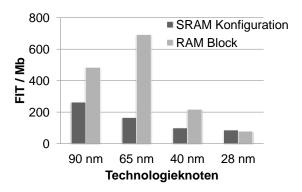

Das CRAM wird größtenteils statisch zur Ablage der Netzlisteninformation genutzt. Daher können flüchtige Fehler nur als SEUs zuverlässig detektiert und ausgewertet werden. In Abbildung 2.10 wird quantitativ die SER für Xilinx FPGAs dargestellt. Die aus dem Xilinx Zuverlässigkeitsreport [Xil13c] entnommenen Werte entsprechen in der Größenordnung auch Werten weiterer Untersuchungen [Les12, DLGO04]. Die Defektwahrscheinlichkeit für SEUs im CRAM hängt unter anderem von der kritischen Ladung  $Q_c$ , der kritischen Fläche  $A_c$  und dem Strahlungsfluss im Substrat ab [NYKB08]. Durch zusätzliche Kapazitäten und Widerstände innerhalb der SRAM Zelle wird  $Q_c$  auf Kosten zusätzlicher Fläche erhöht. Bei kleiner werdenden Technologieknoten verringert sich  $Q_c$  jedoch und muss durch die reduzierte kritische Fläche  $A_c$  kompensiert werden. Zudem wird in aktuellen 28 nm TSMC Technologien der  $\alpha$ -Strahlungsfluss durch bis zu 12 Metalllagen reduziert [DW12]. Diese Abschirmung bewirkt zusammen mit der Verwendung von Ultra Low-Alpha Mouldmasse und Materialien mit kleiner Wechselwirkungswahrscheinlichkeit eine reduzierte SER gegenüber Vorgänger-Technologien.

**Abbildung 2.10.:** Mittelwert SER für Xilinx FPGAs [Xil13c]

Tritt ein SEU im Konfigurationsspeicher auf, trifft er mit einer Wahrscheinlichkeit von maximal 10% ein essentielles Bit [Xil13c]. Nur essentielle Bits im CRAM haben Einfluss auf die Konfiguration und die Netzliste der Schaltung. Somit werden etwa 90% des CRAM aufgrund der feingranularen Struktur nicht verwendet. Für eine weitere Fehlerpropagation in der Logik gemäß Abschnitt 2.2.1 muss demnach ein essentielles Bit betroffen sein.

Der Vergleich der Fehlerwahrscheinlichkeit von FF und CRAM soll exemplarisch anhand des Xilinx Kintex 7 XC7K325T aufgezeigt werden. Tabelle 2.4 zeigt den quantitativen Vergleich, wobei die SER Metriken für den 28nm Technologieknoten von TSMC gelten. Es ergibt sich eine bis zu vierfach höhere SER für das CRAM gegenüber den enthaltenen FF, trotz der durchschnittlich nur 10 % verwendeten Konfigurationsbits. Mit diesen Zahlen liegt auf der Absicherung des Konfigurationsspeichers eine sehr hohe Priorität.

Die Fehlerwahrscheinlichkeit für einen SEU hängt davon ab, wie viele dieser flüchtigen Fehler zu Einzelbitfehlern führen. Um Multibit-Fehler (MBU) zu vermeiden, verwenden die Hersteller Bitverschiebungen zwischen den CRAM Bereichen (engl. bit scrambling) in einer verschachtelten Anordnung (engl. interleaved bits) [BSV11] [WTH13]. Hierdurch werden logisch zusammenhängende Speicherzellen aus einem Wort oder Bereich auf dem Die physikalisch voneinander getrennt (Abbildung 2.11 b). Dadurch kann ein MBU zu SEUs in mehreren Speicherwörtern oder Speicherframes werden [ICW+06]. Die Wahrscheinlichkeit, dass ein MBU sich in allen beteiligten Frames als SEU auswirkt liegt bei über 90 % [WTH13]. Ein Zweibitfehler in einem

Frame hat noch eine Wahrscheinlichkeit von 7,5 %.

**Tabelle 2.4.:** Fehlerwahrscheinlichkeiten für flüchtige Fehler im CRAM und in FF eines Xilinx Kintex 7 XC7K325T

|                             | CRAM                   | Flip-Flop                                                                                            |

|-----------------------------|------------------------|------------------------------------------------------------------------------------------------------|

| SER <sup>1</sup>            | 86 FIT / Mbit [Xil13c] | $\approx 500 - 1000 \; \mathrm{FIT} \; / \; \mathrm{Mbit}$ $[\mathrm{GBN}^+11, \; \mathrm{LBW}^+13]$ |

| Anzahl Bits                 | 91,5 Mbit [Xil13b]     | 0,41 Mbit [Xil14]                                                                                    |

| SER pro Device <sup>1</sup> | $\approx$ 790 FIT $^2$ | pprox 200 - 410 FIT                                                                                  |

$<sup>^{1}</sup>$  Höhenniveau: New York

Auch Flash-basierte Speicherzellen sind nicht immun gegen SEU. Sie zeigen jedoch eine um  $10^3$  reduzierte Wahrscheinlichkeit für Datenerhaltungsprobleme durch SEU gegenüber SRAM-basierten FPGA [Sla11,  $CPL^+02$ ]. Im Zuge der kleiner werdenden Technologieknoten für Flash Zellen sinkt die Ladung im *Floating Gate* und erhöht in der Zukunft die SEU Rate [Sla11] [KFV $^+11$ ]. Somit sind Detektionsmechanismen für Fehler im Konfigurationsspeicher auch für diese Technologie nötig.

- (a) Logische Anordnung mit SECDED ECC Paritätsbits

- (b) Physikalische verschachtelte Anordnung (interleaving bits)

Abbildung 2.11.: Logische und physikalische Anordnung von CRAM Frames

#### 2.3.2. Funktionale Fehlermodelle

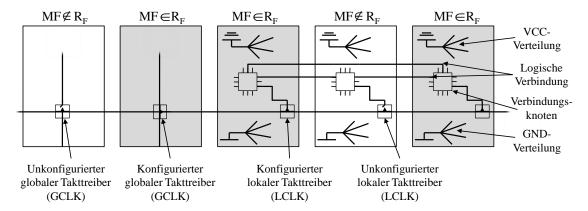

Im Falle eines SEUs im CRAM sind die Verbindungsknoten der flexiblen Verdrahtung aus Abbildung 2.2 in Abschnitt 2.1.1 zu ca. 90 % betroffen. Insofern stellen die Verbindungsknoten und deren Test die besondere Herausforderung für eine effiziente Fehlerdetektion und -Korrektur dar. Die genaue Analyse der potentiellen Fehlermodelle in den Verbindungen zeigt auf, dass auch diese CRAM Anteile deterministisch und lokal begrenzt getestet werden können. Im Folgenden werden die Fehlermodelle und notwendigen Überwachungen für die logischen Verbindungen, die statischen Signale und die verteilen Netze aufgezeigt. Als verteiltes Netz ist standardmäßig der Taktbaum anzusehen oder in Einzelfällen eine Enable- oder Reset-Struktur.

#### • Logische Verbindungen

Die Logiknetze sind Punkt-zu-Punkt Verbindungen von einem Verbindungsknoten zum anderen. Jegliche Signalverteilung erfolgt über die Konfiguration in diesen Knoten, wobei die Verbindungen selbst dedizierte Signalwege ohne CRAM Anteil sind. Daher entstehen Fehler für die logischen Signale in den Verbindungsknoten, die sich nach dem P&R Vorgang für die elektrischen Netze lokalisieren lassen. Ein Fehler in einem anderen Knoten als den zum Netz gehörigen wirkt sich nicht auf die logischen

$<sup>^2</sup>$  Max.  $10\,\%$  Essentielle Bits [Xil13c]

| Verbindungsart | Logische Verbindung | Statisches Signal                           | Verteiltes Netz                                 |  |

|----------------|---------------------|---------------------------------------------|-------------------------------------------------|--|

| Ausbreitung    | Punkt-zu-Punkt      | Ein Major Frame                             | Multiple Major Frames                           |  |

| Lage der PIP   | Verbindungsknoten   | Verbindungsknoten<br>Quelle: Instanz TIE0FF | global: Takttreiber<br>lokal: Verbindungsknoten |  |

| Fehlermodell   | Falsche Verbindung  | Kurzschluss                                 | Erhöhter Jitter, kein Takt                      |  |

| Auswirkung     | Fehlerhafter Pegel  | Erhöhte Stromaufnahme                       | Funktionale Fehler                              |  |

Tabelle 2.5.: Korrelation der Fehlermodelle im Verbindungsgitter zu CRAM Ressourcen

Verbindungen einer Schaltung aus.

#### • Statische Signale

Die statischen Signale werden an multiplen Quellen der Logik über die TIEOFF-Platzhalter mittels ungenutzter LUTs zugänglich gemacht. Die Verteilung erfolgt lokal begrenzt über die Verbindungsknoten an mehrere Senken. Das Fehlermodell ist hier, dass in einem an der Quelle angeschlossenen Knoten ein Fehler auftritt und VCC zu GND oder zur Logik kurzschließt. Der Kurzschluss auf Logikleitungen hat keinen funktionalen Einfluss wenn die Logikleitung kein elektrisches Netz der Schaltung ist. Der Kurzschluss von VCC zu GND kann zum Ausfall des gesamten FPGA führen.

#### • Verteilte Netze

Die verteilten Netze sind als Taktsignale global oder in Regionen hierarchisch verteilt, haben jeweils eine Quelle pro Taktregion und werden durch Treiber propagiert. Die globale Verteilung der Taktsignale erfolgt über dedizierte Takttreiber wie HCLK oder CLK\_BUFG. Die lokale Verteilung zur Logik oder zu dedizierten Blöcken wird mittels Verbindungsknoten hergestellt. Ein Ausfall oder Jitter im Taktnetz wird durch einen fehlerhaften Takttreiber hervorgerufen. Ein Kurzschluss zu VCC oder GND ist nur in den Verbindungsknoten möglich.

Ein Überblick über die genannten Fehlerbilder stellt Tabelle 2.5 dar. Für die Fehlerdetektion ist vor allem die Ausbreitung der verteilten Netze relevant, da dadurch der maximale Testbereich für diese Verbindungen definiert wird.

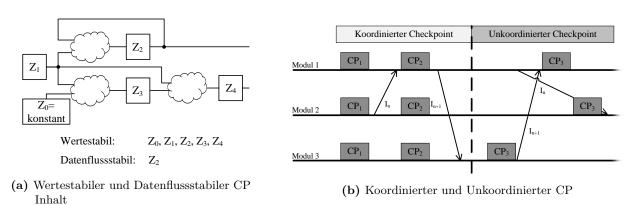

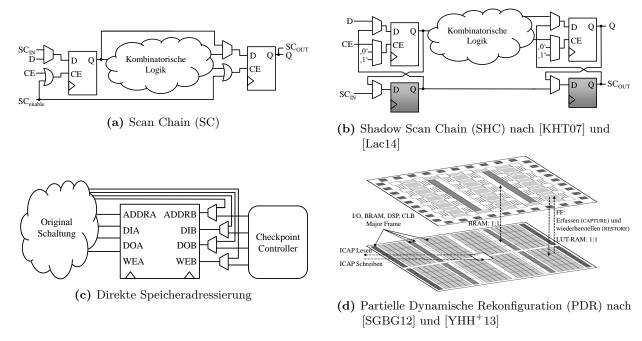

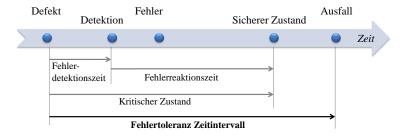

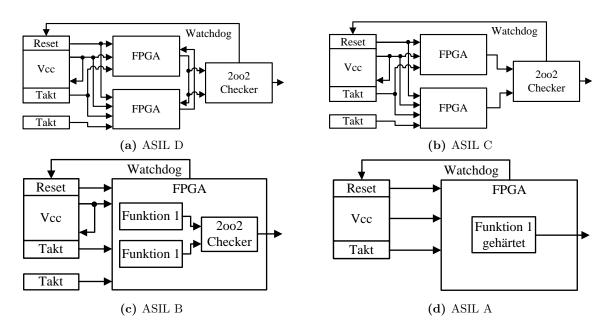

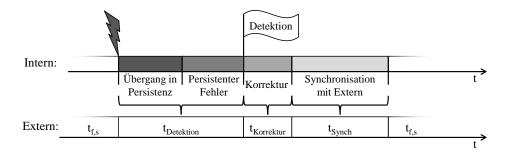

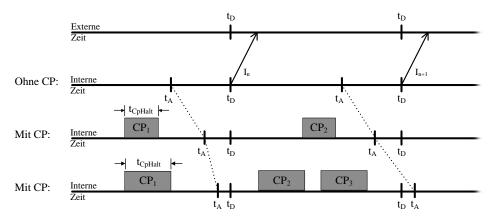

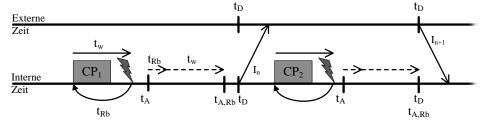

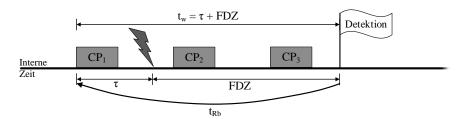

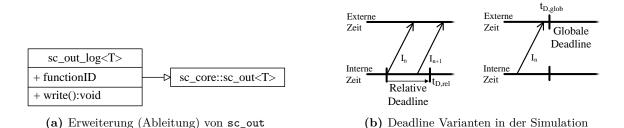

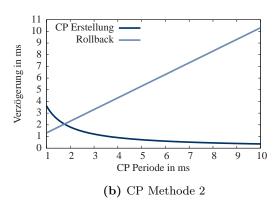

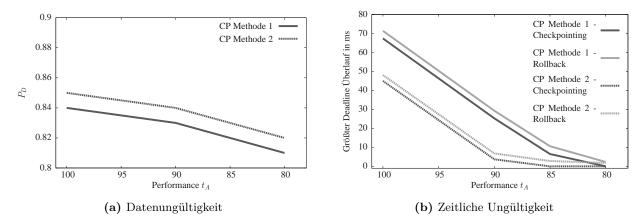

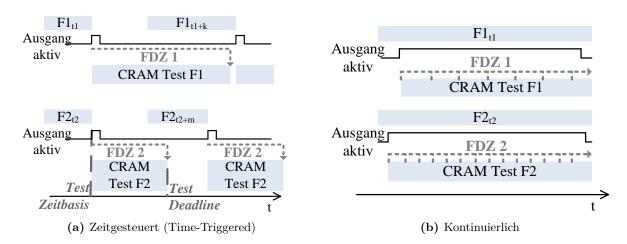

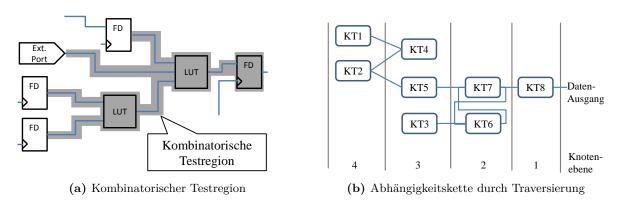

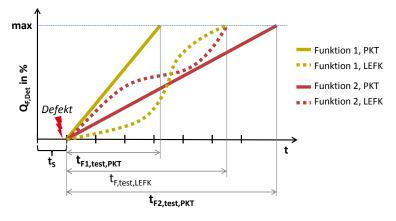

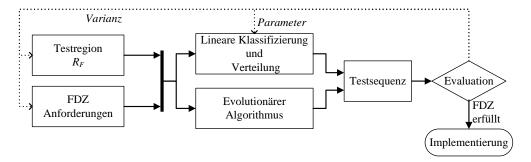

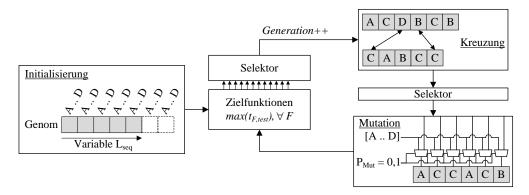

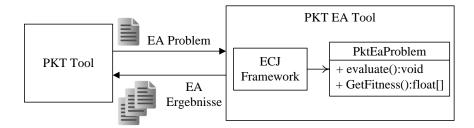

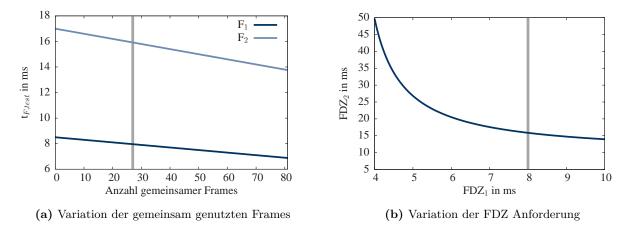

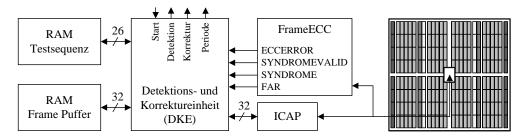

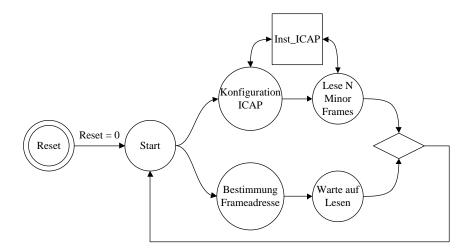

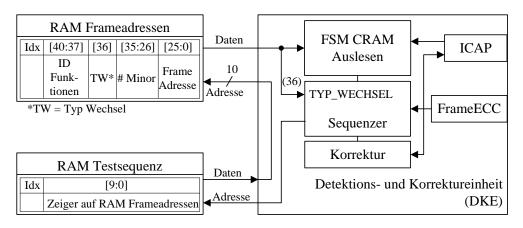

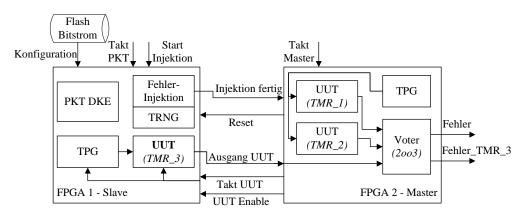

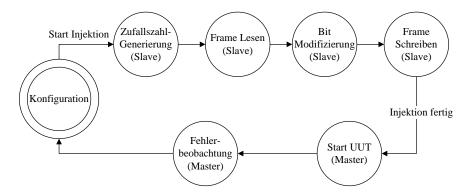

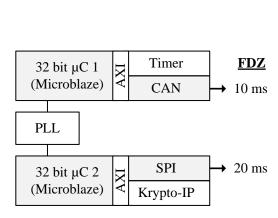

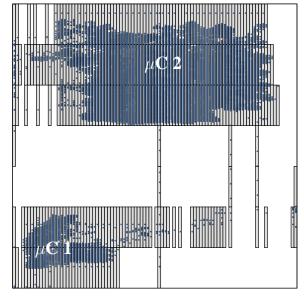

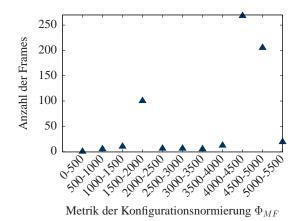

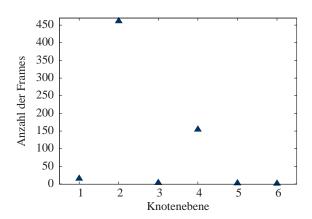

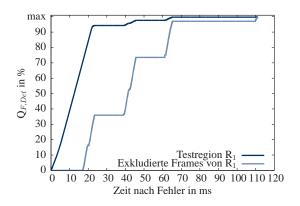

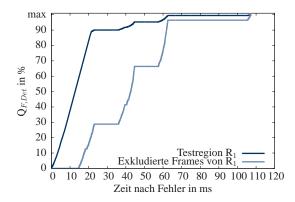

#### 2.3.3. Detektions- und Korrekturmaßnahmen