# TUM

# INSTITUT FÜR INFORMATIK

Model-Based Deployment: From a High-Level View to Low-Level Implementations

Andreas Bauer, Jan Romberg

TUM-I0406 Mai 04

TECHNISCHE UNIVERSITÄT MÜNCHEN

TUM-INFO-05-I0406-0/1.-FI

Alle Rechte vorbehalten

Nachdruck auch auszugsweise verboten

©2004

Druck: Institut für Informatik der

Technischen Universität München

# Model-Based Deployment: From a High-Level View to Low-Level Implementations

Andreas Bauer, Jan Romberg

Institut für Informatik, Technische Universität München

Boltzmannstr. 3, D-85748 Garching b. München, Germany

{baueran|romberg}@in.tum.de

#### Abstract

The development of distributed applications in the automotive domain based on networks of electronic control units is getting increasingly complex and error-prone. In current practice, system-level views of the network are merely used to characterise broad technical constraints such as performance requirements, and to chose the hardand software components accordingly. In contrast, the semantic integration of the distributed functions is typically deferred to later points in the development process, yielding an outstanding effort for integrating and validating such distributed functions. To address in particular this issue, our paper advocates a more stringent use of high-level models based on distinct abstractions and a well-defined behavioural semantics. Corresponding notations, tools, and overall methodology envisioned to support a stepwise development of distributed automotive applications are being introduced. Most importantly, the paper details on the issues of using such high-level models to facilitate deployment and to obtain low-level implementations of integrated system models.

#### 1 Introduction

Until recently, the electronic control system in a vehicle was mostly concerned with light switches, windshield wipers, or starter motors all of which were, more or less, realised as isolated systems provided from independent suppliers. Traditionally, the software for such embedded systems was implemented in a relatively low-level fashion as C, or Ada programs, and often directly in terms of native machine code. The last decade, however, saw an increasing use of integrated development toolkits such as ASCET [4], or the Simulink Real-Time Workshop [7] which facilitate reuse and provide retargetable generation of code based on dataflow models.

However, the nowadays increasing number of distributed electronic control units (ECU) in vehicles imposes fundamentally different problems for the automotive industry which is not tackled by the existing tool support alone. The sharing of data between ECUs that communicate via dedicated busses and bus protocols (e. g. CAN, MOST) allows the integration of additional functionality at lower costs. Consequently, this domain now requires different abstraction levels to be able to capture the actual dataflow between distributed ECUs inside vehicles as well.

Such higher-level models are also necessary to simulate and verify the behaviour and communication between ECUs to guarantee for safety and reliability of the deployed software. Ideally, the abstract models also facilitate reuse on various levels of abstraction. In a distributed system, isolated C solutions are clearly not suitable for these requirements. However, high-level models raise a number of other issues though: for example, is it feasible to use them directly for code generation in a domain which, traditionally, confronts

its users with devices bearing hardly any resources? (i. e. memory, stack space, number of available registers, etc.)

Therefore in § 2, this paper will first outline such a typical target platform for (safety critical) embedded software as we encounter it prominently in the automotive domain. The actual partitioning and deployment issues are described in § 5 for which we first introduce abstractions and system descriptions that will also help classify the presented concepts in a realistic automotive industry context. Additionally, we briefly sketch the underlying synchronously clocked computational model which we assume for deployed applications and use in our own tool prototypes.

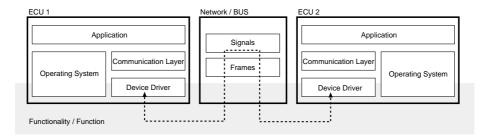

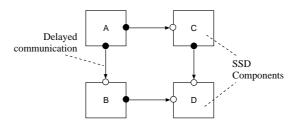

Figure 1: A distributed target architecture.

### 2 An Abstract Target Platform

Our abstract target consists of a network of ECUs connected via a bus. As can be seen in Fig. 1, each ECU is embedded into a *host node* which consists of the ECU itself, an operating system, a device driver module for interfacing the bus, one or many application tasks, and a dedicated communication layer.

The horizontal bar at the bottom of Fig. 1 indicates that the functionality contained within a high-level system model may be arbitrarily distributed among the nodes of the network, i.e. distribution of a functionality is transparent in a top-down systems view. (Note that the terms "function" and "functionality" are used as synonyms in this context to describe a certain ability, or property of the system.)

The dedicated communication layer is merely a wrapper around the inter-task communication between applications of spatially separated ECUs. Its main purpose is to manage resources needed to buffer signals whenever necessary (see also  $\S 5.1$ ). Communication itself, however, is handled by the device drivers which can be automatically generated for each ECU and protocol variant.

# 3 Abstraction & System Description

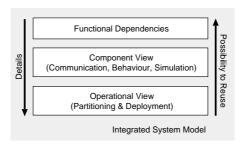

With the ongoing shift in the automotive industry towards distributed—and ideally reusable—software components, practitioners are not faced with a uniform system view anymore, e. g. source code. Components are now designed to be *automatically* deployed in a range of different vehicle types within a single class many of which offer, say, varying on-board electronic controllers and as well as a different number of available ECUs for deployment. On a more abstract level, the behavioural view of the rather differently deployed components is expected to remain constant though. Fig. 2 illustrates how different abstract views on automotive software components can be integrated to a common integrated system model.

The view on functional dependencies is, typically, the most abstract model of an automotive system. It captures the structure as well as the functional dependencies common

Figure 2: Abstract system views.

to a class of vehicles by the same manufacturer. A component view, on the other hand, contains the internal interaction patterns of individual software components in terms of dataflow, communication and behaviour. This is already sufficiently useful and detailed to allow for validation and simulation of designs, while the operational view, typically, contains aspects which are unique to the actual target platform. Naturally, reuse of components gets increasingly difficult with a decreasing level of abstraction.

Each level needs to be associated to a number of custom description techniques, first to allow for independent top-down systems design, e.g. abstract definition of sensor and actuator components, and secondly for a subsequent refinement down to a mapping onto actual hardware.

**Functional Dependencies:** Common to this view are structure oriented views, i.e. system structure diagrams (SSD), to describe the overall structure of a system. Typically, SSDs are specified as hierarchical component networks, where components communicate via *typed* and *directed channels* and typed *ports*, similar to the visual representation of UML-RT [10] and some Architecture Description Languages.

Component View: In this abstraction, we require a description of the individual software components to be complete with respect to behaviour. Therefore, the employed description techniques, typically, include finite state machines (FSM), low-level dataflow diagrams (DFD), or more message-oriented diagrams (see also [5]). DFDs can be viewed upon as a refinement of SSDs and describe the algorithmic dataflow occurring during a computation. They consist of components performing the computation (i. e. blocks), interface elements of those components (i. e. ports), and connections between those interface elements (i. e. channels).

Operational Model: The operational model employs a similar visual representation as the component view — cluster communication diagrams (CCD) — but it is an implementation-driven refinement containing those details essential for deployment. CCDs then represent the main computational units (i. e. clusters, abstract tasks) that interact *directly* with the real-time operating system (scheduler) and the dedicated computational layer; that is, clusters are the least distributable units from the integrated system model: clusters are not split across two tasks and are always connected using explicit signal sampling operators (see § 4 and § 5.2).

Note, at this point, we abstain from giving a more detailed description of the individual visual representations and their exact properties as the important graphical notations relevant for this paper are introduced in  $\S 4$  and  $\S 5$  by practical examples, respectively.

## 4 Computational Model & System Behaviour

The behavioural model of the systems described in this paper is that of current AUTOFO-CUS [1, 5] models. It is based on the *synchrony hypothesis* using a discrete notion of time. The synchronous paradigm [2, 3] basically states that a system reacts to external stimuli within one instant, i. e. the delay between internal computations cannot be observed. This approach has enjoyed widespread acceptance in the control and hardware design domains, and is largely compatible with the commercially established tools such as ASCET, or Simulink. As opposed to several other approaches used for real-time specification and programming, the discrete-time semantics and deterministic concurrency keep behavioural evaluation of large designs manageable. The AUTOFOCUS framework is based on such a deterministic time-synchronous interpretation: *components* communicate through timed *streams*, where each stream uses the same global time base.

In order to support the multiform event patterns and frequencies observed in typical real-time systems, each stream of signals is associated with a *clock*. Similar to other synchronous dataflow languages [2], an AUTOFOCUS clock can be thought of as a boolean stream that merely indicates whether a value is currently present (*tt*), or not (*ff*). Clocks characterise streams both external, such as frequencies imposed by surrounding actors or real-time constraints, and internal to the system: by using clock inference properties the internal clocks can be inferred from the according inputs, respectively. (Think of the integration of black-box "legacy components", for example.)

Our current tool prototypes provide both automated inference of internal clocks and static checking of well-formedness of the model, i.e. detecting absence of causal cycles and soundness verification of clocks. The implementation is very similar to that of a static type system in strongly typed programming languages.

In AUTOFOCUS, each clock is defined w.r. t. a *base clock*, k, which is the fastest clock in and underlying a system. The base clock itself is represented by the boolean expression tt, i. e. the expression that evaluates to true at any instance of k. A model's clock expressions are typically ordered using a  $\leq$ -relation.

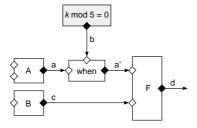

Figure 3: Explicit signal sampling in DFDs.

Furthermore, in AUTOFOCUS it is not only possible to infer clocks, but also to make up new ones based on other clock expressions. The DFD given in Fig. 3 bears an explicit when operator which samples the input stream a to the rate of boolean stream b; that is, a'=a whenever b evaluates to tt. The output and input ports are depicted by black and white rectangles, respectively.

In accordance with the notion of using clock expressions, all of a system model's entities can be represented using a dedicated language based on general expressions. Consequently, *expressions* in AUTOFOCUS range over channels, ports, and combinations thereof using dedicated operators.

Let Exp be the set of all such expressions used in a system model and let  $Exp_{\mathbb{B}}$  denote the set of all boolean expressions. We can now introduce a function ck which gives us the actual clock of any element  $e \in Exp$ :

$$ck: Exp \to Exp_{\mathbb{R}}$$

.

**Example.** To illustrate how clocks are put into practice, let's assume that the following virtual values are being transmitted in the model as it is given in Fig. 3 where  $\tau$  denotes an absent signal/value:

$$a: \ 1 \ 2 \ 3 \ 4 \ 5 \ 6 \ 7 \ 8 \ \dots$$

$b: \ tt \ ff \ tt \ ff \ tt \ ff \ tt \ ff \ \dots$

$a'=a \ \text{when} \ b: \ 1 \ \tau \ 3 \ \tau \ 5 \ \tau \ 7 \ \tau \ \dots$

$c: \ 0 \ \tau \ 1 \ \tau \ 2 \ \tau \ 4 \ \tau \ \dots$

Here, the when operator projects the stream a to the slower clock of stream b. However, up sampling works accordingly and is achieved using the same operator.

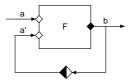

In order to allow for well-defined feedback loops and to provide memory slots holding temporary values, explicit delay operators are necessary. Fig. 4 depicts a model which makes use of an explicit delay block (black and white diamond shape) that behaves as follows: a value is held for one clock period respectively; the period is determined by the clock speed of the stream setting that value.

Figure 4: DFD with delayed signal.

Here, the delay is used to "feed back" a previous value of F's computation, b. For such models, it is assumed that delay blocks are initialised accordingly, although the exact value does not matter in this case. Note, the use of delays does not affect the clocks in any way; that is, the clock of a' is that of b and if ck(a) = ck(b) then ck(a) = ck(b) = ck(a').

### 5 Partitioning and Deployment

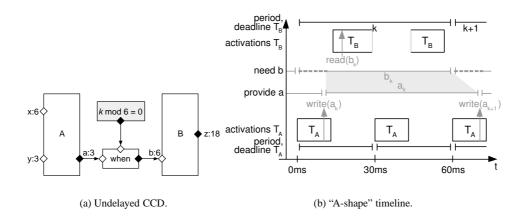

One inherent property of SSDs in AUTOFOCUS is the underlying assumption that communication between components is always delayed (i. e. each connecting channel contains exactly one implicit delay operator) in order to allow for predetermined breaking points within a system's component model. From a methodological point of view, this definition facilitates the individual and also more independent development of each specified component. In the graphical notation, delayed communication is also expressed with rounded ports (see Fig. 5).

Figure 5: Example SSD.

In practice, the nowaday's development processes of distributed automotive software almost totally disregard deployment issues at higher-level system views. However, as we will show in the following, a dedicated communication layer and the introduction of explicit delays in rather early stages of development in our time-synchronous system model

are formidable prerequisites helping to minimise the effort of deploying a distributed application across a network of ECUs.

#### 5.1 Communication Layer

Instead of concerning each ECU-network node directly with low-level implementation details to manage I/O, we define an abstract communication layer that "wraps" all read and write accesses, respectively (see § 2). This layer is a middleware between the operating system's scheduler and the application's tasks running on it. In particular, it provides a write handler (similar to SendMessage() service in OSEK COM [9]), and a read handler for messages (similar to ReceiveMessage() in OSEK COM).

Effectively, the layer constitutes a transparent communication model for each node and the tasks running on it, i. e. its technical realisation ensures that sufficient heap space is allocated when messages need buffering as is the case, for instance, when tasks with different clock speeds exchange signal frames. The following prerequisites are essential for the communication layer to yield the desired behaviour in practice:

- Execution of an accurate static analysis for minimal message allocation,

- and predetermination of an appropriate task scheduling algorithm.

Our AUTOFOCUS-based prototypes already provide for the former by allowing the static analysis and by associating temporaries to delays in the model. The *exact* required amount of temporary space in total is then determined by a subsequent "clock comparison" of the communicating tasks (see § 5.2).

What is more, for the remainder, we assume rate-monotonic scheduling, i. e. that the operating system provides a fixed-priority preemptive scheduler, where task priorities are statically assigned; this corresponds to the OSEK standard [8] for automotive operating systems. Rate monotonicity simply asserts that tasks with smaller periods are assigned higher priorities than tasks with greater periods [6].

#### 5.2 Variables and Message Slots

The operational system abstraction/view, as is also briefly sketched in § 3, contains the transition from the hierarchic and connected SSD components to a *clustered* system view yielding all delay and sampling operators; that is, relevant implementation details.

The CCDs then present a *flat* description of the time-synchronous system model which allows for the static analysis of the heap consumption in terms of message buffers as well as for (almost) arbitrary partitioning variants. Unlike SSDs which are grouped according to conceptual coherency and as reusable units, CCDs are typically partitioned to yield a maximum of technical efficiency in the implementation.

There are cases where it is required to partition CCD clusters along the same boundaries as SSD components. For instance, if components A and B are known to be always mapped to different processors, then the clusters A and B should be fully disjoint, i. e. there exists no cluster containing parts of both A's and B's functionalities.

Note that the semantics of SSD composition, i.e. every channel incorporates a delay, ensures that the following delay constraints for CCDs are met given rate-monotonic scheduling and when communication follows the boundaries of the SSD components. Let A and B be a sending and a receiving cluster, respectively:

- ck(A) = ck(B), i. e. equally fast clocks. In this case, the priority of A's and B's tasks are the same, so communication is delayed; in effect, the middleware needs to provide two message copies to avoid data inconsistencies.

- ck(A) < ck(B). When the clock of A is faster than the clock of B, i.e. the period is smaller, we may use undelayed communication; only one message copy is needed.

ck(A) > ck(B). Communication is delayed, when the clock of A is slower than the clock of B; in this case, two message copies are needed.

Obviously, the above comparison of task periods and static memory analysis is only possible by extending the clock associations from individual ports, or channels to the entire clusters themselves. Therefore, for periodic designs, a *cluster clock* is inferred as the "greatest common divisor" (gcd) of its individual clock periods. Note that internal clocks cannot — by definition of blocks and DFDs — be faster than the fastest external clock, so considering the external clocks in order to determine a cluster clock is fully sufficient. The following examples elaborate on that.

Figure 6: Fast cluster writes to slower cluster.

**Example (fast cluster**  $\rightarrow$  **slow cluster).** Fig. 6(a) shows an example of a CCD with two clusters A and B. For the sake of simplicity, we regard periodic clocks only, and write the clock periods next to the corresponding ports. The label x: 6 then denotes that port x holds a value every 6th tick, i. e. ck(A) = gcd(6,3,3) = 3. A writes signal a, which is sampled by a when-operator and read as signal b by cluster b. Communication between b and b is not delayed.

Let's assume that A corresponds to a task  $T_A$  with period 30ms and deadline 30ms, and that B corresponds to a task  $T_B$  with period 60ms and deadline 60ms.  $T_A$  and  $T_B$  are released periodically at the beginning of their respective cycles. Periods and deadlines of  $T_A$  and  $T_B$  are indicated by the black bars in Fig. 6(b).

Both tasks run on the same processor, and are scheduled according to the rate monotonic policy, so  $T_A$  has higher priority than  $T_B$ . For instance,  $T_B$  is preempted by  $T_A$  at  $t=30 \mathrm{ms}$ . To avoid data inconsistencies, for any step k,  $T_B$  needs a stable value  $b_k$  of its port b during the whole duration of its period. In the timeline, this is indicated by a grey "need b" bar.

A new value for port a is provided periodically by  $T_A$ , indicated by the "provide a" bar. Note for some step k of B, the "provide  $a_k$ " bar is always later than the "need  $b_k$ " bar.

Because of  $T_A$ 's higher priority,  $b_k$  will never actually be read before  $T_A$  has finished its computation, and  $a_k$  has been written. We indicate this by a dashed bar for "need b" during  $T_A$ 's activation. Therefore, we can safely associate  $a_k$  with  $b_k$ , which corresponds to immediate communication in the model. Since the written variable and the read variable correspond to the same memory location, the middleware does not have to perform an explicit copy operation. The example, therefore, illustrates that communication from fast to slow clusters does not require the introduction of a delay in the model.

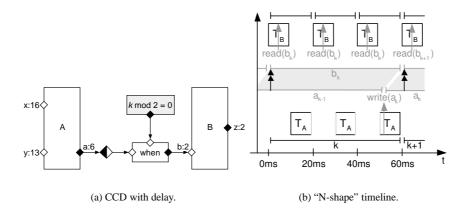

Figure 7: Slow cluster writes to faster cluster.

**Example (slow cluster**  $\rightarrow$  **fast cluster).** Fig. 7(a) depicts a CCD with clusters A and B. The cluster clock of A is 6, B's is 2. Now the slower cluster A writes to the faster cluster, and the clocks are related ck(A) > ck(B). According to the rules on page 6, a delay is imposed, indicated by the delay operator between a and b.

Fig. 7(b) shows how the delay relates to the timeline of two associated tasks  $T_A$  (period/deadline 60ms) and  $T_B$  (period/deadline 20ms). Because of ck(A)>ck(B), the "need b" period can be safely extended to  $T_A$ 's period of 60ms.

If all tasks meet their respective deadlines, for any step k,  $T_B$  will never read  $b_k$  before  $a_{k-1}$  has been written. We can, therefore, safely associate  $a_{k-1}$  with  $b_k$  for any k, corresponding to a delay in the model. The black double-headed arrows indicate copy operations performed by the middleware.

## 6 Conclusions & Summary

In this paper we have shown that deployment related issues in the development of distributed automotive controlling software, like insertion of explicit delays in a time-synchronous system model, must not necessarily be driven in a bottom-up manner, but can also be asserted high-level and from a top-down perspective. Given the underlying assumptions regarding schedulability and the various static analyses, the use of delay operators in early development stages that employ, say, SSDs bear several key advantages: firstly, the delays constitute predetermined breaking points in subsequent refinement and implementation processes, and secondly upon partitioning and clustering of the components, delays must not be added manually, i.e. the original communication structure remains mostly unchanged. The latter is particularly important, because essentially it means that a formerly verified behavioural model of the system, remains stable in the implementation; all the implementation's delays have been present in the structural view as well. This lowers the validation and verification efforts drastically and increases the reusability of components.

Although, as we have sketched in  $\S$  5.2, delays are not always essential to support, say, the writing of a fast cluster to a slower cluster. However, early assertion of a delay does not alter the communication's behaviour if inserted *after* the down sampling operator that lies in between the CCD clusters. What is more, in that case it is theoretically possible to assert an arbitrary amount of delay operators after the down sampling occurs; the result being a higher memory consumption due to excessive message buffering.

On the other hand, this example illustrates that top-down asserted delay operators do not necessarily guarantee for the most efficient implementation of a distributed application. In fact, this paper comprises a trade-off between these very aspects of optimisation and the

advantages of having separate, reusable and verifiable system components. In other words, using the presented concepts results in lower verification efforts, however, probably (but not necessarily) in a less efficient realisation of the application.

Furthermore, in § 3 we have introduced and sketched several graphical notations to support the presented development process of distributed embedded systems: a hierarchic SSD description to capture a system's overall structure, DFDs to express a component's computation and dataflow, and CCDs to explicitly visualise deployment details and to facilitate partitioning according to, say, "clock boundaries", or SSD component boundaries. (Compared to SSD-driven partitioning, a clock-driven strategy groups clusters according to common clock speeds which often results in faster implementations.)

Editors for the discussed notations, the key algorithms for analysis (e.g. clocks, memory allocation) and the various abstract system views are already available in terms of tool prototypes which we have based on and derived from the existing AUTOFOCUS framework.

#### References

- [1] The AUTOFOCUS Homepage. http://autofocus.informatik.tu-muenchen.de/.

- [2] A. Benveniste, P. Caspi, S. Edwards, N. Halbwachs, P. LeGuernic, and R. D. Simone. The Synchronous Languages Twelve Years Later. *Proceedings of the IEEE*, 91(1):64–83, 2003.

- [3] M. Broy and K. Stølen. Specification and Development of Interactive Systems: Focus on Streams, Interfaces, and Refinement. Springer, 2001.

- [4] ETAS Engineering Tools GmbH. ASCET-SD Benutzerhandbuch, 2001.

- [5] F. Huber, B. Schätz, A. Schmidt, and K. Spies. AutoFocus: A Tool for Distributed Systems Specification. In Formal Techniques in Real-Time and Fault-Tolerant Systems, pages 467–470, 1996

- [6] C. L. Liu and J. W. Layland. Scheduling algorithms for multiprogramming in a hard-real-time environment. *Journal of the ACM*, 20(1), 1973.

- [7] The MathWorks Inc. Using Simulink, 2000.

- [8] OSEK VDX consortium. OSEK/VDX Operating System Version 2.2, 2001.

- [9] OSEK VDX consortium. OSEK/VDX Communication Version 3.01, 2003.

- [10] B. Selic and J. Rumbaugh. Using UML for Modelling Complex Real-Time Systems. *Objec-Time Limited/Rational Software White Paper*, 1998.