#### Technische Universität München Lehrstuhl für Nanoelectronics

# Wired and Wireless Inter-Chip and Intra-Chip Communications

Hristomir Yordanov

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

- Doktor-Ingenieurs -

genehmigten Dissertation.

Vorsitzende: Univ.-Prof. Dr. rer. nat. Doris Schmitt-Landsiedel

Prüfer der Dissertation: 1. Univ.-Prof. Dr. techn. Peter Russer

2. Univ.-Prof. Dr. techn. Josef A. Nossek

Die Dissertation wurde am 11.10.2010 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 02.02.2011 angenommen.

#### **ACKNOWLEDGEMENTS**

I wish to thank Professor Peter Russer for offering me the opportunity to join his team and work on my thesis. Special thanks go to the rest of the project participants, Professors Josef A. Nossek and Tobias Noll and my colleagues Michel Ivrlač, Amine Mezghani and Matthias Korb. Warm thanks to Klaus, Susanne and Mark, my friends and colleagues who supported me during my years in München.

I could not have done this work without the support of my family, Boyan and Dessie.

Cheers.

## CONTENTS

| т | 11111                                                                                | roduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1        |  |  |

|---|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|

| 2 | Theoretical Methods for the Analysis of a Multi-Conductor<br>Transmission Line (MTL) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |

|   | 2.1                                                                                  | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>7</b> |  |  |

|   |                                                                                      | Multi-Conductor Transmission Line Equations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0        |  |  |

|   | 2.2                                                                                  | The General Solution of the Multi-Conductor Transmission Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1.4      |  |  |

|   | 0.0                                                                                  | Equations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14       |  |  |

|   | 2.3                                                                                  | Incorporating the terminal Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18       |  |  |

|   | 2.4                                                                                  | Computing the Impedance and Admittance Per Unit Length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |  |  |

|   |                                                                                      | Matrices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20       |  |  |

|   | 2.5                                                                                  | Computing the Ground and Coupling Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22       |  |  |

|   | 2.6                                                                                  | Conformal Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24       |  |  |

|   | 2.7                                                                                  | Schwarz-Christoffel Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 26       |  |  |

|   | 2.8                                                                                  | Characterising the Multi-Conductor Transmission Line as a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |  |  |

|   |                                                                                      | 2 <i>n</i> -Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30       |  |  |

| 3 | Mu                                                                                   | lti-Conductor Digital Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33       |  |  |

|   | 3.1                                                                                  | Computing the Even and Odd Mode Capacitances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 33       |  |  |

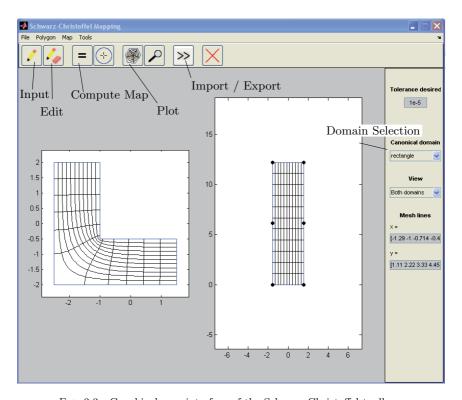

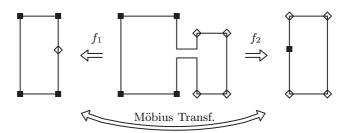

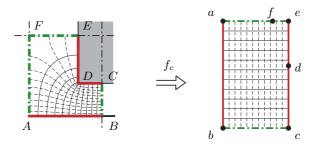

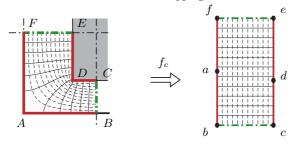

|   | 3.2                                                                                  | The Schwarz-Christoffel Toolbox                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35       |  |  |

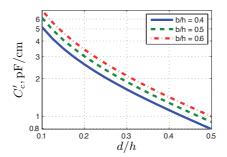

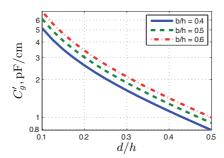

|   | 3.3                                                                                  | Results for the Ground and Coupling Capacitance per Unit Length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39       |  |  |

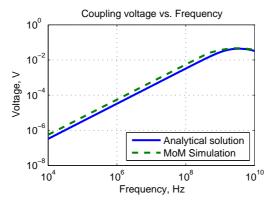

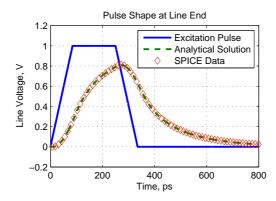

|   | 3.4                                                                                  | Frequency and Time Domain Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 42       |  |  |

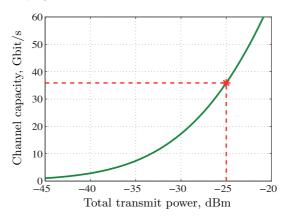

|   | 3.5                                                                                  | The Channel Capacity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 46       |  |  |

|   | 3.6                                                                                  | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50       |  |  |

| 4 | Inte                                                                                 | egrated Antenna Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51       |  |  |

|   | 4.1                                                                                  | State of the Art                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 52       |  |  |

|   | 4.2                                                                                  | Area Efficient Integrated Antenna Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54       |  |  |

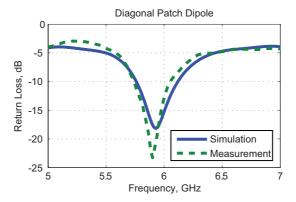

|   | 4.3                                                                                  | Low Frequency Prototypes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57       |  |  |

|   | 1.0                                                                                  | Don froquency from population and the first from th | 01       |  |  |

iv CONTENTS

|   | 4.4        | Estimation of the Channel Capacity                     | 62 |

|---|------------|--------------------------------------------------------|----|

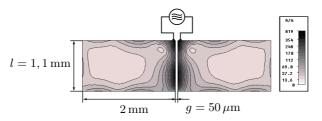

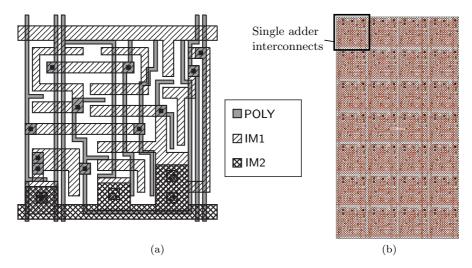

|   | 4.5        | Influence of the Interconnects Under the Patches       | 66 |

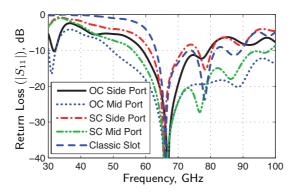

|   | 4.6        | High Frequency Open-Circuited Slot Antenna             | 67 |

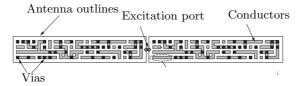

|   | 4.7        | Influence of the Cross-Patch Interconnects             | 69 |

|   | 4.8        | Antenna Feeding Design                                 | 71 |

|   | 4.9        | Short-Circuited Slot Antennas                          | 73 |

| 5 | Inte       | egrated Antenna Prototyping and Measurement            | 77 |

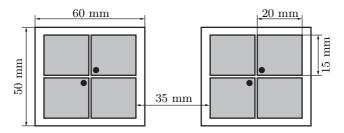

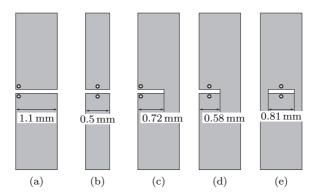

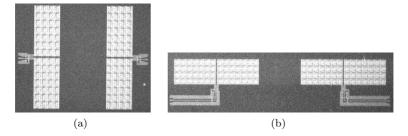

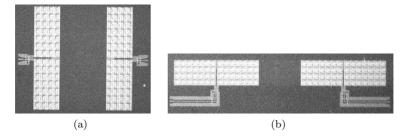

|   | 5.1        | Design of the Antenna Prototypes                       | 77 |

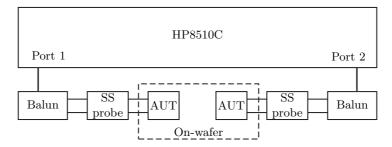

|   | 5.2        | The Measurement Equipment                              | 79 |

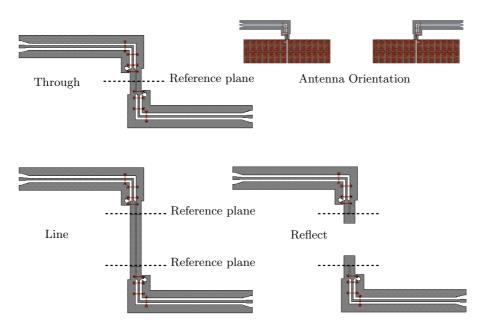

|   | 5.3        | Design of the Calibration Structures                   | 80 |

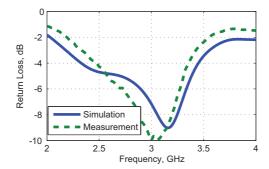

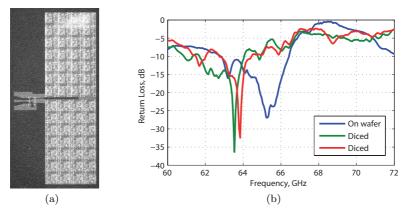

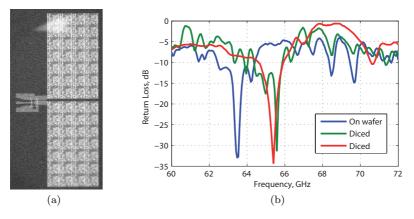

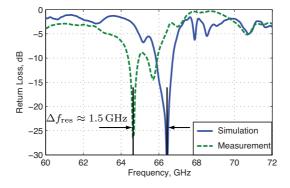

|   | 5.4        | Measurement Results for the Antenna Return Loss        | 85 |

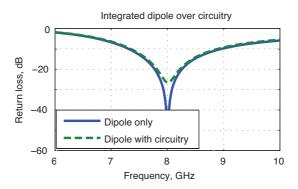

|   | 5.5        | Measurement of the Influence of the Interconnects      | 87 |

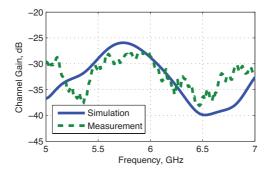

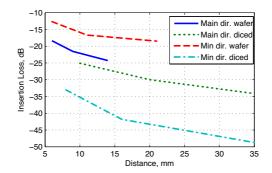

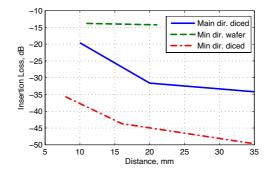

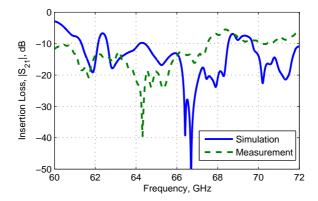

|   | 5.6        | Measurement of Channel Insertion Loss                  | 89 |

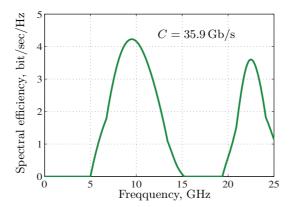

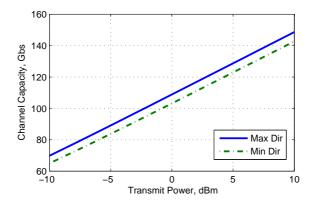

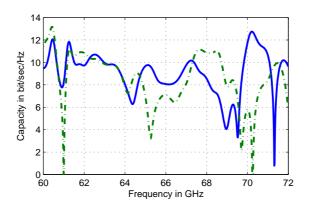

|   | 5.7        | Estimation of Channel Capacity                         | 91 |

| 6 | Con        | clusion                                                | 95 |

| A | Mat<br>Maj | Lab Code For Computation of the Schwarz-Christoffel os | 97 |

|   | -          |                                                        |    |

#### Chapter 1

#### INTRODUCTION

The dimensions of the active elements in the integrated circuits scale down constantly. At the time of writing, 45 nm and 32 nm CMOS technology is considered state-of-the-art and is commercially available for many applications. Even smaller gate lengths are being researched and developed [1]. The down-scaling of the transistors requires interconnects with smaller dimensions. This leads to on-chip interconnections wires with typical dimensions in the range of about 100 nm. As it will be shown, the resistivity of such wire is several hundreds of Ohm-centimetres. This leads to two major problems.

First is the RC delay problem. The delay associated with the bus does not change, while the transistor delay decreases. Therefore the bus delay has long surpassed the inversion delay [2]. In case the bus connects two blocks that are distant from each other on the chip, the RC problem is more significant, because the length of such bus does not scale down. On the contrary, it even tends to increase, because the die sizes also tend to increase [1]. In this case the bus delay scales up, while the transistor delay scales down. Or, in other words, if the on-chip dimensions scale down with a factor  $\lambda$ , the RC delay of the bus scales up with a factor  $\lambda^2$  relative to the transistor delay. The crosstalk between the wires of a multi-wire interconnection bus further limits the bus delay.

The second problem is the increased power dissipation from the integrated circuits. For example a  $45\,\mathrm{nm}$  technology based processor with a die size of  $263\,\mathrm{mm}^2$  dissipates thermally  $130\,\mathrm{W}$  [3], which represents a power density of  $49.4\,\mathrm{W/cm}^2$ . This is in the order of magnitude of the power density of a nuclear reactor [4].

A solution of the first problem, the limitation of the on-chip data rate,

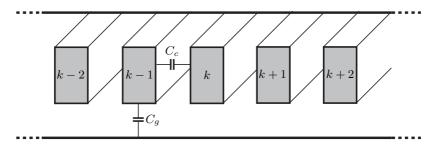

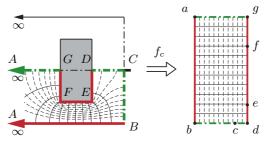

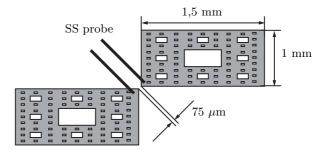

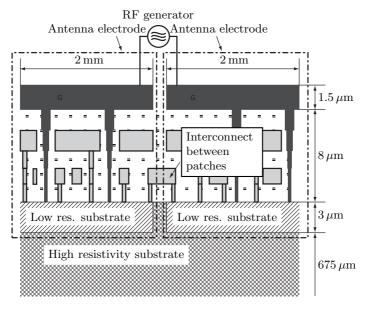

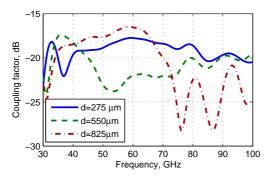

Fig. 1.1 Cross section view of the investigated multi-wire interconnection bus.

is to shield the wires from each other, thus eliminating the cross-talk. This solutions requires too much additional chip area, as for a interconnection bus of N wires N-1 shielding walls are needed. The shieldings have the same dimensions as the wires—the minimum allowed by the technology—therefore the total area required by the bus doubles. Furthermore the shielding only eliminates the cross-talk, whereas the distortion due to the high bus resistivity remains unchanged.

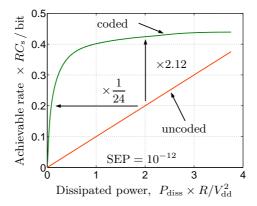

A more appropriate solution is the introduction of coding techniques [5]. As it will be shown, coding of the digital signal, transmitted my the bus, can significantly reduce the power consumption of the bus and increase the channel throughput. The price is that additional wires need to be introduced, and that an encoder and a decoder are needed. Still the total area required by the bus is smaller than in the case of shielded wires.

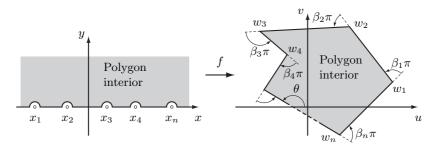

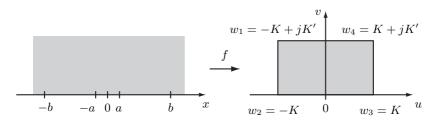

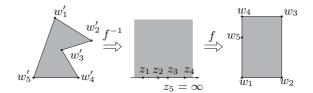

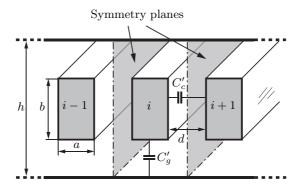

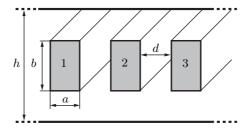

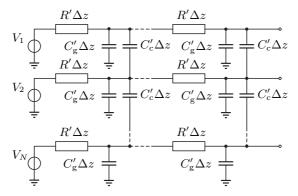

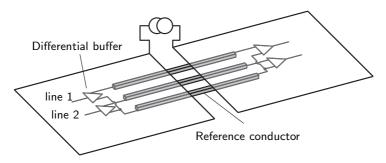

The design of the coding technique requires a good model of the wired interconnects. The first part of this work considers the development of such a model. The bus has a geometry as presented in Fig. 1.1. It consists of N wires with rectangular cross-section, numbered here  $1, \ldots, k-1, k, k+1, \ldots, N$ . The wires are placed between two ground planes, which can be considered infinitely extended. The bus is characterised with the capacitance between each wire and the ground planes, denoted as  $C_g$ , the mutual capacitance between any two neighbouring wires k and k-1, and the resistivity of each wire R. Due to the rectangular geometry of the wire the ground and the mutual capacitance can be computed using Schwarz-Christoffel transformation [6,7]. The resistance is computed assuming that the current in the wire is uniformly distributed across the cross section. Using the obtained static parameters the multi-conductor transmission line equations can be solved [8–12].

The chip-to-chip communication suffers a greater reduction of the data rate

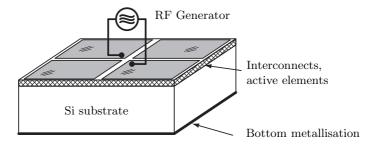

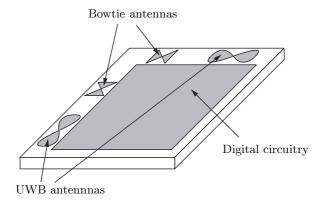

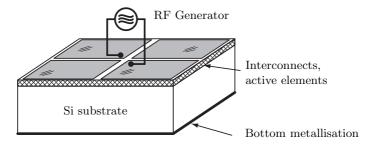

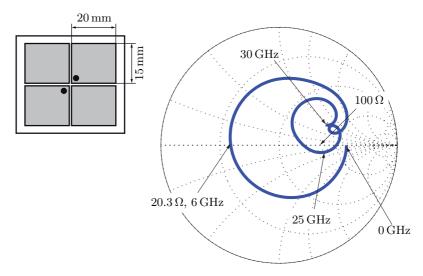

Fig. 1.2 Integrated antenna, using the ground supply metallisation. The antenna consists of four patches. The shown RF generator is also integrated on the chip. Inductive connections, not shown on the figure, provide the DC contact, required for ground supply.

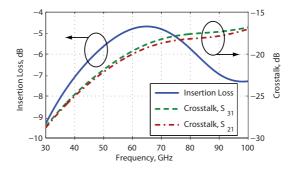

that the on-chip problem, because the off-chip interconnects generally do not scale down with the same rate as the on-chip components, because the printed circuit board limitations have long been reached. The data rate of the chip-to-chip interconnects is limited by the coupling between adjacent wires. The coupling is greater than in the case of on-chip interconnects mostly because of the greater length of the wires, which can easily reach a couple of centimetres. The communication bottleneck presented by the inter-chip interconnects can be widened using coding the very same way as with the on-chip interconnects. This technique is not efficient enough though—it will be shown that it can increase the data rate with a factor of about 2 only. In order to find more effective options we consider wireless chip-to-chip communication as one of the available options.

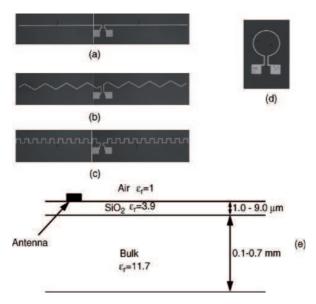

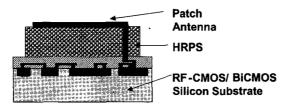

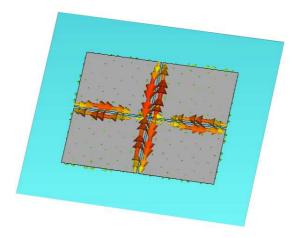

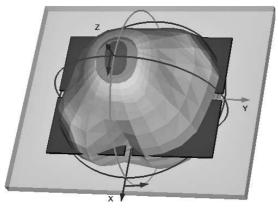

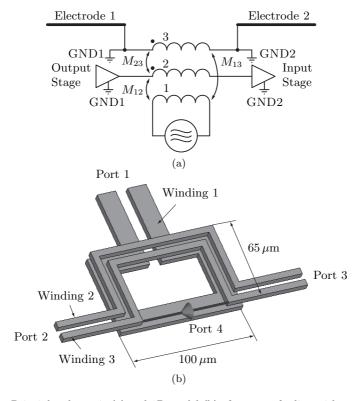

An efficient wireless inter-chip communication must provide high data rates with low bit error ratio and it must utilise minimum chip area. These requirements are easier to meet using higher carrier frequencies. The state of the art in CMOS technology allows for high-frequency generators, amplifiers and passive elements well into the millimetre wave range [13–19]. The unsolved problem is the integration of the antennas utilising minimum chip area. An interesting way to integrate the antennas is to share the chip area between the circuit and the antenna in a way that the antenna and the circuitry will not interfere each other. This can be obtained by cutting the circuit ground plane into patches and using the patches as antenna electrodes [20–24]. The ground plane must be implemented in the top metallisation layer of the integrated circuit, as shown in Fig. 1.2. In the figure the antenna consist of four patches. There are inductive connections across the gaps, providing DC contact between the patches, not shown in the figure.

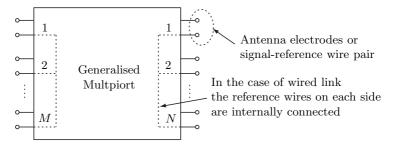

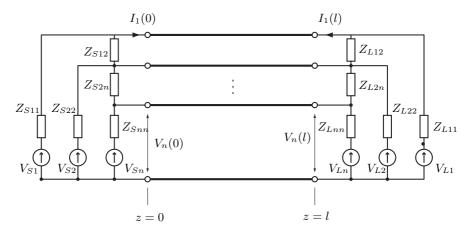

Fig. 1.3 A generalised multiport representing wired or wireless intra- or inter-chip communication link. The ports represent either the electrodes of a single antenna or a signal-reference wire pair. If the multiport represents wired link, the reference wires on each side are connected. In this case M=N

A multi-conductor transmission line with N conductors exhibits N-1 transmission line modes and one antenna mode. These modes are orthogonal, therefore the antenna will not interfere with the circuitry underneath its electrodes.

In order to maximise the antenna efficiency the substrate needs to have high resistivity—more than  $2\,\mathrm{k}\Omega\mathrm{cm}$ . It has been shown [25] that above this resistivity the predominant loss mechanism is the skin effect for frequencies above  $40\,\mathrm{GHz}$ .

The described approach to monolithic integration of antennas does not allow for very much freedom in the antenna design because of the additional requirement of the antenna electrode to serve as a ground plane for the integrated circuit. It will be shown later on that despite the limitations the proposed antenna is suitable for chip-to-chip and on-chip communication.

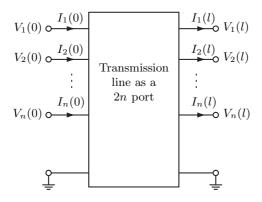

The goal of the investigation both of the wired and wireless inter- and intrachip communication links it to provide multiport models, which can be used for computation of the capacity of the respective channels. A wired link of N+1 wires can be fully described as a 2N port. Each wire end is represented as a port, except for the voltage reference wire. Similarly a multi input multi output (MIMO) wireless link with M antennas on one side and N antennas on the other can be represented as M+N port, where the electrodes of each antenna are represented by a port. The generalised multiport is presented in Fig. 1.3.

The work is divided in four chapters. Chapter 2 presents the theoretical tools for analysis of a multi-conductor transmission line (MTL). A solution of the MTL matrix equations via eigenmode decomposition is presented. Here is

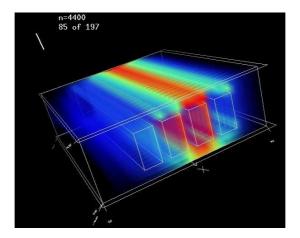

also presented the basis of the conformal mapping technique, used for extraction of the MTL equation parameters from the problem geometry. Chapter 3 describes the application of the theoretical tools to the specific problem of an on-chip digital bus. The results are verified using full-wave simulation and SPICE modelling of the bus equivalent circuit. Chapter 4 describes the design considerations for monolithically integrated antennas. Several antenna modifications are proposed. Different antenna feeding techniques are studied. The interference between the antenna and the circuitry is investigated. Chapter 5 describes the design and measurement of integrated antenna prototypes. Chapter 6 contains the concluding remarks.

The field computations in this work are performed using exterior differential forms instead of the standard vector notation. The differential forms use unit differentials dx, dy, and dz instead of unit vectors. The exterior product of two unit differentials is denoted with the sign  $\wedge$ :  $dx \wedge dy$  The computation is based on the anti-commutative property of the unit differentials

$$dx \wedge dy = -dy \wedge dx$$

.

The vector operators rotor, divergence and gradient are equivalent to a single differential forms operator, the exterior derivative, defined as

$$d\mathcal{U} = dx \wedge \frac{\partial \mathcal{U}}{\partial x} + dy \wedge \frac{\partial \mathcal{U}}{\partial y} + dz \wedge \frac{\partial \mathcal{U}}{\partial z},$$

where  $\mathcal{U}$  is the differential form.

The exterior differential forms offer certain simplification in comparison with the vector notation. They also provide a better intuitive description of the fields, because they inherently discriminate the flow-describing vectors (called axial- or pseudo-vectors) from the vectors describing fields (called true-or  $polar\ vectors$ ). For additional information on exterior differential forms please refer to [6,26-30].

#### Chapter 2

### THEORETICAL METHODS FOR THE ANALYSIS OF A MULTI-CONDUCTOR TRANSMISSION LINE (MTL)

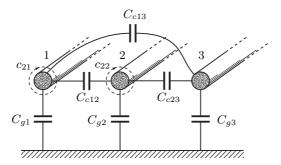

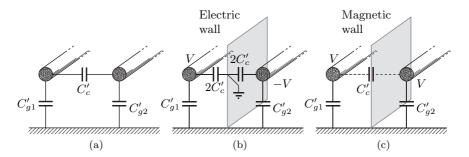

This chapter discusses the theoretical tools needed for computation of the transmission line characteristics of a multi-conductor digital bus. The geometry of a digital bus with typical dimensions is presented in Fig. 2.1. Due to the small dimensions of the bus relative to the wavelength the propagation mode is quasi-TEM. The static parameters defining the propagation mode in this case are the ground  $(C_q)$  and the coupling  $(C_c)$  capacitance, the self and the mutual inductance of the wires, the resistivity of the wires and the conductivity of the dielectric, in which the bus is embedded. Due to the symmetry of the problem we can introduce electric or magnetic walls at the symmetry planes, thus defining the even and the odd mode ground capacitance of each wire,  $C_e$ and  $C_o$  respectively. Since the wires have polygonal shape we can compute the values of these capacitances by means of Schwarz-Christoffel mapping. The ground and mutual capacitance values are arranged into a capacitance matrix. The product of the capacitance matrix and the inductance matrix, which holds the value for the self and mutual inductance of the wires, equals the inverse of the square of the phase velocity of the propagating wave. This relation allows the straightforward computation of the inductance matrix. The resistance matrix, describing the ohmic losses in the wires, is computed under the assumption for uniform current distribution in the wire cross section. Since the on-chip digital buses are normally embedded in silicon dioxide, which is a dielectric with very low losses, the conductivity of the medium is approximated as equal zero.

Fig. 2.1 A cross section of three-wire digital interconnect embedded between ground plates with a coupling and a ground capacitance. Typical bus dimensions are given.

The resistivity, capacitance, inductance and conductance matrices are put together in the matrix telegrapher's equations, which describe the propagation of the voltages and currents along a multi-conductor transmission line (MTL) in frequency domain. These equations are solved using eigenmode decomposition, since the eigenmodes are orthogonal and the matrices describing them are diagonal. The boundary conditions for the MTL equations are defined by the load impedance on both ends of the transmission line and by the input signal.

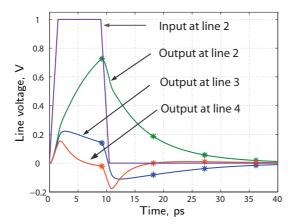

The solution of the MTL equations is the voltage and current distribution along the line in frequency domain. By performing an inverse Fourier transformation of the voltage at the end of the line we obtain the response of the digital bus to a specific excitation signal. The obtained data is used to compute the maximum available data rate on the bus.

#### 2.1 Multi-Conductor Transmission Line Equations

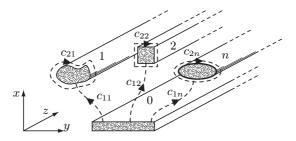

The multi-conductor transmission line (MTL) in general consists of more than two conductors of arbitrary cross section, as shown in Fig. 2.2 [6]. The potential of one of the conductors is considered as a voltage reference for the others. This conductor is the reference conductor and is denoted with the number 0. The rest of the conductors are numbered  $1, 2, \ldots n$ . The total number of conductors, including the reference, is n+1. The sum of the currents on all conductors is zero for a transmission line mode. Therefore only n currents can be chosen independently. Without loss of generality we select the independent

Fig. 2.2 Cross section view of a general multi-conductor transmission line. The paths of the integrals  $c_{2i}$  are at an infinitesimal distance from the conductor surface.

currents to be the carried by the conductors  $1, 2, \dots n$ . Therefore the voltages and currents on the MTL are fully described by the following vectors

$$\mathbf{v}(z,t) = [v_1(z,t), v_2(z,t), \dots v_n(z,t)]^T, \tag{2.1}$$

$$\mathbf{i}(z,t) = [i_1(z,t), i_2(z,t), \dots i_n(z,t)]^T, \tag{2.2}$$

where  $v_k(z,t)$  is the voltage difference between the k-th conductor and the reference conductor and  $i_k(z,t)$  is the current on the k-th conductor.

Let all but the k-th conductor be set to zero potential. The electric field in this case is expressed by the electric field form  $\mathcal{E}_k(\mathbf{x},t)$ . If we let the current on all conductors but the k-th and the reference conductor be zero, the magnetic field is described by the magnetic field form  $\mathcal{H}_k(\mathbf{x},t)$ . In the case of TEM fields these forms can be separated in transverse and longitudinal component as follows

$$\mathcal{E}_k(\mathbf{x},t) = v_k(z,t)\mathbf{e}(x,y), \tag{2.3}$$

$$\mathcal{H}_k(\mathbf{x},t) = i_k(z,t)\mathsf{h}(x,y),\tag{2.4}$$

where e(x, y) and h(x, y) are called correspondingly electric and magnetic structure forms. They describe the transverse distribution of the electric and magnetic field, normalised to the voltage or correspondingly the current at a given point along the line z and at a given time t. Since for  $\mathcal{H}_k(\mathbf{x}, t)$  there is no current flowing in any conductors except for the k-th and the reference, the magnetic field has no component, tangential to the conductor for any but the k-th conductor. Therefore the closed integral on a path, infinitesimally close the conductor (paths  $c_{2l}$  on Fig. 2.2), gives a non-zero result only for the k-th conductor:

$$\oint_{Col} \mathsf{h}_k(x,y) = \delta_{kl}.$$

(2.5)

Similarly since only the k-th conductor is at a non-zero potential, the path integral between the reference and the other conductors (paths  $c_{1l}$  on Fig. 2.2) gives non-zero results only for the k-th conductor:

$$\int_{c_{1l}} \mathbf{e}_k(x, y) = -\delta_{kl}. \tag{2.6}$$

The total electric and magnetic field for the MTL is given as a superposition of the partial electric and magnetic fields,

$$\mathcal{E}(\mathbf{x},t) = \sum_{k=1}^{n} \mathcal{E}_k(\mathbf{x},t), \qquad \mathcal{H}(\mathbf{x},t) = \sum_{k=1}^{n} \mathcal{H}_k(\mathbf{x},t)$$

(2.7)

The structure form  $\mathbf{e}(x,y)$  represents the normalised transverse electric field distribution of a TEM mode. Therefore it satisfies the two-dimensional Laplace equation

$$\frac{\partial^2 \mathbf{e}(x,y)}{\partial x^2} + \frac{\partial^2 \mathbf{e}(x,y)}{\partial y^2} = 0 \tag{2.8}$$

In differential forms notation the Ampère and Faraday equations have the following local form

$$d\mathcal{H} = \frac{\partial}{\partial t} \mathcal{D} + \mathcal{J}, \tag{2.9}$$

$$d\mathcal{E} = -\frac{\partial}{\partial t}\mathcal{B}.\tag{2.10}$$

For the source-free electrostatic case they reduce to

$$d\mathcal{H} = 0, \qquad d\mathcal{E} = 0. \tag{2.11}$$

Since the structure forms e(x, y) and h(x, y) represent the normalised transverse electric and magnetic fields, they also fulfil the above equations and we can write

$$dh(x, y) = 0,$$

$de(x, y) = 0.$  (2.12)

The electrostatic approximation is valid only for the *transverse* field distribution in a transmission line. In order to describe the wave propagation we must consider the variation of the field in time and along the propagation axis. Therefore the exterior derivative of the partial electric and magnetic fields (2.3) and (2.4) are

$$d\mathcal{E}_k = \frac{\partial v_k(z,t)}{\partial z} dz \wedge e_k(x,y), \qquad (2.13)$$

$$d\mathcal{H}_k = \frac{\partial i_k(z,t)}{\partial z} dz \wedge \mathsf{h}_k(x,y). \tag{2.14}$$

Inserting the constitutive relation

$$\mathcal{D} = \varepsilon \star \mathcal{E} \tag{2.15}$$

and the obtained equations for the partial field components (2.3), the representation of the total filed as sum of the partial fields (2.7), and the exterior derivative of the magnetic field (2.14) into Ampère's law (2.9) we obtain

$$\sum_{k=1}^{n} \frac{\partial i_k(z,t)}{\partial z} \, \mathrm{d}z \wedge \mathsf{h}_k(x,y) = \varepsilon \sum_{k=1}^{n} \frac{\partial v_k(z,t)}{\partial t} \star \mathsf{e}_k(x,y). \tag{2.16}$$

We can simplify this expression using the *contraction*, or *angle product*  $\lrcorner$  defined for two unit differentials  $ds_i$  and  $ds_j$  as

$$ds_i \, ds_j = \delta_{ij}. \tag{2.17}$$

The distributive rule for the contraction operator is given by

$$\mathcal{A} \sqcup (\mathcal{B} \wedge \mathcal{C}) = (\mathcal{A} \sqcup \mathcal{B}) \wedge \mathcal{C} + (-1)^{\deg(\mathcal{A})} \mathcal{B} \wedge (\mathcal{A} \sqcup \mathcal{C}). \tag{2.18}$$

We contract both sides of equation (2.16) with  $dz_{\perp}$  and apply the distributive rule to the left side of he equation to obtain the following form

$$\sum_{k=1}^{n} \frac{\partial i_k(z,t)}{\partial z} \mathsf{h}_k(x,y) = \varepsilon \sum_{k=1}^{n} \frac{\partial v_k(z,t)}{\partial t} \, \mathrm{d}z \, \bot \star \mathsf{e}_k(x,y). \tag{2.19}$$

We can simplify further this equation by integrating both sides over any of the closed contours  $c_{2l}$ , encompassing the MTL conductors (see Fig. 2.2). We obtain

$$\sum_{k=1}^{n} \frac{\partial i_k(z,t)}{\partial z} \oint_{c_{2l}} \mathsf{h}_k(x,y) = \varepsilon \sum_{k=1}^{n} \frac{\partial v_k(z,t)}{\partial t} \oint_{c_{2l}} \mathrm{d}z \, \mathsf{d} \, \mathsf{d}$$

We make use of (2.6) to obtain

The integral expression on the right side of the equation requires a detailed investigation. It can be expanded to

$$\varepsilon \oint_{c_{2l}} dz \, dx \, dx \, dx = \varepsilon \oint_{c_{2l}} [e_{kx}(x,y) \, dy - e_{ky}(x,y) \, dx]. \tag{2.22}$$

The structure form  $\mathbf{e}(x,y)$  describes electric field normalised to a certain voltage. Since the metric of the electric field differential form is Volts, the structure form is dimensionless. The metric of the dielectric constant is F/m, therefore the metric of the above expression is also F/m. According to the constitutive relation (2.22) the product of the dielectric constant  $\varepsilon$  with the electric field  $\mathcal{E}$  gives the electric flux density  $\mathcal{D}$ . Therefore the product of the dielectric constant with the normalised electric field gives normalised electric flux density

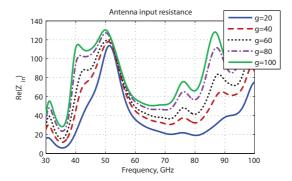

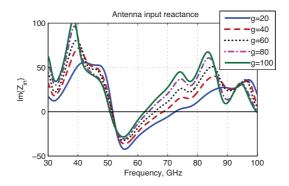

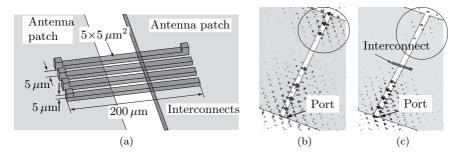

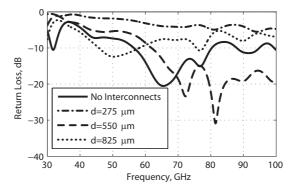

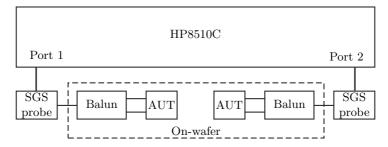

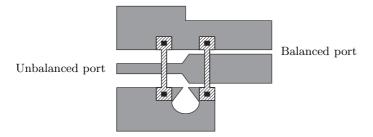

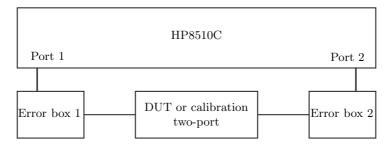

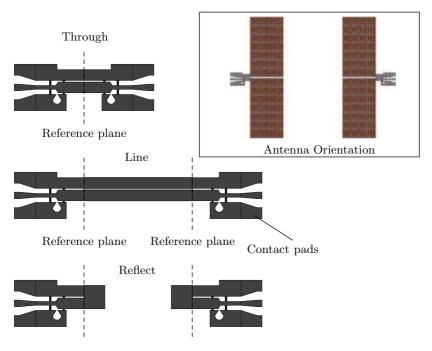

$$\varepsilon \, \mathrm{d}z \, \perp \, \star \, \mathsf{e}(x,y) = \frac{\mathcal{D}(\mathbf{x},t)}{v(z,t)}. \tag{2.23}$$