Fakultät für Elektrotechnik und Informationstechnik Lehrstuhl für Entwurfsautomatisierung Univ. Prof. Dr. -Ing. Ulf Schlichtmann

## **PhD-Thesis**

## Automated Assertion Transformation Across Multiple Abstraction Levels

**Thomas Steininger**

Lehrstuhl für Entwurfsautomatisierung der Technischen Universität München

#### Automated Assertion Transformation Across Multiple Abstraction Levels

#### **Thomas Steininger**

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs**

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr. sc.techn. Andreas Herkersdorf

Prüfer der Dissertation:

- 1. Hon.-Prof. Dr.-Ing. Wolfgang Ecker

- 2. Univ.-Prof. Dr.-Ing. Ulf Schlichtmann

Die Dissertation wurde am 29.10.2008 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 30.09.2009 angenommen.

#### PhD-Thesis

Institute of Electronic Design Automation Univ. Prof. Dr. -Ing. Ulf Schlichtmann Department of Electrical and Information Technology, Technische Universität München

in Cooperation with

Infineon Technologies AG Munich IFAG COM BTS MT SD Dr. -Ing. Matthias Bauer Prof. Dr. -Ing. Wolfgang Ecker

Author: Thomas Steininger

## Zusammenfassung

Im Rahmen dieser Arbeit wurde eine Methodik zur automatisierten Transformation von Assertions, eine erweiterte Auswertungssemantik und eine dazugehörige Transformationssprache entwickelt. Unter Benutzung dieser Methodik ist es möglich, bestehende Assertions auf andere Abstraktionsebenen zu transformieren. Dies erlaubt die Wiederverwertung bestehender Assertions, die für abstrakte Modelle geschrieben wurden, für die Entwicklung von weniger abstrakten Modellen, wobei die Gefahr, manuell Fehler während der Transformation einzuführen, minimiert wird.

## Abstract

In this work, a methodology for automated assertion transformation, an extended assertion evaluation semantics, and a corresponding transformation language has been developed. Using this methodology it is possible to transform existing assertions to other levels of abstraction. This allows reusing existing assertions, which were written for abstract models, for the development of less abstract ones while minimizing the danger of manually introducing errors during the transformation process.

## Acknowledgment

This thesis was conducted in cooperation with Infineon Technologies AG, namely the department IFAG COM BTS MT SD headed by Dr. Matthias Bauer, and with Technische Universität München at the department Electrical Engineering and Information Technology at the institute for Electronic Design Automation, led by Professor Ulf Schlichtmann. I would like to thank Professor Schlichtmann for giving me the opportunity to carry out this thesis at his institute and also for taking over the role of co-advisor for this work. I also want to thank Dr. Bauer for making this thesis possible, as well as for his support and encouragement.

I owe special thanks to my advisor Professor Wolfgang Ecker. He was always willing to take time for discussions about all kinds of problems and new ideas. His continuous support and encouragement were a great motivation for this work. I also want to thank all my other colleagues at Infineon for a good collaboration.

I want to express my gratitude towards Professor Manfred Glesner and Dr. Thomas Hollstein from Technische Universität Darmstadt for their help.

I especially want to thank my girlfriend Yu Hu for her patience. She always supported and encouraged me. I would also like to thank my family who never failed to encourage me during this work and always helped to keep me calm.

Finally, I want to thank my colleague and friend Michael Velten who contributed a lot to this work and who spent a lot of time with discussing problems with me.

Thomas Steininger Munich, November 27, 2009

# Contents

| 1 | Intr | oduction                                           | 1    |

|---|------|----------------------------------------------------|------|

|   | 1.1  | The Pervasiveness of Embedded Systems              | . 1  |

|   | 1.2  | Quality of Embedded Systems                        | . 1  |

|   | 1.3  | Model Equivalence                                  |      |

|   |      | 1.3.1 Connection Verfication                       |      |

|   |      | 1.3.2 Formal Verification                          | . 3  |

|   |      | 1.3.3 Simulation-Based Verification                | 5    |

|   | 1.4  | Motivation                                         |      |

|   | 1.5  | Outline                                            | 9    |

| 2 | Pro  | lem Statement and Targeted Approach                | 11   |

|   | 2.1  | Today's Top-Down Design                            | . 11 |

|   |      | 2.1.1 Abstraction Levels                           | . 11 |

|   |      | 2.1.2 Refinement                                   | 13   |

|   | 2.2  | Assertion Based Verification                       | 15   |

|   | 2.3  | Assertion Refinement                               | 15   |

|   |      | 2.3.1 Example                                      | 16   |

|   | 2.4  | Targeted Approach                                  | . 17 |

| 3 | Req  | uirements and Objectives for Assertions Refinement | 19   |

|   | 3.1  | Requirements for the Assertion Language            | . 19 |

|   |      | 3.1.1 General Requirements                         | . 19 |

|   |      | 3.1.2 Abstraction Levels                           | 20   |

|   |      | 3.1.3 Pipelining                                   | 23   |

|   |      | 3.1.4 SystemC                                      | . 24 |

|   | 3.2  | Requirements for the Transformation Language       | 26   |

|   |      | 3.2.1 Abstraction Levels                           | 26   |

|   |      | 3.2.2 Behavioral Consistency                       | 26   |

|   |      | 3.2.3 Conversion of transactions and events        | . 27 |

|   |      | 3.2.4 Timing                                       | . 27 |

|   |      | 3.2.5 Reset                                        | . 27 |

|   |      | 3.2.6 Ambiguity                                    | . 28 |

|   |      | 3.2.7 Reuse                                        | . 28 |

| 4 | Stat | te of th         | ne Art and Related Work 3                                                         |

|---|------|------------------|-----------------------------------------------------------------------------------|

|   | 4.1  | Assert           | tions in a Top-Down Design 3                                                      |

|   |      | 4.1.1            | SVA and PSL                                                                       |

|   |      | 4.1.2            | Research work                                                                     |

|   |      | 4.1.3            | UAL                                                                               |

|   | 4.2  | Trans            | actor based Refinement                                                            |

|   |      | 4.2.1            | Flexible Transactor Specification                                                 |

|   |      | 4.2.2            | Multi-Level Testbenches and Transactors                                           |

|   |      | 4.2.3            | Automated Transactor Generation                                                   |

|   |      | 4.2.4            | Transaction Level Assertions and Transactors                                      |

|   | 4.3  | Gener            | al Refinement Approaches                                                          |

|   |      | 4.3.1            | Model Driven Architecture                                                         |

|   |      | 4.3.2            | Design Refinement                                                                 |

|   |      | 4.3.3            | Refinement Description Languages                                                  |

|   |      | 4.3.4            | Aspect Oriented Programming                                                       |

| _ | •    |                  |                                                                                   |

| 5 |      |                  | Refinement 4                                                                      |

|   | 5.1  | Conce            | 1                                                                                 |

|   |      | 5.1.1            | Basic Definitions                                                                 |

|   | F O  | 5.1.2            | Problem Classes for Assertion Refinement                                          |

|   | 5.2  | -                | mentation of Assertion Refinement                                                 |

|   |      | $5.2.1 \\ 5.2.2$ | Reasons for choosing UAL4UAL Overview5                                            |

|   |      | 5.2.2<br>5.2.3   | UAL Overview5Transformation Problem Classes and UAL5                              |

|   |      | 5.2.5<br>5.2.4   |                                                                                   |

|   |      | 5.2.4<br>5.2.5   | 1                                                                                 |

|   |      | 5.2.5<br>5.2.6   |                                                                                   |

|   |      | 5.2.0<br>5.2.7   | 8                                                                                 |

|   |      | 5.2.7<br>5.2.8   | 8                                                                                 |

|   |      | 5.2.8<br>5.2.9   | Constrained RTL transactions6Enhancement of time related Operators and Functions6 |

|   |      | 5.2.9<br>5.2.10  | ±                                                                                 |

|   | 5.3  |                  | 0                                                                                 |

|   | 0.0  | 5.3.1            | tion Transformation Language6General Overview6                                    |

|   |      | 5.3.1            | Modeling Layer   6                                                                |

|   |      | 5.3.2            | 0                                                                                 |

|   |      | 5.3.4            | Rule Layer    7      Transactor Layer    7                                        |

|   |      | 5.3.4            | Directive Layer                                                                   |

|   |      | 5.3.6            | Location Parameters                                                               |

|   | 5.4  |                  | raints and Guidelines for Refinement                                              |

|   | 0.4  | 5.4.1            |                                                                                   |

|   |      | 5.4.1<br>5.4.2   | 0                                                                                 |

|   |      | 5.4.2<br>5.4.3   | Detectability Issues8Restrictions on Reuse8                                       |

|   |      | 0.4.0            |                                                                                   |

|   |                   | 5.4.4            | Performance Issues                                | 87                                        |

|---|-------------------|------------------|---------------------------------------------------|-------------------------------------------|

|   |                   | 5.4.5            | Further Issues                                    | 87                                        |

|   |                   | 5.4.6            | Summary                                           | 87                                        |

| 6 | Forr              | nal Ser          | nantics                                           | 89                                        |

| - | 6.1               |                  | Semantics                                         | 89                                        |

|   | 0.1               | 6.1.1            | Classical Trace                                   | 89                                        |

|   |                   | 6.1.2            | UAL Trace Definition                              | 91                                        |

|   |                   | 6.1.3            | Benefits and Problems of LTL for Trace Evaluation | 94                                        |

|   | 6.2               | 0.2.0            | Net Semantics                                     | 95                                        |

|   | 0.1               | 6.2.1            | Definitions of Global Functions                   | 95                                        |

|   |                   | 6.2.2            | Petri Net Definition                              | 96                                        |

|   |                   | 6.2.3            | Token Structure                                   | 96                                        |

|   |                   | 6.2.4            | Places                                            | 99                                        |

|   |                   | 6.2.5            | Transitions                                       | 101                                       |

|   |                   | 6.2.6            | Lists                                             | 105                                       |

|   |                   | 6.2.7            | Mapping Concept                                   | 107                                       |

|   |                   | 6.2.8            | Event Layer                                       | 108                                       |

|   |                   | 6.2.9            | Sequence Layer                                    | 115                                       |

|   |                   | 6.2.10           | Property Layer                                    | 120                                       |

|   |                   | 6.2.11           | Hybrid Component: Match Filter                    | 121                                       |

|   |                   | 6.2.12           | Mapping of Grammar Elements to Petri Nets         | 131                                       |

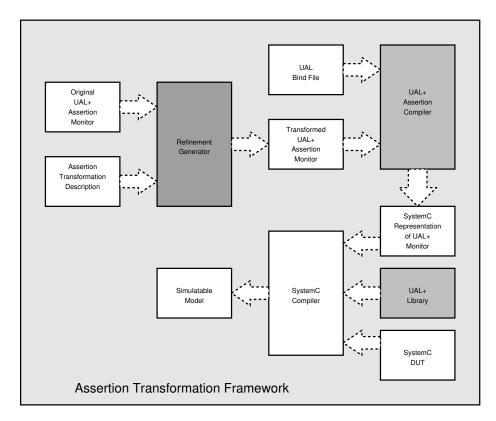

| 7 | Asse              | ertion 1         | Fransformation Framework                          | 135                                       |

| - | 7.1               |                  | ment Generator                                    | 136                                       |

|   | 7.2               |                  | Library                                           | 138                                       |

|   |                   | 7.2.1            | Event Handler                                     |                                           |

|   |                   | 7.2.2            | New Event Based Operators                         |                                           |

|   |                   | 7.2.3            | Token Handling                                    | 139                                       |

|   |                   | 7.2.4            | Further Enhancements                              | 139                                       |

|   | 7.3               | UAL (            | Compiler                                          | 140                                       |

| 8 | ٨٥٥               | lication         |                                                   | 143                                       |

| U | <b>Арр</b><br>8.1 |                  | •<br>formation Example                            | 143                                       |

|   | 0.1               | 8.1.1            | Design Structure                                  | 143                                       |

|   |                   | 8.1.2            | Transformation Categories                         | 145                                       |

|   |                   | 8.1.2            | Transformation between PVT, CA, and CC            | 147                                       |

|   |                   | 8.1.4            | Transformation between PV and other TL sublevels  | $140 \\ 152$                              |

|   |                   | 8.1.5            | Transformation between TV and other TL sublevels  | $152 \\ 154$                              |

|   |                   | 8.1.6            | Transformation between RTL and PV                 | $154 \\ 156$                              |

|   |                   |                  |                                                   |                                           |

|   |                   | 817              | Summary                                           | 157                                       |

|   |                   | $8.1.7 \\ 8.1.8$ | Summary                                           | $\begin{array}{c} 157 \\ 158 \end{array}$ |

|    | 8.2   | Simula  | ation Performance Analysis                       | 159 |

|----|-------|---------|--------------------------------------------------|-----|

|    |       | 8.2.1   | Assertion Drawback                               | 159 |

|    |       | 8.2.2   | Impact of Evaluate-Update and Tentive Mechanisms | 160 |

|    |       | 8.2.3   | Impact of Trigger Mechanism                      | 162 |

|    |       | 8.2.4   | Results                                          | 163 |

| 9  | Con   | clusion | and Outlook                                      | 165 |

| Bi | bliog | raphy   |                                                  | 169 |

| Li | st of | Acrony  | rms                                              | 175 |

| GI | ossar | у       |                                                  | 179 |

| Α  | List  | of Req  | uirements for Assertion Transformation           | 181 |

| В  | Lan   | guage ( | Grammar                                          | 187 |

|    | B.1   | Refine  | ment Grammar                                     | 187 |

|    | B.2   | Basic   | Monitor Grammar                                  | 190 |

|    | B.3   | Chang   | ges/Enhancements of Monitor Grammar              | 195 |

|    | B.4   | Comm    | non Grammar                                      | 196 |

# List of Tables

| 5.1  | Abstraction Levels                                         |

|------|------------------------------------------------------------|

| 5.2  | UAL Event Operators                                        |

| 5.3  | Trigger-related Attributes that produce Events             |

| 5.4  | Trigger-related Attributes that produce Boolean Results 58 |

| 5.5  | Available Add Directives                                   |

| 5.6  | Available Modify Directives                                |

| 5.7  | Available Remove Directives81                              |

| 6.1  | General Methods                                            |

| 6.2  |                                                            |

| -    | General Functions                                          |

| 6.3  | Event Layer Methods                                        |

| 6.4  | Event Layer Functions                                      |

| 6.5  | Sequence Layer Methods                                     |

| 6.6  | Property Layer Methods                                     |

| 6.7  | Match Filter - Methods                                     |

| 6.8  | Match Filter - Antecedent related Functions                |

| 6.9  | Match Filter - Consequent related Functions                |

| 6.10 | Match Filter - Property related Functions                  |

| 6.11 | Match Filter - General Functions                           |

| 8.1  | Assertion Performance Impact                               |

|      | -                                                          |

| 8.2  | Impact of Evaluate-Update and Tentative Matching           |

| 8.3  | Impact of Trigger Mechanism 162                            |

# **List of Figures**

| $\begin{array}{c} 1.1 \\ 1.2 \end{array}$ | The VP Model [1] for System Development Use of Testbenches for Multi Abstraction Checks          |   |   |   |   |   |   |  | $\frac{2}{6}$ |

|-------------------------------------------|--------------------------------------------------------------------------------------------------|---|---|---|---|---|---|--|---------------|

| 2.1                                       | FIFO Example                                                                                     |   |   |   |   |   | • |  | 17            |

| 3.1                                       | Transaction Relations                                                                            |   |   |   |   |   | • |  | 22            |

| 4.1                                       | Sample Testbench System According to $\operatorname{AVM}[2]$                                     |   |   | • |   |   | • |  | 36            |

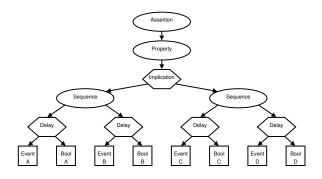

| 5.1                                       | Sample Assertion Structure                                                                       |   |   |   |   |   |   |  | 44            |

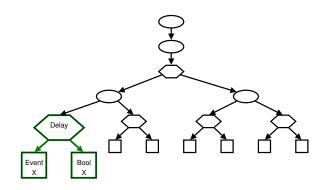

| 5.2                                       | Transformed Assertion with Structure Preservation                                                |   |   |   |   |   |   |  | 44            |

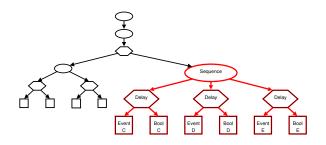

| 5.3                                       | Transformed Assertion without Structure Preservation                                             |   |   |   |   |   |   |  | 45            |

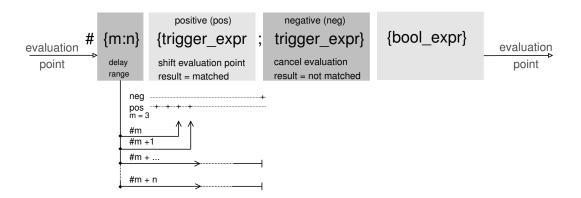

| 5.4                                       | General Delay Operator                                                                           |   |   |   |   |   |   |  | 51            |

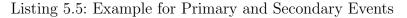

| 5.5                                       | Classification of Events                                                                         |   |   |   |   |   |   |  | 60            |

| 5.6                                       | Interaction of Execution Modes with Tentative Concept                                            |   |   |   |   |   |   |  | 62            |

| 5.7                                       | Split of Threads in case of Tentative Events                                                     | • | · | • | • | • | • |  | 64            |

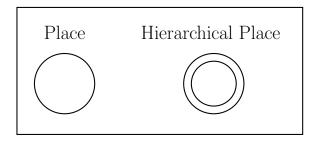

| 6.1                                       | Types of Petri Net Places $\ldots \ldots \ldots \ldots \ldots \ldots$                            |   |   |   | • | • |   |  | 100           |

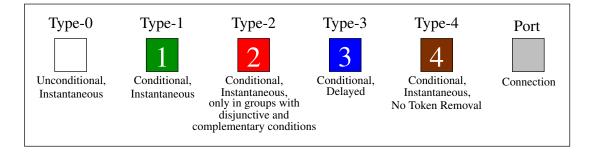

| 6.2                                       | Types of Petri Net Transitions                                                                   |   | • |   |   |   | • |  | 101           |

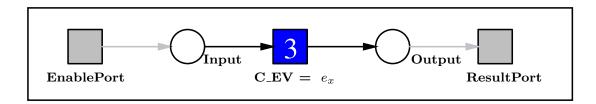

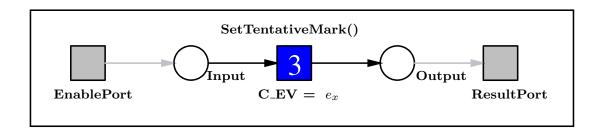

| 6.3                                       | Single Event                                                                                     |   | • |   |   |   | • |  | 110           |

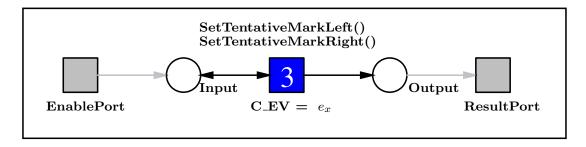

| 6.4                                       | Tentative Event $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |   |   |   |   |   |   |  | 110           |

| 6.5                                       | Tentative Event in First Delay Operator $\ldots \ldots \ldots$                                   |   | • |   |   |   | • |  | 111           |

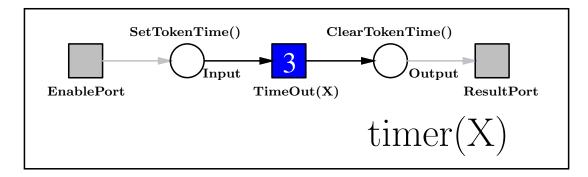

| 6.6                                       | TIMER Operator $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$           |   |   |   |   | • |   |  | 111           |

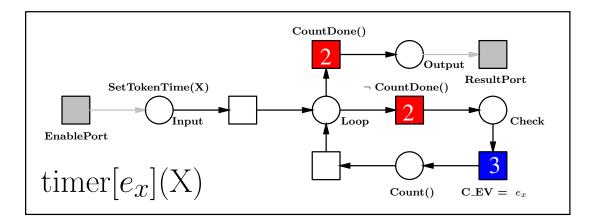

| 6.7                                       | Event-based TIMER Operator                                                                       |   |   |   |   | • |   |  | 112           |

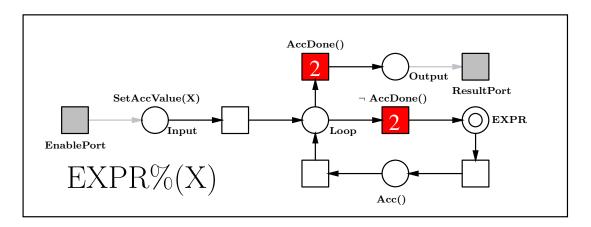

| 6.8                                       | ACCUMULATOR Operator                                                                             |   |   |   | • |   |   |  | 113           |

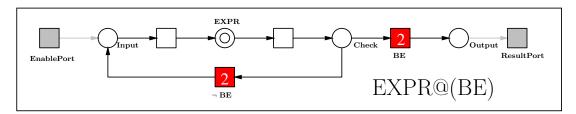

| 6.9                                       | CONSTRAINT Operator                                                                              |   |   |   |   |   |   |  | 113           |

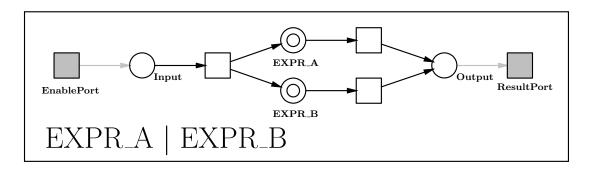

| 6.10                                      | OR Operator                                                                                      |   |   |   |   |   |   |  | 114           |

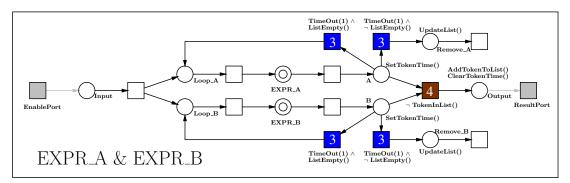

| 6.11                                      | AND Operator                                                                                     |   |   |   |   |   |   |  | 115           |

| 6.12                                      | Zero-Delay Operator                                                                              |   |   |   |   |   |   |  | 117           |

| 6.13                                      | Single-Step-Delay Operator                                                                       |   |   |   |   |   |   |  | 118           |

| 6.14                                      | Empty Event Expression                                                                           |   |   |   |   |   |   |  | 118           |

| 6.15                                      | Ranged Delay Operator                                                                            |   |   |   |   |   |   |  | 119           |

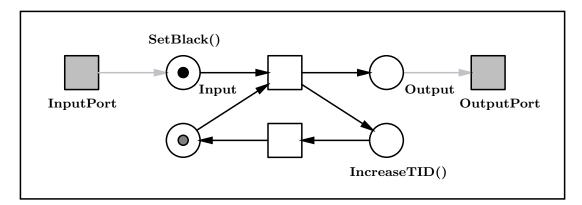

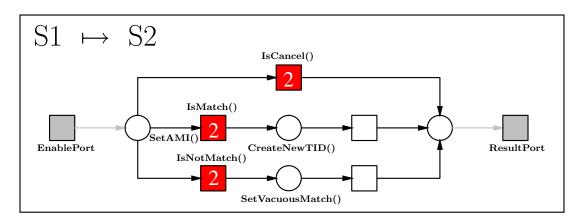

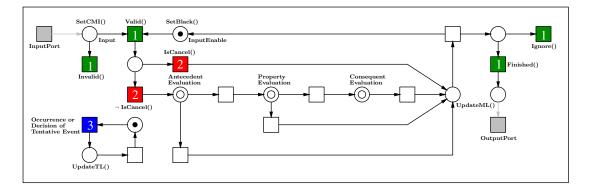

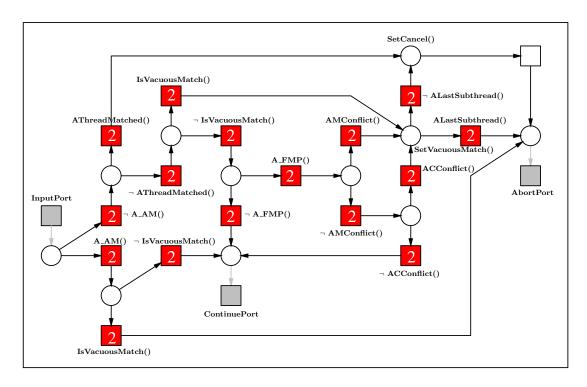

|                                           | Token Generator                                                                                  |   |   |   |   |   |   |  | 119           |

| 6.17                                      | Implication Operator                                                                             |   |   |   | • |   |   |  | 121           |

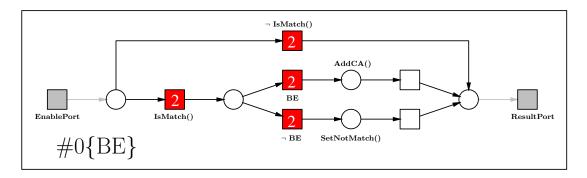

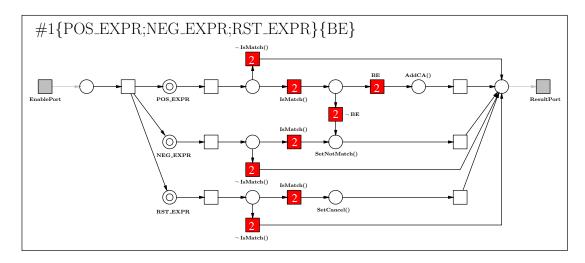

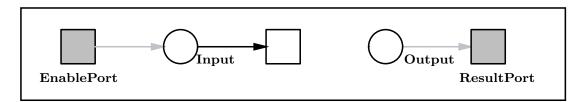

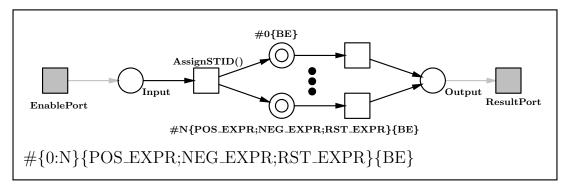

| 6.18                                      | Match Filter                                                                                     |   |   |   |   |   |   |  | 126           |

| 6.19 | Match Filter - Antecedent Evaluation      | 128 |

|------|-------------------------------------------|-----|

| 6.20 | Match Filter - Property Evaluation        | 129 |

| 6.21 | Match Filter - Consequent Evaluation      | 130 |

| 6.22 | Example for Assertion Mapping             | 134 |

| 7.1  | Assertion Refinement Framework            | 135 |

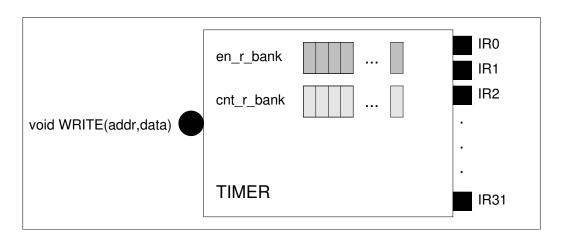

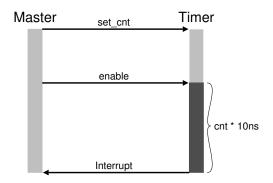

| 8.1  | AHB Timer                                 | 144 |

| 8.2  | Sequence of the Timer Interrupt Procedure | 144 |

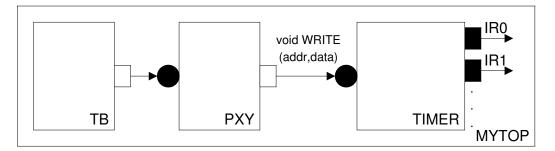

| 8.3  | Transaction detection via Proxy Modules   | 145 |

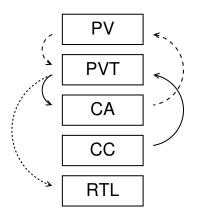

| 8.4  | Overview of the presented transformations | 148 |

# List of Listings

| 2.1  | FIFO assertion for TLM                                              | 16  |

|------|---------------------------------------------------------------------|-----|

| 2.2  | FIFO assertion for RTL                                              | 16  |

| 5.1  | Assertion Example for Structure Preservation                        | 45  |

| 5.2  | Example for Implicit Timing                                         | 47  |

| 5.3  | Sample Event Sequence                                               | 52  |

| 5.4  | Example for Mixed Level Assertions                                  | 54  |

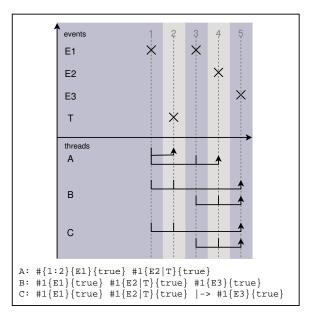

| 5.5  | Example for Primary and Secondary Events                            | 59  |

| 5.6  | Early Confirmation of Tentative Events                              | 65  |

| 5.7  | Example for Constrained RTL transactions                            | 65  |

| 5.8  | Transactor Example                                                  | 72  |

| 5.9  | Example for Rule Instantiation                                      | 75  |

| 5.10 | Example for Transactor Instantiation                                | 76  |

| 5.11 | Example for Adding a Time Constraint                                | 78  |

| 5.12 | Example for Modifying a Timer                                       | 80  |

| 5.13 | Example for Removing a Reset                                        | 81  |

| 5.14 | Location Example: Sample Monitor                                    | 83  |

| 5.15 | Location Example: Sample Locations                                  | 83  |

| 5.16 | Example for Transformation Ambiguity (1)                            | 85  |

| 5.17 | Example for Transformation Ambiguity (2)                            | 85  |

| 7.1  | Example of MAKO template                                            | 137 |

| 7.2  | Sample output of MAKO template                                      | 137 |

| 8.1  | PVT Timer Assertion Monitor                                         | 145 |

| 8.2  | Library File containing Declarations                                | 147 |

| 8.3  | Transformation from PVT to CA                                       | 149 |

| 8.4  | Changing from Absolute Timing to Cyclic Timing (from tim-           |     |

|      | ing_rule_lib.tll)                                                   | 149 |

| 8.5  | CA Timer Assertion Monitor                                          | 150 |

| 8.6  | CC Timer Assertion Monitor                                          | 151 |

| 8.7  | Changing from Clocked Timing to Absolute Timing (from tim-          |     |

|      | ing_rule_lib.tll)                                                   | 151 |

| 8.8  | Transformation from CA to PV                                        | 152 |

| 8.9  | Removing Local Variable References (from misc_rule_lib.tll)         | 152 |

| 8.10 | Changing from Cyclic Timing to Untimed (from timing_rule_lib.tll) . | 153 |

| 8.11 | PV Timer Assertion Monitor                                          | 153 |

| 8.12 | Changing from Untimed to Absolute Timing (from timing_rule_lib.tll) | 154 |

|------|---------------------------------------------------------------------|-----|

| 8.13 | Adding Local Variable References (from misc_rule_lib.tll)           | 155 |

| 8.14 | Transformation from PVT to RTL                                      | 155 |

| 8.15 | Library File containing Transactor                                  | 156 |

| 8.16 | Adding a Reset Statement to an Assertion (from reset_rule_lib.tll)  | 156 |

| 8.17 | RTL Timer Assertion Monitor                                         | 157 |

## **1** Introduction

### 1.1 The Pervasiveness of Embedded Systems

Technical progress over the past decades has made high technology more and more part of people's every day life. Not only the number of devices, but also the complexity of these systems has increased drastically. Nevertheless, most people are only partly aware of the extent of this phenomenon, since in many cases the complex systems are part of seemingly simpler devices. Today, these systems can be found in almost all aspects of daily life: Domestic appliances like dishwashers or washing machines include them for controlling water supply or dosage of detergents in order to clean dishes or clothes as efficiently as possible. HiFi systems like CD players include controlling systems for the laser that reads the information stored on an audio CD. Mobile phones have rapidly spread and have already become a standard accessoir for most people. Clothes with built-in mp3 players are created. Cars include electronics for engine control or electrical control of locks, while current research aims at features as break-by-wire and warning systems that can alert the driver of potential dangers like collisions or leaving the road; these systems are intended not only alert the driver in the end, but also automatically correct wrong behavior. When compared with personal computers, these complex systems are not or not directly visible to the user. Instead they are embedded within a larger system and can only be accessed by a restricted interface.

## 1.2 Quality of Embedded Systems

In contrast to personal computers where a bug in a program can be corrected by a patch of the affected Software (SW) even after the product has been delivered to the customer, access to embedded systems for this purpose is difficult at best. Additionally, bugs in the Hardware (HW) that has already been delivered cannot be fixed at all.

Considering that at least some of these embedded systems control safety critical tasks like the break-by-wire system mentioned above, it is essential that the quality of embedded systems is checked according to strict standards during all stages of the design process. Whenever a bug is detected during those tests, the reaction depends on the location, the severity of the encountered bug, and the stage in the design process. While SW bugs can usually be fixed without much additional effort, bugs in a HW component are not as easily fixed. In simple cases maybe the SW of the embedded system can be adapted to take the bug into account. In more serious cases this might lead to a complete respin of the system development and even fabrication if the system has already been shipped.

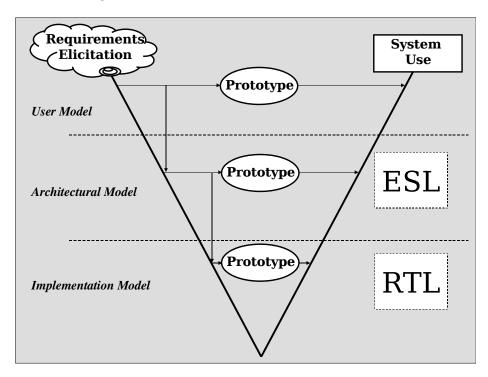

In order to minimize the immense costs of having to start the whole development process again from the beginning (even worse if the system has already been fabricated), the usual course of system development follows the so called VP model [1], which is shown in Figure 1.1.

Figure 1.1: The VP Model [1] for System Development

According to this process, system development starts with a very abstract model that neglects many of the characateristics of the final design in order to focus on the important aspects as for instance the algorithms involved and the basic functionality coverd by the system. The corresponding prototype is then subjected to extensive tests concerning these features. If there are already bugs within the implementation, only a small part of the development work has to be redone. This early model can also help with architecture exploration, since several design decisions only have to be done for less abstract models. After this model has passed an appropriate number of tests, a more complex model is developed. In this context, the more abstract models serve as golden reference for the newly developed ones. At the same time, the more abstract models can be used for early software development or system documentation, before the final version of the design is even ready.

### **1.3 Model Equivalence**

If various models on different abstraction levels exist, a method for checking the functional equivalence of these models is needed. Several different technologies exist that can cover at least a part of this problem, depending on the exact application.

#### 1.3.1 Connection Verfication

There are already efforts of standardizing the description of an Intellectual Property (IP) in order to ease its integration into a system of another company. The SPIRIT consortium [3] for instance already published a standard for the description of Register Transfer Level (RTL) model interfaces. At the moment, the standard is being extended in order to also cover Transaction Level (TL) models. A SPIRIT description captures the necessary data in several Extensible Markup Language (XML) files, which are then delivered to customers in combination with the precompiled IP. A specific IP may include a TL and an RTL implementation.

Using the SPIRIT description as a reference, it is possible to check that the interfaces of both models are consistent. Note that this does not require that they are identical (which will not be the case anyway), but just that the available connections are the same. If for instance, the TL model has a transaction port for a read access to a connected memory module with an address parameter and a data parameter, then the RTL implementation should at least contain an address output to the memory and a data input from the memory.

If the modules in question consist of several submodules then the correct interconnection of these submodules can be verified as well.

#### 1.3.2 Formal Verification

Formal verification includes a variety of different technologies which all examine the model or models in question based on mathematical and logical criteria. In general, two different kinds of formal verification approaches can be distinguished:

- 1. Equivalence Checking: This technique examines two models and breaks down the corresponding functionality into small logical blocks. In order to be equivalent, both models have to behave in exactly the same way when they are faced with the same circumstances. For that purpose, the involved algorithms assume that both models are not equivalent and try to lead this assumption to a logical contradiction.

- 2. Property Checking: This technique tries to prove that a model fulfills a certain set of specified properties which reflect the original specification. When used to prove the equivalence of two models using this technique, it is required to check all properties with both models.

Formal techniques cover all possible transition paths through the design state space (in contrast to just a large number of sample tests). The larger the model in question, the more resources are necessary for a formal analysis. Due to the problem of state space explosion - the size of the state space increases exponentially with the number of design states - today's complex systems simply cannot be evaluated using formal verification.

#### **Equivalence Checking**

In order to at least reduce the problem of state space explosion, it is necessary to have efficient algorithms for the creation of the simplified models which are then compared.

There are already approaches for the formal equivalence checking between RTL models and gate level models. On the other hand, these concepts cannot be transferred easily to higher levels, as for instance the equivalence check between TL and RTL. This is partly the result of the very abstract modeling style on higher abstraction levels. Complex function calls and transfers of complex data objects cannot easily be reduced to logical representations as needed for the equivalence checks.

While a generalized formal equivalence check between TL and RTL is not possible yet, there have been first approaches for the application of formal equivalence checking in a more restricted context. The approach discussed in [4] for instance uses the equivalence checks in combination with a high-level synthesis tool. In other words, the less abstract model is not written by hand in this case and the additional data used or acquired during the model transformation is then used in order to formally verify the equivalence of original and generated model.

#### **Property Checking**

When applying property checking to models of different abstraction levels, checking the same property with all models might require the adaptation of the property description. This leads to similar problems as faced when using assertions (see below).

#### 1.3.3 Simulation-Based Verification

Instead of analyzing a model mathematically, simulation-based verification uses a special testbench that generates stimuli sent into the model and receives the corresponding responses of the model. The generated stimuli might be either specify directly - so called directed tests - or created randomly, with or without constraints. The latter approach is much more efficient of finding bugs, since the randomization leads to checks that normally would not have been specified; thus, it is possible to detect bugs resulting from dependencies that nobody had considered before. The most common approach for simulation based verification is a combination of these two approaches: The testbench starts with generating random stimuli and gathers the results. These results are then stored in a database for several kinds of coverage data. Examples for coverage data include:

- Code coverage measures which parts of the code have been executed how often

- Functional coverage measures how often a certain functionality has been used

- Assertion coverage measures how often a certain assertion has fired or not resulted in a vacuous success (see below)

Since a complete check including every possible combination of values by simulation is impossible for realistic systems<sup>1</sup>, certain coverage goals have to be defined (for instance, "every memory address has to be written three times"). As soon as a coverage goal has been achieved, this particular situation does not have to be checked anymore. As a result, the stimuli generation can be constrained to the remaining situations, which in turn improves the probability of achieving the remaining coverage goals faster. This approach is called *Constrained Random Simulation*.

Depending on the abstraction level of the Design Under Test (DUT), the interfaces between the testbench and the DUT are either method based for TL models, or signal based for RTL models.

$<sup>^1{\</sup>rm A}$  chip with fifty one-bit registers has  $2^{50}$  different states. When checking one million states per second, an exhaustive simulation would take about 850 years.

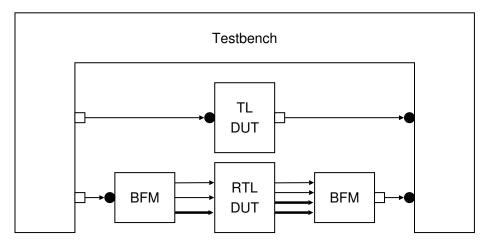

However, in order to ensure equivalence between the corresponding models, it would be beneficial if the same testbench can be used for the verification of both models. This is possible by using dedicated components called Bus Functional Model (BFM) or Transactor that "translate" between the high level and the low level protocol. While it does not matter for this method if the testbench is implemented on a higher or lower level, using an abstract testbench has two advantages:

- 1. It is easier to specify abstract test patterns, since the complex signal protocol does not have to be taken into account.

- 2. According to the VP model, the high-level implementation of the design is created first. Additionally, the creation of the Transactors can be postponed to the start of the low-level implementation. This means that the verification of the high-level model can be started sooner.

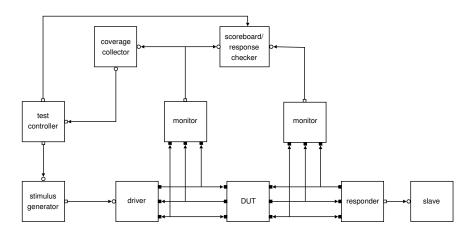

When using this method to check the equivalence of a TL model and an RTL model, the testbench sends the same stimuli to both models, and stores the response in two separate data bases. The corresponding structure is shown in Figure 1.2.

Figure 1.2: Use of Testbenches for Multi Abstraction Checks

While the stimulus generation can be used for both models in the same way, the coverage goals usually have to be redefined for the RTL model, since the modeling styles and paradigms differ greatly in some regards. Low-level structures might not even exist in high-level models, on the other hand, several distinct structures of the high-level model might be mapped on a shared structure in the low level model.

The use of Transactors is not restricted to the direct interaction with a testbench though. It is also possible to include an RTL component including the corresponding Transactors into an existing TL system, replacing the original TL component.

#### Assertions

Assertion Based Verification (ABV) uses specialized watchdog components called assertions that are either included in the design itself or attached to an existing design from the outside. Assertions specify a required temporal and logical behavior that must never be violated. Assertions can be used in addition to both formal verification (property checking) and simulation-based verification. In the former case, assertions are used for specifying both the properties of the design and assumptions about the behavior of external components. In case of simulation-based verification, assertions are simulated in combination with the model and continously check if the specified behavior is violated. If this is the case, the user is immediately informed about this error and - depending on the configuration of the assertion - the simulation is stopped.

In case of simulation-based verification the immediate notification of an error makes localization of the actual error much easier when compared to the tedious backtracking if an error shows up in the testbench (since the error had to propagate to the output first, it could have happened quite some time before it is noticed). Additionally, since assertions monitor the internal behavior of a model in contrast to the external monitoring a testbench does, they ar able to check behavior errors that only rarely become visible at an output. As a result of applying assertions to a design, the amount of coverage goals inside a testbench can be reduced.

In contrast to testbenches, assertions can and should also be written by designers while creating a model. This makes it possible to specify constraints of the model interface, for instance "port A and port B may never be one at the same time". Whenever this model is used within an existing system, every wrong usage would be notified immediately.

Since assertions can also be used in combination with simulation-based verification, it is also possible to apply them to equivalence checking. Besides adding corresponding assertions to both the TL model and the RTL mode, there is also the additional possibility of writing mixed level assertions that try to correlate the behavior of both models at certain matching points (for instance, in both models a register has to be written). Due to the variety of modeling styles on higher levels of abstraction and the fact that both models might differ greatly concerning the timing, finding these matching points within the various functional blocks of both models might be difficult.

While wide spread for RTL verification, only recently first approaches for applying ABV to TL models have been developed.

### 1.4 Motivation

It is vital to ensure consistency between the various models developed during the design process, which are written on different abstraction levels.

Right now, there is no methodology in place for the automated transformation of TL designs down to RTL. Instead, all models are transformed manually, which introduces additional sources for errors.

Unfortunately, verification efforts are mostly focused on checking the correctness of RTL designs. Simulation-based verification using testbenches is applied to TL models as well, in some cases the corresponding testbenches are even reused for RTL models later on. However, in many cases TL testbenches are much less sophisticated than their RTL counterparts. Furthermore, while the usage of assertions in simulation based verification for RTL is common, it is far from wide spread. On TL on the other hand it is almost non-existent (this is partly based on the fact that TL assertion languages are mostly still in development, however). Applying the same sophisticated test strategies already for TL models would allow an earlier identification of errors which in time reduces the overall verification effort. This is even more important since future designs will have a drastically increased complexity which in turn makes early identification of errors critical.

While TL testbenches can be reused for RTL in combination with Transactor components, it is not possible to reuse TL assertions in that way, since they are partly included within the design or access data not visible at the model interface.

As a result, even if assertions will be used more often in combination with TL models in the future, they will have to be manually transformed to a corresponding RTL equivalent, which may introduce additional errors, just as mentioned for the design refinement above.

This work addresses this lack of automated assertion transformation. Based on an existing assertion language capable of handling both RTL and TL assertions (including the various TL sublevels), a dedicated transformation language has been created that allows the automated transformation of assertions from and to all supported abstraction levels.

The peculiarities of all supported abstraction levels have been considered and the underlying assertion language has been enhanced by several features required for a consistent specification of assertions on these abstraction levels. As a consequence, consistent mixed level assertions are supported as both original and generated assertions. This allows the specification of assertions for the equivalence checking method based on matching points mentioned above. The transformation descriptions can be formulated in a flexible way, which allows a reuse of existing transformation rules for other assertion transformation tasks as well.

The expected benefit is the efficient reuse of TL assertions for RTL verification, while only requiring little effort to adapt existing transformation rules. If desired, transformation of RTL assertions for the verification of TL models is possible as well.

## 1.5 Outline

This work is structured as follows:

Chapter 2 describes the problems an assertion transformation approach has to face and outlines possible solutions.

Based on this analysis, Chapter 3 introduces requirements for assertion transformations, split into requirements for the underlying assertion language and requirements for the transformation description.

Existing solutions for these are requirements are analyzed in Chapter 4 and the new work is motivated.

Chapter 5 describes the concepts introduced in this work, split into the extension of an existing assertion language and the development of a dedicated transformation language.

A formal representation of the modified assertion language is described in Chapter 6.

In Chapter 7 an overview over the application framework is given.

The results presented before are used in Chapter 8, which describes how to systematically apply the transformation language using an example that covers all relevant abstraction levels.

Finally, Chapter 9 summarizes the scientific contribution of this work and outlines further directions.

# 2 Problem Statement and Targeted Approach

This chapter discusses the problems an assertion transformation approach has to deal with and also outlines possible ways of solving these problems.

## 2.1 Today's Top-Down Design

Today, designs are created in a top-down process, beginning with a highly abstract model, containing only the information provided by the design specification that serves as a Virtual Prototype (VP) for SW validation and as a golden reference for later models. Partially, more abstract models are used to validate specific aspects, as for instance the algorithms behind a 3G receiver. Due to the high level of abstraction and the ensuing absence of details, the simulation of the VP can be done much faster and with greatly reduced computation effort. The following models gradually add more and more details, while still being consistent with the VP.

#### 2.1.1 Abstraction Levels

In order to provide means for easier model comparison concerning the amount of details involved, several attempts of defining specific abstraction levels have been made. These abstraction levels differ in the way timing is modeled, how data is exchanged between different functional units, how this data is represented, etc. Most of these attempts differ in the names, number, and characteristics of levels defined. One example of how these differences can be categorized is presented in [5]. An example for a list of abstraction levels can be found in [6]. All in all, there are no established standards which clearly define all abstraction levels and what characteristics a model written at a certain abstraction has to show.

The most common abstraction levels are the following<sup>1</sup> (ordered from most abstract to most detailed):

<sup>&</sup>lt;sup>1</sup>While the names may differ depending on the source, the underlying concepts are usually present in all approaches.

- Specification Level: This level only deals with the information relevant for correct system functionality. Timing is only considered when absolutely essential for the system behavior; similarly this levels rarely considers functional partitioning into several components, and thus, there is no concurrency either. Data processing is done in the most abstract way possible while using abstract data representation.

- TL: This level introduces partitioning of the model into different functional blocks which have to exchange data according to one or several protocols. This data exchange is handled by so called transactions, usually modeled as function calls, using abstract data types for parameters and return values; these transactions can be used to encapsulate certain functionality as well as to hide protocol details. Since a Transaction Level Model (TLM) is frequently used as VP, decisions concerning elements accessible by the SW have to be made here and kept for later design stages. In contrast to the other levels mentioned, this level does not represent one specific abstraction of a design but can be further divided into several sublevels. The Open SystemC Initiative (OSCI) TLM standard has introduced specific names for these sublevels, but unfortunately their characteristics are not clearly defined:

- Programmer's View (PV): This sublevel is located only slightly below the Specification Level. PV models do not consider timing in any way, so synchronization between components is restricted to zero-delay wait statements and specific events in combination with conditional wait statements.

- Programmer's View with Timing (PVT): This sublevel additionally introduces the notion of time, modeled by absolute time values. Every kind of functionality including transactions can consume a certain amount of time. Synchronization is done via timed wait statements, in addition to the methods available on PV.

- Cycle Approximate (CA): This sublevel is very similar to PVT, but instead of using arbitrary time values within the components, all delays are replaced by cylic delays, expressed as a multitude of one (or several) clock periods. The available synchronization schemes match those of PVT.

- Cycle Callable (CC): The final TL sublevel replaces the cylic time of the CA models by the introduction of one or several clock signals. The synchronization between different component happens only according to these clock signals.

- RTL: This level models both functionality and structure of the design in a very detailed way. Synchronization is done via clock signals as in Cycle Approximate (CA), but additionally the TL concept of transactions is replaced by signals and

corresponding protocols (e.g., handshake). These signal protocols exactly represent the behavior of the final silicon chip and can be automatically synthesized by corresponding tools. For that purpose, the abstract data types of the upper abstraction layers are replaced by HW data types. Since handling of complex protocols requires more effort than a simple high-level function call, RTL models often implement Finite State Machine (FSM)s for that purpose. The complete description can be easily mapped to simple logical circuits, like AND gates and multiplexors, while abstracting away everything but their functionality.

• Gate Level: This level introduces the other parameters of the low-level logical circuits comprising the RTL description. In addition to their functionality parameters like throughput time and power consumption are modeled.

#### 2.1.2 Refinement

In order to ensure continuity during the design process, whenever a less abstract model is created based on a more abstract one, the differences between the abstraction levels have to be kept in mind. In this context the term refinement is often used:

**Definition 1** Refinement describes the transition between different levels of abstraction<sup>2</sup>, for example the transformation of a Programmer's View with Timing (PVT) model to an RTL model. This transition includes the removal of information no longer relevant on the new abstraction level, as well as the inclusion of additional information that was not available on the original level.

Although number and exact details of the different abstraction levels differ depending on the source, the characteristics used for distinguishing the various levels are the same in all approaches (modeling of time, structure, etc.). As long as refinement processes are discussed in relation to these characteristics and not to particular abstraction levels, everything discussed is generally valid, independently of the definition used. For that reason, the remainder of this work will use the terms and abstraction levels presented above.

The effects of design refinement can be divided into effects on the module interfaces and effects on the module implementation. Interface changes foremost happen at the transition between TL and RTL since the abstract function calls of TL are replaced by complex signal protocols on RTL or vice versa. Implementation changes are less obvious and include the aforementioned topics of timing and data representation.

$<sup>^{2}</sup>$ This term is usually applied to a transformation towards a less abstract version, but it is not restricted to that.

Since an equivalence check between two different implementations of a complete system is very difficult and resource intensive, in many cases a BFM, also called transactor, is used which transforms the interface of a component modeled on one abstraction level to another one. This allows to create a less abstract version of a single component first and then to simulate this component within the existing abstract system.

When creating a design in a top-down process according to the abstraction levels described in Section 2.1.1, the following refinement steps have to be performed:

- Specification Level to Programmer's View (PV): The monolithic functionality of the Specification Level Model has to be partitioned into smaller components which exchange data through transactions.

- PV to Programmer's View with Timing (PVT): The purely untimed PV model is enhanced by the addition of timing information.

- PVT to Cycle Approximate (CA): The timing information expressed by absolute values is converted to cyclic timing.

- CA to Cycle Callable (CC): The cyclic timing is replaced by the usage of one or several dedicated clock signals.

- CC to RTL: Transactions are replaced by elaborate signal protocols. Additionally, data representation is changed to synthesizable data types. Finally, the functionality is modeled with great detail, including the use of state machines and the choice of specific computation architectures.

- RTL to Gate Level: All functional blocks are annotated with information concerning their timing and power consumption.

In most cases, there is not one prototype for each of these abstraction levels. Thus, the resulting refinement steps might combine several of the steps mentioned here. However, the underlying concepts are not touched by this.

It has to be noted that while some of these refinement steps can be automated (for some, automation has even become the standard procedure), all of them require that the details added on the less abstract level are provided to the automation tool. While this problem can be (partially) solved - for instance, most tools for the synthesis from RTL to Gate Level provide easy means for specifying the required data (choice of a suitable technology, clock frequency, etc.) - this approach also limits flexibility. Thus, a completely automated and flexible refinement without any kind of user interaction is - and very probably will always be - impossible.

### 2.2 Assertion Based Verification

ABV is one of the most effective way of checking designs for both intent (done by the designer during the creation of the model) and for correct functionality (done by a verification engineer after the design process has been completed). The approach uses so called assertions, code constructs that monitor a specific part of the design and issue an error message as soon as the observed behavior differs from a specified pattern.

The use of assertions within a design is complementary to the use of testbenches in simulation based verification and can also be used for formal verification. Assertions offer an easy way of specifying desired behavior and being notified immediately when this behavior is violated. Since assertions may be part of the design and thus may have immediate access to internal design objects, it is much easier to locate the origin of an error. In other cases the verification engineer has to rely on the error propagating out of the design, in which case the potential delay can complicate correlating the error to its reason.

While ABV is a frequently applied technology with regards to RTL design, only recently the first successful methods for applying assertions to higher levels of abstraction, namely the various TL sublevels, have emerged. This is based on the fact that most of the existing ABV approaches make heavy use of the specifics of RTL models: Assertions have to run synchronously to the design which is usually achieved by relying on clock signals for triggering the assertion evaluation. Due to this, most current approaches are ill equipped to deal with the very different concepts of timing on TL. Additionally, since they are mostly signal centric, the use of transactions as a means to abstract away parts of the design details causes further problems.

### 2.3 Assertion Refinement

Similarly to a design, high-level assertions can be refined into less abstract assertions in order to perform the same checks on the refined design. Since assertions are closely linked to a design, concerning both the behavior and the structure, assertion refinement follows the same steps and guidelines as design refinement.

Providing a methodical approach for assertion refinement that includes some checks for the correctness of the refined assertion could decrease the effort for the overall verification process. Since the refined assertion, as an additional source of simulation errors, has already passed these checks, the main effort can be used for the verification of the design refinement. In order to ensure the correct assertion refinement, the underlying structure of the assertion has to be kept as much as possible. If different assertion languages are used for the different abstraction levels, this structure preservation gets more complicated due to the conceptual differences between most assertion approaches. Additionally, creating mixed-level assertions - especially useful for the aforementioned example of simulating a low-level component within a high-level environment using transactors - become almost impossible. As a result, assertion refinement is easiest when applied to a language supporting all abstraction levels involved.

Nevertheless, even given such an assertion language, certain problems arise due to the differences in the abstraction levels themselves. For instance, the different synchronization schemes on the various TL sublevels and RTL have to be matched somehow and the notion of TL transactions has to be converted to a comparable concept on RTL.

The refinement process should be captured in a way that allows easy reuse of the transformation description - in case the abstract assertion has been changed, so that the refined assertion does not have to be rewritten from scratch. Additionally, there might be similar assertions in different designs that have to be refined. If the assertion refinement can be described in a flexible way, it could be possible to apply the existing description to these similar assertions as well.

#### 2.3.1 Example

```

1 property p_DATA_PIPE_tlm

2 int D1;

3 #1{PUT'END}{true, D1=PUT.X}

4 |->

5 #{1:6}{GET'END}{GET.X=D1};

6 endproperty

```

Listing 2.1: FIFO assertion for TLM

```

1 property p_DATA_PIPE_rtl

2 int D1;

3 #1{CLK'POS}{SND_ACK, D1=SND_DATA}

4 |->

5 #{1:6}{CLK'POS}{RCV_ACK && (RCV_DATA=D1)};

6 endproperty

```

Listing 2.2: FIFO assertion for RTL

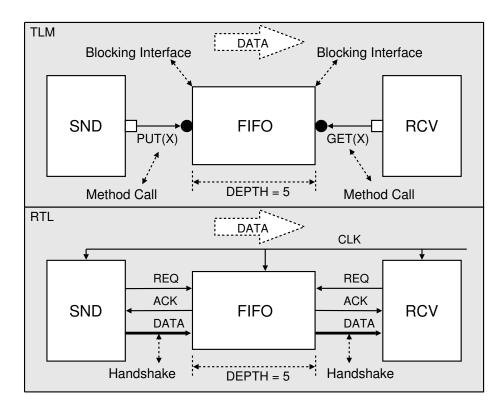

Figure 2.1 shows a FIFO circuit, once modeled on Transaction Level Model (TLM) and once on RTL. The Listings 2.1 and 2.2 give an example of what behavior could

Figure 2.1: FIFO Example

be checked by an assertion in this example: With a given FIFO depth of five, both assertions check that each successful write access to the FIFO is followed by a read access providing the same data within the next six read accesses.

As can be seen, the underlying structure of both assertions are quite similar, although the details are necessarily different due to the different abstraction levels.

# 2.4 Targeted Approach

The approach presented in this work provides solutions for assertion refinement taking into acount the problems stated above. These solutions consist of two parts: First, an assertion language capable of TL, RTL, and mixed-level assertions is enhanced by several features which are required to map concepts from one abstraction level to another; second, a framework consisting of a new language for the description of the refinement process combined with a refinement generator is introduced. This framework allows an easy refinement of existing assertions towards lower, higher, and mixed abstraction levels while preserving their structure. Additionally, refinement rules can be written in a flexible way so that they can easily be reused and applied to other assertions as well.

# **3** Requirements and Objectives for Assertions Refinement

In this chapter, the specific requirements for an assertion refinement approach covering all TL sublevels as well as RTL are listed and explained. First, requirements for the underlying assertion language are discussed, afterwards, the requirements for the transformation language are detailed. The text will provide references to the requirement summary at the end of the chapter (see Appendix A) as Rx where x represents the number of the requirement.

# 3.1 Requirements for the Assertion Language

In order to successfully refine existing assertions, the assertion language has to fulfill certain conditions as well. The following section details these requirements. Beginning with some general requirements which are valid for all kinds of assertions, requirements based on the covered abstraction levels, pipelined execution, and the connection to SystemC as the corresponding design language are listed.

# 3.1.1 General Requirements

Assertions are defined to monitor a design - either constantly or at certain points in time - for any mismatch between the actual behavior and a specified desired behavior. In order to fulfill this role as mere observers, assertions may not influence the design behavior in any way (R 1). Additionally, assertions only monitor a certain part of a design, so that changes of the remaining design parts that are entirely unrelated to the behavior checked by the assertion may not influence the assertion results (R 2); neither may these assertion results be influenced by adding further assertions to the design or removing them (R 3).

There are several different ways in which assertions can be used to support the verification of designs:

• Dynamic Verification: The Design Under Verification (DUV) is simulated in combination with a testbench module that applies stimuli to the design and evaluates the corresponding data provided by the design. This data can be stored in a coverage database and / or compared to the results of a golden reference model. This method has the advantage of easy use and low resource consumption, but it is almost impossible to guarantee that a design is absolutely error free.

Assertions in Dynamic Verification can be used to immediately detect design errors during the simulation run; additionally they can be used to provide coverage data for the testbench.

• Formal Verification: This verification method does not rely on testbenches or other ways of stimulus generation. Instead, abstract properties are formulated which the design has to fulfill. The formal checker then tries to falsify the given properties. If these tries result in a contradiction, the corresponding property is proven. The advantage of proving that specified properties are fulfilled at all times without having to simulate every possible combination of inputs is offset by the amount of resources this method requires for formally verifying even a medium sized design.

Assertions in Formal Verification are used for specifying both the properties to be proven and certain assumptions that can be made about the behavior of the environment.

• Semiformal Verification: This combination of the two methods mentioned above starts out with a normal simulation run during which "states of interest" are collected. Beginning with each of these states of interest, a bounded formal check<sup>1</sup> is then started. Basically this method enhances the probability of detecting design errors, but without the certainty of a pure formal check.

Assertions in Semiformal Verification can serve for all purposes described for dynamic verification and formal verification.

Since the targeted approach deals with dynamic verification, assertion evaluation has to be done during the simulation run (R 4) while the assertions also have to be able to provide coverage information (R 5).

# 3.1.2 Abstraction Levels

As mentioned in Chapter 2.1.1, a typical design process spans several abstraction levels with corresponding prototypes created on these levels. Currently, there are no

<sup>&</sup>lt;sup>1</sup>"Bounded" in this context means that the formal check is not completed, but only executed to a certain iteration depth, the bound.

attempts to bring ABV to the specification level yet, while gate level on the other hand introduces a lot of data to the models that are not present on the higher levels even in an abstract way. Thus, it is of low interest to cover these two abstraction levels in an approach for assertion refinement. The remaining levels on the other hand should be supported by a transformation approach (R 6). Since TLMs often contain parts on different TL sublevels and in order to allow verification of low-level components inside a high-level system (using transactors for connecting both parts), assertions containing parts on different abstraction levels have to be supported as well (R 7).

While it is possible to transform assertions of one abstraction level written in one language to another abstraction level and another language, this is no longer feasible if mixed level assertions have to be considered. Since any mix of abstraction has to be supported, the whole refinement approach should be based on only one assertion language that is able to cover all required abstraction levels by itself (R 8).

#### **Transactions and Signals**

All TL sublevels exchange data using remote function calls (so called transactions). In order to check TL models for correct behavior, these transactions and their arguments and return values have to be accessible for assertions as well. Thus, the assertion language has to be able to detect transaction occurrence as well as provide access to transaction parameters (R 9 and R 10).

Since RTL designs use signal protocols for data exchange, it is necessary to provide the assertions with access to all design signals (R 11). If assertions containing transactions have to be refined to RTL, it is necessary to provide a mechanism which maps TL transactions to a comparable RTL representation in order to ease the transformation (R 12).

#### Synchronization

Since the various abstraction levels differ greatly in how timing is modeled (or if it is modeled at all), there are also different synchronization schemes in place.

Programmer's View (PV) models do not consider timing at all. This does not necessarily mean that the model executes in zero time, but just that timing is of no importance for the interaction between the different components. As a result synchronization between these components and also synchronization between the design and the assertions is based on implicit events (zero delay wait statements) and explicit events (conditional wait statements) only (R 13). Programmer's View with Timing (PVT) and Cycle Approximate (CA) models additionally include timing. Synchronization between design components and assertions can now happen based on simulation time (timed wait statements) as well (R 14).

Cycle Callable (CC) and RTL designs use clock signals for synchronization which as a consequence have to be usable for the synchronization of assertions as well (R 15).

#### **Temporal Relations**

As a consequence of different synchronization schemes, the abstraction levels also differ in what temporal relations between events, transactions and signal changes can be detected.

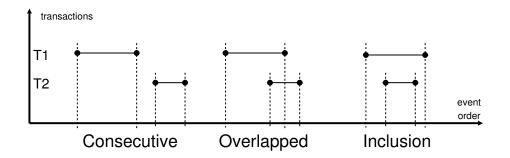

Since timing is not modeled in PV designs, and since the simulation kernel simulates the concurrent processes of a design in a sequential way, it is not possible to detect any kind of simultaneity between different events or transactions. However, it is possible to order events and transactions according to the execution order in the simulation kernel. This order might originate from causal dependencies between the corresponding events or transactions (in which case every simulator and every simulation run will produce this particular order), or by the fact that the kernel randomly processed first one event and then the other if there is no causal dependency (in which case the order might differ between simulation runs or simulators).

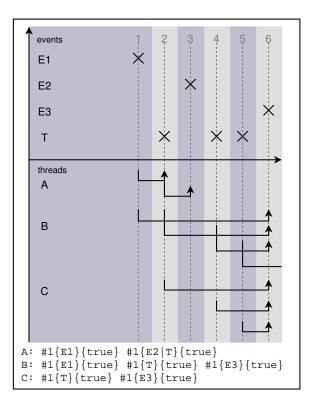

Figure 3.1: Transaction Relations

If care is taken to only reason about dependent transactions / events, then this order allows detecting the order of occurrence of events and of the different relations transactions have to each other (R 16) (see Figure 3.1).

Since every part of the design is able to produce events or call transactions, it is very likely that the use of a global event counter for determining the distance between two events would lead to dependencies between the assertion result and the completely unrelated parts of the design which are not checked by the assertion at all; this behavior though would contradict R 2. Therefore, it is necessary to specify partial orders on events, which consider only those events relevant for a particular assertion and neglect the rest (R 17). One additional problem lies in the unreliable occurrence of specific events; in contrast to RTL where it can be easily assumed that the next clock edge will happen, the same is not true for TL. But if an expected event does not happen due to an error in the design, the assertion has to be able to detect this absence. The specification of strict partial orders on events allows the detection of event absences relative to the occurrences to other events (R 18).

PVT models introduce timing to the design. When comparing every occurrence of events or transations with the corresponding time stamp, it becomes possible to correlate these events and transactions not only with regard to their order, but also based on the simulation time. Since an arbitrary amount of events can happen at the same simulation time, it is now possible for several events to occur simultaneously. Additionally, events or transactions that happened one after the other may now happen simultaneously (e.g. "A before B" becomes "A before or simultaneous to B"). These possibilities have to be taken into account for the assertion evaluation, which implies that temporal relations based on simulation time have to be detectable as well (R 19).

In most cases the underlying paradigms of CA models are very similar to PVT. The one big difference concerning the detection of temporal relations is that in a CA model it is possible to change the frequency of the simulated clock by changing the corresponding clock period. As a consequence it is possible for time delays to change dynamically which means that assertions have to support dynamic temporal behavior as for example the dynamic change of a time delay (R 20).

CC and RTL models do not use direct time delays anymore. Instead clock signals are used for synchronization and execution. Therefore, assertions have to be able to correlate events, transactions, and signal changes according to the clock signals as well (R 21).

# 3.1.3 Pipelining

Pipelining in one way or other is a quite frequently used mechanism. When refining a TL design down to RTL for instance, a previously sequential computation is often transformed into a parallel one, either by introducing some sort of dedicated pipeline, or by using multiple resources of a kind. Similarly, many TL designs make use of FIFOs or other structures with a built-in pipelined evaluation. In order to capture this behavior with assertions, the assertion language has to support checks of pipelined behavior (R 22).

# 3.1.4 SystemC

#### **Simulation Kernel**

With the rise of Electronic System Level (ESL) and Transaction Level Modeling, several new languages have been developed. One of them, SystemC<sup>2</sup>, has managed to establish itself as the de facto standard for creating TLMs while also supporting the modeling of RTL designs.

For that reason the assertion language should be able to check SystemC designs (R 23), which also means that all SystemC and C++ data types have to be supported for assertion notation and refinement (R 24).

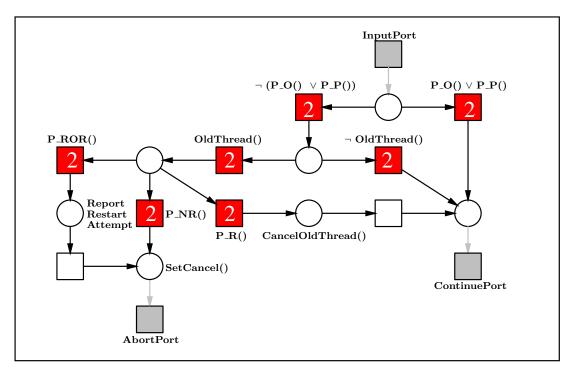

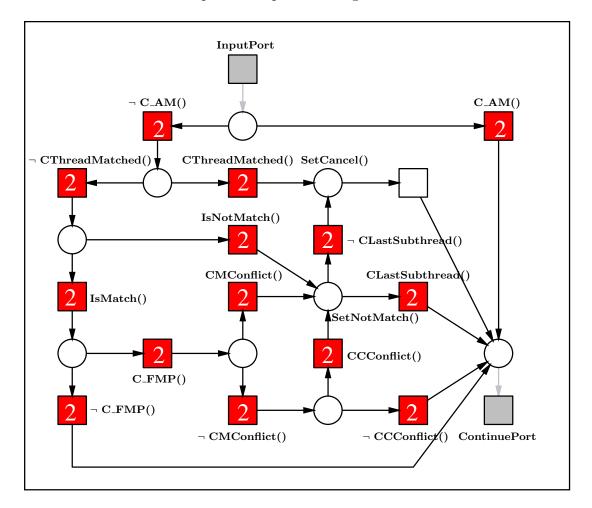

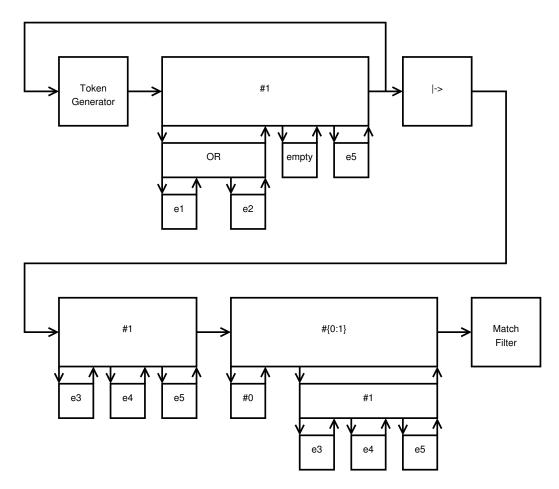

A SystemC reference kernel including infrequent new releases is provided by Open SystemC Initiative (OSCI). It is possible to either use the unchanged simulation kernel of OSCI SystemC or to include some custom changes that have to be transferred on every new version, followed by extensive tests to ensure compliance to OSCI SystemC. Since the continuous update of various kernel versions is too tedious, it is essential that the assertion evaluation does not require changes of the basic simulation kernel (R 25).