# Technische Universität München

Halbleiterlabor des Max-Planck-Institut für Physik und für extraterrestrische Physik München

# Studies of Radiation Hardness of MOS Devices for Application in a Linear Collider Vertex Detector

Qingyu Wei

Vollständiger Abdruck der von der Fakultät für Physik der Technischen Universität München zur Erlangung des akademischen Grades eines

### Doktors der Naturwissenschaften

genehmigten Dissertation.

Vorsitzender: Prüfer der Dissertation: Univ.-Prof. Andrzej Jerzy Buras

Hon.-Prof. Dr. Siegfried Bethke

2. Univ.-Prof. Dr. Stephan Paul

Die Dissertation wurde am 30.07.2008 bei der Technischen Universität München eingereicht und durch die Fakultät für Physik am 17.10.2008 angenommen.

# Contents

|     | stract                                                        |     |

|-----|---------------------------------------------------------------|-----|

| Ku  | ırzfassung                                                    | 6   |

| Int | roduction                                                     | 7   |

| 1.  | Motivation                                                    | 9   |

|     | 1.1. The standard model                                       | 9   |

|     | 1.2. ILC project                                              | 11  |

|     | 1.2.1. Linear collider                                        | 13  |

|     | 1.2.2. Detector concept for the international linear collider | 16  |

|     | 1.2.3. DEPFET-based vertex detector for the ILC experiment    | 19  |

|     | 1.3. Irradiation tolerance                                    | 26  |

|     | 1.4. Silicon detectors                                        | 27  |

| 2.  | MOS-Structures                                                | 31  |

|     | 2.1. MOS-DEPFET                                               | 31  |

|     | 2.1.1. Definition of a MOSDEPFET                              | 31  |

|     | 2.1.2. Operation of DEPFET                                    | 35  |

|     | 2.1.3. Noise                                                  | 38  |

|     | 2.2. MOS-capacitance                                          | 39  |

|     | 2.2.1. Definition of a MOS structure                          | 39  |

|     | 2.2.2. Calculation of a MOS capacitance                       | 44  |

|     | 2.3. Gated-controlled diode                                   |     |

| 3.  | Experiment methods and characteristic parameters              | 47  |

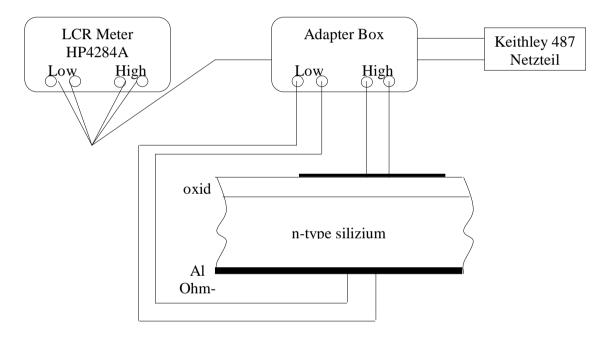

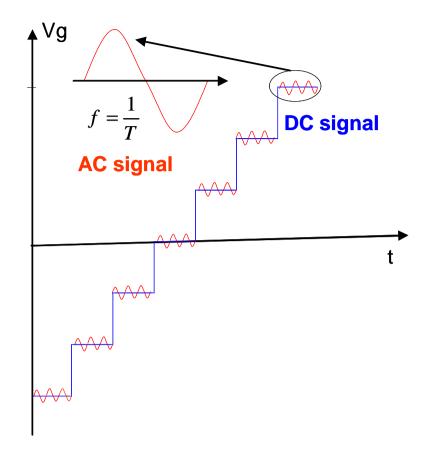

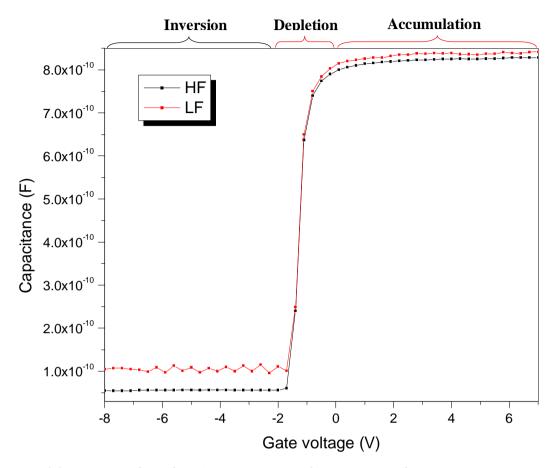

|     | 3.1. CV measurement using MOS capacitance                     |     |

|     | 3.2. Subthreshold technique concerning MOSDEPFET              | 52  |

|     | 3.3. Gated diode technique                                    |     |

| 4.  | Damage mechanism                                              | 57  |

|     | 4.1. Oxide                                                    | 57  |

|     | 4.1.1. Properties of thermal oxide                            | 58  |

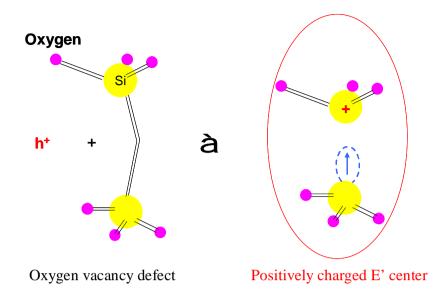

|     | 4.1.2. Defects in the oxide                                   | 59  |

|     | 4.2. Nitride                                                  | 62  |

|     | 4.2.1. Nitride properties                                     | 62  |

|     | 4.2.2. Defects in the nitride                                 | 63  |

|     | 4.3. Physical model                                           | 64  |

| 5.  | Irradiation experiments                                       | 76  |

|     | 5.1. Photon irradiations                                      | 76  |

|     | 5.2. Proton/neutron                                           | 77  |

|     | 5.3. Experimental setup                                       | 78  |

| 6.  | Irradiation on MOS-structures                                 | 82  |

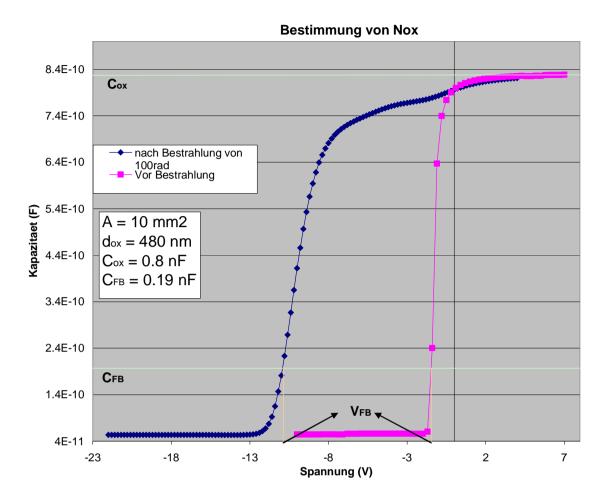

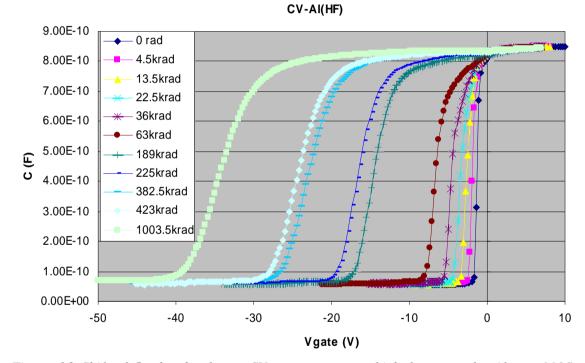

|     | 6.1. Dose                                                     | 83  |

|     | 6.2. Dose rate                                                | 96  |

|     | 6.3. Bias conditions                                          | 98  |

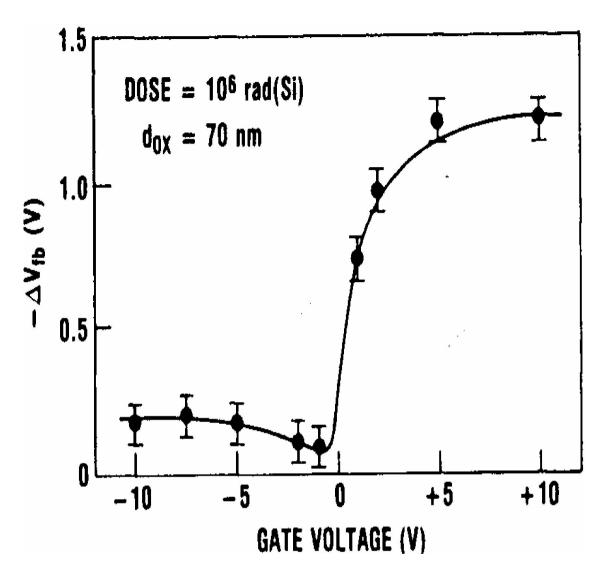

|     | 6.4. Oxide thickness                                          | 103 |

| 6.5. Nitride layer                             | 108                                   |

|------------------------------------------------|---------------------------------------|

|                                                |                                       |

|                                                |                                       |

| -                                              |                                       |

| 6.9. Surface damages affected by other factors | 141                                   |

|                                                |                                       |

| Conclusion and outlook                         | 149                                   |

|                                                | <ul> <li>6.5. Nitride layer</li></ul> |

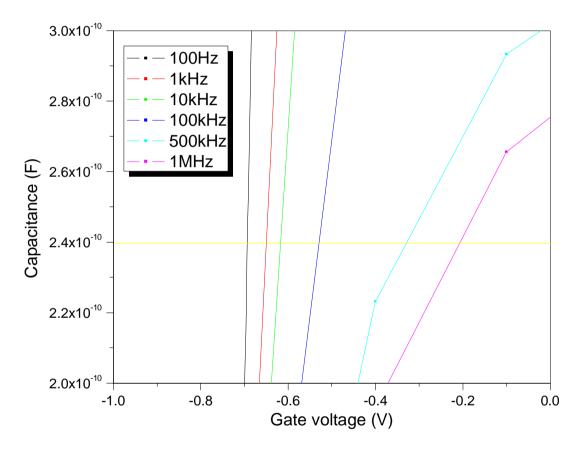

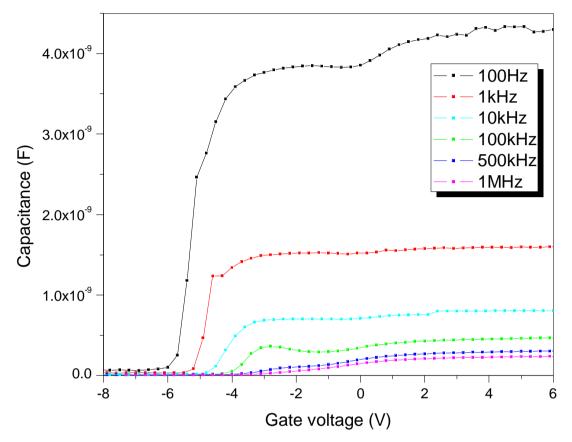

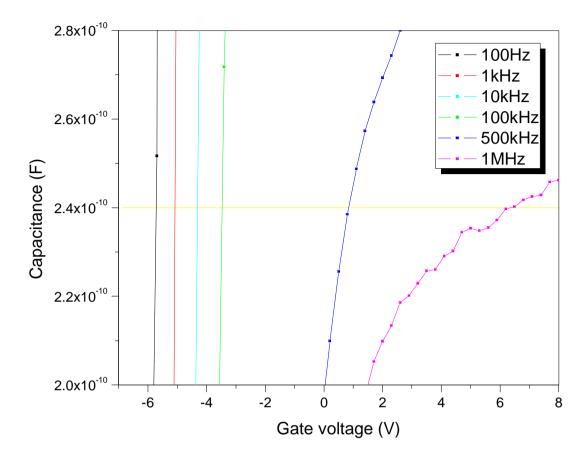

| Frequency dependency of CV measurement before and after irradiation | 152 |

|---------------------------------------------------------------------|-----|

| List of Figures                                                     | 156 |

| List of Tables                                                      | 161 |

| List of symbols                                                     | 162 |

| Bibliography                                                        | 164 |

| Acknowledgements                                                    | 169 |

## Abstract

The proposed International Linear Collider (ILC) together with the Large Hadron Collider (LHC) at CERN serve as a combined tool to explore the mysteries of the universe: the former is a precision machine and the latter can be considered as a finding machine. The key component of the ILC is the vertex detector that should be placed as close as possible to the Interaction Point (IP) and has better radiation tolerance against the dominant electron-positron pair production background from beam-beam interactions. A new generation of MOS-type Depleted-Field-Effect Transistor (MOSDEPFET) active pixel detectors has been proposed and developed by Semiconductor Labor Munich for Physics and for extraterrestrial Physics in order to meet the requirements of the vertex detector at the ILC.

Since all MOS devices are susceptible to ionizing radiation, the main topic is focused on the radiation hardness of detectors, by which a series of physical processes are analyzed: e.g. surface damage due to ionizing radiation as well as damage mechanisms and their associated radiation effects. As a consequence, the main part of this thesis consists of a large number of irradiation experiments and the corresponding discussions. Finally, radiation hardness of the detectors should be improved through a set of concluded experiences that are based on a series of analysis of the characteristic parameters using different measurement techniques. The feasibility of the MOSDEPFET-based vertex detector is, therefore, predicted at ILC.

# Kurzfassung

Um viele physikalischen Fragestellungen zu beantworten, wie. z.B. Higgs, SUSY and Extra Dimensions, usw., gibt es ein Standardmodel. Es hat sich bisher bewärt, jedoch bleiben einige Fragen (Higgs-Teilchen) noch offen. Diese Fragen können an einem zukünftigen Elektron-Positron-Linearbeschleuniger mit Energien von 500 bis etwa 1000 Milliarden Elektronenvolt werden. Der ILC könnte ungefähr im Jahr 2020 in Betrieb sein.

Eine wichtige Komponente des ILC ist ein Vertexdetektor, der sich um den Wechselwirkungspunkt befindet, wo Teilchen (Elektron und Positron) kollidieren. Mit dem Vertexdetektor können die Zefälle langlebiger Teilchen, wie B-Meson, rekonstruiert werden. Dies, und vieles andere, ist zur Rekonstruktion neuer Teilchen, wie dem Higgs, notwendig. Wegen der hohen Luminosität einer solchen Maschine, dem hohen Strahlungsuntergrund und der Nähe zum Wechselwirkungspunkt muss der Vetexdetektor hohen Anforderungen an die Strahlungsresistenz genügen. MOS-type Depleted-Field-Effect Transistor (MOSDEPFET) Aktive Pixel Detektoren stellen einen der besten Kandidaten für die Anwendung am Vertexdetektor im ILC dar. Diese DEPFETs wurden am Halbleiterlabor des Max-Planck-Instituts für Physik München entwickelt.

Wie alle MOS Strukturen leiden DEPFETs unter Oxidschädigung durch ionisierende Strahlung. Bisher erwiesen sich die am HLL gefertigten Strukturen als erstaunlich strahlungsresistent. Um dies genauer zu untersuchen wurden für diese Arbeit spezielle MOS Teststrukturen gefertigt, bestahlt und vermessen. Dazu wurden vor allem einige Messapparaturen für wie z.B., Strom-Spannung Messung (IV), Kapazitäts-Spannung Messung (CV) und Gated-Diode Messung entwickelt und aufgebaut. Die Messdaten wurden mit Literaturdaten verglichen und analysiert, darauf aufbauend konnte ein physikalisches Model entwickelt werden, um die Strahlenschädigungen simulieren und berechnen zu können. Zum Schluss konnten Vorschläge entwickelt werden um die Strahlenhärte der DEPFETs weiter zu verbessern, wie z.B., durch eine Reduzierung der Oxiddicke, oder Einhaltung einer bestimmten Biasbedingung an dem Gate-Kontakt (0V) und durch Produzierung einer zusätzlichen Nitrideschicht, usw. Der letzte Vorschlag war der wichtigste Punkt dieser Doktorarbeit, weil er die unerwarteten Eigenschaften der DEPFETs - eine kleine Threshold Spannung Verschiebung (ungefähr 4~5V) von DEPFETs, erklärt, welche laut Literatur wesentlich höher sein sollte. In dieser Arbeit wird nicht nur die Verwendbarkeit von MOSDEPFET am Vertexdetektor des ILC gezeigt, sie zeigt auch wie, mit einigen Verbesserungen des Designs und der Technologie diese Detektoren auch an Beschleunigern mit weit höherer Strahlenbelastung verwendet werden können.

# Introduction

In order to unravel the secrets of the universe, many central topics still remain unexplored such as Higgs mechanism, Supersymmetry and top quark etc., that are expected to come from the large collider experiments made with the Large Hadron Collider (LHC) and the International Linear Collider (ILC) at the TeV energy scale: the former is a proton-proton collider built at CERN and serves as a exploring machine; the latter is electron positron collider and will be a powerful tool to explore TeV-scale physics complementary to LHC offering the experimental data with high precision.

A great deal has been learned about silicon detectors during the last few decades. The choice of this detector material has received a lot of attention in high energy physics. To date silicon material is still the first choice among the many semiconductor materials as a detector material due to its wide availability and fast readout speed with small signal rise time in the range of a few nanoseconds as well as its processing possibilities. To achieve the detector requirement of high spatial resolution, a pixel detector can be used.

The DEPFET (Depleted-Field-Effect Transistor) [1] based pixel vertex detector is an advanced semiconductor detector. DEPFET provides the combined function of detector and amplifier simultaneously. A MOS or JFET (Junction-Field-Effect Transistor) is integrated onto a detector substrate. In comparison with other pixel detectors DEPFET pixels have much better spatial, energy and time resolution even at room temperature. In a DEPFET pixel using a row-by-row readout mode, the detector has low power consumption. Signal charges are stored in the pixel until readout and multiple read out is possible. An excellent noise performance is also an outstanding property of such a detector.

Within this thesis, a new generation of MOS-type DEPFET [2] active pixel detector will be described, which meets the requirement of a vertex detector at the ILC. Due to the dominant electron-positron-pair background from beam-beam interactions, the radiation hard detectors should be developed and improved. For this reason, the knowledge of the damage mechanism and its influence on the detector performance is required. As a consequence, this thesis is focused on the radiation damages (mainly about surface damage) of MOS-structure-based devices.

As irradiation source X-rays are mainly utilized. X-rays are a form of ionizing radiation. In addition, other irradiation environments such as results from gamma ray, proton and neutron will shortly be discussed.

Normally radiation damages can be categorized into two different types depending on location and mechanism: Bulk damages mainly take place in the silicon volume due to displacement of silicon lattice atoms; surface damages are generated due to the ionization at the silicon surface. Displacement damages are generated through non-ionizing energy loss (NIEL) and can be optimized by an appropriate choice of the type of silicon, whereas

surface damages can be controlled by the improved technological design of the detectors. For a long time a large amount of experimental data about bulk damages has already been collected from R&D programs for LHC, and several corresponding models were then also developed; radiation-induced effects like change of depletion voltage, leakage current and trapping time are parameterized with good precision. Although damage mechanism about surface damages and many impressive models are already well known, there is still not a series of complementary systematic model descriptions that provide predictions about radiation damage level in advance. It is therefore the goal of this thesis to find a set of characteristic surface parameters and the associated experimental methods for their proper determination with the intention to study radiation effects on detectors developed for particle physics experiments with respect to a specific process and design.

For this reason, the aim of this thesis is not only to describe a generation mechanism for surface damages, but also to study systematically radiation effects using a set of characteristic surface parameters and the corresponding experimental methods on MOS devices and, furthermore, to make a precise prediction about the applicability of the DEPFET-based pixel vertex detector for the proposed linear collider, and at the same time to find an improved detector design.

This thesis is structured as follows:

In the first chapter a general concept of the proposed ILC project will be described. The DEPFET-based pixel vertex detector and irradiation tolerance will be briefly introduced.

The second chapter explains the Metal-Oxide-Semiconductor (MOS) structure, which is mainly utilized in the irradiation experiments. The functionality of three different MOS devices will be discussed: MOS-capacitance, MOS-DEPFET and MOS-gated diode.

In Chapter 3, the damage mechanism of MOS structures will be introduced. Models for damage generation and recovery process will be analyzed.

In Chapter 4, different experimental techniques performed on the corresponding devices will be presented. Some characteristic parameters will be analyzed in detail.

In Chapter 5, irradiation experiments will be introduced. Different irradiation sources and experimental setups are described and detailed analysis before and after irradiation will be given.

In Chapter 6, the highlight of this thesis is focused on the radiation effects on MOS structures. Radiation hardness will be discussed depending on several factors. As a consequence optimization for radiation hard detector design can be achieved.

Finally, in the chapter 7, this thesis will be summarized and an outlook of a future design technology of detectors for ILC will be given.

# Chapter 1 Motivation

### 1.1 The Standard Model

Over the past few decades physicists have attempted to characterize the matter and energy of our universe – to understand the basic forces of nature and the components of matter.

In order to explain this mysterious nature, a large number of particle physics experiments have been performed to collect data in the past few decades. The emerging standard model [3] gives us the opportunity to describe the building blocks of matter and the fundamental interactions of particles. It is the most important basis of modern particle physics, and has received a great deal of experimental attention. According to the standard model, the matter is made up of a total of twelve fundamental particles (fermions) [4]: six quarks and six leptons. All of these particles can be divided up into three families, each containing two quarks and two leptons (see table 1.1).

| Fundamental Particles | Families          |               |              |

|-----------------------|-------------------|---------------|--------------|

| Quarks                | Up<br>O           | Charm         | Тор          |

|                       |                   | ~             |              |

|                       | Down              | Strange       | Bottom       |

|                       | ٩                 | ٩             | ٩            |

| Leptons               | Electron neutrino | Muon neutrino | Tau neutrino |

|                       | •                 | •             | •            |

|                       | Electron          | Muon          | Tau          |

|                       |                   |               |              |

Table 1.1 Fundamental particles: 6 Quarks and 6 Leptons.

In general, normal matter (inclusive stellar materials) is made up of particles that come only from the first family, i.e., up and down quarks buildup the atomic nuclei and the electrons (one of the important leptons to date) contribute to the atomic construction. The other two families in this table can not be found in stable matter, but they can be recreated from intensive energy, e.g., cosmic rays or particle accelerators and they do not exist in a stable form of matter. Each of the twelve particles has corresponding antiparticles such as the antiparticle of the electron is the positron. Although particles and antiparticles have opposite electrical charges, they are actually very similar. If they interact with each other, they will annihilate one another and create radiation. In addition to the fundamental particles, the standard model also describes three of four known fundamental interactions between the fundamental particles and makes precise predictions about the behavior of these interactions. A concise theoretical framework for the forces between these fundamental particles has been developed based on the theoretical principle of gauge invariance [5], by which Quantum Chromo Dynamics (QCD) [5] can describe very well the strong interaction that includes color-charged particles (quarks) and gluons. In addition, the electromagnetic and weak interaction can also be unified into a combined electroweak interaction that introduces a photonmediated electromagnetic interaction and  $Z/W^{+/-}$  bosons as the force mediating weak interaction. However, according to gauge principle all force-mediating particles should have no mass. This is contrary to the large mass of the W and Z bosons. For this reason, the Higgs-mechanism [5] as well as the Higgs field and particle are proposed to solve this problem, by which particles are given a mass through their interaction with the background medium - the Higgs field. The Higgs mechanism is a good model for the mass of W and Z. Fermion's masses are put by hand into the Lagrange formula [57]. A full study of the Higgs boson coupling consists of the determination of the top-quark Yukawa coupling, and of the Higgs self-coupling [57].

Despite providing an accurate description of nature by this model, there are still some unsolved physics problems. For instance: Why do different particles have different masses? By which mechanism do particles acquire mass? Although the Higgs mechanism seems to offer a solution to give particles masses, to date no experiment has directly detected the existence of the Higgs boson. Therefore, to find the Higgs particle is a challenging task of particle physics. On the other hand, there are further mysteries such as the hierarchy problem [6] and agreement of cosmology with the standard model of particle physics. For example, why is there a matter/antimatter asymmetry? The fourth fundamental interaction 'gravitation' is not included in the standard model. Meanwhile, research has already been focused on the Grand Unified Theory (GUT), in order to unify all fundamental particle interactions at large energy. The proposed Supersymmetry (SUSY) is the most popular concept. The answer to these deficiencies implies that there is new physics beyond the standard model which will hopefully be discovered at the next generation of particle accelerators.

One of them is the LHC (already finished this year), which is circular proton-proton collider with a centre of mass energy of 14 TeV. Proton collisions are mainly for two large experiments – A Toroidal LHC AparatuS (ATLAS) and Compact Muon Solenoid (CMS) – and a small experiment LHCb. In addition, a modus for heavy ion (lead ion) collision is also included. ATLAS and CMS are multipurpose experiments. Their goal is to identify the elementary particles, e.g. discover the Higgs boson and eventually SUSY particles if they really exist. The study of CP-violation in the B-system is specially made with LHCb. Quark-Gluon-Plasma is generated and investigated with heavy ion collision by ALICE.

Protons are easier to accelerate than electrons in a circular medium to a high energy (proton synchrotron), since electron acceleration is limited by the losses of synchrotron radiation. During collision a large number of new particles can be created. Although LHC

tries to look for and find them, it is still difficult to measure their properties with high precision, because the protons consist of many quarks, antiquarks and gluons and a large amount of fraction bursts out in all directions from the collision. The detailed collision processes cannot be well controlled or selected and the background, due to unexpected collision processes, is really high. For this reason, the International Linear Collider (ILC) can be considered as an ideal complement of LHC, ILC is a global project and could be constructed in the next decade. The proposed ILC will provide a variety of particle physics experiments in the future, and extend discoveries.

Detectors for collider machines should be optimized for physics precision in respect of their special environment. Therefore, detectors should be hermetic, with a good charge tracking system for following the charged particles after collision (momentum, energy and charge of produced particles with high precision). Therefore the tracking part of the detector system should be placed as close as possible to the interaction point and as a consequence, the vertex tracking may provide the jet flavor identification and accurate track reconstruction and excellent impact parameter resolution. The muon and hadron's calorimeter have to provide good resolution and granularity, especially in the electromagnetic section.

In addition, the Mont Carlo computer simulation is an important method used in particle physics experiments to design detectors and to understand their behavior and compare experimental data with theory.

### 1.2 ILC Project

At present many hot topics have received a great deal of attention and many driving physics questions are waiting to be answered about the Terascale in the micro-universe (the first two of the following) and in the macro-universe (the third one):

- Electroweak symmetry breaking

- Higgs particle

- Ultimate unification of forces

- Supersymmetry or extra space dimensions (> 4)

- ∨ Connection between particle physics and cosmology

- o Determination of the nature of cold dark matter particles

In order to unravel these mysteries of nature, particle physicists have concentrated their attention on particle accelerators. ILC is a huge linear accelerator, in which electrons and

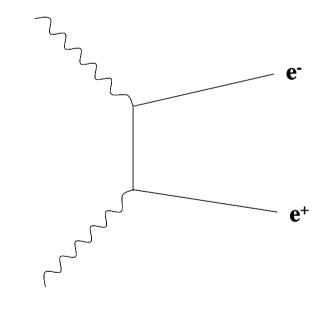

positrons collide (Figure 1.1), whose energy is within the range of 0.5 to 1 TeV. Electrons and positrons come from opposite directions through the beam pipe in the detector. After the collision in the central point, two particles are annihilated and turn completely into energy, and new particles are generated. Since it is known more precisely about the initial conditions of particle production and there is also no remnant from collision partners (electron and positron), the results are simpler to explain than in the case of proton collision. In addition, due to the clear elementary process with less spurious interactions (background) there are more advantages of electron-positron collisions than proton-proton collisions. For this reason, LHC is a detection machine, and ILC is a precision machine. With ILC, one can measure more precisely the features of new particles, such as mass, lifetime, spin and quantum number.

Figure 1.1 Electron positron collision [64].

LHC is already in progress. The realization and construction of such a facility for ILC is still not confirmed. However, in any case physics needs both – precision of ILC and energy of LHC.

#### **1.2.1 Linear collider**

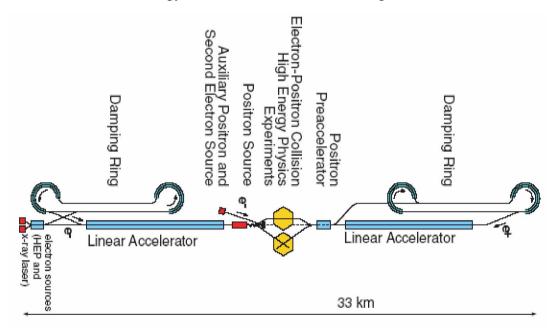

In principle, there are two main concepts responsible for the realization of acceleration of a collider machine: the circular accelerator (circle) and the linear accelerator (straight line). The advantage of circular over linear is that in a circular medium, the beam is recycled and the circular accelerator is relatively smaller than a linear accelerator of comparable energy. However, the linear concept is mainly used for the design because energy loss in the circular ring accelerator (Figure 1.2), the two particles are located at two different sites and are accelerated in a straight line until they collide with each other. In this case there is no energy loss because there is no bending section.

Figure 1.2 Schematical overview of TESLA facility with linear accelerator [5].

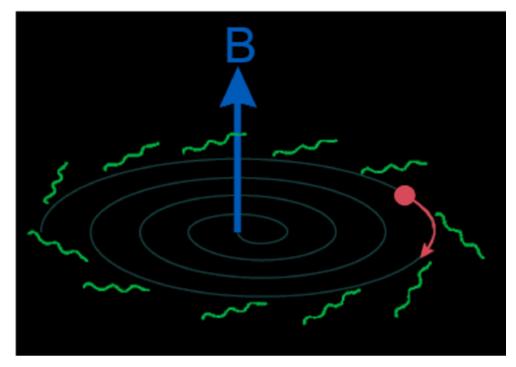

Taking into account the energy loss [7] due to the synchrotron radiation emitted by a charged particle that is accelerated on a circular ring (Figure 1.3), the following is given:

$$\Delta E \propto \frac{E^4}{R} \tag{1.1}$$

Figure 1.3 Charged particle is forced on a circular accelerator.

Where R is the radius of the circular ring. Observing the energy range and dimensions of the LEP collider at CERN, which stopped operating at the end of 2000, a list of parameters of the synchrotron radiations of a circular accelerator are shown in following Table 1.2 below.

|            | LEP II | Super LEP | Hyper LEP |

|------------|--------|-----------|-----------|

| ECMS (GeV) | 180    | 500       | 2000      |

| L (km)     | 27     | 200       | 3200      |

| E (GeV)    | 1.5    | 15        | 240       |

Table 1.2 Energy losses due to synchrotron radiation for different circular accelerator configurations [5].

In general, the energy losses are not so relevant for heavy particles in the high-energy region, e.g., protons. However, they can reach to about 10% per revolution for center of mass energy in the range of TeV and a radius of a million meters for electrons. From the economic point of view, this circular accelerator is not worth operating. For this reason, a linear accelerator should be operated instead of a circular one.

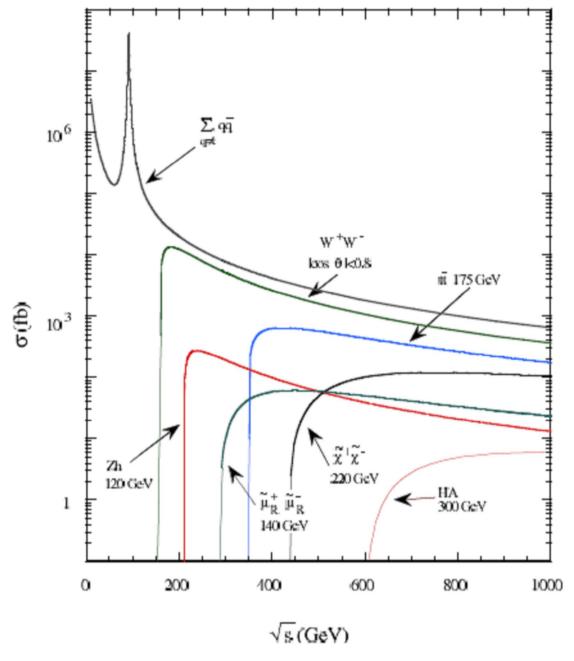

In the case of a linear accelerator, two important aspects have to be taken into account: the center of mass energy and luminosity. In order to meet the requirement of energy, the acceleration gradient should be much higher than that of a circular one. In addition, Figure 1.4 below shows a series of theoretical cross section for electron-positron annihilation processes with the center of mass energies up to 1 TeV. In case the collider is operated at high energies, the cross section is reduced. Since the expected event rate is

determined by both the luminosity and cross section, the luminosity of the beam must be increased to achieve a sufficient event rate.

Figure 1.4 Expected cross section for selected electron-positron annihilation processes depending on the center of mass energy of the collider [8]

There have been many proposals [9] for such a machine with respect to this worldwide global project that can be distinguished by the selection of acceleration technology. After an intensive survey by an expert group (International Technology Recommendation Panel – ITRP) the superconducting RF technology for the acceleration of electrons and

positrons was chosen for the future linear collider, since then a further step towards the realization of the ILC was taken in 2004. Superconductivity technology offers zero resistance to electric current. In other words, there is no energy loss during current flow. This technology can be achieved with the superconducting material niobium at very low temperatures instead of copper structures that operate at room temperature. Thus, much better energy efficiency is achieved.

The ILC accelerator will be constructed according to this acceleration structure, which was initially proposed by the DESY in Hamburg and the TESLA (TeV Energy Superconducting Linear Accelerator) [18] technology collaboration. In the following the TESLA accelerator will be shortly introduced. A comprehensive overview of this project can be found in the TESLA Technical Design Report [10]. TESLA should include two facilities: one of them is the 33-km-long linear accelerator for particle physics that is used for the ILC project; it consists of electron and positron sources, and will be constructed for the first phase of the linear collider at 500 GeV in the center of mass. It will be extended in a second phase to 800 GeV or even more of course depending on the acceleratory [11] that is operated as a Free Electron Laser (FEL) and will be constructed to provide coherent X-ray. Both of them are completely separated and are used as independent projects.

### **1.2.2** Detector concept for the international linear collider

Detector should have an excellent performance to fully exploit the physics potential at ILC. As mentioned previously, ILC is considered to be a precision machine that can measure the standard model physics processes near the electroweak energy scale and probably could find new physics beyond it. In order to take full advantage of the physics potential of the ILC, the performance of the detector components has to be optimized with respect to its special environment.

The detector at ILC should be significantly better than those at LEP and SLC accelerators. The most important requirements for the detector are summarized in the following [12]:

- ∨ Good charged track momentum

- ∨ Excellent vertex resolution for efficient b- and c-tagging

- ∨ Efficient track reconstruction in an multi-jet environment

- ✓ Good resolution provided by high granularity in the calorimeters and particular in the electromagnetic section, efficient electron and muon identification

- ✓ Hermeticity and particle-detection capabilities in the forward direction, since missing energy is the main expected signature for the characterization of SUSY and for other process of interest.

- ∨ Compatibility with a triggerless operation for maximal efficiency

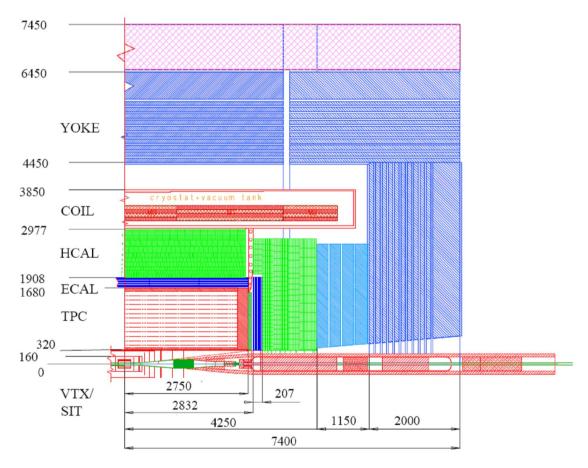

At present there are three main detector concepts plus one: Large Detector Concept (LDC) from TESLA detector groups in Europe, the Silicon Detector Concept (SiD) from the US and Global Large Detector (GLD) from Asia; the fourth concept is still in progress. Figure 1.5 shows a schematic cross section through a typical detector. The main tracker in the center part of the detector is made up of a combined tracking system – Vertex Detector (VTX) / Intermediate Tracker (SIT) and Central Tracker (TPC).

Figure 1.5 Schematic layout of a quadrant of the TESLA detector. All dimensions are in mm [12].

An electromagnetic calorimeter (ECAL) and a hadronic calorimeter (HCAL) are located direct outside of them. The magnetic field of 2-4 T provided by a coil helps to measure the momentum of charged particles and to further limit the beam-related background. With increasing field, the pair production background in the vertex detector is further reduced and the momentum measurement is improved by the tracking (providing a better resolution). It is worth having the electromagnetic calorimeter and part of the hadronic

calorimeter inside the coil to reduce the amount of the material for the detector taking consideration of the extra cost. Here the iron is used as a magnetic return yoke (muon chamber) and also as a tail catcher for hadronic showers outside HCAL. Resistive plate chambers (RPC) [13] are chosen as a choice for the detector technology. It is worth mentioning that the advantages of standalone track reconstruction are internal alignment optimization and reduction of track ambiguity.

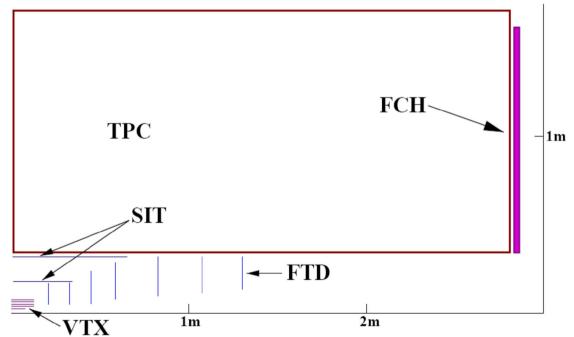

In the following it will be discussed how these various components are optimized. As shown in Figure 1.6 a multilayer vertex detector is located as close as possible around the interaction point (IP) in the innermost part of the tracking system in order to provide an excellent impact parameter resolution. An efficient vertex detection has become the physics goal of the ILC. The physics signals are rich in secondary vertices, and event rates are limited; for this reason, the vertex detector is mainly optimized to reconstruct secondary vertices by b- and c-tagging to identify multi-b final states like ZHH and  $t\bar{t}H$  and to separate  $H \rightarrow c\bar{c}$  events from  $H \rightarrow b\bar{b}$  decay. In addition to good impact parameter resolution the vertex detector can also provide an efficient momentum measurement. More requirements of vertex detector will be discussed in the next section in detail. Two additional layers of the silicon tracking detector (Silicon Intermediate Tracker - SIT), consisting of cylinders in the barrel, are placed between the vertex detector and the TPC to further optimize the momentum resolution of the tracking system. Seven discs in the forward region are laterally mounted along the beam pipe, since the combined vertex detector and TPC resolution degrades at low polar angle due to a shorter projected track length and additional information given by these discs makes momentum measurements more precisely. In addition, the discs can also improve the polar angle resolution in this area. The first three layers of this system that are closest to the IP are made up of active pixel sensors, and the outer four are silicon strip detectors.

Figure 1.6 Schematic layout of the tracking system of the TESLA detector [12].

A large Time Projection Chamber (TPC) – a gaseous chamber with readout at the side via a fine segmented endplate is chosen as the central tracking device since it has many advantages compared to other techniques. The TPC provides good momentum resolution due to the large radius of the central tracker and a large number of precise spatial point measurements along the track can offer efficient pattern recognition even in a dense track environment. The TPC can enable good particle identification by measuring the specific energy loss of the charged particles. At last a TPC is easy to maintain since the endplate is divided up into small parts, which can be replaced and serviced if necessary.

A precise forward chamber is placed behind the TPC endplate (FCH) to compensate for the degraded track reconstruction performance of the TPC in the forward direction. In addition, it can also improve the momentum resolution in that region and assist the TPC in the pattern recognition. It is worth noting that the tracking system can provide an excellent momentum resolution of  $\Delta(1/p) = 5 \times 10^{-5} (GeV/c)^{-1}(1/10 \text{ of LHC/LEP})$  in the central region [10].

As noted to meet the requirement at ILC, a detector capable of precision measurements is required. In order to fully exploit the clean experiment conditions of ILC, the detector must have the ability to present a complete picture of the newly produced particles as possible, e.g., for charged particles this is done by the tracker. How about the energy they achieve after collision? These considerations require a calorimeter with excellent performance and many important requirements, i.e., calorimeters must be significantly better in their features than the already existing identification device. For instance, in order to distinguish nearby flying particles, the calorimeters are used to measure the energy of charged and neutral particles. Longitudinal and lateral segmentation enables the location of the energy deposition and makes it possible to identify not only electromagnetic and hadronic components of the showers produced by the particles but also muons. In addition, calorimeters can also be used for measuring missing energy, the characteristic signature of SUSY particles and of neutrinos.

#### **1.2.3 DEPFET-based vertex detector for ILC experiment**

As mentioned above the vertex detector in ILC experiments is located as close as possible to the interaction point. The physics motivation and requirement for the vertex detector will be dealt with in detail in the following section. Finally a proposal for MOSDEPFETbased vertex detector at ILC will be given.

Firstly the ILC needs a vertex detector with unprecedented precision that should allow efficient and good flavor identification and separation, for measuring branching ratios  $H \rightarrow b\bar{b}, c\bar{c}, gg, \tau^+\tau^-$ , SUSY Higgs searches such as  $A \rightarrow \tau^+\tau^-$ , searches for staus, top studies. It is also important to identify charm quarks for a complete reconstruction of

the kinematics, e.g., in the process  $e^+e^- \rightarrow W^+W^- \rightarrow csl^-\nu$ . In addition, physics requires an efficient b and c tagging including charge determination in a wide range of  $\cos(\theta)$ .

The average impact parameter of tracks of a B decay product is approximately 300 micrometers, which suggests that modest detector performance may suffice. However, this is misleading for several reasons: First of all, the average impact parameters for tau and charm particle decay products are 3–4 times smaller. In addition, improved detector systems based on the experience from LEP and SLD allow a correct assignment of all tracks to primary, secondary or tertiary vertices in order to determine the vertex mass and charge that could allow improved b/c separation and allow to separate between quark and anti quark like b or  $\bar{b}$  and c or  $\bar{c}$ .

In vertex detectors, better tagging efficiency of the jet flavor is achieved by better spatial resolution and tracking efficiency. Vertex reconstruction is performed by extrapolating tracks measured by several layers of the detectors. In order to get a better vertex resolution and flavor tagging efficiency, the vertex detector should meet the following requirements:

- The length of the extrapolation should be as short as possible, i.e., the innermost layer should be as close to the interaction point as possible.

- In order to minimize the effect of multiple scattering, the thickness of the detector and supporting substrate should be as thin as possible, by which no cooling system should be required and material can also be saved.

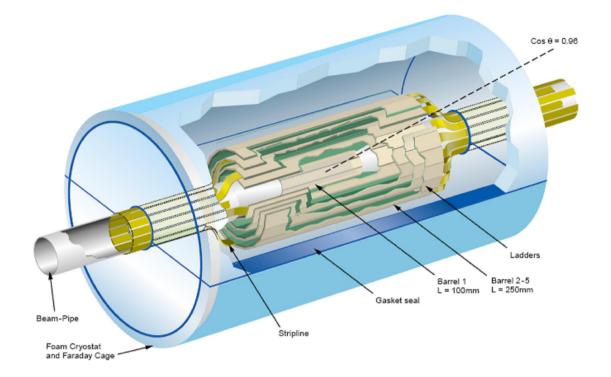

According to TESLA TDR design the vertex detector would consist of nested low-mass spherical shells positioning at five different radii of a few centimeters (Figure 1.7); in every layer there is a set of detectors arranged in ladders designed in a cylindrical form. Each ladder is an array of pixel cells with readout system located at the end of ladder outside the sensitive volume and extends in length to cover a polar angle range of  $|\cos \theta| \le 0.96$  for layer 1 and 2 and  $|\cos \theta| \le 0.9$  for layer 3–5.

Figure 1.7 General layout of the vertex detector at ILC [16].

The impact parameter resolution is the key parameter of the vertex detector that is required separately in  $r\phi$  and rz projections [17]. For a set of cylindrical detectors, this impact parameter resolution can be expressed as:

$$\sigma = \sqrt{a^2 + \left(\frac{b}{p\sin^{\frac{3}{2}}\theta}\right)^2}$$

(1.2)

Where the constant *a* depends on the point resolution and geometrical stability of the detectors and *b* represents the resolution degradation due to multiple scattering, which changes with track momentum p and polar angle  $\theta$ .

The impact parameter resolution to be reached is  $\sigma(IP_{r\phi,z}) = 5\mu m \oplus \frac{10\mu m \, GeV/c}{p \times \sin^{3/2} \theta}$ . The

innermost layer of this five-layer-type vertex detector, right outside the beam pipe, should be at a radius of 15mm and have a length in z of  $\pm$  50mm. A summary of the radii and dimensions of all five layers can be found in Table 1.3.

| Layer | Number of | Radius | Ladder length  | width |

|-------|-----------|--------|----------------|-------|

|       | ladders   | (mm)   | (mm)           | (mm)  |

| 1     | 8         | 15.0   | 100            | 13    |

| 2     | 8         | 26.0   | $2 \times 125$ | 22    |

| 3     | 12        | 37.0   | $2 \times 125$ | 22    |

| 4     | 16        | 48.0   | $2 \times 125$ | 22    |

| 5     | 20        | 60.0   | $2 \times 125$ | 22    |

Table 1.3 General geometrical parameters of the MOSDEPFET-based vertex detector at ILC [61].

In addition to impact parameter resolution the detector should also have stand-alone pattern recognition and tracking capabilities for the reconstruction of tracks with low momentum. In order to achieve the desirable resolution especially at low momenta, a point resolution of less than four micrometers is required and the requirement on the material budget of a detector layer with a radiation length of less than 0.1% should also be met.

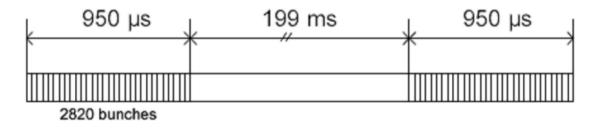

Taking into account Equation 1.2, the impact parameter resolution is determined by both the point resolution and the detector layout. The detector technology and the radius of the innermost detector layer are controlled by the expected occupancies. These are due to both the track density in jets and time structure and the background conditions of the accelerator. With respect to the time structure of the ILC beam (shown in Figure 1.8) [9], 2820 bunch are delivered within 950 microseconds with a corresponding bunch interval of 337 ns followed by a long gap of 199 ms. It is impossible to read out a full frame of a pixel sensor within a bunch spacing without integrating several bunch crossings for the detector. Without compromising pattern recognition and track reconstruction the amount of the integrated bunch crossings depends on the beam associated background.

Figure 1.8 Time structure of the ILC accelerator [9].

Normally the background for  $e^+ e^-$  colliders is relatively low compared to hadron colliders; however, the detector at ILC will be confronted with a considerably higher background environment than that at LEP or SLC. This higher background arises mainly

from beam-beam interactions  $(e^+, e^- \text{ and } \gamma)$ , synchrotron radiation and from muon and neutron sources. Particles from beam-beam interactions generated at the IP that cannot be shielded from the detector volume are responsible for much of the background in the detector. In principle, the beam-beam interaction leads to two main experimental consequences: Firstly, the energy distribution will be widened because of the emission of photons by a beam in the field of the oncoming beam; secondly, the subsequent background is produced by interactions of those photons. Below various physics process for the beam-beam interaction will be discussed:

- Pair production through the interaction of a photon with the collective field of the oncoming beam is called coherent  $e^+ e^-$  pair production [14]. In case of ILC detector, this contribution is of no importance.

- Pair production via the interaction with the field of an individual particle is called incoherent  $e^+ e^-$  pair production [16]. The following three processes are the main source of background at the present generation of LC

- The Breit-Wheeler process (  $e^+e^-$ ) describes the interaction of two real photons

• The Bethe-Heitler process  $(e^{\pm} e^{\pm}e^{-})$  – describes the interaction of one real and one virtual photon

• The Landau-Lifschitz process  $(e^+e^- e^+e^-e^+e^-)$  – describes the interaction of two virtual photons

The dominant  $e^+ e^-$  pair background from the beam-beam interaction is confined with a small radius by the high magnetic field of 4T. For this reason, a strong peak for the background rate is found close to the IP and then it falls rapidly in layer 2-5. The beam pipe radius of the collider machine is set at 1.5cm. The pair background in layer-1 right outside the beam-pipe produces a hit density of 0.03 (0.05) hits per BX and mm<sup>2</sup> for  $\sqrt{s} = 500 (800) GeV$  [12].

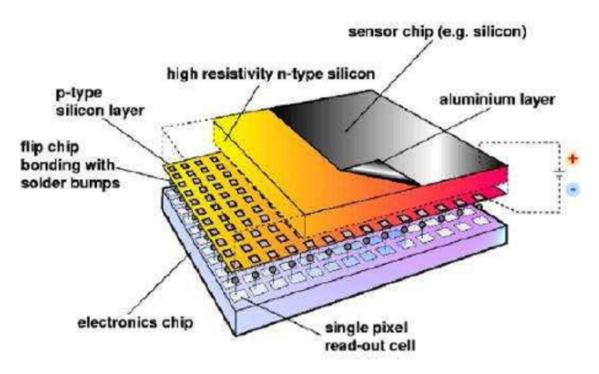

In order to meet the requirement set by the ILC environment, a proposal using DEPFET – an active pixel sensor with an integrated amplification – is made. The basic principle of such a structure is the integration of amplifying FET transistors into a fully depleted bulk in such a way that all signal charges are collected in the 'internal gates' of the transistors

(see next chapter for details). The key features of this structure, which make it an ideal candidate for the vertex detector at ILC, are summarized as follows:

- Low pixel size ~ 20-30µm

- Fast collection of large signal

- Charge collection arises from the fully depleted bulk

- Low noise through small capacitance (several 10 fF) of the internal gate

- High frame readout rate ~ 20kHz

- Charge generation and first amplification in a fully depleted FET

à Good Signal/Noise (40:1)

• No charge transfer needed (unlike in a Charge Coupled Detector (CCD))

à Radiation hardness against hadron irradiation

• Thinner detector of ~ 50  $\mu$ m using thinner technology (HLL)<sup>\*</sup>

à Less material ~  $0.1 \% X_0$  each layer

• Charge collection in "OFF" state, only one row active during readout:

à Low power consumption

• Production technology completely under the control of detector designers and physicists

To date, no show limits are known with respect to DEPFET – only its many advantages; for this reason it could compete with other alternative candidates – like Charged Coupled Devices (CCD), CMOS Monolithic Active Pixel Sensors (MAPS) and Hybrid Active Pixel Sensors (HAPS) – for the vertex detector at ILC. Each has its own disadvantages: CCD may be limited by the radiation tolerance and higher readout speed; CMOS sensor (MAPS) cannot be produced in large area devices; the layer thickness and power consumption of HAPS is too high.

#### HLL: Semiconductor labor Munich

### **1.3** Irradiation Tolerance

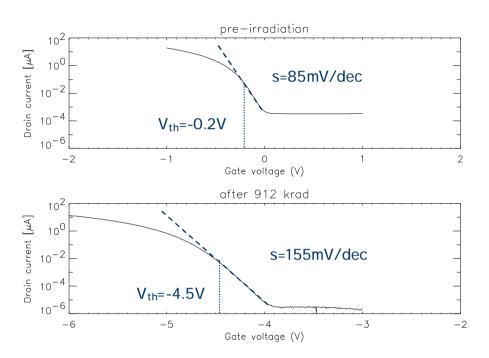

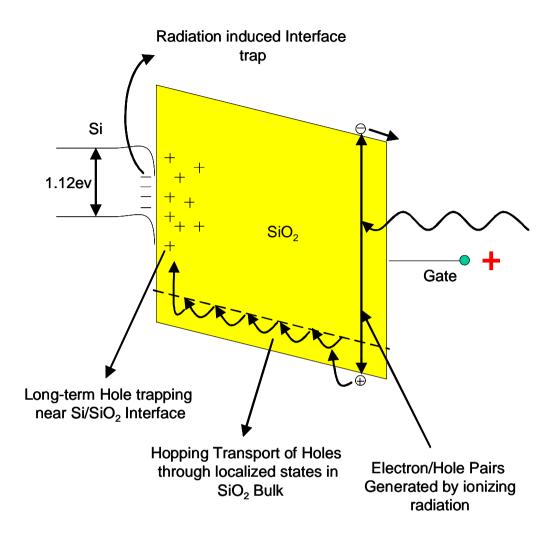

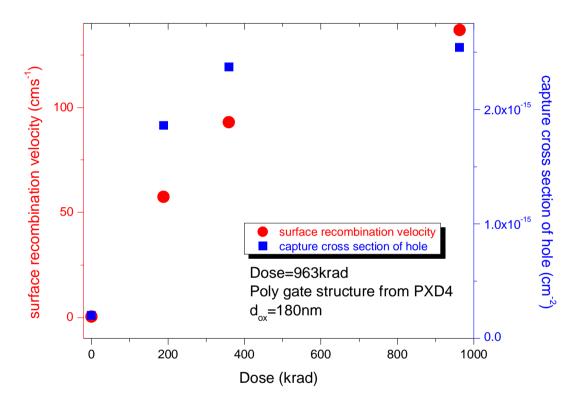

Due to the high background the question should be considered for radiation damage to the DEPFET-based vertex detector at ILC. Therefore, a requirement of radiation hardness of about 100 krad for a 5-year life time is needed [2]. Since such detectors are produced by MOS technology and almost all of the MOS devices are sensitive to ionizing radiation, damages will be generated in the oxide and interface between silicon and  $SiO_2$  and play an important role on the MOS-structure-based devices. The main total ionizing dose effects are summarized as follows:

- ✓ The threshold voltage shift (due to radiation-induced positive oxide charges)

- $\vee$  The increased subthreshold slope

- ∨ A higher low-frequency noise (due to interface traps generated between Si/SiO<sub>2</sub>)

- ✓ The degradation of the transconductance (due to a lower mobility of the charge carriers in the channel after irradiation)

On the other hand, unlike the background at LHC, bulk damage due to NIEL (Non Ionizing Energy Loss) at ILC is arising from the neutron background, which is estimated to be at the level of  $10^9$  /cm<sup>2</sup> (1MeV-neutrons) per year. It is not so relevant for the DEPFET-based vertex detector, since there is no charge transfer (charge trapping) during the operation of DEPFET matrices. However, with increasing doses from proton or neutron sources, radiation damages will be generated in the silicon bulk volume that affect the performance of MOS devices. These bulk damages result in leakage current, which leads to a higher noise. As a consequence, a radiation tolerance against proton or neutron sources is limited to an order of magnitude of  $10^{12}$  /cm<sup>2</sup>.

Depending on different technologies (e.g. improved oxide processing) and irradiation conditions, the degradation of MOSDEPFET transistors is characterized by a series of parameters and experimental methods.

In order to study the radiation hardness of the detectors, several MOS test devices were constructed and irradiated.

### **1.4 Silicon detectors**

A silicon detector is a device that uses a silicon diode operated under reverse bias to detect traversing charged particles or the absorption of photons, where the depleted zone of the silicon diode acts as a solid ionization chamber. Silicon detectors have found many applications, especially for X-ray spectroscopy and as particle detectors in high-energy physics. The passing ionizing particles ionize the silicon atoms and, therefore, create numerous electron-hole pairs along their track, which will drift to the electrodes following the electric field in the depletion zone. A minimum ionizing particle (MIP) traversing a silicon layer will create about 80 electron-hole pairs per micrometer, since the required average energy to produce an electron-hole pair is about 3.6 eV. It is about 30 eV for gases. The resulting signal can be detected by a charge sensitive amplifier. The output is proportional to the overall generated charges in the detector if the detector is fully depleted.

A comparison with other detector materials (gas detector or scintillation detector) shows that silicon is still the best choice of material for tracking purposes. On the one hand, silicon detectors have much higher density (Silicon: 2.33 g/cm<sup>2</sup>) than gas detectors; on the other hand, their intrinsic energy resolution is much better than the scintillation detectors.

Interaction of charged particles with detector materials takes place by electromagnetic interaction with the electrons of the atom shell. Two processes are generally used to identify the particles:

- Excitation

- Excitation of the atoms and molecules of the detector materials through charged particles à fall-back to ground state à emission of light à changing of light into electric signal (identification through e.g. Photomultiplier or Avalanche Photo Diodes)

- Ionization

- Ionization of detector materials through charged particles à generation of free charge carriers à charge collection to the electrodes through a electric field à electric amplification through charge sensitive amplifier à registration of signals (identification through silicon detectors e.g. strip detector or pixel detector)

The energy loss for charged particles traversing materials is given by the Bethe-Bloch formula with respect to heavy particles [59]:

$$-\frac{dE}{dx} = \frac{4\pi z^2 e^4 nZ}{m\beta^2 c^2} \left( \ln \left[ \frac{2m\beta^2 c^2}{I} \gamma^2 \right] - \beta^2 - \frac{\delta}{2} \right)$$

(1.3)

With

- *m* : rest mass of electrons

- $\beta := v/c$  relativistic velocity of particles

- $\gamma := (1 \beta^2)^{-1/2}$  Lorenz factor

- *z e* : electric charge of particles

- *Z* : atomic number of materials

- *n* : atom number per unit volume

- $= \rho A_0 / A$ ;  $A_0$ : Avogadro-number; A : atom mass,  $\rho$  : matter density

- $\delta$ : density parameter

- *I* : characteristic ionization constant

The energy loss for electrons or positrons by interaction with materials is proportional with energy [59]:

$$-\frac{dE}{dx} = \frac{E}{X_0} \tag{1.4}$$

With  $X_0$ : radiation length.

According to requirements of application areas, a highly precise measurement of particle energy is required and performed by a better proportionality of generated charges with deposed energy (X-ray spectroscopy). The main concern of high-energy physics is fast particle readout and high position resolution. A single PN-junction can be used for detection of an ionizing particle but cannot provide any position information about the particles track. For this reason it is necessary to segment the diode into an array of smaller individual PN-junctions. Depending on the type of segmentation of detector electrodes they can be classified into strip and pixel detectors, which can be produced by modern planar technology.

• Strip detectors: a type of detector based on a segmentation of the  $p^+/n^+$ implantation into a periodic arrangement of strips. Typical dimension of the strip length is several centimeters whereas the pitch is several tens of micrometers. Normally strip detectors provide information about only one dimension position of particle track. The spatial resolution can be determined by  $pitch/\sqrt{12}$  for binary readout. In order to obtain the second dimension, it is necessary to pattern the backside of detectors into the strips as shown in Figure 1.9. The disadvantage of a double-side strip detector is the presence of ambiguities if two or more particles pass the detector simultaneously. In addition, insulation problem should also be taken into account between each  $n^+n$  strip from its neighbors for double-side strip detectors. Typical solutions against this problem are p-spray technique or p-implantation between every  $n^+n$  strip.

Figure 1.9. Layout of a two-dimension silicon micro strip detector [62].

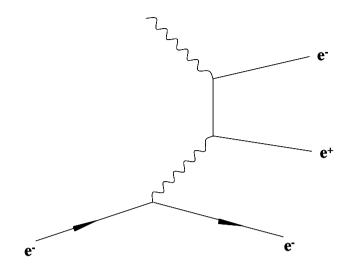

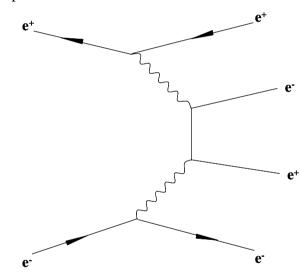

• Pixel detectors: a detector produced by segmenting p<sup>+</sup> implantation of the strip detector into an array of diodes (Figure 1.10). Pixel detectors can provide a two-dimensional localization of particle track without ambiguities like double-side strip detectors.

Figure 1.10. Layout of a pixel detector [63].

## Chapter 2 MOS Structure

For a long time, silicon has been widely used as material in semiconductor devices. Moreover, Metal-Oxide-Semiconductor (MOS) structures became the most important component in silicon semiconductor devices, e.g. MOSCCD, MOSFET, CMOS, and so on. Study on the radiation damage of MOS-Structure under different radiation sources has received extensive attention in the past few years in order to understand the radiation-induced performance degradation of silicon devices. A great deal of effort has been made to correlate the changes in the electrical properties of irradiated silicon devices with the type and dose of irradiation. At the same time the widely used silicon detector in High Energy Physics (HEP) experiments has implied that there is a close relationship between fundamental study and technology development. A detailed analysis of radiation damage correlated with fundamental material research needs to be given in the irradiated silicon detector. Accordingly, anticipated improvement of radiation damage for future HEP experiments will be achieved through improved technological development and optimized detector design.

#### 2.1 MOS DEPFET

The metal oxide semiconductor depleted field-effect transistor (MOSDEPFET) is one type of field-effect transistors. Principally it can be distinguished from the depletion field-effect transistor (JFET) and metal oxide semiconductor field-effect transistor (MOSFET). The highlight of DEPFET is the quite small input capacitance of only a few tens of fF, and from the point of view of functionality it simultaneously has detector and amplification properties. In the following chapter more details about MOSDEPFET will be presented.

#### 2.1.1 Definition of a MOSDEPFET

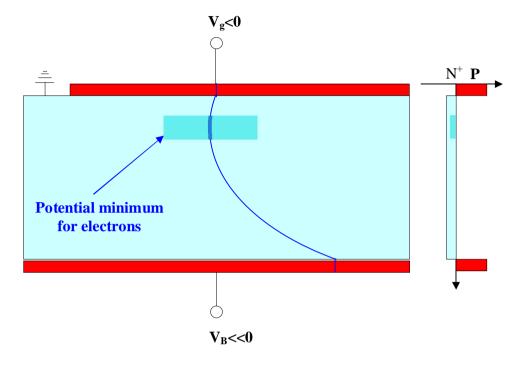

The depleted field-effect transistor (DEPFET) was proposed in 1987 by Kemmer and Lutz [19], and experimentally confirmed by Kemmer et al. in 1990. MOS-type DEPFET offers a solution to combine depleted silicon volume and amplification level (MOSFET). These substrates are depleted by means of sideward depletion [20]. The principle of sideward depletion is represented in Figure 2.1 below. This structure is not a single PN diode, but a combination of two PN diodes contacted with each other by the same doping side to form a PNP or NPN sandwich. Considering PNP structure, if a small negative voltage is applied to both P-contact with respect to substrate (here N side in between),

there are two space charge regions generated and separated by the conducting undeleted bulk region (here N volume); in the case of higher voltage, the device volume is depleted from both sides of the PN diodes.

Figure 2.1 Principle of sideward depletion and distribution of doping and potential in the substrate.

When two unequal negative voltages are applied on both sides, under fully depletion a potential minimum for electrons is created assisted by an additional deep n implantation right below the gate contact (shown in the above Figure marked with sky blue), which is parallel to the front side. This potential minimum is for majority carriers: electrons in n-type silicon.

In order to analyze the behavior of MOSDEPFET, it is necessary to firstly consider a normal MOSFET that contains three terminals: Gate, Source and Drain. If the MOSFET is an n-channel MOSFET, then the source and drain are n+ regions and the substrate material is a P region. In case the gate voltage is above a threshold voltage value, electrons from the source and drain will enter the inversion layer at the interface between the P region and the oxide to form the conduction channel. If the gate voltage is below the threshold value ( $V_{GS}$ < $V_{th}$ ), there is only a very small subthreshold current flowing between the source and the drain. This region is called the cut-off.

The transistor is turned on and behaves like a resistor, which can be controlled by the gate voltage to the source, if  $V_{GS} > V_{th}$  and  $V_{DS} < (V_{GS} - V_{th})$ . It is shown in Figure 2.2 as a linear region.

$$I_{D} = \frac{W}{L} \mu C_{ox} \left[ \left( V_{GS} - V_{th} \right) V_{DS} - \frac{V_{DS}^{2}}{2} \right]$$

(2.1)

In case where the drain voltage is higher than the gate voltage ( $V_{GS} > V_{th}$  and  $V_{DS} > (V_{GS} - V_{th})$ ), the drain current reaches a saturation value (shown in Figure 2.2 called the saturation region).

$$I_{D} = \frac{W}{L} \mu C_{ox} (V_{GS} - V_{th})^{2}$$

(2.2)

Figure 2.2. MOSFET drain current  $I_D$  vs. drain-to-source voltage  $V_{DS}$  for several values of  $V_{GS} - V_{th}$ ; the boundary between linear and saturation modes is indicated by the dashed line [60].

Another important parameter is the transconductance, which is defined as:

$$g_m = \frac{\partial I_D}{\partial V_g} \tag{2.3}$$

Using equations 2.1 and 2.3

$$g_m = \mu C_{ox} \frac{W}{L} V_{DS}$$

(2.4)

33

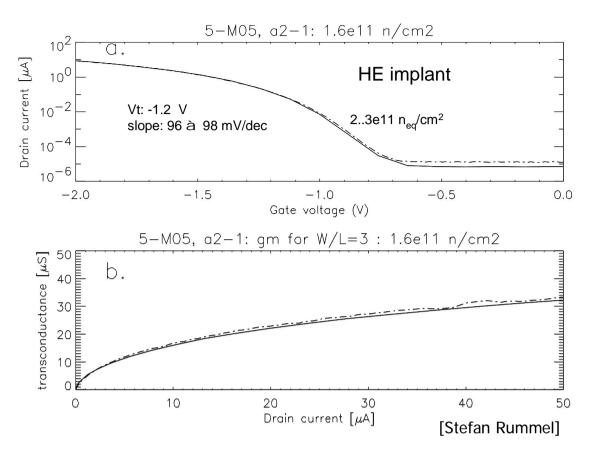

It is obvious that the transconductance increases linearly with  $V_{DS}$  but does not depend on  $V_{GS}$ . For a given device geometry (channel width W and length L) and a given  $V_{DS}$ , the mobility  $\mu$  depends on the carrier scattering due to the oxide charges and interface traps. Accordingly, the transconductance will be reduced due to ionizing radiation.

With respect to saturation region, combining equations 2.2 and 2.3 gives

$$g_{m_{sat}} = 2\mu C_{ox} \frac{W}{L} (V_{GS} - V_{th})$$

$$(2.5)$$

Therefore, the transconductance in the saturation region is linearly proportional to  $V_{GS}$  but does not depend on  $V_{DS}$ .

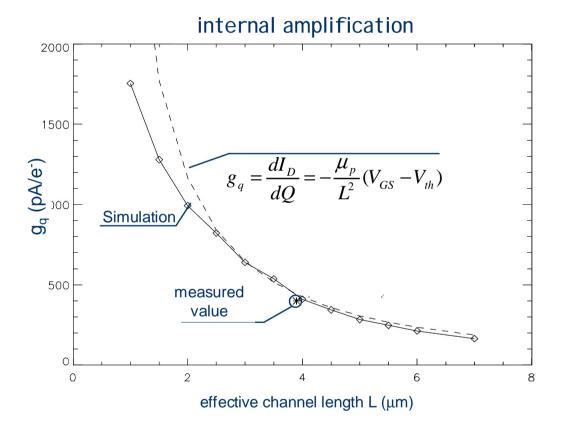

Figure 2.3. Dependence of the charge amplification  $g_q$  on the channel length. : 2 dimension TesCA simulation (50  $\mu$ A drain current); \*: measurements with 50  $\mu$ A drain current. [Performed by Rainer Richter]

The drain current response to a given signal charge defines the amplification of the internal gate, which can be defined as:

$$g_q = \frac{dI_D}{dq} \tag{2.6}$$

The amplification  $g_q$  is dependent on  $1/L^2$  and carrier mobility for a given gate voltage [61].

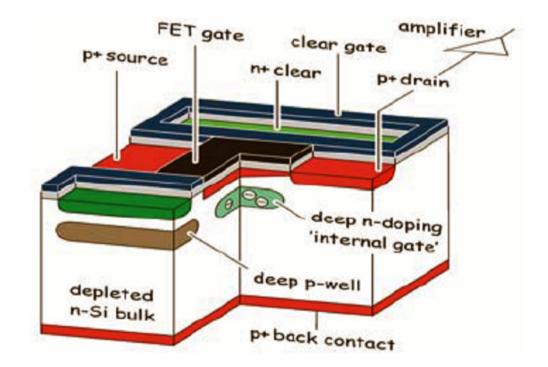

#### 2.1.2 Operation of MOSDEPFET

The MOSDEPFET principle of operation is shown in Figure 2.4 [2]. A MOS field-effect transistor is built on top of the detector substrate. Two terminals (source and drain) are connected by the transistor channel, which is created by biasing of a MOS gate contact in order to form an inversion layer at the interface between oxide and silicon. The gate voltage can steer the conductivity of the channel. By means of sideward depletion the whole substrate is fully depleted, and a potential minimum for electrons is created underneath the MOS transistor channel at a depth of about 1 micrometer. By ionizing radiation there will be electron-hole pairs generated in the depleted bulk, holes will move towards the backside of the substrate, electrons will be collected in the potential minimum (internal gate) where they are stored. These collected signal charges result in a change in the potential of the internal gate, which modulates the channel current of the transistor. The non-destructive readout mode can be repeated several times. After signals are read out, the signal charges and collected electrons in the internal gate can be removed through a positive voltage applied on the clear contact.

Figure 2.4 Linear MOSDEPFET with internal gate as charge collection and clear gate as clearing of signal electrons [2].

In addition, the potential barrier between the internal gate and the clear contact can be lowered by an additional clear gate (shown in Figure 2.4). If the internal gate is not located close enough to the surface, a significant fraction of the signal charges is lost in the source and drain of the transistor. As a consequence, the signal charge modulating the transistor current will be reduced. By means of an additional N-implantation underneath the transistor, the internal gate will move much closer to the transistor channel. Two available readout modes are source follower and drain readout. The latter has some attractive advantages, i.e., it offers much faster operation which is especially important for ILC experiment.

The feature of the simultaneous detection and amplification of a MOSDEPFET is important for the low noise operation.

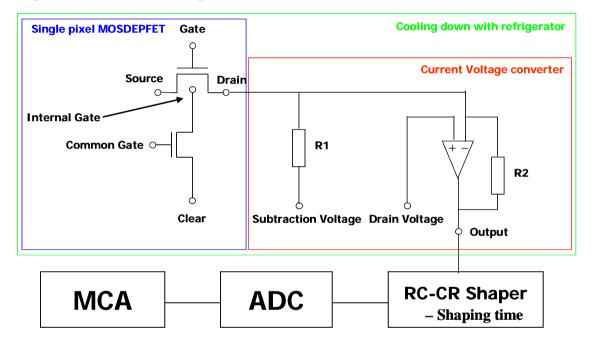

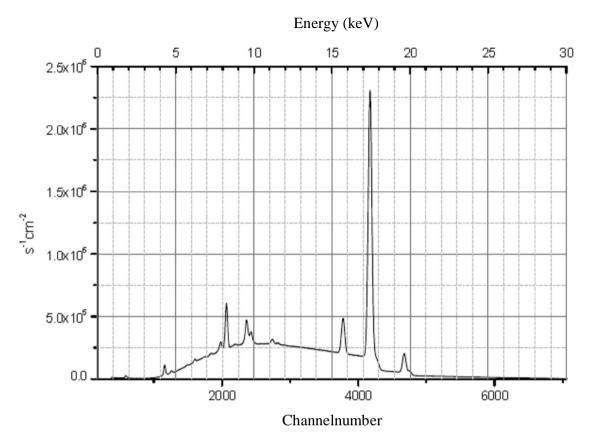

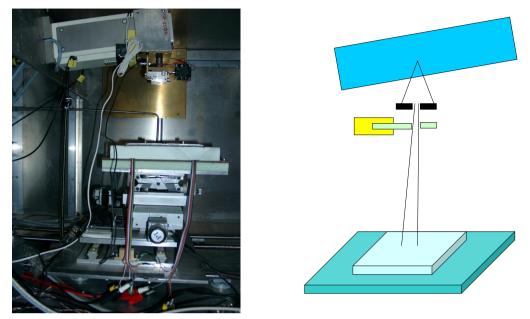

Figure 2.5 Experimental setup for the measurement of spectroscopic performance for the singlepixel MOSDEPFET.

In addition to the application of ILC, MOSDEPFET can also find use for X-ray spectroscopy [21]. Using Fe<sup>55</sup> radiation, the spectroscopic performance of a DEPFET can be measured. The whole experimental setup can be found in Figure 2.5. Drain current is firstly read out using a current/voltage converter; furthermore, the signal is formed by a shaping amplifier that is operated through series differential element (CR) and integration element (RC) — differential element is used as a high-pass filter and integration element as a low-pass filter, whose characteristic parameter is the time constant:

$$\tau = RC \tag{2.7}$$

In general, the stepwise input signal can be converted into an exponential falling output signal by CR differential elements, while the RC integration element can convert the

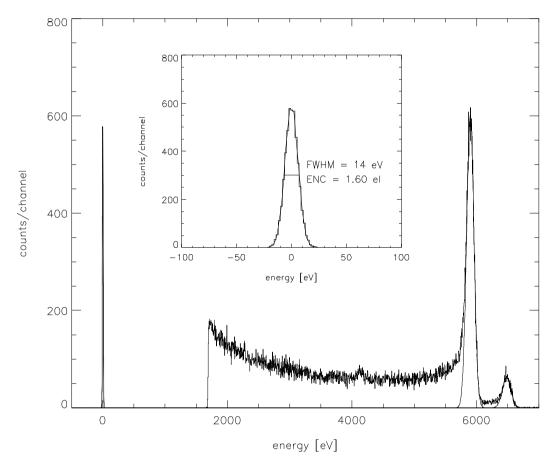

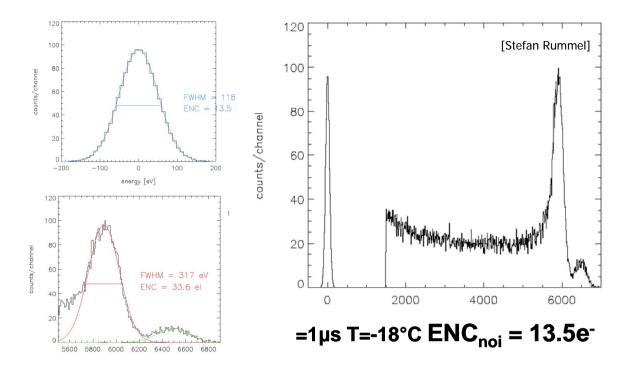

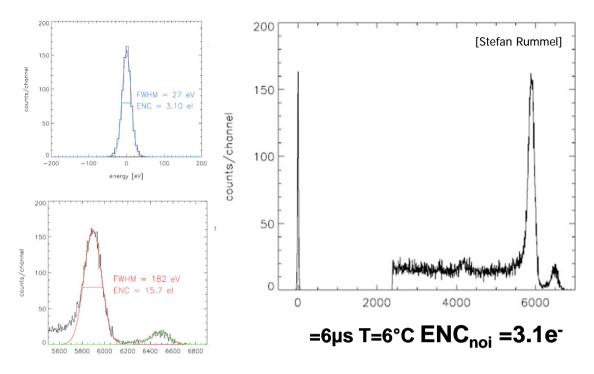

input signal into an exponential rising output signal. Hence, a Gauss-shaped signal is achieved accordingly through a combination of a CR differential element and a couple of RC integration elements. Furthermore, the analog signal coming from the shaper is converted into digital signal by SILENA ADC. Using a multi-channel analyzer the signal can be sorted to different channels by its amplitude. Of course, in order to assign the channel number to the corresponding energy, a precision energy calibration should be done with the help of the well-known characteristic lines of the recorded spectrum. An example of the spectrum is shown below in Figure 2.6.

Figure 2.6 Spectroscopic performance of a linear MOS-type DEPFET (with gate length L=7um and gate width W=25um) before irradiation at room temperature, integration time is set to 10us. The insert shows the noise peak with an ENC (rms) = 3.5e-(Performed by Laci Andricek).

#### 2.1.3 Noise

Noise measured in spectroscopy can characterize the detector properties. Normally it is determined in the unit of equivalent noise charge (ENC) [25.26.27.28]. The noise of a DEPFET can be written as follows:

$$ENC^{2} = \alpha \frac{8kTg_{m}}{3g_{a}^{2}\tau} + 2\pi a_{f}C_{tot}^{2} + qI_{leakage}n\tau$$

(2.8)

The first term of Equation 2.8 is the series white noise (or thermal noise), which depends on the integration time  $\tau$ , temperature T, the transconductance of the DEPFET  $g_m$ , the charge amplification of the internal gate  $g_q$  and a factor  $\alpha$  that depends on the exact shaping of the amplifier; the second term is series low-frequency noise, which depends on the effective capacitance  $C_{tot}$  and the normalization factor  $a_f$ ; the third one is parallel noise (or called shot noise) due to the leakage current  $I_{leakage}$  and integration time.

From the point of view of physical origin for the noise, series white noise is due to the resistor and is generated in the transistor. This white noise arises from the Brownian movement of the electrons in the channel and leads to different potentials and thus fluctuating voltages at the two contacts (source and drain), which can be measured as noise voltage. The low-frequency noise occurs due to the active traps located in the transistor channel, which can capture or emit charge carriers. This will affect the electric field in the transistor channel and accordingly also the current in the channel. For this reason low-frequency noise is generated. The variation of the electric field is determined by the trap density and the related capture cross-section and emission rate. The parallel noise is formed by currents that come from any electric input. The original source of parallel noise is the surface leakage current due to the interface traps induced by ionizing radiation and the leakage current from the silicon bulk due to thermal generation of electron-hole pairs. There are energy levels within the band gap due to either defects in the silicon crystal lattice or contaminations from metal foreign atoms. In general, there is an expectation of temperature-dependent leakage current — leakage current decreases in factor of two by a temperature reduction of about 7K, in the case of the energy level of the traps staying in the middle of the band gap. On the other hand, leakage current through the gate contact and also the feedback current through the feedback resistor in the preamplifier can contribute to the parallel noise.

In order to minimize the noise in the detector, it is necessary to reduce primarily the parameters like capacitance, temperature and leakage current. The capacitance can be minimized by a reduced gate area — reduced input capacitance (à reduction of low-frequency noise). As shown in Figure 2.5, the detector and readout system can be placed in a refrigerator to cool down the detector to reduce the leakage current (à reduction of the parallel noise). In addition, the noise components depending on the integration time in a manner that the first one – serial noise is proportional with the reciprocal of integration time  $\sim 1/\tau$ , the second one – serial low-frequency noise does not depend on the

integration time and the third one – parallel noise is direct proportional with integration time  $\sim \tau$ . For the sake of optimized energy resolution, a compromise between serial white noise and parallel noise due to different dependence of integration time can be found by a lower temperature. Consequently, the noise is given as a function of integration time.

## 2.2 MOS capacitance

In order to study the quality of the oxide, the easiest way is to use a MOS capacitance (MOS: Metal Oxide Semiconductor) [23]. The main reason to research the MOS capacitance is to understand the principle of operation as well as the detailed analysis of the MOS Field-Effect Transistor (MOSFET). The MOS structure is one of the simplest structure and most important component in many semiconductor devices and ideal probe to understand properties of the SiO<sub>2</sub>. In this chapter the basic principle for understanding of the functionality of a MOS capacitance will be presented.

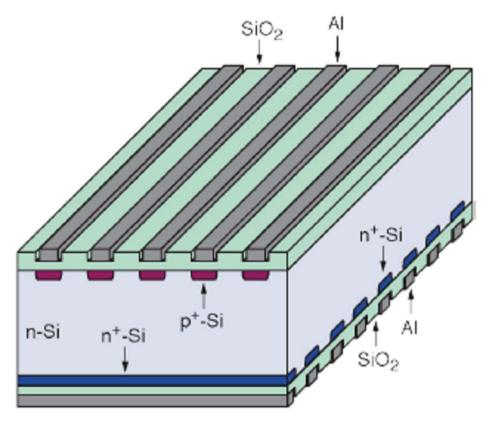

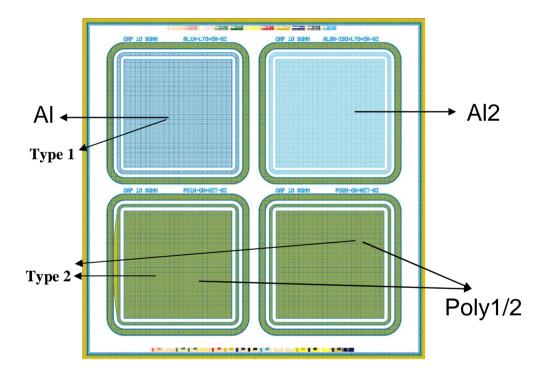

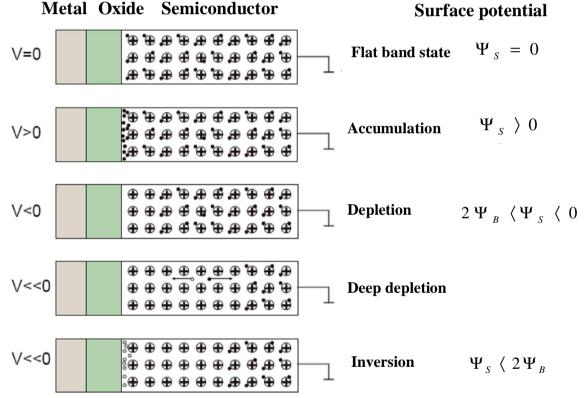

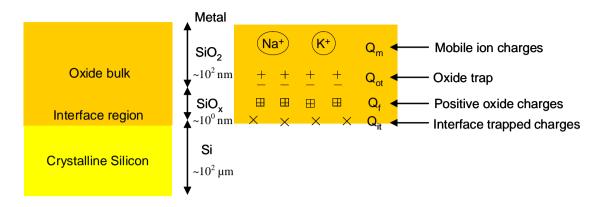

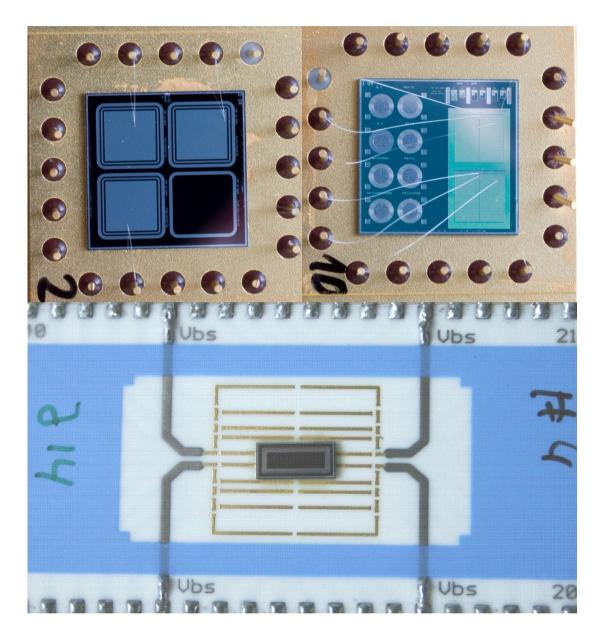

## 2.2.1 Definition of a MOS structure

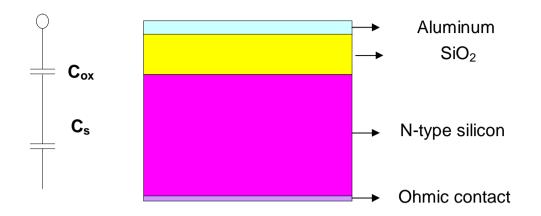

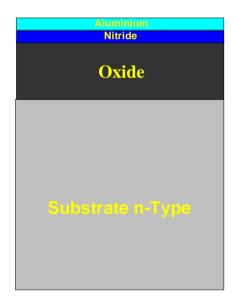

The profile of an ideal MOS capacitance is schematically shown in Figure 2.7. On the left hand side, an equivalent circuit diagram is shown, which consists of oxide capacitance and capacitance of the depletion layer. Within the scope of this thesis, n-type silicon substrate is used to produce MOS capacitance. At first, a layer of  $SiO_2$  is grown on the substrate at about 1050 degrees by thermal oxidation. In general, the silicon substrate has a thickness of 450 micrometers. For the gate contact two different materials are mainly used: either Aluminum or poly silicon (Figure 2.8). In the next chapter results from irradiation experiments will be generally discussed based on these two structures. Normally the gate contact is about 10 mm<sup>2</sup> large.

In addition, silicon nitride can be used as additional dielectrics, which have shown to have better tolerance against ionizing radiation (discussed later). On the backside an ohmic contact is made.

Figure 2.7 Schematic profile of a MOS capacitance (right), the equivalent circuit diagram consists of an oxide capacitance and a capacitance from the depleted layer (left).

Figure 2.8 Layout of a standard MOS capacitance that consists of four different structures: Al-gate structure (top left); Al2-gate structure (top right); Poly1-gate structure (bottom left); Poly2-gate structure (bottom right).

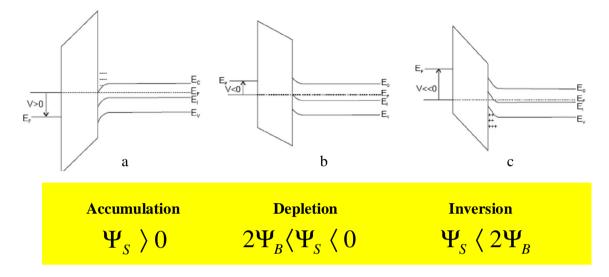

By measurements of the MOS capacitances a lot of information about the oxide quality can be derived. A series of experimental methods are available to qualify the oxide. Here, the MOS capacitance is measured by applying a gate voltage. In the case a voltage is applied on the gate, there is a relative shift of the Fermi level between metal and semiconductor, and a space charge region will be formed. In order to understand the different bias modes of a MOS capacitor, three different bias voltages are applied: the first one is above the flat band voltage -  $V_{FB}$ ; the second one is between the flat band voltage and the threshold voltage -  $V_T$  and the last one is lower than the threshold voltage. The corresponding biasing regions are as shown in Figure 2.9: accumulation, depletion and inversion.

Figure 2.9 Band diagram of a MOS capacitance, A. Accumulation, b. Depletion, c. Inversion.  $\Psi_{B}$  is surface potential;  $\Psi_{S}$  is bulk potential [23].

#### Accumulation

If the applied voltage on the gate is positive, the produced band deflection shows downward. The positive polarity can attract majority carriers (electrons) from the silicon substrate toward the gate. Since the oxide has a good quality and can be considered as a good insulator, electrons will move to the interface between silicon and SiO<sub>2</sub> and, furthermore, accumulate there. As a consequence, a negative charge  $Q_s$  is collected compared to the positive gate charge  $Q_G$ . An accumulation layer of electrons is created. It can be described by the following formula:

$$n_n = n_i e^{(Ei - E_F)/k_B T}$$

(2.9)

Where  $n_n$  is the concentration of charge carriers,  $n_i$  is the intrinsic concentration of charge carriers for silicon at room temperature. The concentration of electrons is exponentially proportional to the energy difference  $E_i$ - $E_F$ . On the one hand, there are charges on the metal gate; on the other hand, the electrons are accumulated in the accumulation layer. Therefore, the MOS structure in accumulation state can be

considered as a plate capacitor. The total capacitance is equal to the oxide capacitance, and the surface potential is positive in this case as shown in Figure 2.9a.

$$\Psi_s \rangle 0$$

In general, the oxide thickness can be extracted from the oxide capacitance, which is measured by CV measurement on a MOS capacitance in accumulation. Accordingly, the oxide thickness may be calculated from  $C_{ox}$  using the following equation:

$$d_{ox} = \frac{\mathcal{E}_0 \mathcal{E}_{ox} A}{C_{ox}}$$

Compared with conventional ellipsometry <sup>\*</sup>, the oxide thickness calculation based on CV measurement is very precise, as long as the oxide capacitance is measured in accumulation, where the measured capacitance is essentially constant. In the case a high-resistance silicon substrate is used for MOS capacitance, oxide capacitance could be extracted only from low-frequency CV measurement in accumulation (discussed later).

#### **Flat band**

In this case flat band means that the energy band diagram of the silicon is flat, thus there is no bending of the band. Hence the charge carriers will not be forced to move in any direction. The surface potential is equal to zero. Ideally the flat band voltage is 0V; however, in real case it is approximately  $0.5 \sim 2$  V due to the difference of the work function from metal and semiconductor, and also the initial condition of the oxide charges cannot be neglected. Therefore, the flat band voltage for the real case can be calculated as follows:

$$V_{FB} = \frac{\phi_{ms}}{q} - \frac{N_{ox}}{C_{ox}} - \frac{N_{it}}{C_{ox}}$$

(2.10)

Where  $V_{FB}$  is the flat band voltage that should be applied on a real MOS capacitor to achieve flat band condition,  $\phi_{ms}$  is the work function difference between the metal (aluminum) gate and silicon,  $N_{ox}$  and  $N_{it}$  are the surface damages arising from oxide charges and interface traps. The surface potential is equal to zero:  $\Psi_s = 0$

<sup>\*</sup>*Ellipsometry: an optical method to measure the dielectric properties of thin films.*

#### Depletion

As the gate voltage changes towards negative values, which leads to an upward band bending, the majority carriers (electrons) are repelled from the  $Si/SiO_2$  interface. Moreover, a depletion layer is developed underneath the oxide, where the majority of charge carriers become depleted. The depletion layer width increases with increasing gate voltage. The higher is the doping concentration  $N_D$ , the narrower is the space charge region. The capacitance in depletion does not remain constant and becomes sharply small. In this case, the surface potential is (shown in Figure 2.9b):

$2\Psi/\Psi$

( )

$$\sum B \left( 1 \right) \left( 2 \right)$$

Figure 2.10 various states on the MOS Structure: flat band, Accumulation, depletion, deep depletion, Inversion [1].

(2 11)

#### Inversion

If the gate voltage changes much lower than the flat band voltage, the Fermi level crosses the intrinsic energy level  $E_i$ ; this is called inversion, since the minority carriers (holes) are more than the majority carriers (electrons). This state is shown in Figure 2.10. In the case the gate voltage decreases further, the space charge region reaches its maximal value  $W_m$ . The capacitance in depletion remains constant. This is called strong inversion. In this case, the surface potential is (shown in Figure 2.9c) given as follows for n-doping material:

$$\Psi_{s}\langle 2\Psi_{B} \tag{2.12}$$

With respect to MOS capacitance, the flat band voltage  $V_{FB}$  is important (Figure 2.10), and the threshold voltage  $V_T$  for MOS-FETs in case of inversion as well, i.e. the MOS-FET remains conductive, if this voltage is applied on the gate [29].

$$V_T = -2\Psi_B - \frac{\sqrt{4qN_D \mathcal{E}_0 \mathcal{E}_{Si} \Psi_B}}{C_{ox}}$$

(2.13)

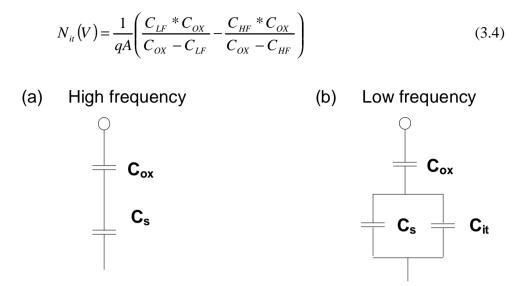

#### 2.2.2 Computation of a MOS capacitance

As mentioned above MOS capacitance consists of the oxide capacitance  $C_{ox}$  and the capacitance from space charge region  $C_s$ . Both are switched in series. Depending on the applied gate voltage, the total capacitance is given in equation 2.14:

$$C(V) = \frac{C_{ox}C_{s}(V)}{C_{ox} + C_{s}(V)}$$

(2.14)

The flat band voltage C<sub>FB</sub> can be Figured out by means of Equation 2.15:

$$C_{FB} = \frac{C_{ox}C_F}{C_{ox} + C_F}$$

(2.15)

Where the total flat band capacity  $C_F$  is defined as [29]:

$$C_F = \frac{\mathcal{E}_0 \mathcal{E}_{Si}}{L_D} \tag{2.16}$$

Where  $\varepsilon_0$  and  $\varepsilon_{si}$  are dielectrical constants,  $L_D$  is the Debye length and is defined by:

$$L_D = \sqrt{\frac{\varepsilon_0 \varepsilon_{Si} k_B T}{q^2 N_D}}$$

As mentioned above, for a positive gate voltage, MOS capacitance remains in accumulation. Therefore the MOS capacitance is represented by:

$$C_{ox} = \frac{\mathcal{E}_0 \mathcal{E}_{SiO2} A}{d_{ox}}$$

(2.17)

The thicker the oxide, the smaller the gate surface area, and the lower the MOS capacitance. In the case where the gate voltage scans from positive to negative value, the state of a MOS capacitance will change from accumulation to depletion, and flat band is only a transition state. In depletion, electrons are pushed away from interface; as a consequence, a space charge region is produced, whose width will increase if the voltage becomes more negative. Because the capacitance of the space charge region is switched with the oxide capacitance in series, the total capacitance decreases rapidly. In inversion, an additional inversion layer is formed, which hinders a further extension of the space charge region. Accordingly, the capacitance remains constant.

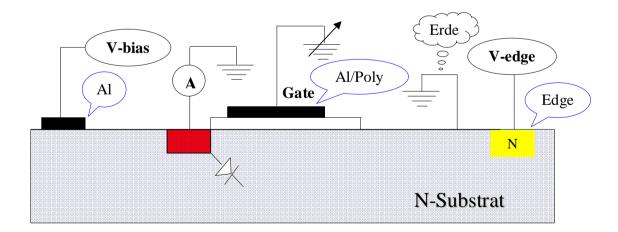

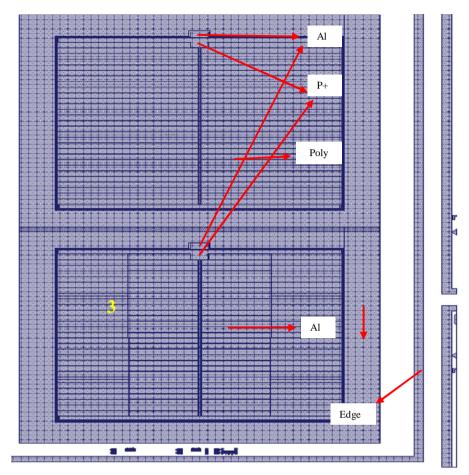

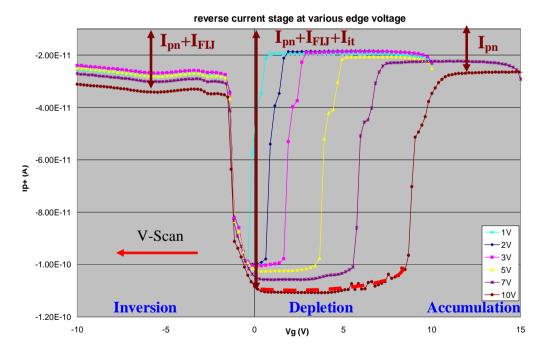

#### 2.3 Gated controlled diode

A gated controlled diode [30] is utilized to characterize the generation parameters of charge carriers in order to study the space charge region near the surface. A schematic cross section of such device is shown in Figure 2.11. It consists of an N substrate, a p+ implantation region, and rectangular gate surrounding the p+ region.

Figure 2.11 the gated controlled diode. Al /poly gate, p+ implantation region, Al contact and edge contact.

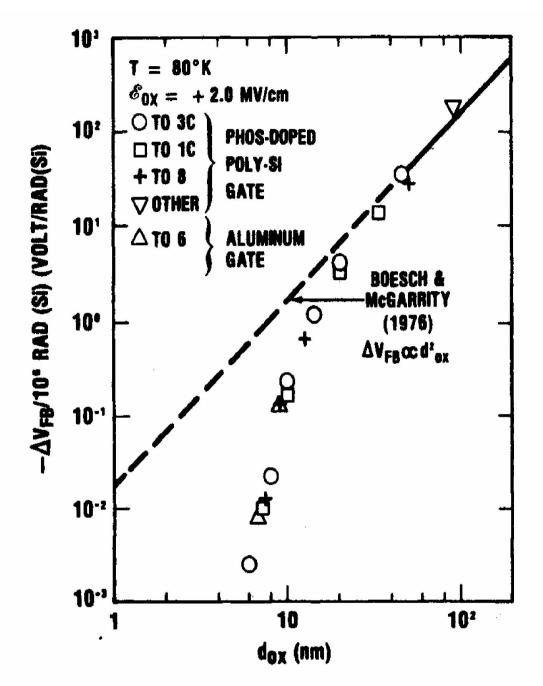

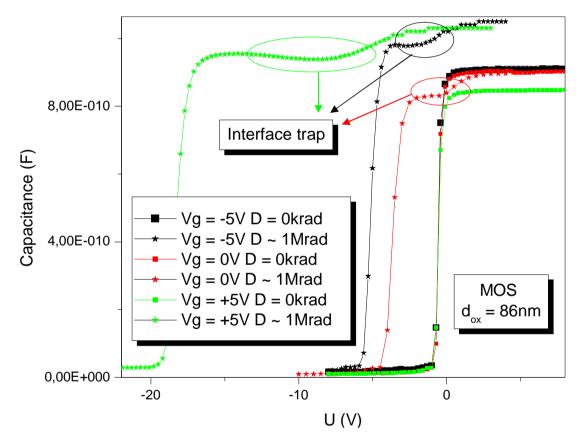

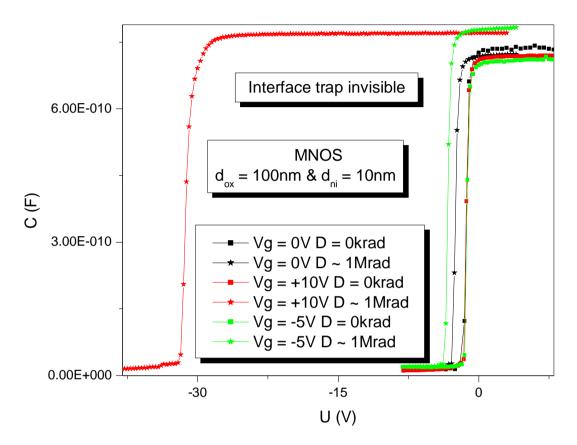

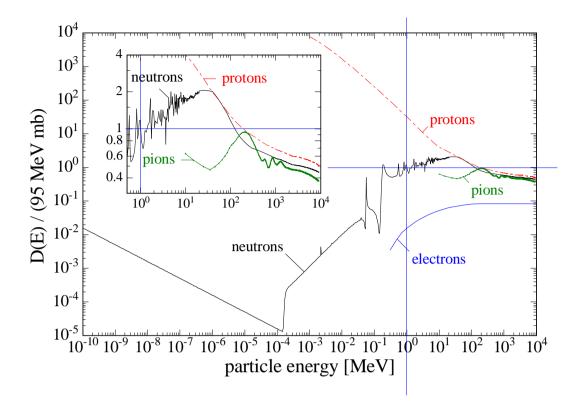

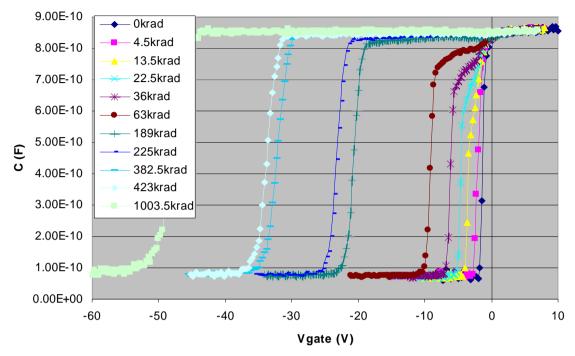

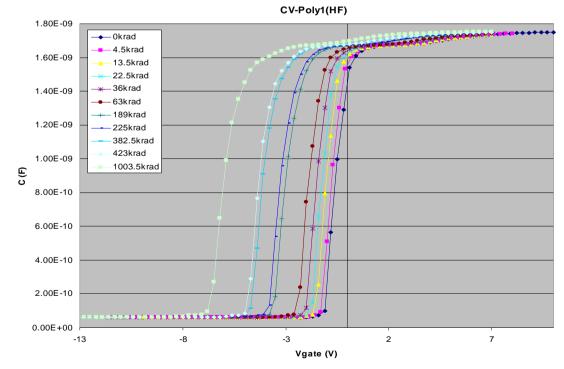

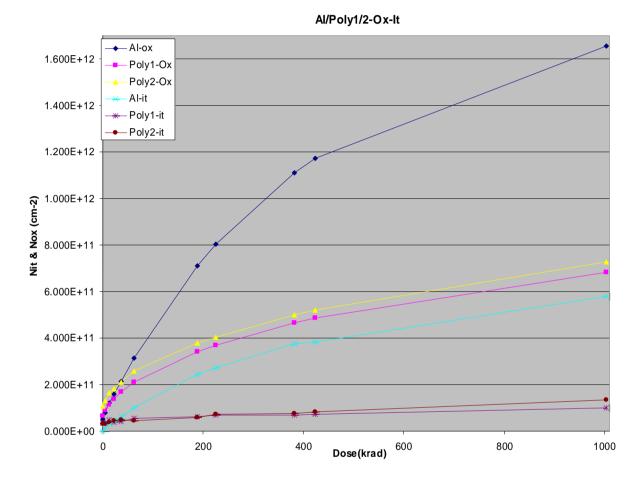

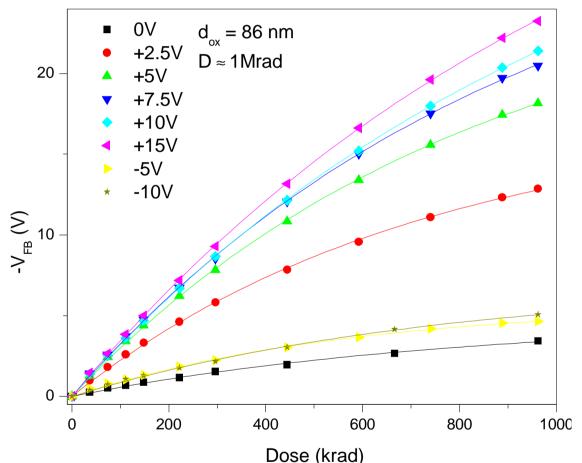

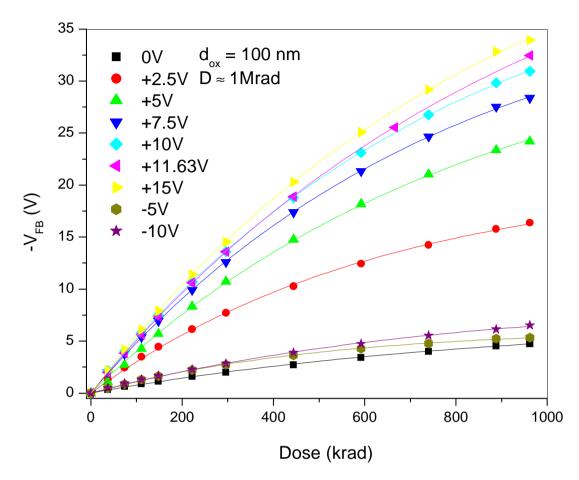

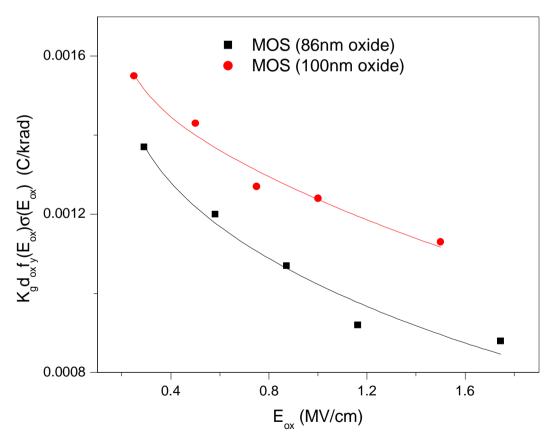

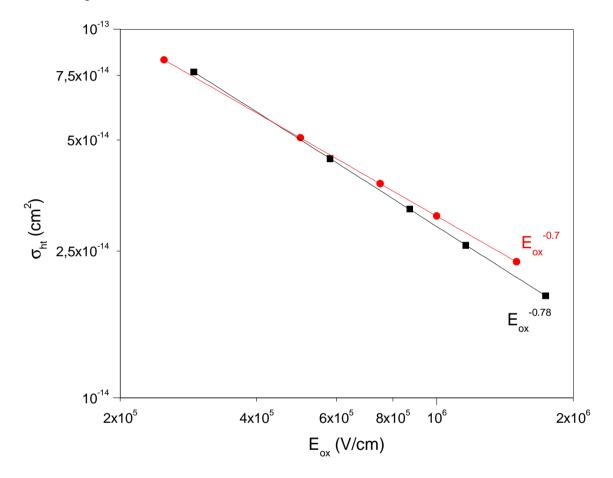

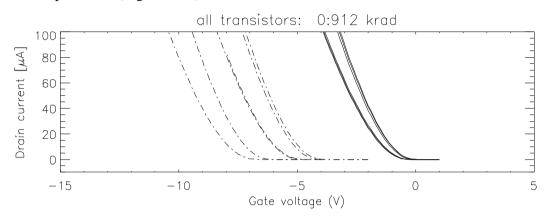

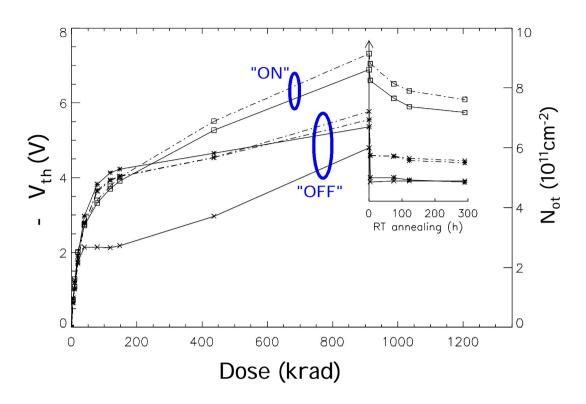

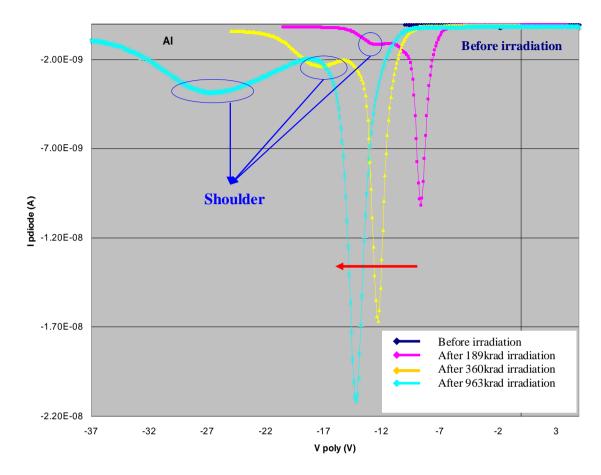

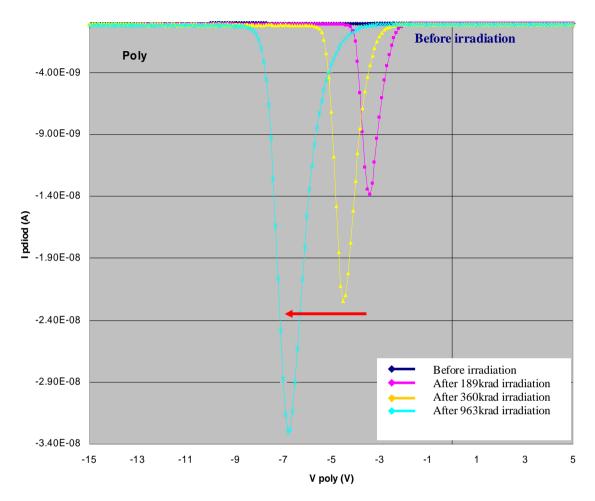

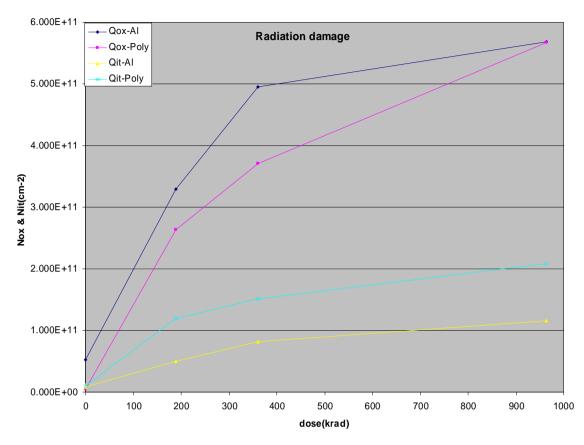

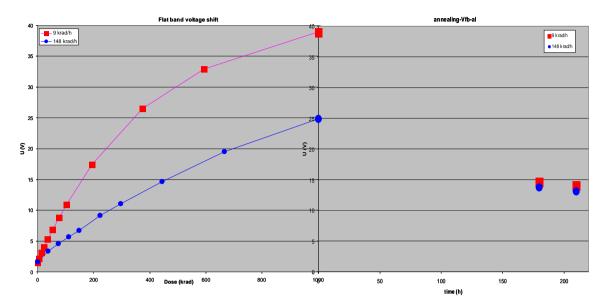

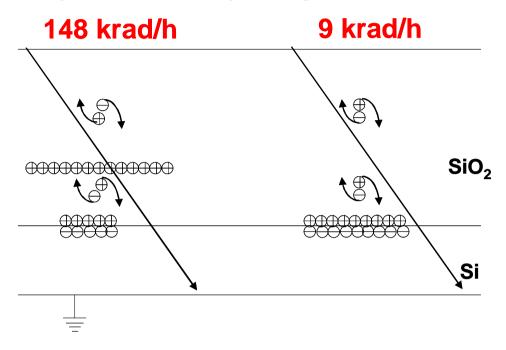

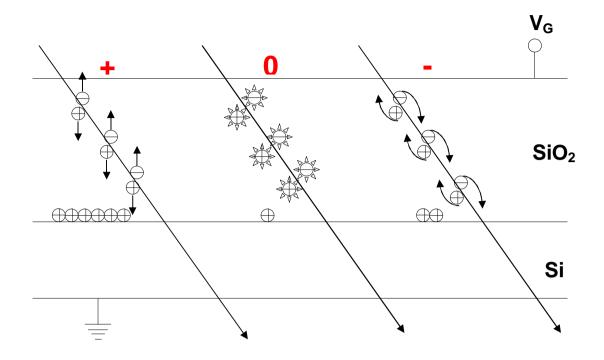

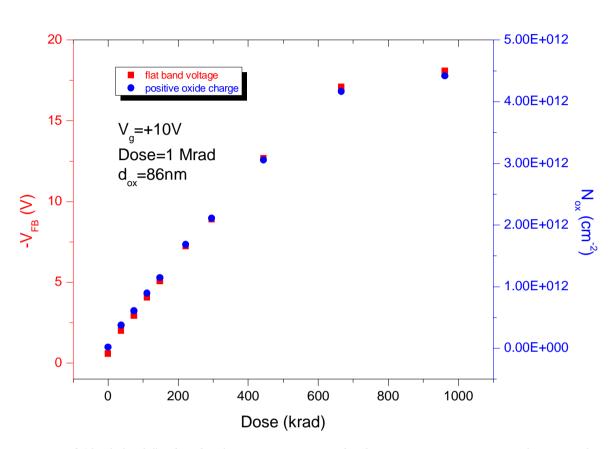

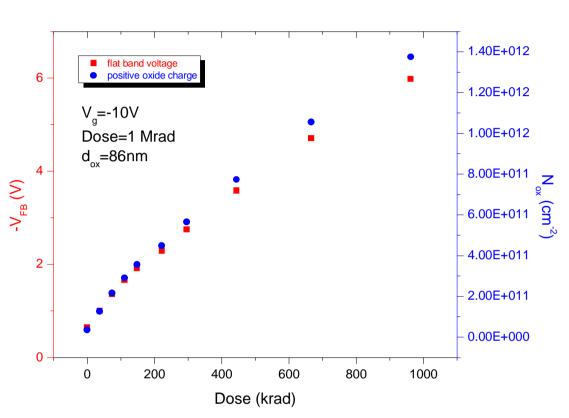

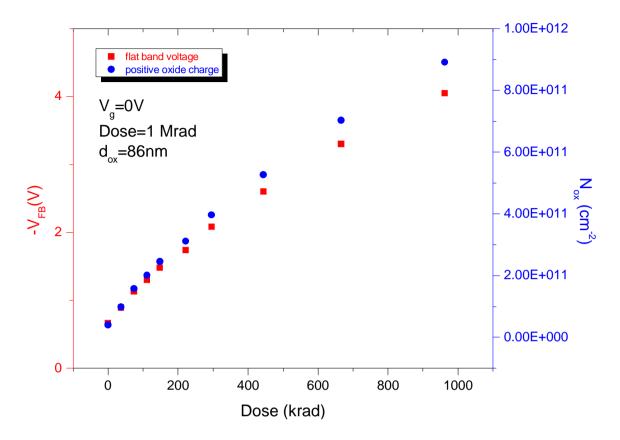

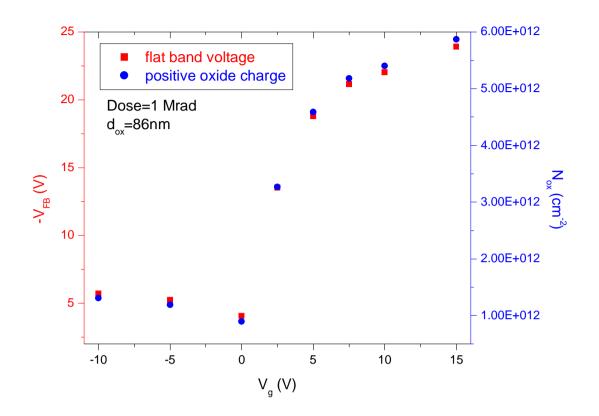

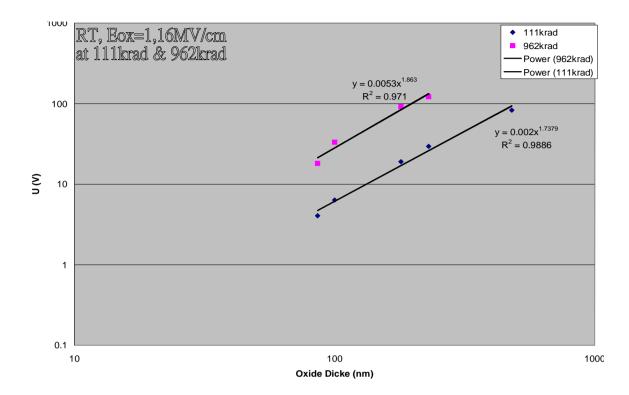

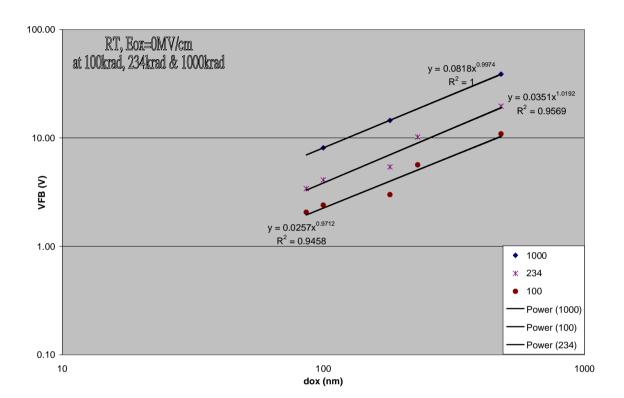

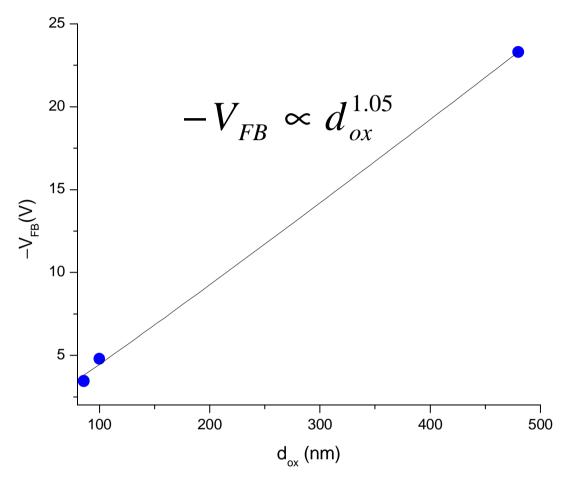

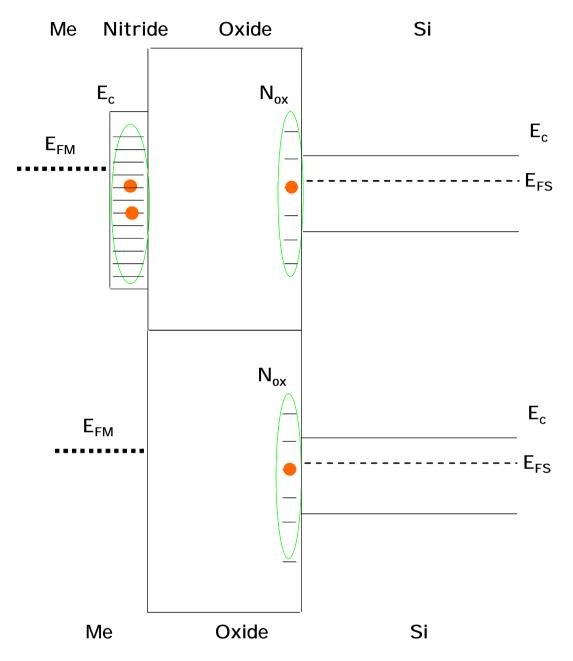

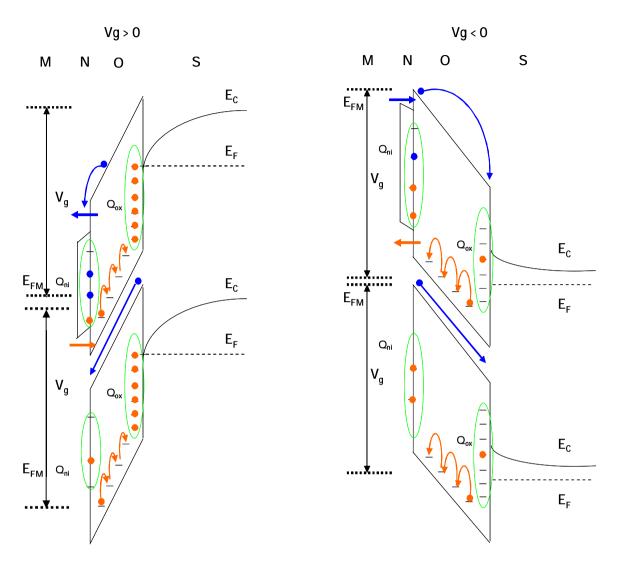

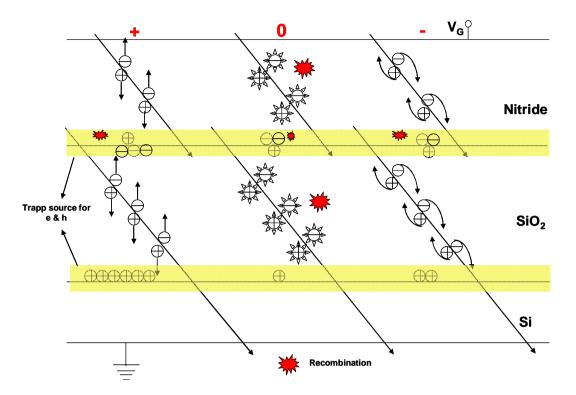

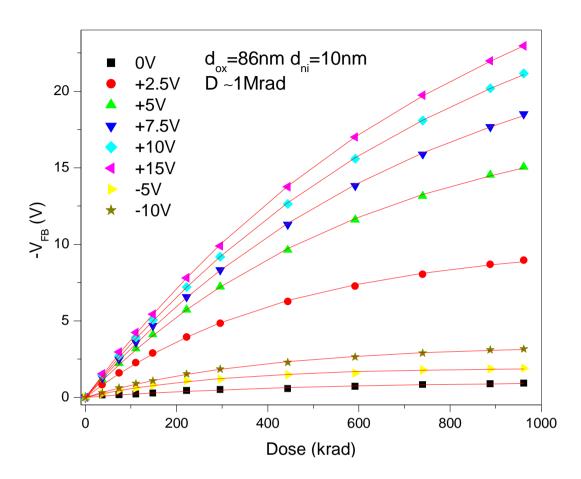

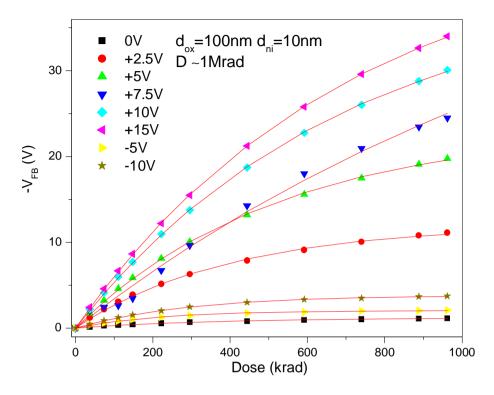

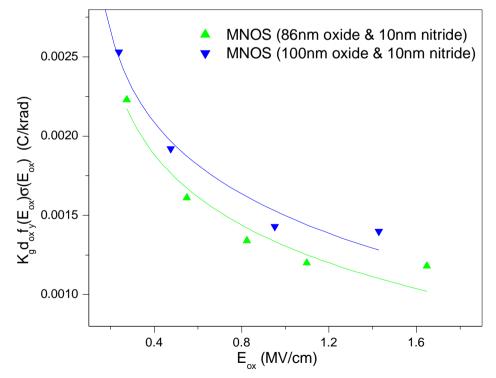

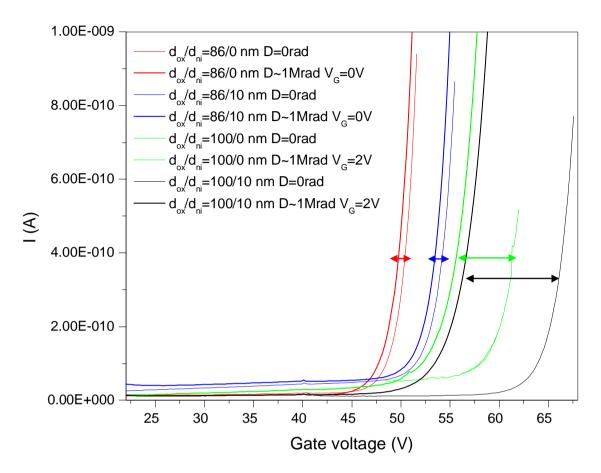

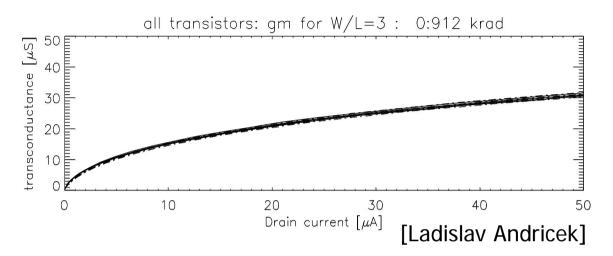

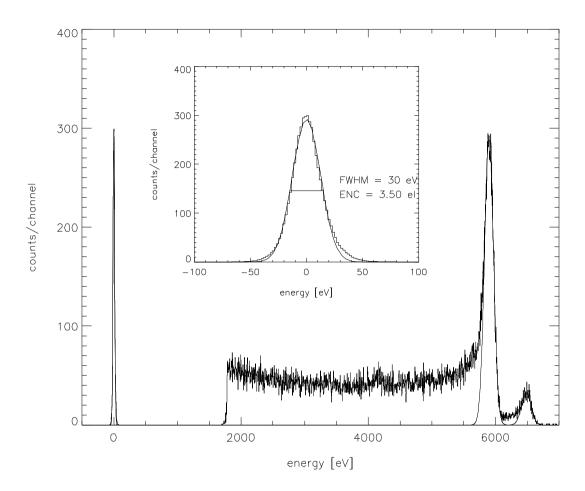

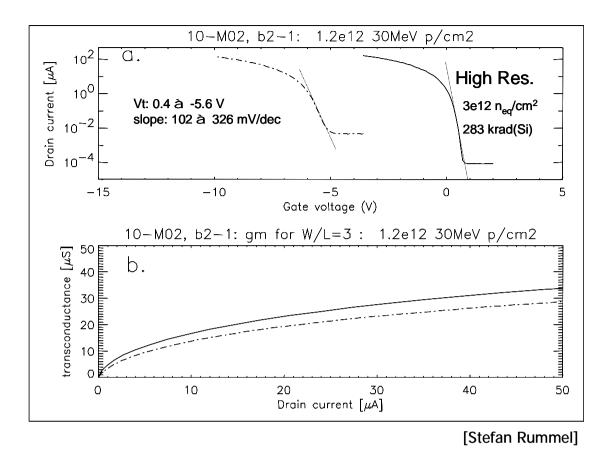

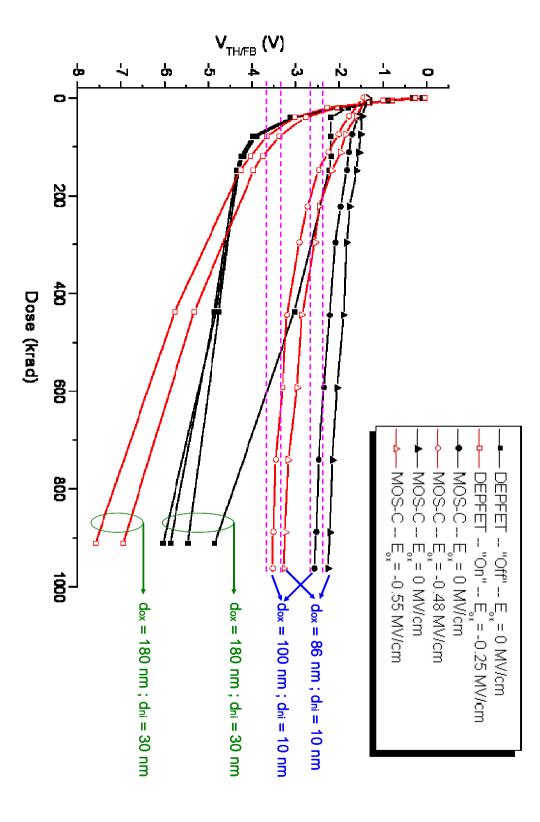

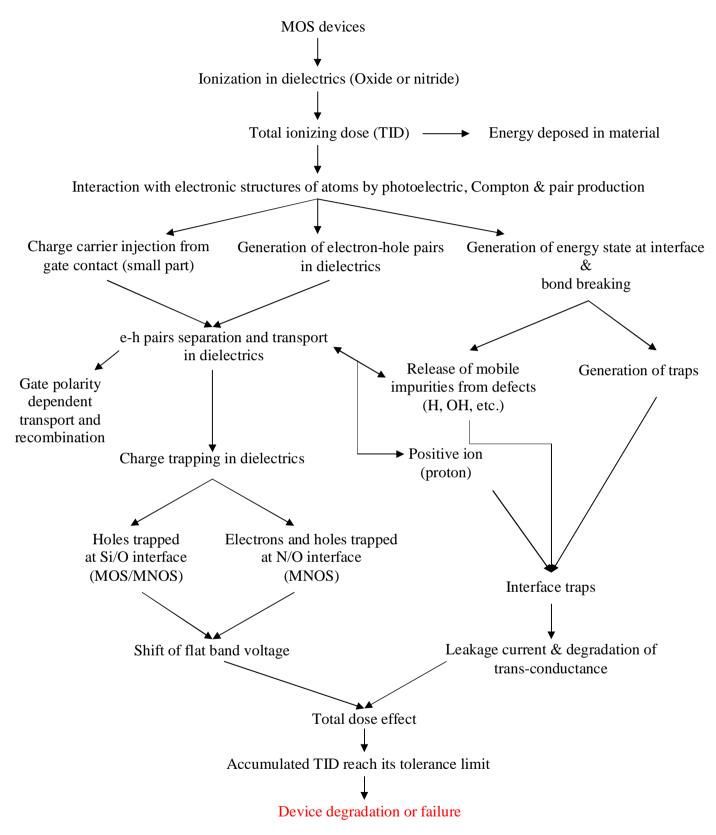

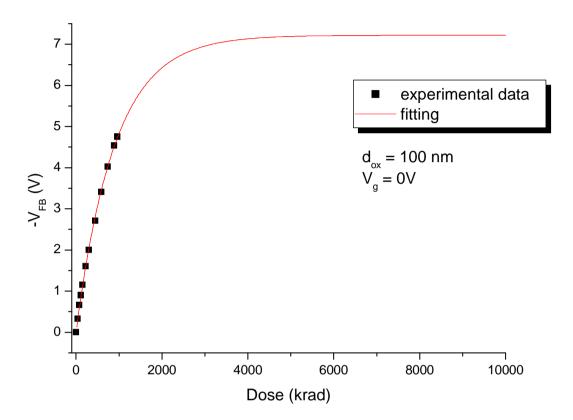

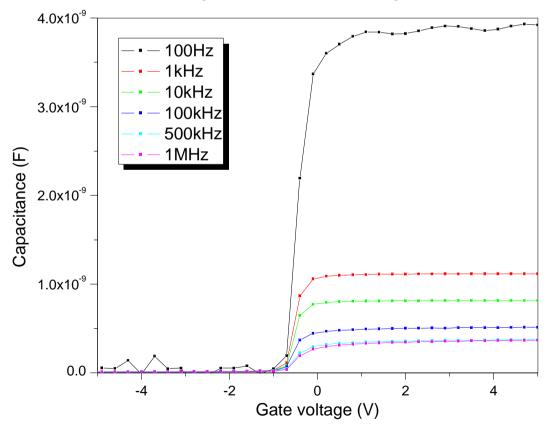

Figure 2.12 Layout design for gated controlled diode.