#### Lehrstuhl für Entwurfsautomatisierung der Technischen Universität München

## **Efficient Quadratic Placement of VLSI Circuits**

## **Peter Spindler**

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs**

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr. techn. Josef A. Nossek

Prüfer der Dissertation:

- 1. Univ.-Prof. Dr.-Ing. Frank M. Johannes

- 2. Univ.-Prof. Dr.-Ing. Jens Lienig Technische Universität Dresden

Die Dissertation wurde am 20.12.2007 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 05.06.2008 angenommen.

## Acknowledgment

This thesis is the result of my work and all the help and advice that has been provided to me through all of my years at the Institute for Electronic Design Automation, Technische Universität München, Germany.

The person who deserves most of my credit is undoubtedly my adviser Professor Frank M. Johannes. With the prolific discussions, not only about the field of research, and his continuous encouragement, he gave the essential requirements for successful research. I am also very grateful for the constant support and inspiration of Professor Ulf Schlichtmann. I would also like to thank Professor Jens Lienig and Professor Josef A. Nossek for their interest in my thesis and their job as reviewers.

The many interesting discussions with my colleagues contributed much to this thesis. Amongst others, I would like to thank Martin Strasser, Dr. Helmut Gräb, and my predecessor in the layout group, Dr. Bernd Obermeier. Special thanks go to Dr. Hans Eisenmann, who laid with his work the basis for this thesis. I owe respect to Dr. Bernd Finkbein, Getraude Kallweit, Hans Ranke, Werner Tolle, Susanne Werner, and Jürgen Zenz for their administrative and technical support.

Finally, I would like to thank with all my heart my girlfriend Katrin Mayer-Arnold, who always stands behind me and supports me under all circumstances.

# **Contents**

| 1 | Intr | oductio  | n                                         | 1  |  |  |  |

|---|------|----------|-------------------------------------------|----|--|--|--|

|   | 1.1  | Electro  | onic Design Automation                    | 1  |  |  |  |

|   | 1.2  | Types    | of Integrated Circuits                    | 3  |  |  |  |

|   | 1.3  | Placen   | ment                                      | 5  |  |  |  |

| 2 | Stat | e of the | Art                                       | 7  |  |  |  |

|   | 2.1  | Globa    | l Placement                               | 7  |  |  |  |

|   |      | 2.1.1    | Greedy Placement                          | 7  |  |  |  |

|   |      | 2.1.2    | Cluster-Growth                            | 8  |  |  |  |

|   |      | 2.1.3    | Min-Cut Placement                         | 8  |  |  |  |

|   |      | 2.1.4    | Stochastic Placement                      | 9  |  |  |  |

|   |      | 2.1.5    | Analytical Placement                      | 10 |  |  |  |

|   |      | 2.1.6    | Warping Placement                         | 16 |  |  |  |

|   | 2.2  | Multil   | evel Approach                             | 16 |  |  |  |

|   | 2.3  | Net M    | odels                                     | 16 |  |  |  |

|   |      | 2.3.1    | Graphs and Metrics                        | 17 |  |  |  |

|   |      | 2.3.2    | Net Models for Quadratic Placement        | 18 |  |  |  |

|   | 2.4  | Routal   |                                           | 19 |  |  |  |

|   |      | 2.4.1    | •                                         | 19 |  |  |  |

|   |      | 2.4.2    |                                           | 20 |  |  |  |

|   | 2.5  | •        |                                           |    |  |  |  |

|   |      | 2.5.1    | Legalization of Standard Cell Circuits    | 22 |  |  |  |

|   |      | 2.5.2    |                                           | 22 |  |  |  |

| 3 | This | Thesis   |                                           | 25 |  |  |  |

|   | 3.1  | "Kraft   | werk": Force-Directed Quadratic Placement | 25 |  |  |  |

|   | 3.2  | "Boun    | d2Bound" Net Model                        | 26 |  |  |  |

|   | 3.3  | Routal   | bility-Driven Placement                   | 26 |  |  |  |

|   |      | 3.3.1    |                                           | 26 |  |  |  |

|   |      | 3.3.2    |                                           | 27 |  |  |  |

|   | 3.4  | "Abacı   | _                                         | 27 |  |  |  |

II CONTENTS

| 4 | Bour | nd2Bound Net Model                                                      | 29 |

|---|------|-------------------------------------------------------------------------|----|

|   | 4.1  | Clique/Star Net Model                                                   | 30 |

|   | 4.2  | Bound2Bound Net Model                                                   | 32 |

|   | 4.3  | Comparison                                                              | 32 |

|   | 4.4  | Approximation Error depending on Module Movement                        | 34 |

| 5 | Kraf | twerk: Force-Directed Quadratic Placement                               | 35 |

|   | 5.1  | Quadratic Placement                                                     | 35 |

|   | 5.2  | Creation of Matrix $C_x$ and Vector $d_x \dots \dots \dots \dots \dots$ | 37 |

|   | 5.3  | Force-directed Quadratic Placement                                      | 39 |

|   | 5.4  | Geometry                                                                | 40 |

|   | 5.5  | One Placement Iteration                                                 | 42 |

|   |      | 5.5.1 Move Force                                                        | 42 |

|   |      | 5.5.2 Hold Force                                                        | 44 |

|   |      | 5.5.3 Illustration                                                      | 46 |

|   | 5.6  | Core of Kraftwerk                                                       | 46 |

|   | 5.7  | Overview of the Placement Algorithm                                     | 47 |

|   | 5.8  | Quality Control                                                         | 48 |

|   | 5.9  | Convergence                                                             | 50 |

|   |      | 5.9.1 Theory                                                            | 50 |

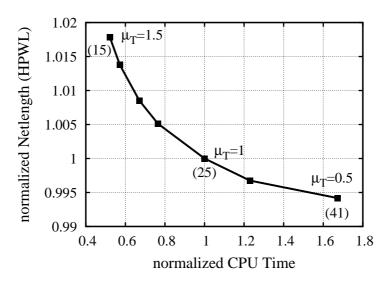

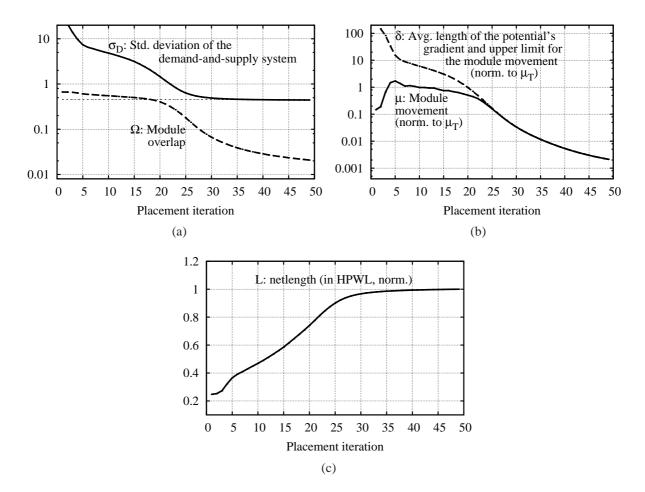

|   |      | 5.9.2 Experimental Results                                              | 52 |

|   |      | 5.9.3 Limitations                                                       | 54 |

|   | 5.10 | Advanced Module Demand                                                  | 54 |

|   | 5.11 | Advanced Module Supply                                                  | 56 |

|   |      | Implementation Details                                                  | 57 |

|   |      | 5.12.1 Calculation of the Potential                                     | 57 |

|   |      | 5.12.2 Solving the System of Linear Equations                           | 58 |

| 6 | Rout | tability-Driven Placement                                               | 61 |

|   | 6.1  | RUDY: Efficient Routing Demand Estimation                               | 62 |

|   | 6.2  | Characteristics of RUDY                                                 | 62 |

|   | 6.3  | Routing Supply                                                          | 64 |

|   | 6.4  | Integration in Kraftwerk                                                | 65 |

| 7 | Lega | alization                                                               | 69 |

|   | 7.1  | Puzzle: Macro Legalization                                              | 71 |

|   |      | 7.1.1 Construction of Matrix A and Vector b                             | 72 |

|   |      | 7.1.2 Initial Legalization                                              | 72 |

|   |      | 7.1.3 Constraint Direction based on Placement                           | 73 |

|   |      | 7.1.4 Optimization of Constraint Direction                              | 74 |

|   |      | 7.1.5 Comparison                                                        | 76 |

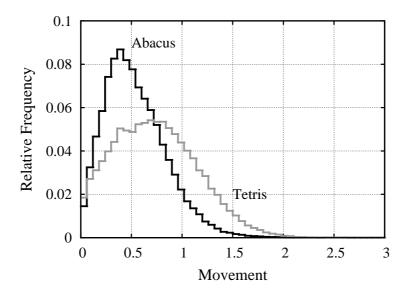

|   | 7.2  | Abacus: Standard Cell Legalization                                      | 79 |

|   |      | 7.2.1 PlaceRow                                                          | 80 |

|   |      | 7.2.2 Implementation by Dynamic Programming                             | 82 |

CONTENTS

|                                |     | 7.2.3    | Worst-Case Computational Complexity            | . 84 |

|--------------------------------|-----|----------|------------------------------------------------|------|

|                                |     | 7.2.4    | Average-Case Computational Complexity          | . 84 |

|                                |     | 7.2.5    | Comparison                                     |      |

|                                | 7.3 | Tetris   |                                                | . 86 |

| 8                              | Exp | eriment  | al Results                                     | 89   |

|                                | 8.1 | Stabilit |                                                | . 90 |

|                                | 8.2 | Engine   | ering Change Order                             | . 92 |

|                                | 8.3 | IBM-P    | LACE 2.0 Benchmark Suite                       | . 92 |

|                                | 8.4 | ISPD 2   | 2006 Contest Benchmark Suite                   | . 94 |

|                                | 8.5 |          | 2005 Contest Benchmark Suite                   |      |

|                                | 8.6 | ICCAL    | 2004 Mixed-Size Benchmark Suite                | . 97 |

|                                | 8.7 |          | IB <sup>+</sup> Floorplacement Benchmark Suite |      |

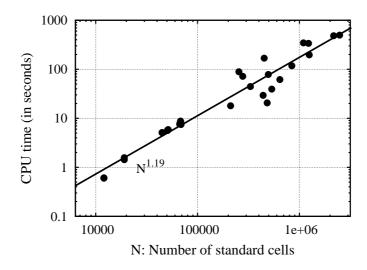

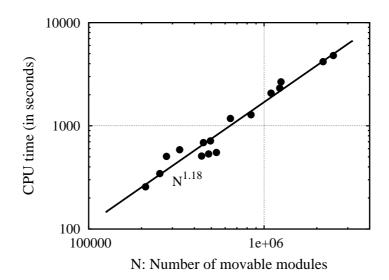

|                                | 8.8 |          | e-Case Computational Complexity                |      |

| 9                              | Con | clusion  |                                                | 101  |

| Bibliography List of Variables |     |          |                                                | 103  |

|                                |     |          |                                                | 123  |

| List of Figures                |     |          | 126                                            |      |

IV CONTENTS

# Chapter 1

## Introduction

Integrated circuits (ICs) are part of our daily live as they are the hearts of MP3 players, cell phones, personal digital assistants (PDAs), laptops, and even cars have a high number of integrated circuits. Also the industry mainly depends on integrated circuits in different applications, ranging from simulations of complex processes on main-frame computers to efficient control of production lines.

The history of integrated circuits started around 1960, when analog components were integrated on a piece of silicon for the first time. In 1971, Intel presented the 4004, the first microprocessor of the world with about 2300 transistors. At the time this thesis was written, integrated circuits can have billions of transistors. Hence, integrated circuits are today mostly called VLSI circuits, with VLSI standing for very large scale integration. This enormous complexity of integrated circuits can only be handled if the circuits are designed not by hand, but by algorithms, executed on computers. The usage of such computer algorithms in order to design integrated circuits is called electronic design automation (EDA).

In the year 1965, Gordon Moore [Moo65] detected that the numbers of transistors in an integrated circuit is doubling every 18 months (approximately). Still today, Moore's law is valid [SEM], which means that the complexity of integrated circuit is steadily growing. Therefore, fast and efficient algorithms are necessary for the EDA of future circuits.

## 1.1 Electronic Design Automation

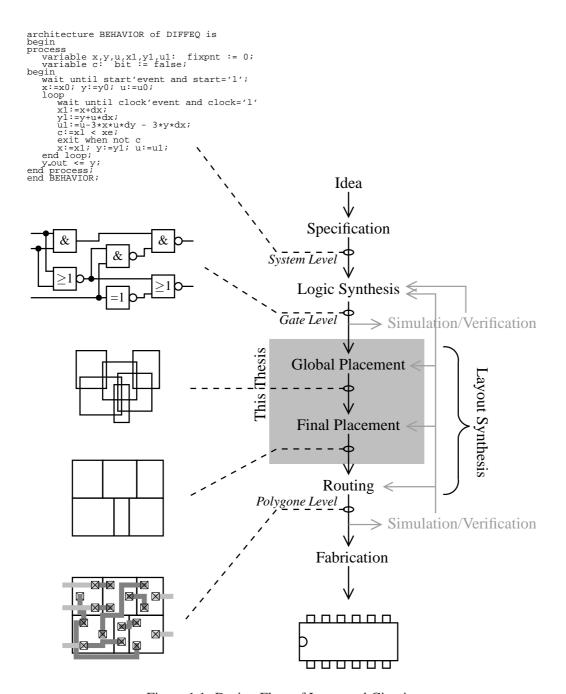

Starting from the idea of a circuit, electronic design automation is done in several steps [SY95, Lie06], as shown in Figure 1.1. In each step, the description of the circuit is refined. After all steps, the circuit can be fabricated.

The first step of EDA is to specify the circuit. Here, the main features like performance, functionality, and physical dimensions are defined. Amongst others, also decisions on the architecture have be done, e.g., which type of processor, or which kind of memory the circuit should use. After this, the circuit is described as a behavior modeled at system level using a hardware description language like VHDL or Verilog. The next step is logic synthesis, which first transforms the behavior description of the circuit into a register transfer description. At register transfer level, the circuit mainly consists of a control unit and a data path. The data

Figure 1.1: Design Flow of Integrated Circuits

path includes registers and functional blocks like arithmetic logic units. Moreover, the data are described as bit vectors. Based on the register transfer model of the circuit, the logic synthesis constructs the gate level description then. At gate level, the circuit consists of gates like inverters, and-gates, or-gates, flip-flops, etc. The gates themselves consists of transistors. The data are described as single bits. After logic synthesis, the gate level description of the circuit is simulated, and different specifications are verified, e.g., the maximal clock frequency. If the specifications are not met, the logic synthesis is done again. If the circuit is working correctly at gate-level, layout synthesis is done next. The main steps of layout synthesis is placement of the gates, and routing of the nets, which interconnect the gates. However, prior to placement, floorplanning is invoked to determine the positions of the I/O pins, the dimensions of big gates, and the dimensions of the chip. Due to the high numbers of gates, placement itself is done in two steps: global placement and final placement. During global placement, the gates are roughly spread on the chip. Final placement then removes the remaining overlap, aligns the gates to a given row/grid structure. There, different design rules are considered, like minimal distances between the gates. This thesis presents novel approaches for global and final placement. After the gates are placed, the nets, which interconnect the gates, are routed. After routing, the polygon level of the circuit is reached, i.e., the circuit is described only by polygons now. At polygon level, the circuit is simulated again, and it is checked if all given specifications are met. If not, the EDA is started from previous steps, and if necessary, it is even started again with logic synthesis. At the end of EDA, the lithography masks are created, and the circuit is fabricated using these masks.

## 1.2 Types of Integrated Circuits

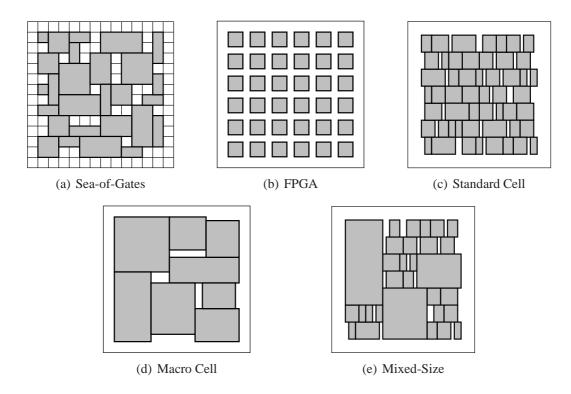

Figure 1.2 displays different types of integrated circuits used today. Each circuit type reflect one design style. The differences between them is mainly the type of gates, and how they are implemented on the "die". "Die" here means the piece of silicon which implements the circuit.

#### 1. Mask-Programmable Gate-Arrays/Sea-of-Gates

The dies of mask-programmable gate-arrays and the dies of sea-of-gates have prefabricated transistors, aligned in a regular pattern. To implement circuits with such dies, the gates of the circuit are broken down to transistors first. Then, the gates as groups of transistors are assigned (placed) to the prefabricated transistors of the die. The routing is done in metal layers, either in channels between the transistors (mask-programmable gate-arrays), or above the transistors (sea-of-gates).

#### 2. Field-Programmable Gate-Arrays (FPGA)

The die of a FPGA is completely prefabricated, and consists of a regular matrix of programmable logic blocks and interconnect blocks. Placement of FPGAs means to assign gates of the circuit to the logic blocks of the FPGA. Routing is done by configuring the interconnect blocks.

#### 3. Standard Cell Circuits

The die of a standard cell circuit is not prefabricated. The circuit is implemented with

Figure 1.2: Different circuit types

gates all having the same height but different widths. Such gates are called standard cells. Placement of standard cell circuits means to align the cells to a row structure. Today, routing of standard cell circuits is done mostly above the standard cells using various routing layers.

#### 4. Macro Cell Circuits

Similar to standard cell circuits, the dies of macro cell circuits are not prefabricated. Macro cell circuits consists of a few, but complex macro blocks, e.g., memory blocks, arithmetic units, or even processor cores. Today, these macros are often so called intellectual property (IP) cores. IP cores are purchased and are available at different description levels: system level (in VHDL or Verilog), at gate-level, or even at polygon level. Considering placement, there are two types of macros. Soft macros have a fixed area but are free in the aspect ratio (relation between width and height). Hard macros have fixed widths and heights. Therefore, placement of circuits with soft macros means not only determining the position of the macros, but also the aspect ratio.

#### 5. Mixed-Size Circuits

Mixed-size circuits consist of a few macros and a high number of standard cells. This circuit type is mostly used today.

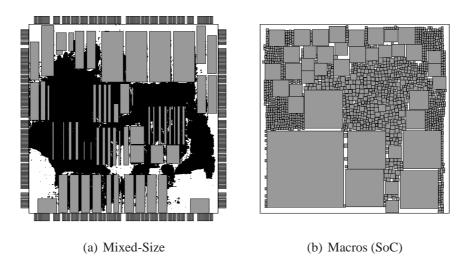

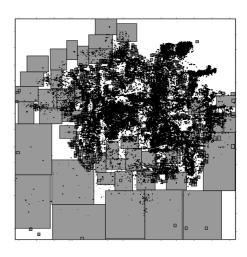

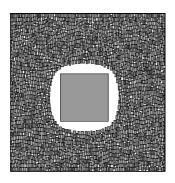

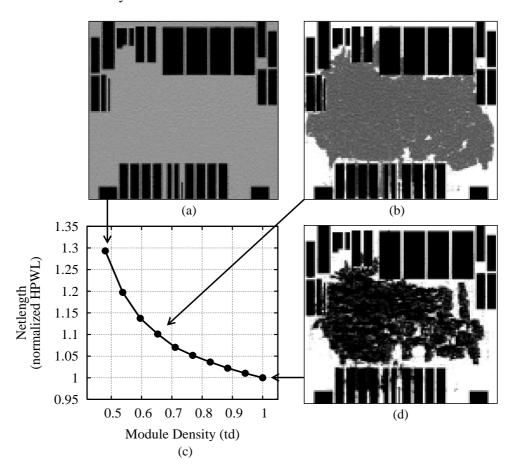

Figure 1.3 shows two modern design styles based on state-of-the-art circuits: (a) mixed-size, and (b) macro cells. Due to the high number of standard cells, these cells are represented as "black clouds" around the gray macros in Figure 1.3 (a). The macro cell circuit depicted

1.3. PLACEMENT 5

in Figure 1.3 (b) represents the widely used System-on-Chip (SoC) design style. There, each macro can represent one system, e.g., processor core, cache block, or network stack.

Figure 1.3: Two modern design styles.

## 1.3 Placement

Placement is one important step of the EDA flow (see Figure 1.1), which highly affects the quality of a circuit. The input of placement is the circuit described at gate-level. This means that the circuit consists of gates, and the gates are interconnected by nets. In the rest of the paper, the gates are called modules. Placement is to determine the positions of the modules, while considering different objectives and constraints. The fundamental constraints are that the modules do not overlap, and that all modules are located within the chip area. Here, it should be noted that today, the chip area is mostly given by floorplanning. An additional constraint of placement is for example to align the modules to rows or to a grid structure. The main objective of placement is to minimize the total wirelength, i.e., to minimize the sum of the lengths of all nets. This objective is used because with a minimal wirelength, the circuit is easy to route, the maximal clock frequency is high, and the power consumption is low. In summary, placement can be formulated as to solve the following problem.

#### **Placement Problem:**

Place all modules such that all relevant objectives (e.g., total wirelength) are optimal and all constraints (e.g., no overlap) are met.

# Chapter 2

## State of the Art

Although the placement problem proposed in the previous section sounds easy, it is a combinatorial problem, which is known to be a NP-complete problem [GJ79, Don80, SB80, Len88, Len90]. This means, there exists no algorithm up to date, which solves the problem optimal with polynomial runtime complexity. In the extreme case, all feasible placements have to be inspected, in order to find the optimal placement. With millions of modules (which is the number of modules in modern VLSI circuits), the number of feasible placements is quite high, i.e., the runtime is not practicable.

Hence, to get good solutions in polynomial runtime, the placement problem is solved by heuristics. One traditional method is to use two steps for placement: global and final placement. In global placement, the modules are spread roughly on the chip, with few overlap remaining. In final placement, the overlap is removed, and the modules are aligned to the grid/row structure. This thesis covers novel solutions for both placement steps. In the following, the state-of-the-art in global placement is described first, including different aspects as net models and routability optimization. Second, the state-of-the-art in final placement is presented.

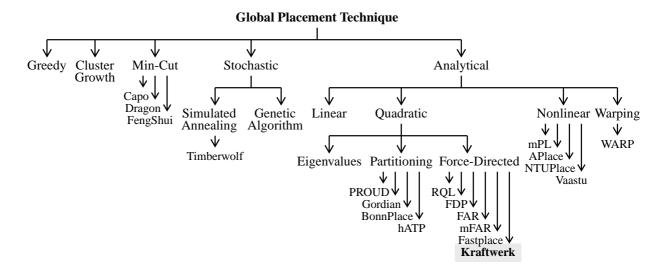

### 2.1 Global Placement

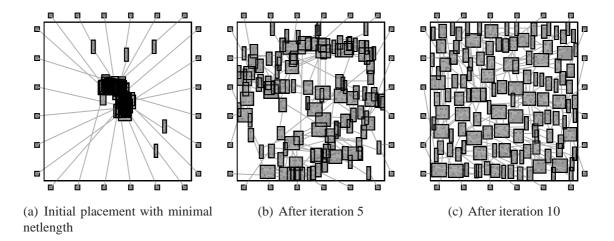

Global placement means to spread the modules roughly on the chip, resulting in a placement with few overlaps. In the previous decades, different algorithms for global placement were developed. They differ mainly in the way how the wirelength is minimized, and how the modules are spread on the chip. Figure 2.1 categorizes different techniques, and lists the names of different state-of-the-art placers. Some of these techniques are able to spread the modules without any overlap on the chip. However, they are mostly stopped if there is only little overlap remaining. This overlap is removed in final placement then.

### 2.1.1 Greedy Placement

Placers based on greedy methods have in common to modify a given start placement over a sequence of iterations, and accept only better placements according to their cost. Here, the

Figure 2.1: Different placement techniques and names of various placers.

start placement can be random, and the cost is mainly a combination of wirelength and overlap. Due to the fact that only better placements are accepted, greedy placers are likely to get stuck in a local minimum, i.e., they will probably not find the optimal solution. In principle, greedy placers modify the placement by permuting modules, either just two modules [HK72, Shu75, Sch76, Bla85a, Bla85b, CP80, IKB83, KP77, HWA76], or three and more modules [HWA76, Got79, Got81]. However, only for circuits with just a few modules, all possible modifications can be tested. For bigger circuits, only neighboring modules can be permuted in practicable runtime. Therefore, heuristics were developed to decide which modules are best to permute [Qui75, HWA76, Got79, Got81]. The main drawback of greedy placers is that they only do a local optimization of the placement. Thus, they highly depend on the start placement.

#### 2.1.2 Cluster-Growth

Placers based on cluster-growth iteratively cluster new modules around already placed modules. Here, the first placed modules can be random. The strategy of cluster-growth placers can be viewed as bottom-up: starting from some placed modules, more and more modules are placed, until all modules are placed. The decision, which modules are clustered, is done based on a cost function representing the wirelength and the module overlap. Placers using this method are for example [SU72, HK72, Shu75, Sch76, HWA76, KP77, Got79, Got81, DK87, LM90, Mül90, YK92, KK92, Lee93, SSL93]. These approaches have good results for small circuits, but degrade with increasing numbers of modules per circuit. This problem is due to the local view of the method, and due to the high dependence on the start placement.

#### 2.1.3 Min-Cut Placement

In contrast to the bottom-up strategy of cluster-growth placers, placers based on min-cut are following a top-down technique. Here, the placement area and the circuit are recur-

sively partitioned. In doing so, parts of the circuit are assigned to parts of the placement area. The recursive process is done until each module is assigned to a unique part of the placement area, which results in a placement with no or just little overlap. The partitioning of the circuit is driven by minimizing the wirelength. In principle, this is achieved by minimizing the number of nets cut ( $\Rightarrow$  min-cut) by a partition. However, partitioning a circuit is a NP-hard problem [SH86]. Therefore, different heuristics were developed for this task [KL70, SK72, FM82, GB83, Kri84, Saa93, LLLC96, DD96b, DD96a, KAKS97, AHK97, CLL+97, ACH+97]. Beside the improvement in partitioning the circuit, the partitioning of the placement area was also improved. The first min-cut placers divided the placement area in two parts (bi-partitioning) in each step of the recursive placement process. [Bre77a, Bre77b, Cor79, Lau79, SH80, BH83, DK83, DK85, LD86, Zim88, SC88]. Later on, four parts [SK87, SK88, Apt90, HK97], and even eight parts [San89, Vij89, ML90] were used. Modern min-cut placers are for example Capo [RPA+05], Dragon [TYC05], and Feng-Shui [AOL+05].

#### 2.1.4 Stochastic Placement

Stochastic placers combine the wirelength and the module overlap in one cost function, and minimize this cost function with stochastic methods. Stochastic methods means to create randomly sets of placements in a sequence of iterations. In the end, the placement with the lowest cost function is chosen as the result. Stochastic placers can easily extend the cost function in order to consider different objectives or various constraints. Moreover, stochastic placers are able to escape from local minima, and are even able to find the optimal solution for the placement problem. However, stochastic optimization in general needs a lot of samples (placements), and thus, stochastic placers are only practicable for circuits with a low number of modules. In principle, there are two main methods of stochastic optimization: simulated annealing and evolutionary algorithms.

#### **Simulated Annealing**

Simulated Annealing [KGV83] follows the annealing process in metallurgy: a hot metal is cooled (over time) such that in the end, it is most perfect (one crystal, no defects). As an optimization method, Simulated Annealing starts with an arbitrary start configuration (placement). Over the iterations, new configurations are created randomly by so called "moves". A move for a placement can be to choose randomly a module, and to change randomly its location. Each new configuration is given a cost, and a decision is made if the new configuration is accepted, and thus replaces the best-so-far configuration. This decision is done based on the cost of both configurations, and based on the current temperature. The temperature is high at the start, and is decreasing over the iterations. As a result, worse configurations are accepted at the start of the optimization process, in order to escape from local minima. At the end, only better configurations are accepted. The method of decreasing the temperature affects highly the quality of the solution [Whi84, HRSV86, LD88, BKT93].

The authors of [RSV85, vLA87, Sec88, OvG89, AK89] showed that simulated annealing is able to find the global optimum. Moreover, the basic operations of the optimization

techniques are easy to implement. Hence, this technique was very popular for placement in the past [SSV85, NSS85, SSV86, WL86, Sec88, WLL88, MFNK96, NFMK96]. However, the number of configurations necessary to find the optimum increases dramatically with the complexity, i.e., the number of modules per circuit. Therefore, different heuristics were used along with simulated annealing to cope with the increasing number of modules per circuit [MG88, HCC92, SKK<sup>+</sup>93, SS95, SW97]. A typical representative of a stochastic placer is Timberwolf [SS93]. Today, simulated annealing is rarely used to place circuits with millions of modules.

#### **Evolutionary Algorithms**

Evolutionary algorithms use mechanisms inspired by biological evolution: heredity, mutation, selection, and survival of the fittest. In placement, evolutionary algorithms start by creating a set of random placements. In an iterative process, new placements are created based on current placements (heredity), and based on random changes (mutation). Then, the new placement are selected according to their cost. Over the iterations, the better placements survive, and at the end, a good placement is found. In principle, the basic operations of evolutionary algorithms are simple, and the optimization can be run in parallel using numbers of computers. However, the runtime is still high for modern circuits. Evolutionary algorithms for placement are presented in [CP86, CP87, KB89, SM90, KB91, RR96, EK97].

#### 2.1.5 Analytical Placement

Analytical placers are based on an analytical cost function, which is continuous and in most cases differentiable. The minimum of the analytical cost function is determined by numerical optimization. Mostly, the cost function represents the wirelength, and sometimes it is a combination of wirelength and overlap. Depending on the cost function, analytical placers can be subdivided in linear, quadratic and non-linear placers.

#### **Linear Placement**

Linear placers are using a linear cost function, and remove the module overlap by linear constraints between the modules. This gives a linear program. However, such programs have a high computational complexity. Hence, linear placers like [WM87, HWM86, WM88, JK89, RC06] can only be used for circuits with a low number of modules. The analytical cost function in linear placement can be non differential (e.g., using the absolute value function). In all other analytical placement approaches, the cost function is differentiable.

#### **Quadratic Placement**

All quadratic placers represent the wirelength in a quadratic cost function  $\Gamma$ :

$$\Gamma = \frac{1}{2} \sum_{i,j} w_{x,ij} (x_i - x_j)^2 + w_{y,ij} (y_i - y_j)^2$$

(2.1)

$\mathbf{p_i} = (x_i, y_i)$  is the position of module i.  $\Gamma$  is the sum of the weighted quadratic Euclidean distances between pairs of modules (i and j). The pairwise connections are called two-pin connections. To represent the wirelength by two-pin connections in  $\Gamma$ , a net model is necessary in quadratic placement. Next Section 2.3 gives an overview on net models in general, and on state-of-the-art net models for quadratic placement. Amongst others, this thesis presents a novel net model for quadratic placement.

Representing the positions of all N movable modules in vector  $\mathbf{p} = (x_1, x_2, ..., x_N, y_1, y_2, ...y_N)^T$ , the sum notation of the quadratic cost function (2.1) can be represented in a matrix-vector notation:

$$\Gamma = \frac{1}{2} \mathbf{p}^T \mathbf{C} \mathbf{p} + \mathbf{p}^T \mathbf{d} + const$$

(2.2)

Matrix C represents the connections between movable modules, and vector  $\mathbf{d}$  reflects the connections between movable and fixed modules. Fixed modules are for example I/O pins (input/output pins). By minimizing  $\Gamma$ , quadratic placers obtain the module positions  $\mathbf{p}$  with minimal netlength, which is the optimal placement. Since minimizing just the netlength results in a lot of module overlap, quadratic placers need a method to reduce the overlap. Depending on this method, quadratic placers can be subdivided into three categories: based on eigenvalues, based on partitioning, and based on forces.

#### **Eigenvalue-Based Quadratic Placement**

Quadratic placers based on Eigenvalues assume that all modules are movable, i.e.,  $\mathbf{d} = \mathbf{0}$  in (2.2). To reduce the module overlap, and to spread the modules on the placement area, these placers are using the constraint  $\mathbf{p}^T\mathbf{p} = const$ . Combining this constraint with the quadratic cost function  $\Gamma$  by Lagrangian relaxation gives a new function, whose minimum is found by setting its derivative (with respect to  $x_i$  and  $y_i$ ) to zero. This results in  $\mathbf{C}\mathbf{p} - \lambda\mathbf{p} = \mathbf{0}$ , which is similar to determining the Eigenvalues and Eigenvectors of  $\mathbf{C}$ . Then, the module positions are given by the Eigenvectors with the lowest Eigenvalues. Eigenvalue quadratic placers are for example [Hal70, Ott82a, Ott82b, FYSK83, Bla85a, Bla85b, FK86]. Since computing Eigenvalues and Eigenvectors is complex, quadratic placers based on this technique are rarely used to place state-of-the-art circuits with millions of modules.

#### **Partitioning-Based Quadratic Placement**

In order to reduce the module overlap, partitioning-based quadratic placers divide recursively the circuit and the placement area, and assign parts of the circuit to parts of the placement area. In contrast to min-cut placers, which use a similar technique for placement, partitioning-based quadratic placers minimize a quadratic cost function in each step of the recursive placement process. In quadratic placement based on partitioning, different techniques are used to partition the placement area, to partition the circuit, and to hold the modules in the placement region to which they are assigned.

The authors of [WWM82, Wip85] presented a placer, which first places the modules by minimizing the quadratic cost function, and then assigns modules to placement regions us-

ing a technique similar to min-cut. In [CK83, CK84], a method is described, which recursively partitions the placement area in two regions. In each iteration of recursion, the positions of the modules are used to partition the circuit, and to assign the modules to placement regions. To place the modules in one region, the modules of the other regions are fixed, and linear constraints (center-of-mass constraints) are used to spread the modules. PROUD [TKH88a, TKH88c, TKH88b] is similar to this technique, but does not utilize linear constraints. To spread the modules in one region, the fixed modules of the other regions are projected to the border of the current region. With the recursion, the placement regions, and the number of modules assigned to them are continuously decreasing. By placing only the modules in one region, and fixing all other modules, the placement problem is solved more and more locally. This will decrease the quality of the solution. In contrast to this, Gordian [KSJ88, KSJ89, Kle89, KSJA91] places all modules concurrently in all iterations of the recursive partitioning process. The partitioning is driven by the module positions. To hold the modules, which are assigned to one placement region, in this region, Gordian uses center-of-mass constraints. GordianL [SDJ91, Sig92] improves the method for partitioning the placement area, and introduces weights in the quadratic cost function, which are used for linearization the quadratic wirelength.

BonnPlace [Vyg97, BS05], and hATP [NRA+06] partition the placement area in four regions in each step of recursive placement process. A min-cost-max-flow is used to partition the circuit, and to assign modules to placement regions. To hold the modules in their placement regions, BonnPlace and hATP use center-of-mass constraints, and so called "terminals". These terminals arise while cutting the nets by partitioning. In other words, the terminals connect two nets of two partitions, which where formerly one net in one partition. The terminals are located at the border between two partitions, are treated as fixed modules, and results in that the modules in each placement partition stay within its partition. In addition, with the fixed terminals, each placement partition can be placed concurrently using different CPUs. This improves runtime, but advanced methods for positioning the terminals are necessary in order to prevent a decline in the placement quality.

In general, partitioning quadratic placers are able to place modern circuits in reasonable runtime. Since they reduce the module overlap by partitioning, and mostly ignore the module dimension here, they are problematic if the modules are of different dimension like in mixed-size circuits.

#### **Force-Directed Quadratic Placement**

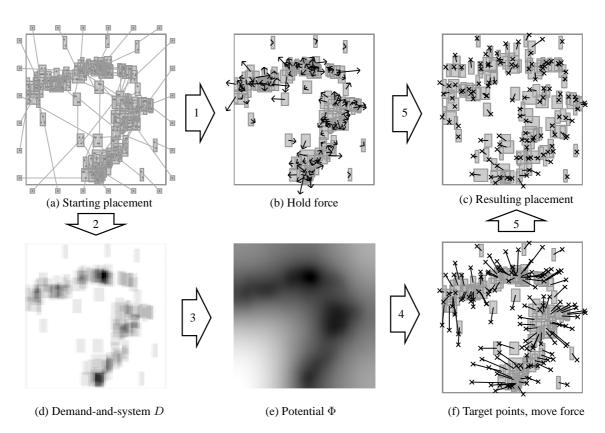

The two-pin connections used in (2.1) for the quadratic cost function  $\Gamma$  can be viewed as elastic springs. This creates a spring system, and  $\Gamma$  represents the total energy of the spring system. The derivative of  $\Gamma$  is the "net" force, created by the springs:  $\mathbf{F}_{net} = \mathbf{Cp} + \mathbf{d}$ . Setting this force to zero gives the module positions with minimal wirelength, which equals the equilibrium state of the spring system. In other words, the springs, i.e., the two-pin connections, of quadratic placement create a force, which attracts the modules. Force-directed quadratic placers utilize an additional force  $\mathbf{F}_{add}$  to spread the modules on the placement area. This spreading is done in a sequence of placement iterations. Each iteration starts with a given placement. Then, an additional force is determined. Setting the sum of the net force and the

additional force to zero results in a system of linear equations. This system can be solved efficiently with respect to **p**. At the end of each placement iteration, the modules are placed to the positions described by **p**.

Different approaches exist for the additional forces. In [FCW67], the additional force is modeled in that all modules are repelling each other. However, this results in a high number of additional forces. To reduce the computational complexity, other approaches utilize repelling forces only between unconnected modules. In [Sca71, Qui75, QB79, AJK82, JJA83, Kir84, For87, Jus87], the repelling force is constant over the distance between the not connected modules. In [FCW67, QB79, Kir82, Waw88], the repelling force is reciprocal to the distance. Another modification is to model the overlaps between the modules rather than the modules themselves as the source for the repelling force. In [Sca71, Shu75, Rob83, SD85, SB87, AA88, KKM91] overlaps between modules are repelling each other. The overlap between modules and the border of the placement region is modeled in [FCW67, Shu75, KKM91] as the source for the repelling force. In [Joh87], the triangulation of the placement area based on the module positions is used to determine a force, which spreads the modules on the placement area.

Modern force-directed quadratic placers like Eisenmann's approach [EJ98, Eis99, Obe05], FDP [VKV04, VK05a, VK05b, KV06], FAR [HMS02b], mFAR [HMS05], FastPlace [VC05, VPC06, VPC07], and RQL [VNA+07], have in common to use the distribution of the modules on the placement area to determine one additional force per module. This force drives the modules away from high density regions towards low density regions. The above mentioned modern force-directed placers differ in the way how the additional force is implemented, i.e., in the way how the force is determined and modeled. Since this thesis presents a force-directed placer, details and differences of modern force-directed placers are described in the following; Figure 2.2 gives an overview.

| Placer                     | Controlling Force<br>Hold Force | Spreading/Perturbing Force<br>Move Force |  |

|----------------------------|---------------------------------|------------------------------------------|--|

| Eisenmann's approach, FDP* | Const. Force, Potential         |                                          |  |

| FastPlace, RQL             | Fixed Points, Bin Utilization   |                                          |  |

| FAR                        | Fixed Points                    | Const. Force, Potential                  |  |

| mFAR                       | Fixed Points                    | Fixed Points, Bin Utilization            |  |

| Kraftwerk                  | Const. Force                    | Target Points, Potential                 |  |

Figure 2.2: Implementation of the additional force in modern force-directed quadratic placers. \*FDP uses two more forces, but they are not necessary to spread the modules on the chip. A dark gray box means that heuristics are necessary. A light gray box means low controllability.

Eisenmann's approach is based on the idea that modules are positively charged, the placement area is negatively charged. Thus, the modules repel each other, and the modules are attracted by the placement area. The distribution of the charges on the placement area is used to determine an electrostatic potential. For each module i, the gradient of the potential is

determined, and the gradients are accumulated in the additional force over the placement iterations. The additional force in Eisenmann's approach is modeled as constant force, i.e., the force does not depend on p.

Using a constant force is one way to model a force. Another way to model a force is to use fixed points (each located at  $\mathring{p}_i$ ), and connect each module to its fixed point by an elastic spring having the strength  $s_i$ . This spring creates the force then.

$$\mathbf{F}_{\mathbf{i}}^{\mathbf{spring}} = s_i \left( \mathbf{p}_{\mathbf{i}} - \mathring{\mathbf{p}}_{\mathbf{i}} \right) \tag{2.3}$$

The authors of [HMS02b] showed that using fixed points are a generalization of using a constant force, and they showed that fixed points control the placement better than constant forces do. In principle, the controllability is improved because each module is moved at most to its fixed point in each placement iteration. Using a constant force, the movement is not limited.

FDP is similar to Eisenmann's approach in that the gradients of the potential are accumulated in a constant force to spread the modules on the chip. In addition, FDP used two forces to stabilize the placement algorithm, and to improve the netlength. These two forces are modeled by fixed points in FDP. Similar to Eisenmann's approach, FAR utilizes an electrostatic potential to determine a force, which spreads the modules on the chip. This additional force is modeled as a constant force. Instead of accumulating the spreading force over the iterations, FAR uses a second additional force for each module to control the placement process. This force is modeled by fixed points and is determined by achieving force equilibrium at the start of each placement iteration. The main difference between FAR and mFAR is that mFAR uses a local bin utilization to determine the spreading force, and the spreading force is modeled by fixed points. Using a local bin utilization, the spreading force has a local view, as the force of one module depends only on the surrounding modules. In contrast to this, the (spreading) force in Eisenmanns' approach, FAR, and FDP has a global view, i.e., the force of one module depends on all modules. This is because the force is based on potential formulation there, and the potential represents all modules.

Instead of accumulating one additional force over the placement iterations, or using two additional forces, FastPlace and RQL are using a different method to spread the modules. In each placement iteration, a local bin utilization is determined similar to mFAR. The additional force for one module i is then determined as follows. Module i is temporary placed to the position determined by the local bin utilization. This can be viewed as a local diffusion process. Then, the force is determined, which holds module i at its temporary position. After that, module i is put back to its original position. After determining the additional force for all modules, the new positions for all modules are obtained by setting the sum of the net force and the additional force to zero. The additional force is modeled by fixed points. In FastPlace, the fixed points are located at the border of the placement regions. RQL uses a location between the border and the module position. In addition, RQL modulates the additional force, which means that for some modules, the additional force is ignored. With this, the modules are reordered during placement, which can improve the netlength. On the other hand, the convergence of the placement algorithm can be harmed.

In summary, fixed points are widely used in modern force-directed quadratic placers. The locations of the fixed points are all determined in that a force is given. This force is to be

represented by the spring connection between each module and its fixed point. In this case, where the force is given, a good heuristic is necessary to obtain suitable locations of the fixed points. This is a well-known critical problem of using fixed points [HMS02b, HMS05, VNA+07].

$$\mathbf{F}_{\mathbf{i}}^{\mathbf{spring}}\Big|_{\mathbf{p}_{\mathbf{i}}=\mathbf{p}_{\mathbf{i}}'} = \mathbf{e}_{\mathbf{i}} \quad \Leftrightarrow \quad \mathring{\mathbf{p}}_{\mathbf{i}} = \mathbf{p}_{\mathbf{i}}' - \frac{1}{s_{i}}\mathbf{e}_{\mathbf{i}}$$

(2.4)

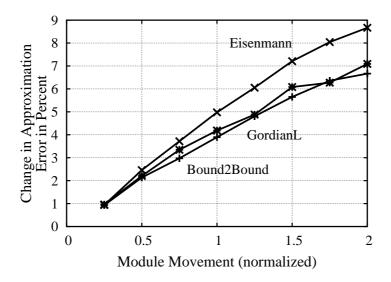

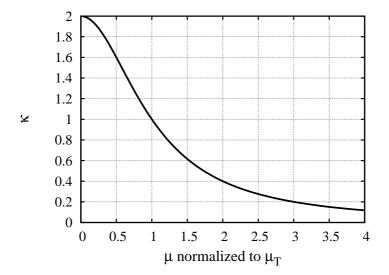

In (2.4), the force  $\mathbf{e_i}$  of module i is given, and the module is located at  $\mathbf{p'_i}$ , i.e.,  $\mathbf{p_i} = \mathbf{p'_i}$ . If the strength  $s_i$  of the spring is too low, the fixed point  $\mathbf{p'_i}$  is too far away from the module position  $\mathbf{p'_i}$ , and the force is modeled like a constant force, resulting in low controllability. If the strength  $s_i$  is too high, the fixed point is too near to the module, and the module movement is highly limited. Thus, all modern force-directed placers, using fixed points, rely on heuristics for good values of  $s_i$ . The force-directed quadratic placer Kraftwerk, as presented in this thesis, also uses fixed points (called "target points"), but does not depend on critical heuristics. Rather, the locations of the target points are directly given by the gradients of an electrostatic potential. In other words, not the force is given, but the location of the target points. In Kraftwerk, two forces are used: a moving force, modeled by target points, and a hold force, modeled as a constant force. The constant hold force does not reduce controllability of the placement process, but enforces the convergence.

#### **Nonlinear Placement**

Nonlinear placers are based on a nonlinear cost function, which is even not quadratic. Placers based on nonlinear cost functions have appeared in the recent years, after developing an efficient representation of the wirelength by a log-sum-exp function [NDS01]. The major drawback of nonlinear placers is that nonlinear numerical optimization takes high runtimes. Nonlinear placers differ mainly in the way how the module overlap is removed.

#### Density-Driven Nonlinear Placement

Density-driven nonlinear placers are using the distribution of the modules on the placement area (i.e., the module density at various points) to determine a nonlinear function, which represents the module overlap, and which is continuous and differentiable. This function is combined with the wirelength function in a total cost function, and the total cost function is minimized by nonlinear numerical optimization. In this way, the modules are iteratively spread over the placement area. Examples for density-driven nonlinear placers are APlace [KW05a, KRW05], mPL [CCS05], and NTUPlace [CJH<sup>+</sup>06].

#### Nonlinear Placement Based on Pseudo Nets

Nonlinear placers based on pseudo nets are using additional "pseudo" nets (one for each module). This is similar to the fixed point approach used in force-directed quadratic placement. Minimizing the wirelength of the nets and the pseudo nets, the modules are spread iteratively over the placement area. In each placement iteration, Vaastu [AM07] is using a min-cost-max-flow to assign modules to placement regions. Then, the pseudo nets are created between each module and the center position of the placement region to which the module is assigned. In other words, and considering force-directed quadratic placement, the fixed points of the

pseudo nets are determined by a min-cost-max-flow approach in Vaastu. Other nonlinear placers using pseudo nets are not known up to now.

#### 2.1.6 Warping Placement

Placers based on warping start with an initial placement, and are using approaches of computational geometry to deform the placement area, and thus moving the modules indirectly. The deformation of the placement area is driven by minimizing the wirelength and the module overlap. Placers based on warping are for example [XMFR04, XR07, CS07]. To obtain the initial placement, warping placers usually follow quadratic placement and minimize the quadratic wirelength.

## 2.2 Multilevel Approach

To place "large" circuits, i.e., circuits with a high number of modules, some placement approaches are following a hierarchical approach. Min-cut placers, placers based on cluster-growth, and some partitioning placers are per se hierarchical, because not all modules of the circuit are placed simultaneously in all placement iterations.

A general hierarchical approach to cope with "large" circuits is the multilevel approach, which can be used for all placement techniques. Starting from the "flat" circuit, which consists of all modules, the modules are clustered over a few levels during the coarsening phase. Then, the coarsest circuit is placed. In the refinement phase, the placement of the previous level is used as input, the clusters are declustered, and the new "refined" circuit is placed. The refinement is done until the flat circuit is placed. Since only some placement iterations are spent in each level of refinement, and in particular only some iterations for the flat circuit, the runtime decreases with the multilevel approach. However, the major drawback of the multilevel approach, and of all hierarchical approaches in general, is that a good heuristic is necessary to partition or cluster the circuit. This is because optimal partitioning is an NP-hard problem [SH86]. In addition, using a hierarchical approach, the placement problem is solved more locally then using a flat approach, where all modules are placed concurrently in all placement iterations.

#### 2.3 Net Models

The previous sections described different techniques to solve the placement problem. The general objective of the placement problem is to minimize the total length of all nets. This objective is used because a placement with minimal netlength is usually optimal also in other objectives like area consumption, routability, timing (length of the critical path), etc. This section describes how to measure the length of one net. There, the net is represented by graphs, different net metrics are shown, and net models necessary for quadratic placement are presented.

2.3. NET MODELS

#### 2.3.1 Graphs and Metrics

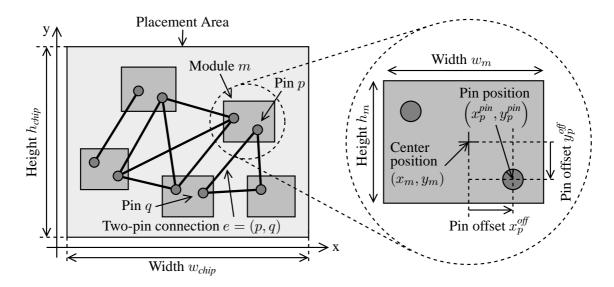

In principle, one arbitrary net consists of N pins, and each pin i=1,2,...,N is located at  $(x_i,y_i)$ . The property of a net is that all its pins must have the same electric potential. Consequently, all pins of one net must be connected by a wire. Using graph theory, the pins are nodes, and the connections between the nodes are represented by edges (each connecting two nodes), or by a hyperedge (each connecting two or more nodes).

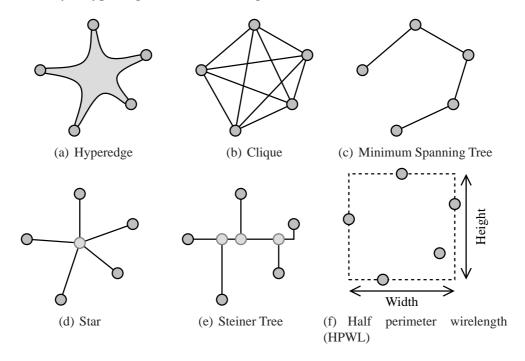

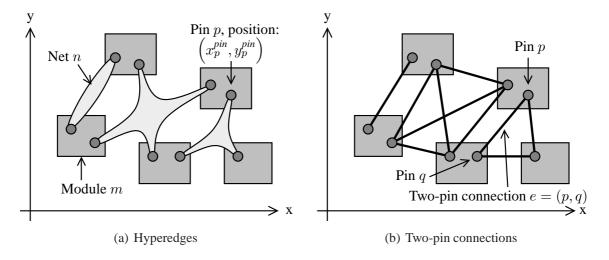

Figure 2.3: Different net models.

Figure 2.3 shows different net models. The hyperedge net model, as displayed in Figure 2.3(a), consists of one hyperedge, connecting all pins of the net. All other net models are using two-pin connections to represent the net. There, each two-pin connection, i.e., each edge e=(i,j) between two pins i and j, is associated a cost, and the cost represents the distance between both pins. Using the Manhattan norm, which is based on just using horizontal and vertical wires, the distance between both pins is  $|x_i-x_j|+|y_i-y_j|$ . In the quadratic Euclidean norm, the distance is  $(x_i-x_j)^2+(y_i-y_j)^2$ . This quadratic norm is used in the next section addressing net models for quadratic placement.

The clique net model (see Figure 2.3(b)) uses all possible two-pin connections of one net. The number of two-pin connections is  $0.5 \cdot N \cdot (N-1)$ . The minimum spanning tree model [Pri57], which is displayed in Figure 2.3(c), is driven by using a minimal set of edges, whose total cost is minimal. Here, there are N-1 number of edges. However, the construction of the minimum spanning tree needs some runtime, and the runtime complexity is more than O(N) [Eis97]. The star net model (see Figure 2.3(d)) uses one additional star pin, which is located in the center of the net, and connects each pin with the star pin. This results in N edges, and the runtime complexity is O(N). The Steiner tree net model, as shown in Figure 2.3(e), uses several additional pins, and is driven by connecting all pins by horizontal or vertical

edges only. In the minimal Steiner tree, the edges are chosen such that the total cost of all edges is minimal. Finding such an optimal Steiner tree is known to be a NP-hard problem [GJ77]. However, there exist numbers of algorithms, which find a near-optimal Steiner tree in practicable runtime [Han66, Hwa79, Ser81, CRS88, HVW90, GRSZ94, Chu04]. Since routing of a net is similar to constructing the minimal Steiner tree, the routed wirelength, i.e., the wirelength after routing, is best approximated by length of the minimal Steiner tree. However, routing is more complex than just constructing the minimal Steiner tree, as more things have to taken into account in routing. For example, there is only a limited number of routing tracks available in a chip, which limits the resources for routing. Or not only the wirelength is to be minimized in routing, but also the number of vias.

The half-perimeter wirelength (HPWL), as illustrated in Figure 2.3(f), is rather a metric for the netlength, than a net model. Here, "half-perimeter" means the half-perimeter of the smallest rectangle enclosing all pins of the net. The width of this rectangle is given by  $w = \max x_i - \min x_i$ , and the height is given by  $h = \max y_i - \min y_i$ . Then, the HPWL is w + h. The HPWL equals the length of the minimal Steiner tree for nets with two or three pins [Han66]. For nets with four and more pins, the HPWL is a lower bound. Since most of the nets of a circuit are two and three pin nets, the HPWL is an efficient estimation of the length of the minimal Steiner tree [Chu04], and consequently, it is an efficient estimation of the routed wirelength [Ser81, SKAS88]. Here, efficient means that the HPWL offers low runtime and good approximation.

#### 2.3.2 Net Models for Quadratic Placement

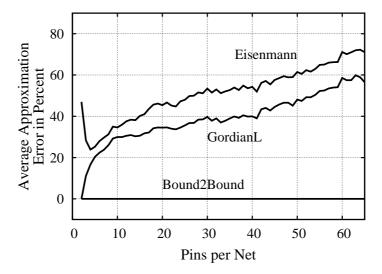

Quadratic placement is based on two-pin connections, and minimizing a quadratic cost function (2.1), which represents the sum of the quadratic lengths of the two-pin connections. Since the runtime complexity of determining suitable two-pin connections is practicable in the clique and the star net model, these net models are used widely in quadratic placement. Traditionally, the weights of the two-pin connections are used to linearize the quadratic length, and to approximate the quadratic cost function to the HPWL metric.

Considering one net with N pins, a weight of 1/N in the clique net model adapts its quadratic costs to the cost of the corresponding star net model [Sig92, VC05]. Hence, clique and star net model can be used interchangeably. The authors of [Vyg97, BS05] use an additional weight of 1/N-1 for each net, in order to prevent that nets with a high number of pins are dominating the quadratic cost function. In [SDJ91, Sig92], the additional weight for each net is 2/N, and a linearization weight for each two-pin connection is used, in order to adapt the quadratic cost to the HPWL.

Since the clique and the star net models have different characteristics, and both can be used concurrently, there is a trade-off between both net models [EJ98, Eis99, VC05]. The clique net model has no additional star pin, but a complexity of  $O(N^2)$  in the number of two-pin connections. The star net model introduces one additional star pin per net, but has only O(N) two-pin connections. To minimize the quadratic cost function in short runtime, the number of two-pin connections, and the number of pins should be as low as possible. In an average circuit, most of the nets have two or three pins, and nets with a high number of pins are rare. Hence, the clique model is used for small nets, i.e., for nets with a about six or less

pins, as the number of two-pin connections is reasonable here. For big nets, the star net model is used, as the number of two-pin connection is low here, and the number of additional star pins is reasonable. Using clique and star net models concurrently in a circuit gives the hybrid clique/star net model.

The authors of [BS05] propose a net model suitable for partitioning quadratic placers, which is based on the star net model, but introduces additional pins (so called "terminals") for those nets, which cross the border of two placement partitions. In [OJ04a, Obe05], a method is described, which integrates the minimal Steiner tree in the quadratic cost function. This is used to obtain better timing-driven placements. However, determining a minimal Steiner tree is time consuming.

This thesis presents a new net model, which accurately represents the HPWL in the quadratic cost function. Compared to a hybrid clique/star net model, the new net model offers better placements in lower runtime.

## 2.4 Routability-Driven Placement

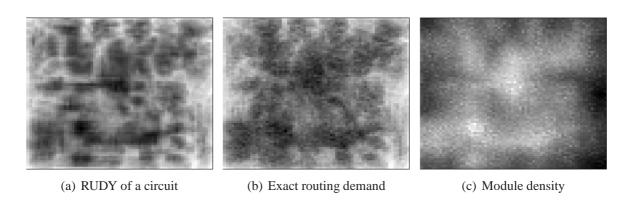

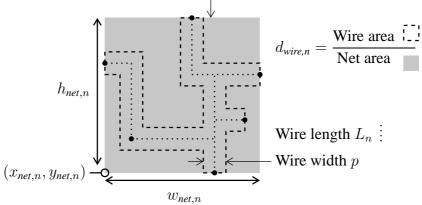

In the layout synthesis of an integrated circuit, the modules are placed first, and the nets are routed then. These are two separate steps, mostly done by two different computer programs. Placement traditionally targets to minimize the total wirelength, which in general improves routability. However, the placed circuit may not be routable, because there are so called "congested regions" on the chip, where too many wires are necessary to route the nets than routing tracks are available. In other words, the routing demand, created by the nets, exceeds the routing supply, given by the routing layers. Due to such congested regions, the circuit has a high routed wirelength, or is even not routable. Therefore, besides minimizing the total wirelength, placement has to be driven by routability, which means to remove the congestions during placement. To do routability-driven placement, two problems have to be solved. First, a fast and accurate method to estimate the congestions is necessary. This is because the exact informations about congested regions would be given after routing, but routing itself takes enormous runtime. Second, the congestion estimation has to integrated effectively in the placer. This thesis presents novel solutions for both problems. Therefore, the state-of-the art in congestion estimation and in the integration in placement is described next.

## 2.4.1 Congestion Estimation

Assuming a constant routing supply, congestion estimation means to estimate the routing demand. Most published methods to estimate the routing demand are using a grid structure to divide the chip area into a number of bins, and estimate the routing demand in each bin.

Based on the bounding box of one net, i.e., the smallest rectangle enclosing all pins of one net, the authors of [IEC94] presented a simple method to estimate the routing demand in one bin: the routing demand of one net in one bin depends on the overlap between the bounding box of the net and the bin. Another simple technique to estimate the routing demand in one bin is to use the pin density within this bin [BR02, ZD02]. A widely applied technique to estimate the routing demand is to use a routing model, which models possible routes of each

net. The number of possible routes crossing the border of a bin reflects the routing demand in the bin. In most approaches based on routing models, multi-pin nets are broken down into two-pin connections by using a minimum spanning tree. Then, for each two-pin connection, different routes with different number of bends are modeled. The authors of [LKS02] use all possible routes for each two-pin connection. This probabilistic routing model is improved in [KX03, SZJ06] by adjusting its result to the result obtained by routing. The authors of [WBG04] state that one- and two-bend routes are enough to model the routing demand. In [PC06], a fast global router is proposed, which uses different Steiner Trees to model the possible routes of each net. In [YKS01, YKS02, HMS02a], the maximal routing demand of a circuit is estimated based on Rent's Rule [LR71]. Another technique to estimate the routing demand is the analysis of the distribution of the number of nets per bin [WYES00].

#### 2.4.2 Integration in Placement

Estimating the routing demand in an efficient way is the first step to optimize routability during placement. The second step is to integrate the estimation of the routing demand in the placement algorithm, in order to remove the congestions and to improve routability. Since the congested regions are characterized that the routing demand of the nets is higher than the supply by the routing layers, there exist two main approaches to optimize routability. The direct approach reduces the routing demand in congested regions, and the indirect approach increases the routing supply in congested regions. The routing supply can be increased, because modules block some routing layers, and with a lower module density, more free space is available in the routing layers. The routing demand can be decreased by replacing modules, such that the nets connected to the modules are moved out of the congested regions. The direct approach is often used as a post-process to tune an already placed circuit for routability. A post-process utilizing Simulated Annealing is described in [IEC94, HMS02a, WS99]. A flow-based method is presented in [WYS00, WS00]. Linear programming is used in [LWH03].

The indirect approach to optimize routability is mostly used during placement. In [HYH<sup>+</sup>01, BR02], a quadratic placer is described, which inflates modules in congested regions. The authors of [PBS98] present a quadratic placer, which reduces module density in congested regions by growing these regions. In [YCS03], a min-cut placer is shown, which allocates white space, i.e., reduces module density, in congested regions during top-down placement.

In the following, routability optimization in state-of-the-art placers is described. mPL [LXK+04, LXK+07] is a multilevel analytical placer based on non-linear optimization. mPL estimates the routing demand based on a two-pin connection routing model developed in [CCPY02]. Routability is optimized in global placement by moving certain modules out of congested regions in order to reduce the routing demand there. In final placement, a white space allocation (WSA) method is used, which is based on recursively partitioning the placement area, and shifting the cut lines according to the routing demand. Thus, mPL utilizes the direct approach during global placement, and the indirect approach after wards in detailed placement.

ROOSTER [RLM06], as a feature of Capo 10, is a min-cut placer. The placer models nets by Steiner trees [Chu04], and estimates the routing demand by a probabilistic routing model [WBG04]. The cut lines are shifted during global placement based on the routing de-

mand. During final placement, the WSA method of [LXK<sup>+</sup>04] is used. Therefore, ROOSTER applies the indirect approach to optimize routability.

APlace [KW05b] is a multilevel analytical placer based on non-linear optimization. APlace estimates the routing demand by a probabilistic routing model [KX03]. Routability is optimized during global placement by decreasing module density in congested areas, i.e., by the indirect approach.

#### 2.5 Final Placement

The global placement approaches proposed in Section 2.1 spread the modules roughly on the chip, while considering different objectives like total wirelength and routability. After global placement, final placement is done. Final placement itself consists mostly of two consecutive steps: legalization and detailed placement. In legalization, the remaining overlap of the global placement is removed, and the modules are aligned to a row or grid structure if necessary. In detailed placement, the legal placement is improved such that the total wirelength is further reduced, or more complex objectives like design for manufacturing (DFM) [GKP05] or design for yield (DFY) [ABD+07] are considered. The common approach in detailed placement is to use small sliding windows in order to capture a low number of modules (about 10 modules), and to do different transformations on this set of modules. For example, single modules are rotated, pairs of modules are exchanged, or all modules in the set are permuted [CKM00, CX06, LXK+07, PVC05, RPA+07]. In [KTZ99, BV00], a detailed placement approach suitable for standard cell circuits is described. There, the modules in each row are placed such that their total HPWL netlength is minimized. The ordering of the modules is not changed here.

Since this thesis describes new approaches for legalization, this section focuses on the state-of-the-art techniques for legalizing a global placement. To preserve the global placement as far as possible, the common objective of legalization is to move the modules as little as possible. While most global placement approaches can deal with different circuit types like standard cell circuits, macro cell circuits, and mixed size circuits, legalization approaches differ in the circuit type for which they are applicable. This difference in legalization is because of the different "design rules" for each circuit type. So, the modules of FPGA circuits, and the modules of sea-of-gates circuit have to aligned to a grid structure. The modules of standard cell circuits have to be aligned to rows. And the modules of macro cell circuits have not to be aligned to rows. These design rules are mostly ignored during global placement as the modules are spread just roughly on the placement area. Because of the difference in the application of the legalization approaches, the modules of global placement are now called standard cells, or macros. In the following, state-of-the-art approaches for legalizing standard cell circuits are proposed. Most of the approaches are also applicable for FPGA circuits, and for sea-of-gates circuits. In addition, modern methods for legalizing macros are described. In Chapter 7, novel approaches for legalizing these two circuit types are presented.

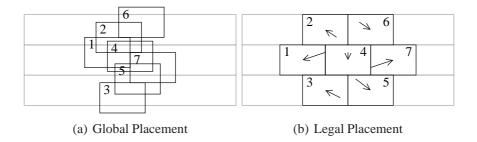

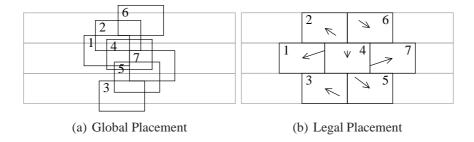

Figure 2.4: Global and legal placement of standard cells.

### 2.5.1 Legalization of Standard Cell Circuits

Figure 2.4 displays a global and legal placement of a (very small) standard cell circuit. Various approaches exists for legalizing standard cell circuits. Domino [DJA94] is based on network flow, shreds cells into subcells and rows into places. Here, all subcells and all places have the same height and width. The subcells are placed, i.e., assigned, to places by solving a min-cost-max-flow. The authors of [BV04, BPV04] present a similar method as Domino, but assign sets of modules to row regions by a min-cost-max-flow. Fractional Cut [YKM+03] is a two stage approach: first the cells are assigned to rows by dynamic programming, then the cells of each row are packed from left to right. The authors of [KMR04] also present a two stage approach: first the cells are assigned to the rows by heuristical cell juggling, then the cells of each row are placed by finding a shortest path in a graph. Mongrel [HL00] uses a greedy heuristic to move cells from overflowed bins to under capacity bins in a ripple fashion based on total wire length gain. Diffusion based placement migration is presented in [RPAV05] to remove cell overlap. In [LRAP07], computational geometry is used to spread the cells, and to align them to rows. NRG [SW97] uses simulated annealing for legalization.

Tetris [Hil02] is a fast greedy heuristic, which is used widely [LXK<sup>+</sup>07, KW05a, KLA<sup>+</sup>04], for example. In [LK03] a similar approach to Tetris is described. Tetris sorts the cells first, and legalizes one cell at a time then. Legalizing one cell is done by moving the cell over the rows, and within the rows by moving the cell over free places. This movement is done until the nearest free place is found. Once a cell has been legalized, it will not be moved anymore. This results in a high total cell movement during legalization.

## 2.5.2 Legalization of Macros in Mixed-Size Circuits

In pure macro circuits, which consist only of macros, legalizing can be driven by minimizing the area consumption, rather than the macro movement. Such legalization of macro circuits can be done for example with shape-functions [Ott83, SS91], sequence-pairs [MFNK95, MFNK96], or B\*-trees [CCWW00, WC04, cCYc+07].

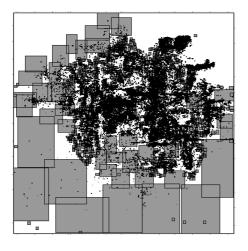

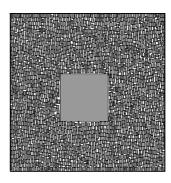

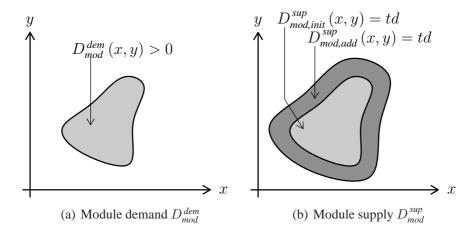

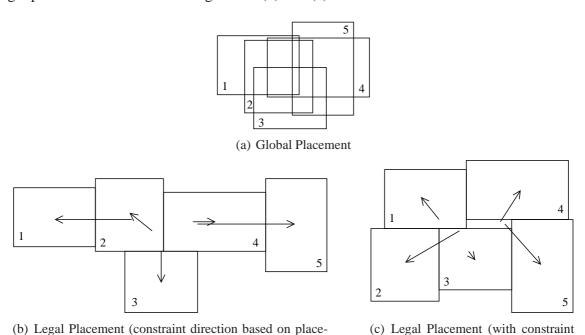

However, mixed-size circuits consist of a few macros, and millions of standard cells. Figure 2.5 displays a global and a legal placement of such a mixed-size circuit. To respect the standard cells, the macros of mixed-size circuit have to be legalized such that their total movement in minimized. In Figure 2.5(b), the macros are legalized in this way.

Different approaches exist for legalizing macros in mixed-size circuits. The authors of

(a) Global Placement

(b) Legal Placement for Macros

Figure 2.5: Legalization of macros in mixed-size circuits. Gray rectangles represent macros, black clouds represent the standard cells.

[CCY03, VPC06] are using a low-temperature Simulated Annealing approach in combination with sequence-pairs. Although Tetris was introduced in the previous section as a legalization approach for standard cell circuits, it can also be used for legalizing macros [KLA+04, CX06]. A direct approach to minimize the movement of the macros during legalization is to use linear programming (LP) [Vyg97, CX06, RC06]. Here, the objective is the total movement, and linear constraints between all (or almost all) pairs of macros assure that the macros do not overlap. In detail, two macros are not overlapping, if the distance between the center positions of both macros is large enough, either in x-direction, or in y-direction. Consequently, one constraint per macro pair in the LP is enough to assure that both macros do not overlap. However, the direction (x or y) of the constraint influences the objective of minimal movement. Different approaches exist to optimize the direction of the constraints. The authors of [Vyg97] utilize a branch-and-bound optimization approach. In [CX06], the initial directions of the constraints are determined based on the global placement. Then, a min-cut like technique is used to change some constraints from x- to y-direction, or vice versa.

## Chapter 3

## This Thesis

This thesis presents novel approaches for quadratic placement, both for global placement and for legalization<sup>1</sup>. All these approaches are driven by minimizing a quadratic cost function, which results in low runtime. In global placement, the total wirelength is minimized, while in legalization the total movement is minimized. In the following, different enhancements of the new quadratic placement approaches are summarized.

## 3.1 "Kraftwerk": Force-Directed Quadratic Placement

The force-directed quadratic (global) placer "Kraftwerk", as presented in this thesis, is characterized by the following enhancements over other force-directed quadratic placement approaches:

- The placement is represented in a general demand-and-supply system. Therefore, different circuit types are supported, e.g., standard cell circuits, macro cell circuits, mixed-size circuits, and circuits with fixed modules. In addition, the demand-and-supply system is used to optimize the routability of a placement.

- The additional force is separated into a hold force and a move force. This is new compared to Eisenmann's approach, FDP, FastPlace, and RQL, but somewhat similar to FAR and mFAR.

- Both additional forces are implemented in a novel and systematic way. The move force is modeled by target points, and the locations of the target points are directly determined by the gradient of the potential of the demand-and-supply system. The hold force is modeled as a constant force, and decouples each placement iteration from its preceding iteration.

- Compared to other placement approaches, no heuristics are necessary in Kraftwerk to determine the locations of the target points. In addition, the target points enforce the control of the module movement. Since the potential represents all modules, and the

<sup>&</sup>lt;sup>1</sup>Some content of this thesis is pre-published in [SJ06, SJ07a, SJ07b, SSJ08a, SSJ08b].

potential gives the target points of the move force, the move force has a global view. This means that the move force of one module depends on all modules. Furthermore, the constant hold force does not reduce controllability, but enforces convergence.

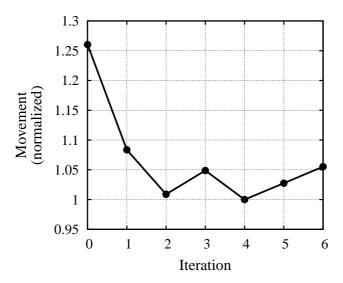

- As a result of the systematic force implementation, Kraftwerk converges such that the

demand is adapted further to the supply in each placement iteration. This in principle

means that the module overlap is reduced in each iteration. The consequence of the

convergence is a fast, robust, and stable placement algorithm. In this thesis, the convergence is analyzed in theory and demonstrated by experimental results. In addition, the

stability is shown by experimental results.

- A flat placement approach is followed, which means that the complete circuit is considered in each placement iteration. Compared to a multilevel approach, no heuristic for partitioning or clustering the circuit is necessary in the flat placement approach, and the solution space is not narrowed.

#### 3.2 "Bound2Bound" Net Model

Besides a force-directed quadratic placer, this thesis also presents the new "Bound2Bound" net model, which can be used universally in all quadratic placers. The advantages of the Bound2Bound net model are:

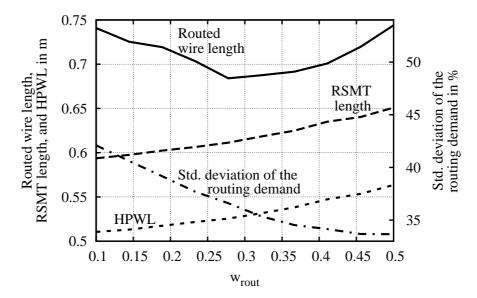

- Exact representation of the half-perimeter wire length (HPWL) in the quadratic cost function. Based on experimental result in routability-driven benchmark suites, the HPWL is an efficient metric for the routed wire length.

- Compared to the clique net model, the number of two-pin connections is lower.

- Compared to the star net model, no additional star pins are introduced.

- Based on experimental results, the Bound2Bound net model offers lower runtime and better netlength than a hybrid clique/star net model.

## 3.3 Routability-Driven Placement

An important objective for global placement is to optimize routability. For this, two problems have to be solved. First, an efficient estimation of the congestions based on routing demand is necessary. Second, an effective integration of the congestion estimation in the placer is needed. Solutions for both problems are presented in this thesis.

## 3.3.1 "RUDY": Routing Demand Estimation

The advantages of the routing demand estimation called "RUDY" is as follows:

No grid structure is necessary, which means the placement area is not divided into bins.

- No routing model is used, which means the estimation is independent of the router.

- The estimation is accurate.

- The runtime is low.

#### 3.3.2 Integration in Placement

The enhancements of the presented integration of RUDY in Kraftwerk are:

- Straight-forward integration by extending the demand-and-supply system of Kraftwerk.

- Concurrent reduction of the routing demand and increment of the routing supply in congested regions.

- One parameter models the characteristics of the router.

## 3.4 "Abacus" and "Puzzle": Legalization

In addition to novel global placement techniques, including a net model and routability optimization, this thesis also addresses new approaches for legalizing standard cell circuits, and for legalizing macros in mixed-size circuits. The enhancements over other legalization approaches are as follows:

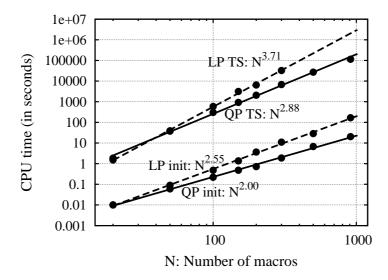

- The total quadratic movement is minimized. Other approaches are targeting the linear movement. Using the quadratic norm, the placement with minimal movement is found in low runtime.

- The relative order of the macros/standard cells is preserved. This means that considering two macros/standard cells a and b, with a left of b in the legal placement, then a was left of b in the global placement.

- "Abacus" determines the legal placement of standard cells by using efficient dynamic programming.

- "Puzzle" determines the legal placement of macros by quadratic programming. In addition, Tabu Search approach is used to determine if two macros are made overlap-free in x-direction, or in y-direction.

Figure 4.1: Circuit with hyperedges (a) and two-pin connections (b).

# **Chapter 4**

# **Bound2Bound Net Model**

Placement in general is based on the gate-level description of the circuit. This means, the circuit consists of modules (set  $\mathcal{M}$ ), the modules have pins (set  $\mathcal{P}$ ), and the pins are connected by nets (set  $\mathcal{N}$ ). Each pin  $p \in \mathcal{P}$  is located at  $(x_p^{pin}, y_p^{pin})$ . Representing each net by one hyperedge gives the circuit as shown in Figure 4.1(a). In quadratic global placement, the nets are modeled by two-pin connections. This modeling is done by a net model, and results in that each net  $n \in \mathcal{N}$  is represented by a set  $\mathcal{E}_n$  of two-pin connections, as displayed in Figure 4.1(b). One two-pin connection e = (p,q) connects pin p and q. The sum of the weighted quadratic Euclidean lengths of all two-pin connections gives the quadratic cost function  $\Gamma$ :

$$\Gamma = \frac{1}{2} \sum_{n \in \mathcal{N}} \sum_{e = (p,q) \in \mathcal{E}_n} w_{x,p\,q} (x_p^{pin} - x_q^{pin})^2 + w_{y,p\,q} (y_p^{pin} - y_q^{pin})^2$$

(4.1)

$$= \sum_{n \in \mathcal{N}} \Gamma_{n,x} + \Gamma_{n,y} \tag{4.2}$$

This cost function  $\Gamma$  can be separated in x and y-direction and in single nets, i.e., the cost  $\Gamma_{n,x}$  is the cost of net n in x-direction. In the following, the focus is on  $\Gamma_{n,x}$ .

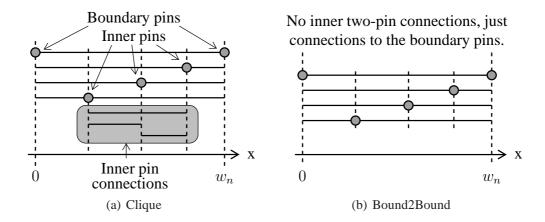

# 4.1 Clique/Star Net Model

Traditionally, the clique net model, or the star net model is used in quadratic placement. The clique net model utilizes all possible two-pin connections of a net. The star net model introduces an additional star pin per net, and connects each pin of the net to the star pin. With P pins in net n, the clique is equivalent to the star in the quadratic cost, if the clique cost is scaled with 1/P [LO73, Sig92, VC05]. Due to this equivalence of both net models, the focus is on the clique net model in the following. The quadratic cost of the clique net is:

$$\Gamma_{n,x} = \frac{1}{2} \sum_{p=1}^{P} \sum_{q=p+1}^{P} w_{x,pq} (x_p^{pin} - x_q^{pin})^2$$

(4.3)