# Data Locality Optimizations for Multigrid Methods on Structured Grids

**Christian Weiß**

# Technische Universität München Institut für Informatik Lehrstuhl für Rechnertechnik und Rechnerorganisation

# Data Locality Optimizations for Multigrid Methods on Structured Grids

#### Christian Weiß

Vollständiger Abdruck der von der Fakultät für Informatik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr. Hans Michael Gerndt

Prüfer der Dissertation:

- 1. Univ.-Prof. Dr. Arndt Bode

- 2. Univ.-Prof. Dr. Ulrich Rüde Friedrich-Alexander-Universität Erlangen-Nürnberg

- 3. Univ.-Prof. (komm.) Dr.-Ing. Eike Jessen, em.

Die Dissertation wurde am 26. September 2001 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 06. Dezember 2001 angenommen.

# **Abstract**

Beside traditional direct solvers iterative methods offer an efficient alternative for the solution of systems of linear equations which arise in the solution of partial differential equations (PDEs). Among them, multigrid algorithms belong to the most efficient methods based on the number of operations required to achieve a good approximation of the solution. The relevance of the number of arithmetic operations performed by an application as a metric for the complexity of an algorithm wanes since the performance of modern computing systems nowadays is limited by memory latency and bandwidth. Consequently, almost all computer manufacturers nowadays equip their computers with cache—based hierarchical memory systems. Thus, the efficiency of multigrid methods is rather determined by good data locality, i.e. good utilization of data caches, than by the number of arithmetic operations.

In this thesis, the cache and memory access behavior of multigrid methods is systematically analyzed for the first time. The analysis is based on an exhaustive study of modern microprocessor memory hierarchies. Detailed runtime as well as theoretical studies of the performance of these methods demonstrate the interaction between multigrid algorithms and deep memory hierarchies. In particular, issues involved with the multilevel nature of the memory hierarchy are addressed. Furthermore, delays due to main memory accesses are clearly revealed as the performance bottlenecks of multigrid methods and their components. Besides the performance bottlenecks, upper limits for the achievable performance of multigrid methods on RISC based microprocessors are determined by means of theoretical models.

Based on the knowledge gained from the analysis of multigrid algorithms and micro-processor architectures, new data locality optimization techniques for multigrid methods are proposed. The techniques extend existing code and data layout restructuring techniques and are able to significantly improve data locality and consequently speed up the execution of multigrid algorithms by a multiple. With the improved data locality multigrid methods are able to utilize 15 to 30 per cent of the peak performance on a multitude of modern computer systems. The impact of the techniques is demonstrated with runtime and memory hierarchy behavior measurements as well as theoretical data locality examinations.

The applicability of the techniques is demonstrated by means of the DiMEPACK library. DiMEPACK is a multigrid solver for two-dimensional problems with constant coefficients on structured grids. In this thesis, however, aspects of multigrid methods for three-dimensional problems and variable coefficients are discussed as well.

# Acknowledgments

First of all, I would like to thank my doctoral adviser, Prof. Dr. Arndt Bode, for his valuable support throughout the years. He provided an excellent research environment and great freedom to carry out my research.

Furthermore, I would like to thank my co—adviser Prof. Dr. Ulrich Rüde and Prof. Dr. Hermann Hellwagner for their technical advice. Despite their positions they proved to be committed colleagues and it was a pleasure to work with them on the DiME project.

I would also like to thank Prof. Dr. Eike Jessen for taking the duty to be my second co–referee in an unbureaucratic way and for providing valuable hints.

A special thank—you goes to Dr. Wolfgang Karl, Markus Kowarschik, and Oliver Creighton. They spent many hours of their spare time to read my thesis and provide numerous comments and ideas on how to improve this thesis.

The German Science Foundation (Deutsche Forschungsgemeinschaft) deserves credit for supporting my work on the DiME Projekt (research grants Ru 422/7–1,2,3).

I would also like to thank all of my former and current colleagues, in particular Georg Acher, Rainer Buchty, Michael Eberl, and Detlef Fliegl. Without them, work would have been a lonesome task.

Finally, I would like to thank my love Veronika for her support and patience.

# **Contents**

| 1 | Intr | oductio | n                                         | 1  |

|---|------|---------|-------------------------------------------|----|

|   | 1.1  | Motiva  | ation                                     | 1  |

|   | 1.2  | Contri  | butions                                   | 2  |

|   | 1.3  | Thesis  | Organization                              | 4  |

| 2 | Men  | nory Hi | derarchy Aspects in Computer Architecture | 5  |

|   | 2.1  | •       | · · · · · · · · · · · · · · · · · · ·     | 6  |

|   | 2.2  | The Bo  | ottleneck: Memory Performance             | 8  |

|   | 2.3  |         |                                           | 0  |

|   |      | 2.3.1   |                                           | 1  |

|   |      | 2.3.2   |                                           | 2  |

|   |      | 2.3.3   | Block Replacement                         | 2  |

|   | 2.4  | State o | of the Art                                | 3  |

|   |      | 2.4.1   | Compaq Microprocessors                    | 3  |

|   |      | 2.4.2   | Hewlett Packard Microprocessors           | 5  |

|   |      | 2.4.3   | Sun Microsystems Microprocessors          | 6  |

|   |      | 2.4.4   |                                           | 8  |

|   |      | 2.4.5   | Intel Microprocessors                     | 9  |

|   |      | 2.4.6   |                                           | 20 |

|   |      | 2.4.7   |                                           | 20 |

|   | 2.5  | Future  | Processor Trends                          | 21 |

|   | 2.6  | Summ    | ary                                       | 23 |

| 3 | Men  | norv Cl | naracteristics of Multigrid Methods       | 25 |

|   | 3.1  | •       | e e e e e e e e e e e e e e e e e e e     | 25 |

|   |      | 3.1.1   |                                           | 25 |

|   |      | 3.1.2   |                                           | 27 |

|   |      | 3.1.3   |                                           | 30 |

|   | 3.2  | Standa  | 6                                         | 35 |

|   |      | 3.2.1   |                                           | 35 |

|   |      | 3.2.2   | 1                                         | 37 |

|   |      | 3.2.3   | $\mathcal{E}$                             | 38 |

|   |      | 3.2.4   |                                           | 39 |

vi CONTENTS

|   |     | 3.2.5    | Data Access and Cache Behavior                   | . 41  |

|---|-----|----------|--------------------------------------------------|-------|

|   |     | 3.2.6    | Workload Distribution Among Multigrid Components | . 43  |

|   |     | 3.2.7    | Impact of Different Multigrid Configurations     |       |

|   | 3.3 | Cache l  | Behavior of Red-black Gauss-Seidel               |       |

|   | 3.4 |          | vel Considerations                               |       |

|   | 3.5 |          | ury                                              |       |

|   |     |          |                                                  |       |

| 4 |     |          | Locality Optimization Techniques                 | 55    |

|   | 4.1 |          | ction                                            |       |

|   | 4.2 |          | lence Analysis                                   |       |

|   |     | 4.2.1    | Data Dependence Types                            |       |

|   |     |          | Loop-carried Data Dependences                    |       |

|   |     | 4.2.3    | Dependence Testing                               |       |

|   | 4.3 | Data A   | ccess Transformations                            |       |

|   |     | 4.3.1    | Loop Interchange                                 |       |

|   |     | 4.3.2    | Loop Fusion                                      |       |

|   |     | 4.3.3    | Loop Blocking and Tiling                         |       |

|   |     | 4.3.4    | Data Prefetching                                 |       |

|   | 4.4 |          | ayout Transformations                            |       |

|   |     | 4.4.1    | Array Padding                                    |       |

|   |     | 4.4.2    | Array Merging                                    | . 69  |

|   |     | 4.4.3    | Array Transpose                                  | . 70  |

|   |     | 4.4.4    | Data Copying                                     |       |

|   | 4.5 | Summa    | ıry                                              | . 71  |

| 5 | Cac | he Ontin | nization Techniques for Red-black Gauss-Seidel   | 73    |

|   | 5.1 | _        | nental Techniques                                |       |

|   |     | 5.1.1    | Array Transpose                                  |       |

|   |     | 5.1.2    | Fusion                                           |       |

|   |     | 5.1.3    | One–Dimensional Blocking                         |       |

|   |     | 5.1.4    | Two–Dimensional Blocking                         |       |

|   |     | 5.1.5    | Array Padding                                    |       |

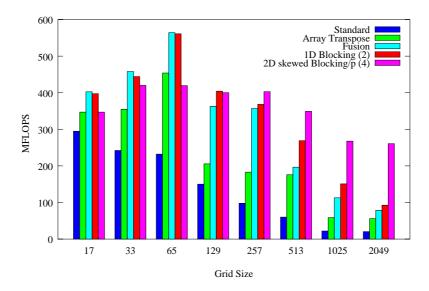

|   |     | 5.1.6    | Summary of Performance Results                   |       |

|   | 5.2 | Nine Po  | oint Stencil Discretization                      |       |

|   | 5.3 |          | zations for Three–dimensional Methods            |       |

|   | 5.4 | -        | ns with Variable Coefficients                    |       |

|   | 5.5 |          | ury                                              |       |

|   |     |          |                                                  |       |

| 6 |     |          | : A Cache-Optimized Multigrid Library            | 123   |

|   | 6.1 |          | onality of DiMEPACK                              |       |

|   | 6.2 |          | etic Optimizations                               |       |

|   | 6.3 |          | ccess Transformations                            |       |

|   |     | 6.3.1    | Smoother Optimizations                           | . 126 |

CONTENTS

|    |          |                                                                     | _ |

|----|----------|---------------------------------------------------------------------|---|

|    | - 1      | 6.3.2 Inter–Grid Transfer Optimizations                             |   |

|    | 6.4      | Data Layout Transformations                                         |   |

|    | 6.5      | DiMEPACK Performance Evaluation                                     |   |

|    |          | 6.5.1 Smoother Performance                                          |   |

|    |          | 6.5.2 Multigrid Performance                                         |   |

|    |          | 6.5.3 Performance Impact of the Inter–Grid Transfer Optimization 13 |   |

|    |          | 6.5.4 A Case Study: Chip Placement                                  |   |

|    | 6.6      | Related Work                                                        |   |

|    | 6.7      | Summary                                                             | 9 |

| 7  | Tool     | Support for Data Locality Optimizations 14                          | 1 |

| •  | 7.1      | The Software Development Process                                    | _ |

|    | 7.2      | Performance Analysis Tools                                          |   |

|    | ,        | 7.2.1 Performance Profiling                                         |   |

|    |          | 7.2.2 Simulation                                                    |   |

|    | 7.3      | Memory Hierarchy Visualization Techniques                           |   |

|    | ,        | 7.3.1 Cache Visualization for Education                             |   |

|    |          | 7.3.2 Complete Program Run Visualization                            |   |

|    |          | 7.3.3 Dynamic Cache Visualization                                   |   |

|    |          | 7.3.4 MHVT: A Memory Hierarchy Visualization Tool 152               |   |

|    |          | 7.3.5 Existing Visualization Tools                                  |   |

|    | 7.4      | Program Transformation Tools                                        |   |

|    | 7.5      | Summary                                                             |   |

| 8  | <b>C</b> | -1                                                                  | _ |

| ð  |          | clusion 15                                                          | - |

|    | 8.1      | Summary                                                             |   |

|    | 8.2      | Applicability                                                       |   |

|    | 8.3      | Outlook                                                             | J |

| Bi | bliogi   | raphy 16                                                            | 1 |

| In | dex      | 17                                                                  | o |

| ıı | uca      | <b>1</b> I                                                          | , |

<u>viii</u> CONTENTS

# **List of Figures**

| 2.1  | Sequential execution of instruction vs. pipelined and superscalar execution  | 7  |

|------|------------------------------------------------------------------------------|----|

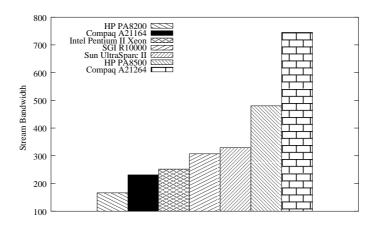

| 2.2  | Stream Bandwidth for several workstations                                    | 10 |

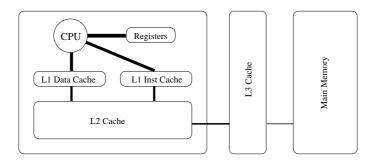

| 2.3  | A typical memory hierarchy                                                   | 11 |

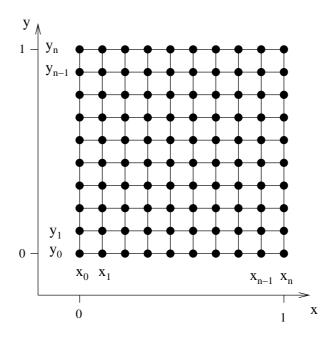

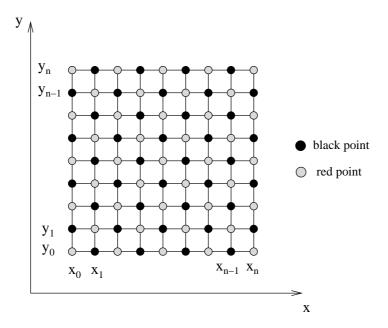

| 3.1  | Discretization of the domain $(0,1) \times (0,1)$                            | 26 |

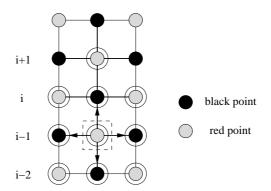

| 3.2  | A two-dimensional grid with red-black coloring                               | 29 |

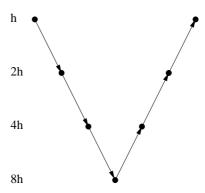

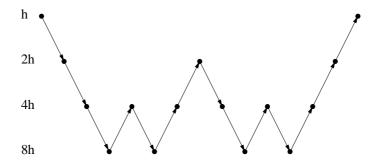

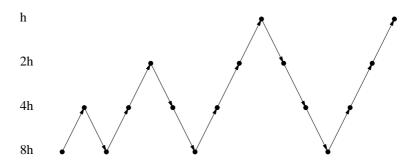

| 3.3  | Grid visiting of the V–cycle scheme                                          | 32 |

| 3.4  | Grid visiting of the $\mu$ -cycle ( $\mu = 2$ ) scheme                       | 33 |

| 3.5  | Grid visiting of the FMG scheme                                              | 34 |

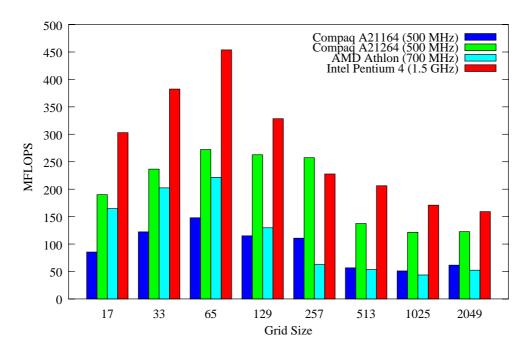

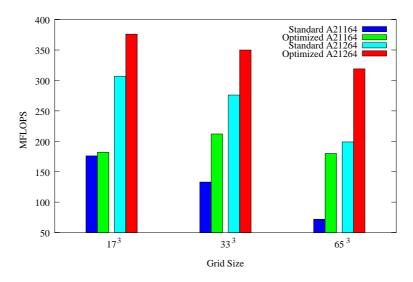

| 3.6  | MFLOPS of a standard multigrid V-cycle scheme                                | 37 |

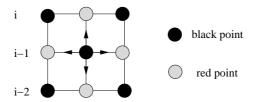

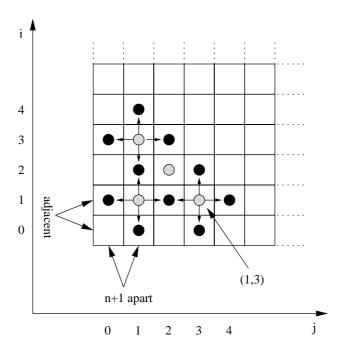

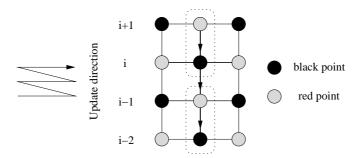

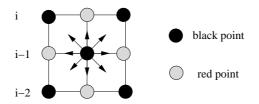

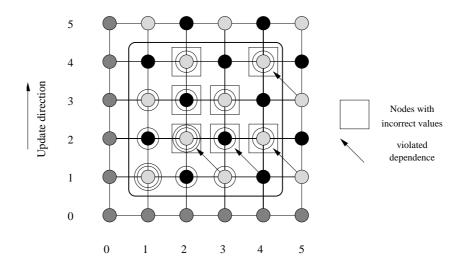

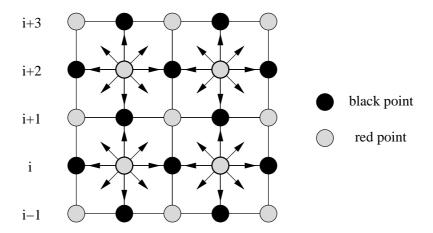

| 3.7  | Data dependences in a red-black Gauss-Seidel algorithm                       | 49 |

| 3.8  | Residual calculation after red-black Gauss-Seidel smoothing                  | 51 |

| 3.9  | Propagation of coarse grid data to fine grid nodes                           | 53 |

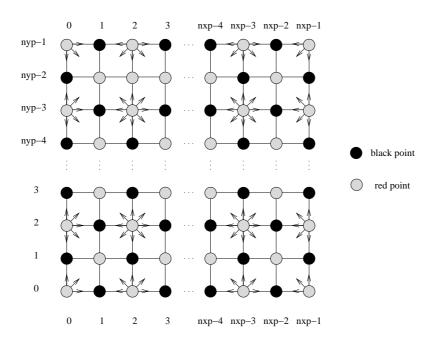

| 4.1  | Representing dependences with a dependence graph                             | 58 |

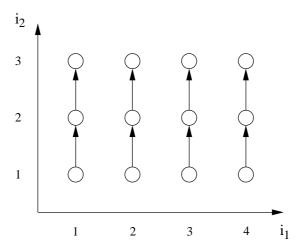

| 4.2  | Representing loop–carried dependences                                        | 60 |

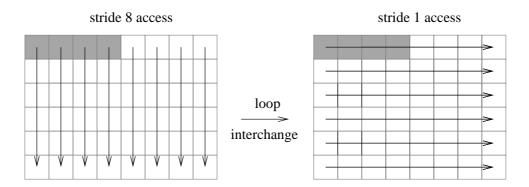

| 4.3  | Access patterns for interchanged loop nests                                  | 63 |

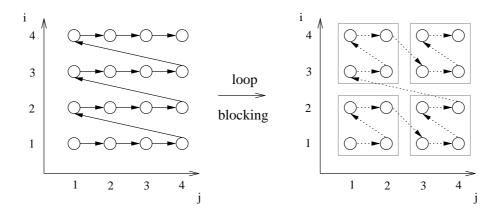

| 4.4  | Iteration space traversal for original and blocked code                      | 65 |

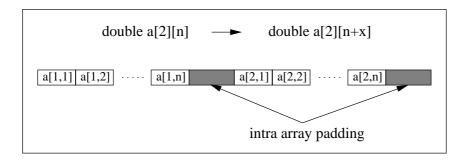

| 4.5  | Intra array padding in a C-style language                                    | 69 |

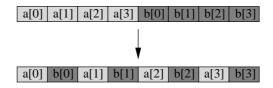

| 4.6  | Changing data layout with array merging                                      | 70 |

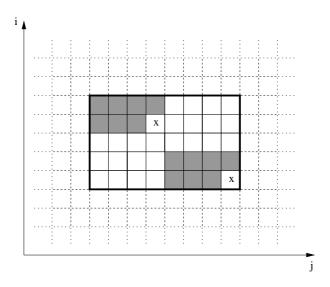

| 4.7  | Self interference in blocked code                                            | 71 |

| 5.1  | Grid memory layout before array traversal                                    | 76 |

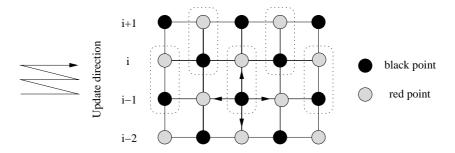

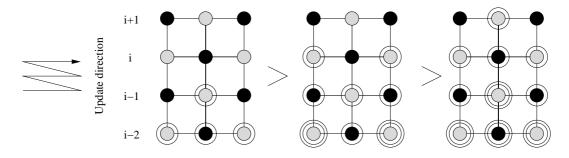

| 5.2  | Updating red and black nodes in pairs                                        | 78 |

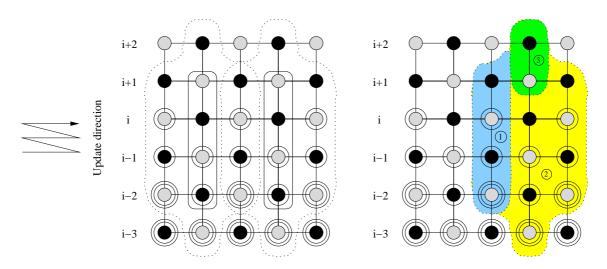

| 5.3  | Data propagation using the 1D blocking technique                             | 82 |

| 5.4  | Blocking two red-black Gauss-Seidel sweeps                                   | 82 |

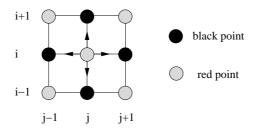

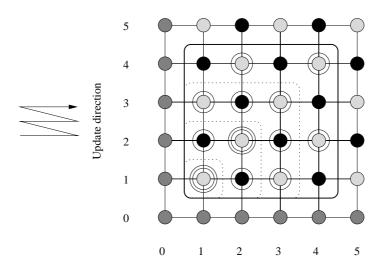

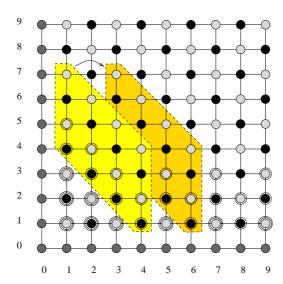

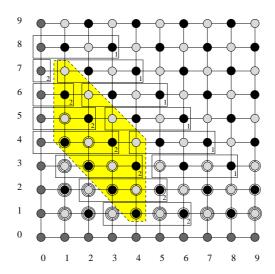

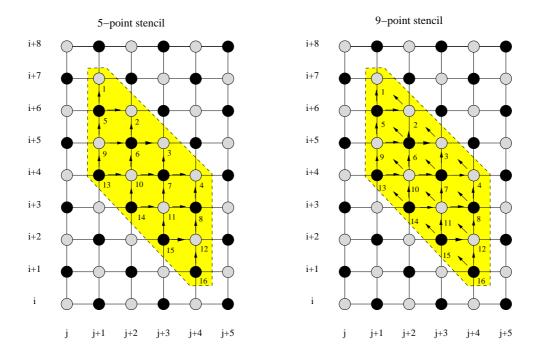

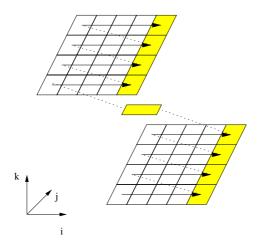

| 5.5  | Data region classification for the one–dimensional blocking technique        | 83 |

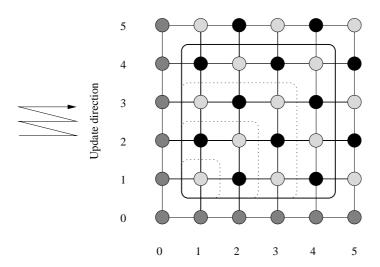

| 5.6  | A two-dimensional subblock of the grid                                       | 87 |

| 5.7  | Two-dimensional blocked red-black Gauss-Seidel: Getting started              | 89 |

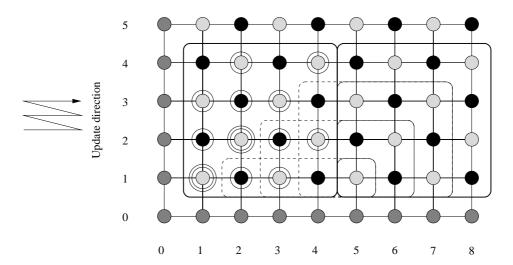

| 5.8  | Two-dimensional blocked red-black Gauss-Seidel: Continued                    | 91 |

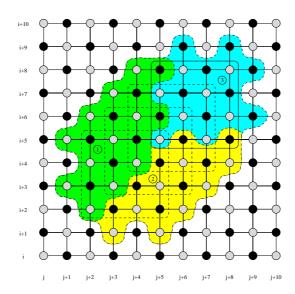

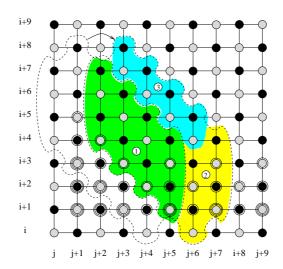

| 5.9  | Data region classification for the square two–dimensional blocking technique | 92 |

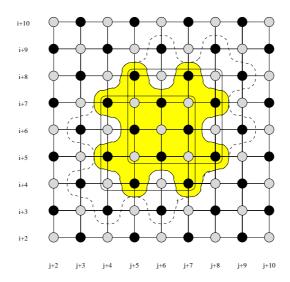

| 5.10 | Data reused between the relaxation of cascading tiles                        | 92 |

| 5 11 |                                                                              | 93 |

| 5.12 | Data region classification for the skewed two-dimensional blocking tech- |     |

|------|--------------------------------------------------------------------------|-----|

|      | nique                                                                    | 94  |

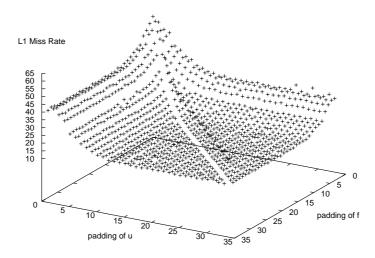

| 5.13 | Alpha 21164 L1 cache mapping for a $1025 \times 1025$ grid               | 00  |

| 5.14 | L1 miss rate for different padding sizes for $1025 \times 1025$          | 01  |

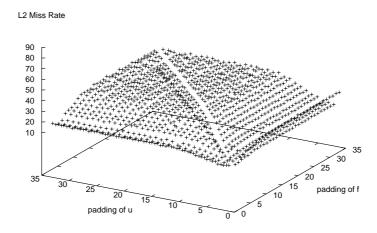

| 5.15 | L2 miss rate for different padding sizes for $1025 \times 1025$          | 02  |

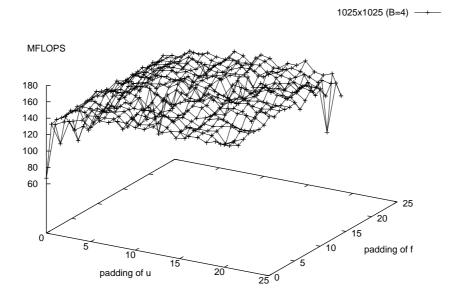

| 5.16 | MFLOPS for square two-dimensional blocked red-black Gauss-Seidel         |     |

|      | $\iota$ $\upsilon$                                                       | 07  |

| 5.17 | MFLOPS for different red-black Gauss-Seidel variants on a Compaq         |     |

|      |                                                                          | 108 |

|      |                                                                          | 11  |

| 5.19 | Square two-dimensional blocking violates data dependences in the 9-      |     |

|      | point stencil case                                                       | 12  |

| 5.20 | 5-point stencil and 9-point stencil data dependences within the skewed   |     |

|      | block                                                                    |     |

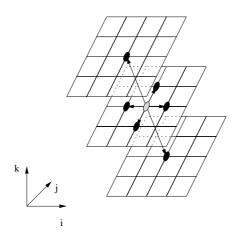

|      | 7–point stencil discretization                                           |     |

|      | Array padding for three–dimensional grids                                | 17  |

| 5.23 | MFLOPS for a 3D red-black Gauss-Seidel algorithm on a Compaq PWS         |     |

|      | 500au and a Compaq XP1000.                                               |     |

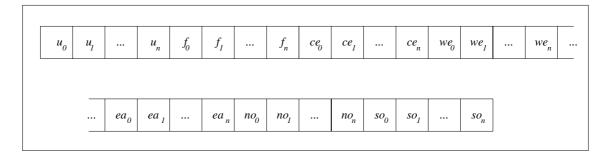

|      | Equation—oriented storage scheme                                         |     |

|      | Band—wise storage scheme                                                 |     |

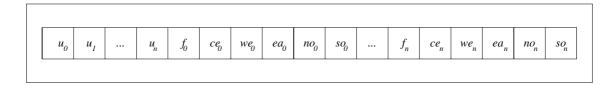

|      | Access—oriented storage scheme                                           | 20  |

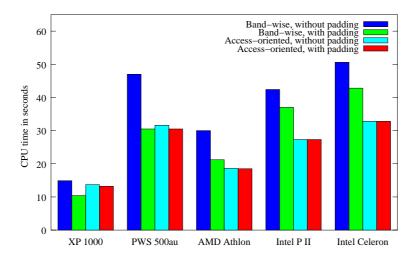

| 5.27 | CPU times for the multigrid codes based on different data layouts with   |     |

|      | and without array padding                                                | 21  |

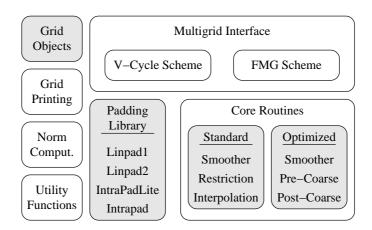

| 6.1  | DiMEPACK library overview                                                | 124 |

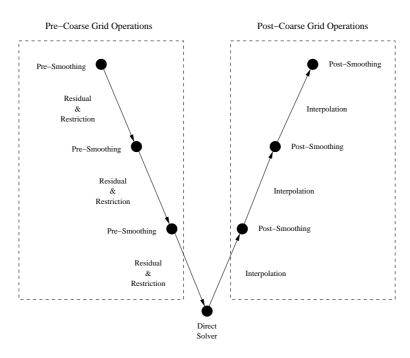

| 6.2  | Pre– and post–coarse grid operations                                     |     |

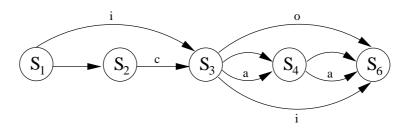

| 6.3  | Data dependences in pre–coarse grid operations                           |     |

| 6.4  | Data propagation of the binlinear interpolation                          |     |

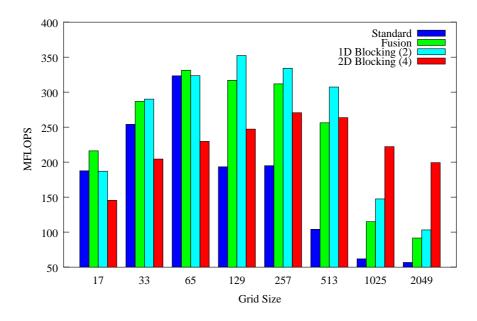

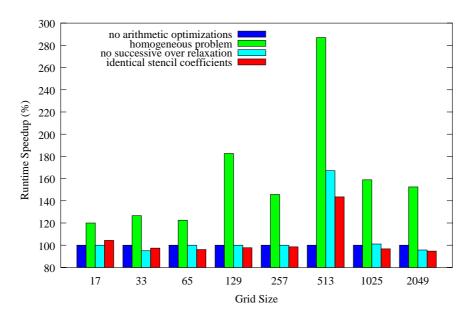

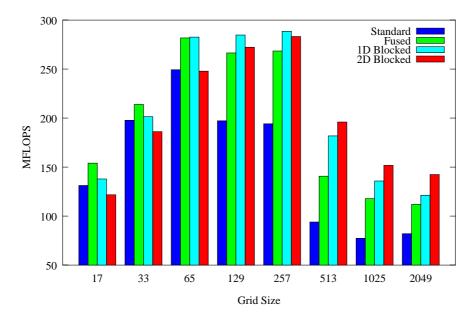

| 6.5  | DiMEPACK red-black Gauss-Seidel smoother performance                     | 132 |

| 6.6  | Runtime speedup of standard red-black Gauss-Seidel smoother obtained     |     |

|      | with arithmetic optimizations.                                           | 33  |

| 6.7  | DiMEPACK multigrid performance with different smoother optimizations.    | 35  |

| 7.1  | Snapshot of a cache animation                                            | 47  |

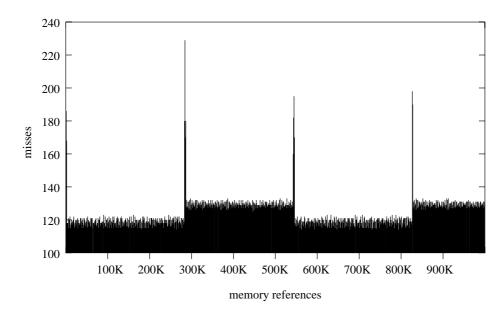

| 7.2  | A strip chart sample showing cache misses distribution over time         |     |

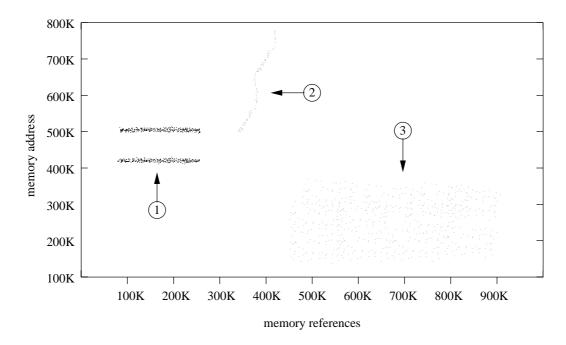

| 7.3  | Address–memory reference plots                                           |     |

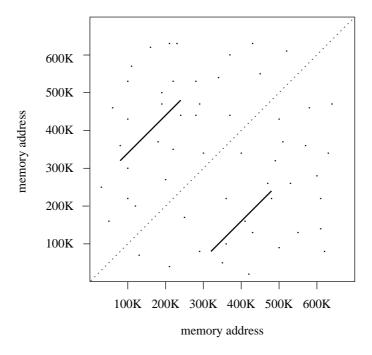

| 7.4  | Memory Address Scatter Plot                                              |     |

# **List of Tables**

| 2.1  | Microprocessor parameters in 2001                                               | 6   |

|------|---------------------------------------------------------------------------------|-----|

| 2.2  | Microprocessor parameters in 2001 (continued)                                   | 9   |

| 3.1  | Runtime behavior of DiMEPACK                                                    | 39  |

| 3.2  | Instruction partitioning of DiMEPACK                                            | 40  |

| 3.3  | Memory access behavior of DiMEPACK                                              | 41  |

| 3.4  | Cache miss rates of DiMEPACK                                                    | 42  |

| 3.5  | Per cent of CPU time spent in different multigrid components                    | 43  |

| 3.6  | MFLOPS of different DiMEPACK configurations                                     | 44  |

| 3.7  | Memory access behavior of DiMEPACK (single precision)                           | 45  |

| 3.8  | Instruction partitioning of DiMEPACK (9–point stencil)                          | 46  |

| 3.9  | Runtime behavior of red-black Gauss-Seidel                                      | 48  |

| 3.10 | Memory access behavior of red-black Gauss-Seidel                                | 48  |

| 3.11 | CPU time spent on different multigrid levels                                    | 50  |

| 5.1  | Runtime behavior of red-black Gauss-Seidel                                      | 75  |

| 5.2  | Speedup after array transpose                                                   | 77  |

| 5.3  | Memory access behavior of fused red-black Gauss-Seidel                          | 80  |

| 5.4  | Runtime behavior of fused red-black Gauss-Seidel                                | 80  |

| 5.5  | Memory access behavior of 1D blocked red-black Gauss-Seidel                     | 85  |

| 5.6  | Runtime behavior of one-dimensional blocked red-black Gauss-Seidel              | 86  |

| 5.7  | Runtime behavior of square two–dimensional blocked red–black Gauss–Seidel       | 96  |

| 5.8  | Runtime behavior of skewed two-dimensional blocked red-black Gauss-             |     |

|      | Seidel                                                                          | 97  |

| 5.9  | Memory access behavior of square two–dimensional blocked red–black Gauss–Seidel | 98  |

| 5.10 | Memory access behavior of skewed two–dimensional blocked red–black Gauss–Seidel | 99  |

| 5.11 | Runtime behavior of skewed two-dimensional blocked red-black Gauss-             | 103 |

| 5.12 | Memory access behavior of skewed two–dimensional blocked red–black              | 104 |

xii LIST OF TABLES

| 5.13 | Runtime behavior of square two–dimensional blocked red–black Gauss– |

|------|---------------------------------------------------------------------|

|      | Seidel after array padding                                          |

| 5.14 | Memory access behavior of square two-dimensional blocked red-black  |

|      | Gauss–Seidel after array padding                                    |

| 5.15 | Performance summary of several PCs (5–point)                        |

| 5.16 | Performance summary of several workstations (5–point)               |

|      | Performance summary of several workstations (9–point)               |

| 5.18 | Performance summary of several PCs (9–point)                        |

| 6.1  | Overview of the DiMEPACK smoother performance                       |

| 6.2  | DiMEPACK performance overview (no arithmetic optimization) 136      |

| 6.3  | DiMEPACK performance overview (with arithmetic optimization) 136    |

| 6.4  | DiMEPACK multigrid runtime in seconds for one V(2,2) V-cycle 136    |

| 6.5  | Performance results of optimized inter–grid transfer operations 137 |

# **List of Algorithms**

| 3.1  | $V$ -cycle $(v_1, v_2, A^h, v^h, f^h, h)$                                | 32 |

|------|--------------------------------------------------------------------------|----|

| 3.2  | $\mu$ -Cycle $(v_1, v_2, \mu, A^h, v^h, f^h, h)$                         | 33 |

| 3.3  | FMG-V-cycle $(v_1, v_2, A^{h_{min}}, v^{h_{min}}, f^{h_{min}}, h_{min})$ | 34 |

| 3.4  | Standard implementation of red-black Gauss-Seidel                        | 47 |

| 4.1  | Example of control and data dependences                                  | 57 |

| 4.2  | Loop-independent and loop-carried dependences within a loop nest         | 59 |

| 4.3  | Testing dependences in loop nests                                        | 60 |

| 4.4  | Loop interchange                                                         | 62 |

| 4.5  | Loop fusion                                                              | 64 |

| 4.6  | Loop blocking                                                            | 64 |

| 4.7  | Loop blocking for matrix multiplication                                  | 66 |

| 4.8  | Applying inter array padding                                             | 68 |

| 4.9  | Applying array merging                                                   | 69 |

| 4.10 | Applying array transpose                                                 | 70 |

| 5.1  | Standard implementation of red-black Gauss-Seidel                        | 74 |

| 5.2  | Red-black Gauss-Seidel after array transpose                             | 77 |

| 5.3  | Red-black Gauss-Seidel after loop fusion                                 | 79 |

| 5.4  | Red-black Gauss-Seidel after one-dimensional loop blocking               | 84 |

| 5.5  | Red-black Gauss-Seidel after square two-dimensional loop blocking        | 90 |

| 5.6  | Red-black Gauss-Seidel after skewed two-dimensional blocking             | 94 |

# Chapter 1

# Introduction

#### 1.1 Motivation

The performance of microprocessors increased significantly over the years so that nowadays standard computer systems provide a theoretical peak performance of one GFLOPS¹ and beyond. Nevertheless, it is a well–known fact that the speed of processors has been increasing much faster than the speed of main memory components. Recently, there is much effort in improving memory technology but many computer architects are expecting that the tendency will persist for at least a decade. As a general consequence, current memory chips based on DRAM technology cannot provide the data to the CPUs as fast as necessary. This memory bottleneck often results in significant idle periods of the processors and thus in very poor code performance compared to the theoretically available peak performance of current machines.

To mitigate this effect, modern computer architectures use multilevel cache memories which store data frequently used by the CPU. Caches are usually integrated into the CPU or based on SRAM chips. Both approaches deliver data much faster than DRAM components, but on the other hand have comparatively small capacities, for both technical and economical reasons. Efficient execution can therefore be achieved only if the hierarchical structure of the memory subsystem (including main memory, caches and the processor registers) is respected by the code, especially by the order of memory accesses. Unfortunately, even modern compilers are not very successful in performing data locality optimizations to enhance cache efficiency. As a consequence, most of this effort is left to the programmer.

Applications such as simulations of physical phenomena require apparently unlimited calculation power. Therefore, they are predestinated for more powerful microprocessors. These phenomena, for instance currents in fluids, are often described by partial differential equations (PDEs) which can be approximated by sparse systems of algebraic equations. To represent realistic two– resp. three–dimensional problems, however, systems of linear

One MFLOPS  $\equiv 10^6$  floating point operations per second. One GFLOPS  $\equiv 10^9$  floating point operations per second.

2 Introduction

equations with up to several hundred millions of unknowns are required. The data structures which store the equations easily consume several hundred Mbyte or even Gbyte of main memory.

Multigrid methods are among the most efficient algorithms for the solution of large systems of linear equations arising in the context of numerical PDE solution, based on the number of operations required to achieve a good approximation of the solution. Generally speaking, multigrid methods approximate the physical domain with one fine grid and several coarser grids. The problem on the finest grid is solved approximately with a smoother resp. relaxation method such as the red–black Gauss–Seidel algorithm. The coarser grids are in turn used to calculate corrections to the approximation. Information between grid levels is transferred with inter–grid transfer operations such as restriction and interpolation.

Multigrid algorithms belong to the class of iterative methods, which means that the underlying data set is repeatedly processed several times. Thus, during one iteration the whole or at least a large part of the data has to be delivered from main memory to the CPU to be processed. In the following iteration the same process happens again with a slightly changed data set. The fact that multigrid methods repeatedly access their data set promises high data locality, however, in reality this data locality is not exploited. The direct consequence of their bad data locality is that multigrid methods merely reach a small fraction of the available peak performance of current microprocessors.

The discrepancy between inherent and exploited data locality of multigrid algorithms forms the key motivation for this work. With a consolidated knowledge of microprocessor architectures with deep memory hierarchies and of the algorithmic behavior of multigrid methods it should be possible to restructure multigrid methods so that the inherently available data locality is exploited and consequently a better performance is achieved. It must be pointed out that the optimizations should not change the semantics of the multigrid algorithms so that standard multigrid convergence estimates apply to the new cache optimized multigrid codes.

Another approach to improve the performance of iterative methods which is not investigated in this thesis is *parallelization*. Many researches have implemented hand-coded efficient parallel multigrid methods very often based on domain decomposition techniques. While parallelization often leads to significant speedups, the computation on each node will still suffer from high latency and low bandwidth involved with main memory accesses. Thus, the work in this thesis will apply to both parallel and sequential multigrid codes. However, details and extensions to parallel codes are left for further research.

### 1.2 Contributions

This thesis reveals that the major problem, which prohibits the exploitation of the data locality inherently present in multigrid methods, is the fact that the data sets involved with realistic problems are much larger than the cache levels built in currently available or fore-

1.2 Contributions 3

casted computer systems. The direct consequence of the bad data locality is a bad runtime performance on architectures with deep memory hierarchies. Based on a detailed study of multigrid methods and microprocessor architectures new data locality optimizations are proposed which significantly improve the runtime performance of multigrid methods. The key contributions of the thesis are as follows:

- For the first time a detailed and systematic study of the runtime, cache, and memory behavior of multigrid methods is performed. The analysis demonstrates the interaction between multigrid methods and deep memory hierarchies. The analysis is based on runtime measurements as well as on theoretical studies of the data locality and performance of multigrid methods. In particular, issues involved with the multilevel nature of the memory hierarchy are addressed. The analysis exposes that the performance of multigrid algorithms is determined by main memory accesses. When executing the smoother which is by far the most time consuming component of the multigrid method on a Compaq PWS 500au, for example, the microprocessor is idle 80 per cent of all cycles waiting for data to arrive from main memory. Furthermore, properties of multigrid methods are exposed which are responsible for the bad performance.

- Upper limits for the achievable performance of multigrid methods on RISC based microprocessors are determined by means of theoretical models. The models testify that multigrid algorithms will at best achieve 50 per cent of the available peak performance on typical microprocessors.

- New data locality optimization techniques for multigrid methods on structured grids are developed based on the knowledge gained from the detailed analysis of multigrid methods, modern microprocessor memory hierarchies, and their interaction. The techniques extend existing data locality optimization techniques such as *loop fusion* or *loop blocking* and are able to significantly improve the data locality of multigrid algorithms. The optimizations which focus on the smoother component are able to speed up the execution on currently available workstations and PCs by a factor of up to five, especially for large grid sizes. The significance of all optimization techniques is demonstrated by means of detailed performance analysis and theoretical discussions of data locality properties.

- Although the thesis focuses on optimization techniques for the smoother component, other optimization techniques for inter-grid transfer operations are proposed. These optimization techniques combine pre- and post-coarse-grid operations. Thus, the number of global sweeps through the data structure is reduced which in turn improves data locality and performance.

The applicability of the techniques will be demonstrated by means of the DiMEPACK library. DiMEPACK is a fully functional multigrid library for two-dimensional constant coefficient problems on structured grids. The fast smoothers and inter-grid transfer optimizations developed in this thesis establish the core elements of the DiMEPACK multigrid

4 Introduction

solver. The library demonstrated its robustness and efficiency in a global cell placement code for VLSI circuits developed at the Institute of Electronic Design Automation (LEA), Technische Universität München.

In addition to the major contributions, new cache visualization techniques are proposed based on the experience gained during the performance analysis. The new visualization techniques provide a more intuitive understanding of the dynamical nature of memory hierarchies. Some of the techniques have been integrated in the experimental memory hierarchy visualization tool called *MHVT*.

## 1.3 Thesis Organization

The thesis is structured as follows: Chapter 2 describes the architectural development and performance issues involved with high main memory latency and insufficient memory bandwidth. Common properties of all memory hierarchies are identified and establish the fundamentals for the algorithmic studies. In Chapter 3, the idea of multigrid methods is introduced and the runtime, cache, and memory behavior of multigrid algorithms is analyzed. Thus, the algorithmic properties, memory performance bottlenecks, and upper limits for the achievable floating point performance of multigrid methods are determined. The fundamental principles of data locality optimizations based on data access and data layout transformations are introduced in Chapter 4. Although these kinds of optimizations are able to improve the performance of simple codes, they fail to improve the performance of multigrid codes due to data dependences. However, the techniques are the basis of new data locality optimization techniques for the red-black Gauss-Seidel smoother which are proposed in Chapter 5. The performance improvement is demonstrated by means of detailed runtime and memory access analysis. The cache-optimized smoother routines as well as cache-optimized inter-grid transfer operations have been integrated in the DiME-PACK multigrid library which is introduced in Chapter 6. They establish the core routines for the library. In Chapter 7, existing tool support for data locality optimization is discussed and new cache visualization techniques are proposed which are derived from the experience gained during the performance study of multigrid codes. The thesis concludes with some final remarks and a brief outlook on future work.

# Chapter 2

# **Memory Hierarchy Aspects in Computer Architecture**

Microprocessors nowadays operate at a clock frequency of one GHz and above. In contrast to the past, however, high performance microprocessors are no longer limited to expensive high end products. Mass market microprocessor products like the Pentium 3 [Int00b, Int00c], Pentium 4 [Int01] and AMD Athlon [Adv99] can be bought in the shop around the corner for reasonable prices and used in common PCs. They provide a floating point peak performance equal or even higher than high end workstations. Hence, new PCs provide a peak performance of one billion floating point instructions per second ( $\equiv$  one GFLOPS)and beyond at home for a reasonable price.

The reason for the incredible performance increase is the continuing advance in integrated circuit (IC) technology over the years. 0.18-micron IC process is standard nowadays and microprocessors produced with 0.15-micron and 0.13-micron IC processes already start to appear (see Table 2.1). Along with the continuing miniaturization of circuits the numbers of transistors which can be realized on a chip has been increasing over the years and this trend continues. For example, The HP PA-8500 and HP PA-8600 microprocessors are built with 130 million transistors. Even mass market products like the Pentium 4 and AMD Athlon microprocessor already use a transistor budget of more than 30 million transistors. The average transistor budget of a CPU is still approximately 10 to 20 million transistors (see Table 2.1) but microprocessors with billions of transistors have already been forecasted [BG97]. Microprocessor manufacturers employ these transistors to implement more and more fine-grain parallel instruction execution techniques such as deep pipelining, multiple instruction issue, dynamic scheduling, out-of-order execution, speculative execution, and also on-chip caches with small capacities as compared to main memory. These structural enhancements are additionally contributing to the performance improvement.

In this chapter, the architectural features *pipelining* and *superscalar execution* will be introduced which are among the most important architectural improvements in microprocessor architecture. Then, the limiting performance factor in todays computer architecture — the memory bottleneck — is identified. Subsequently, the memory hierarchy concept

| Processor       | Clock Rate | Transistors | IC Process | Pipeline     |

|-----------------|------------|-------------|------------|--------------|

| Intel Pentium 4 | 1.5 GHz    | 42.0 mio.   | $0.18\mu$  | 22/24 stages |

| AMD Athlon      | 1.2 GHz    | 37.0 mio.   | $0.18\mu$  | 9/11 stages  |

| Intel Pentium 3 | 1.0 GHz    | 24.0 mio.   | $0.18\mu$  | 12/14 stages |

| Sun Ultra-3     | 900 MHz    | 29.0 mio.   | $0.15\mu$  | 14/15 stages |

| Alpha 21264B    | 833 MHz    | 15.4 mio.   | $0.18\mu$  | 7/9 stages   |

| HP PA-8600      | 552 MHz    | 130.0 mio.  | $0.25\mu$  | 7/9 stages   |

| Sun Ultra-2     | 480 MHz    | 3.8 mio.    | $0.29\mu$  | 6/9 stages   |

| IBM Power 3–II  | 450 MHz    | 23.0 mio.   | $0.22\mu$  | 12/14 stages |

| MIPS R12000     | 400 MHz    | 7.2 mio.    | $0.25\mu$  | 6 stages     |

Table 2.1: Some parameters of currently available microprocessor chips in 2001[Mic00].

is described which is used by computer manufacturers to mitigate the impact of the memory bottleneck. Then, an overview of the state of the art in microprocessor architecture with an emphasis on the memory hierarchy architecture is given. The chapter concludes with a summary of trends in microprocessor architecture.

## 2.1 Pipelining and Superscalar Execution

In this section, pipelining will only be briefly introduced. A more detailed description of pipelining for microprocessors can be found in [Kog81, HP96].

Pipelining is a technique that is applied to many situations to speed up the overall execution of a process which repeatedly performs a certain task. It must be possible to divide the task into a series of individual and independent operations, or stages, that, when applied sequentially, perform the overall task. With pipelining the individual operations are executed in an overlapped manner. As one item progresses through the pipeline, other items can be initiated before the first has completed all stages. That is, once the first stage of the first task is completed, the second stage of the first task is executed concurrently with the first stage of the second task, and so on.

Pipelining exploits parallelism among instructions in a sequential instruction stream to speed up execution. In a microprocessor each pipeline stage executes one part of an instruction like instruction fetch (IF), instruction decoding (ID), execution (EX), memory access (MA), and write back (WB). Figure 2.1 illustrates different execution schemes. If instructions are executed sequentially the processor has to execute each phase of the first instruction before it can start executing the next instruction. In a pipelined CPU the execution of the first phase of the second instruction can begin as soon as the first phase of the first instruction is finished.

The longest running stage in a pipeline determines the time (usually measured in clock ticks) to advance all instructions to the next stage. Hence, the work done in each stage should be distributed equally. If this is the case the execution time of one instruction is

sequential execution: 1st instruction 2nd instruction ID EX MA WB IF ID EX MA WB pipelined execution: ID EX MA WB 1st instruction ID EX MA WB 2nd instruction 3rd instruction ID EX MA WB 4th instruction IF ID EX MA WB pipelined and superscalar execution: ID EX MA WB IF 1st instruction ID EX MA WB 2nd instruction IF 3rd instruction ID EX MA WB ID EX MA WB 4th instruction

Figure 2.1: Sequential execution of instruction vs. pipelined and superscalar execution

equal to the sequential execution time. In real systems, however, the execution time for one instruction is usually higher than the one for sequential execution. Nevertheless, the throughput of instructions will be increased. Provided that an ideal pipeline is considered, i.e. the work in each stage is equally distributed and no further overhead is present, a pipelined microprocessor will accelerate execution by a factor equal to the number of stages.

The Compaq Alpha 21264 microprocessor [Com99, Gwe96a] implements a 7 stage pipeline for instruction execution, for example. The stages include instruction fetch, instruction slot, mapping, issue, register read, execute, and data cache access. Other processors like the HP PA-8500, the Sun UltraSparc-II, the Power PC G4, or the MIPS R12000 implement pipelines of similar depth. With the increase in clock frequency the time which can be spent in one pipeline stage is decreased. Consequently, some operations which have been completed in one cycle in the past will require several cycles when the CPU is operated at higher frequency. Thus, the stages which process such operations have to be split into several stages leading to an architecture such as the Pentium 4 architecture developed by Intel which already uses a very deep pipeline with 24 stages.

The idea of pipelining only works if there is a continuous flow of instructions through them. If, for whatever, reason a pipeline stage cannot complete its work there will be a long delay until new instructions can be processed. Such a situation is called a *hazard*. Possible hazards are *structural*, *control* and *data hazards*. A more detailed description of

hazards can be found in the literature [HP96].

The concept of pipelining can be extended to groups of instructions. Figure 2.1 illustrates the instruction execution of a microprocessor which is able to start the execution of two instructions per cycle. A microprocessor which is able to execute multiple instruction per cycle is called superscalar. Typically, only a small number of instructions — like one to eight — can be executed simultaneously. Parallel instruction execution requires that the instructions are independent of each other. The independence is checked by the microprocessor dynamically during the execution of the instructions.

To be able to process several instructions in parallel the microprocessor must provide the resources needed in each stage like integer and floating point calculation units multiple times. To reduce the number of resources which have to be duplicated, simultaneously executed instructions typically must obey some constraints. A typical constraint, for example, is that only a certain number (usually two to four) of integer instructions can be issued together with a certain number of floating point instructions (usually two).

The Compaq Alpha 21264 microprocessor is able to issue up to four instructions per cycle, for example. It provides two floating point units and four integer execution units (two general–purpose units and two address arithmetic logic units (ALUs)). Hence, although four instructions can be issued simultaneously, only two floating point instructions are allowed per cycle; and also only for certain combinations of integer operations four instructions can be issued per cycle.

## 2.2 The Bottleneck: Memory Performance

Baskett [Bas91] estimated in 1991 that the performance of microprocessors increased by 80 per cent per year in the past. At the same time the access delays for DRAM chips, however, decreased more slowly at an annual rate of 5 – 10 per cent [ASW<sup>+</sup>93]. The speed of microprocessors as well as the speed of DRAM chips improved exponentially during the same time. Unfortunately, the exponent for microprocessors is substantially larger than that for DRAM chips. The trend already produced a large gap between CPU and DRAM speed. Although the annual performance of microprocessors slightly decreased in the last years, the general trend is still maintained so that the gap will grow further. The significance of this trend will be illustrated with the following example.

At a clock frequency of one GHz a two-way superscalar CPU is theoretically able to perform two floating point operations every nanosecond. For each floating point operation two words are required as operands and one word is produced as a result. With a memory access latency of about 100 nanoseconds which is approximately the memory latency of the Compaq PWS 500au, for example, a microprocessor will face a memory access latency of approximately 100 cycles every time it fetches data from main memory. This is a severe problem since the microprocessor could execute up to 200 floating point instructions during that time. This problem is called *latency problem*. Researchers have developed several techniques, like software and hardware prefetching [CKP91, MLG92, CB94], non-blocking caches [Kro81, SF91], stream buffers [Jou90, PK94], multithread-

| Processor       | Bandwidth   | Out-of-Order          | Cache (I/D/L2)      |

|-----------------|-------------|-----------------------|---------------------|

| Sun Ultra-3     | 4.8 Gbyte/s | none                  | 32 K / 64 K / –     |

| Intel Pentium 4 | 3.2 Gbyte/s | 126 ROPs <sup>1</sup> | 12 K / 8 K / 256 K  |

| Alpha 21264B    | 2.7 Gbyte/s | 80 instr              | 64 K / 64 K / –     |

| AMD Athlon      | 2.1 Gbyte/s | 72 ROPs               | 64 K / 64 K / 256 K |

| Sun Ultra-2     | 1.9 Gbyte/s | none                  | 16 K / 16 K / –     |

| IBM Power 3–II  | 1.6 Gbyte/s | 32 instr              | 32 K / 64 K / –     |

| HP PA-8600      | 1.5 Gbyte/s | 56 instr              | 512 K / 1 M / –     |

| Intel Pentium 3 | 1.1 Gbyte/s | 40 ROPs               | 16 K / 16 K / 256 K |

| MIPS R12000     | 0.5 Gbyte/s | 48 instr              | 32 K / 32 K / –     |

Table 2.2: Memory peak bandwidth, out–of–order capability, and on–chip cache sizes of microprocessor chips in 2001 [Mic00].

ing [LGH94], and out—of—order execution [HP96] to tolerate at least some memory access latency. However, these techniques are not able to compensate a latency of over 100 cycles. Especially, since instructions executed while loading data might access other data themselves which may again lead to idle time which has to be tolerated. Another problem involved with some latency tolerating techniques such as prefetching, for example, is that they increase the total amount of memory traffic and thus will expose the *memory bandwidth problem* [BGK95].

To store the results of two floating point operations per cycle in memory, a micro-processor requires a memory bandwidth of six words each nanosecond, or 48 Gbyte/s (assuming double precision floating point operations). Although the focus of computer designers has recently shifted towards increasing the memory bandwidth, the peak main memory bandwidth of today's computers is still far below 48 Gbyte/s. As Table 2.2 shows the peak bandwidth of microprocessors is typically between one and two Gbyte/s. The peak bandwidth, however, is a theoretical value which is very hard to achieve in real life.

Another measure of bandwidth is the sustainable bandwidth of user programs which is determined with the STREAM benchmark [McC95]. The STREAM benchmark program accesses data in a way which is advantageous for memory systems. Thus, the memory bandwidth achieved with it can be seen as the maximally achievable user program memory bandwidth. Figure 2.2 summarizes the results of the STREAM benchmark on a HP SPP 2200 Convex Exemplar node (HP PA–8200, 200 MHz), a Compaq PWS 500au (Alpha 21164, 500 MHz), a Dell PC (Intel Pentium 2 Xeon, 450 MHz), a SGI Origin 2000 node (SGI R10000, 195 MHz), a Sun Ultra 60 (UltraSPARC–II, 296 MHz), a HP N–Class node (HP PA–8500, 440 MHz), and a Compaq XP1000 (Alpha 21264, 500 MHz). The Compaq XP1000 with a peak bandwidth of over two Gbyte/s reaches only a STREAM bandwidth of 745 Mbyte/s. As Figure 2.2 shows the sustainable bandwidth for other

<sup>&</sup>lt;sup>1</sup>The Intel Pentium 4, Intel Pentium 3, and AMD Athlon are x86–compatible microprocessors. Thus, they internally translate the complex x86 instructions into possibly several RISC operations (ROPs) which are then executed by the microprocessor core.

Figure 2.2: Stream Bandwidth for several workstations

architectures might be even less.

Current computers are already slowed down considerably by the slower main memory. If the difference in microprocessor speed and main memory speed diverges at the same pace, a point will be reached where the speed of calculations is determined by the speed of memory. Improving microprocessor speed will then only result in marginal improvement in execution speed. This phenomenon is called *hitting the memory wall* [WM95]. The typical solution is to postpone the impact to a later date by implementing the concept of a *memory hierarchy*.

## 2.3 The Memory Hierarchy Concept

There are many different ways of implementing the *memory hierarchy* concept, but the consistent theme is that there is a small, expensive, high speed memory at the top of the hierarchy which is usually integrated within the CPU to provide data with low latency and high bandwidth. As we move further away from the CPU the layers of memories get successively larger and slower. These high speed memories are called *caches* and are intended to contain copies of main memory blocks to speed up accesses to frequently needed data. The lowest level of the memory hierarchy is the main memory which is large but also comparatively slow. The levels of the memory hierarchy usually subset one another so that data residing within a smaller memory is also stored within the larger memories.

A typical memory hierarchy is shown in Figure 2.3. It contains a small number (32 to 64) of registers on the chip which are accessible without delay. Furthermore, a small cache — usually called level one (L1) cache — is placed on the chip to ensure low latency and high bandwidth. The L1 cache is usually split into two separated caches. One only keeps data, the other instructions. The latency of on–chip caches is typically one or two cycles. The chip designers, however, already face the problem that large on–chip caches of new high–frequency microprocessors aren't able to deliver data within one cycle since

Figure 2.3: A typical memory hierarchy containing two level one on–chip caches, one on–chip level two caches, and a third level of cache off–chip. The thickness of the interconnections emblematizes the bandwidth between levels of the memory hierarchy.

the signal delays are too long. Therefore, the size of on-chip L1 caches is limited to 64 Kbyte or even less for many chip designs. Larger cache sizes with accordingly higher access latency, however, start to appear. Table 2.2 summarizes on-chip cache sizes of some state of the art microprocessors.

The L1 caches are usually backed up by a level two (L2) cache. In some architectures like for example the Compaq Alpha 21164 [Com97], the Intel Pentium 4 [Int01] or the AMD Athlon [Adv99] the second level cache is also implemented on chip. Most of the architectures still build the L2 cache with SRAM chips on the motherboard of the computer. Off—chip caches are much bigger but also provide data with lower bandwidth and higher access latency. L2 caches on chip are usually smaller than 512 Kbyte and provide data with a latency of approximately 5 to 10 cycles. If the L2 caches are implemented on the chip, a third level of off—chip cache may be added to the hierarchy. Off—chip cache sizes vary from one Mbyte to 16 Mbyte. They tend to provide data with a latency of 10 to 20 cycles.

## 2.3.1 Locality of References

Because of the limited size, caches can only hold copies of recently used data or code. Typically, when new data is loaded into the cache other data has to be replaced<sup>2</sup>. Caches improve performance only if data already loaded into the cache is *reused* before it is replaced by other data. The reason why caches are nevertheless able to substantially reduce program execution time is the *principle of locality of references* [HP96] which states that recently used data is very likely to be used again in the near future. Locality can be subdivided into *temporal locality* and *spatial locality* [WL91]. A sequence of references has temporal locality when recently accessed data is likely to be accessed again

<sup>&</sup>lt;sup>2</sup>In the startup phase of a microprocessor or after a cache flush no data has to be replaced since the cache is considered to be empty. Some set–associative caches may also voluntarily evict data, so that empty cache lines are present in the cache. To simplify matters, the further explanation ignores these special cases. A description of the handling of these cases can be found in [HP96], for example.

in the near future. A sequence of reference has spatial locality when data located close together also tends to be referenced close together in time.

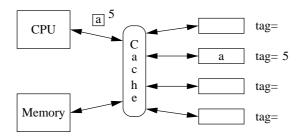

#### 2.3.2 Block Placement

Data within the cache is stored in *cache lines*. A cache line holds the content of a contiguous block of main memory. If data requested by the processor is found within a cache line this is called a *cache hit*. Otherwise, a *cache miss* occurs. The content of a *memory block* containing the requested word is fetched from a lower memory layer and copied into a cache line. In that process another item is (typically) replaced. Therefore, the question into which cache line the data should be placed and how to locate it must be handled efficiently to guarantee a low latency.

One of the cheapest approaches to implement block placement strategies in respect to hardware expense is *direct-mapping*. Thereby, the contents of a memory block can be placed (or mapped) into exactly one cache line. The cache line in which the contents will be copied is determined by the following formula:

cache line address = (block address) MOD (number of cache lines)

Direct—mapped caches have been among the most popular cache architectures in the past. Recently, however, computer architects returned to implement more and more k—way set—associative on—chip caches. Direct—mapped caches, however, are still very common for off—chip caches. k—way set—associative caches have higher hardware expenses but usually imply higher hit rates.

The cache lines of k-way set-associative caches are grouped into sets of k cache lines and the contents of a memory block can be placed into any cache line of exactly one set. The set in which the contents will be placed is determined by the following equation:

set address = (block address) MOD (number of sets)

Finally, a cache is *fully associative* when the contents of a memory block can be placed into any cache line of the cache. Fully associative caches are usually only implemented in small sized special purpose caches, but not in general data or instruction caches.

Direct—mapped and fully associative caches can be viewed as special cases of k—way set—associative caches. A direct—mapped cache is a one—way set—associative cache and a fully associative cache is an n—way set—associative cache provided that n equals the number of cache lines.

## 2.3.3 Block Replacement

In fully associative and k-way set-associative caches the memory block can be placed in several cache lines. The question into which cache line a new memory block is copied and consequently which block has to be replaced is decided by a (block) replacement strategy. The two most commonly used strategies for today's microprocessor caches are random

2.4 State of the Art

and *least–recently used* (LRU). The random replacement strategy chooses a random cache line to be replaced. The LRU strategy replaces the block which hasn't been accessed for the longest time. According to the principle of locality it is more likely that a recently accessed item will be accessed again in the near future. Less common strategies are the *least–frequently used* (LFU) and *first in, first out* (FIFO) replacement strategy. The former replaces the item which was least frequently used whereas the latter replaces the memory block in the cache line which resided in the cache for the longest time.

Finally, the *optimal* replacement strategy [Bel66, SA93] replaces the memory block which will not be accessed for the longest time. It is impossible to implement this strategy in a real cache, since it requires information about future cache references. Thus, the strategy is only of theoretical value. Note, however, that a fully associative cache with optimal replacement strategy will have the minimal number of cache misses any cache of the same size for any possible sequence of references can have [SA93, Tem98].

#### 2.4 State of the Art

In the following, an overview of the state of the art in microprocessor technology is given with an emphasis on the cache and memory system. In addition, predecessor models and some already announced, but not yet available, microprocessors are introduced briefly. Readers not interested in technical details may skip the following sections and resume the reading in Section 2.4.7.

## 2.4.1 Compaq Microprocessors

The microprocessor currently shipped by Compaq is the Alpha 21264 [Gwe96a]. It is the successor to the Alpha 21164 [Com97]. For the Alpha 21164 the chip manufacturer decided to use a very simple design without out—of—order execution, branch prediction, or other sophisticated features which were state of the art at the time the Alpha 21164 was released. The simple design was chosen to allow the chip to be operated at a clock frequency that was much higher than that of other microprocessor at that time.

#### **Alpha 21164**

The Alpha 21164 is equipped with a direct—mapped 8 Kbyte instruction and a direct—mapped 8 Kbyte data cache, both located on the chip. Furthermore, a unified three—way set—associative 96 Kbyte second level cache for data and instruction is implemented on chip. The design allows a L1 data access with only one cycle latency. A second level cache access already takes 6 to 10 cycles. Finally, the L2 cache is backed up by an optional direct—mapped off—chip cache of up to 64 Mbyte. Data from main memory can be delivered to the microprocessor resp. L3 cache if present with a peak memory bandwidth of 400 Mbyte/sec.

#### Alpha 21264

In contrast to its predecessor, the Alpha 21264 implements state of the art processor features. The Alpha 21264 implements out—of—order execution of 80 instructions and allows 8 outstanding loads. It also provides branch prediction techniques to reduce idle time. The execution core is equipped with four integer and two floating point arithmetic units. It is able to execute up to six instructions per cycle. However, only four instructions can be issued per cycle so that only an execution of four instructions can be sustained. The drawback of the new design is that it only allows a marginal increase of the clock frequency and the peak performance of the chip is equal to the peak performance of its predecessor, operated with the same clock frequency. Nevertheless, the sustained performance for many applications increased substantially.

One reason for this is, that the designers spent a lot of effort into improving the memory access performance of the new chip. The Alpha 21264 is equipped with two separated 64 Kbyte on-chip L1 caches for instructions and data. Both caches are two-way setassociative. The instruction cache uses 32 byte cache lines whereas the data cache uses 64 byte cache lines. The designers decided to build two large L1 caches for instruction and data instead of two small caches backed up by an additional second level of on-chip cache. The access latency of the primary data caches, however, is two to four cycles and not one cycle like for the L1 cache of the Alpha 21164 microprocessor. The data cache is dual ported and can deliver two independent 64-bit words every cycle. The microprocessor includes a dedicated 128-bit L2 cache bus and a separated 64-bit system bus to main memory. Both can be operated at speeds up to 333 MHz. The external cache provides a backup store for both primary caches. It is direct-mapped and shared by instructions and data. The off-chip cache is controlled by a cache controller on the processor to guarantee a low latency. The off-chip cache size can vary from one to 16 Mbyte and the latency is 12 to 14 cycles. Data from the second level off-chip cache can be delivered to the primary data caches with a peak bandwidth of 4 Gbyte/s with 250 MHz SRAM chips. For the Alpha CPU also a slot architecture with processor and L2 cache on a small PC board similar to Intel's Slot 2 Xeon is available. This allows the off-chip cache to be operated at a higher clock frequency to reduce latency and increase bandwidth. The system bus which connects the chip with main memory is operated at 333 MHz and delivers a peak main memory bandwidth of 2.7 Gbyte/s.

#### Alpha 21364

The successor to the Alpha 21264, the Alpha 21364, is announced for the second half of 2001 [Gwe98a]. It will be based on a the Alpha 21264 CPU with additional features wrapped around the core. The main improvement will be the use of multiple Direct RDRAM channels which will increase main memory bandwidth and greatly reduce memory access latency. Furthermore, a six—way set—associative 1.5 Mbyte L2 cache will be placed on chip. The cache will cycle at the speed of the CPU, delivering 128 byte of data every nanosecond. The latency of the L2 cache will be the same as the second level cache latency of the Alpha 21264. This is a direct consequence of the decision that the 21364

2.4 State of the Art

uses the same core design with only minor changes. In contrast to the other Compaq chips the Alpha 21364 will not support any off-chip caches. However, the RDRAM channels will provide a direct main memory access with a peak bandwidth of 6.0 Gbyte/s

#### 2.4.2 Hewlett Packard Microprocessors

The current microprocessor shipped by Hewlett–Packard is the HP PA–8600 [Gwe99c]. It is a member of the PA–8x00 family which is based on the core design of the PA–8000 microprocessor.

#### PA-8000

The PA-8000 [Hun95] is a four-way superscalar microprocessor with dynamic instruction reordering capability (out-of-order execution). The PA-8000 includes two integer ALUs and two floating point multiply/accumulate units. Hence, the chip is able to execute up to four floating point operations per cycle in the case of multiply-add operations. Otherwise two floating point operations and two integer operations can be performed in parallel.

The memory hierarchy design of the PA-8x00 family is very conservative. It is limited to a single level of two large low latency caches for data and instructions. The PA-8000, for example, is equipped with a one Mbyte two cycle latency direct-mapped off-chip cache for both data and instructions.

#### PA-8200

The PA–8200 microprocessor [SBK<sup>+</sup>97, Gwe96b] uses a fine tuned version of the PA–8000 core. The cache design is more or less equal to the design of the PA–8000, however, newer SRAM technology allows a cache size of two Mbyte for both data and instructions.

#### PA-8500

The PA-8500 processor [LH97] is based on the PA-8200 core with only minor enhancements. The use of a newer fabrication process allows a larger amount of transistors for the PA-8500 microprocessor. The enhanced transistor budget is used to move the two first-level caches on chip. Therefore, the PA-8500 includes a 0.5 Mbyte four-way set-associative cache for instructions and a one Mbyte four-way set-associative cache for data. Further off-chip caches are not supported. The latency of both caches is still two cycles, but the new design allows a higher clock frequency for the cache and consequently a higher clock frequency for the CPU core. The drawback of the decision to move both caches on chip, however, is a dramatically increased die size and consequently higher manufacturing costs. Consequently, the PA-8500 microprocessor as well as its successor the PA-8600 microprocessor currently have the largest die size of all microprocessors available.

#### PA-8600

The PA-8600 microprocessor [Gwe99c] in turn is based on the PA-8500 core. Improvements in the fabrication process allow slightly higher clock frequencies. The CPU is equipped with two on-chip caches of the same size as the PA-8500. The cache system is also more or less unchanged. However, the cache prefetching algorithm was improved and the cache replacement was changed from round-robin to LRU replacement.

#### PA-8700

The next microprocessor — the PA-8700 [Gwe98b, Kre00a] — from Hewlett Packard is expected to be shipped in 2001. The design will be based on the PA-8600 design with only minor modifications to integrate the new cache sizes of 1.5 Mbyte of L1 on-chip data cache and 0.75 Mbyte on-chip instruction cache. Furthermore, again minor improvements will be made in the data prefetching algorithm and the replacement strategy will be changed to quasi LRU replacement. After 2002, the PA-8x00 microprocessor family will be replaced by IA-64 based CPUs.

#### **2.4.3** Sun Microsystems Microprocessors

#### UltraSparc-II

The UltraSparc–III [Sun97] is the predecessor of the UltraSparc–III chip which is currently shipped by Sun Microsystems. It is equipped with two separate 16 Kbyte caches on the chip for instructions and data. The instruction cache is pseudo associative and the line size is 32 bytes<sup>3</sup>. The data cache is direct mapped and the cache line size is also 32 bytes. Both caches are backed up by a unified direct–mapped external L2 cache of up to 16 Mbyte with a cache line size of 64 byte. The external cache is controlled by an on–chip integrated cache controller.

#### UltraSparc-III

The UltraSparc–III [Son97b, Kre00c, HL99] chip is based on a completely new core design. The new core supports four–way superscalar in–order execution. The core operates a pipeline with 14 stages to allow a high clock frequency. The chip is equipped with a 32 Kbyte four–way set–associative instruction cache using pseudo random replacement. The instruction cache uses a cache line size of 32 bytes and provides data with a two cycles latency. Furthermore, the chip is equipped with three first level on–chip data caches: a 64 Kbyte four–way set–associative general purpose data cache using pseudo random replacement and 32 byte cache lines, a two Kbyte four–way set–associative write cache

<sup>&</sup>lt;sup>3</sup>Upon a memory request a pseudo associative cache looks up a memory block in cache like a direct mapped cache. If the data is not present, i.e. a cache miss happens, a secondary slot is checked for the data. If it is found there the cache lines are swapped. Thus, a pseudo associative cache behaves like a two–way set–associative cache but has a shorter access time.

2.4 State of the Art

using LRU replacement and 64 byte cache lines to reduce store traffic to the external L2 cache, and a two Kbyte four—way set—associative prefetch cache using LRU replacement. The L1 general purpose data cache provides data with a two cycle latency. If data is not found in the L1 general purpose data cache but in the prefetch cache, the prefetch cache is able to provide the data for two load instructions per cycle with a latency of three cycles. Furthermore, the prefetch cache fills its 64—byte cache lines in 14 cycles from the L2 cache. The prefetch cache is able to process up to 8 software—and hardware—initiated prefetch requests simultaneously.

The on-chip caches are backed up by an external direct-mapped L2 cache which can be up to 8 Mbyte large. The cache is managed by a cache controller which is on the chip to keep latency low [HL99]. The peak bandwidth of the L2 cache is 6.4 Gbyte/sec with 200 MHz SRAM chips. To reduce main memory latency the microprocessor also includes an SDRAM controller which delivers a main memory peak bandwidth of 2.4 Gbyte/sec.

#### **MAJC-5200**

Besides the SPARC–architecture Sun Microsystems also developed the MAJC (Microprocessor Architecture for Java Computing) architecture [Sun99]. The architecture is a very long instruction word (VLIW) architecture [Kar93] which allows several instructions to be grouped into one package which is then issued to functional units. Note, that instructions are grouped into packages at compile time to be executed concurrently at runtime. Contrary, superscalar RISC architectures use complex control logic in order to decide dynamically at run time which operation can be executed concurrently. To provide a Java–friendly environment MAJC also supports thread–level parallelism by providing several CPU cores on a chip. Instructions of different threads are bundled into different packages which can then be dispatched to different CPU cores.

The MAJC–5200 [Sud00, Cas99] is the first (and so far only) implementation of MAJC. It implements two identical and independent but cooperative processor cores. Each core is equipped with a 16 Kbyte, two–way set–associative (LRU replacement) instruction cache using 32 byte lines. Furthermore, both cores share a single 16 Kbyte, four–way set–associative (LRU replacement) data cache with 32 byte cache lines. The data cache is dual ported to allow the simultaneous access of both cores. The design does not include a L2 cache. In order to compensate for the missing L2 cache the chip is equipped with four IO–ports. Two of the ports are general purpose off–chip communication paths with a bandwidth of 2 Gbyte/sec each. Furthermore, the chip is equipped with a Rambus DRAM (RDRAM) interface which is able to deliver data from main memory with a bandwidth of up to 1.6 Gbyte/sec. Finally, the chip is equipped with a PCI interface. The high off-chip bandwidth is supposed to give the chip an advantage in multimedia processing where typically large amounts of streaming data have to be processed.

#### 2.4.4 IBM Microprocessors

#### Power 3

The Power 3 [Son97a, PDM<sup>+</sup>98] processor from IBM implements a two level memory hierarchy. The first level instruction and first level data cache are located on chip, whereas the unified L2 cache is located off chip. The L1 instruction cache is 32 Kbyte large, using 128 byte cache lines. The latency of the instruction cache is one cycle. The L1 data cache is 64 Kbyte large and uses 128 byte lines. According to [PDM<sup>+</sup>98] both L1 caches are 128—way set—associative. The instruction cache allows two outstanding loads, whereas the data cache allows four outstanding loads. The controller for the off—chip L2 cache is placed on board. The L2 cache controller allows a maximum of 16 Mbyte of cache. At 200 MHz the bandwidth from the L2 cache to the processor is 6.4 Gbyte/sec. The chip also implements a hardware initiated prefetching. Sequential instruction or data accesses are detected in hardware. A stream is detected when the data accesses happen with a stride of one cache line. The Power 3 allows four streams to be prefetched with up to two cache lines fetched ahead from L2 or main memory.

#### Power 4

The successor to the Power 3 microprocessor will be the Power 4 microprocessor [Die99b, Kre00b]. It will supports multithreaded programs by implementing chip multiprocessing (CMP) and provides a high bandwidth chip-to-chip interconnection network. The microprocessor chip will include two identical processor cores on chip. Each will be equipped with a 64 Kbyte L1 instruction cache and 32 Kbyte L1 data cache. The core will allow 11 outstanding loads (eight from the data cache and three from instruction cache). The caches of both cores will be backed up by a unified L2 cache which will be split into three equally sized, and independent 0.5 Mbyte caches. Two slices will be dedicated for the two cores. The remaining slice will be dedicated for the chip-to-chip interconnect. The slices will be connected to the cores by a 100 Gbyte/sec port to allow high bandwidth from caches. The L2 slices will be ensured to be cache coherent. All L2 slices together will allow a total of 12 outstanding loads from L3 or main memory. Furthermore, the chip will include a cache controller for an eight-way set-associative off-chip cache. The controller will deliver data from L3 cache with a bandwidth of 10 Mbyte/sec. Similar to the Power 3 microprocessor, the Power 4 chip will also implement hardware prefetching. The Power 4 chip will allow eight prefetch streams with up to 20 cache lines kept in flight. Finally, the chip will be equipped with a chip-to-chip interconnect which allows highspeed coupling with two other Power 4 microprocessors. The chip-to-chip interconnect will allow a sustained data transfer bandwidth of 35 Gbyte/sec from chip to chip.

2.4 State of the Art

#### 2.4.5 Intel Microprocessors

#### Pentium 3

The Pentium 3 processor [Gwe99a, Int00c, Int00b] implements a two level cache hierarchy. The first level of the hierarchy includes a 16 Kbyte, four—way set—associative L1 instruction cache and a 16 Kbyte, four—way set—associative L1 data cache on chip. The L2 cache contains both data and instructions. The L2 cache is available in two different variants [Gwe99a]: a 512 Kbyte, four—way set—associative off—chip cache or a 256 Kbyte, eight—way set—associative, on—chip cache.

#### Pentium 4

The successor chip — the Pentium 4 [Sti00, Gla00] — also implements a two level cache hierarchy. The first level of the hierarchy includes a 8 Kbyte four—way set—associative data cache using 64 byte lines and a newly designed instruction cache called *trace cache*. The Pentium microprocessor family decodes x86 instructions into several micro operations which can then be executed internally in a RISC style manner. The trace cache does not store x86 instructions like the older Pentium instruction cache designs do, but already decoded micro operations. The trace cache is able to cache 12K of micro operations. The second level cache is a unified eight—way set—associative L2 cache of 256 Kbyte. The L2 cache uses 128 byte cache lines and is integrated on chip. An option for an L3 off—chip cache is planned to appear in the next version of the core. The chip is connected to main memory with a 400 MHz bus. Instead of DRAM or SDRAM, so far only RDRAM with a peak bandwidth of 3.2 Gbyte/sec is supported.

#### **Itanium**

Besides the Pentium architectures Intel also developed the IA-64 based on EPIC. EPIC (Explicitly Parallel Instruction Computing) is a 64-bit microprocessor instruction set, jointly defined and designed by Hewlett Packard and Intel, that provides up to 128 general and floating point unit registers and uses speculative loading, predication, and explicit parallelism (VLIW style). The Itanium processor [Int00a] is the first implementation of the IA-64 architecture based on EPIC. In contrast to the Pentium systems the Itanium processor is not equipped with a out–of–order execution RISC core but executes instructions in software–supplied order.