# Shared Memory Programming on NUMA-based Clusters using a General and Open Hybrid Hardware / Software Approach

**Martin Schulz**

# Institut für Informatik Lehrstuhl für Rechnertechnik und Rechnerorganisation

### Shared Memory Programming on NUMA-based Clusters using a General and Open Hybrid Hardware / Software Approach

#### Martin Schulz

Vollständiger Abdruck der von der Fakultät für Informatik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. R. Bayer, Ph.D.

Prüfer der Dissertation:

1. Univ.-Prof. Dr. A. Bode

2. Univ.-Prof. Dr. H. Hellwagner, Universität Klagenfurt / Österreich

Die Dissertation wurde am 24. April 2001 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 28. Juni 2001 angenommen.

#### **Abstract**

The widespread use of shared memory programming for High Performance Computing (HPC) is currently hindered by two main factors: the limited scalability of architectures with hardware support for shared memory and the abundance of existing programming models. In order to solve these issues, a comprehensive shared memory framework needs to be created which enables the use of shared memory on top of more scalable architectures and which provides a user–friendly solution to deal with the various different programming models.

Driven by the first issue, a large number of so-called SoftWare Distributed Shared Memory (SW-DSM) systems have been developed. These systems rely solely on software components to create a transparent global virtual memory abstraction on highly scalable, loosely coupled architectures without any direct hardware support for shared memory. However, they are often affected by inherent performance problems and, in addition, do not solve the second issue of the existence of (too) many shared memory programming models. On the contrary, the large amount of work done in the DSM area has led to a significant number of independent systems, each with its own API, thereby further worsening the situation.

The work presented within this thesis therefore takes the idea of SW–DSM systems a step further by proposing a general and open shared memory framework called HAMSTER (Hybrid-dsm based Adaptive and Modular Shared memory archiTEctuRe). Instead of being fixed to a single shared memory programming model or API, this framework provides a comprehensive set of shared memory services enabling the implementation of almost any shared memory programming model on top of a single core. These services are designed in a way that minimizes the complexity for target programming models making the implementation of a large number of different models feasible. This can include both existing and new application or application domain specific programming models easing both the porting of given and the parallelization of new applications.

In addition, the HAMSTER framework avoids typical performance problems of SW–DSM systems by relying on so–called NUMA (Non–Uniform Memory Access) architectures which combine scalability and cost effectiveness with limited support for shared memory in the form of non–cache coherent hardware DSM. Their capabilities are directly exploited by a new type of hybrid hardware/software DSM system, the core of the HAM-STER framework. This Hybrid–DSM approach closes the semantic gap between the global physical memory provided by the underlying hardware and the global virtual memory re-

quired for shared memory programming enabling applications to directly benefit from the hardware support.

On top of this Hybrid–DSM system, the HAMSTER framework defines and implements several independent and orthogonal management modules. This includes separate modules for memory, consistency, synchronization, and task management as well as for the control of the cluster and the global process abstraction. Each of these modules offers typical services required by implementations of shared memory programming models. Combined they form the HAMSTER interface which can then be used to implement shared memory programming models without much effort.

This capability is proven through the implementation of a number of selected shared memory programming models on top of the HAMSTER framework. These models range from transparently distributed thread models all the way to explicit put/get libraries and also include various APIs from existing SW–DSM systems with different relaxed consistency models. It therefore covers the whole spectrum of shared memory programming models and underlines the broad applicability of this approach.

The presented concepts are evaluated using a large number of different benchmarks and kernels exhibiting the performance details of the individual components. In addition, HAMSTER is used as the basis for the implementation or port of two real—world applications from the area of nuclear medical imaging, more precisely the reconstruction of PET images and their spectral analysis. These experiments cover both the porting of an already existing shared memory application using a given DSM API and the parallelization of an application from scratch using a new, customized API. In both cases, the system provides an efficient platform resulting in a very scalable execution. These experiment, therefore, prove both the wide applicability and the efficiency of the overall HAMSTER framework.

## **Acknowledgments**

I would like to take this opportunity to express my deepest gratitude to the following people, for I realize that this work would not have been possible without their help, guidance, and support.

First, I am indebted to my two advisors, Prof. Dr. A. Bode, chair of LRR-TUM, and Prof. Dr. H. Hellwagner, now at the University of Klagenfurt. Prof. Hellwagner initially took me in as his student and after his move to Klagenfurt, Prof. Bode took over without hesitation. Together they provided me with an excellent research environment and gave me the greatest possible freedom to pursue my work and interests. In addition, despite their busy schedules, they both always had an open ear for me.

I would also like to direct my special thanks to Dr. Wolfgang Karl who, in his function as leader of the architecture group at LRR, significantly contributed to the excellent research environment. In addition, his support and the many long, informal discussions and helpful comments regarding my work were invaluable, especially in times when I seemed stuck.

I would also like to thank my many colleagues at LRR-TUM; I enjoyed very much working with them and the many discussions we shared over coffee. Especially I would like to mention my office mates over the years: Phillip Drum, Michael Eberl, Detlef Fliegl (who also contributed significantly to the Windows NT driver for the SCI-VM and provided personal system administration support), Günther Rackl, and Christian Weiß. Additionally, I would like thank Jie Tao, whose pleasant disposition and enthusiasm made it a pleasure to work with her.

Our secretaries, especially Mrs. Eberhardt, Mrs. Wöllgens, and Mrs. Brunnhuber, deserve my special thanks for their help in maneuvering through the many administrative obstacles ranging from contract issues to business trip applications. Without them, I would still be sitting here in a pile of paper work. I would also like to thank Klaus Tilk, our system administrator, for keeping our systems alive and healthy.

I do not want to forget to mention Prof. Dr. A. Chien and the members of his Concurrent Systems Architecture Group (CSAG) from the University of Illinois at Urbana–Champaign (now at the University of California at San Diego). During my stay in this group and during my Master's work there, they introduced me to a scientific style of working from which I still very much profit.

The European Union/Commision deserves credit for the funding it provided for the majority of my work. This was done mainly within the ESPRIT projects SISCI (EP 23174)

and NEPHEW (EP 29907). In addition, the many partners Europe—wide involved in these projects provided an additional source of inspiration and support. Special thanks go to Dolphin ICS, most specifically to Kåre Løchson, Hugo Kohmann, Torsten Amundsen, and Roy Nordstrøm, who were involved not only in these ESPRIT projects, but also technically supported our work within SMiLE.

The work within NEPHEW also brought me in contact with the Clinic for Nuclear Medicine at the "Klinikum Rechts der Isar". From this cooperation I received valuable input for the evaluation part of this work. This would not have been possible without help from Frank Munz, Sibylle Ziegler, and Martin Völk and I am very thankful for the time and energy they invested.

On a more personal note, I am indebted to my friends and my whole family who were always at my side providing constant encouragement and support. I would especially like to thank my good friend, Dr. Johannes Zimmer, for all our long talks and for his prolific help with LATEX. I would also like to express my deepest gratitude to my parents. From early on, they sparked and encouraged my interest in learning and provided unconditional support in all of my endeavors, both financially and (most important) spiritually. Last, but certainly not least, I would like to thank the love of life, my wife Laura, who not only took the time to review my thesis and to give valuable comments regarding language and style, but who also supported me throughout the entire time and with her whole heart.

Martin Schulz April 2001

# **Contents**

| l | Mot  | ivation |                                                         | 1  |

|---|------|---------|---------------------------------------------------------|----|

|   | 1.1  | Curren  | nt Deficiencies of the Shared Memory Paradigm           | 2  |

|   | 1.2  | The A   | pproach                                                 | 3  |

|   |      | 1.2.1   | Benefiting from the Rise of NUMA Architectures          | 3  |

|   |      | 1.2.2   | Exploiting Hybrid–DSM Techniques                        | 4  |

|   |      | 1.2.3   | Towards an Open Architecture for Shared Memory          | 4  |

|   | 1.3  | Contri  | butions                                                 | 5  |

|   | 1.4  | Thesis  | Organization                                            | 7  |

| 2 | Bacl | kgroun  | d                                                       | 9  |

|   | 2.1  | Shared  | l Memory Programming                                    | 9  |

|   |      | 2.1.1   | Definition of Shared Memory Programming Models          | 9  |

|   |      | 2.1.2   | Available Models and APIs                               | 10 |

|   |      | 2.1.3   | Shortcomings of Shared Memory Programming               | 12 |

|   | 2.2  | Archit  | ectural Support for Shared Memory                       | 12 |

|   |      | 2.2.1   | Full Hardware Support within UMA Systems                | 13 |

|   |      | 2.2.2   | Improving Scalability with CC–NUMA                      | 14 |

|   |      | 2.2.3   | Transitions Towards Pure NUMA Systems                   | 16 |

|   |      | 2.2.4   | Shared Memory for Clusters                              | 16 |

|   | 2.3  | NUMA    | A for Clusters: The Scalable Coherent Interface         | 18 |

|   |      | 2.3.1   | History and Principles of SCI                           | 18 |

|   |      | 2.3.2   | 7 11                                                    | 18 |

|   |      | 2.3.3   | Commercial Success of SCI                               | 21 |

|   |      | 2.3.4   | Other SCI–based Research Activities                     | 23 |

|   |      | 2.3.5   | HAMSTER as Part of the SMiLE Project                    | 27 |

|   | 2.4  | Summ    | ary                                                     | 28 |

| 3 | HAI  | MSTER   | t <del>:</del>                                          |    |

|   | Hyb  | rid–dsr | m based Adaptive and Modular Shared memory archiTEctuRe | 31 |

|   | 3.1  | Relate  | d Work                                                  | 31 |

|   | 3.2  | HAMS    | STER Design Goals                                       | 32 |

|   |      | 3.2.1   | Main Characteristics                                    | 32 |

|   |     | 3.2.2   | Target Architectures                               | 34 |

|---|-----|---------|----------------------------------------------------|----|

|   | 3.3 | The H   | AMSTER Layers                                      | 36 |

|   | 3.4 | Under   | lying Principles                                   | 37 |

|   |     | 3.4.1   | The Principle of Orthogonality                     | 37 |

|   |     | 3.4.2   | Resource and Performance Monitoring                | 38 |

|   | 3.5 | Summ    | ary                                                | 39 |

| 4 | SCI | Virtual | Memory: Creating a Hybrid–DSM System               | 41 |

|   | 4.1 |         | of the Art                                         | 41 |

|   |     | 4.1.1   | Idea and Concept of DSM Systems                    | 41 |

|   |     | 4.1.2   | - · · · · · · · · · · · · · · · · · · ·            | 42 |

|   |     | 4.1.3   | Alternative Approaches                             | 46 |

|   |     | 4.1.4   | Exploiting Existing Hardware Support               | 48 |

|   | 4.2 |         | CI-VM Design                                       | 50 |

|   |     | 4.2.1   | Building Block 1: SCI-based Hardware-DSM           | 50 |

|   |     | 4.2.2   | Building Block 2: Software–DSM Systems             | 50 |

|   |     | 4.2.3   | Combining Both Building Blocks to the SCI-VM       | 50 |

|   | 4.3 | Static  | vs. Dynamic Memory Management                      | 51 |

|   |     | 4.3.1   | Static Memory Mappings                             | 52 |

|   |     | 4.3.2   | Dynamic Global Memory Management                   | 54 |

|   | 4.4 |         | lying Task and Execution Model                     | 56 |

|   | 4.5 | Integra | ating the SCI-VM with Existing SCI-based Platforms | 57 |

|   |     | 4.5.1   | SCI Driver Integration                             | 57 |

|   |     |         | Operating System Integration/Extension             | 57 |

|   | 4.6 | Memo    | ry Coherency of the SCI-VM                         | 59 |

|   |     | 4.6.1   | 7 1                                                | 60 |

|   |     | 4.6.2   | Impact on Memory Coherency                         | 61 |

|   |     | 4.6.3   | 3                                                  | 62 |

|   | 4.7 | SCI-V   | M Performance                                      | 62 |

|   |     | 4.7.1   | •                                                  | 63 |

|   |     |         | Effect of Memory Optimizations                     | 65 |

|   | 4.8 |         | ning Problems and Challenges                       | 67 |

|   |     | 4.8.1   | Transparency Gaps in the Underlying Hardware       | 67 |

|   |     | 4.8.2   | Full Operating System Integration                  | 68 |

|   | 4.9 | Summ    | ary                                                | 68 |

| 5 | HAI | MSTER   | R Management Modules                               | 71 |

|   | 5.1 | Memo    | ory Management                                     | 71 |

|   |     | 5.1.1   | State of the Art                                   | 71 |

|   |     | 5.1.2   | Functionalities of the Module                      | 72 |

|   |     | 5.1.3   | Influencing the Memory Layout                      | 73 |

|   |     | 5.1.4   | Controlling the Coherency of Global Memory         | 77 |

|   |     | 5.1.5   | Dealing with Static Application Data               | 79 |

|   | 5.2 | Consi  | stency Management                                  | 83  |

|---|-----|--------|----------------------------------------------------|-----|

|   |     | 5.2.1  | State of the Art                                   | 84  |

|   |     | 5.2.2  | Enabling the Control of the SCI-VM Memory System   | 84  |

|   |     | 5.2.3  | Minimizing the Global Impact                       | 85  |

|   |     | 5.2.4  | Introducing Scope                                  | 86  |

|   |     | 5.2.5  | Functionalities of the Module                      | 87  |

|   |     | 5.2.6  | Low-level Performance                              | 89  |

|   |     | 5.2.7  | Realizing Consistency Models in HAMSTER            | 89  |

|   | 5.3 | Synch  | ronization Management                              | 90  |

|   |     | 5.3.1  | State of the Art                                   | 90  |

|   |     | 5.3.2  | Functionalities of the Module                      | 91  |

|   |     | 5.3.3  | Implementation Aspects and Performance of Locks    | 93  |

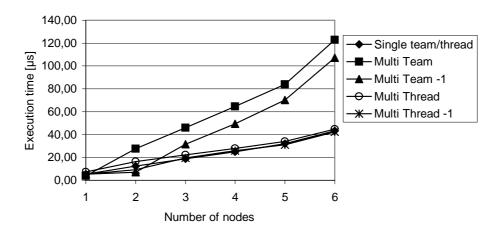

|   |     | 5.3.4  | Implementation Aspects and Performance of Barriers | 96  |

|   |     | 5.3.5  | Global Counters and Interrupts                     | 99  |

|   | 5.4 | Task N | Management                                         | 99  |

|   |     | 5.4.1  | State of the Art                                   | 100 |

|   |     | 5.4.2  | Functionalities                                    | 100 |

|   | 5.5 | Towar  | ds a Global View: The Cluster Control Module       | 102 |

|   |     | 5.5.1  | State of the Art                                   | 102 |

|   |     | 5.5.2  | Functionalities                                    | 103 |

|   |     | 5.5.3  | Asynchronous RPC-like Communication Service        | 103 |

|   |     | 5.5.4  | Control Over the Global Process Abstraction        | 104 |

|   |     | 5.5.5  | Startup Control                                    | 104 |

|   |     | 5.5.6  | Clean Termination                                  | 106 |

|   | 5.6 | Summ   | nary                                               | 106 |

| 6 | Imp | lement | ing Programming Models on Top of HAMSTER           | 109 |

|   | 6.1 | The H  | IAMSTER Interface                                  | 109 |

|   |     | 6.1.1  | HAMSTER Services                                   | 109 |

|   |     | 6.1.2  | Multiplatform Timing Support                       | 109 |

|   |     | 6.1.3  | Using the HAMSTER Interface                        | 110 |

|   | 6.2 | A Firs | st Model: Single Program – Multiple Data (SPMD)    | 110 |

|   | 6.3 | Suppo  | ort for Various Consistency Models                 | 111 |

|   |     | 6.3.1  | State of the Art                                   | 111 |

|   |     | 6.3.2  | Combining Consistency and Synchronization          | 112 |

|   |     | 6.3.3  | Implementing Release Consistency                   | 112 |

|   |     | 6.3.4  | Implementing Scope Consistency                     | 114 |

|   |     | 6.3.5  | Experimental Evaluation                            | 116 |

|   |     | 6.3.6  | Applicability                                      | 120 |

|   | 6.4 | Transp | parent Multithreading on top of HAMSTER            | 121 |

|   |     | 6.4.1  | State of the Art                                   | 121 |

|   |     | 6.4.2  | Global Thread Identification                       | 122 |

|   |     | 6.4.3  | Forwarding Requests to Potentially Remote Threads  | 122 |

|   |     | 6.4.4    | Memory Consistency Model                          | 123 |

|---|-----|----------|---------------------------------------------------|-----|

|   |     | 6.4.5    | Extended Synchronization                          | 125 |

|   |     | 6.4.6    | Available APIs and Limitations                    | 126 |

|   |     | 6.4.7    | Performance Evaluation                            | 127 |

|   | 6.5 | Suppo    | rt for Explicit Shared Memory Models              | 130 |

|   |     | 6.5.1    | The Cray T3D/E Put/Get Programming Interface      | 130 |

|   |     | 6.5.2    | Implementing Put/Get in HAMSTER                   | 131 |

|   |     | 6.5.3    | Performance Aspects                               | 132 |

|   | 6.6 | Implei   | mentation Complexity Analysis                     | 135 |

|   | 6.7 | Vision   | s for Further HAMSTER-based Models                | 136 |

|   |     | 6.7.1    | Application or Domain Specific Programming Models | 136 |

|   |     | 6.7.2    | HAMSTER as Runtime Backend                        | 137 |

|   | 6.8 | Summ     | ary                                               | 137 |

| 7 | App | lication | Performance Evaluation                            | 139 |

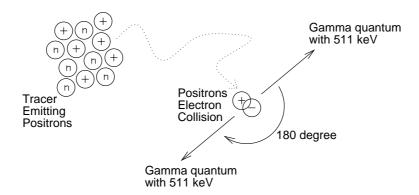

|   | 7.1 | The Pa   | rinciple of Positron Emission Tomography          | 139 |

|   | 7.2 | Recon    | struction of PET Images                           | 142 |

|   |     | 7.2.1    | Iterative PET Reconstruction                      | 142 |

|   |     | 7.2.2    | Parallel Implementation                           | 143 |

|   |     | 7.2.3    | Performance Discussion                            | 144 |

|   | 7.3 | Spectr   | al Analysis of PET Images                         | 146 |

|   |     | 7.3.1    | Application Description                           | 147 |

|   |     | 7.3.2    | Parallel Implementation                           | 147 |

|   |     | 7.3.3    | Performance Discussion                            | 148 |

|   | 7.4 | Summ     | ary                                               | 149 |

| 8 | Con | clusion  | s and Outlook                                     | 151 |

|   | 8.1 | Applic   | eability                                          | 152 |

|   | 8.2 | Future   | Directions                                        | 153 |

|   |     | 8.2.1    | Towards a Cluster-enabled Operating System        | 153 |

|   |     | 8.2.2    | A Tool Environment for On–line Monitoring         | 153 |

|   | 8.3 | Final I  | Remarks                                           | 154 |

| A | The | HAMS     | TER Execution Environment                         | 155 |

|   | A.1 | -        | n Requirements                                    | 155 |

|   |     |          | STER Directory Structure                          | 155 |

|   |     |          | ing the HAMSTER Environment                       | 156 |

|   |     |          | ng Against HAMSTER                                | 157 |

|   | A.5 | Runni    | ng Applications                                   | 157 |

| В |     |          | Sample Programming Model on Top of HAMSTER        | 159 |

|   | B.1 |          | escription                                        | 159 |

|   | B.2 | A Sim    | ple Example Code for the SPMD Programming Model   | 163 |

| Abbreviations | 169 |

|---------------|-----|

| Bibliography  | 175 |

| Index         | 199 |

# **List of Figures**

| 2.1  | Memory organization of UMA architectures.                                      | 13  |

|------|--------------------------------------------------------------------------------|-----|

| 2.2  | Memory organization in CC–NUMA architectures.                                  | 15  |

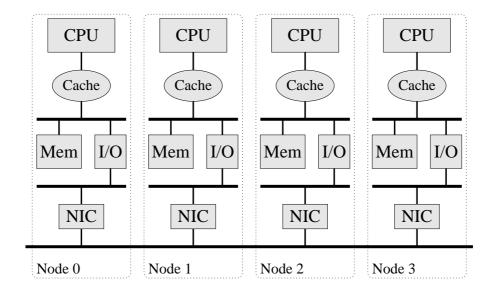

| 2.3  | Memory organization in clusters or NoWs with NORMA characteristics.            | 17  |

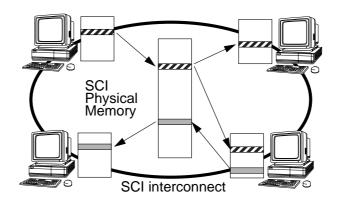

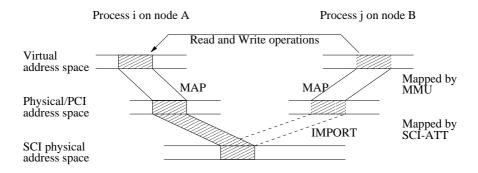

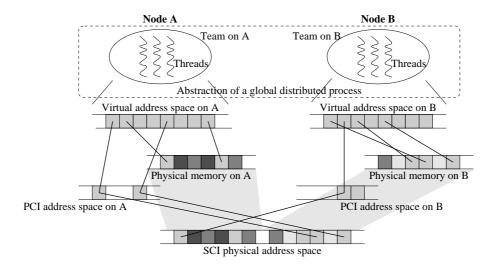

| 2.4  | SCI HW–DSM using a global address space (from [74]).                           | 19  |

| 2.5  | The various mapping levels in PC based SCI systems.                            | 19  |

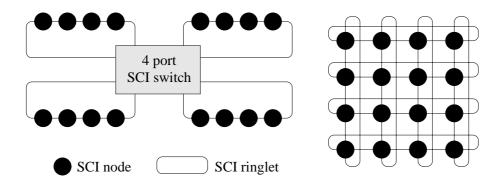

| 2.6  | Switched SCI ringlets (left) vs. two dimensional torus (right).                | 22  |

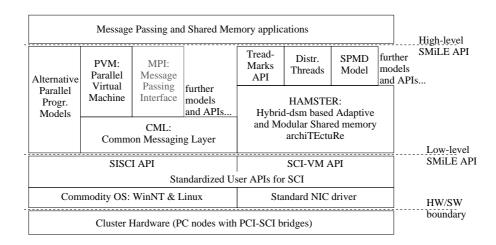

| 2.7  | Overview of the SMiLE software infrastructure.                                 | 27  |

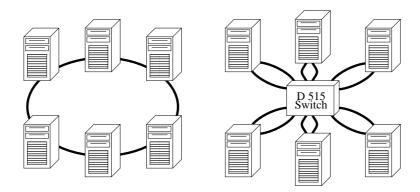

| 3.1  | SCI topologies used for the SMiLE cluster: ringlet (left) or switched (right). | 35  |

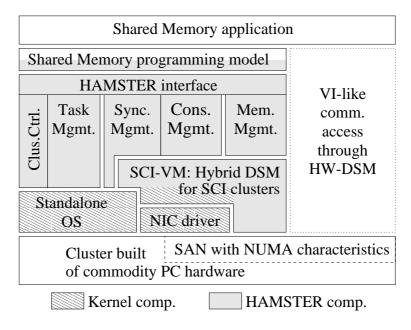

| 3.2  | The HAMSTER framework for SCI-based clusters of PCs.                           | 37  |

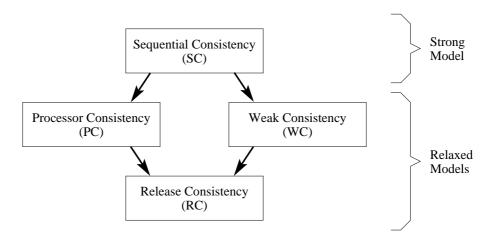

| 4.1  | Classification of memory consistency models; arrows point from stronger        |     |

|      | to more relaxed models [86, 169].                                              | 43  |

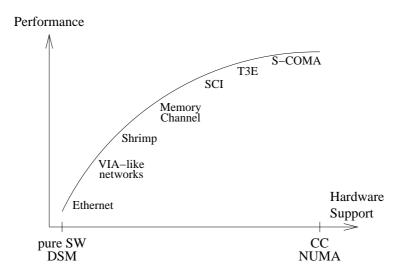

| 4.2  | Hardware complexity vs. Performance (after [201]).                             | 48  |

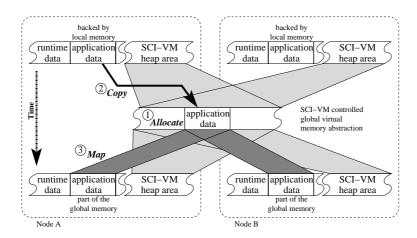

| 4.3  | Principal design of the SCI Virtual Memory.                                    | 51  |

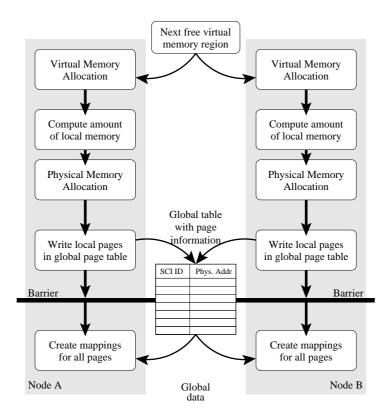

| 4.4  | Static memory allocation procedure.                                            | 53  |

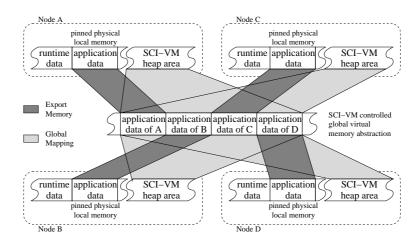

| 4.5  | Activities triggered by a page fault or swapping event.                        | 55  |

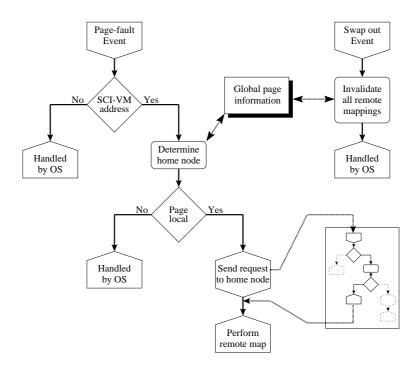

| 4.6  | Potential cache inconsistency when caching remote memory.                      | 61  |

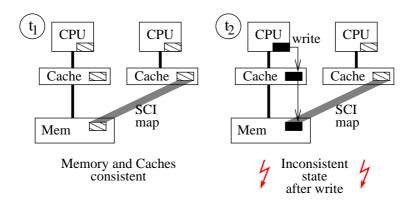

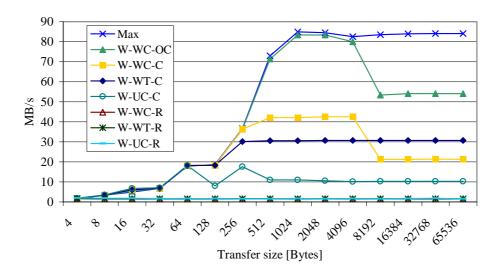

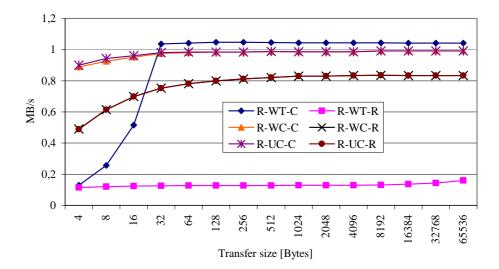

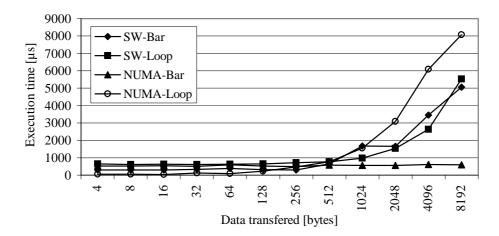

| 4.7  | Write performance on SCI-VM memory.                                            | 63  |

| 4.8  | Read performance on SCI-VM memory.                                             | 65  |

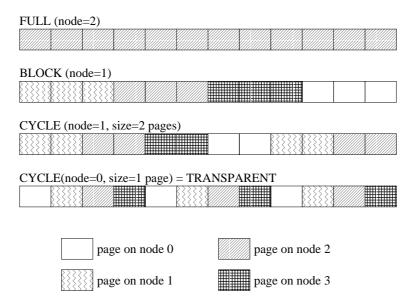

| 5.1  | Examples of memory distribution types (based on a system with 4 nodes).        | 75  |

| 5.2  | Pseudo code for the SOR code (left) and the Gaussian elimination (right).      | 76  |

| 5.3  | Speedup of dense matrix codes using locality annotations.                      | 77  |

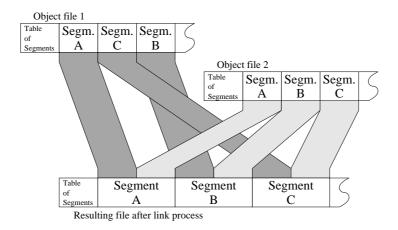

| 5.4  | Segments within the file format and linking process.                           | 80  |

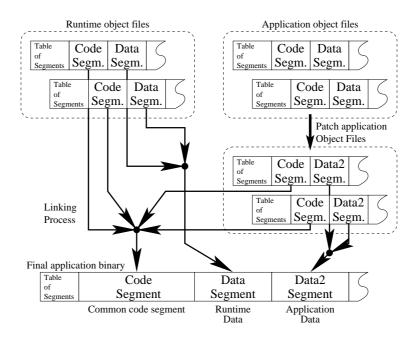

| 5.5  | Linking process after patching the application's object files.                 | 81  |

| 5.6  | Implementing the implicit access scheme to static application data.            | 82  |

| 5.7  | Implementing the explicit access scheme to static application data.            | 83  |

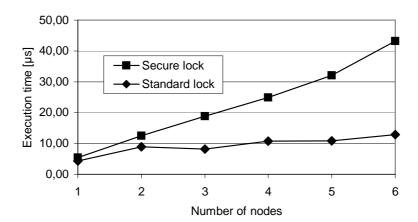

| 5.8  | Comparing the two locking algorithms under contention.                         | 95  |

| 5.9  | Lock performance under contention with secure algorithm in different SMP       |     |

|      | scenarios.                                                                     | 96  |

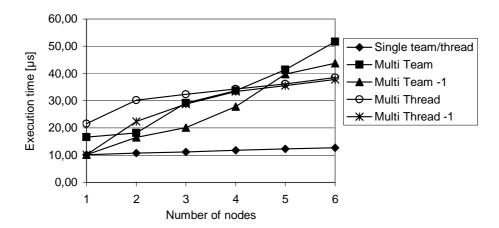

|      | Barrier performance on up to 6 nodes.                                          | 98  |

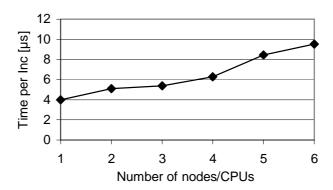

| 5.11 | Performance of atomic counters under varying numbers of nodes.                 | 100 |

| 5.12 | HAMSTER configuration file for complete SMiLE cluster consisting of 6 dual SMP nodes in SCI ringlet configuration — left: exploiting SMPs with multiple threads; right: exploiting SMPs with multiple teams per node.                                                                | 105 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

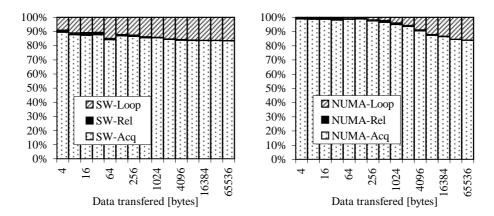

| 6.1  | Time distribution during <i>Acquire/Write/Release</i> cycle (SW–DSM left, NUMA–DSM right).                                                                                                                                                                                           | 118 |

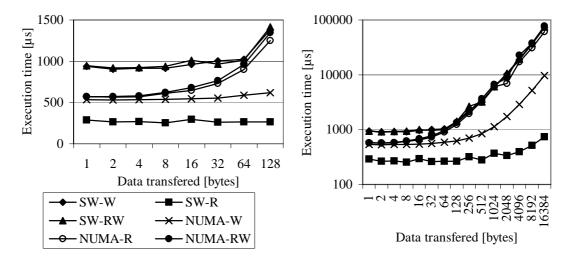

| 6.2  | Performance under <i>Read</i> , <i>Write</i> , and <i>Read/Write</i> traffic.                                                                                                                                                                                                        | 119 |

| 6.3  | Distribution of work in the <i>Read/Write</i> scenario.                                                                                                                                                                                                                              | 120 |

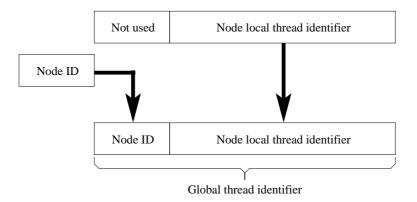

| 6.4  | Adding global information to the thread identifier of both Linux and Win-                                                                                                                                                                                                            |     |

|      | dows NT/2000 (TM).                                                                                                                                                                                                                                                                   | 123 |

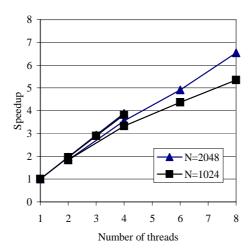

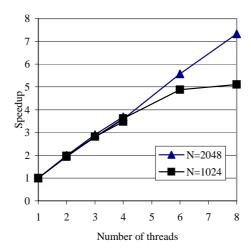

| 6.5  | Speedup of the SOR code with up to 8 threads (4 nodes/8 CPUs).                                                                                                                                                                                                                       | 128 |

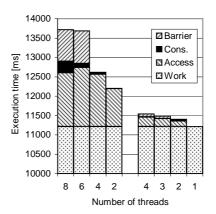

| 6.6  | Work distribution of the SOR code with up to 8 threads (4 nodes/8 CPUs) — 1024x1024 matrix (left) and 2048x2048 matrix (right).                                                                                                                                                      | 128 |

| 6.7  | Speedup of the LU code with up to 8 threads (4 nodes/8 CPUs).                                                                                                                                                                                                                        | 129 |

| 6.8  | Work distribution of the LU code with up to 8 threads (4 nodes/8 CPUs) —                                                                                                                                                                                                             |     |

|      | 1024x1024 matrix (left) and 2048x2048 matrix (right).                                                                                                                                                                                                                                | 129 |

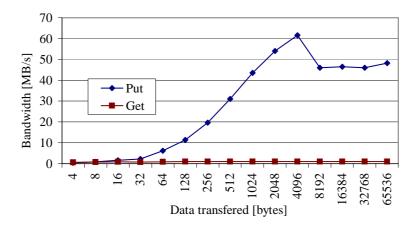

| 6.9  | Put/Get bandwidth.                                                                                                                                                                                                                                                                   | 133 |

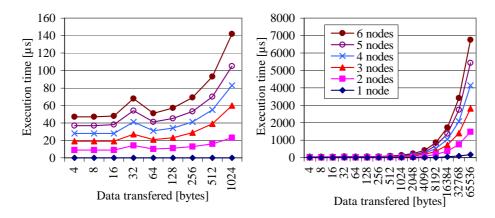

| 6.10 | Broadcast performance with varying numbers of target nodes and data transfer sizes (small transfer sizes left, large transfer sizes right).                                                                                                                                          | 134 |

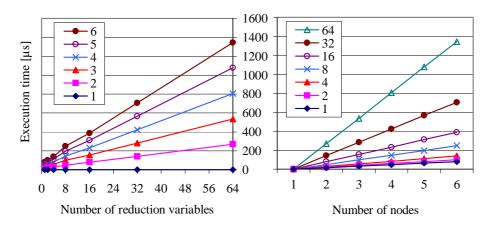

| 6.11 | Performance of collective addition across various number of nodes (left) and using various numbers of reduction variables (right).                                                                                                                                                   | 134 |

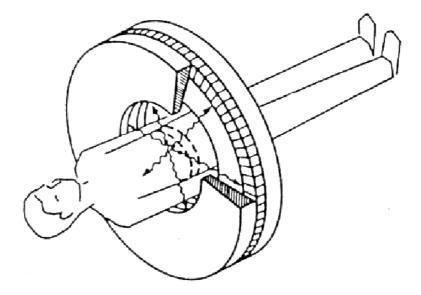

| 7.1  | Positron / Electron annihilation (from [166]).                                                                                                                                                                                                                                       | 140 |

| 7.2  | Schematic structure of a PET scanner (from [166]).                                                                                                                                                                                                                                   | 141 |

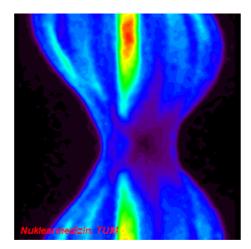

| 7.3  | Typical sinogram as delivered by the PET scanner before reconstruction.                                                                                                                                                                                                              | 141 |

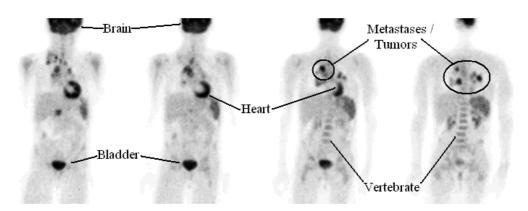

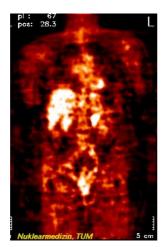

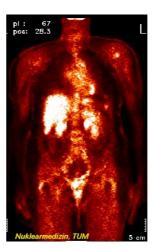

| 7.4  | Reconstructed and post–processed images of a human body, tracer F18 labeled glucose analog (FDG) (coronal slices, Nuklearmedizin TUM).                                                                                                                                               | 142 |

| 7.5  | Comparing the image quality of FBP (left) and an iterative reconstruction (right), both with tracer F18 labeled glucose analog (FDG).                                                                                                                                                | 143 |

| 7.6  | Reconstructed images — data set whole body (before proper alignment of neighboring scans and without attenuation correction; the borders between the 6 individual scans are still visible).                                                                                          | 145 |

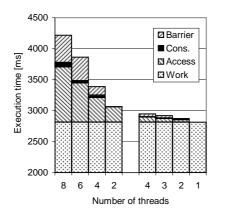

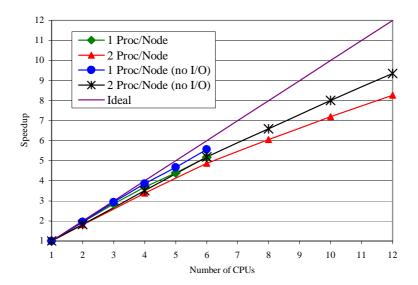

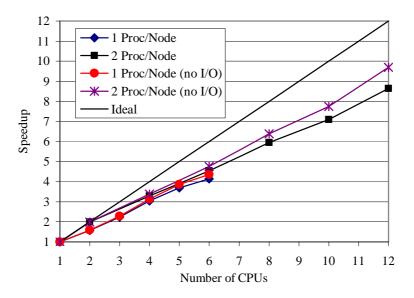

| 7.7  | Speedup of the PET image reconstruction on up to 12 CPUs.                                                                                                                                                                                                                            | 145 |

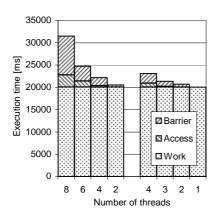

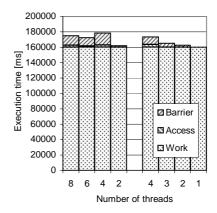

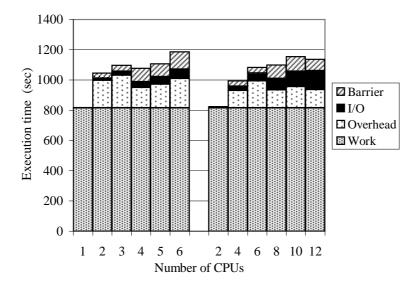

| 7.8  | Aggregated execution times for the PET image reconstruction (left: 1 thread/node, right: 2 threads/node).                                                                                                                                                                            | 146 |

|      | Sample slice of a human head, representing the impulse response function at 60 min after injection, tracer: dopamin receptor legand C–11 diprenorphin Speedup of the Spectral Analysis on up to 12 CPUs.  Aggregated execution times for the Spectral Analysis (left: 1 thread/node, |     |

| 7.11 | right: 2 threads/node).                                                                                                                                                                                                                                                              | 150 |

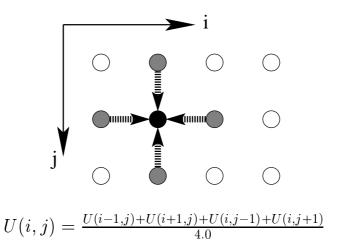

| B.1  | Update pattern for each point in the matrix.                                                                                                                                                                                                                                         | 164 |

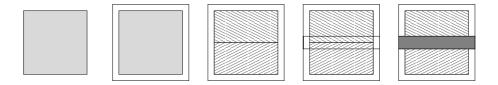

B.2 Data distribution and sharing pattern for the SOR code — from left to right: initial dense matrix, boundary, splitting the matrix, local boundary, area with implicit communication.

164

# **List of Tables**

| 3.1        | Configuration of the SMiLE cluster nodes.                                                                             | 35  |

|------------|-----------------------------------------------------------------------------------------------------------------------|-----|

| 4.1        | Performance data for low-level experiments: array sum algorithm.                                                      | 66  |

| 4.2        | Performance data for low-level experiments: matrix multiplication algorithm.                                          | 66  |

| 5.1        | API of the memory management module.                                                                                  | 73  |

| 5.2        | Statistical information collected by the memory management module.                                                    | 74  |

| 5.3        | Memory distribution types available for locality annotations.                                                         | 74  |

| 5.4        | Impact of locality annotations on dense matrix codes (on 4 nodes).                                                    | 76  |

| 5.5        | Memory coherency types.                                                                                               | 77  |

| 5.6        | Parameters to control the handling the coherency type request.                                                        | 79  |

| 5.7        | API of the consistency management module.                                                                             | 88  |

| 5.8        | System defined scopes.                                                                                                | 88  |

| 5.9        | Statistical information collected by the consistency module.                                                          | 88  |

| 5.10       | Cost of consistency enforcing mechanisms (measured on one dual proces-                                                |     |

|            | sor node of the SMiLE cluster).                                                                                       | 89  |

| 5.11       | API of the synchronization management module.                                                                         | 92  |

| 5.12       | Statistical information collected by the synchronization management module.                                           | 93  |

| 5.13       | Cost of locking operations.                                                                                           | 94  |

| 5.14       | Execution time of interrupts in HAMSTER.                                                                              | 99  |

| 5.15       | API of the task management module.                                                                                    | 101 |

| 5.16       | Statistical information collected by the task management module.                                                      | 102 |

| 5.17       | API of the cluster control module.                                                                                    | 103 |

| 6.1        | Performance of Acquire and Release operations.                                                                        | 117 |

| 6.2        | Properties of two applications running with both Release and Scope Con-                                               |     |

|            | sistency (on 4 nodes).                                                                                                | 121 |

| 6.3        | Main routines provided by the <i>Shmem</i> programming model (names simplified by the <i>Shmem</i> programming model) | 121 |

| <i>c</i> 1 | fied)                                                                                                                 | 131 |

| 6.4        | Implementation complexity of programming models using HAMSTER.                                                        | 134 |

| 7.1        | Parameters for the data set used in the experiments.                                                                  | 144 |

#### **Motivation**

Even with today's capabilities of modern microprocessors, a whole range of applications exist which are too computationally intensive in order to be solved by a single processor within a reasonable amount of time. Only by spreading the work across multiple processors can the computational power necessary for these kind of applications be aggregated. This has led to the development of parallel architectures, but has also raised the question of their programmability; how can applications organize and manage multiple activities on different processors and how can information be shared among them?

For this purpose, a variety of different parallel programming paradigms has been proposed, each providing a different approach on how to specify the intended parallelism. The two most common among them are the message passing and the shared memory paradigm; the first is based on explicit messages being sent between (in principle) independent threads or tasks on different processors while the latter one enables a single application running across all nodes to share data implicitly through a common global address space and uses additional mechanisms for explicit synchronization.

Each of these two paradigms has its strengths and weaknesses. It depends on the target application and/or on the user's preference and previous experience which paradigm is more suited for a specific parallelization. In general, however, the shared memory paradigm is seen as easier and more intuitive since it is based on a single global address space. This is very close to the sequential model, which is familiar to virtually any programmer, and hence easy to learn and understand. It also provides a simple and straightforward parallelization without major code changes, in most cases. In addition, the use of a global address space also eliminates the need for an explicit data distribution across nodes, which normally requires major changes in global data structures. This has to be seen in contrast to message passing programming models which do require an explicit data distribution across the utilized processing nodes and hence often lead to major code changes during the parallelization of an application. The strongholds of message passing, on the other hand, have to be seen in the direct mapping of the programming paradigm with its concept of processing nodes and messages being sent between them to the underlying hardware. In most cases, this ensures a more predictable performance and allows for easier performance optimizations as the programmer has to take the distributed nature of the underlying system into account from the beginning.

A free choice of a certain paradigm is in reality often restricted by external circumstances, mostly the missing support for one of them on a particular platform. This problem

can actually be found on most of the current parallel architectures or systems and hence severely limits their flexibility since it introduces additional complexity for the users. They need to adjust their codes to the subset of available programming models rather than being able to choose the models most appropriate for their target application.

Researchers in the field of parallel programming have therefore focused for a long time on eliminating this problem by providing comprehensive software infrastructures for parallel architectures, which include efficient implementations of programming models from both major paradigms on top of a single system. This thesis is a contribution to these efforts and aims at providing shared memory programming for cluster architectures with minimal hardware support in the form of a NUMA interconnection fabric, traditionally the domain of message passing models. More specifically, this work concentrates on clusters connected with the Scalable Coherent Interface (SCI) [75], an IEEE–standardized [92] state-of-the-art System Area Network (SAN) with NUMA characteristics, and provides a working prototype for these architectures.

It goes, however, one step beyond the traditional work done in this field in the respect that not only a single, new shared memory programming model is being implemented on top of the target architecture, but rather a flexible environment is created that enables the implementation of almost any shared memory programming model on top of a single shared memory core. The result is a general and open shared memory programming environment for NUMA-based clusters called HAMSTER (Hybrid dsm-based Adaptive and Modular Shared memory archiTectuRe). This environment provides a maximum of flexibility to the users since it does not require them to adjust their codes to a specific shared memory programming model or API, but instead enables them to choose the ones appropriate for their applications. This significantly increases the attractiveness of shared memory programming on NUMA-based clusters and hence represents an important step towards the envisioned complete software infrastructure for these architectures.

# 1.1 Current Deficiencies of the Shared Memory Paradigm

Despite the advantages of the shared memory paradigm with regard to easier programma-bility, the message passing paradigm currently dominates the area of High Performance Computing (HPC). For one, this can be attributed to the restricted availability of shared memory programming models on large scale systems; while message passing models, mostly represented through libraries like MPI [152] or PVM [60], have been successfully implemented on almost all common parallel architectures, programming models based on the shared memory paradigm are mostly restricted to tightly coupled machines like SMPs, which provide only a limited scalability. Only these machines feature the hardware mechanisms which enable the creation of a consistent global virtual address space.

Such support is generally not available on more scalable, loosely coupled architectures. Therefore, shared memory programming models can only be implemented using software emulation mechanisms, as is done in SoftWare Distributed Shared Memory (SW–DSM)

1.2. The Approach 3

systems. They create the illusion of a global address space and enable the user to utilize this illusion directly in their applications. These systems, however, face several inherent performance problems which are unavoidable in pure software solutions. Examples include false sharing due to large sharing granularities or complex differential update protocols responsible for packing and sending data between nodes [143]. Even though vast amounts of research worldwide have been devoted to these performance problems, no sufficient solution has been found, thereby confining SW–DSM systems mainly to the realm of research and lacking broad acceptance.

Besides these architectural deficiencies, the use of shared memory programming is further hindered by the fact that a large variety of different shared memory programming models and APIs have been developed and are present on different systems. This reaches from pure thread models, as can be found in SMPs, to explicit one–sided communication libraries and also includes all the different APIs from the individual SW–DSM systems. This greatly reduces the portability of shared memory codes since they often need to be retargeted to different APIs when being moved from one machine to another. While this porting is certainly less complex than porting codes between paradigms, it still requires a significant amount of work, increases cross–platform code maintenance, and hinders code reuse. In addition, it steeply increases the learning curve for users since they have to deal with the subtle details in both syntax and semantics of a large variety of models. All of this lowers the acceptance of shared memory programming and hinders its wider use among the HPC user community.

In summary, these deficiencies render the shared memory paradigm unsuitable for many problems and application areas, especially those generally classified as HPC. Only in certain areas, mainly those dealing with small number of processors and dynamic task structures, the shared memory paradigm has gained significant acceptance and is widely available in the form of thread libraries. In most other areas, however, message passing is dominant. This is mainly due to the standardization towards only a few portable libraries and to their straightforward implementation, even on loosely coupled architectures.

#### 1.2 The Approach

The work presented here aims at overcoming these shortcomings connected with shared memory programming and to provide users with a choice of the appropriate programming paradigm for their application needs, even on loosely coupled architectures. This is done by providing a general and open framework for shared memory programming. This framework is based on the following three principles:

#### 1.2.1 Benefiting from the Rise of NUMA Architectures

As briefly mentioned above, an implementation of shared memory programming systems on loosely coupled architectures without any hardware support possesses some inherent performance problems. This work focuses therefore on architectures that offer some support for shared memory programming models, but maintain the scalability of loosely cou-

pled architectures, as is found in NUMA (Non Uniform Memory Access) systems. More specifically, this work focuses on clusters of PCs connected by using the Scalable Coherent Interface (SCI) [75, 92] which enables a direct remote memory access to any physical memory location in hardware. This is accomplished using a global physical address space created by the network which can be used as the basis for shared memory programming.

In general, NUMA architectures, whether they are cluster-based or implemented as more integrated Massively Parallel Processor (MPP) systems, require only limited hardware resources for their remote memory access capabilities and hence can be implemented in a straightforward manner. In addition, they are not based on a centralized component or global maintenance protocol and therefore show very favorable scaling properties. On the software side, the remote memory access capabilities can be exploited for both shared memory programming and high performance messaging [51], making these kinds of platforms very attractive for a broad range of users and application domains. Due to these properties, all kinds of NUMA architectures are becoming increasingly popular and could rise to become the dominating architecture in the near future, thereby making work in this direction very promising.

#### 1.2.2 Exploiting Hybrid-DSM Techniques

In order to exploit such NUMA architectures in a loosely coupled scenario, like it is given in cluster architectures, a new type of DSM system must be developed. On one side, it has to directly exploit the benefits provided by the NUMA hardware, while on the other side, a strong software component needs to ensure a global view onto the distributed system across the individual nodes and distinct operating system instances. This results in a hybrid DSM scheme, which merges the hardware DSM support found in NUMA systems in the form of remote memory access capabilities with the global memory management of traditional software DSM systems. In such a system, any communication is efficiently performed directly in hardware without any protocol overhead and it thereby forms a bridge between SW–DSM systems on cluster architectures on one side and complex hardware supported shared memory systems on the other.

For the implementation of a hybrid DSM system, one major challenge needs to be solved: the gap between the global physical memory provided by the NUMA system and a global virtual memory abstraction required for shared memory programming needs to be closed. This is achieved in tight cooperation with the underlying operating system through a global memory management component. This software module extends the concept of virtual memory to all participating nodes within the system. The result is a global virtual memory abstraction backed transparently by distributed physical resources which can then directly be used for any kind of shared memory programming.

#### 1.2.3 Towards an Open Architecture for Shared Memory

Such a hybrid DSM system alone, however, has only the ability to solve one of the problems mentioned above, namely the performance problems of DSM systems in loosely coupled environments. The second problem, the availability of (too) large a number of different

1.3. Contributions 5

APIs and programming models would remain, if not further worsened, because the new hybrid DSM would introduce yet another API. On the other side, it is also illusory to work towards a unified programming model since it would be impossible to convince people to retarget applications and systems towards a new API based only on its claims to be "better" or "unified".

Therefore, another approach has to be found to help users deal with the abundance of programming models in a manner that allows them to avoid extra porting or maintenance efforts for their applications. The solution for this problem proposed by the work presented here and implemented in HAMSTER (Hybrid–dsm based Adaptive and Modular Shared memory archiTEctuRe) consists of a comprehensive framework which enables the availability of multiple models on top of a single system. This system is designed in a way that additional programming models can easily be added without requiring much implementation complexity thereby making it feasible to create as many programming models as required.

With this approach, the user is no longer bound to the one programming model provided by the target system, but has the option to choose a model fitting to the particular application. This can either be an existing programming model or API adopted from another platform to ease the porting of existing applications or a new programming model specifically deployed to support a special class or domain of applications. In both cases, the user is alleviated from tedious porting and implementation efforts thereby significantly easing the use of shared memory environments.

#### 1.3 Contributions

This work provides the following main contributions:

#### • Modular framework for arbitrary shared memory programming models

The HAMSTER system, as presented in this work, provides the ability to implement almost any kind of shared programming model on top of a single core. With that, it enables users to work with different models on a single system at the same time without having to worry about obtaining, installing, and maintaining a large number of models or porting a given application to the particular model available on the target machine, which is often a cumbersome task. This system therefore allows users to choose the programming model most suited to the application needs for an efficient implementation rather than to the hardware and software constraints on the target platform.

This capability has been tested within this work based on several selected programming models. These models range from full thread libraries to explicit shared memory programming models and also include the emulation of various APIs from traditional SW–DSM systems. Each of these programming models was implemented with only limited complexity proofing both the feasibility and the flexibility of the pursued approach.

#### Orthogonal support for shared memory services

This ability to support almost any programming model on top of a single framework is created by providing a large variety of shared memory services. These services include facilities for memory, consistency, synchronization, and task management and are organized in several distinct and independent modules. The modules themselves are organized in a way that ensures a full orthogonality between them, i.e. each service can be used without unwanted side effects. This guarantees the required flexibility for the easy and safe implementation of shared memory programming models on top of these services.

Each of these management modules has been implemented in a way ensuring a maximum of flexibility and performance. Special care in this respect has been given to synchronization and consistency enforcing mechanisms. Both have been implemented in a very lean manner taking direct advantage of present hardware mechanisms, thereby avoiding unnecessary overheads and providing a rich functionality. This enables the user of HAMSTER to create the necessary synchronization constructs and consistency models for the intended target programming models in an efficient and straightforward manner without high implementation complexity.

#### • Hybrid-DSM core for NUMA-based clusters

In order to guarantee an efficient performance for all programming models implemented on top of HAMSTER, the framework includes a new type of DSM system, a hybrid hardware / software DSM system. It directly exploits the hardware capabilities of the underlying NUMA architecture without losing the two main advantages of loosely coupled architectures, scalability, and cost effectiveness. It provides the necessary support to transform NUMA support for a global physical memory into a global virtual memory abstraction suitable for the implementation of shared memory programming models.

A prototype based on these concepts has been implemented on top of clusters of PCs interconnected by the Scalable Coherent Interface (SCI) [75, 92]. This prototype shows both the feasibility and the efficiency of the approach presented in this work. The overall concepts, however, are not restricted to this specific NUMA architecture alone, but can be principally be applied to any NUMA–like architecture and hence represents a general approach for shared memory programming on these kinds of architectures.

#### • Detailed performance evaluation

This work includes a detailed performance assessment of the overall system using several applications and computational kernels from various areas as well as an evaluation of the individual components used to create the shared memory services and management modules. This allows a detailed insight into the system characteristics and provides useful hints for future users of the system.

In summary, this work provides a comprehensive framework which aims at overcoming the current problems of shared memory programming for loosely coupled architectures with NUMA characteristics. With its ability to support arbitrary shared memory programming models, it guarantees a high degree of flexibility and openness. Additionally, these properties are achieved without sacrificing performance since the overall system is based on an efficient Hybrid–DSM core, capable of directly exploiting the advantages of NUMA architectures.

#### 1.4 Thesis Organization

The thesis is organized as follows: Chapter 2 introduces the fundamental concepts of this work from both the programming model and the architectural point of view and briefly discusses the context from which it originates. The work itself, the HAMSTER framework, is introduced in Chapter 3 together with the discussion of its fundamental design guidelines and principles.

The following chapters discuss the various components of the HAMSTER system in detail: Chapter 4 presents the hybrid hardware / software distributed shared memory system, followed by the discussion of the various shared memory services provided by several independent modules in Chapter 5. These services are then used to form shared memory programming models, which is shown in Chapter 6.

In Chapter 7, the overall system is evaluated using two larger applications from the area of nuclear medical imaging. Based on these codes, both HAMSTER's capabilities to support new codes on top of special programming models and the porting of existing codes using standard programming models have been evaluated proving the efficiency and wide applicability of the HAMSTER framework.

In conclusion, Chapter 8 offers a brief outlook on future work and closes with some final remarks.

The work is completed with a short manual containing information on how to run applications using HAMSTER in Appendix A and with a small example of a HAMSTER–based programming model in Appendix B.

# **Background**

Before going into the details of the shared memory framework for NUMA-based clusters proposed in this thesis, it is necessary to look at a few basic concepts. This chapter first discusses the principles of shared memory from both the programmer's and the architectural point of view and presents the problems associated with different approaches. It then introduces a NUMA-based cluster interconnection fabric — the Scalable Coherent Interface (SCI) — as a suitable tradeoff between hardware support for shared memory programming and architectural scalability and provides a detailed overview of its history, current status, and its use in both the commercial world and the research community. The chapter ends with a brief description of the context of this work.

#### 2.1 Shared Memory Programming

Shared memory programming generally refers to parallel programming models that exhibit a global virtual address space which can then be used to share data implicitly among multiple tasks potentially located on different processors. Synchronization between the individual tasks within a parallel application is accomplished by using additional explicit mechanisms specific to the programming model. Additionally, the task model, i.e. the control over the concurrent activities within a parallel application, varies from model to model and can range from a static task assignment to processors to a fully dynamic scheme with task creations and destructions during the runtime of the application.

Compared to other paradigms, this basic approach is often seen as more intuitive and easier to learn since it eliminates the need for explicit communication and data distribution. Rather data is shared in the global address space and can be accessed from there by any node at any time. This simplicity makes the shared memory paradigm especially suitable for programmers with little experience in parallel programming or for those lacking a formal computer science background.

#### 2.1.1 Definition of Shared Memory Programming Models

The exact connotation of the term "Shared Memory" is influenced by the direction from which it is seen: when looking at it from an architectural view, it normally denotes the ability of the architecture to access global data, while from a programming model point of view, the sharing of data is emphasized. In the latter context, often the term "Shared

Variable Programming" [33] is used as a synonym.

In the context of this work, the term "shared memory programming model" refers to parallel programming models which exhibit a single global virtual address space to all tasks within the parallel program. This address space is then used for any communication between the tasks and does not require the use of any explicit communication or copy routines. Besides this basic definition of memory behavior, no further restrictions to the type of used programming model is set forth. This refers especially to synchronization mechanisms and the task structure offered by the programming model. Their definitions are intentionally left open to include a wide range of models and hence to increase the scope of this work.

#### 2.1.2 Available Models and APIs

Based on this general definition, many different types of shared memory programming models and systems exist. The following list provides an overview of the major subtypes:

#### • Thread libraries

The most typical representatives of shared memory programming models are thread libraries. Such libraries are present in any modern operating system and are mostly used to exploit the capabilities of SMPs. Examples for thread libraries are *POSIX threads* [219] as implemented e.g. in Linux, *Solaris* threads [148], a slight variation for SUN Solaris platforms, *Win32 threads* [154] available in Windows NT<sup>TM</sup> and Windows 2000<sup>TM</sup>, and *Java* threads [104] as part of the standard Java<sup>TM</sup> Development Kit (JDK).

Next to these operating system inherent implementations of thread packages, also several standalone thread libraries exist, mostly from the research community. Examples for this are the FSU threads [163] or the ACE thread package [191].

#### • Distributed Shared Memory systems

Distributed Shared Memory (DSM) systems aim at emulating a shared memory abstraction on loosely coupled architectures in order to enable shared memory programming despite missing hardware support. They are mostly implemented in the form of standard libraries and exploit the advanced user–level memory management features present in current operating systems. In recent years, a large number of such systems, each with its own API, have been developed by the research community, but only one, the TreadMarks system [5], has made it to the product stage. Examples for research systems are IVY [136], the predecessor of all DSM systems, Munin [29], Brazos [209], Shasta [189], and Cashmere [213]. A more comprehensive list and a detailed description of DSM systems can be found in Chapter 4.1.

#### • Macro packages for parallel programming

Special macro packages can also be used for the construction of parallel shared memory applications, although they do not represent full programming models. They

merely provide an easy and high–level way to specify the intended parallelism in the target applications and provide the appropriate preprocessor rules to transparently transform these into intermediate applications based on a second, often platform specific shared memory programming model at a much lower level of abstraction. The most prominent example for this kind of approach are the ANL or *parmacs* m4 macros, which are used within the SPLASH [206, 233] benchmark suite and exist for a variety of different shared memory platforms.

#### • Parallel Programming Languages with global address space

In addition to the library–based programming models discussed so far, parallel programming languages based on the shared memory paradigm also exist. The most prominent example among them is High–Performance Fortran (HPF) [236], a data parallel language, which allows the specification of parallelism based on shared arrays. A compiler then transfers the program into a message passing code which can then be executed on the target machine. The programmers, however, do not need to deal with the translated code and therefore maintain the shared memory view on their application at all times. Due to these properties, HPF has gained acceptance among the Fortran and scientific computing community and is available on most MPPs.

Besides HPF, also further parallel shared memory languages, again mostly research—based, exist. An examples for this is ZPL [139], developed and maintained at the University of Washington, a data—parallel array programming language.

#### Program Annotation Packages

Between library based models and full shared memory programming languages, a third principal approach exists which is based on code annotations. A quite renowned approach in this area is OpenMP [172], a newly developed industry standard for shared memory programming on architectures with uniform memory access characteristics. In contrast to HPF, OpenMP is based on task parallelism and focuses mostly on the parallelization of loops.

OpenMP implementations use a special compiler to evaluate the annotations in the application's source code and to transform the code into an explicitly parallel code which can then be executed. In contrast to full parallel languages, annotated codes can still be compiled with standard compilers which ignore the annotations and produce normal sequential codes. Hence a common code basis of sequential and parallel versions can easily be maintained.

#### Explicit shared memory

Lying on the border of the definition of shared memory programming models are explicit shared memory programming models. In such systems, accesses to remote data are no longer fully transparent, but are normally executed through special remote memory access routines provided by the programming model which copy the data to the intended remote location. Accesses to local data however are still carried

out directly without the need to call specific routines. An example for such an explicit model is the so called "shmem" library provided by SGI and Cray for the MPP machines [98].

One step further than the Cray shmem library are approaches like Linda [230] or Java<sup>™</sup> Spaces [158]. They no longer provide even a transparent access to any part of the data, but rather require users to explicitly call routines for data storage and retrieval at any time. However, a global address space of some kind is also present in these approaches, making them at least related to shared memory.

#### 2.1.3 Shortcomings of Shared Memory Programming

Despite the advantages of shared memory programming discussed above, this paradigm has by far not reached the same level of acceptance as the message passing paradigm, especially in the area of High Performance Computing (HPC). This can be attributed to mainly two shortcomings inherently connected with shared memory programming:

#### Abundance of Different APIs without a Dominant Standard

One shortcoming is already directly visible from the pure size of the list of examples of shared memory programming models presented above. This abundance of different models severely restricts both code portability and reuse since codes and code parts frequently have to be ported from one shared memory programming model to another. In addition, each programming model may have subtle differences in both syntax and semantics with regard to their APIs thereby causing ports to be cumbersome and error prone. This results in a steep learning curve for programmers dealing with more than one system or programming model.

#### **Limited Scalability of the Underlying Architectures**

The second shortcoming comes from an architectural point of view. Shared memory programming normally requires hardware support to be present in the underlying hardware architecture. Traditionally, such support is only available in tightly coupled systems, such as Symmetric MultiProcessors (SMPs). These architectures, due to their need for a tight coupling between the individual processors, generally exhibit rather unfavorable scaling properties and hence provide only a limited amount of aggregated computational power limiting their use.

#### 2.2 Architectural Support for Shared Memory

In order to further illustrate this shortcoming of limited scalability and to point towards approaches to overcome it, it is necessary to briefly talk about the various types of memory organizations in existing architectures and their support for shared memory programming. This will help understand the implications introduced by hardware shared memory support

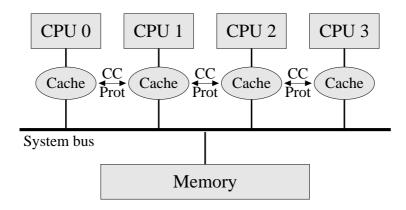

**Figure 2.1** Memory organization of UMA architectures.

with respect to scalability and performance and will allow to judge the suitability of existing architectures for shared memory programming.

To structure this discussion, a simple and straightforward classification of architectures based upon their type of global memory access is used. Based on this scheme, three major types can be identified:

#### • UMA – Uniform Memory Access architectures

In this class of architectures, any memory location can be reached from any processor with the same access characteristics in terms of cost (i.e. uniform)

#### • NUMA – Non Uniform Memory Access architectures

Like UMA systems, these architectures allow any processor to access any memory location directly, but the access characteristics varies with respect to the access latency.

#### • NORMA – NO Remote Memory Access architectures

In this class of architectures no direct hardware support is available to access memory locations other than those local to a processor.

#### 2.2.1 Full Hardware Support within UMA Systems

The first class of architectures discussed in more detail are the UMA (Uniform Memory Access) architectures. Their general structure is shown in Figure 2.1. A number of processors, potentially with additional caches in the memory path, are connected to a single global memory through a common system bus. Such busses are normally only able to cover short distances due to their electric properties, which leads to systems with all processors installed within one box. Such systems are therefore often referred to as tightly coupled systems.

This organization is currently widely used in Symmetric MultiProcessor (SMP) machines. In these machines several processors of the same type and speed are coupled to a

single system. In addition, no one of these processors has a special role; instead all nodes are configured in a fully symmetric way<sup>1</sup>. Typical configurations range from 2 or 4 processors in commodity PC-based system [38] to up to 16 or 32 processors in high-end servers, like the SGI Power Challenge<sup>TM</sup> [58] and the SUN Enterprise systems [251].

As any processor is connected to the global memory through the system bus, it can directly access any memory location resulting in a full hardware support for shared memory. In the presence of caches, SMP machines also provide an appropriate cache coherency protocol [175], which automatically guarantees a coherent state of all involved caches. This maintains their transparency known from single processor systems also in such a multiprocessor scenario. On the software side, these systems are normally equipped with the appropriate operating system support for multiple processors, especially with respect to a global virtual memory management. The shared memory can therefore be easily exploited by the users without the need for any additional software complexity.

The major drawback to these architectures is their limited scalability. Any access to the memory has to be performed across a single bus, leading to a major bottleneck with rising numbers of processors. This can be seen with respect to both performance, due to bus contention, and space, due to the limited distances such buses are able to cover. In recent years, a significant amount of effort has been invested in the area of high–end servers to reduce this bottleneck, leading e.g. to the PowerPath™ bus system [58] used in the SGI systems. However, the principal problems remain. Due to this, the number of processors within an SMP system with which a system is still able to provide sufficient performance will always be limited.

The only way to overcome this problem is to leave the bus-based design and deploy new, more scalable interconnection technologies which do not suffer from the contention problem. An example for such a novel approach can be found in the SUN Starfire architecture [34] which couples up to 16 boards with 4 Sparc processors each using point—to-point links through a highly efficient crossbar backplane. Such a design, however, requires a very complex hardware in order to keep the total memory latency both uniform and at an acceptable level.

#### 2.2.2 Improving Scalability with CC-NUMA

This scalability problem of SMPs with UMA organization has led to the development of CC–NUMA machines. In this class of architectures, whose typical layout is depicted in Figure 2.2, again any processor has direct access to any memory location in the whole system. This memory, however, is now distributed to the individual processor nodes and no longer only available at a single location. This introduces a distinction between local and remote memory, i.e. memory on the same or on another processor node than the accessing processor. This distinction with respect to memory location consequently also leads to a distinction in memory access types, which can also be local or remote and therefore lead to different (non–uniform) memory access times.

<sup>&</sup>lt;sup>1</sup>The only exception is normally visible at boot time, where one processor takes the role of a master and controls the further initialization of the remaining processors.

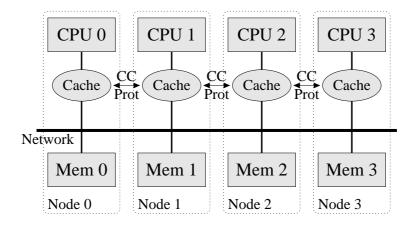

**Figure 2.2** Memory organization in CC–NUMA architectures.

This concept of CC-NUMA architectures enables the construction of systems with a larger number of processors since it allows a more flexible packing with individual nodes each with its own memory and replaces the single common bus with a more flexible internode interconnection fabric. To further raise the number of processors, CC-NUMA machines often use a hybrid scheme with SMP nodes with a small number of processors sharing a local memory connected by a CC-NUMA interconnection fabric.

Like in the UMA case, a cache coherence protocol (hence the name CC–NUMA) is deployed to maintain the transparency and consistency of the caches in the system. Its implementation, however, is normally much more complex than in a UMA scenario because it has to take the increased latencies for remote accesses and the potentially higher number of involved CPUs and caches into account. This has led to new approaches in the area of cache coherency protocols [175, 86, 202].

The concept of CC–NUMA machines (sometimes referred to as S2MP: Scalable Symmetric MultiProcessing) has gained quite a bit of popularity in the last few years and has led to both research prototypes, like the FLASH architecture [128], and a number of commercial developments which are used for both server and scientific computing applications. Commercial examples include the SGI O2000/O3000<sup>™</sup> series [131], which couples Dual SMP nodes to a CC–NUMA architecture, the Exemplar<sup>™</sup> [35] machines by Hewlett Packard (formerly by Convex) with its 8–way SMP nodes connected by four independent cross–node links, and the Numa–Liine<sup>™</sup> [37] by Data General coupling 4–way SMP nodes based on the PC architecture using a CC–NUMA interconnection fabric. These systems allow processor numbers in the range of 32 to 128 processors and hence significantly exceed the typical number of processors in current SMP systems.

Together with appropriate software mechanisms, present in proprietary operating systems or extensions thereof, which are available on all of these machines, the concept of CC–NUMA architectures, like their UMA counterparts, enables users to directly exploit shared memory programming in a fully coherent global address space. The distributed nature of the underlying memory resources, however, requires the user to take this distri-

bution into account and to optimize with respect to data locality, which leads to additional complexity in using such systems for parallel processing.

#### 2.2.3 Transitions Towards Pure NUMA Systems

A problem of these CC–NUMA architectures is their often quite complex cache coherency protocol. While extremely useful for the user, as it maintains the cache transparency known from single processor systems, it again forms a limit for the scalability of the overall system. This is caused, for one, by the complexity of the protocol which can lead to a performance problem and, secondly, by the requirement of tightly coupling the individual nodes from a logical point of view to allow the maintenence of a global state.

This observation has inspired non–CC–NUMA architectures without a global cache coherency protocol, which will simply be referred to as NUMA architectures in the following. Such systems are capable of supporting a larger number of processors since the only hardware requirement imposed by a NUMA system is the ability to perform loads and stores to remote memory locations. The implementation of this capability requires only very little hardware complexity enabling a simple and cost effective system design. This reduced complexity on the hardware side, however, leads to a higher complexity demand in software as applications have to compensate for the missing hardware coherency. This can, however, even lead to a higher performance compared to CC–NUMA machines, as the coherency control can be adapted to the application needs instead of using a general cache coherency protocol.