### Lehrstuhl für Realzeit-Computersysteme

# Scheduling with Message Deadlines for Hard Real–Time SDL Systems

Thomas Kolloch

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktor-Ingenieurs (Dr.-Ing.)

genehmigten Dissertation.

| Vorsitzender:            | UnivProf. DrIng. K. Antreich       |

|--------------------------|------------------------------------|

| Prüfer der Dissertation: | 1. UnivProf. DrIng. G. Färber      |

|                          | 2. UnivProf. DrIng. J. Eberspächer |

Die Dissertation wurde am 17.01.2002 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 18.06.2002 angenommen.

# Summary

Hard real-time system design requires both, a methodology that allows to control the increasing functional complexity and additionally an a-priori proof that all timing requirements will be met even in worst case situations. This work introduces a design heuristics based on the formal "Specification and Description Language" SDL aiming on the integration of a timeliness verification into an automated design process.

SDL's semantics which is especially suited to event-driven systems relies on nonblocking signal exchange, i.e. a receiving SDL process will be activated on signal arrival. To enforce a deterministic behaviour of a SDL system, the vague semantics of SDL has to be pinpointed to a predictable model of computation. For this, <u>Message based Earliest</u> <u>Deadline First scheduling (MEDF)</u> will be suggested as basis for SDL's processing sequence.

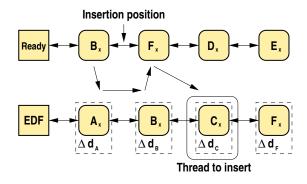

With MEDF, a task inherits the deadline transported by an incoming message, i.e. its dynamic priority is adapted accordingly. Finally, the task bequeathes this deadline to its outgoing messages. For predictability reasons, incoming messages carrying a new deadline now have to be inserted into a task's only queue in a deadline sorted order. Deadline inheritance (DIP), respectively deadline ceiling (DCP) applied to message queues raise the dynamic priority of the receiving task and assure the avoidance of priority inversion effects caused by server tasks responding to multiple requests with unequal urgencies. Since MEDF scheduling implicates an earliest deadline first processing sequence for all tasks, Gresser's schedulability analysis methodology for event–driven real–time systems [Gre93a] can be applied to prove the timeliness of a MEDF system.

With these presumptions, a real-time system's implementation and its worst case timing behaviour can be automatically derived on the basis of its SDL system specification by one strike, if the system model has been extended by timing constraint annotations (deadlines, execution times, timing of system stimuli). Code generation that preserves MEDF processing sequence on the one hand, and mapping of the system specification to a task precedence graph (TPG) mirroring the structural inter-relationships between all resource-sharing components on the other hand, assures conformance between specification, implementation, and analysis model. The latter incorporates all necessary timing properties to perform the final schedulability analysis step and serves as information source to reveal hidden unpredictability and optimization potential in SDL system models.

The MEDF scheduler has been integrated into the real-time operating system RTEMS. An additional test suit validates the correct functionality of the scheduler and demonstrates its timing behaviour. Tool support for the proposed design methodology has been prototypically realized and its applicability has been evaluated with design examples. iv

# Contents

| Sι            | ımma                             | ry                                                                                                                                                                                                                      | iii                                          |

|---------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| C             | onter                            | ts                                                                                                                                                                                                                      | $\mathbf{v}$                                 |

| $\mathbf{Li}$ | st of                            | Acronyms and Variables                                                                                                                                                                                                  | ix                                           |

| $\mathbf{Li}$ | st of                            | Figures                                                                                                                                                                                                                 | xi                                           |

| Li            | st of                            | Tables                                                                                                                                                                                                                  | v                                            |

| 1             | <b>Intr</b><br>1.1<br>1.2<br>1.3 | oduction         Contribution         Prerequisites and Restrictions         This work's background:                                                                                                                    | 1<br>2<br>2<br>5                             |

|               | 1.4                              | Synopsis                                                                                                                                                                                                                | 7                                            |

| 2             | Rela<br>2.1<br>2.2<br>2.3<br>2.4 | Schedulability Analysis                                                                                                                                                                                                 | 9<br>9<br>11<br>12<br>14                     |

| 3             | <b>SDI</b><br>3.1<br>3.2         | Specification and Description Language SDL                                                                                                                                                                              | 17<br>18<br>19<br>20<br>21<br>21<br>21<br>22 |

|               | 3.3                              | 3.2.3       SDL Process Activation       2         3.2.4       Atomicity and Run–To–Completion Semantics       2         Finalization/Restriction of SDL's Semantics       2         3.3.1       MEDF Semantics       2 | 22<br>23<br>23<br>23<br>23<br>23<br>23       |

|   |              | 3.3.3          | MEDF Process Sequencing                        |   |   |   |     | • |   |   |   |   | • | 25         |

|---|--------------|----------------|------------------------------------------------|---|---|---|-----|---|---|---|---|---|---|------------|

|   |              | 3.3.4          | MEDF Timers                                    |   |   |   |     |   |   |   |   |   | • | 26         |

|   |              | 3.3.5          | Discussion of further SDL Language Constructs  |   |   |   |     |   |   |   |   |   |   | 27         |

|   | 3.4          | Non-fr         | unctional Specification                        |   |   |   |     |   |   |   |   |   |   | 28         |

|   |              | 3.4.1          | Timing Constraints                             |   |   |   |     |   |   |   |   |   |   | 28         |

|   |              | 3.4.2          | Extensions to the Functional Model             |   |   |   |     |   |   |   |   |   |   | 29         |

|   | ~            |                |                                                |   |   |   |     |   |   |   |   |   |   | ~ 1        |

| 4 |              |                | eration                                        |   |   |   |     |   |   |   |   |   |   | 31         |

|   | 4.1          |                | position Principles                            |   |   |   |     |   |   |   |   |   |   | 32         |

|   |              | 4.1.1          | Decomposition by Maximizing Parallelism        |   |   |   |     |   |   |   |   |   |   | 32         |

|   |              | 4.1.2          | Decomposition by Timing Constraints            |   |   |   |     |   |   |   |   |   |   | 33         |

|   |              | 4.1.3          | Minimizing Interprocess Communication          |   |   |   |     |   |   |   |   |   |   | 33         |

|   | 4.2          |                | of-the-Art Code Generators                     |   |   |   |     |   |   |   |   |   |   | 35         |

|   |              | 4.2.1          | SDT's C–Basic and C–Advanced                   |   |   |   |     |   |   |   |   |   |   | 35         |

|   |              | 4.2.2          | SDT's C–Micro                                  |   |   |   |     |   |   |   |   |   |   | 37         |

|   | 4.3          | Code (         | Generation for MEDF Semantics                  |   |   |   |     |   |   |   |   |   |   | 37         |

|   |              | 4.3.1          | Server Model                                   |   |   |   |     |   |   |   |   |   |   | 38         |

|   |              | 4.3.2          | Activity Thread Model                          |   |   |   |     | • |   |   |   | • |   | 39         |

|   |              | 4.3.3          | System Time and MEDF Timers                    |   |   |   |     |   |   |   |   |   |   | 41         |

|   |              | 4.3.4          | System Environment and Software Architecture   |   |   |   |     | • |   |   |   | • |   | 42         |

| 5 | Sch          | odulin         | g with Message Deadlines                       |   |   |   |     |   |   |   |   |   |   | 45         |

| 0 | 5.1          |                | Scheduling Scheme                              |   |   |   |     |   |   |   |   |   |   | <b>4</b> 5 |

|   | $5.1 \\ 5.2$ |                | tability of MEDF                               |   |   |   |     |   |   |   |   |   |   | 40<br>46   |

|   | 0.2          | 5.2.1          | Task Precedence Constraints                    |   |   |   |     |   |   |   |   |   |   | 40<br>46   |

|   |              | 5.2.1<br>5.2.2 |                                                |   |   |   |     |   |   |   |   |   |   | 40<br>50   |

|   |              |                | Sequencing                                     |   |   |   |     |   |   |   |   |   |   | 50<br>51   |

|   |              | 5.2.3          | Message Blocking on Server Tasks               |   |   |   |     |   |   |   |   |   |   | 51<br>56   |

|   | ۲ ۹          | 5.2.4          | Mutual Exclusion on Semaphores                 |   |   |   |     |   |   |   |   |   |   |            |

|   | 5.3          |                | me System Support                              |   |   |   |     |   |   |   |   |   |   | 56         |

|   |              | 5.3.1          | The EDF Event Object                           |   |   |   |     |   |   |   |   |   |   | 57         |

|   |              | 5.3.2          | The MEDF Message Queue                         |   |   |   |     |   |   |   |   |   |   | 58         |

|   | <b>-</b> ,   | 5.3.3          | Priority Inversion Avoidance                   |   |   |   |     |   |   |   |   |   |   | 59         |

|   | 5.4          | -              | lexity and Execution Times                     |   |   |   |     |   |   |   |   |   |   | 63         |

|   | 5.5          | Optim          | ized Server Model Scheduler                    | • | • | • | • • | • | • | • | • | • | • | 69         |

| 6 | SDI          | L Real-        | -Time Analysis                                 |   |   |   |     |   |   |   |   |   |   | 75         |

|   | 6.1          | Real-7         | Fime Analysis                                  |   |   |   |     |   |   |   |   |   |   | 77         |

|   |              | 6.1.1          | Task Model                                     |   |   |   |     |   |   |   |   |   |   | 77         |

|   |              | 6.1.2          | Analysis Algorithm                             |   |   |   |     |   |   |   |   |   |   | 78         |

|   |              | 6.1.3          | Influence of System Environment and Timer Task |   |   |   |     |   |   |   |   |   |   | 80         |

|   | 6.2          |                | tion of the Real–Time Analysis Model           |   |   |   |     |   |   |   |   |   |   | 82         |

|   |              | 6.2.1          | Task Precedence Graph (TPG) Synthesis          |   |   |   |     |   |   |   |   |   |   | 82         |

|   |              | 6.2.2          | Derivation of the Worst–Case TPG               |   |   |   |     |   |   |   |   |   |   | 85         |

|   |              |                |                                                |   |   |   |     |   | - |   |   |   |   |            |

|    |                                      | 6.2.3                                                                              | Calculation of Start Times                           |   |   |   |          | •           | 86                                                                                                    |

|----|--------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------|---|---|---|----------|-------------|-------------------------------------------------------------------------------------------------------|

| 7  | Cas                                  | e Stud                                                                             | y and Evaluation                                     |   |   |   |          |             | 89                                                                                                    |

|    | 7.1                                  |                                                                                    | bus Attitude and Orbital Control System              |   |   |   |          |             | 89                                                                                                    |

|    |                                      | 7.1.1                                                                              | SDL System Model                                     |   |   |   |          |             | 90                                                                                                    |

|    |                                      | 7.1.2                                                                              | Timing Constraints                                   |   |   |   |          |             | 91                                                                                                    |

|    |                                      | 7.1.3                                                                              | Computation Times of MEDF Run–Time System            |   |   |   |          |             | 92                                                                                                    |

|    |                                      | 7.1.4                                                                              | System Environment and Timer Task                    |   |   |   |          |             | 96                                                                                                    |

|    |                                      | 7.1.5                                                                              | Schedulability Analysis                              |   |   |   |          |             | 98                                                                                                    |

|    | 7.2                                  | SDL S                                                                              | tyle Guidelines for Real–Time Systems                |   |   |   |          |             | 102                                                                                                   |

|    |                                      | 7.2.1                                                                              | General Rules                                        |   |   |   |          |             | 102                                                                                                   |

|    |                                      | 7.2.2                                                                              | Minimizing Number of SDL Servers                     |   |   |   |          |             | 103                                                                                                   |

|    |                                      | 7.2.3                                                                              | Minimizing Length of Blocking Transitions            |   | • | • |          | •           | 103                                                                                                   |

| 8  | Con                                  | clusior                                                                            | n and Future Work                                    |   |   |   |          |             | 105                                                                                                   |

| Bi | bliog                                | raphy                                                                              |                                                      |   |   |   |          |             | 109                                                                                                   |

|    | C                                    | ping                                                                               |                                                      |   |   |   |          |             | 100                                                                                                   |

| A  |                                      |                                                                                    | n Examples                                           |   |   |   |          |             |                                                                                                       |

| A  | App                                  | olicatio                                                                           | n Examples<br>us Attitude and Orbital Control System |   |   |   |          |             | 119                                                                                                   |

| A  | <b>App</b><br>A.1                    | olicatio<br>Olymp                                                                  | us Attitude and Orbital Control System               |   |   |   |          |             | <b>119</b><br>119                                                                                     |

| A  | <b>App</b><br>A.1                    | olicatio<br>Olymp                                                                  | us Attitude and Orbital Control System               |   |   |   |          |             | 119                                                                                                   |

| A  | <b>App</b><br>A.1                    | olicatio<br>Olymp<br>Code (<br>A.2.1                                               | us Attitude and Orbital Control System               | • |   |   | <br>     |             | <b>119</b><br>119<br>137                                                                              |

| Α  | <b>App</b><br>A.1                    | olicatio<br>Olymp<br>Code (<br>A.2.1                                               | us Attitude and Orbital Control System               |   |   |   | <br>     |             | <b>119</b><br>119<br>137<br>137                                                                       |

|    | Apr<br>A.1<br>A.2                    | Dicatio<br>Olymp<br>Code (<br>A.2.1<br>A.2.2<br>A.2.3                              | us Attitude and Orbital Control System               |   |   |   | <br>     |             | <b>119</b><br>119<br>137<br>137<br>138<br>139                                                         |

| в  | <b>Ap</b><br>A.1<br>A.2<br><b>ME</b> | Dicatio<br>Olymp<br>Code (<br>A.2.1<br>A.2.2<br>A.2.3<br>DF Im                     | us Attitude and Orbital Control System               |   |   |   | <br><br> |             | <ul> <li>119</li> <li>119</li> <li>137</li> <li>137</li> <li>138</li> <li>139</li> <li>145</li> </ul> |

|    | Арр<br>А.1<br>А.2<br>МЕ<br>В.1       | Dicatio<br>Olymp<br>Code (<br>A.2.1<br>A.2.2<br>A.2.3<br>DF Im<br>Delta 1          | us       Attitude and Orbital Control System         |   |   | • | · · ·    |             | <ul> <li>119</li> <li>119</li> <li>137</li> <li>137</li> <li>138</li> <li>139</li> <li>145</li> </ul> |

|    | <b>Ap</b><br>A.1<br>A.2<br><b>ME</b> | Dicatio<br>Olymp<br>Code (<br>A.2.1<br>A.2.2<br>A.2.3<br>DF Im<br>Delta I<br>EDF L | us Attitude and Orbital Control System               |   |   |   | · · ·    | ·<br>·<br>· | <ul> <li>119</li> <li>119</li> <li>137</li> <li>137</li> <li>138</li> <li>139</li> <li>145</li> </ul> |

### CONTENTS

# List of Acronyms and Variables

# Acronyms

| AOCS                   | Attitude and Orbital Control System              | 7  |

|------------------------|--------------------------------------------------|----|

| ATM                    | Activity Thread Model                            | 11 |

| $\mathbf{AT}$          | Activity Thread                                  | 39 |

| BCET                   | Best Case Execution Time                         | 5  |

| CASE                   | Computer Aided System Engineering                | 3  |

| CIOP                   | Configurable Input/Output Processor              | 5  |

| $\mathbf{CSP}$         | Communicating Sequential Processes               | 10 |

| DCP                    | Deadline Ceiling Protocol                        | 53 |

| DIP                    | Deadline Inheritance Protocol                    | 55 |

| $\mathbf{EDF}$         | Earliest Deadline First                          | 4  |

| $\mathbf{EDM}$         | Event Dependency Matrix                          | 29 |

| $\mathbf{EFSM}$        | Extended FSM                                     | 19 |

| $\mathbf{ES}$          | Event Stream                                     | 28 |

| FCFS                   | First–Come First–Serve                           | 51 |

| FIFO                   | First–In First–Out                               | 15 |

| $\mathbf{FSM}$         | Finite State Machine                             | 19 |

| HOOD                   | Hierarchical Object Oriented Design              | 14 |

| HOQ                    | Hand–Over Qeue                                   | 67 |

| HPU                    | High Performance Unit                            | 5  |

| $\mathbf{H}\mathbf{W}$ | Hardware                                         | 6  |

| $\mathbf{IQ}$          | Input Qeue                                       | 67 |

| ISR                    | Interrupt Service Routine                        | 25 |

| ITU                    | International Telecommunication Union            | 18 |

| $\mathbf{LLF}$         | Least Laxity First                               | 13 |

| MEDF                   | Message based Earliest Deadline First Scheduling | 2  |

| $\mathbf{MSC}$         | Message Sequence Charts                          | 10 |

| OMG                    | Object Modeling Group                            | 17 |

| OMT                    | Object Modeling Technique                        | 15 |

| OOD                    | Object Oriented Design                           | 1  |

| OSI                    | Open Systems Interconnection                     | 11 |

| PAD                    | Process Activity Description                     | 35 |

| PIP                        | Priority Inheritance Protocol                                    | 55 |

|----------------------------|------------------------------------------------------------------|----|

| PI                         | Priority Inversion                                               | 15 |

| PMSC                       | Performance Message Sequence Charts                              | 10 |

| $\mathbf{PU}$              | Processing Unit                                                  | 5  |

| $\mathbf{QSDL}$            | Queuing SDL                                                      | 15 |

| REAR                       | Rapid Prototyping Environment for Advanced Real–Time Systems     | 5  |

| $\mathbf{RMA}$             | Rate Monotonic Analysis                                          | 4  |

| ROOM                       | Real–Time Object–Oriented Modeling                               | 10 |

| RTAM                       | Real–Time Analysis Model                                         | 6  |

| RTEMS                      | Real–Time Executive for Multiprocessor Systems                   | 56 |

| RTOS                       | Real–Time Operating System                                       | 14 |

| $\mathbf{RTU}$             | Real–Time Unit                                                   | 5  |

| SA/SD                      | Structured Analysis/Structured Design                            | 1  |

| $\mathrm{SDL}/\mathrm{GR}$ | SDL Graphical Representation                                     | 18 |

| $\mathrm{SDL/PR}$          | SDL Prose Representation                                         | 18 |

| $\mathbf{SDL}$             | Specification and Description Language                           | 2  |

| $\mathbf{SDT}$             | Telelogic's SDL Design Tool                                      | 3  |

| $\mathbf{SM}$              | Server Model                                                     | 11 |

| $\mathbf{SQ}$              | Server Qeue                                                      | 67 |

| $\mathbf{SW}$              | Software                                                         | 6  |

| $\mathbf{TPG}$             | Task Precedence Graph                                            | 76 |

| $\mathbf{TPS}$             | Task Precedence System                                           | 4  |

| $\mathbf{UML}$             | Unified Modeling Language                                        | 10 |

| VHDL                       | Very high speed integrated circuit Hardware Description Language | 6  |

| WCET                       | Worst Case Execution Time                                        | 5  |

# Variables

| computation function, maximum computation time in interval $I$ |

|----------------------------------------------------------------|

| absolute deadline $D_i$ of task $i$                            |

| absolute deadline $D$ of task $i$                              |

| event function, maximum number of events per interval $I$      |

| jth instance of event $E$ of type $m$                          |

| overall computation function of ISRs in interval $I$           |

| worst case execution time                                      |

| best case execution time                                       |

| relative deadline $d$ of task $i$                              |

| relative end–to–end deadline for event $E_m$                   |

| time of occurrence of event $E$ of type $m$                    |

| completion time of task $i$                                    |

| release time of task $i$                                       |

| start time $s_i$ of task $i$                                   |

| start of computation of task $i$                               |

|                                                                |

х

# List of Figures

| $1.1 \\ 1.2$ | Core Phases and Premises in a SDL based Design Methodology REAR Design Framework | $\frac{2}{6}$ |

|--------------|----------------------------------------------------------------------------------|---------------|

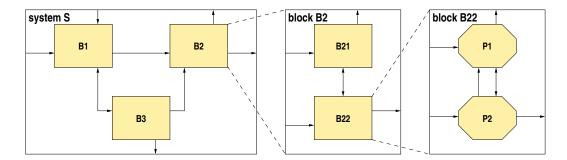

| 3.1          | SDL System Syntax (graphical representation)                                     | 19            |

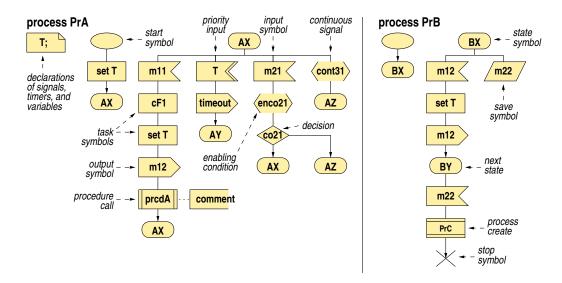

| 3.2          | SDL Process Syntax (graphical representation)                                    | 20            |

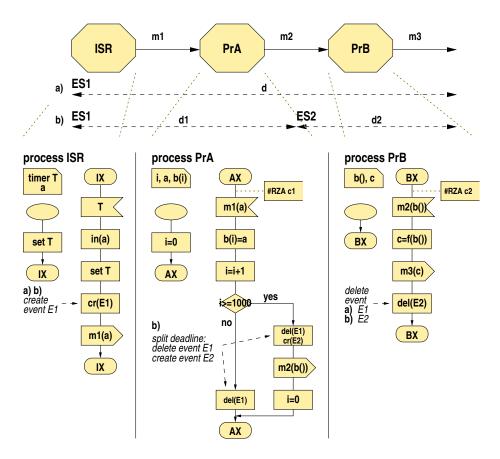

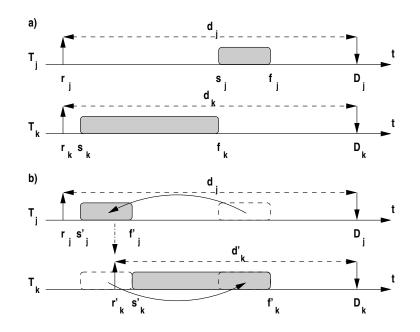

| 3.3          | a) End–to–end Deadline vs. b) Triggering Less Stringent Processing               | 24            |

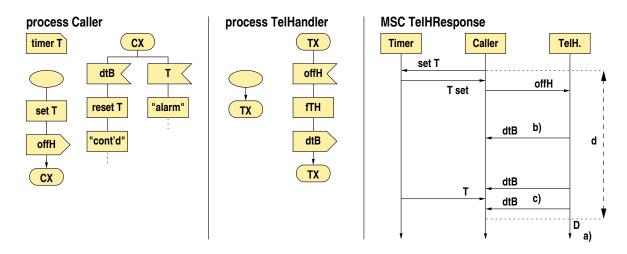

| 3.4          | Timeout with MEDF Timer                                                          | 26            |

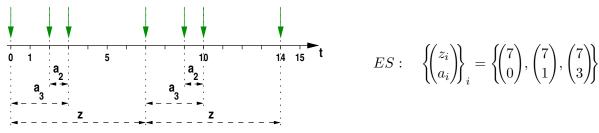

| 3.5          | Event Stream Example                                                             | 29            |

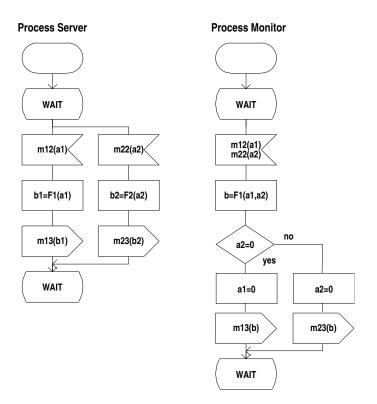

| 4.1          | a) Synchronizing Mutual Exclusion and b) Monitoring Shared Function              | 34            |

| 4.2          | a) Simple SDL System and b) its Tight Integration with SDT's C–Advanced          | 36            |

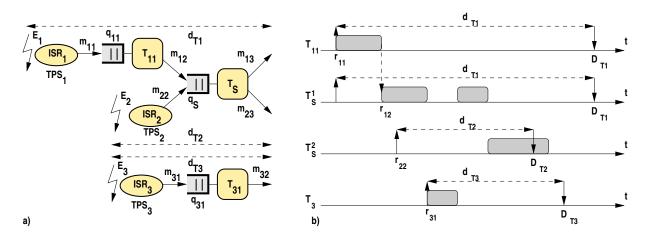

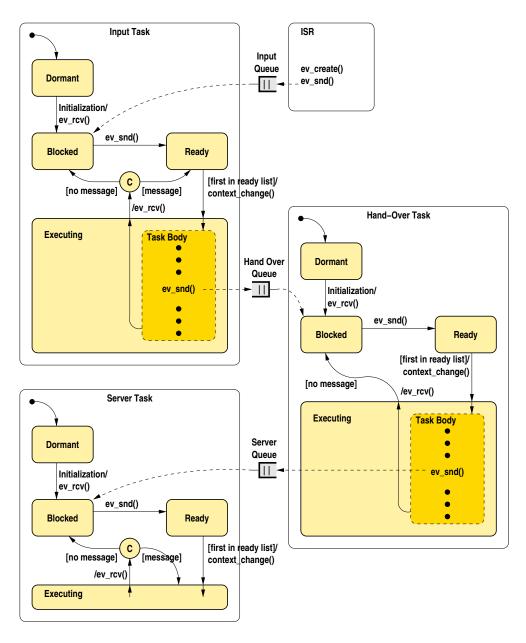

| 4.3          | a) SDL System with Two Timing Constraints and b) its Activity Threads .          | 39            |

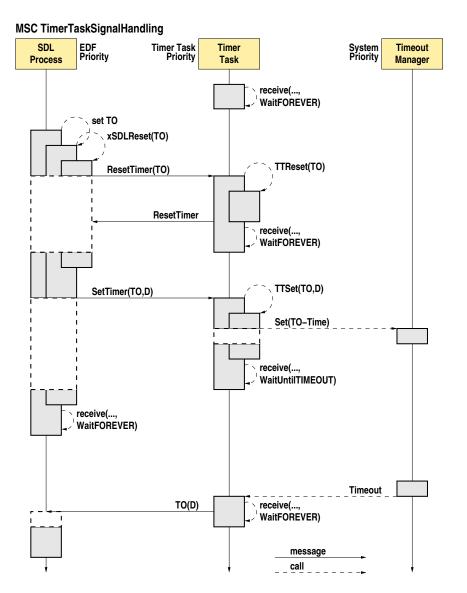

| 4.4          | Timer Task: Signal and Timeout Handling                                          | 41            |

| 4.5          | Timer Task with Timer Deadline Management                                        | 43            |

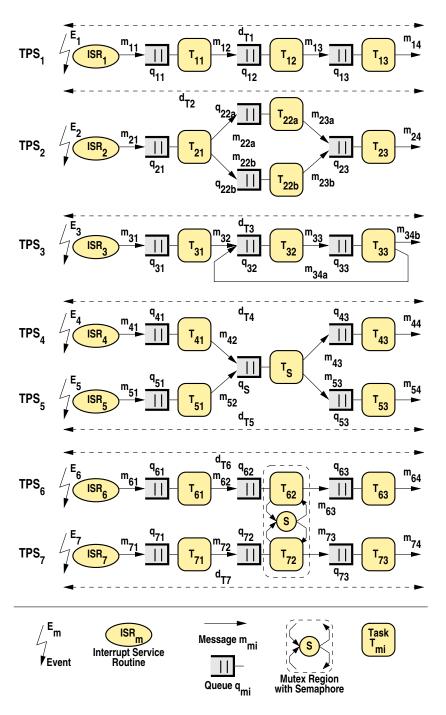

| 5.1          | Examples of Task Precedence Systems                                              | 48            |

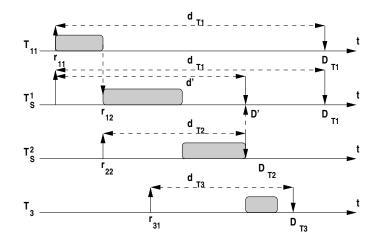

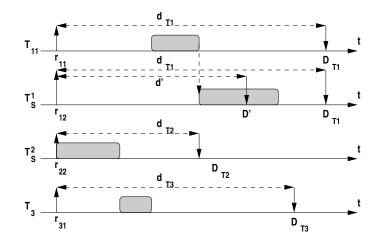

| 5.2          | Feasible Schedule without a) and with b) Precedence Constraint                   | 49            |

| 5.3          | a) Server Task and b) Priority Inversion                                         | 52            |

| 5.4          | Priority Inversion Avoidance                                                     | 53            |

| 5.5          | Violation of Ceiling Deadline $D'$ without Priority Inversion                    | 54            |

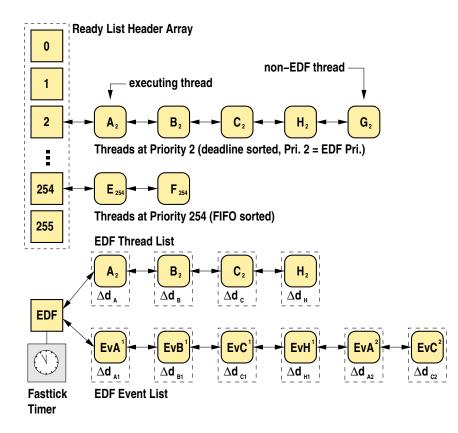

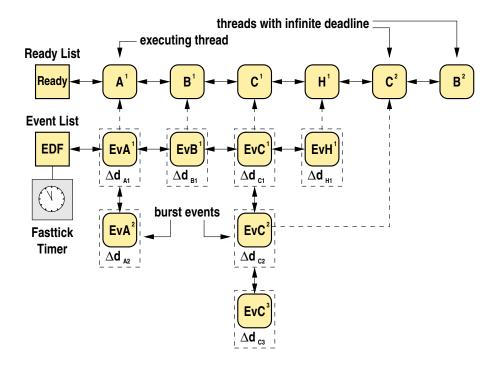

| 5.6          | RTEMS Priorities, Ready List, EDF Thread List and EDF Event List                 | 56            |

| 5.7          | Priority Based Thread Queue                                                      | 60            |

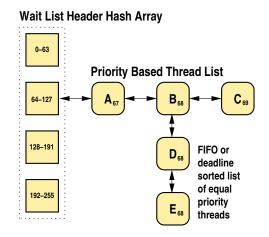

| 5.8          | Transitive Deadline Inheritance with a) Nested Semaphores and b) Servers         | 62            |

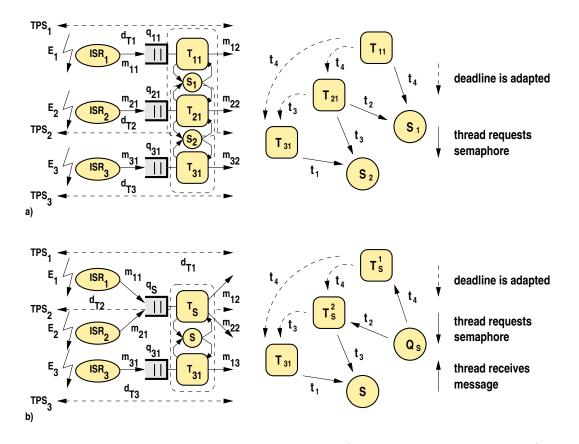

| 5.9          | Server Model Task States and Structure of Task Body                              | 66            |

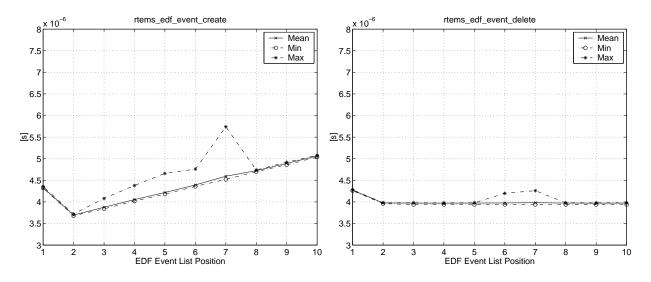

| 5.10         | Timing: a) EDF Event Create and b) EDF Event Delete                              | 67            |

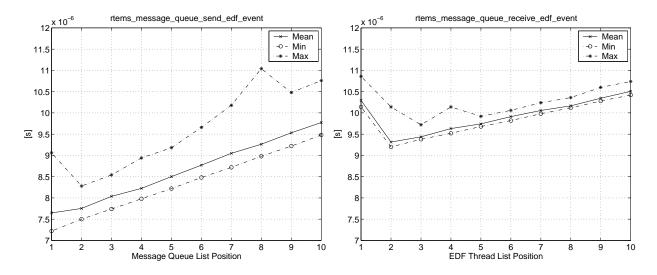

| 5.11         | Timing: a) Send (No waiting task) and b) Receive (Message available)             | 69            |

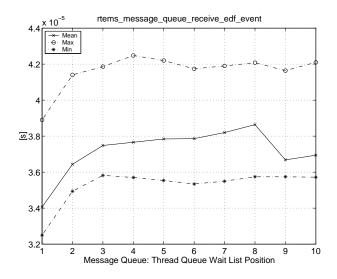

| 5.12         | Timing: EDF Event Receive (Caller blocks)                                        | 70            |

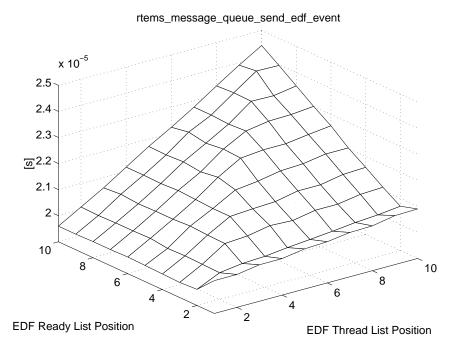

| 5.13         | Timing: EDF Event Send (Task readied)                                            | 71            |

| 5.14         | List Structures and References for Optimized Server Model Scheduler              | 72            |

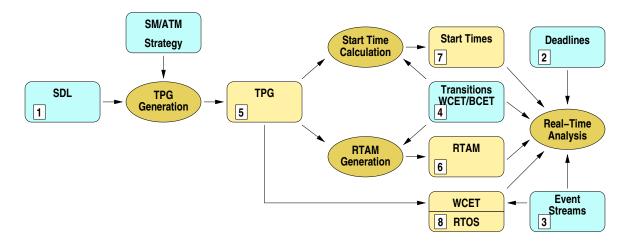

| 6.1          | Information Flow and Dependencies of Real–Time Analysis                          | 76            |

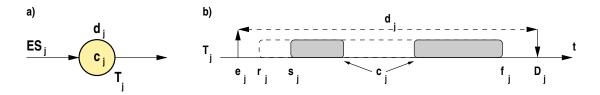

| 6.2          | Graphical Representation of a Task Node [Gre93a] and Analysis Parameters         | 77            |

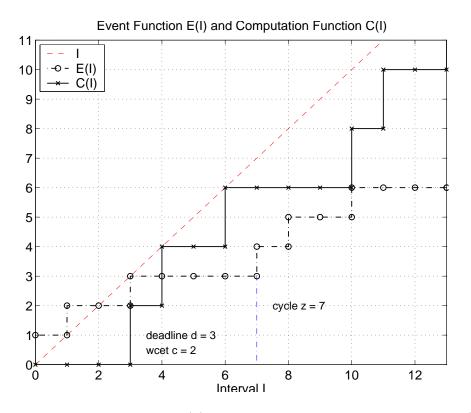

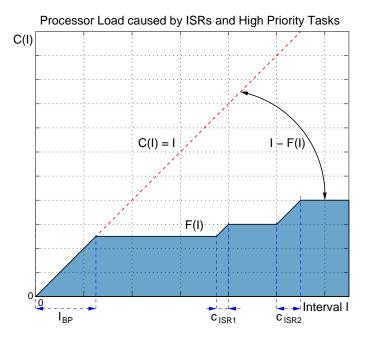

| 6.3          | Event Function $E(I)$ and Requested Computation Time $C(I)$                      | 79            |

| 6.4          | Busy Periods due to ISRs and Supplementary Tasks                                 | 81            |

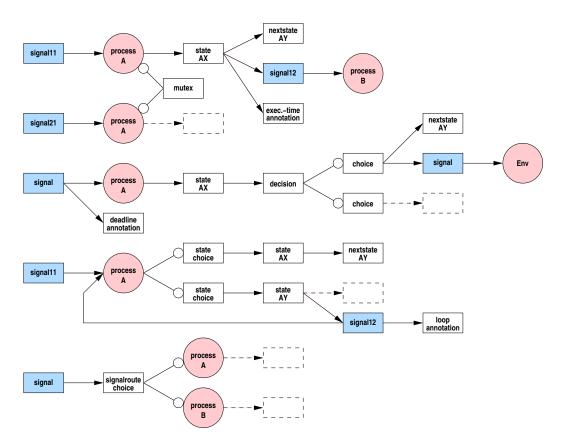

| 6.5        | Syntax of Task Precedence Graph and its Annotations                      | 82                |

|------------|--------------------------------------------------------------------------|-------------------|

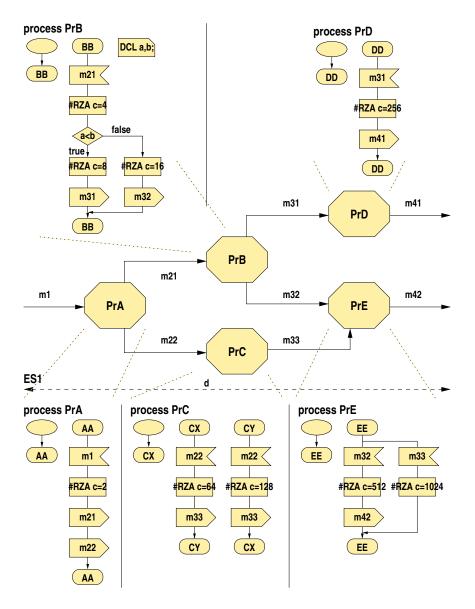

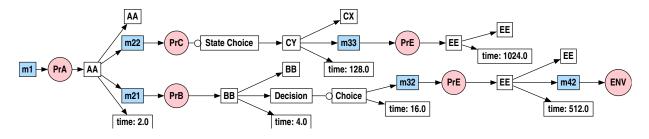

| 6.6        | TPG Synthesis Example SDL System                                         | 83                |

| 6.7        | Task Precedence Graph Including All Transition Alternatives              | 84                |

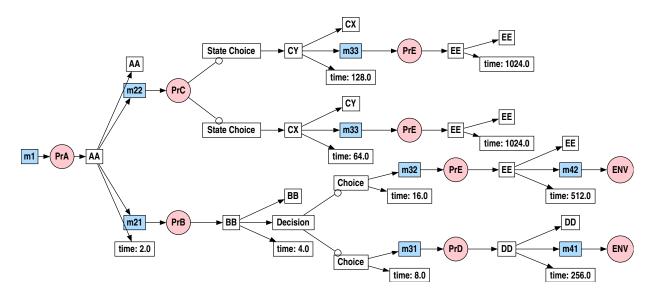

| 6.8        | Worst Case Task Precedence Graph                                         | 85                |

| 6.9        | Recursive TPG WCET Calculation (simplified)                              | 86                |

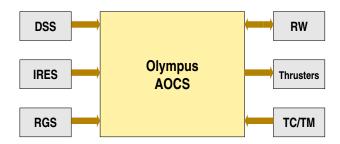

| 7.1        | Olympus AOCS Sensors and Actuators                                       | 90                |

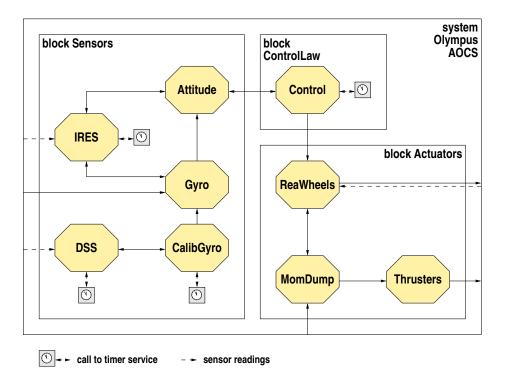

| 7.2        | AOCS SDL System Survey                                                   | 91                |

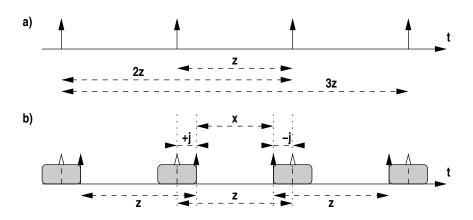

| 7.3        | Cyclic Event a) without and b) with Jitter                               | 93                |

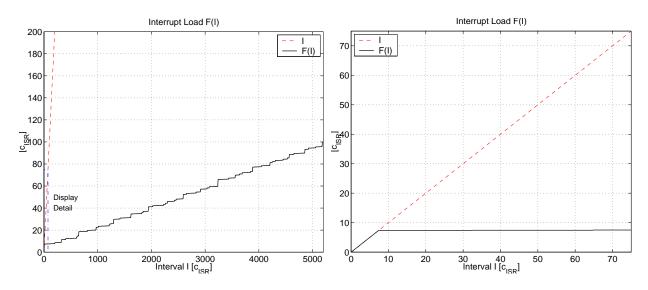

| 7.4        | a) AOCS Interrupt Load and b) Busy Period at Interval 0                  | 97                |

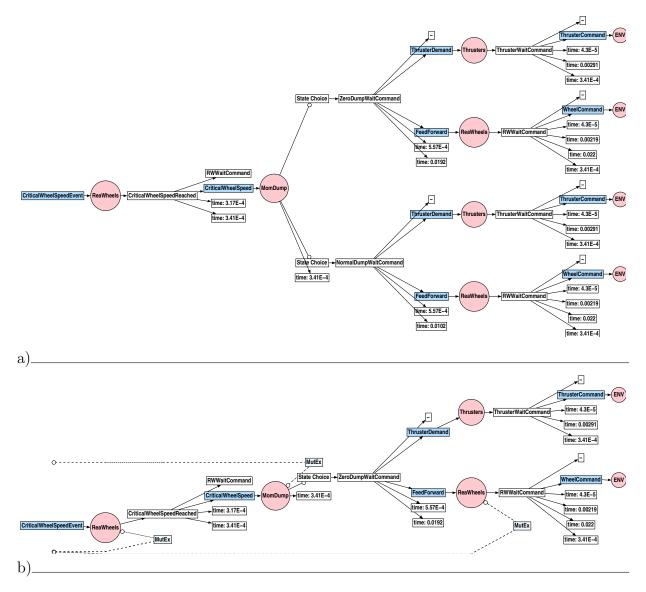

| 7.5        | a) CWS Task Precedence System and b) Real–Time Analysis Model            | 98                |

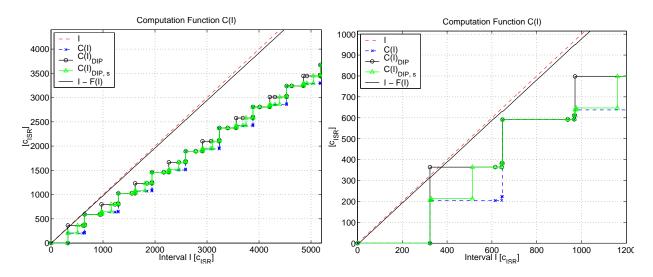

| 7.6        | a) AOCS Overall Computation Function, b) Detailed View in Interval 0     | 101               |

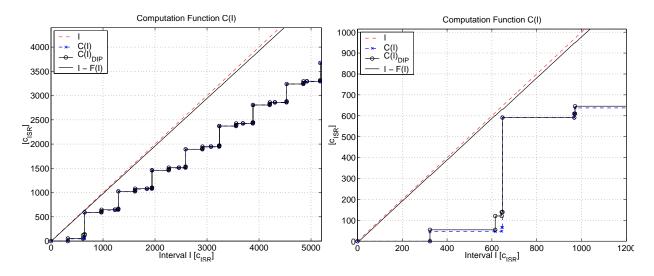

| 7.7        | a) AOCS $C(I)$ with $d_{CWS} = 200  ms$ , b) Detailed View in Interval 0 | 102               |

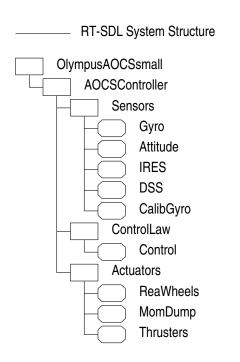

| A.1        | Olympus AOCS System Structure                                            | 120               |

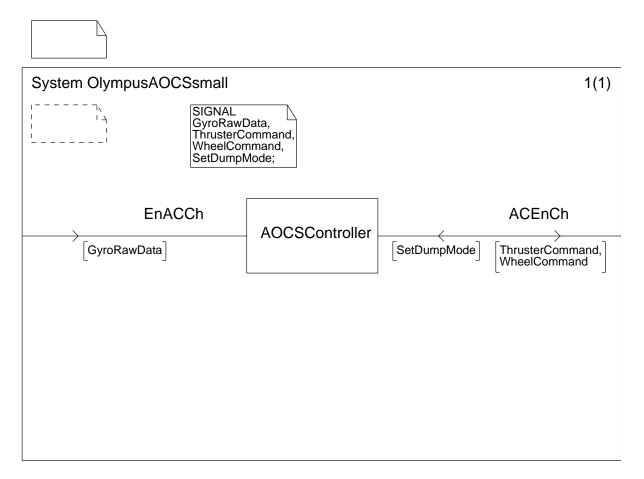

| A.2        | Olympus AOCS SDL System                                                  | 120               |

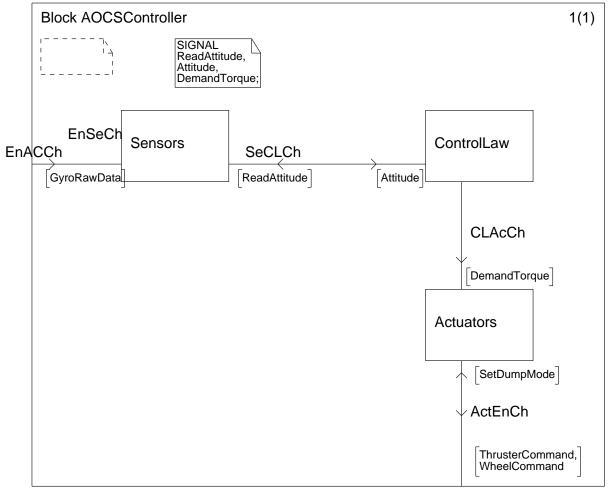

| A.3        | Block AOCSController                                                     | 121               |

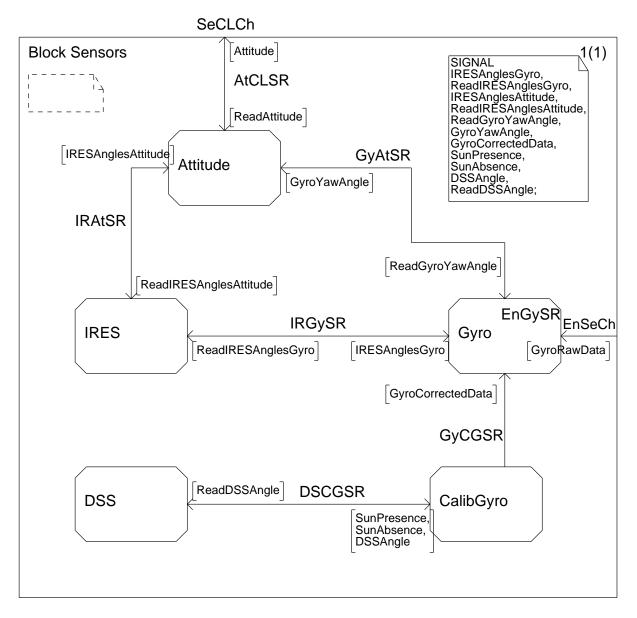

| A.3<br>A.4 | Block Sensors                                                            | 122               |

| A.4<br>A.5 |                                                                          | 123               |

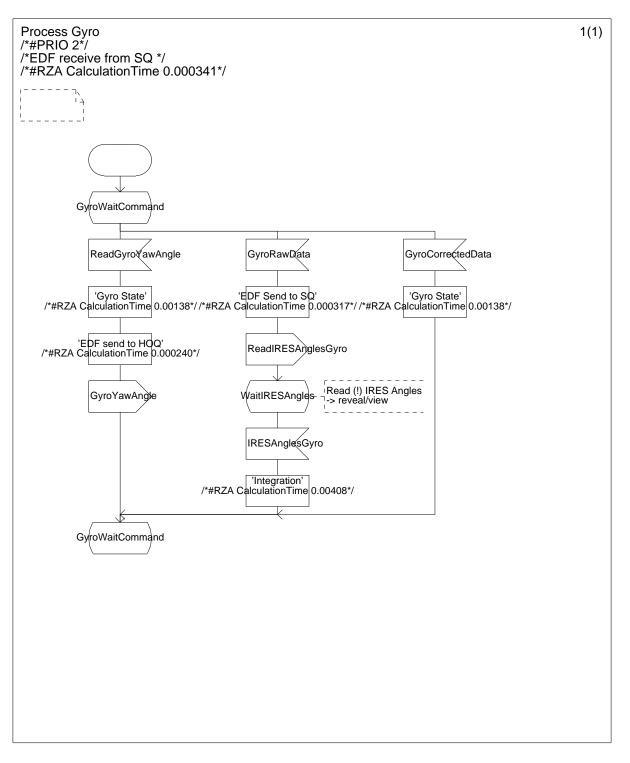

| A.5<br>A.6 | Process Gyro                                                             | $\frac{124}{125}$ |

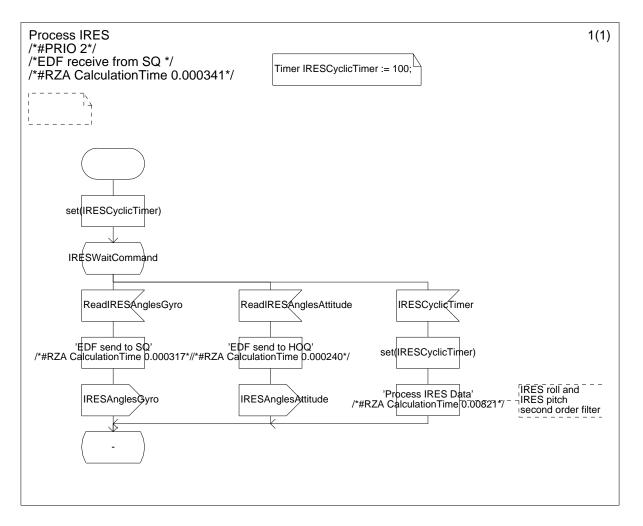

| A.0<br>A.7 | Process IRES                                                             |                   |

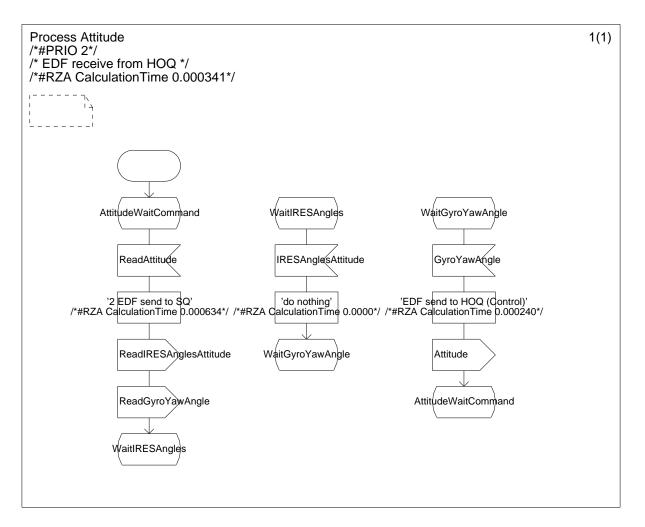

|            |                                                                          | 126               |

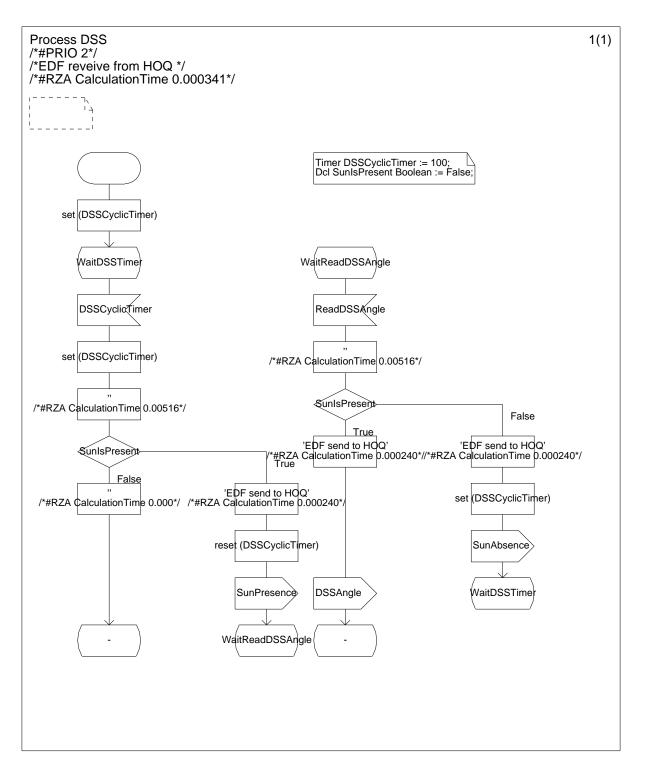

| A.8        | Process DSS                                                              | 127               |

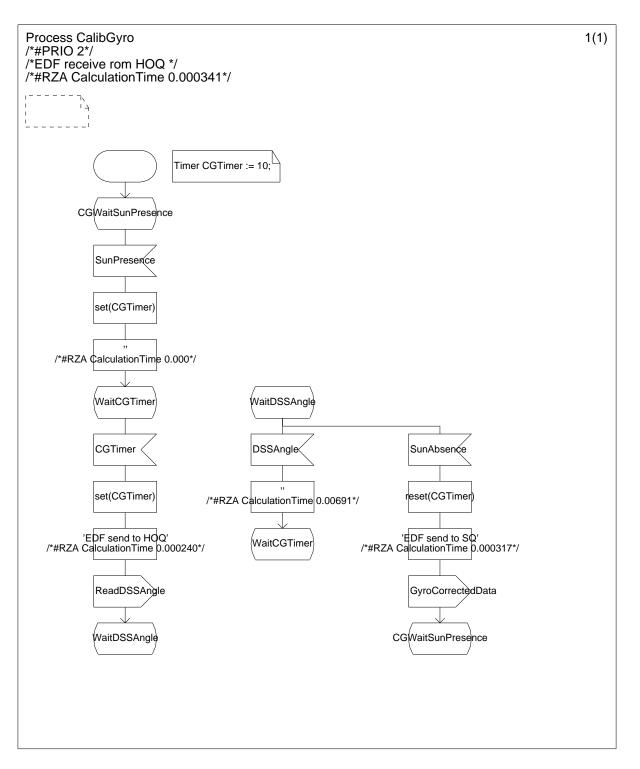

| A.9        | Process CalibrateGyro                                                    | 128               |

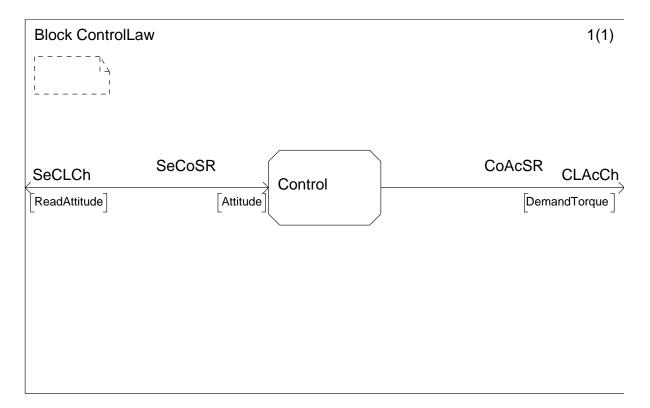

|            | Block ControlLaw                                                         | 129               |

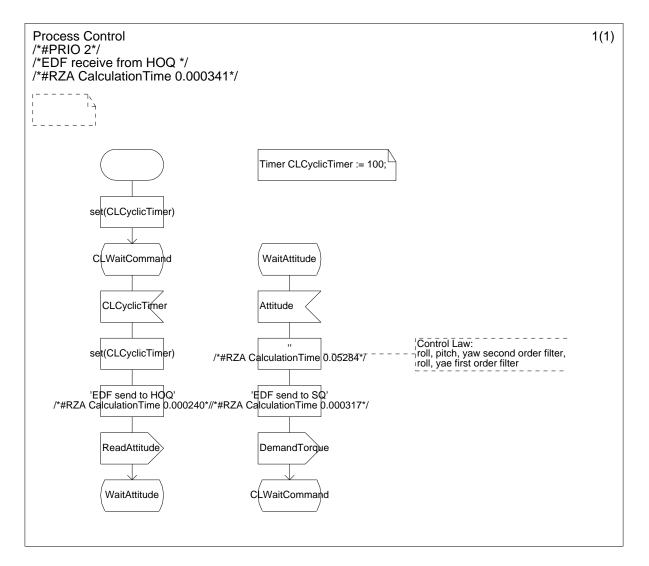

|            | Process Control                                                          | 130               |

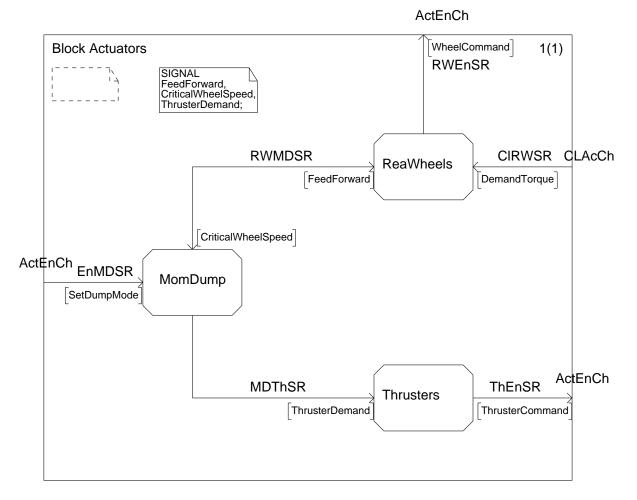

|            | Block Actuators                                                          | 131               |

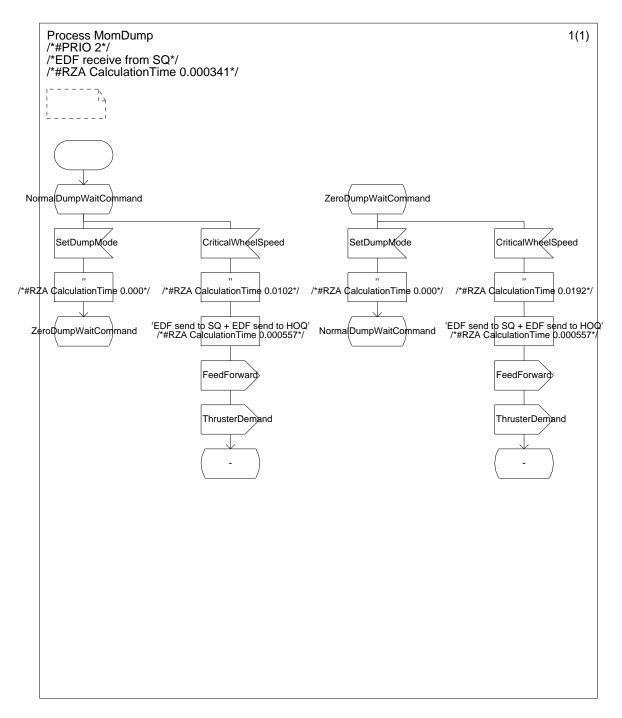

|            | Process MomentumDump                                                     | 132               |

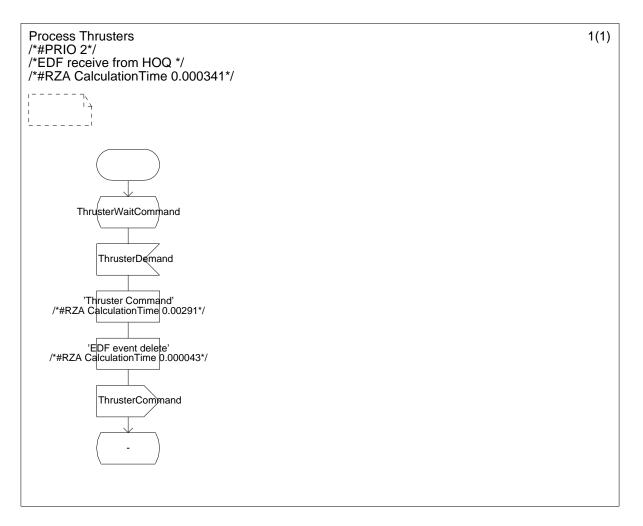

|            | Process ReactionWheels                                                   | 133               |

|            | Process Thrusters                                                        | 134               |

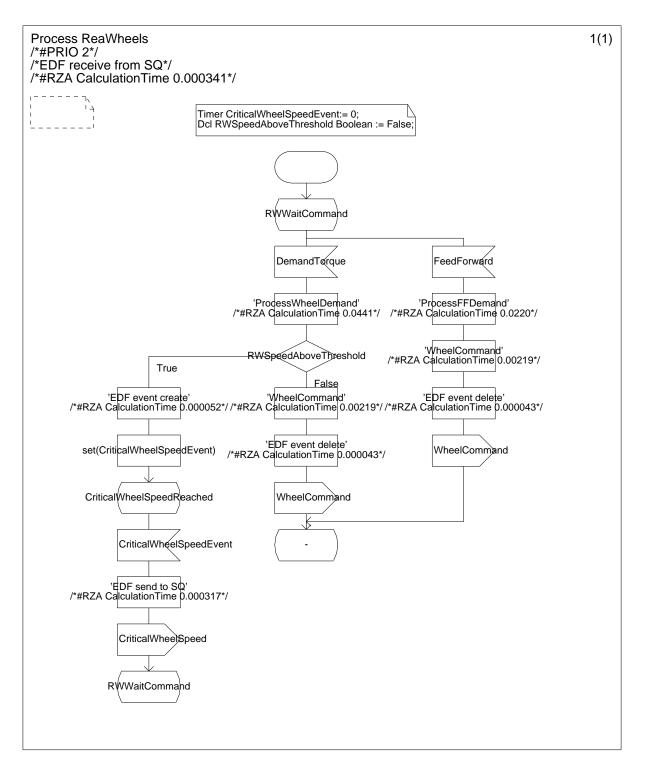

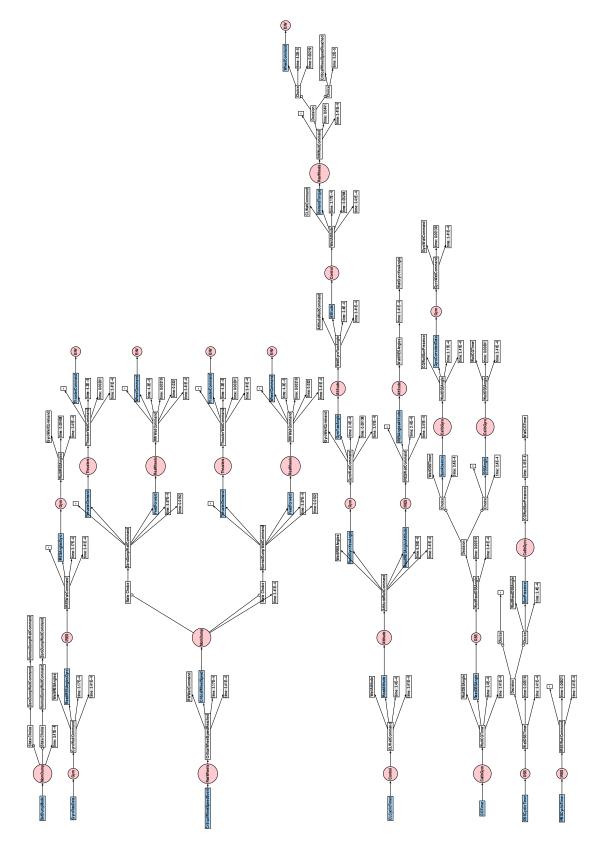

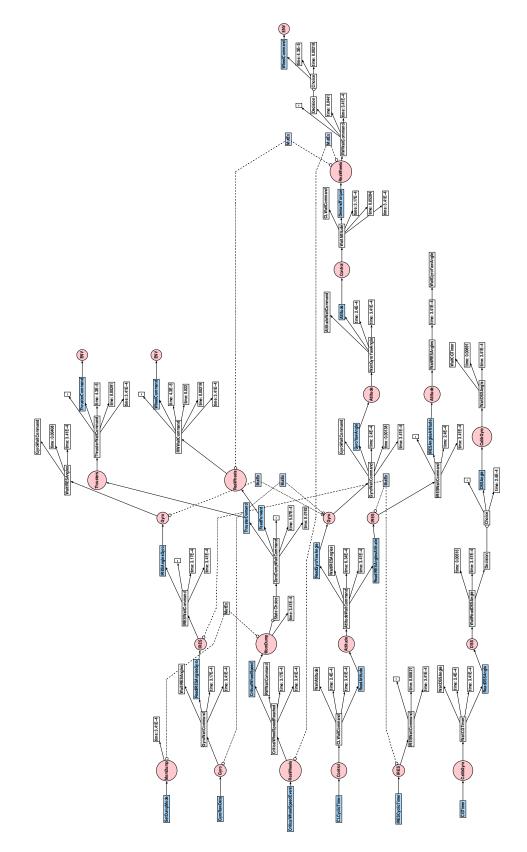

|            | Olympus AOCS Task Precedence Graph                                       | 135               |

|            | Olympus AOCS Real–Time Analysis Model                                    | 136               |

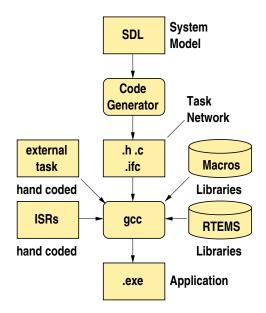

|            | SDT C-Advanced System Build Process                                      | 137               |

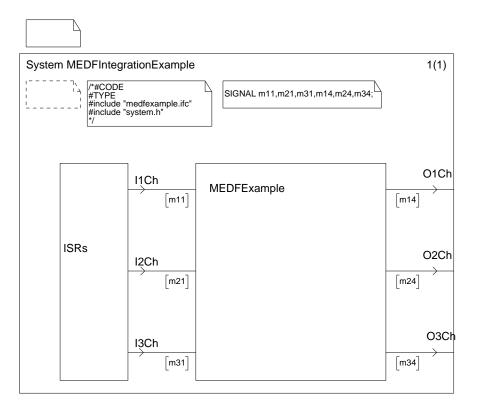

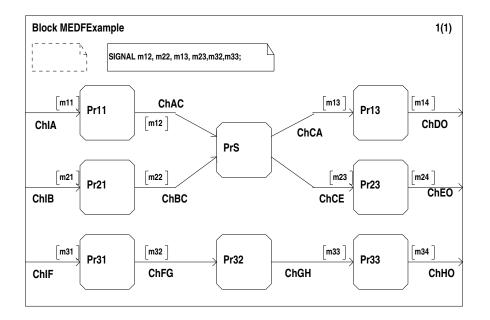

|            | Application Example: SDL System                                          | 139               |

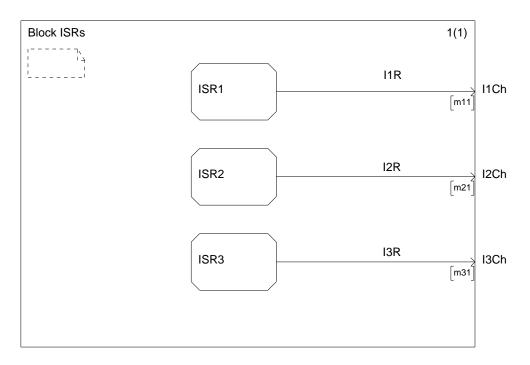

|            | Application Example: ISR Block                                           | 140               |

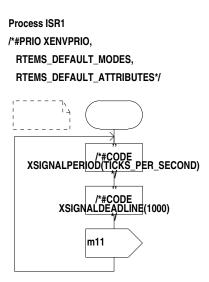

|            | Application Example: Interrupt Service Routine                           | 141               |

|            | 2 Application Example: SDL Process Network                               | 142               |

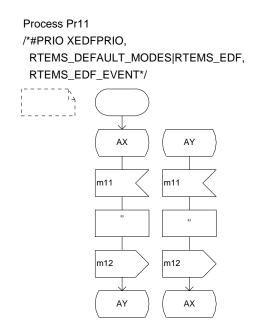

|            | Application Example: Process 11                                          | 142               |

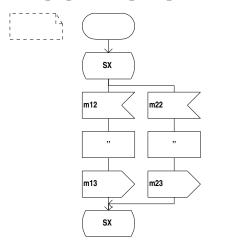

|            | Application Example: Server Process S                                    | 143               |

|            | Generated Task System                                                    | 143               |

| A.26       | Application Example: Organizer View                                      | 144               |

| B.1        | Deadline Management                                                      | 145               |

| B.2        | Inserting into the Ready List                                            | 146               |

|            |                                                                          |                   |

### LIST OF FIGURES

| B.3 | Insertion with EDF List Algorithm                                 | 147 |

|-----|-------------------------------------------------------------------|-----|

| B.4 | Deadline Supervision with Clock and Fasttick Support (simplified) | 148 |

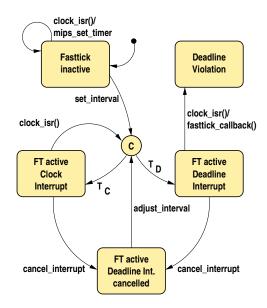

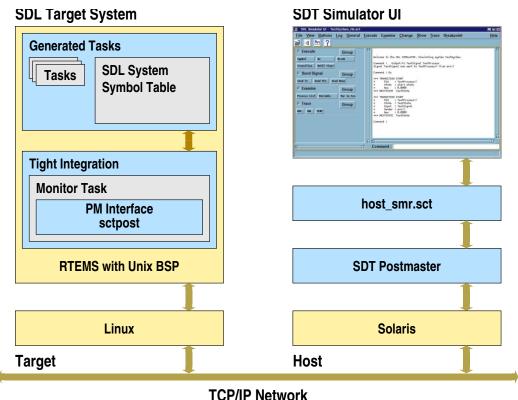

| B.5 | MEDF Simulation based on SDT Tool Suit                            | 149 |

### LIST OF FIGURES

# List of Tables

| 5.1 | Task and Environment Parameters                                                                 | 47  |

|-----|-------------------------------------------------------------------------------------------------|-----|

| 5.2 | EDF event send and EDF event receive list dependencies and processing effort                    | 68  |

| 5.3 | EDF event send and EDF event receive processing sequences with optimized server model scheduler | 73  |

| 7.1 | AOCS Event Streams and Deadlines                                                                | 92  |

| 7.2 | Execution times of RTEMS message queue directives                                               | 94  |

| 7.3 | Execution times of MEDF directives for a AOCS Server Model implementation                       | 95  |

| 7.4 | Processing Times of AOCS Task Precedence Systems and Server Processes                           | 99  |

| A.1 | Annotations to the SDL Model                                                                    | 119 |

| A.2 | MEDF directives, object modes and attributes                                                    | 138 |

LIST OF TABLES

xvi

# Chapter 1 Introduction

In July 1997 the Mars probe *Pathfinder* survived its rubber ball landing on the Martian surface due to its airbag protection. After successful deployment of the *Sojourner* rover, it resumed its mission with gathering environmental data from this distant neighbor planet. Caused by a priority inversion between a sensor, the communication, and the system management task, the spacecraft experienced sporadically total system resets repeatedly leading to a loss of measurement data. Press releases stated the "computer was trying to do too many things at once", but a detailed analysis of the software system showed a watchdog timer had detected an avoidable *deadline* violation for the communication task.

The timing characteristics of this *real-time system* were considered as *soft* during this phase of the mission. A similar failure during the more mission critical phase of approaching the Martian surface would have probably led to a loss of the space vehicle. In this case, the timing constraints and therefore the real-time software system would have been classified as *hard* and a system reset of course would not have been a viable recovery strategy for a deadline miss. Although functionally correct, and although single components had been designed with efficiency in mind, inter-dependencies (resource sharing) of the concurrent tasks had led to a timely incorrectness.

As can be seen, complexity of the whole application makes an analysis of timing requirements difficult. Neither black box simulation, nor performance analysis with state– of–the–art computation models like queuing theory or functional prototyping would had revealed the additional blocking time caused by priority inversion for the communication task in all probability. On the other hand, current practice in schedulability analysis theory is based on very restrictive task models and could have been applied only if the real–time software has been designed accordingly.

Software engineering methodologies like structured analysis/structured design (SA/SD) or object oriented design (OOD) win increasing recognition even in the area of dedicated systems. There exist sophisticated tool support for a multitude of design languages, because it is now generally accepted that software design automation will help shortening development times and thus development costs. But when timing specifications are not met, structural modifications may become necessary. In this case or when design changes occur, e.g. through additional required functionality, a rescheduling of all components and

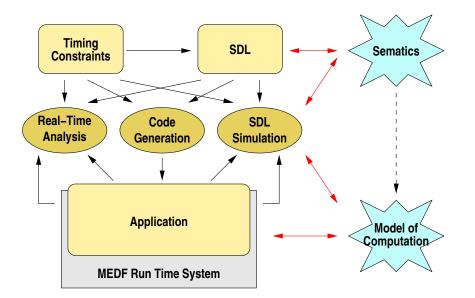

Figure 1.1: Core Phases and Premises in a SDL based Design Methodology

consequently a reanalysis of the temporal properties has to be done. This means, for realtime systems the schedulability analysis should have to be an automated design step as well.

# 1.1 Contribution

This work introduces a methodology framework based on the "Specification and Description Language" (SDL) aiming on the integration of a timeliness proof into the automated design process for hard real-time systems. For that purpose, SDL's semantics is pinpointed to a predictable model of computation allowing on the one hand to automatically derive analyzable implementations. On the other hand the system specification can now be mapped to a real-time analysis task graph that mirrors the structural inter-relationships between the resource sharing components and is the basis for the final schedulability analysis step. Message based earliest deadline first scheduling (MEDF) serves as a platform for this design process. Therefore MEDF's predictability will be shown and algorithms to evaluate timing properties of MEDF based software systems will be provided.

# **1.2** Prerequisites and Restrictions

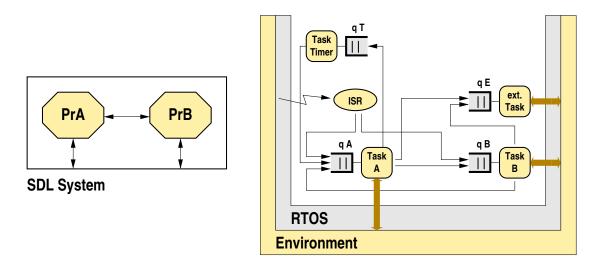

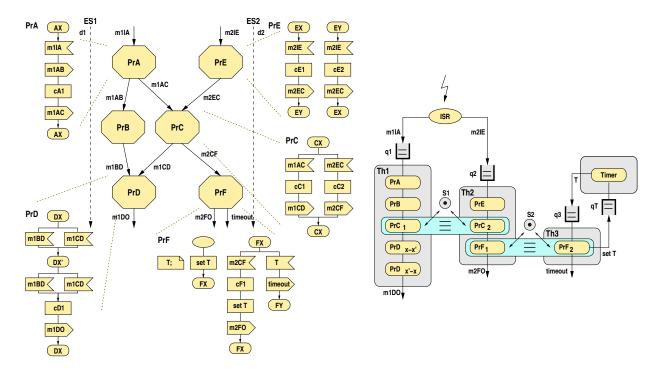

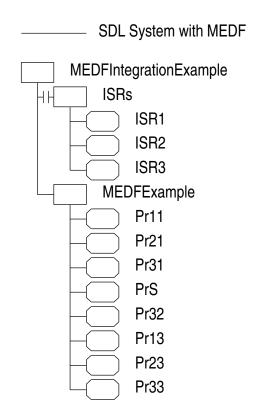

A coarse survey of a design methodology for hard real-time systems based on SDL [Kol98] is given in Fig. 1.1. In the follow section, motives for choosing SDL as the starting point for this framework are outlined. Based on this, restrictions and requirements for automated code generation and the applied scheduling policy are outlined.

#### 1.2. PREREQUISITES AND RESTRICTIONS

#### System Specification

Design automation in general needs a formal system description to capture the functional and non-functional requirements. Beyond this, automated schedulability analysis requires a formal semantics which suits to the applied analysis task model. Due to the concurrent nature of the embedding environment, concurrency too is used as a means to structure the design of a real-time application. Therefore process models are the basis of most state-of-the-art specification or real-time programming languages. The *Specification and Description Language* SDL as a formal description technique originally developed and standardized [ITU94a] for telecommunication systems is more generally suitable for control flow dominated systems. SDL's message oriented, asynchronous communication and the state-machine like behaviour of its processes matches well the event driven nature of many real-time applications.

Like most specification languages SDL too implies some abstractions and nondeterminisms in its semantics due to its intended application in the early phases of the design cycle. This fact is tolerable or even useful during the specification phase, but of course not acceptable in the implementation, respectively during run-time. For this reason, the execution model has to be pinpointed to the chosen scheduling policy to enforce conformance between the language semantics, the model of computation during functional simulation, the schedulability analysis task model, and the implementation strategy. Added to that, there is a need to restrict the usage of some SDL language constructs to avoid unpredictability.

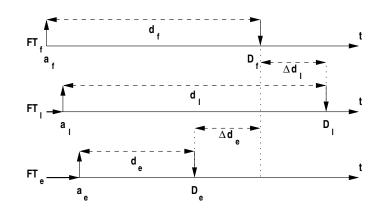

Unlike general purpose systems, the dedicated functionality of *embedded systems* imposes additional constraints like maximal memory usage or maximal power consumption on the design. Therefore the functional specification has to be complemented with a description of non-functional requirements. This work focuses on the analysis of timing properties of hard real-time systems. Thus, the non-functional specification must include a worst case description of the temporal behaviour of the *embedding* system and on the other hand, must specify the *deadlines* to be reached by the final system realization.<sup>1</sup> In case of integrated control systems, deadlines are imposed by the system's environment, i.e. the embedding system that has to be controlled by the application. Consequently, deadlines are understood as attributes of the stimulating events, i.e. they are *end-to-end* constraints. A triggering event has to be responded within a specified deadline interval. The event's characteristics are added as annotations to the functional description.

#### **Code Generation**

CASE tools like Telelogic's SDL Design Tool SDT support the mapping of a functional specification to an executable prototype. Unfortunately, the semantical gap between the assumed "each SDL process runs independently on its own processor" behaviour in the specification and the sequential computation on a single–processor target can be the source

<sup>&</sup>lt;sup>1</sup>As will be shown later (cf. Sec. 3.2.2), SDL's timer mechanism is inappropriate for timing constraint specification.

for inefficiencies in automatically generated implementations preserving the process model. This leads to the effect that a system designer will manipulate the generated target code instead of the system model to achieve the required performance. Thus, system specification and implementation diverge and become inconsistent.

This observation underlines the importance of an efficient decomposition of the system model. This is especially necessary when the application is control flow dominated, i.e. processing time for communication and synchronization of application threads is in the order of magnitude of the application's computation time. Maintainability is gained, if the specification and only the specification is the place for changes. But instead of average or best case throughput and latency, code generation strategies have to concentrate on guaranteeable, worst case performance and *predictability*. Since the model of computation of the system specification and the processing order of the final implementation must correspond exactly to enable a specification based real-time analysis, code generation strategies must also preserve the semantics of the specification language.

#### Scheduling Policy and Run–Time System

Earliest deadline first (EDF) scheduling is often regarded as dangerous, because under overload, it may show awkward behaviour. However, in a hard real-time system's life cycle an overload situation must not occur, because a deadline miss may lead to a loss of money or even a loss of lives. This fact requires an a-priori proof that all timelines will be met even in worst case situations, e.g. when burst events occur simultaneously<sup>2</sup> and all tasks in a system exhaust their worst case processing time budgets.

EDF has been shown to be an optimal scheduling strategy for single processor systems [LL73], i.e. if you can find a schedule with an alternative policy, you will find a feasible solution with EDF too. Furthermore, an existing deadline specification needs not to be transformed into a process priority assignment, like it has to be done with e.g. rate monotonic analysis (RMA, [KRP+93]). Therefore it is easier to integrate into an automated design process. Finally, time–driven schedules for sporadic task activations result in unsatisfactory achievable processor utilization. This fact and their inflexible design speaks for a dynamic management for *event–driven* real–time systems.

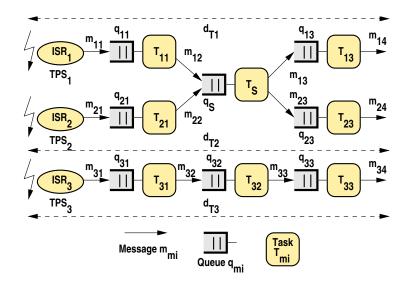

Complex process networks in the final realization may emerge through the use of a process based specification language. As a consequence, more than one task will be involved in the processing of a stimulating event and on the other hand one task may serve more than one type of event (with different required response times). Thus, a deadline will span a whole *task precedence system* (TPS). Static partitioning of deadlines and that followed an assignment of sub-deadlines to processes would lead to a loss of laxity, i.e. an over-specification of the system. Consequently, there is a need to dynamically transport a deadline to the succeeding tasks within a TPS. The resulting scheduling scheme is *scheduling with message deadlines* (MEDF).

It will be shown that applying MEDF to a network of communicating processes will lead

<sup>&</sup>lt;sup>2</sup>called *critical instant*

to an EDF processing sequence of these processes. Thus, feasibility analysis algorithms like [Gre93b, Gre93a], [SSRB98], or [Jef92] may be applied to prove the required timeliness.<sup>3</sup> Unfortunately, there exists no known MEDF implementation in state–of–the–art real–time operating systems. Therefore, necessary run–time system support has to be provided.

Schedulability analysis requires all best (BCET) and worst (WCET) case execution times to be known in advance. There exist different approaches in research, based on measurement or code evaluation, to derive processing time variations caused by e.g. different program paths. Preemption delays caused by cache flushes and pipeline stalls may complicate this problem. WCET/BCET determination is out of scope for this work. Thus, processing times are assumed to be known. For a detailed problem description refer to [PF99, Pet02].

## **1.3** This work's background: Rapid Prototyping

*Rapid prototyping* has been proposed as a methodology to find design errors and flaws in the embedded system's requirements at a very early stage of its development cycle. A re–usable, configurable and scalable target architecture serves as a platform to execute a system's specification in the real environment in form of a working prototype. An automated design process is needed to translate the formal system description into an executable in order to rapidly derive such a prototype. The rapid prototyping environment REAR<sup>4</sup> [PMK<sup>+</sup>99, PMK<sup>+</sup>00] realizes such a design framework and includes the design methodology as introduced in this work.

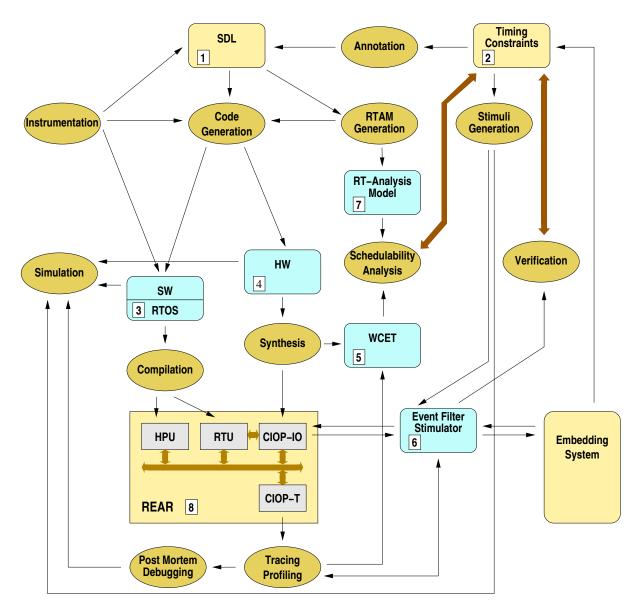

REAR's target architecture (8 in Fig. 1.2, [FKMF97]) consists of an heterogeneous multi-processor system complemented with additional field programmable gate arrays, tightly coupled with the microprocessor based units. Its processing nodes (High Performance Unit (HPU), Real-Time Unit (RTU), and Configurable I/O Processor (CIOP)) are specialized according to the "task classification model" [FFKM97], where each type of real-time task corresponds to a best suited type of processing unit (PU), in terms of performance and deterministic execution times. Therefore, a straight-forward allocation of the application tasks to the single PUs can be derived from a task grading according to both, computing complexity and deadline.

Implementing a prototype in software means high flexibility, short design cycles, and good debug facilities, therefore as much functionality as possible will be implemented in software. Since target systems have to fulfill real-time characteristics, HPU and RTU provide means to guarantee predictable limits for run time variations caused by caching or pipelining effects. Application specific hardware on the other hand is very often necessary as a link to the embedding process and as execution unit for processes with deadlines too short to be met in software. A CIOP acts like a pre-processor for external events (CIOP-IO) or may be used for timing measurement respectively trace collection (CIOP-T).

<sup>&</sup>lt;sup>3</sup>These analysis methodologies take into account inter–task dependencies like precedence constraints or blocking times caused by mutual exclusive access to shared resources.

<sup>&</sup>lt;sup>4</sup>Rapid Prototyping Environment for Advanced Real–Time Systems

Figure 1.2: REAR Design Framework

A Hardware/Software co-design methodology with SDL [] as starting point allows to translate the specification into C [3] and VHDL [4] code. C-code generation is partly based on the CASE-tool family SDT (SDL Design Tool) from Telelogic, SDL to VHDL synthesis is part of the research focus [MKMKF00, MF00]. Together with run-time and interface libraries, executables can be compiled and mapped to the dedicated target nodes.

The worst (WCET) and best (BCET) case execution times 5 needed for the final schedulability analysis 7 are on the one hand provided by synthesis tools for the HW–part, on the other hand are determined measuring instrumented code during execution on the target architecture for the SW–part [PF99]. The real–time analysis model (RTAM) automatically generated from the SDL model reveals the structural inter–dependencies

#### 1.4. SYNOPSIS

incorporated in the system. It includes the timing constraints 2 that are added to the system specification by annotation. Furthermore, the RTAM is needed as information source for the optimizing code generators. If the final timeliness proof reveals there are no deadlines misses to expect, the prototype can be executed in the real environment. An event filter 6 supervises a minimum distance between events.

In contrast to simulation, the idea of a prototype is to be executed in the real world with real data. It allows to verify by execution if all assumptions were correct and the functional and timing requirements have been modeled correctly. Temporal feasibility is the crucial point in the development of hard real-time systems. Next to the proof that the prototype will meet all specified timing constraints, a first estimation on minimum required processor performance for the final realization can be gained. Furthermore, possible bottlenecks in the SDL system model can be detected, e.g. the negative effect on the responsiveness of a system caused by large areas of mutual exclusion, originating from long state transition times in server processes can be revealed. Finally, the system's predictability can be verified by analyzing the communication structure of the SDL system.

## 1.4 Synopsis

This work is organized as follows: The next chapter covers state of the scientific and technical knowledge in research topics tangent to this thesis.

Chapter 3 provides a detailed analysis of the SDL's syntax and semantics. It will be shown this language is appropriate for functional specification of hard real-time systems. Its model of computation as well as use of its language features however has to be restricted to gain predictability. A methodology to express non-functional requirements based on the "Event Stream" model is introduced.

Mapping principles allowing the translation of a SDL system model to a final implementation thereby preserving SDL's semantics are discussed in Chapter 4. Requirements to the software architecture imposed by the "Scheduling with Message Deadlines" (MEDF) model of computation are given. MEDF's predictability will be proven in Chapter 5, before implementation alternatives for the necessary run-time system support will be evaluated.

The mapping methodology to translate a SDL specification to a "Real–Time Analysis Model" (RTAM) will be explained in Chapter 6. The RTAM consists of a network of task precedences and shows processes monitoring shared resources. Both is necessary structural information needed by the final scheduling analysis algorithms which will be shortly re–introduced.

The Olympus AOCS case study, i.e. a specification of a satellite's "Attitude and Orbital Control System", serves as sample application to demonstrate the proposed design process and to evaluate the influence of modeling style and code generation strategy on results of the final schedulability analysis step. For this, overhead caused by run-time system directives will be taken into account (Chap. 7). This thesis concludes with a discussion of proposed methodologies and finally outlines possible future work.

CHAPTER 1. INTRODUCTION

# Chapter 2

# **Related Work**

The incorporation of schedulability analysis into an automated design process involves the following research areas:

- What languages are used to describe the functionality of real-time systems and how are non-functional requirements expressed?

- What methodologies are deployed to translate a system specification into a predictable realization?

- And finally, what analysis algorithms and heuristics exist to prove the required timelineness of the final implementation?

In the following sections, a closer look to answers provided for these questions will be taken, before holistic approaches comparable with this work are evaluated in detail.

## 2.1 Real–Time Constraint Specification

It can be generalized that the main focus of all specification languages lies in managing system complexity. For this, they provide means to deal with concurrency and hierarchy as well as communication and synchronization mechanisms to organize data flow and timely inter-dependencies [GVNG94, ELLSV97]. Therefore, common to most languages are process models, whereas at this level of abstraction the term *process* denotes the concept of an autonomous object with its own thread of control.

Synchronous languages like Esterel, Lustre, or Signal [Hal93] idealistically assume that processing of data consumes no time and time progresses only on the occurrence of new external stimulating events. This means actions are instantaneous and the underlying broadcast communication takes zero time as well. Aiming on formal verification of characteristics like causality, liveliness or safeness, this class of specification language necessitates such a strong synchronization. A translation to an efficient implementation keeping this restrictive semantics is difficult, for distributed applications even nearly impossible. This

is even true for Statecharts [Har87, HLN<sup>+</sup>90], whose timing model is as well synchronous in the sense that time elapses only in equally sized steps.

Asynchronous languages assume that progress of time is continuous, thus actions in processes consume an unspecified but non-zero interval of time. Communication schemes are mostly based on message exchange and may be either blocking, e.g. rendezvous concept in Ada or waiting send in Hoare's CSP [Hoa78], or non-blocking paradigms like the port concept in ROOM (*Real-Time Object-Oriented Modeling* [SGW94]) or SDL's (*Specification and Description Language* [ITU94a]) signal communication. Especially for modeling of event driven real-time applications, asynchronous (non-blocking) message communication schemes are preferable, since they allow a timely decoupling of application threads, often necessary to achieve real-time behaviour.

Although these specification languages are called "real-time", they all lack means to formulate non-functional requirements, e.g. like maximum allowed response times or to describe timing constraints imposed by the system environment, e.g. minimum intervals between external events. In a work-around like approach, expressiveness is improved in combining functional specification languages with real-time temporal logic formulas [Leu95, PB98]. Applicability however remains limited due to the cryptic appearance of temporal logic languages.

In a similar solution comparable to this work, annotations to the system specification are proposed in [SSD97]. Beneath mapping, resource, and cost requirements, the so called *SDL*\* allows to add timing requirements in form of comments. Two types of constraints are distinguished: *duration* and *jitter*. With this, definition of response times is possible, but constraining the behaviour of the system environment in a worst case manner remains unsolved.

The later problem is addressed in *PMSCs* [FLMTS97]. Again annotations in comments or text symbols, but now to Message Sequence Charts (MSC [ITU94b]) are used to express "performance requirements". So called *traffic sources* allow the specification of inter–arrival times of system stimuli. *Durations* and *spans* between marks on the MSC time axis are provided for timing constraint specification. PMSCs may be used as basis for an analysis to calculate mean processing times of system scenarios, i.e. exemplary signal sequences that cover parts of a SDL system [Lam97]. In [BAL97], the general expressiveness of MSCs for timing constraint specification is discussed and an algorithm for verifying the consistency of these timing specifications is presented. Conflicting constraints will be detected by translating basic MSCs into (cycle–free) temporal constraint graphs.

Although there exist combined efforts to incorporate those language features into new versions of SDL [MTMC99], even its latest release SDL'2000 provides no support for a description of non-functional requirements.

A contrary trend can be observed with the Unified Modeling Language (UML [Obj99b]). UML can be seen as a general–purpose specification language latterly applied even for development of real–time applications. There exist different "flavors" of this language depending on the appropriate CASE tool manufacturer [TG00]. UML has still a vague semantics and is itself under ongoing standardization [Kob99], but there are attempts to take care of special requirements imposed by this application area: The "UML Profile for Scheduling, performance, and Time" [Obj99a] includes so called "mandatory requirements" for future extensions to UML. Its section "Timing Specifications" aims on expressing constraints like deadlines, periods, jitter, inter–arrival times, and so on.

## 2.2 Code Generation Efficiency

System synthesis and thus automatic translation of a system specification into (executable) code is well understood in the field of "Electronic Design Automation". There exist sophisticated tool support (e.g. [Syn99]) to compile hardware description languages like VHDL [IEE00] and Verilog [IEE95] into networks of target components, whereupon nearly any chip manufacturer is supported. Optimizing synthesis steps allow a translation even of behavioral descriptions into system realizations that are near to an optimal solution. This means uncertainties caused by level of abstraction and granularity of the underlying timing model are successfully resolved by stepwise refinement of the input description.

Unfortunately, the latter does not apply for design processes targeting software. For a detailed problem statement refer to [Mok83] or read the discussion in Sec. 4.1. Research on code generation from SDL is mainly based on implementation strategies developed in the effort to efficiently realize multi-layered OSI protocols [Svo89]. Two different methodologies with different clustering concepts were identified: The Server Model centralizes a whole OSI protocol unit into one single task in the final implementation. Inter-layer and thus inter-task communication is based on message exchange. In contrast to this, the clustering concept of the Activity Thread Model (ATM) forces all procedures that are involved in serving an incoming request through all protocol layers into one software task. Since inter-layer communication is now based on procedure calls, no overhead due to message queuing or process scheduling can arise. The influence on efficiency when applying these strategies on protocol implementations derived from *Estelle* specifications is evaluated in [HK95]. The semantical correct mapping of SDL specifications to the Activity Thread Model is evaluated in [HKMT97]. [LK97, LK99] present refinements of the initial approach that include serving multiple, concurrent external requests (Extended ATM) and means to ensure a processing order as defined by the model of computation in SDL (e.g. reordering of SDL statements at compile time).

SDL is as well used as a system level specification language for a rapid prototyping design process [PMK<sup>+</sup>00] with both software and hardware [Mut02] as target. Since this approach partly builds upon the above mentioned design methodology and thus relies on the synchronous language VHDL for its hardware components, a timing paradigm shift during system synthesis is indispensable. Thus, the necessary "hardware run–time library" which provides components for synchronization and communication of concurrent entities on the final chip has to include a certain overhead which is acceptable for rapid prototyping. A performance evaluation of Server Model and ATM based code generation strategies can be found in [MKMKF00, MF00].

## 2.3 Schedulability Analysis

Especially hard real-time systems require an a-priori proof that all specified timing constraints will hold even in worst case situations. Reacting not until a deadline has been missed in an overload situation may have harmful consequences on the system itself or in case of a safety-critical application even on human lives.

There exist two general classes of scheduling strategies for real-time systems: The first category, called *static* scheduling, includes all methodologies that use an off-line calculation to establish a "task calendar". This table defines start times for all task and is read by the run-time system's dispatcher to allocate a certain concurrent task at a pre-defined time to the processor. The task calendar is repeatedly processed leading to cyclic task activations. Start times are referring to the beginning of each round.

Static scheduling is the basis of the fault-tolerant architecture of MARS [DRSK89, SRG89]. Since a single time table can not cope with all operational situations, multiple calendars are prepared before run-time. A "schedule switch" is then initiated in emergency situations or at pre-defined points in time when the operation mode has to be changed. Timeliness of all schedules is achieved by construction. This approach proves to be inflexible since all combinations of possible situations have to be analyzed in advance.

Off-line generation of a parametric calendar is as well proposed by [SGA93]. Their concept of static scheduling allows processing times of single tasks to be in pre-specified  $[c_{min}, c_{max}]$  intervals to increase flexibility. Processing order constraints (precedence constraints) lead to so called transactions that consist of partially ordered tasks, but there are no further inter-dependencies between transactions supported. It has been shown that the construction of a time-table for non-preemptive hard real-time scheduling is a NP-complete problem.

Taking into account sporadic tasks that occur seldom but have a short deadline (e.g. initiate the inflation of an airbag in a car crash) leads to a very pessimistic layout of the task calendar. Since polling for the sporadic event is necessary, it will devour the majority of the available processing time. *Dynamic* scheduling approaches utilize this wasted spare time in dispatching a high priority task only in the moment of the sporadic event's occurrence. One differentiates between two approaches, scheduling with *fixed priorities* and scheduling with *dynamic priorities*.

Liu and Layland [LL73] submitted the fundamental theorems to dynamic scheduling. Their assumptions rely on a very simple task model: 1. All requests to tasks are strictly periodic (cycle time  $T_i$ ); 2. New requests occur only after the previous job has been completed; 3. No shared resources and no precedence constraints are allowed; 4. Run-times have to be constant (execution time  $C_i$ ). 5. Tasks are perfectly preemptible. Liu and Layland introduce an overall "processor utilization factor" U for a number of m tasks.

$$U = \sum_{i=1}^{m} \frac{C_i}{T_i} \tag{2.1}$$

For fixed priorities, their *rate monotonic analysis* (RMA) algorithm requires priorities to be assigned to tasks in the following way: the higher the task's rate, the higher its priority.

$$U_{RMA} = m(2^{\frac{1}{m}} - 1) \tag{2.2}$$

For a large number of tasks, this upper bound goes to  $U_{RMA} = ln(2)$  which is quite pessimistic. This utilization bound can be relaxed and even set to  $U_{RMA} = 1$ , if task periods are harmonic.

utilization U remains below the least upper bound  $U_{RMA}$  (sufficient requirement).

Much research has been invested to extend Liu and Layland's restrictive task model and incorporate e.g. release jitter, aperiodic tasks, and precedence constraints into RMA analysis. A good summary is given in [KRP+93]. Special care to analyzing tasks sets that share common resources and the application of the "priority inheritance" protocol can be found in [Raj91]. An interesting approach in minimizing blocking times on shared resources by adapting a "preemption threshold" is described in [WS99].

For dynamic priorities, Liu and Layland proposed in their *deadline driven* scheduling algorithm, to assign priorities to tasks according to their deadline in the *current* request. With this, tasks with the earliest deadline will be dispatched first (EDF). Now, for a fixed set of m tasks they proved that it is sufficient to show that the overall processor utilization U remains below or equals  $U_{EDF}$ .

$$U_{EDF} = 1 \tag{2.3}$$

This means, in applying EDF scheduling a 100% processor utilization can be achieved, although periods are not harmonic. Furthermore, EDF has been shown to be an optimal scheduling algorithm. It is optimal in this sense, that if one can find a feasible schedule with a task set with fixed priorities, one will always find a feasible schedule with the deadline driven approach too.

Again, there exist innumerable research papers addressing the relaxation of the task model strictness assumed by Liu and Layland. EDF analysis algorithms to schedule task with precedences, aperiodic task activations and protocols to synchronize tasks with shared resources are summarized in [SSRB98]. Feasibility conditions for sporadic task sets with common resources are presented for example in [Jef92] and [CLB99]. Event driven systems that are triggered by stimuli with sporadic or even burst behaviour are investigated in [Gre93a, Gre93b]. Gresser's EDF scheduling theorems and his "Event Stream Model" for description of task stimuli is the basis for this work.

Astonishingly, although scheduling theory for both approaches is equally sophisticated, tool support is given mostly for rate monotonic analysis. "TimeWiz" (TimeSys), "RT–Architect" (Realogy), "PERTS" (Tri–Pacific) and others provide a real–time kernel as well as a timing analyzer.

Further dynamic scheduling algorithms are e.g. "Least Laxity First" scheduling (LLF) or distance constraint algorithms like the "Pinwheel" strategy [HL97]. The later has been designed with purpose to minimize jitter between task activations and therefore is especially suitable for multi–media applications.

### 2.4 Real–Time System Design and Schedulability

As has been shown in Sec. 2.1, real-time specification languages lack means to express quantitative timing constraints. Furthermore, there exist only few approaches that integrate a schedulability proof into the system design process as required to construct predictable real-time applications.

"Hard Real–Time Hierarchical Object Oriented Design" (HRT–HOOD, [BW95b]) provides dedicated terminal object types to identify the characteristics of activities within a real–time application. Decomposition rules force the designer to apply a defined calling paradigm when decluttering active objects into terminal objects. Each terminal object possesses certain non–functional properties. *Cyclic* objects are used to represent periodic activities. Timing and criticality attributes for this object type are period, release time offset, worst case execution time, deadline, and priority. *Sporadic* objects allow to specify a minimum interval between successive task releases instead of a period, but are treated equally during timing analysis. *Protective* objects are resource control objects that do not possess an own thread of control, but may be activated by cyclic or sporadic objects. To synchronize concurrent activations, and to minimize blocking times on common resources, a ceiling priority can be assigned to them. Finally, *passive* objects encapsulate functionality, again without a controlling thread, that may be repeatedly used by other active objects.

Unfortunately, HOOD and thus HRT–HOOD lacks a behavioural description for its objects. Instead, release time offsets and deadline splitting is needed to ensure correct processing sequence. To circumvent this, [PB98] proposes to use HOOD objects to specify system structure, but to use Modecharts to describe object details. In contrast to this, [CW95] enhance HOOD with so called *transactions* to specify object behaviour. Lack of a behaviour specification is as well the cause, that execution times in HRT–HOOD apply only to whole objects. Thus, timing resolution of schedulability analysis has to be coarse grained. Burns and Wellings show how a HRT–HOOD specified system has to be mapped to an Ada based software architecture to ensure predictability and provide a heuristic for a rate monotonic analysis based timeliness proof that takes into account the implications of an Ada real–time kernel [BW95a].

Saksena et. al. [SFR97, SK00] provide design style guidelines for ROOM ("Real–Time Object–Oriented Modeling, [SGW94]) specifications to improve schedulability. For a final implementation, they propose either a single–threaded (leading to a non–preemptive schedule) or a multi–threaded software architecture in which several ROOM objects are grouped into one real–time operating system (RTOS) thread. Fixed event priorities have to be manually assigned to inter–thread as well as to inter–object messages. Their schedulability analysis calculates the worst case blocking times of events on objects caused by ROOM's run–to–completion semantics of encapsulated transitions and the run–to–completion processing of each implementation thread. To avoid priority inversion effects, either priority ceiling or the above mentioned preemption threshold [WS99] protocol may be applied and is incorporated into their analysis scheme. Even applying a deadline monotonic approach to find a suitable allocation of priorities to internal and external events need not necessarily

lead to an optimal schedule [SKW00].

Extensions to SDL to support a performance analysis based on queuing theory is proposed in [DHHM95, DHM96]. "Queuing SDL" (QSDL) and the underlying tool QUEST allow to estimate wait time distributions of signals in SDL queues at processes. The later are bound to so called machines that provide one or several services. System stimulations, i.e. triggering events are created by traffic sources. Although a multitude of traffic sources and machine service types are made available, only stochastical predictions on system behaviour can be made. Parameters like a utilization distribution of a machine or a mean response time for a service request are not suitable for hard real-time systems which require a worst case consideration.

Transition priorities instead of normally applied process priorities are proposed for SDL systems in [ADL+00, ADL+99]. A thereof derived rate monotonic analysis is embedded in an object-oriented design process starting with "Object Modeling Technique" (OMT), respectively UML. To avoid priority inversion (PI) on transitions monitoring shared resources, the priority ceiling protocol has to be applied. Due to the run-to-completion semantics of SDL transitions, and due to the retained "first-in first-out" (FIFO) semantics of SDL process queues, i.e. a high priority event will be appended behind low priority events, blocking times of events can be become very large despite the PI avoidance mechanism.<sup>1</sup> Though this effect is covered in their timing analysis, maximum achievable processor load however has to be very pessimistic.

<sup>&</sup>lt;sup>1</sup>This is also true for the ROOM/RMA integration [SK00].

CHAPTER 2. RELATED WORK

# Chapter 3

# SDL Semantics and Timing Constraints

On the one hand, advantages in applying specification languages like SDL or UML/RT<sup>1</sup> for the design of hard real-time systems are increasingly accepted in industrial practice. For example, newest trends in standardization of the "Unified Modeling Language" [Dou98] follow SDL and ROOM language concepts. Furthermore it can be observed that these two languages will be included into the specification and design process as proposed by the "Object Modeling Group" (OMG). State-of-the-art case tools like Telelogic's Tau framework provide a tool chain, covering a continuous design process, starting with UML for requirement specification and concluding with SDL for detailed design and implementation for exactly this application domain.

But on the other hand, applicability of these languages especially for the domain of real-time systems is criticized in theoretical computer science [Hin98b, Hin98a]. Main points of criticism include:

- 1. Expressiveness to capture real-time requirements that are complementary to the *functional* description of a real-time system is poor in  $SDL^2$  [Leu95].