Technische Universität München – Fakultät für Maschinenwesen

Application concept and evaluation of a formal specification approach usable by engineers for retrofitting production automation by software changes

Suhyun Cha

Vollständiger Abdruck der von der Fakultät für Maschinenwesen der Technischen Universität München zur Erlangung des akademischen Grades eines <a href="Doktor-Ingenieurs">Doktor-Ingenieurs</a>

genehmigten Dissertation.

Vorsitzender: Prof. Dr.-Ing Wolfgang A. Wall

Prüfende/-r der Dissertation:

1. Prof. Dr.-Ing. Birgit Vogel-Heuser

2. Prof. Dr. rer. nat. Bernhard Beckert

Die Dissertation wurde am 09.02.2021 bei der Technischen Universität München eingereicht und durch die Fakultät für Maschinenwesen am 14.04.2021 angenommen.

#### Bibliografische Information der Deutschen Nationalbibliothek

Die Deutsche Bibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über <a href="http://dnb.ddb.de">http://dnb.ddb.de</a> abrufbar.

# Application concept and evaluation of a formal specification approach usable by engineers for retrofitting production automation by software changes

Autorin:

Suhyun Cha

ISBN: 978-3-96548-110-7 (Print) ISBN: 978-3-96548-111-4 (E-Book)

1. Auflage 2021

Cover: sierke WWS GmbH sierke MEDIA, Göttingen

#### Copyright-Hinweis:

Das Buch einschließlich aller seiner Teile ist urheberrechtlich geschützt. Jede Verwertung außerhalb der engen Grenzen des Urheberrechtsgesetzes ist ohne Zustimmung des Verlags unzulässig und strafbar. Der Nutzer verpflichtet sich, die Urheberrechte anzuerkennen und einzuhalten.

© 2021 sierke VERLAG sierke WWS GmbH Sternstraße 7 37083 Göttingen Tel. +49 551 503 664 5 info@sierke-verlag.de http://www.sierke-verlag.de

# Acknowledgments

I would like to thank my advisor, Professor Birgit Vogel-Heuser, for her support, including many valuable discussions of my research. She has been a great professor and a mentor. I would also like to thank my thesis committee members, Professor Bernhard Beckert, for giving me great feedback and opinions, and Prof. Wolfgang A. Wall for serving as the committee head.

I am also very grateful to all the colleagues of the Chair of Automation and Information Systems at the Technical University of Munich for all the research-related discussions and personal conversations which encourage and motivate me all the time.

Most of the dissertation is based on the German Research Foundation (DFG) Priority Programme 1593 (SPP1593) IMPROVE APS project result in close cooperation with the group of Professor Bernhard Beckert, Dr. Mattias Ulbrich, and Alexander Weigl in Karlsruhe Institute of Technology; I would like to thank all project members. Thanks also to Thomas Mikschl, who has been a great support in this project for implementation.

In addition, I would like to thank my family, Soobin and Sunyul in Munich, and Mrs. Kang, Mr. Cha, Sujeong, Mrs. Park, Mr. Lee, and Jiyoung in Korea, who support me all the time.

# Table of Contents

| 1.     | Introduction                                                        | 1        |

|--------|---------------------------------------------------------------------|----------|

| 2.     | Field of Investigation                                              | 5        |

| 2.1.   | Technical characteristics of automated production systems           | 5        |

| 2.1.1. | Process automation and aPS                                          | 5        |

| 2.1.2. | Control software of aPS                                             | <i>6</i> |

| 2.2.   | Control software engineering of automated production systems        | 10       |

| 2.2.1. | Implementation of the aPS – focusing on the software development    | 10       |

| 2.2.2. | Control software quality assurance                                  | 11       |

| 2.3.   | Formal verification terms and basics                                | 12       |

| 2.3.1. | A framework for formal verification                                 | 13       |

| 2.3.2. | Regression verification                                             | 14       |

| 2.3.3. | Formal specification of the requirement                             | 16       |

| 3.     | Requirements on a Formal Specification of Reactive System's Control |          |

| 2.1    | Behavior                                                            |          |

| 3.1.   | Requirement considering target system characteristics               |          |

| 3.2.   | Requirements considering engineering processes of aPS               |          |

| 3.3.   | Requirements considering the users' point of view                   |          |

| 3.4.   | Summary of requirement                                              | 25       |

| 4.     | State of the art                                                    | 27       |

| 4.1.   | Formal specifications behavior: language and utilization            | 27       |

| 4.1.1. | Text based temporal logics                                          | 27       |

| 4.1.2. | Graphical and signal pattern based languages                        | 30       |

| 4.1.3. | Specification approaches for automation systems                     |          |

| 4.2.   | Monitoring of aPS execution                                         | 36       |

| 4.3.   | Usability studies of specification approaches                       |          |

| 4.4.   | PLC software programming tools                                      | 38       |

| 4.5.   | Discussion of the research gap                                      | 38       |

| 5.     | A Concept of the Table-Based Formal Specification Language For Rea  |          |

|        | System Software                                                     | 41       |

| 5.1.   | Concept overview                                                    | 42       |

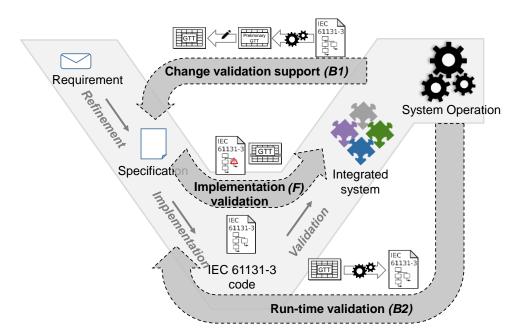

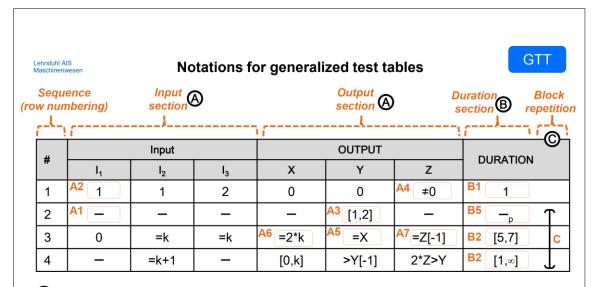

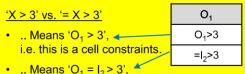

| 5.2.   | Generalizing test tables as a specification representation          | 44       |

| 5.2.1. | Structure of GTTs                                                   | 44       |

| 5.2.2. | Value referencing and generalization                                | 45       |

| 5.2.3. | Generalizing duration                                               | 47       |

| 5.2.4. | Simplifying exclusion                                               | 48       |

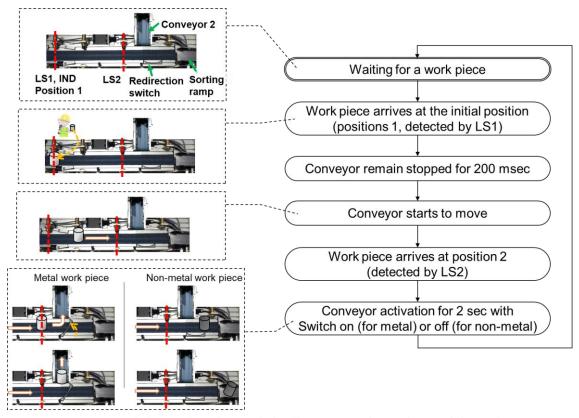

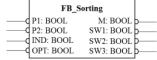

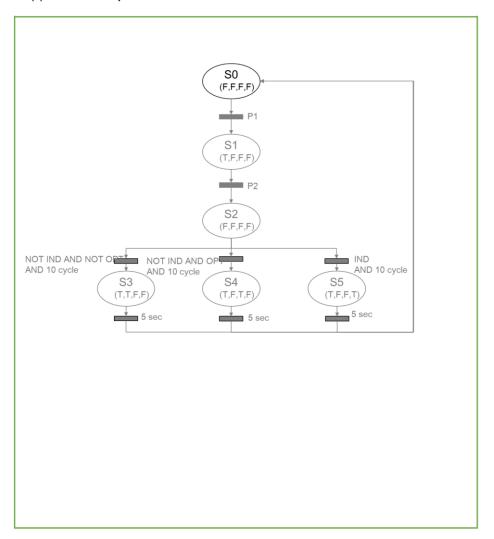

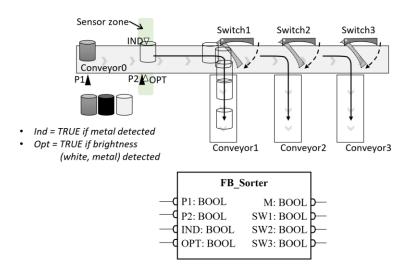

| 5.3.   | Application example                                                 | 50       |

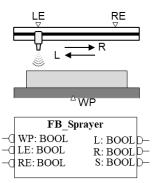

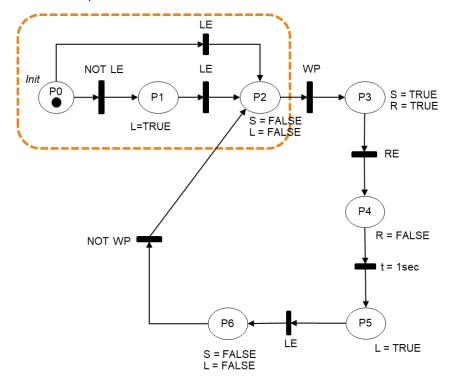

| 5.3.1. | Description of the module                                           | 51       |

| 532    | Requirements of the module                                          | 52       |

| 5.3.3.  |         | ses for the module in test tables                                           |      |

|---------|---------|-----------------------------------------------------------------------------|------|

| 5.3.4.  | Behavi  | or specification in GTTs                                                    | 53   |

| 5.4.    | Extens  | ion of the developed approach                                               | 56   |

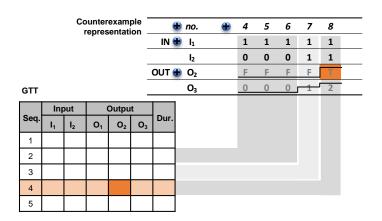

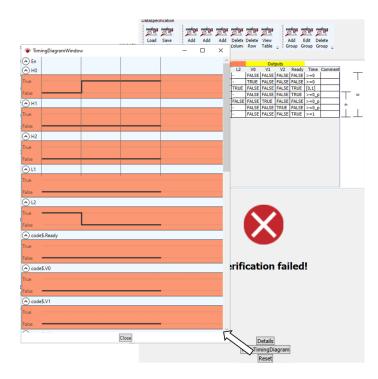

| 5.4.1.  | Debug   | ging through the counterexample presented as related to GTT(F)              | 57   |

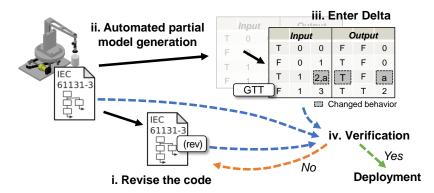

| 5.4.2.  | Achiev  | ring preliminary specification out of IEC 61131-3 program in GTT (B1)       | 58   |

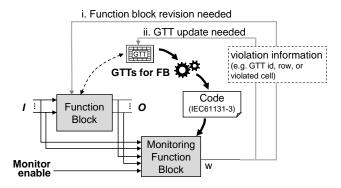

| 5.4.3.  |         | ing monitors by the transformation of the specification into IEC 61131-3    |      |

|         |         | n block (B2)                                                                |      |

| 5.5.    | Summa   | ary: table-driven two-way quality assurance process - embedding user-frie   | ndly |

|         | formal  | specification in the engineering process                                    | 66   |

| 6.      | Imple   | nentation                                                                   | 69   |

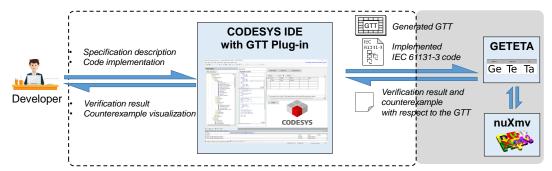

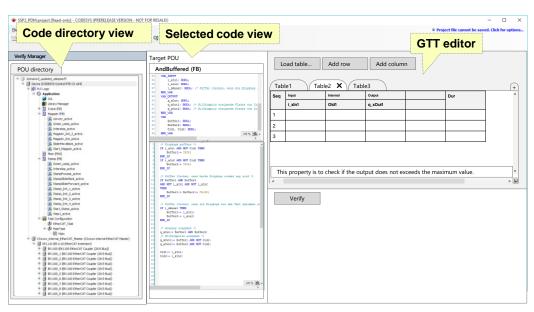

| 6.1.    | Overvi  | ew                                                                          | 70   |

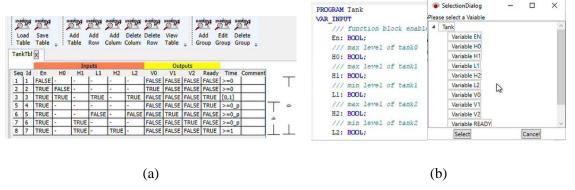

| 6.2.    | Genera  | ating and editing the generalized test tables                               | 71   |

| 6.3.    |         | cting to the verifier                                                       |      |

| 6.4.    |         | ation result representation                                                 |      |

| 7.      | Evalua  | ation of the approach                                                       | 75   |

| 7.1.    |         | ility analysis through application case studies                             |      |

| 7.1.1.  |         | or description of a single component – in the viewpoint of module develop   |      |

| 7.1.1.  |         | se 1)                                                                       | -    |

| 7.1.2.  | Behavi  | or description of a multi-component module - in the viewpoint of applicat   | ion  |

|         | engine  | er (use case 2)                                                             | 79   |

| 7.1.3.  | Obtain  | ing changed specification based on the preliminary specification generated  | 1    |

|         | (use ca | se 3)                                                                       | 81   |

| 7.1.4.  | Monito  | oring of the target function block – automated generation of the monitoring | 5    |

|         | block ( | (use case 4)                                                                | 83   |

| 7.2.    | Empiri  | cal study of the usability evaluation                                       | 87   |

| 7.2.1.  | Experi  | mental hypotheses                                                           | 87   |

| 7.2.2.  | Experi  | ment planning                                                               | 89   |

| 7.2.3.  | Partici | pants profile                                                               | 92   |

| 7.2.4.  | Experi  | ment results                                                                | 95   |

| 7.2.5.  | User ev | valuation summary                                                           | 100  |

| 7.3.    |         | evaluation from industry                                                    |      |

| 0       | •       | •                                                                           |      |

| 8.      | Assess  | ment of the Fulfillment of the Requirements                                 | 105  |

| 9.      | Conclu  | ısion and Outlook                                                           | 109  |

| 10.     | Litera  | ture                                                                        | 113  |

| 11.     | List of | Figures                                                                     | 131  |

| 12.     | List of | Tables                                                                      | 135  |

| Append  |         | Materials of experiment 1 for Chapter 7                                     |      |

|         |         |                                                                             |      |

| Appendi |         | Demographic data and prior knowledge questionnaire                          |      |

| Appendi | x A.2   | Evaluation tasks with possible answers                                      | 141  |

| Appendix A.3 | Given handout to be used during evaluation |  |

|--------------|--------------------------------------------|--|

| Appendix B.  | Materials of experiment 2 for Chapter 7157 |  |

| Appendix C.  | Materials of experiment 3 for Chapter 7164 |  |

## 1. Introduction

Automated Production Systems (aPS), including manufacturing machines and logistics, are required to cope with various and varying production requirements over their long lifecycles [VFST15]. These various requirements lead to the increased complexity of aPS [DKKK12, FKWV19, McBu00], introducing a lot of changes in various forms and objectives with different reasons, and, accordingly, their engineering becomes more complex, following current trends and increasing customer flavor varieties [VFST15]. Malfunctions (i.e., severe failures) of aPS might cause severe issues economically and safety-relatively [UIVo18a], as aPS are socio-technical systems, which are defined as operational processes and people (i.e., operators) are inherent parts of the system [Somm15]. Therefore, aPS have high requirements on availability and reliability during the running period [VFST15] not only for its productivity concerning dramatic maintenance or product producing cost but also for its safety not to harm any personnel or customer of the product. In the meantime, the proportion of system functionality realized in software is increasing [Thra10]; the control software of aPS is, therefore, to be developed and revised continually, e.g., due to bug fixing or changed/new functionalities [VFFL15], requiring continuous quality (re-)assurance activities accordingly.

In today's industrial practice, software quality is commonly achieved by dynamic validation either by manual stepwise testing or by running automated testing [UIVo18b] as a quality assurance activity "in which a system or component is executed under specified conditions, the results are observed or recorded, and an evaluation is made of some aspect of the system or component" according to the definition of ISO [ISO10]. However, one of the main weaknesses of traditional testing is coverage. One test case covers only a particular execution of the software and, thus, many possible cases remain uninvestigated. Therefore, testing is useful for typical or expected faults while unpredictable and rare cases, which can also have severer consequences, are less likely to be discovered using testing. In aPS engineering processes, changes also occur during the commissioning and start-up procedure [VFST15] for on-site assembling [Voge09] and fine-tuning. According to the time delay analysis [Hack18, ReWü07, VFST15], software debugging during the commissioning takes more than half of the effort though it requires small changes. In detail, it is observed that 15-25% of the total project time is used for commissioning, and almost 63% of it is used for control software debugging [ReWü07]. This commissioning procedure also requires testing (mostly manual [VFFU17]) under the high time pressure [UIVo18a] and the high chances of damage either by operating incompletely integrated machine or by switching the operation mode [VFRF15] for testing, since quality assurance through testing requires real equipment executions.

2 Introduction

As one other main method of quality assurance, there is formal verification. In this formal verification framework, the behavior of the target artifact (typically formal model) is examined mathematically and proved (or guaranteed) as conforming/violating given conditions [CWAC96] through the mathematical and exhaustive checking, providing full coverage in contrast to testing. Since it calculates the given artifacts by (mathematical) analysis, the equipment, i.e., plant and machine in aPS' case, is not needed to be running in contrast to testing and, thus, damages during the (testing) execution do not have to be concerned. The conditions to be satisfied are actually the requirement that is desired to be implemented (or designed in case of early stage of the development) in and satisfied by the artifact. These are stated and documented in a way that could be comprehended and processed, which is called as specification. Although the specification is the essential entity within the formal verification context, providing the criteria to decide the targetunder-verification is correct or not, a good specification is still lacking [Sesh12, UlVo18b]. Specifications for many aPS in operation are not easily found [VFST15] because, on the one hand, aPS have been built decades ago going through a lot of changes in the meantime without appropriate and precise history records, and on the other hand, the way of providing formalism, such as temporal logics, is not what typical automation engineer would take and develop [Holz02]. Ultimately, the absence of formal specification hinders applying formal verification along the automation engineering processes.

The importance of the specification is highlighted not only for verification purpose. Specifications are involved in almost all engineering processes including the maintenance phase, not only for the initial development processes but also for modification (i.e., change implementation) processes [Somm15] as it indicates the intention to be implemented. Explicit documentation is also required to comply the legal regulations and guidelines, such as Good Automated Manufacturing Practice (GAMP [ISPE20]), for some particular type of product production. Furthermore, formally specified requirements could be handled systematically to synthesis or generate another artifacts (e.g., program code) by transforming it or forming/extracting information into/from formalism respectively [Li14]. It would become more beneficial in the context of aPS engineering, for which various types of developers and engineers collaborate by communicating with each other and delivering their results to others, even only within the software discipline [VFST15].

The objective of the research in this thesis is to provide a support for increased control software quality for aPS in production automation. A formal specification approach for the aPS control software behavior description to support software is proposed aiming at accessibility from the automation engineers and systematic manipulation for further utilization, tackling the motivations and challenges above. Accessible notations to describe comparably small scale software changes

Introduction 3

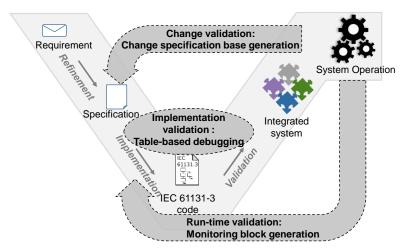

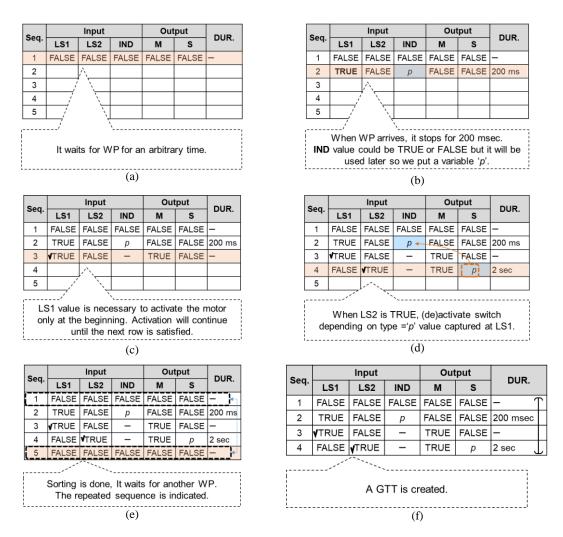

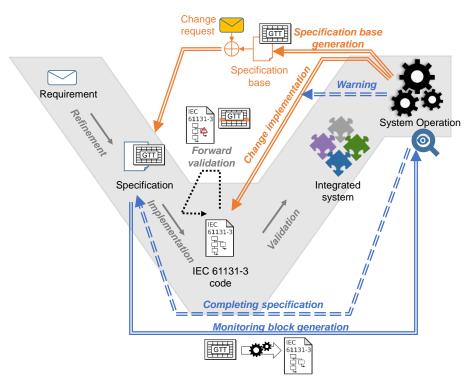

retrofitting the production automation are approached, grounded on the practices which are typically used in the industry settings. Besides used as a formal specification in formal verification framework, additional concepts of utilizing specifications are also presented to strengthen the control software quality assurance through the proposed approach: generating monitoring block from the specification and mining the preliminary specification in a user-guided way (Figure 1).

Figure 1: Schematic representation of the thesis scope: complementing quality control driven by specification

This thesis has been developed in the context of the German Research Foundation (DFG) Priority Programme 1593 (SPP1593) IMPROVE APS project in close cooperation with the group of Professor Bernhard Beckert and Dr. Mattias Ulbrich in Karlsruhe Institute of Technology (KIT). The formal basis of the introduced concept (i.e., Generalized Test Tables) has been proposed by KIT (Alexander Weigl) as well as the regression verification tool (cf. [Weig21]). The contents and contributions of this thesis are based on previous publications by the author, which are [BCUV17, CUVW17, CUWB19, CVWU21, CWUB18a, CWUB18b, VoCh20, WWUU17]. The overall requirements for the concept have been derived jointly, and the focus of this thesis is put on the automation engineering perspectives and applications of the concept from the mechanical requirements and use cases, to the notation without its formal underpinning. The work in this thesis also include the empirical evaluation with students and the expert evaluation with industrial engineers.

The thesis is structured as follows. First, an overview on the field of investigation together with basic definitions is provided in Chapter 2, considering the characteristics of the target system and its engineering domain that presented approaches are to be applied to, precisely aPS as a specific type of mechatronics system. In Chapter 3, considered requirements as a formal specification method are presented, separated into the different views on system characteristics, engineering characteristics, usability to be satisfied by the presented approach. The related works which have

4 Introduction

tackled the presented requirements are introduced and analyzed in Chapter 4 to identify the research gap as a current state of the art. In Chapter 5, the approach developed in the course of this thesis to satisfy the identified requirements and research gap are presented. The approaches are presented into two parts: presenting the formal specification syntaxes and their applications as the concepts for further utilization. The prototypical tool concept, embedded within the IEC 61131-3 code development environment, is overviewed in Chapter 6 to demonstrate how the proposed approach is to be implemented as an add-on to the aPS control software development process. The approaches are evaluated in Chapter 7 in three different manners: feasibility studies with practical application examples, usability studies through empirical observation from the survey, and industry expert feedback through the intensive discussion. In Chapter 8, the conclusive finding and the assessed results obtained throughout the evaluation are presented. Finally, the thesis concludes the summary of the achieved results and the outlook on future works in Chapter 9.

The approach is researched and developed to strengthen the quality of the implemented control software, easing engineering processes of aPS, especially for the case of control software changes. To specify the target of the presented approach and the domain requirements, descriptions about the target system, engineering processes, as well as the related techniques are to be introduced. First, the target system has to be narrowed down regarding the relevant characteristics to apply the presented approach. The root of the formal specification with respect to the formal verification comes from the computer science field targeting pure software behavior verification; this work aims at aPS, which realize the technical processes being interwoven with the multi-discipline artifacts. Second, among the various constituents of aPS, the focus is put on the control software part of the system and its small changes, especially during/after commissioning and start-up, more specifically. The control software gets more complicated to cope with the increasing and varying requirements and takes part in a bigger role than before by being attended as its flexibility [VFST15]. The description of these two characteristics answers the question – where this approach aims at to be applied. Along the engineering process of the aPS control software, the quality assurance step will be focused as the target stage that the presented approach is to be applied, especially while implementing small changes. Among various techniques of system validation, formal methods and verification concept are under consideration of the approach. Thus, the fundamentals to understand the approach will be introduced in this chapter so that the following concept description could be easily understood.

# 2.1. Technical characteristics of automated production systems

The presented approach aims at the formal behavior specification of the software changes of aPS. Therefore, special properties of the target system and its control software will be presented in the following to allow for a better understanding of the requirements and the approach.

#### 2.1.1. Process automation and aPS

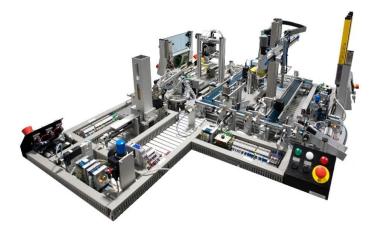

The target systems, i.e., aPS, are process automation systems specialized in controlling production processes. APS are defined in [VFST15] as "...comprised of mechanical parts, electrical and electronic parts (automation hardware) and software, all closely interwoven, and thus represent a special class of mechatronic systems. "In the viewpoint of engineering and operations, "aPS, a particular type of mechatronic system on which this paper focuses, is designed-to-order systems. These are complex manufacturing systems, and they have a typical lifetime in the operation of several decades". In the functionality point of view, aPS refer to the manufacturing and logistics

plants like production lines for automobiles or bottling beverages focusing on the production automation.

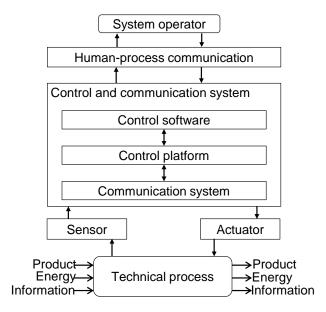

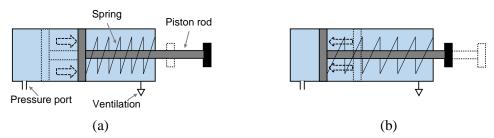

During the operation, the system status is changed by the technical processes with relevant parts (de)activated. The technical processes proceeded within aPS are based on the definition in [VFRF15] – a process by which the involved object, i.e., matter, energy, or information, is altered in its state (Figure 2). Thereby, a technical process is the totality of all operations in which material, energy, or information is converted, transported, or stored. Automation [IEC13] in general requires to access to information from this technical process (via sensors) to influence the technical process (via actuators) based on its behavior. Here, material, energy, and information are the objects of the technical processes. Also, human interaction is an important element in aPS since a human is one of the main elements contained in the process automation as an entity, who develops, follows the process event, controls and influences process, and handles the faults [VFRF15].

Figure 2: Technical process and technical system (reproduced from [VFRF15])

#### 2.1.2. Control software of aPS

The execution of the aPS control software is based on the operation mode of the system [VRFS16]. As presented by Güttel et al. [GüWF08], the main operation modes of function blocks can be defined as follows:

- Automatic mode: the normal and usual behavior of the machine part

- Setup mode: the behavior of a machine part before or during the operation (if necessary) to set up the machine part to a specific status to proceed to the further operation mode

- Manual mode: the behavior to move the machine part as the manual input drives

Semi-automatic mode: the behavior to operate the machine part automatically but also guided by the manual input

- Initialize: the behavior of a machine part executed at the beginning or after a resume followed by the halt of the machine (part) to be prepared for the further modes

- Shut down: the behavior of a machine part when the machine (part) finishes the execution

- Save stop: the behavior of a machine part when the machine (part) gets into the safe mode These operation modes of aPS are explicitly defined and modeled including the states valid within each mode and the transitions of those states, as represented in OMAC standard typically for food and beverage production systems, and OMAC state machine is a part of PackML [Omac09], which accommodates the operational consistency of packaging as a standard. Thus, most of the control software is implemented its various functionalities considering its operation mode.

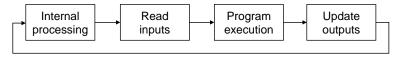

The control to execute computing and signaling is conducted by Programmable Logic Controllers (PLCs) for aPS. It consists of a central processing unit(s) (CPU), memory, and I/O units with all connected by bus systems [Hans15]. The control software is loaded on the memory part and executed by CPU, accessing I/O units, where all the sensor and actuators are connected ultimately for signaling. The control software, which is loaded on the PLC, is similar to the typical software in the sense that they cause some changes on the system as its task by being fetched, calculated, and update the system status. Typically, software running on a PC is executed to get a result at the end or in the middle of the execution by updating variable values on each statement in a program. Different from this typical software system, the PLC control software should react to every environmental signal concerned and, thus, this has to be under consideration of the executing by reading the values frequently. Therefore, PLC operates in a cycle-based way, which consists of internal processing, reading inputs, program execution, and updating output [LaGö99] (Figure 3). First, the PLC checks its state to ensure the availability of the operation regarding any error or interrupt in the initial processing. After that, the input status (i.e., sensor values) is read from the clamp and stored in the memory part. Based on the stored value to be participated in the calculation, the program execution takes place. Once all the output and internal variable values are calculated and decided, the output memory is read and put on the clamps so that the corresponding signals could be updated. These four steps repeat in a cyclic manner within PLC and continue until the controller is turned off. As the name already infers, a PLC requires a high-level language element, i.e., control software, to control the connected element to execute the technical process as the user of the

Figure 3: Schematic view of a cyclic operation of PLCs (reproduced from [LaGö99])

system intends [IEC09]. In other words, functional operations of the PLC is achieved by an appropriate (to the system mission) program. Many PLC programming standards have been suggested over the years and converged to IEC 61131 standard IEC 61131-3 [IEC09], being followed by most of the major PLC manufacturer [Hans15].

IEC 61131-3 consists of three types of program organization units (POUs) of *Programs, Function Blocks*, and *Functions*, implemented in five language varieties, two textual languages, which are Instruction List (IL) and Structured Text (ST), and three graphical languages, which are Ladder Diagram (LD), Function Block Diagram (FBD), and Sequential Function Chart (SFC). *Function* type POUs could be considered as a subroutine without any memory inside of it, meaning that it depends on the parameter value when it is called by other POUs and results in the same output whenever it is called as long as the input parameter is the same. In contrast, *Programs* and *Function blocks* could have the individual state of the execution inside of them, meaning that POUs in these type change their internal state and result in different output depending on the state, in which the POU is, even if they get the same input. *Programs* are the highest level to define the execution of the program within a *Task*, which is an execution control element (of the resource) as a whole, and a *Program* consists of a network of *Function blocks* and *Functions* within its implementation. Thus, Task(s) could be defined for the missions of the target system on a resource (i.e., PLC) in a particular configuration, and the mission is realized by calling the Programs and following Function Blocks and Functions.

Among the five different languages of IEC 61131-3, ST and SFC are mainly focused on in this thesis. ST is a high-level language with similar characteristics to Pascal language as well as C and C++ [Hans15]. It has the strength to handle arithmetic calculations and structured data types with compressed expression (e.g., compared to Ladder Diagram) as a textual language benefitting from its higher degree of freedom. SFC is one of the graphical IEC 61131-3 languages, derived from GRAFDCET (IEC 60848), typically used to describe the control flow structure of the system in a sequential manner. With the advantage that it is suitable to used various levels (i.e., higher level to define the abstract process description and lower level to define the code events in the detailed level) [Hans15]; it is accepted as one of the major languages of PLC programming. Since the syntax of ST is similar to the other conventional languages as mentioned and the syntax itself is not the focus of the work of the thesis, it is not described in detail, while that of SFC is to be introduced here mainly following [IEC09] and [Hans15] as a preliminary knowledge to understand the application concept further especially Section 5.4.2.

#### Basics of SFC

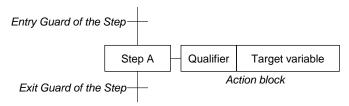

SFC consists of three main elements: steps, transitions, and actions. Steps are the unit of the sequence controls. Transitions indicate turning over the control from one step to another step decided by the transition guard. Actions are the events included in the step and executed while the step is active (e.g., Figure 4). Execution consists of activation, execution of the actions, and deactivation of the step in order. When the control is in the previous step, and the entry transition guard is satisfied (*Entry Guard of the Step* in Figure 4), then the step is activated, and the actions are executed. Actions shall be either associated with action blocks or declared in the nested form in all kinds of IEC 61131-3 languages; the action block cases are only considered in this thesis. After one cycle of the action execution, step deactivation is decided by checking the exit transition guard (G2 in Figure 4). The following step is activated once the guard is satisfied. Each step might have entry and exit action, which is executed when the step is activated and deactivated, respectively.

Figure 4: A step of SFC with entry and exit guard

An action block consists of a qualifier to indicate relevant action type and a Boolean variable as the target of the indicated action. Among all the behaviors of the qualifiers (Table 1), *SD* (Stored & Delay) and *SL* (Stored & Time Limited) are excluded since their timing behaviors are independent of the activation of the step. They violate the step activation, so they are not recommended due to the unpredictable risks [Hans15]. It is only considered that the final scan is disabled, so P1 has the same behavior as P, although the action control can have a "final scan" option to enable or disable all actions executed one extra time after the deactivation. The enabled case can be easily derived by applying a disabled case with an additional execution at the end of the step.

Table 1: SFC action qualifiers

| Requirement ID | Requirement description                                             |  |

|----------------|---------------------------------------------------------------------|--|

| N              | Set the value during active(Non-stored)                             |  |

| S              | Set and store the value (Set)                                       |  |

| R              | Reset and store the value (Reset)                                   |  |

| P              | Generate a pulse for one cycle (Pulse)                              |  |

| P1             | Generate a pulse on step activation                                 |  |

| P0             | Generate a pulse on step deactivation                               |  |

| $\overline{L}$ | Perform for a certain time as long as it is active (time Limited)   |  |

| D              | Perform after a certain time as long as it is active (time Delayed) |  |

| DS             | Performed after a certain time and store the value (Delayed Set)    |  |

### 2.2. Control software engineering of automated production systems

The presented approach is to be used for validation of developed control software, which lies in the process of aPS engineering. To define the field of investigation more clearly, aPS engineering processes focusing on the control software and its validation will be presented in the following.

#### 2.2.1. Implementation of the aPS – focusing on the software development

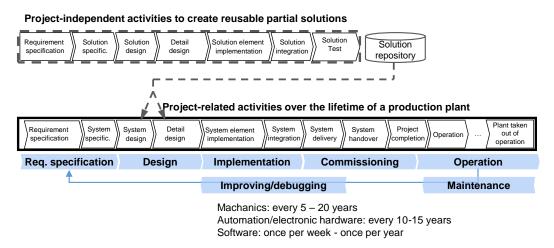

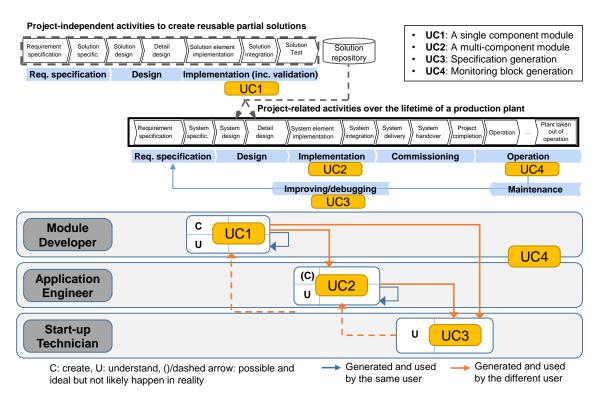

Since aPS, a particular type of mechatronic system, are designed-to-order systems, each aPS engineering process goes through specific engineering methods depending on the own requirements and objectives of the system. The engineering life cycle has been depicted in [VFST15] (Figure 5), and the focus of the explanation here is put on software development. Basically and ideally, it is assumed that project-independent activities (upper part in Figure 5) are already done in the metalevel, or this could be regarded as to be done from the former project by extracting common elements over the projects. Common and reusable artifacts and their arrangement developed and kept in the solution repository to be used further within the individual project. Libraries modules are expected to be developed by the module developers [VFND18] during the project-independent. Later, customer-specific projects are designed and developed in particular (lower part in Figure 5). Coping with the customer requirements, a specific type of plant is developed. Application engineers organize the library modules adding some glue codes to generate the project-specific software. Though the overall process of engineering from requirement specification to the maintenance in the coarse level is similar to the other systems, like pure software systems, one of the big difference is that aPS have physical substances. Many plant pieces are shipped in part, assembled, and commissioned on-site [Voge09]. Although the software has been already validated regarding

Figure 5: V-Modell XT with separation of the project-independent and project related activities (primarily presented in [VERE10], reproduced from the figure in [VFST15])

the module composition (earlier done in house), there comes further adjustment, not only for hardware adjustment but also for software modification, during the commissioning stage [VFST15]. As longer life cycle (usually decades) and corresponding aging cause components from different disciplines to go through re-engineering and modernization (mechanical engineering: 5-40 years, electrical engineering: 10-15 years, software engineering: weeks to months), it is unavoidable to face various changes with various reasons, e.g., physical wear and tear of the components [Kern19], changing requirements, lack of spare part availability [VHCR17], or technology trends. For the change implementation, project-specific engineering processes are gone through iteratively. Conclusively, aPS developers face many chances of developing (including validating) and changing/adjusting software functionalities over the lifecycle. This means that the effort to engineer aPS is not only put on the initial implementation entirely, but a lot of maintenance activities as well as following up changes including to update or add functionalities, to improve behavior, or to debug, occur very often (cf. [VoOc18]: frequency of software updates of machine and plant manufacturers were revealed as every less than 6 months for 44% and 13%, as every less than 12 months for 44% and 64% respectively) and also require quite amount of resources, i.e., cost and time (cf. [ReWü07]).

#### 2.2.2. Control software quality assurance

During and after the implementation or the change realization, the implemented part of the system is required to be assured that it meets the specification as well as the expectation of the customer. Following the engineering steps, the implementation goes through unit level validation – for its functional conformance (in the implementation stage), integration validation – to assure the functional correctness as a part of the whole system (in the integration stage), and the acceptance testing – to be validated under the actual operating environment (commissioning and start-up stage).

These validations are typically being done in the form of testing, which is defined as "An activity in which a system or component is executed under specified conditions, the results are observed or recorded, and an evaluation is made of some aspect of the system or component" [IEEE14A]. Testing is intended to discover the system defects before its usage by executing the system (or system part) under test (SUT) with the artificial but plausible data to provide the input to the SUT, and observing the outcome [Somm15]. In other words, the correctness of the implementation is determined by controlling the system to traverse a specific execution path of the statements within the code. Strictly speaking, testing can show the executed system run is safe and correctly working without any error. However, since executing all possible execution paths is not feasible, only a limited number of test runs could be conducted, which means some existing errors (in the executed part of the system) could be figured out, but error-freeness cannot be assured. Formal methods,

which is one of the static analysis of verification techniques and represented by the formal verification, are considered as a complementary technique not only to this weakness of testing [Somm15], but also its less resource usage, i.e., state analysis does not require the physical system which could help to save cost and time of the validation process. More details on the formal verification rationale are to be discussed in the following section (cf. Section 2.3). To have a closer look at the current industry practices, although a number of companies apply automated testing, there exist still many of them adopting manual testing or some companies relying solely on the testing at commissioning: 84% and 10% of the participants respectively of the survey presented in [VoOc18]. Also, it was shown in the same research that many companies are testing every specified scenario to obtain the requirement coverage (61%) though the code coverage is comparably low (15%), resulting in low efficiency of the testing.

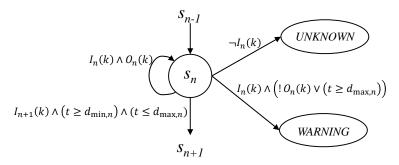

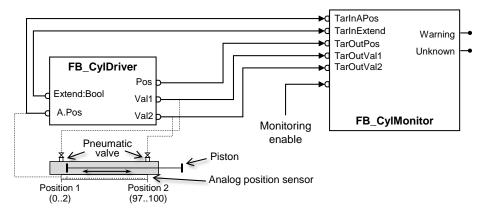

As an a posteriori quality control mechanism, monitoring takes an important role for safety-critical systems such as aPS [AbRo10] since any malfunction may cause not only damage on the system (itself) or the operating personnel but also the payload that the system handles and that the harm to the user of the resulting product might be inherent potentially. To avoid these critical effects, the main objective of monitoring is identifying both error situations during runtime and unexpected behavior of the technical process or the hardware not covered by the specification. Possible causes for erroneous states of these parts of the system are, for example, wear on the hardware and manipulation of the technical process or the aPS. Malfunctions and their resulting harms could be avoided by faults identified and handled as soon as possible. Today, monitoring functions are often related to a specific piece of hardware and are directly connected to functions that abstract the interface to that component (driver functions). Information about the hardware behavior is tapped from the inputs and outputs of the drivers. In case of undesired hardware behavior, warnings are given to the driver and the rest of the software system. It is of utmost importance that the monitoring functions work as intended and detect all errors and unknown states of the system to allow the system to give appropriate warnings, handle these errors or bring the system into a safe state by performing an emergency stop to prevent further damage.

#### 2.3. Formal verification terms and basics

Formal methods are software engineering methods through the application of mathematics for modeling and analyzing systems utilizing the benefits of its rigor [BaKa08]. As the complexity of the control software and its functionality grows, and the demand for high-quality solutions as well as reduced engineering cost (including time), formal approaches in aPS engineering, or in PLC programming more specifically, are required [FrLi00]. The formalisms within aPS engineering processes have been introduced in the form of specific modeling languages like UML or SysML

for the design phases in the scope of model-based engineering, and later, also for the quality assurance purposes as formal verifications [Vyat13]. As the focus of this thesis is put on the formal specification of the aPS control software, the basics of the formal verification follow below.

#### 2.3.1. A framework for formal verification

System verification is defined as "the process of evaluating a system or component to determine whether the products of a given development phase satisfy the conditions imposed at the start of that phase" according to [IEEE14A] It is often stated with the "written statement," which is the specification comparable to the "conditions" in the earlier quotation. That means verification is an activity to assure the flawless of the target system concerning the specification, meaning the target system behavior conforms to the required conditions, which are reflected in specification.

Such activities mainly aim to obtain dependability, including the quality properties of availability, reliability, and safety of the system [IEEE14B]. The verification result is not meaningful if there exists any ambiguity regarding the requirement interpretation, and, accordingly, system verification activities fall in the range of formal analysis in this sense since the formal descriptions do not allow any ambiguity with rigorous syntaxes and semantics. In addition, formalisms allow the automated tool supporting since mathematical expressions can be easily transformed into a form, in virtue of its formalisms, that computer systems can process.

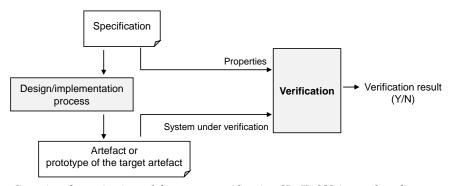

As a static analysis technique, formal verifications do not require the system execution, and, thus, no plant is needed. They use mathematical calculations to prove the conformance of the system to the given properties. There are two different approaches to verification: one is theorem proving, and the other is model checking [BaKa08]. In theorem proving, the system is described as a set of logic formulas (i.e., system axioms), and so the properties are. Theorem proving is to find proof to obtain the properties as conclusions from the system formulas as premises. In model checking, the system is described as a finite model, and the properties are in logic formulas. Model checking methods compute whether the asserted hypotheses (properties) are valid in any case. In both approaches, it is necessary to have formal descriptions of the system (either as a set of formulas or a formal model) and formal specifications as the properties to be confirmed (Figure 6). Though this thesis focuses on the formal specification part in the formal verification, all the concepts introduced are framed within the model-checking scope since the overall approach has been developed under the model checking approach.

Figure 6: Generic schematic view of the system verification [BaKa08] (reproduced)

The result of the formal verification may appear in three types [HaMM16]: proven (meaning that the given system representation conforms to the specification), a violation with a counterexample, and timeout (meaning that the proof calculation takes a too long time or runs out of memory). If the software is proven as conforming to the specification, it would be the most favorable case from the viewpoint of the user (of the verification) since building a system satisfying the given requirement is the gold of the engineering. Even if the proof fails, it is still meaningful if the verification gives the information of counterexample, which shows the execution path leading the system status to a state that violates the property described as specification, starting from the initial state. The third type, timeout, is the worst case of verification, which is also regarded as one of the barriers to utilize formal verification. As easily seen in many practical cases [BaKa08], the state space could be very large, which leads to the so-called state explosion. This is critical for the approaches using state-space search algorithms, such as model-checking. State variables with a number of values, e.g., integer, or higher number of parallelisms of separate processes, entail states growing exponentially in the program model [BaKa08] and consume extremely large size of memory as well as long computation time [CaHN11].

PLC control software has been also targeted of the formal verification, using model checking, taking predefined software modifications into account [SüVZ13], approached over various IEC 61131-3 languages (e.g., [BEHL04, Huuc05]) investigates by means of the model checker. Coupling simulation and formal verification has also been approached to compensate each other (e.g., [BaKa08]).

#### 2.3.2. Regression verification

In the single program verification, the program is examined with respect to the specification. However, formal verification has not been commonly used yet since it is not realistic to expect whole formal specification of the software when it comes to industrial size [StGo08]. Especially in many cases of the industry practices, not even an informal description of the requirements is available, which could be used as a basis for a formal specification [CWUB18a]. Different from the typical formal verification, regression verification [StGo08] focuses on the comparison of two different

versions of the programs and proves that there is no regression during the implemented change with assuming that the previous version of the program is correct. It executes a process of providing deductive evidence (i.e., a proof) showing that the behavior of one software is in a well-specified relation to the other software behavior. That is, new software revision can be proved to be "as correct as of the previous version" rather than to be "correct" absolutely.

The main advantage of regression verification is that no functional or behavioral specification is required besides the old version software. Actually, this verification technique is suitable and reasonable for the aPS evolution, in which the implementation is usually based on the previous version of the system; and benefits of the advantage could be fully realized. The applicability of this methodology on the aPS control software in PLC code in IEC 61131-3 has been shown in [BUVW15]. In this case, regression verification proves that a new revision of the PLC code shows the same behavior as the old revision, and no unintentional behavior is introduced. Additionally, it was also shown that the size of the specification can be reduced to the difference of the versions by applying regression verification in [UUWK16].

Regression verification can be described as a process to assure that the trust earned by a previous version of the system remains through the evolution steps: whether the software is still trustful (partially or entirely) after the evolution. Formal methods might be suggestive to the application engineers of "correctness," and the regression verification, which is a sort of formal methods also might. However, the "correctness" of software in the regression verification scope is different from the one in the view of the defined specification but rather more related to the "still-trustfulness" after some changes in the software. In [CUWB19], the obligation of the regression verification in the sense of the trust preservation during aPS evolution was shown. The sources of trust on regression verification of system software are

- A (formal) analysis of the software against properties trusted to be adequate

- A (formal) analysis on a model of the system (i.e., comprising not only the software but also trusted adequate models of electrical and mechanical parts)

- Executing test runs on the systems

- Simulation executions

- Successful (test) operation

- Long-running successful in-service operation.

Also, the transference of the trust over the evolution could be classified depending on the different level of changes as a) a complete change, b) a partial change outside of the observed range, c) a change including observed range partially, d) a change including all observed range, and e) A change including all observed range. This explicit trust inheritance analysis was to clarify for the

engineers to understand the extent of the trust that regression verification provides and consequently facilitates them to utilize this formal technique for system validation.

#### 2.3.3. Formal specification of the requirement

The formal specification is essential constituent in the context of the formal verification, which is described in logics aiming to model the situations designers/developers/testers encounter in such a way that they can reason about them formally [Gora06]. However, its meaning is not limited only to formal verification but rather spread over the entire engineering processes in this thesis. A system is built to satisfy the user's requirements, which are defined in SWEBOK [IEEE14B] as "software requirement is a property that must be exhibited by something in order to solve some problem in the real world," and SEBOK as "that describe optional, functional, or design-related aspects of a system" [IEEE14B]. The required system characteristics are specified in the specification regarding what and how the system is supposed to behave and what not [BaKa08]. The informality of a requirement description, i.e., specification, may cause ambiguities, which could cause severe and extensive flaws in the following artifacts eventually [HuRy04]. Also, manual verification of real-world problems is not feasible when it comes to the industrial scale. Considering these concerns, the formal specification is required, being defined including formalisms as in [Lams88] "the expression in some formal language at some level of abstraction of a collection of properties some system should satisfy." Nevertheless, it is still observed that no formally described requirement transmitted over the aPS engineering in practice; even the specification is only done oral description without any document. Almost 12% of participants answered they fall into this case in the survey conducted in [VoOc18] and this appeared even worse in the serial machine builders (this data is not published yet).

Specifications are claimed as essential in [Lams88] for almost all of the engineering phases and activities, namely designing, validation, documenting, communicating, reengineering, and reusing. Huth and Ryan also highlight the reason of specification in [HuRy04] as documentation, decreased time-to-market, reuse, through the clear specifications. Especially, Lamsweerde shows the same view with this thesis on the various utilization of the specification depending on the user of it and the usage, which is "One of the problems with the formal specification is that they may concern different classes of consumers having fairly different background, abstractions and languages - clients, domain experts, users, architects, programmers, and tools."

Within the formal verification, one checks that the system description satisfies the formal specifications in terms of mathematical logic mostly regarding the following properties: a) Functional correctness – the system should do what it is supposed to do, b) Safety – something bad (including deadlock) will not happen, and c) Liveness – something good will happen eventually [BaKa08,

HuRy04]. Formal specifications are described in the formal specification language, defined as "textual languages that use basic notions from mathematics (for example, logic, set, sequence) to rigorously and abstractly define software component interfaces and behavior" [IEEE14B]. Since Pnueli suggested the functional properties of reactive systems in temporal logic [Pnue77], these temporal logic expressions have been widely accepted [CHVB18, EiFi18]. The term 'temporal logics' means and is intended to express such that a logic formula is not statically true or false in a model, but its notion of truth might change dynamically depending on the states and the order of events [BaKa08, HuRy04]. Therefore, temporal logics, typically represented by Linear Temporal Logic (LTL) or Computational Tree Logic (CTL), depicts these event occurrence's orders.

# 3. Requirements on a Formal Specification of Reactive System's Control Software Behavior

Today's quality assurance in aPS software engineering is done through testing most of the time. For some software code, however, not all the cases are suitable for testing, e.g., break- or teardown, and also, it is not possible to validate the target code for all the possible test cases most of the time. In practice, many mandatory test cases are rather omitted on purpose, especially after change implementation on the existing code, due to the lack of time. Despite the known power of exhaustiveness of the formal verification, it is not widely used in aPS software engineering, and one of the main reasons is the barrier to the specification. Through the discussion with industry experts, it is learned that the stipulated specification, even in a natural language (informal), often does not exist in the current state of practices (cf. some survey result was shown in Section 2.3.3). To utilize the formal verification, formal specification of the targeted properties is a prerequisite since the verification process requires them as a main subject. Also, aside from the formal verification, formal specification takes an essential role in system validation as an uncontroversial baseline to decide (by a human or by the responsible system automatically) the correct behavior through formalism. Still, engineers in the field like module developers, application engineers, and commissioning personnel have little knowledge or experience in the formal languages [Holz02]. To approach these barriers to achieve formal specifications and ultimately to apply formal verification on the aPS engineering process, requirements are derived below.

Requirements are analyzed from various angles. First, the approach should be feasible to be applied to the technical characteristics of the target system in Section 3.1. Second, the approach should be embeddable into the engineering processes of the system in the context of validation, especially for the software change cases, in Section 3.2. Third, the approach should be usable for the field engineers to be promoted in Section 3.3 for effective effort reduction (i.e., cost and time). All requirements are summarized in Section 3.4.

# 3.1. Requirement considering target system characteristics

APS are basically reactive systems, which adapt the behavior based on the environment as programmed in the control software. In the viewpoint of the functional hierarchy of automation systems, the layer concerned in the approach includes field devices like sensors (as input) and actuators (as output). The control software refers to input, executes its logic, and results in output to control the target process.

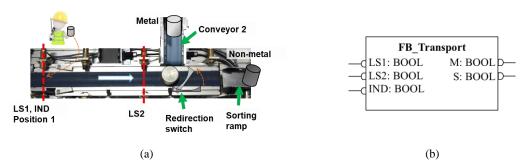

Requirement specification does not have to describe the exact behaviors (or a sequence of them) in detail to specify how operations should consist, but rather have to describe what would be the result of the operations. For example, to describe a function block for multiplying calculation, the requirement specification would describe the result to be the multiplication of the operands as its input, not how the multiplication to be implemented. In the process' subject point of view, the software accepts sensor information (signal) and generates actuator information (signal), which are involved in the information flow. Thus, the developed specification language shall allow presenting the relationship of input and output of the technical system regarding the information flow effectively (R-T1).

The specification information can be classified in either functional description, structural description, or behavioral description as defined in [HSFS17]. The targeted specification shall describe the target software from the functional point of view macroscopically; however, the function is realized by the behaviors representing states and procedures. If the system is non-causal, whose output depends only on the current input, the expected output can be described only using the current input value; however, the calculation is complicated. For a causal system, whose output is decided not only based on the current input but also the past input (or, in other words, the current state of the system), behaviors appear differently depending on the current state and form a sequence of them to realize a specific functionality. Thus, the specification in the developed language shall present the state changes regarding its condition and the results including timing constraints (R-T2). As the target of the specification is not describing specific execution sequence with concrete values but describing states (i.e., transition conditions, results, and timing constraints) and their procedures for general behavior properties, the specification shall present the state in abstracted value ranges (R-T3).

Industrial processes can be classified as continuous (including batch) or discrete. In the continuous process, although the behavior changes over the process, it is not easy to divide into separate states clearly due to its continuous change of the material's state. Therefore, stopping the process, returning the system status back to a certain status, and resuming it cannot be simply done. Rather, the process should be handled as a whole. Contrastively, a discrete process can be separated into apparently divided behavioral steps, recognizing exact input and generating corresponding output. Since it is targeted to verify the state-based behavior regarding the input and output signals, the target of the specification shall be the discrete event processes (R-T4).

The control software of the targeted technical system is loaded and executed in PLC. Instead of control circuits consisting of relays, switches, and clocks, PLC allows programmable logic and input/output interfaces [Hans15]. PLC operates in a cyclic-manner in which a procedure to execute

the control code repeats at every certain time. Each cycle consists of scanning values (input), execution, and updating values (output), so the unit of the input recognition and output change cycles (cf. Section 2.1.2). Thus, the specification in the developed specification language shall be capable of the cyclic execution representation (R-T5). Also, IEC 61131-3 is the standard language to program the PLC software and is applied throughout the production automation industries [VFST15]. Thus, the specification language shall be compatible with the software in IEC 61131-3 as well as its execution (R-T6). In this way, common library functions do not have to be described regarding their detailed behavior when they are used within the description, but rather could be used just as they are (as assumed that no fault exists in the library functions); using the common library functions with the description, therefore, will provide both description efficiency and readability.

## 3.2. Requirements considering engineering processes of aPS

A technical system realizing its corresponding technical process is developed throughout aPS engineering processes. As a designed-to-order system and also for serial machines (which means a number of machines in a type), the aPS engineering process goes through specific engineering methods depending on the own requirements and objectives of the system or the type of the system. Nevertheless, a general engineering life cycle can be defined as described in Section 2.2 (Figure 5). Over the engineering steps, system requirement specification is to be generated and used. In this section, the requirements regarding the engineering activities related to the requirement specification are described.

Control software is more promoted to consist of module libraries to speed up the development and validation [VFST15], developed by module developers and integrated by the application engineers into an application project [VFND18]. When a module is developed for the first time for new behavior, a behavior specification grounded on the customer requirement would be delivered to module developers or created by them interpreting the requirement intention to develop the software [VFND18]. Then, the module is developed in the company's convention programming language, and an application engineer is supposed to build up the desired project out of the modules inserting glue codes [KBSK10].

The developed software module is to be validated. The correctness of the behavior is determined based on the previously defined specification regarding how it is supposed to behave to the expected input sequences by testing and verification. A formal specification language is required over the aPS engineering processes to describe requirement as the most important prerequisite of all engineering activities (R-E1). That is, the characteristics of the expected output sequences are

defined according to the input (or input sequence) sorts. Thus, the specification shall allow describing the input/output trace characteristics of modules, and this also holds in the engineering point of view. In this way, the changed part or behavior, which is mainly aimed in this work, can be described. As a prevalent validation method, applicability to the testing would also be beneficial to the current practices right away. In the form of model-based testing, the test cases shall be instantiated easily from the specification (R-E2). For sure, the specification in the developed formal approach would be a form that a model checker can interpret and process since the approach also targets the specification to apply formal verification not only to document requirements (cf. [Weig21]). Through the verification, conformance of the specification is checked. In case of any proof failure, a counterexample exists, and this could be fed back to the engineers for further debugging. Therefore, the approach shall provide a way for automation engineers to use the verification result effectively for further debugging (R-E3).

The completed developed project is delivered to the real production environment and executed for the test run during the commissioning stage by the on-site start-up technician [VFFU17]. The personnel (i.e., commissioner) adjusts system parts (hardware and software) to accustom the integrated plant to the best fitting condition. In the meantime, some parts of the software are discovered to be revised or reconfigured. Although the best way to make any change on the software would be analyzing the inappropriate behavior, re-designing, re-implementing, and validating by the development department, the commissioning stage often lacks of time so this entire re-engineering process is not possible to be conducted [Voge09]. An optimized and ideal way to solve it is that the start-up technician implements the change, validate it regarding the correctness of the behavior and side-effect freeness as much as possible, and document it delivering to the corresponding office (then the further proof would be done within the development department). The same requirement as R-E2 and R-E3 applies here for the validation process. However, this organized procedure is still lacking in practices, appearing as just individual development forms; thus, it threatens the following maintenance and update efficiency by generating unauthorized variants and versions [VFFU17].

During the operation, significant signals within the system are supposed to be monitored to detect unexpected behaviors or unconsidered conditions during the requirement specification stage. Monitoring functions are often related to a specific piece of hardware and are directly connected to functions to obtain information about the hardware behavior by tapping from inputs and outputs, and to invoke alarms if necessary. In case of undesired hardware behavior, warnings are given to the system. It is of utmost importance that the monitoring functions work as intended and detect all errors and unknown states of the system to allow the system to give appropriate warnings,

handle these errors or bring the system into a safe state by performing an emergency stop to prevent further damage. As the monitoring block conducts a role of dynamic validation, the most efficient way is to generate the code directly and automatically from the specification to conduct the monitoring function. Thus, the specification shall be in the suitable form to generate the monitoring block, and the generation method is to be developed (R-E4).

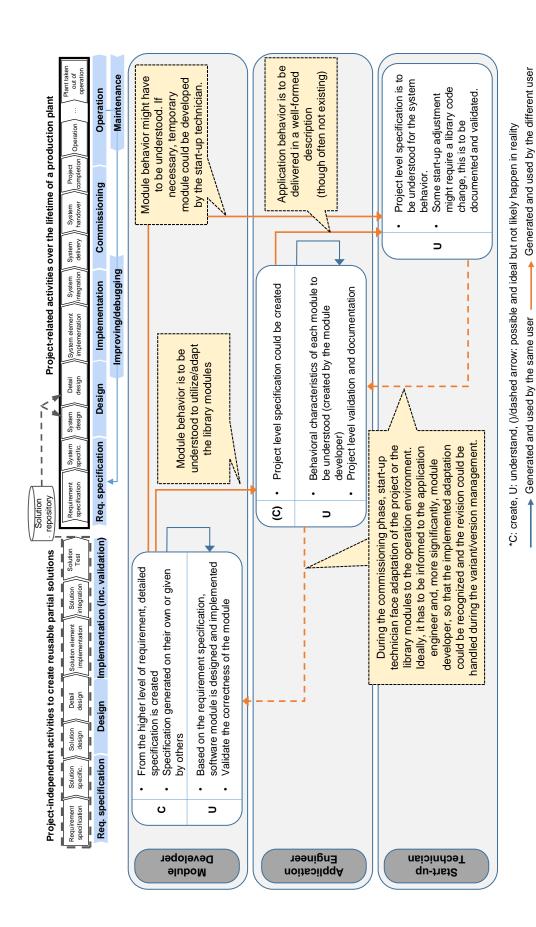

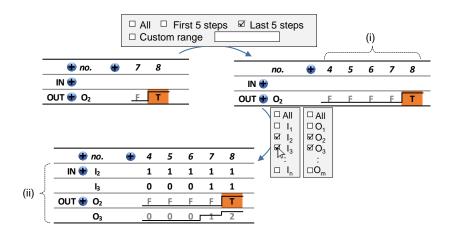

Over the aPS' lifecycle, changes are caused by various reasons unavoidably [VFST15], e.g., to fix some bugs, to implement additional functionality, or to come up with some technology trend. Thus, the aPS control software often has to be adapted to the changed requirements for these reasons. The change has to be carefully implemented not only to realize the intended change effect but also not to introduce any side effect. Over this change implementation activity in the maintenance stage including functionality updates, debugging, and behavior improvement, intended change specification would be conducted and these shall also be supported by the specification and validation activities similarly. What is different from the initial development process is that not the entire part of the system is to be checked, but the change-related part is the scope of the validation, which is especially effective for small changes. Nevertheless, the unchanged part of the system also should be validated regarding the side effect caused by the change. Therefore, the changed part should be described clearly and formally at best to apply validations methods systematically, e.g., test case generation, model validation, or formal verification (R-E5). Overall, documenting the software behavior with various objectives and utilizing them should be easily embedded as a method of each engineering process and different users by exchanging them (R-E6, cf. Figure 7).

# 3.3. Requirements considering the users' point of view

For all descriptions necessary over the engineering processes so far, other specification forms or languages, e.g., a path-time diagram, might work theoretically since it can describe the multiple signals, their value sequences, and synchronization of them. Although it is a very intuitive graphical representation of signals, it is effective with a fewer number of signals and time sequences to read it at a glance. Actually, one of the machine and plant manufacturing company expressed to reject timing diagram explicitly in an interview due to its scalability and also its additional notations for automation engineers to learn and familiar with, but proposed test tables as a more preferable and already familiarized means instead. When the value ranges are wider, or for some aggregately representable values, graphical notation has some limitations. Also, as a graphical notation, it is not easy to export and import the information systematically and automatically. Therefore, the approach shall support the systematic handling of the information with structured data representation from usable practices and, correspondingly, a software tool shall enable various users to utilize the approach (R-U1). This premises to ease the applications of the approach by

Figure 7: Activities and users of the specification over the engineering process – depicting the information exchange (arrows)

various type of users (i.e., module developers, application engineers, as well as the commissioning/start-up personnel, as stated).

Thus, the approach shall be accessible regarding its usage (R-U2), namely to be understandable (R-U2), to enable to create (R-U3), and to be learnable (R-U4). Considering the applicability to the industrial cases, scalability is another factor to be evaluated (R-U5). Ultimately, the developed method is expected to satisfy the user of the approach so that they would like to use it for the intended purpose with minimum resistance (R-U6).

### 3.4. Summary of requirement

In short, the overall requirement could be summarized as "the specification language shall enable automation engineers to express the requirement and the behavior of the system in a formal way without knowing the conventional formal logic to specify and understand small changes." Detailed requirements and its description is given in Table 2.

Table 2: Summary of the requirements

| Requirement ID | Requirement description                                                                                                                                                                       |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| R-T1           | The developed specification language shall allow presenting the relationship of input and output of the technical system regarding the information flow effectively                           |  |

| R-T2           | The specification in the developed language shall present the state changes regarding its condition and the results, including timing constraints.                                            |  |

| R-T3           | The specification shall present the state with the abstracted value range.                                                                                                                    |  |

| R-T4           | The target of the specification shall be the discrete event processes.                                                                                                                        |  |

| R-T5           | The specification in the developed language shall allow the cyclic execution representation.                                                                                                  |  |

| R-T6           | The specification language shall be compatible of the software in IEC 61131-3 as well as its execution.                                                                                       |  |

| R-E1           | Formal specification language to be used over the aPS engineering process shall be developed.                                                                                                 |  |

| R-E2           | The test cases shall be instantiated from the specification.                                                                                                                                  |  |

| R-E3           | The approach shall support for implementation debugging with respect to the specification.                                                                                                    |  |

| R-E4           | The specification shall be a suitable form to generate the monitoring block.                                                                                                                  |  |

| R-E5           | The changed part should be described clearly and formally at best to apply validations methods systematically.                                                                                |  |

| R-E6           | Documenting the software behavior with various objectives and utilizing them should be easily embedded as a method of each engineering process and different users by exchanging them.        |  |

| R-U1           | The approach shall support the systematic handling of the information through a tool with structured data representation.                                                                     |  |

| R-U2           | The approach shall be understandable, meaning the typical automation engineers can understand (after reasonable training) by reading the specification in GTT.                                |  |

| R-U3           | The approach shall support creation of specification, meaning the typical automation engineers can create the specification in GTT (after reasonable training).                               |  |

| R-U4           | The approach shall be learnable, meaning that it requires reasonable time and effort from the typical automation engineers to utilize the language regarding reading and creating activities. |  |

| R-U5           | The approach shall be usable for the scaled behavior description.                                                                                                                             |  |

| R-U6           | The approach shall be satisfactory, meaning that the users of it (i.e., automation engineers) would be willing to use it.                                                                     |  |

## 4. State of the art

There have been approaches introduced that could be applied to satisfy the requirements presented in the previous chapter. To give an overview, specification approaches that are targeted to be applied over the aPS control software engineering processes are discussed in this chapter. Not only the basic characteristics of the specification approach targeting technical aspects of the aPS (T1 – T6) but also the engineering viewpoint (E1 – E6) and usability aspects (U1 – U6) are discussed (Section 4.1). As one of the major concepts of the thesis, monitoring techniques which are not connected to the formal specification approach is separately reviewed (Section 4.2). The usability aspect focused in Section 4.1 is more general; as one other primary requirement of the approach introduced in this thesis is usability to the automation engineers, research and evaluation approaches concerning this point are discussed (Section 4.3). The conclusive research gap is derived at the end of this chapter.

## 4.1. Formal specifications behavior: language and utilization

Formal modeling and verification techniques are originally created in the pure computer science field, and aPS behavior verification is a comparably recent research topic [HLLT06]. Since initiated by the early works such as [MPBC92], verifying PLC software has been actively researched (e.g., up to [ShVy20]), motivated by the fact that software engineering techniques in automation engineering today are not sufficient to thoroughly assure the required level of quality efficiently along with the system operation duration with shortened evolution cycles. Formal methods provide proofs that the implemented steps are correctly conducted with respect to the specification [Berg82]. Behavioral specifications define how the system is supposed to process, i.e., requirements, and the system model is verified regarding its conformance to the specification in the formal verification. In this section, formal specification languages introduced for or utilized in automation system engineering are reviewed and compared with respect to the requirements presented in the previous chapter (Chapter 3). Note that mature languages with more utilization methods with respect to the requirements were selected here among various newly introduced languages. Namely, test case generation, specification inferencing, and monitoring/debugging approaches will be focused for each formal specification language.

#### 4.1.1. Text based temporal logics

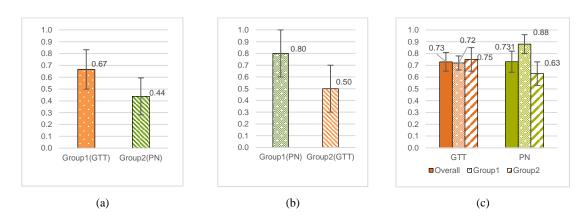

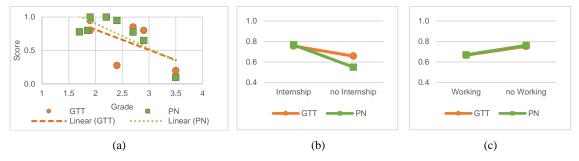

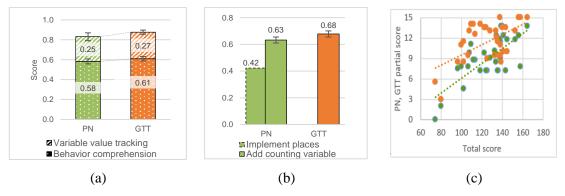

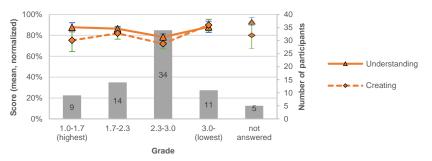

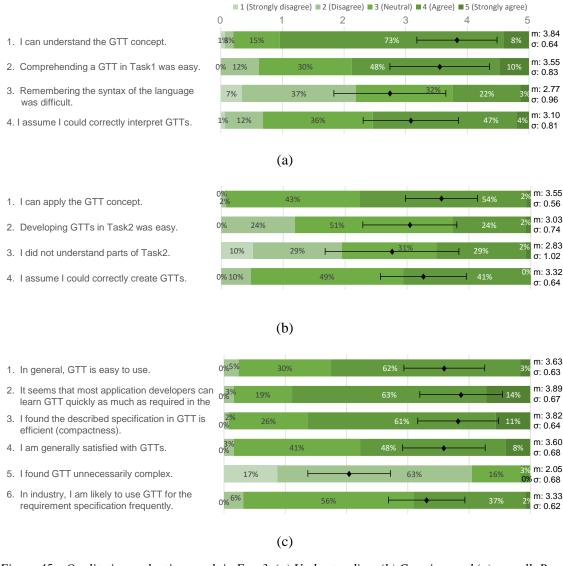

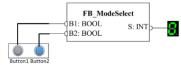

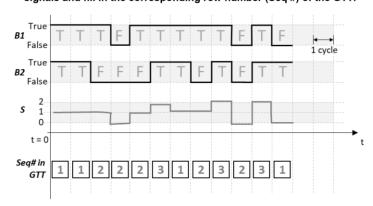

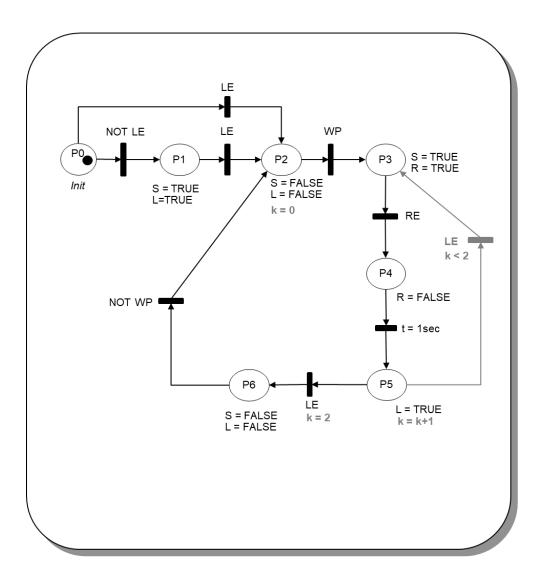

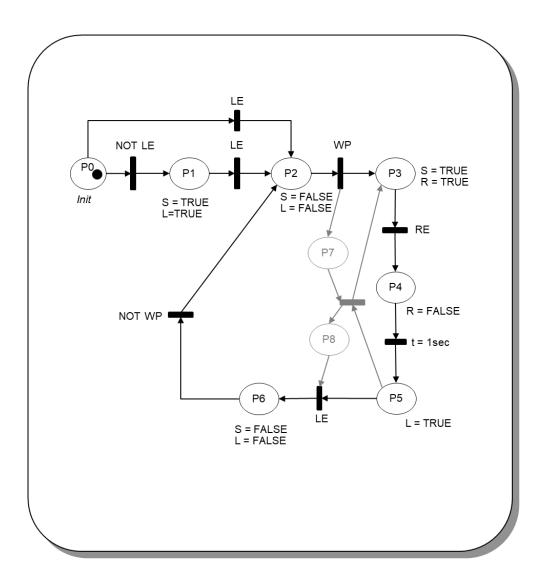

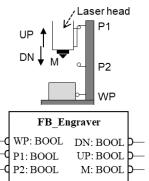

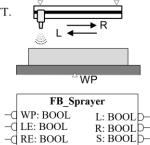

Pnueli suggested the functional properties of reactive systems in temporal logic [Pnue77] as almost the earliest one, and these temporal logic expressions have been widely accepted [CHVB18][EiFi18] by providing the expressions for sequences or order (causality) of the states