# A Hardware Benchmarking Platform for the Standardization of Authenticated Encryption Algorithms

# **Michael Theodor Tempelmeier**

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs (Dr.-Ing.)**

genehmigten Dissertation.

#### Vorsitzender:

Apl. Prof. Dr.-Ing. Walter Stechele

#### Prüfer der Dissertation:

- 1. Prof. Dr.-Ing. Georg Sigl

- 2. Assoc. Prof. Jens-Peter Kaps, Ph.D. George Mason University

Die Dissertation wurde am 11.01.2021 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 03.05.2021 angenommen.

# Quidquid agis, prudenter agas et respice finem!

```

with Ada.Text_IO;

procedure Thanks is

begin

Ada.Text_IO.Put_Line("Thanks, Dad!");

end Thanks;

```

In memory of Prof. Dr. Theodor Tempelmeier (1952–2019)

# **Abstract**

This thesis describes and solves the challenges of evaluating and benchmarking cryptographic algorithms during the standardization process of Authenticated Encryption with Associated Data (AEAD). Candidates of the CAESAR competition (Competition for Authenticated Encryption: Security, Applicability, and Robustness) serve as the data basis. AEAD algorithms combine two properties: they can independently authenticate and encrypt/decrypt data. These properties are especially important for network protocols, where parts of the data, e.g. the header information, must be protected from manipulation, but at the same time must be readable, and thus must not be encrypted; other data, however, should not be readable during transmission and thus must be encrypted.

This work focuses on hardware implementations on FPGAs. In contrast to software implementations, which are usually embedded in a larger software context, hardware implementations often do not provide a uniform interface, since they are often embedded in application-specific devices. This hinders a fair comparison because different implementations are measured against different requirements. For this reason, this thesis first motivates a uniform interface for hardware implementations. At the same time, it critically examines the current implementations of such an interface and proposes an improved version.

In the course of this work, the previous practice of evaluating cryptographic hardware implementations during the CAESAR competition is also critically examined: Due to the lack of a clear evaluation process, implementation flaws remained undetected until late in the competition. This is demonstrated by means of a specification problem and an implementation problem.

To overcome these problems, a low-cost, developer-friendly evaluation platform is developed. It consists of a Xilinx PYNQ-board. The platform uses a common hardware interface and can be used for pure functional testing as well as for advanced performance analysis. Due to its low price and ease of use, it can be used by any hardware developer. This results in two advantages: First, the quality of the implementations increases, since every developer is both financially and technically able to use this platform to test his or her implementation against a uniform set of tests; second, the results are comparable since every implementation is measured against the same assumptions.

Subsequently, this platform is used to evaluate all the finalists and a large part of the prefinalists of the CAESAR competition. Here, functionality; specification conformance; re-

source, power and energy consumption; and runtime are evaluated. It is shown that the winners in the field of "lightweight applications" do not necessarily have "lightweight" properties and that, according to the measured data, other eliminated candidates should have been considered as finalists.

Furthermore, this work presents an alternative for the uniform hardware interface. It turns out that for very specific hardware software co-design applications, the presented unified hardware interface is suboptimal. Nevertheless, for the majority of applications the advantages of a uniform hardware interface outweigh. This is demonstrated on the basis of two selected examples: "Physical Unclonable Functions" and "Network-on-Chip" applications. In both cases the above mentioned implementations are integrated in other scientific research areas and the uniform hardware interface allows for a fast evaluation of a large number of different implementations.

Finally, this work results in a set of rules for comparing and creating cryptographic algorithms under the aspects of good hardware optimizability and using a general hardware interface. These rules are designed to fit the current standardization of Lightweight Crypography (LWC) by the National Institute of Standards and Technology (NIST).

# Zusammenfassung

Diese Arbeit beschreibt und löst die Herausforderungen bei der Evaluierung und Leistungsbewertung von kryptographischen Algorithmen der Klasse "Authenticated Encryption with Assosiated Data (AEAD)", die typischerweise während der Standardisierung auftreten. Als Datenbasis dienen hierbei Kandidaten des CAESAR-Wettbewerbs ("Competition for Authenticated Encryption: Security, Applicability and Robustness"). AEAD Algorithmen vereinen dabei zwei Eigenschaften: Sie können unabhängig voneinander Daten verschlüsseln, bzw. entschlüsseln und authentifizieren. Diese Eigenschaften sind insbesondere bei Netzwerkprotokollen wichtig, da hier Teile der Daten, z.B. Metainformationen, vor Manipulation geschützt werden müssen, aber gleichzeitig im Klartext lesbar sein müssen; andere Daten hingegen sollen während der Übertragung nicht lesbar sein.

Diese Arbeit fokussiert sich auf Hardwareimplementierung auf Basis von FPGAs. Im Gegensatz zu Softwareimplementierungen, die meistens in einem größeren Softwarekontext eingebettet sind, ist bei Hardwareimplementierungen häufig kein einheitliches Interface vorgesehen, da sie oftmals als eigenständige, anwendungsspezifischen Bausteine bestehen. Aus diesem Grund wird in dieser Arbeit zuerst ein einheitliches Interface für Hardwareimplementierungen motiviert. Gleichzeitig wird sich kritisch mit dessen bisheriger Implementierung auseinandergesetzt und eine verbesserte Version des Selbigen vorgeschlagen.

In diesem Zuge wird sich auch kritisch mit der bisherigen Praxis der Bewertung von kryptographischen Hardwareimplementierungen während des CAESAR-Wettbewerbs befasst. Durch das Fehlen von klaren Bewertungsprozessen blieben Implementierungsprobleme lange Zeit unentdeckt. Dies wird Anhand eines Spezifizierungs- und eines Implementierungsproblem demonstriert.

Als Lösung dieser Probleme wird hierzu eine kostengünstige, entwicklerfreundliche Evaluierungsplattform entwickelt. Sie basiert auf einem Xilinx PYNQ-Board. Sie nutzt eine einheitliche Hardwareschnittstelle und kann sowohl zum reinen Funktionstest als auch zur erweiterten Leistungsanalyse verwendet werden. Wegen des günstigen Preises und der einfachen Bedienbarkeit kann sie von jedem Hardware-Entwickler eingesetzt werden. Dadurch entstehen zwei Vorteile: Erstens steigt die Qualität der Implementierungen, da jeder Entwickler sowohl finanziell, als auch technisch in der Lage ist, diese Plattform zu benutzen und somit frühzeitig Fehler im Design erkennen zu können; zweitens verbessert sich die Vergleichbarkeit der Ergebnisse, da jede Implementierung anhand der gleichen Voraussetzungen gemessen wird.

Anschließend wird diese Plattform genutzt um alle Finalisten und einen Großteil der Vorfinalisten des CAESAR-Wettbewerbs zu bewerten. Hierbei wird sowohl die Funktionalität, die Spezifikationskonformität, der Ressourcen-, Leistungs- und Energieverbrauch als auch die Laufzeit evaluiert. Dabei zeigt sich, dass die Gewinner im Bereich "lightweight applications" nicht zwangsweise "lightweight" Eigenschaften besitzen und dass gemäß der gemessenen Daten andere, ausgeschiedene Kandidaten als Finalisten berücksichtigt hätten werden müssen.

Weiterhin präsentiert diese Arbeit eine Alternative für die einheitliche Hardwareschnittstelle. Es zeigt sich, dass für sehr spezielle Hardware-Software-Codesign-Anwendungen, die präsentierte einheitliche Hardwareschnittstelle suboptimal ist. Trotzdem überwiegen für das Gros der Anwendungen die Vorteile einer einheitlichen Hardwareschnittstelle. Dies wird nochmals anhand von zwei ausgewählten Beispielen demonstriert, wobei die oben genannten Implementierungen in anderen wissenschaftlichen Kontexten ("Physical Unclonable Functions" und "Network-on-Chip"-Anwendungen) eingebunden werden. Die verwendete Hardwareschnittstelle erlaubt dabei eine schnelle Evaluation einer Vielzahl von verschiedenen Implementierungsvarianten.

Abschließend wird basierend auf den Ergebnissen dieser Arbeit eine Handreiche für das Vergleichen und das Erstellen von kryptographischen Algorithmen unter den Gesichtspunkten einer guten Hardwareoptimierbarkeit sowie unter Verwendung einer allgemeinen Hardwareschnittstelle gegeben. Diese Handreiche ist darauf ausgelegt bei der aktuellen Standardisierung von "leightweight Authenticated Encryption with Assosiated Data" des National Institute of Standards and Technology (NIST) Verwendung zu finden.

# **Contents**

| 1 | Intro             | oduction                                                                                                                                                                                                                                                                                                             | 11             |

|---|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2 | 2.1<br>2.2<br>2.3 | Authenticated Encryption with Associated Data Competition for Authenticated Encryption: Security, Applicability, and Robustness (CAESAR)  2.2.1 Functional Requirements for Submissions  2.2.2 Process for Determining the Final Portfolio  2.2.3 Examined Ciphers  New Generation of Reconfigurable System-on-Chips | 17<br>17<br>18 |

| 3 | Cha               | Ilenges in Evaluating Cryptographic Competitions                                                                                                                                                                                                                                                                     | 29             |

|   | 3.1               | Review Process Flaws at the Example of CAESAR                                                                                                                                                                                                                                                                        | 29             |

|   |                   | 3.1.1 Algorithmic or Software Flaws                                                                                                                                                                                                                                                                                  |                |

|   |                   | 3.1.2 Hardware Flaws                                                                                                                                                                                                                                                                                                 |                |

|   | 3.2               | The Role of the Interface                                                                                                                                                                                                                                                                                            |                |

|   |                   | 3.2.1 The Example of Icepole                                                                                                                                                                                                                                                                                         |                |

|   |                   | 3.2.2 Is it fair?                                                                                                                                                                                                                                                                                                    | 38             |

| 4 | Hard              | dware APIs                                                                                                                                                                                                                                                                                                           | 41             |

|   | 4.1               | The CAESAR-API                                                                                                                                                                                                                                                                                                       | 41             |

|   | 4.2               | The LWC-API                                                                                                                                                                                                                                                                                                          |                |

|   | 4.3               | Comparison and Evaluation of the APIs                                                                                                                                                                                                                                                                                |                |

|   |                   | 4.3.1 API Compliant Development Packages                                                                                                                                                                                                                                                                             |                |

|   |                   | 4.3.2 Resource Analysis of Lightweight APIs                                                                                                                                                                                                                                                                          |                |

|   |                   | 4.3.3 Exemplary Analysis of Published Implementations                                                                                                                                                                                                                                                                |                |

|   | 4.4               | 4.3.4 Tweaking the Development Package                                                                                                                                                                                                                                                                               |                |

|   | 4.4               | Guilliary                                                                                                                                                                                                                                                                                                            | 50             |

| 5 | A Fr              | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                | 61             |

|   | 5.1               | Functional Verification using Simulations                                                                                                                                                                                                                                                                            |                |

|   | 5.2               | Functional Verification using Hardware Testbeds                                                                                                                                                                                                                                                                      |                |

|   |                   | 5.2.1 System Design                                                                                                                                                                                                                                                                                                  |                |

|   |                   | 5.2.2 Validation and Testing                                                                                                                                                                                                                                                                                         |                |

|   | <b>-</b> ^        | 5.2.3 Functional Behavior                                                                                                                                                                                                                                                                                            |                |

|   | 5.3               | Resource Implications                                                                                                                                                                                                                                                                                                | 08             |

| 6   | Ben   | chmarking of CAESAR-Implementations                                | 73  |

|-----|-------|--------------------------------------------------------------------|-----|

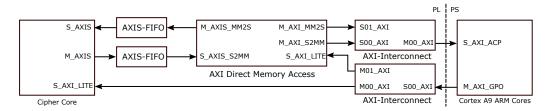

|     | 6.1   | Hardware Architecture                                              | 74  |

|     | 6.2   | Measurement Setup                                                  | 75  |

|     |       | 6.2.1 Runtime                                                      |     |

|     |       | 6.2.2 Power and Energy                                             |     |

|     | 6.3   | Results                                                            |     |

|     |       | 6.3.1 Synthesis                                                    |     |

|     |       | 6.3.2 Runtime                                                      |     |

|     |       | 6.3.3 Power Consumption                                            |     |

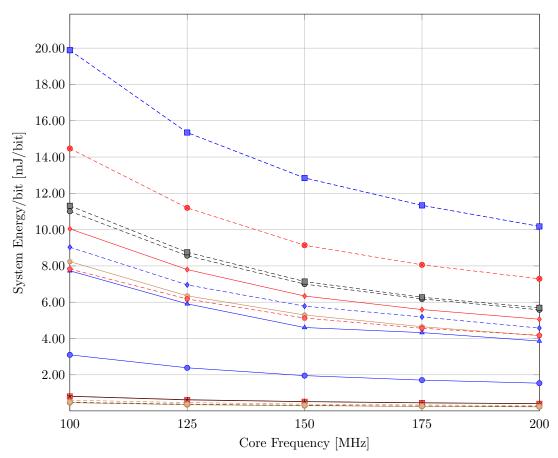

|     | 6.4   | 6.3.4 Energy Consumption                                           |     |

|     | 6.4   | Consequences for Ciphers                                           | 91  |

| 7   | Cas   | e Studies                                                          | 99  |

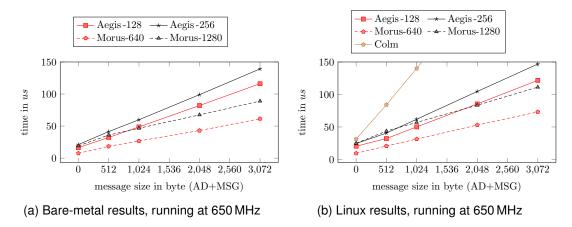

|     | 7.1   | Enhancing Authenticated Encryption with Hardware Software Codesign |     |

|     |       | Techniques                                                         | 99  |

|     |       | 7.1.1 Setup                                                        |     |

|     | 7.0   | 7.1.2 Results                                                      |     |

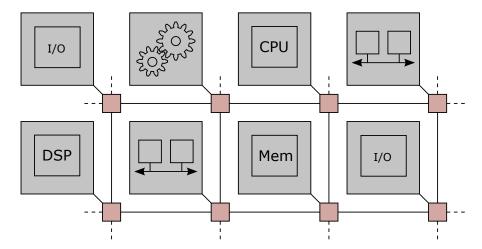

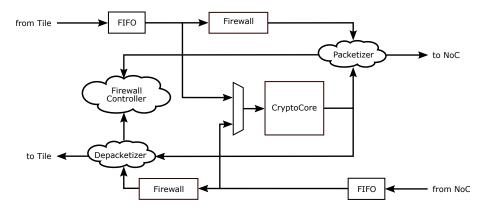

|     | 7.2   | Securing Network-on-Chip Applications                              |     |

|     |       | <ul><li>7.2.1 Multiprocessor Systems on Chips</li></ul>            |     |

|     |       | 7.2.3 CAESAR Network Interface Reconfiguration                     |     |

|     |       | 7.2.4 Results                                                      |     |

|     | 7.3   | Authenticated Encryption based on Physical Unclonable Functions    |     |

|     | , .0  | 7.3.1 Physical Unclonable Function                                 |     |

|     |       | 7.3.2 Hardware Setup                                               |     |

|     |       | 7.3.3 Results                                                      | 109 |

| 8   | The   | Implementer's Point of View                                        | 111 |

| 9   | Con   | clusion                                                            | 115 |

| Lis | t of  | Figures                                                            | 117 |

| Lis | st of | Tables                                                             | 119 |

| Ac  | rony  | ms                                                                 | 121 |

| Bil | olioa | raphy                                                              | 125 |

# 1 Introduction

When in 1997 the National Institute of Standards and Technology (NIST) initiated a public competition to determine which block cipher algorithm should become the Advanced Encryption Standard (AES) [62], it broke new ground, since all previous cryptographic standards were determined behind closed doors [7].

In 2000, two similar research projects were launched: NESSIE (New European Schemes for Signatures, Integrity and Encryption) by the European Commission [50] and CRYPTREC (Cryptography Research and Evaluation Committee) by the Japanese government [15]. They are comparable in many respects to the AES competition run by NIST. Therefore, there were no new groundbreaking findings during these competitions. However, they strengthened the idea of publicly available cryptographic competitions.

Thus, subsequent contests for cryptographic standards became more and more popular, with more algorithms submitted each time:

In 2004, another European project, called eSTREAM (ECRYPT Stream Cipher Project), was launched by the European Network of Excellence in Cryptology (ECRYPT) [49]. In contrast to the previous projects, eSTREAM focused on stream ciphers.

In 2007, NIST announced its second cryptographic competition: the SHA3-hashing competition. While other projects like NESSIE already included hashing to their call for submissions, NIST chose to have a dedicated competition for hashing. Again, this competition formed a new standard: the SHA-3 standard [20].

One of the latest concluded contests is CAESAR (Competition for Authenticated Encryption: Security, Applicability, and Robustness) [12], which was announced in 2013 and ended in February 2019. Its goal was to determine a portfolio of authenticated ciphers that offer advantages over AES in Galois Counter Mode (AES-GCM) in terms of performance, security, and ease of correct implementation. Throughout the contests, candidates were evaluated based on their security, efficiency in software, efficiency in hardware, and flexibility. In contrast to the other competition, CAESAR did not report to any governmental agency.

There are more competitions that are still ongoing: the NIST Post-quantum Cryptography (PQC) project [61], started in 2016, and the NIST Lightweight Crypography (LWC) project [60], started in 2018. While the first focuses on the new field of post-quantum cryp-

tography, the latter combines very well known cryptographic primitives to form lightweight primitives which are suitable for the Internet-of-Things (IoT) era. The latter can also be seen as a successor of CAESAR, as the specification of the encryption primitives is a subset of CAESAR's.

In this thesis, we focus on hardware implementations of CAESAR and LWC candidates. One characteristic of both projects is the volume of different submissions compared to the AES competition: In 1998, there were only 15 candidates competing for the new Advanced Encryption Standard. Furthermore, 13 of them were based on well known structures like Feistel Networks, or substitution-permutation networks, and only two of them were of dedicated character. This made a fast decision possible, so that in 1999 five finalists could be presented. One year later, Rijndael was chosen to become the new Advanced Encryption Standard [82].

CAESAR on the other hand had 57 submissions, divided into more than six different categories [1] and the LWC project accepted 56 submissions [60]. This poses a serious challenge for their evaluation. Furthermore, the CAESAR and LWC competition included hardware benchmarking into their evaluation process because hardware implementations gain more and more importance.

Today, high-speed co-processors are used to speed up cryptographic operations on server CPUs, but even desktop CPUs are equipped with AES instruction set extensions. Dedicated Field-programmable gate array (FPGA) or even Application-specific Integrated circuit (ASIC) clusters are used for blockchain operations. More and more memory elements (e.g. hard disks, or RAM) provide an on the fly memory encryption. Lightweight, power and energy optimized implementations are used in IoT devices. Side-channel and fault attack protected implementations are mandatory even for consumer products.

Taken the afore mentioned tremendous number of submissions into account, benchmarking becomes even more challenging because there are now multiple benchmarking dimensions, which must be applied to each submission, like security, software performance on different processors, hardware performance on FPGAs, hardware performance on ASICs, performance in mixed hardware software co-designs, ability for IoT applications, etc.

This thesis addresses the following points and thus contributes to the overall evaluation process:

We will demonstrate that one of the main challenges when benchmarking different

hardware implementations is the used interface. Thus, it is crucial to adopt a common

hardware API for all implementations. However, even a common API is not enough.

We will show that such an API can be misused to "optimize" the synthesis results of

a cipher, but actually only the implementation of the API is improved. Therefore, we

will closely analyze the CAESAR-API in terms of area cost and propose an improved

API, which could be used for the NIST-LWC competition.

- Next, we will motivate the need for an universal hardware testbed by showing that more than expected (official) hardware implementations are functionally incorrect.

- For the functionally correct implementations, we will extend this testbed to allow for benchmarking. We will present benchmarking results in terms of area, throughput, power, and energy consumption.

- We will compare those API compliant, pure hardware results with mixed hardware software implementations and show the advantages of both approaches.

- Finally, we will demonstrate the benefits of a fixed API implementation with an external

and internal interface: Ciphers fully equipped with the API can be easily integrated on

protocol level. We will demonstrate this at the example of a PUF-based IoT protocol.

Having also a common internal interface between the cipher and API implementation

will allow for a seamless integration of the Cipher into custom projects, without the

(communication) overhead of the API. We will demonstrate this at the example of a

NoC router.

Consequently, the thesis is organized as follows:

As preliminaries, we first explain Authenticated Encryption with Associated Data, introduce the "Competition for Authenticated Encryption: Security, Applicability, and Robustness", and present the hardware platform used throughout this thesis in the next chapter.

Having dealt with the preliminaries, we carve out the challenges and problems, when evaluating different hardware implementations in Chapter 3. In Chapter 4, we present and analyze a solution to make different implementations comparable by examining the CAESAR hardware API and present an improved LWC hardware API.

The actual analysis of the ciphers starts in Chapter 5. In this chapter, we focus on the functional behavior. We show, that many implementations are not functional correct. This emphasizes the need of the presented framework. In the next chapter, this framework is extended to allow for performance benchmarking.

Chapter 7 is an excursus to show the applicability of CAESAR ciphers in other research domains. We show how these domains benefit from the common API presented in Chapter 4.

In Chapter 8, we conclude the thesis with a very personal point of view on how things should be done.

### 2 Preliminaries

In the following, we introduce the concepts of Authenticated Encryption with Associated Data, the CAESAR competition, and Systems on Chips, as this thesis heavily relies on these concepts.

#### 2.1 Authenticated Encryption with Associated Data

Secure communication is based on two main principles: *Secrecy* and *Authenticity*. Secrecy, the oldest cryptographic principle, ensures that a message can only be read (decrypted) by the appropriate recipient. However, in many cases secrecy is not the (only) concern. It is at least as important to verify that a message has not been altered intentionally or unintentionally during its transmission.

Therefore, cryptographic protocols rely on authentication and encryption to provide confidentiality, as well as integrity and authenticity. Traditionally, a Message Authentication Code (MAC) and an encryption scheme were combined at protocol level:

- *MAC-and-Encrypt*, where a message is independently encrypted and authenticated. This scheme is used amongst others by SSH [55].

- *MAC-then-Encrypt*, where a message is first authenticated and then together with the resulting MAC encrypted. This scheme is used amongst others by SSL/TLS [69].

- Encrypt-then-MAC, where a message is first encrypted and then the encrypted message is authenticated. This scheme is the recommended mode to combine an encryption algorithm with a MAC, as it is the only one that can provide indistinguishability under adaptive chosen ciphertext attacks (IND-CCA), non-malleability under chosen plaintext attacks (NM-CPA), and the integrity of ciphertexts (INT-CTXT) [5]. It is used amongst others in IPsec [52], but there are extensions for TLS and SSHv2 to use this mode [30].

While these composition approaches have obvious advantages in terms of re-usability, they suffer from being neither efficient nor always secure and prone to implementation errors [6,

5, 53]. Additionally, a key separation is needed, as MAC and encryption are two distinct cryptographic primitives and therefore need two distinct keys [51]. Otherwise the above mentioned security goals can not be guaranteed [5]. A more modern approach is to consider Authenticated Encryption (AE) as a cryptographic building block on its own, rather than as the mere combination of two. For this reason and others, the NIST-recommended modes like Counter with CBC-MAC (CCM) [18] and AES-GCM [19], as well as the ISO standard AES in Offset Codebook 2 Mode (AES-OCB2) [71] are used.

In the following the term AE is used for algorithms that combine both principles into one single algorithm. Typical use cases for AE are (embedded) software updates. In this scenario, the update is confidential, as it involves Intellectual Property (IP) and at the same time, it must be ensured that it is not altered.

In addition to authentication and encryption, several protocols require checking the integrity and authenticity of so called Associated Data (AD), which are public data that must be authenticated by the receiver, but do not contain confidential information. The most prominent example of AD is the header of a network protocol: While the header must not be encrypted, as it must be readable by the network router, it must be protected in terms of integrity and authenticity. This leads to Authenticated Encryption with Associated Data (AEAD) as a building block. The most recent example for AEAD is TLS-1.3 which only allows AE algorithms and purged all composition-based approaches, as they are considered legacy [68].

Formally, an AEAD scheme is defined as follows [1]:

**Definition 1** Let  $k, \nu, t \geq 1$ ,  $K \in \{0,1\}^k$  denote a secret key,  $N \in \{0,1\}^\nu$  a nonce,  $T \in \{0,1\}^t$  an authentication tag,  $P \in \{0,1\}^*$  a plaintext,  $AD \in \{0,1\}^*$  associated data, and  $C \in \{0,1\}^*$  a ciphertext. An AEAD is a triple  $\Pi = (\mathcal{K}, \mathcal{E}, \mathcal{D})$ , with a key-generation procedure  $\mathcal{K}$  that returns a randomly K, an encryption algorithm  $\mathcal{E}_K(N,AD,P)$ , and a decryption algorithm  $\mathcal{D}_K(N,AD,C,T)$ , where  $\mathcal{E}$  outputs a pair (C,T), and  $\mathcal{D}$  outputs either the plaintext P or the void symbol  $\bot$  if the tag is invalid:

$$\mathcal{E}: \{0,1\}^k \times \{0,1\}^{\nu} \times \{0,1\}^* \times \{0,1\}^* \qquad \to \{0,1\}^* \times \{0,1\}^t \qquad \textbf{(2.1)}$$

$$\mathcal{D}: \{0,1\}^k \times \{0,1\}^{\nu} \times \{0,1\}^* \times \{0,1\}^* \times \{0,1\}^t \to \{0,1\}^* \cup \{\bot\}$$

(2.2)

The formal definition of the decryption in Equation (2.2) is often relaxed for implementations: As the tag verification takes place after the complete decryption and as it is often infeasible to store the entire decrypted plaintext, the plaintext is released regardless whether the tag is valid or not. There is only a flag set to indicate the status of the verification and appropriate actions must be taken on system or protocol level.

# 2.2 Competition for Authenticated Encryption: Security, Applicability, and Robustness

In the past few years, some concerns about the performance and ease of side-channel secure implementations of AES-GCM, which had been the defacto standard for AEAD for many years, were raised. As a result, the Competition for Authenticated Encryption: Security, Applicability, and Robustness (CAESAR) was started with the goal to

"identify a portfolio of authenticated ciphers that (1) offer advantages over AES-GCM and (2) are suitable for widespread adoption". [12]

Although funded by NIST grant 60NANB12D261 and supported by the University of Illinois at Chicago [7], it was organized by "the international cryptologic research community", a loose committee of 18 international researchers from eleven different countries. Secretary of the committee and most prominent spokesman was D. J. Bernstein [12].

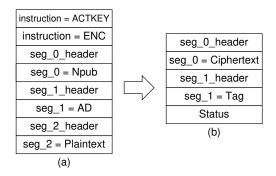

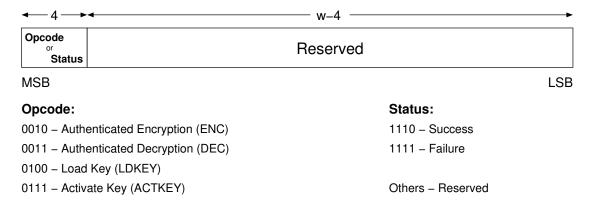

#### 2.2.1 Functional Requirements for Submissions

The call for submissions [12] had very limited requirements: The submissions must support AEAD, that provides integrity for the plaintext, the Associated Data, public message number, and the secret message number, as well as confidentiality for the plaintext and the secret message number. Both message numbers may impose a single-usage.

The plaintext and the secret message number had to be recoverable from the ciphertext, AD, public message number, and key. The submissions had to support a minimum length of  $2^{16}$  bytes for plaintext/ciphertext and AD. However, designers were encouraged not to limit the maximum length. For practical reasons, most ciphers were designed to support maximum lengths up to  $2^{64}$  bytes. The support for public and secret message numbers was optional. There are no prerequisites on these numbers, except that they are only used once with the same key. As there are no late-round candidates that made use of the secret message number, in the following, the term nonce (number used only once) always refers to the public message number. There was no definition for a minimum or maximum length of the key.

Additionally, each submission was allowed to specify a family of ciphers with different parameter sets for each family member.

#### 2.2.2 Process for Determining the Final Portfolio

In 2014, more than 50 algorithms were submitted to the competition. The competition was designed to identify a portfolio of ciphers in three consecutive rounds. For each round, the committee

"will issue a report that, for each selected algorithm, cites the previously published analyses that led the algorithm to be selected. [...] an excellent algorithm might fail to be selected simply because not enough analysis was available at the time of the committee decision." [12]

An appeal of the committee decision was not possible. However, submitters were "expected to promptly and publicly respond to those analyses" they disagree with [12].

In the first round, the cryptographic strength of the submitted algorithms was evaluated. Additionally, all first round candidates were required to publish a software reference implementation. Based on their findings, 28 candidates were eliminated with the announcement of the second round in 2015.

The second round was dedicated to software implementations. Authors of the ciphers and independent designers were invited to submit optimized software implementations for different platforms ranging from embedded devices to servers. SUPERCOP (System for Unified Performance Evaluation Related to Cryptographic Operations and Primitives) was used to benchmark the different implementations [8]. It compiles the submitted code with different compilers, for different target platforms, and with different compiler options to find the best ones. Additionally, all authors of second round candidates were required to submit hardware implementations written in either VHDL or Verilog. 13 candidates were eliminated during this round in 2016.

The third round was dedicated to hardware implementations, but also software tweaks were allowed. Again, authors and independent designers were invited to submit optimized implementations. Planned to be the last round, it was the longest round and lasted until 2018. Nine candidates were eliminated.

With seven finalists remaining, it took another year, until the final portfolio was announced in 2019. It consists of a primary and a secondary recommendation for *lightweight* applications (use case 1), and *defense in depth* applications (use case 3) and lists two recommendations without a preference for *high-performance* applications (use case 2).

#### 2.2.3 Examined Ciphers

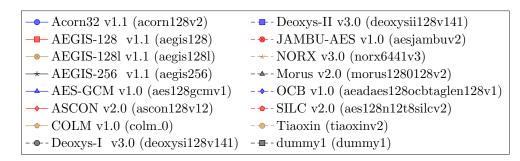

In this thesis, we focus on fifteen different families of ciphers and in parts multiple implementations or versions of the same cipher. Those implementations cover all CAESAR finalists and half of the second round candidates. Table 2.1 lists their parameters. In the following, they are briefly explained to allow for a better classification throughout this thesis.

Like Abed et al. in [1], we classify them into the following groups<sup>1</sup>: *block cipher based*, *stream cipher based*, *sponge based*, and *dedicated* algorithms. In [1], Abed et al. also provide an overview of external cryptanalysis and security proofs of the ciphers.

#### **Nomenclature**

In the literature, there are two ways to refer to the same cipher: first, the common name of the cipher, which may include a version number e.g. "SILC v2.0", a data path width e.g. "Acorn32", or a key width e.g. "AEGIS-128"; second, the name of the (software reference) implementation. This can be simply the same name, but without any white spaces and upper cases or a more specific name like "aes128n12t8silcv2". The latter contains additional information like the used Block Cipher (BC) (AES-128), the length of the nonce (n=12 bytes), or the length of the tag ( $\tau=8$  bytes). The release version is indicated with a "v" suffix; dots in the versioning are ignored, i.e. "v141" stands for "release 1.41". This nomenclature is often used, when the construction is very generic and allows for a variaty of different parameters. For the SILC example, there existed also "present80n6t4silcv2", which uses Present-80 with a six byte nonce and a four byte tag. If both names are given, the software reference implementation is notated in parenthesizes, e.g. "AEGIS-128 v1.1 (aegis128)". A "\_"-suffix can be used to specify to distinguish optimized implementations from the reference implementation, e.g. "aegis128\_ref", "aegis128\_arm64", etc.

#### **Block Cipher**

The following ciphers use a BC to form an AEAD scheme:

AEZ [34] uses multiple, different instances of AES. According to the authors "writing software for AEZ is not easy, while doing a hardware design for AEZ is far worse." Homsirikamol and Gaj confirmed that in their paper "Anything-but EaZy in Hardware" [35]. Throughout this thesis, only one – non working – implementation is used as a bad example.

<sup>&</sup>lt;sup>1</sup>Abed et al. also used the groups *compression function based* and *(non-sponge) permutation based*, but non of the late round CAESAR candidates fall into those categories.

Table 2.1: Security parameters of used implementations

| Cipher<br>Name | Claimed<br>Security <sup>5,6</sup> | Key<br>Size <sup>6</sup> | Nonce<br>Size <sup>6</sup> | Tag<br>Size <sup>6</sup> | Block<br>Size <sup>6</sup> | State<br>Size <sup>6</sup> | Main security function                        | Use Case         |

|----------------|------------------------------------|--------------------------|----------------------------|--------------------------|----------------------------|----------------------------|-----------------------------------------------|------------------|

| AEZ            | 128                                | 384                      | 96                         | 128                      | 128                        | 128                        | three AES-like structures                     | defense in depth |

| Acorn          | 128                                | 128                      | 128                        | 128                      | <u> </u>                   | 293                        | non linear shift register                     | lightweight      |

| AEGIS-128      | 128                                | 128                      | 128                        | 128                      | 128                        | 640                        | 5 rounds of AES-128 <sup>4</sup>              | high-performance |

| AEGIS-128I     | 128                                | 128                      | 128                        | 128                      | 128                        | 1024                       | 8 rounds of AES-128 <sup>4</sup>              | high-performance |

| AEGIS-256      | $256^{1}$                          | 256                      | 256                        | 128                      | 128                        | 768                        | 6 rounds of AES-128 <sup>4</sup>              | high-performance |

| AES-GCM        | 128                                | 128                      | 128                        | 128                      | 128                        | 128                        | 10 rounds of AES-128 <sup>2</sup> + "H"-mult. | 1                |

| ASCON          | 128                                | 128                      | 128                        | 128                      | 64                         | 320                        | 6 rounds of permutation + sponge              | lightweight      |

| CLOC           | 128                                | 128                      | 64                         | 64                       | 128                        | 128                        | 10 rounds of AES-128                          | lightweight      |

| COLM           | 64                                 | 128                      | 128                        | 128                      | 128                        | 128                        | 10 rounds of AES-128                          | defense in depth |

| Deoxys-I       | 128                                | 128                      | 64                         | 128                      | 128                        | 128                        | 10 rounds <sup>3</sup> of Deoxys-BC           | high-performance |

| Deoxys-II      | 127                                | 128                      | 120                        | 128                      | 128                        | 128                        | 10 rounds <sup>3</sup> of Deoxys-BC           | defense in depth |

| Icepole        | 128                                | 128                      | 128                        | 128                      | 1024                       | 1 280                      | 6 rounds of permutation + sponge              | High-performance |

| Jambu-AES      | 128                                | 128                      | 64                         | 64                       | 64                         | 192                        | 10 rounds of AES-128                          | defense in depth |

| Norx           | 256                                | 256                      | 256                        | 256                      | 768                        | 1024                       | 4 rounds of permutation + sponge              | high-performance |

| Morus          | 128                                | 128                      | 128                        | 128                      | 256                        | 1 280                      | shift, rotate, AND, XOR                       | high-performance |

| OCB            | 128                                | 128                      | 128                        | 128                      | 128                        | 128                        | 10 rounds of AES-128                          | high-performance |

| SILC           | 128                                | 128                      | 96                         | 64                       | 128                        | 128                        | 10 rounds of AES-128                          | lightweight      |

| Tiaoxin        | 128                                | 128                      | 128                        | 128                      | 256                        | 1664                       | 6 rounds of AES-128                           | high-performance |

| dummy          | I                                  | 128                      | 128                        | 128                      | 128                        | 128                        | XOR                                           | 1                |

|                |                                    |                          |                            |                          |                            |                            |                                               |                  |

<sup>1 128</sup> bit for authenticity2 not for Associated Data

<sup>3 20</sup> rounds for plaintext/ciphertext4 without key scheduling

<sup>&</sup>lt;sup>5</sup> security decreases for large number of blocks <sup>6</sup> numbers are in bits

- Jambu [85] uses the blocksize of a BC as its state. This state is divided into two even parts. One part absorbs the AD and plaintext by xoring it. The other part acts as a key generator. By xoring this block key with the data, the data is encrypted or decrypted. Finally, the BC is executed on the complete state and new data can be absorbed and encrypted/decrypted. For security reasons, there is also a forward path, that bypasses the BC and xors the absorbing halve of the state to the other halve after executing the BC. Throughout this thesis we use JAMBU-AES, i.e. AES-128 as the BC.

- CLOC [40] is a kind of cipher block chaining mode of operation for AES-128 and TWINE-80. In contrast to the original cipher block chaining, there are some additional function blocks before passing data to the block cipher. Throughout this thesis, the 64-bit nonce and AES-128 version is used.

- OCB [54] stands for "offset codebook" and is a patent-registered mode of operation for AES. In favor of the CAESAR competition, there is also a free license which is suitable for most non military use cases<sup>2</sup>. In contrast to other modes of operation, OCB only requires one pass of the AES BC per input and a linear masking of the input and output. This mask can be a precomputed and stored in a table. Throughout CAESAR OCB version 3 is used.

- SILC [41] is very similar to CLOC and also a kind of cipher block chaining mode of operation for AES128, Present-80, and LED-80. In contrast to the original cipher block chaining, there are some additional function blocks before passing data to the block cipher. Throughout this thesis, the 96-bit nonce and AES128 version is used.

- AES-GCM [19] is the oldest and well-known dedicated AEAD scheme. It uses the AES-128 BC for encryption, but heavily relies on the "H" point-multiplication for authentication. Throughout this thesis AES-GCM is used as reference, as the goal of CAESAR is to find algorithms that "offer advantages over AES-GCM".

- Deoxys-I [43] is based on the Deoxys-BC. For 128-bit keys it uses Deoxys-BC-256 and for 256-bit keys it uses Deoxys-BC-384. In both both cases a 64-bit nonce and 128-bit input blocks are used. Deoxys-BC is based on the AES functions SubBytes, ShiftRows and MixBytes. The AddRoundKey function is replaced with a AddRoundTweakey, which is basically a Linear Feedback Shift Register (LFSR) based key scheduling. The two Deoxys-BCs only differ in their Tweakey generation. The AEAD construction itself is very similar to OCB. Throughout this thesis we use deoxysi128v141.

- Deoxys-II [43] is a nonce-misuse resistant mode that uses the same BC and same general structure as Deoxys-I, but with a 120-bit nonce. To achieve its nonce-misuse resistance, it uses a two-pass structure: In the first pass an authentication checksum is generated. In the second pass this checksum is used as as a tweakey to encrypt/

<sup>2</sup>https://www.cs.ucdavis.edu/~rogaway/ocb/license.htm

decrypt the message. It is the only remaining two-pass cipher in the competition. Throughout this thesis we use deoxysii128v141.

• COLM [3] superseded AES-COPA and ELmD and combines the best of both. There were two versions COLM<sub>127</sub> and COLM<sub>0</sub>. However, only COLM<sub>0</sub> is of practical relevance and in the following referred to as COLM. Like Deoxys-II, it is nonce-misuse resistant. It has a Encrypt-Linearmix-Encrypt structure: Data is first encrypted using AES-128. For processing the AD the encrypted data is then xored. For processing the plaintext, the output is fed to a linear mixing function ρ. The result is then again encrypted with AES-128. ρ has a second input and a second output. This additional output is fed to the second input for the processing of the next input block. Additionally, like OCB, COLM applies a linear mask to its input and output.

#### **Stream Cipher based**

Acorn [84] is the only late round stream cipher. It uses a 128-bit key and a 128-bit nonce. Its state consists of a 293-bit shift register, which is a mix of six Galois and Fibonacci LFSRs. A feedback function uses 13 out of the 293 bits to generate an overall feedback bit. Eight out of these 13 bits are used to generate an intermediate key bit, which is used to encrypt or decrpyt one bit of the stream input. The overall feedback bit is xored with the input bit and fed back to update the shift register. After the initialization the register is shifted for 1535 cycles with a constant input of one. After processing the AD, and the plaintext/ciphertext, it is shifted for 512 cycles with a key dependent input.

#### Sponge-based

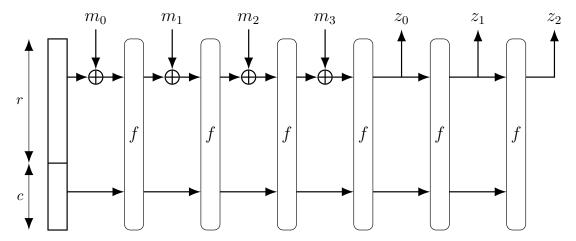

Figure 2.1 shows the general structure of a sponge construction. It consists of a state and a permutation function f. The state is divided into a capacity c and a rate r. The round function performs a permutation of the state. Typically this round function is applied several times to form f. The (padded) input m is xored to the rate. The output of the sponge construction is z. The individual ciphers differ in the used permutation, the width of r and c, the padding function, the way how the construction is used to encrypt data (i.e. how m is generated from the input (e.g. plaintext) and how the output (e.g. ciphertext) ist generated from z) and some minor tweaks. These differences are as follows:

• ICEPOLE [58] uses a duplex construction, where m and z are not divided into two consecutive phases, but are interleaved. The key and nonce are used to initialize the state. There are three variants of Icepole: Icepole128, Icepole128a, and Icepole256a. Icepole256a uses a 256-bit key, a 96-bit nonce, a 962-bit rate and a 318-bit capacity. Icepole128a uses a 128-bit key, a 128-bit nonce, a 1026-bit rate and a 254-bit capacity.

Figure 2.1: Sponge construction [42]

The odd choice of the rate is due to Icepole's special padding, which always needs two additional bits. Thus, subtracting the value two from the rate results in an even power of two. This also influence the capacity, which is built to form a complete state of 160 byte. Icepole128 uses the same parameter as Icepole128a but has additional support for a secret message number. Throughout this thesis we use icepole128av2.

- ASCON [17] again uses the duplex construction. The state is initialized with the key, the nonce, and a constant. Additionally, the key is used for domain separation. This means, that the capacity is xored with the padded key and a constant between different processing phases. There are two variants Ascon-128 (ascon-128-64) and Ascon-128a (ascon-128-128). Both use a 128-bit key, a 128-bit nonce, and a 320-bit state. Ascon-128a uses a 128-bit rate and a 192-bit capacity. Ascon-128 uses a 64-bit rate and a 256-bit capacity. Throughout this thesis we use ascon128v12 as this is the primary recommendation of the authors.

- NORX [4] is a highly parameterizable cipher. In this thesis we use norx6441v3, which refers to a wordsize of 64 bits, 4 rounds and a parallelism of degree 1. In this configuration it is a strait forward duplex construction with domain separation. It uses a 256-bit key, a 256-bit nonce, a rate of 768 bit and a capacity of 256 bits.

#### **Dedicated structures**

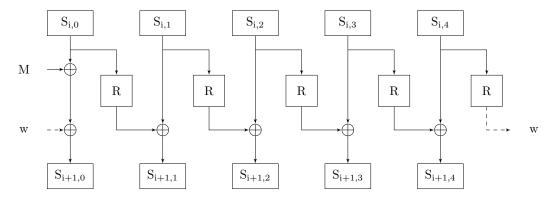

The following ciphers have a similar structure as a *Type-3 Feistel* scheme. They consist of a multi-block state  $S = S_0 ||S_1||...||S_n$ . A message (block) M is added to one or all sub-states, e.g.  $S_0 := S_0 \oplus M$  and the individual sub-states are updated by adding their neighbor states e.g.  $S_i := S_i \oplus f(S_{i-1})$ .

Figure 2.2: Aegis-128 state update: The state update function R consists of the AES functions SubBytes, ShiftRows and MixColums [88].

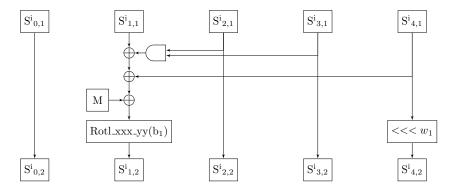

Figure 2.3: Second step of Morus's update function: The circuit is sequentially repeated for each substate [86]. ©2019 IEEE [80]

- AEGIS-128 (aegis128), AEGIS-128I (aegis128I), and AEGIS-256 (aegis256) [88] share

the same structure as depicted in Figure 2.2, but differ in their parameters: Aegis-128

consists of five 16-byte sub-states, uses a 128-bit key and permutes the state ten

times for initialization. Besides eight 16-byte sub-states, Aegis-128I has the same parameters as Aegis-128. Aegis-256 consists of six 16-byte sub-states, uses a 256-bit

key and permutes the state 16 times for initialization.

- The Morus family [86] has two parameters: the state size and the key size. In this thesis morus1280128v2 is used. That means the state size is 1280 bits and the keysize is 128 bits. Other parameters would be a 640 bit state and a 256 bit key. This state is divided into five substates of 256 bits. Three at a time are used to update one substate by anding two and xoring them and remaining one to the updated one. Finally the results is rotated by a round constant. Figure 2.3 shows the update function of the second substate.

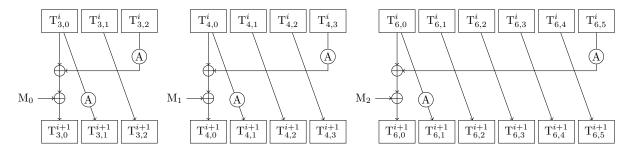

- Tiaoxin [63] also called Tiaoxin-346 pronounced Tiaoxin three four six uses a 128-

Figure 2.4: Tiaoxin-346 state update: The state update function (A) consists of the AES functions SubBytes, ShiftRows and MixColums [63].

bit key, a 128-bit nonce and can encrypt six bytes per round. It has three states  $T_3$ ,  $T_4$ ,  $T_6$ . They are composed of 3, 4, and 6 16-byte words, respectively. Figure 2.4 shows the associated update function.

#### **Dummy Cipher**

The dummy cipher simply xors a 128-bit key, a 128-bit nonce, and a counter with a 128-bit input block. It is used to provide a lower boundary for ciphers and to allow for testing benchmarking frameworks. Other names are dummy1 [39] in the CAESAR competition<sup>3</sup> and dummy\_lwc [79] in the LWC competition.

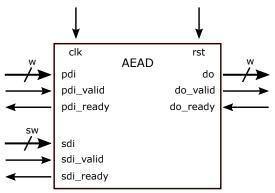

#### 2.3 New Generation of Reconfigurable System-on-Chips

As mentioned, today's cyptographic algorithms must perform in a variety of different environments: in high-performance computing clusters, in embedded devices, in mixed hardware-software codesigns, and in low-powered IoT-devices. With cheap hardware available, hardware implementations gain more and more importance. Another factor for the increasing interest is the spread of re-configurable Systems on Chips (SoCs). They become more and more common, not only in ASICs, but also on FPGAs, as they combine the advantages of a fully Programmable Logic (PL) with the flexibility of a Processing System (PS) running arbitrary software. In Chapter 5 we will pointed out the advantages of using the PS of a SoC to pre- and post-process data, e.g. test vectors for the actual hardware under test, which is programmed into the PL.

<sup>&</sup>lt;sup>3</sup>As part of the development package, there are also dummy2 to dummy5, but they are not used throughout this thesis.

Therefore, we first introduce the used SoC-platform. It integrates a single or dual core ARM-Cortex-A9 processor with an Artix-7 or Kintex-7 based.

#### PYNQ: Xilinx Zynq-7000 SoC

Throughout this thesis we use the Xilinx' PYNQ, which is a portmanteau of Python and Zynq. It combines the very successful Zynq-7000 SoC with an easy to use and program Python interface. The hardware consists mainly of a XC7Z020 FPGA, which combines an Artix-7 based FPGA fabric with an integrated dual-core ARM Cortex-A9 [93]. Additionally, 512 MB of DDR3 RAM, 16 MB of QUAD-SPI Flash, and a MicroSD-card slot are available. Furthermore, the XC7Z020 also features an analog-to-digital converter (XADC), which can be used to measure analog values like temperature or current draw. The board itself is striped to the basics, which enables a very low (academia) price. The Arduino and Pmod input/output interfaces can be used for additional measurement and control extensions. An Ethernet connector enables a fast way of communication with the board, such that a realistic amount of data can be processed without a bottleneck, like when using an UART. Since there are only very few additional interfaces such as HDMI (in and out), USB, and analog audio (in and out) on the board, it is very well suited for realistic power and performance measurements, as on one side, there is no exotic hardware that influences the measurement, yet on the other side, it has the characteristics of a complete embedded system.

The software side features a fully functional Linux, which runs a SAMBA server, a webserver with a Jupyter notebook, and an SSH-client. Thus, it enables a very broad spectrum of applications and use cases.

There are three particularly useful features of the PYNQ board:

#### On-the-fly FPGA programming

In order to use the Programmable Logic to its fullest potential at all times, the programmed logic inside has to be changed to the current requirements of the software running on the Processing System. This is a complex task and requires the user to either re-program the FPGA using the appropriate vendor toolchain, or know how to use partial reconfiguration for on-the-fly reconfiguration. PYNQ overcomes this problem by making it possible to load *overlays* at runtime using a simple Python command. Overlays are precompiled bitstreams of the desired FGPA configuration, along with a corresponding block design representation in TCL, that can be stored on the Linux file system of the SoC.

#### **Python drivers**

The python driver uses the information of the block design from the TCL-file to abstract the underlying complexity, for example, the bus communication, or the individual configuration steps needed for a DMA transfer, and allows the user to easily address the PL from the PS. This is especially useful for designers who want to test their design on real hardware, but are not aware of each and every detail in a SoC.

#### **Web-based User Interface**

Additionally the Python framework provides a Jupyter notebook interface that allows prototyping Python code directly from the web browser.

# 3 Challenges in Evaluating Cryptographic Competitions

In the following, we will discuss the challenges in evaluating cryptographic competitions. Our findings are based on the CAESAR competition, but can be transferred to the NIST-LWC competition, because –besides the official character– they are very similar in terms of requirements and submissions. We hope, that this discussion helps to improve the currently ongoing NIST-LWC-competition and helps to prevent some of the discovered flaws.

#### 3.1 Review Process Flaws at the Example of CAESAR

The review process of the CAESAR competition was purely steered by the CAESAR committee. It consisted of 18 members; 17 of them with voting power. They made their selection decisions on the basis of published analyses. Besides the problem that "an excellent algorithm might fail to be selected simply because not enough analysis was available at the time of the committee decision" [12], there was also a risk of flaws in the review process itself:

As the cryptographic community is relatively small, a pure independent evaluation was rarely possible. Often only mutual evaluation was possible. This problem was further increased by the huge amount of heterogeneous submissions. As a consequence, there was an overlap between the decision-makers, the participants, and the evaluators. This resulted in four of seven finalists having at least one author being part of the CAESAR committee.

The CAESAR competition required the authors to submit both hardware and software reference implementations. Due to the nature of the different approaches, common verification platforms were hard to put into practice. First, there was only a common benchmarking and verification suit for software implementations. Second, even with this tool, there was no process to verify if the submitted reference implementation matches the specified requirements.

For hardware implementations there was no official verification suite, and only very late in the competition a mandatory hardware interface was put into practice. Thus, there were undetected flaws in the official hardware reference implementations of late round candidates.

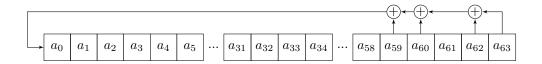

Figure 3.1: Intended LFSR

#### 3.1.1 Algorithmic or Software Flaws

One example for a very long undiscovered mismatch between specification and the algorithm itself is ICEPOLE. It uses round constants in its  $\kappa$  function which are defined

"as the output of a simple 64-bit maximum-cycle Linear FeedbackShift Register (LFSR). The polynomial representation of LFSR is  $x^{64}+x^{63}+x^{61}+x^{60}+1$ . The LFSR state is initialized with the 64-bit vector '0123456789ABCDEF' (hexadecimal format) and then each cycle generates a subsequent constant." [58]

Figure 3.1 shows the intended hardware.

However, as we have shown in [76], this is not the case. The algorithm itself does not calculate them on the fly, but uses predefined constants, which were generated with the following C-code<sup>1</sup>

```

1 # include <stdint.h>

2 int main(void)

3 {

uint64_t lfsr = 0x0123456789ABCDEFu;

unsigned bit;

int i = 0;

int number_of_rounds = 12;

9 printf("Initial state: %01611X\n",lfsr);

10

11 for (i=0; i<number_of_rounds; i=i+1){</pre>

12

// taps: 64 63 61 60

13

// feedback polynomial: x^64 + x^63 + x^61 + x^60 + 1

14

bit = ((lfsr >> 0) ^ (lfsr >> 1) ^ (lfsr >> 3) ^ (lfsr >> 4)) & 1;

15

(lfsr >> 1) | (bit << 63);

16

18 printf("constant[%2d] := %016llX\n",i,lfsr);

19 }

```

Unfortunately, this does not generate an LFSR but a non LFSR, due to an overflow in line 16, caused by the wrong datatype declaration in line 5. The variable bit is defined as unsigned.

<sup>&</sup>lt;sup>1</sup>confirmed by the author Paweł Morawiecki <pawel.morawiecki@gmail.com> via email on 19.10.15, 22:24

Figure 3.2: Implemented non LFSR

On most architectures this is equal to uint32\_t. Thus, it can only contain 32 bits of data. In the right part of line 16 the value of bit is shifted to the left by 63. This results in an overflow. The real pity is that default compiler warnings even tell this:

Therefore, bit is not shifted by 63, but actually by  $63 \mod 32 = 31$ . Thus in line 16, the feedback bit is not added to the most left side of lfsr but is ored in the middle. Thus resulting in a non linear feedback shift register. Figure 3.2 shows the corresponding hardware.

Unfortunately, this was first discovered during the hardware benchmarking in the second round of the competition.

#### 3.1.2 Hardware Flaws

One example for a very long undiscovered erroneous hardware reference implementation, is the CAESAR finalists Morus: The official reference hardware implementation is dated July 2016<sup>2</sup>. This implementation is also used to back up the claimed implementation and performance results.

However, even a brief look at the VHDL code reveals the following flaws:

```

19 entity CipherCore is

37

port (

--! Global

38

std_logic;

clk

: in

39

bdi

std_logic_vector(G_DBLK_SIZE

-1 downto 0);

43

msg_auth_done

: out std_logic;

63

msg_auth_valid

: out std_logic

);

66 end entity CipherCore;

```

<sup>&</sup>lt;sup>2</sup>https://www.ntu.edu.sg/home/wuhj/research/caesar/caesar.html

#### 68 architecture structure of CipherCore is : std\_logic\_vector(G\_DBLK\_SIZE -1 downto 0); 73 signal tag\_rev signal msg\_auth\_done\_s : std\_logic; 125 144 begin process (clk) 148 begin 149 if rising\_edge(clk) then 150 if (msg\_auth\_done\_s = '1') then if $(tag_rev(255 downto 128) = bdi(255 downto 128))$ then msg\_auth\_valid <= '1'; else msg\_auth\_valid <= '0';</pre> 208 end if: 209 msg\_auth\_done <= '1';</pre> 210 211 end if: 212 213 end if; end process;

If the condition in line 204 is true, the tag is evaluated in line 205. If the tag is correct, the corresponding output is set to one (line 206), otherwise it is set to zero (line 208). In any case, the corresponding done-flag is set to one (line 210). These are the only lines where the outputs of lines 63 and 64 are set. There is no line in the entire architecture, where msg\_auth\_done is set to zero. Thus, if the condition of line 204 is false afterwards, e.g. during the processing of the next message, the output is not reset.

This is a very basic error in the output handling, nevertheless the candidate made it to the final round. Thus, hardware testing was not conducted carefully during the competition.

#### 3.2 The Role of the Interface

441 end structure;

When benchmarking (cryptographic) hardware implementations, the assumptions made on the interface between the primitive and the surrounding benchmarking framework is crucial. In the following we will demonstrate this at the example of ICEPOLE [58] a second round CAESAR candidate. For doing so, we first explain an optimized implementation of ICEPOLE. Next, we analyze the presented results and explain the pitfalls when using different interfaces.

Figure 3.3: ICEPOLE-128 © 2016 IEEE [76]

Parts of the following analysis have already been pre-published in "Michael Tempelmeier, Fabrizio De Santis, Jens-Peter Kaps, and Georg Sigl. An area-optimized serial implementation of ICEPOLE authenticated encryption schemes. In 2016 IEEE International Symposium on Hardware Oriented Security and Trust (HOST), pages 49–54, May 2016. doi: 10.1109/HST.2016.7495555".

#### 3.2.1 The Example of Icepole

ICEPOLE is a high-speed, hardware-oriented family of single-pass authenticated encryption schemes based on the duplex construction as introduced in [10]. In this example, only lcepole-128 is considered, but the results can be translated to any sponge-based block cipher with an arbitrary state size.

Icepole-128 works on a 1280-bit state S arranged into a three dimensional  $4\times 5\times 64$ -bit cube S[x][y][z]. According to [58], bits S[x][y], which share the same axis z, are called *slices*, bits S[y], which share the same axes x and z, are called *rows*, while bits S[z], which share the same axes x and y, are called *words*. Therefore, the state can be seen alternatively as a collection of either  $64\times 20$ -bit slices, or  $256\times 5$ -bit rows or  $20\times 64$ -bit words.

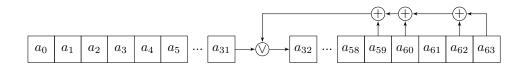

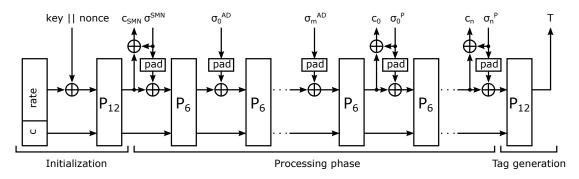

ICEPOLE-128 encrypts and authenticates variable-length messages in three phases: the initialization phase, the processing phase, and the tag generation phase, as illustrated in Figure 3.3. In each phase the state is transformed by a 1280-bit permutation P that is based on the successive execution of the round function R. In the initialization phase, the permutation P is denoted by  $P_{12}$  and transforms the initial state by applying a round function R 12 times. The initial state is obtained by filling the state with a "1280-bit pseudo-random constant" and then adding the secret key and the nonces to the first four words of the state  $S[i][0], i \in \{0,1,2,3\}$ . All the successive invocations of P in the processing phase are denoted by  $P_6$ . The permutation  $P_6$  transforms the current state by applying the round function R only 6 times.

\_

<sup>&</sup>lt;sup>3</sup>truncated result of applying Keccak-f[1600] to an all zero input [58]

The round function  $R=\kappa\circ\psi\circ\pi\circ\rho\circ\mu$  consists of a composition of 4 linear steps denoted by  $\mu,\ \rho,\ \pi$  and  $\kappa$  and a single non-linear step denoted by  $\psi$ . The  $\mu$  step transforms each slice of the state using a Maximum Distance Separable (MDS) matrix. More formally, each slice of the state is viewed as a column vector of 5-bit words  $(Z_i)_{0\leq i\leq 3}$  and is multiplied by a constant matrix defined as follows:

$$\begin{bmatrix} 2 & 1 & 1 & 1 \\ 1 & 1 & 18 & 2 \\ 1 & 2 & 1 & 18 \\ 1 & 18 & 2 & 1 \end{bmatrix} \begin{bmatrix} Z_0 \\ Z_1 \\ Z_2 \\ Z_3 \end{bmatrix} = \begin{bmatrix} 2Z_0 + Z_1 + Z_2 + Z_3 \\ Z_0 + Z_1 + 18Z_2 + 2Z_3 \\ Z_0 + 2Z_1 + Z_2 + 18Z_3 \\ Z_0 + 18Z_1 + 2Z_2 + Z_3 \end{bmatrix}$$

where all operations are performed in the finite field  ${\rm GF}(2^5)/(x^5+x^2+1)$ . The  $\rho$  step bitwise rotates all 20~64-bit words of the state according to the mapping

$$S[z] \mapsto S[z + r(x, y) \bmod 64],\tag{3.1}$$

where the offsets r(x, y) are defined as follows:

$$r(0,0) = 0$$

,  $r(0,1) = 36$ ,  $r(0,2) = 3$ ,  $r(0,3) = 41$

$r(0,4) = 18$ ,  $r(1,0) = 1$ ,  $r(1,1) = 44$ ,  $r(1,2) = 10$

$r(1,3) = 45$ ,  $r(1,4) = 2$ ,  $r(2,0) = 62$ ,  $r(2,1) = 6$

$r(2,2) = 43$ ,  $r(2,3) = 15$ ,  $r(2,4) = 61$ ,  $r(3,0) = 28$

$r(3,1) = 55$ ,  $r(3,2) = 25$ ,  $r(3,3) = 21$ ,  $r(3,4) = 56$

The  $\pi$  step permutes the words within the state by replacing the word at position (x,y) with the word at the position (x',y') according to the following rule:

$$(x', y') = (x + y \mod 4, x' + y + 1 \mod 5)$$

(3.2)

The  $\psi$  step performs a non-linear transformation of each 5-bit row of the state  $(M_k)_{0 \le k \le 4}$  using the following boolean equations:

$$Z_k = M_k \oplus (\neg M_{k+1} M_{k+2}) \oplus (M_0 M_1 M_2 M_3 M_4) \oplus (\neg M_0 \neg M_1 \neg M_2 \neg M_3 \neg M_4), \quad 0 \le k \le 4$$

(3.3)

Finally, the  $\kappa$  step adds a round constant  $C_r$  to the word at position (0,0) in each round  $0 \le r < 12$ .

#### Processing of the Input

In the data processing phase, the permutation  $P_6$  is iterated to wrap the 128-bit secret message number  $\sigma^{SMN}$ , the associated data blocks  $\sigma_i^{AD}$  and the plaintext blocks  $\sigma_i^P$  into the state and to generate the ciphertext blocks  $c_i$ . Figure 3.3 shows the interleaved absorbing and squeezing of data. Each block  $\sigma_i^{AD}$  and  $\sigma_i^P$  has a length between 0 and 1024 bits and

is padded as follows: A frame bit is appended to the block, followed by "1" and a number of "0"s to reach the required length of 1026 bits. The frame bit is used for domain separation as follows: The frame bit is set to "1" for the last associated data block  $\sigma^{AD}$  and all the plaintext blocks  $\sigma_i^P$  but the last. A detailed view on the padding is not needed for understanding this thesis and therefore out of the scope. Finally, in the tag generation phase, the permutation  $P_{12}$  is iterated once more to generate a 128-bit tag T=S[0][0] S[1][0] given by the concatenation of the two S[0][0] and S[1][0].

#### **Optimized Hardware Implementations**

For optimized hardware implementations, we first analyze the optimization potential of the individual subfunctions or building blocks. Then, based on the findings, we combine them to form an implementation that has a high throughput, but still obtains a reasonable area footprint. This also means, that it can make sense to use a suboptimal implementation for a subfunction, because it enables a global optimization. Therefore, in the following, we discuss how the different parts of the round function can be implemented:

The  $\pi$  step solely changes the position of the individual words within the state. Therefore, the  $\pi$  step can be implemented through simple rewiring, which comes at no additional costs in hardware, but also offers no further potential for optimization in FPGA implementations.

The  $\rho$  step performs a circular shift of each word of the state. This can be implemented either as rewiring in parallel architectures or as shift registers in serial architectures. We use the latter.

The  $\mu$  step consists of  $64 \times 20$  equations that operate on one slice of the state at a time. One way to implement the  $\mu$  step is to instantiate these 20 equations and iterate over them for 64 clock cycles, thus trading area for time.

The  $\psi$  step applies the ICEPOLE S-box 256 times on all 5-bit rows of the state. The ICEPOLE S-box can be implemented either in combinational logic by instantiating the five boolean equations of Equation (3.3) or as a Look Up Tables (LUTs).

Finally, the  $\kappa$  step adds the round constants  $C_r$ . It can be implemented either as LUTs or as a particular shift register<sup>4</sup>.

<sup>&</sup>lt;sup>4</sup>As shown in Section 3.1.1 on page 30,  $\kappa$  cannot be realized by a LFSR as claimed in the original specification [58] because it contains a nonlinearity.

#### An optimized 20-bit Slice-Serial Implementation

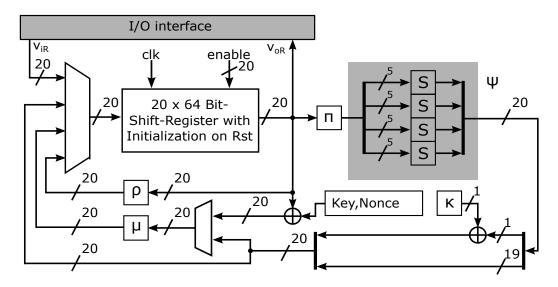

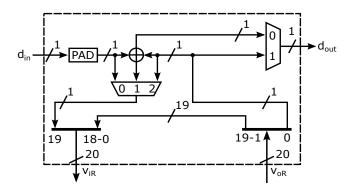

All but the  $\kappa$  and  $\rho$  steps need to access at most one bit of each word within the state at the same time. Therefore, a very natural choice for a serialized implementation is a 20-bit sliced-serial architecture based on the 20-bit slice representation of the state S. In the following, every slice S[x][y] is mapped to the linear vector v by the formula v[4x+y]=S[x][y]. Figure 3.4 illustrates the architecture diagram of our 20-bit serial architecture.

Figure 3.4: ICEPOLE: 20-bit architecture ©2016 IEEE [76]

The  $\mu$  step is a straight forward serial implementation as explained in subsubsection 3.2.1.

With a 20-bit slice data path, the  $\pi$  step becomes trivial. It is a fixed rewiring of the 20 bits as described in Equation (3.2). After 64 cycles all words of the state are correctly reordered.

The implementation of the  $\rho$  step is a little more complicated, as it does not change the position of the bits within a slice, but within a word. In our slice-wise architecture the implementation of the  $\rho$  step is performed by the control logic:

The 1280-bit state is implemented using D-Flip-Flops (FFs) with input enable to control the

shifting operations. Hence, 64 FFs are cascaded to form 20 64-bit simple shift registers<sup>5</sup>. The 4-to-1 20-bit multiplexer placed before the state register selects either a new input message from outside or one of the three parts  $(\rho, \mu, \text{ or } \kappa \circ \psi \circ \pi)$  of the round function R.

Each shift register stores one word of the state and has its own enable signal. The enabled FFs of the state are shifted by one position in each clock cycle. Thus, the  $\rho$  step takes 62 clock cycles to complete, as this is the largest offset given in Equation (3.1).

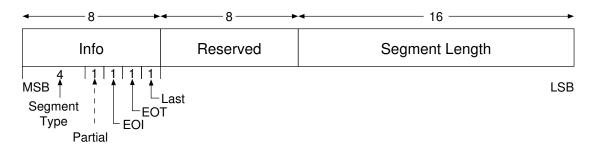

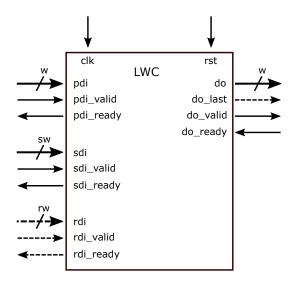

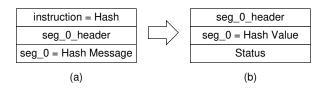

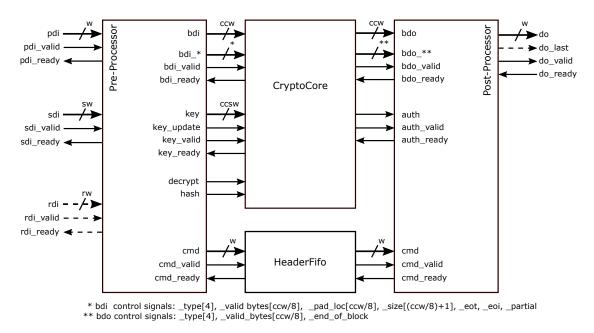

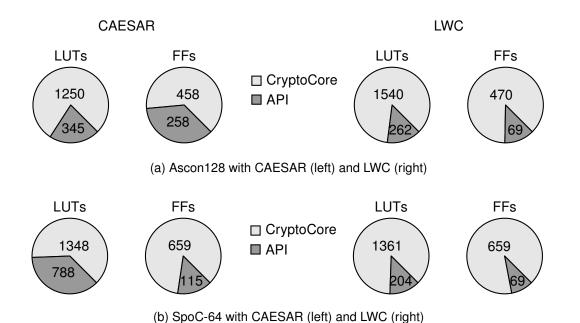

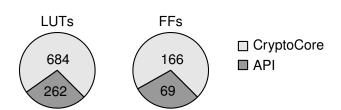

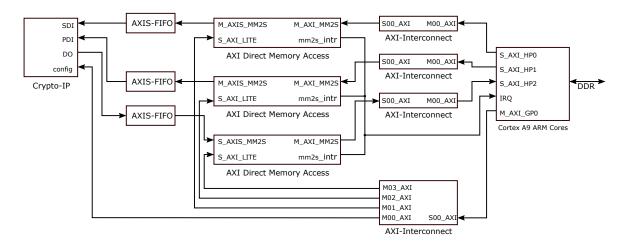

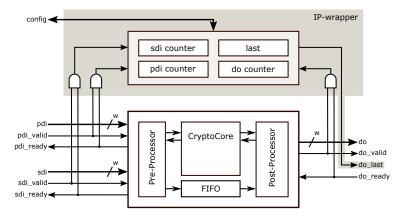

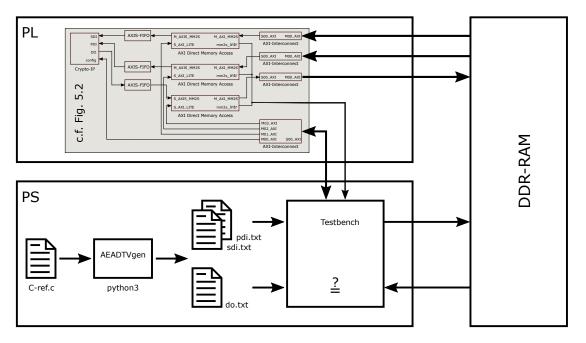

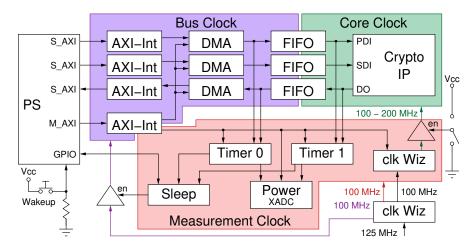

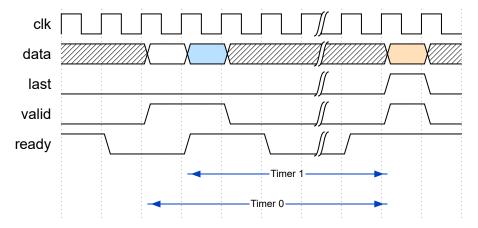

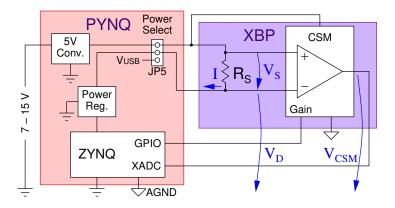

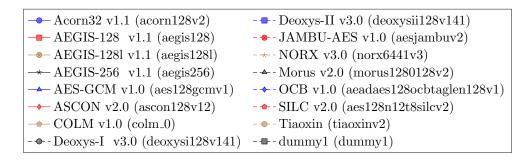

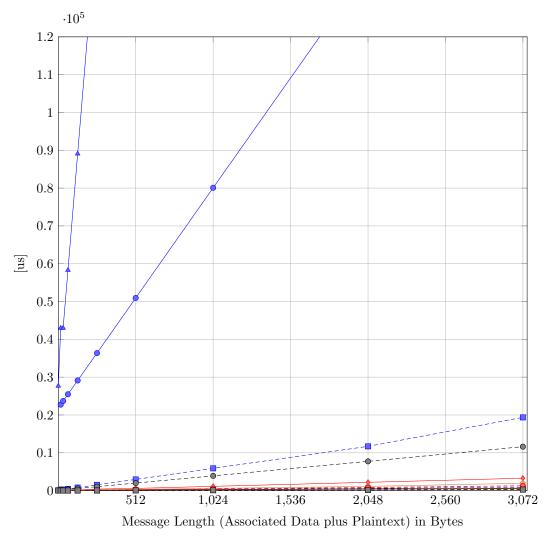

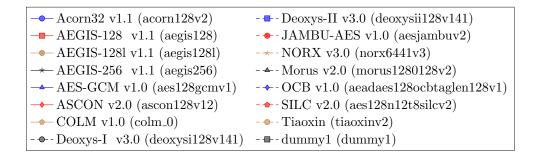

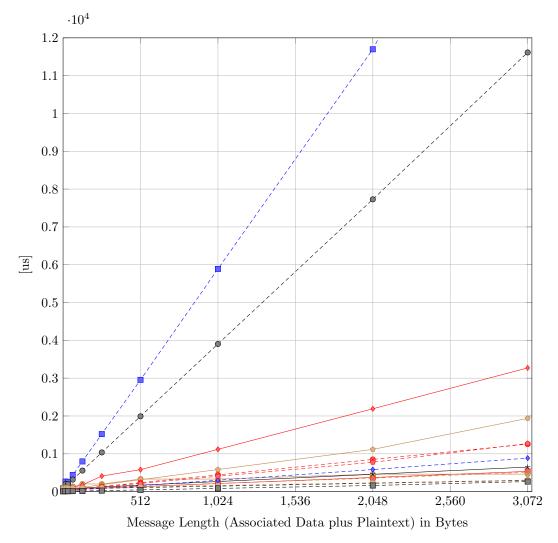

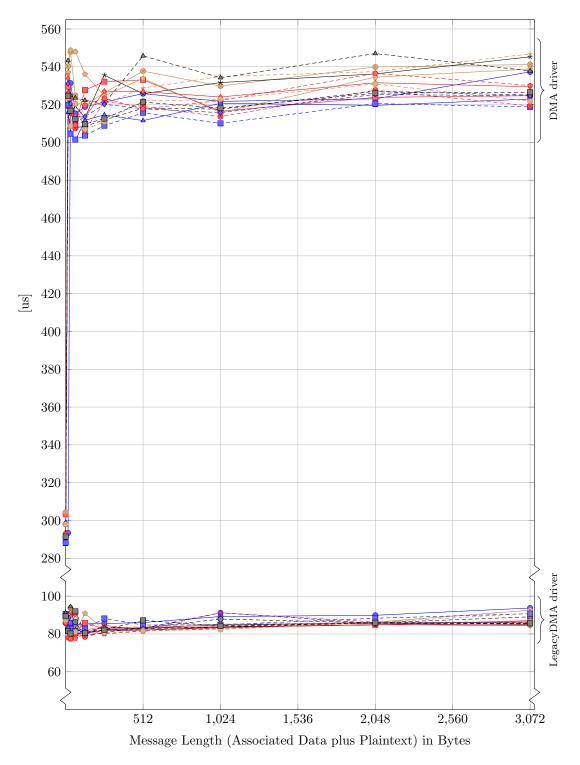

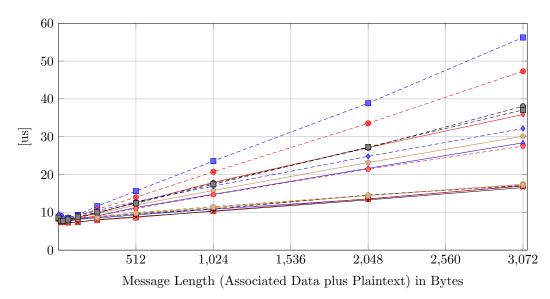

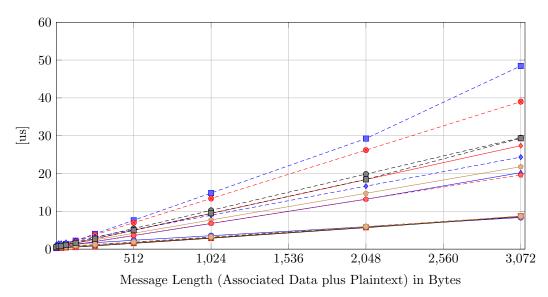

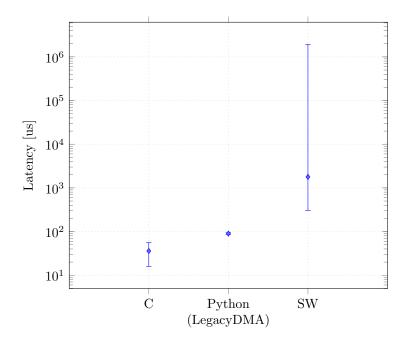

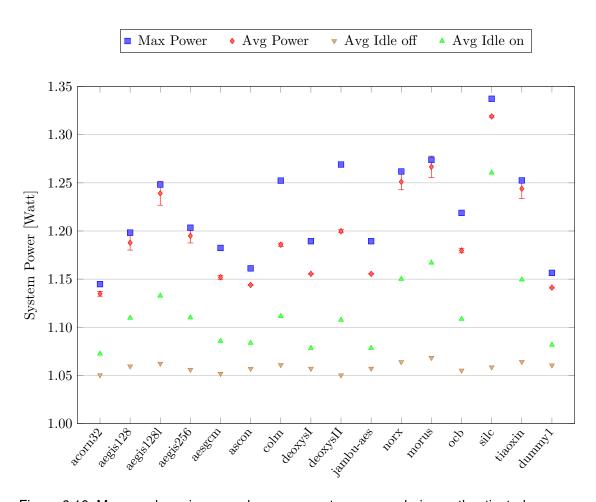

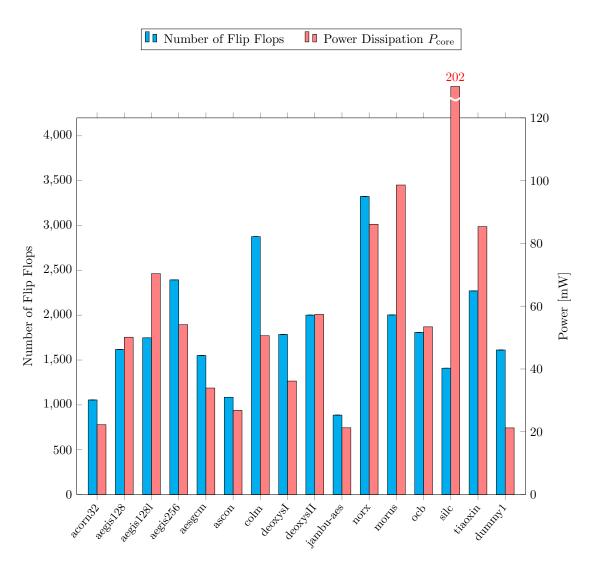

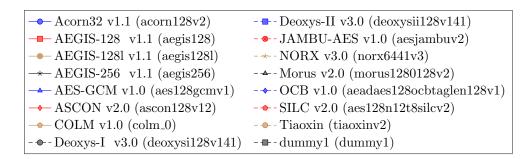

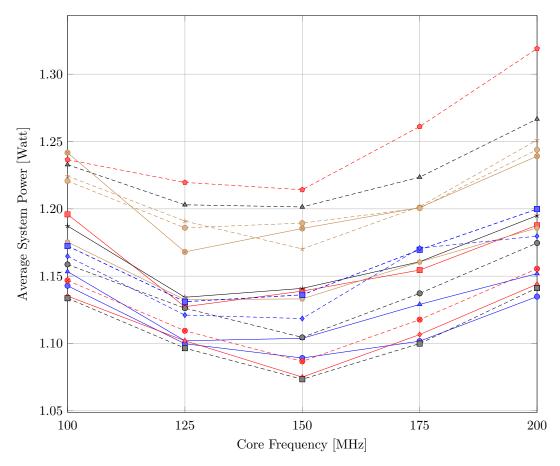

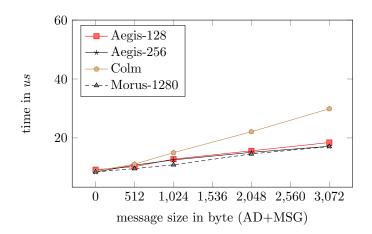

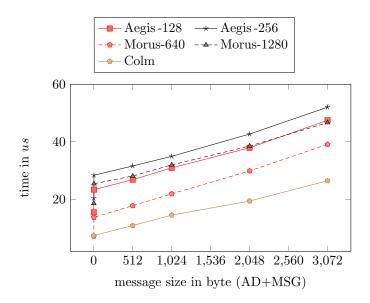

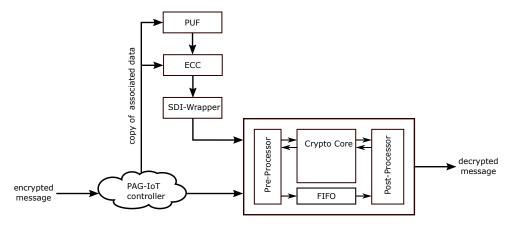

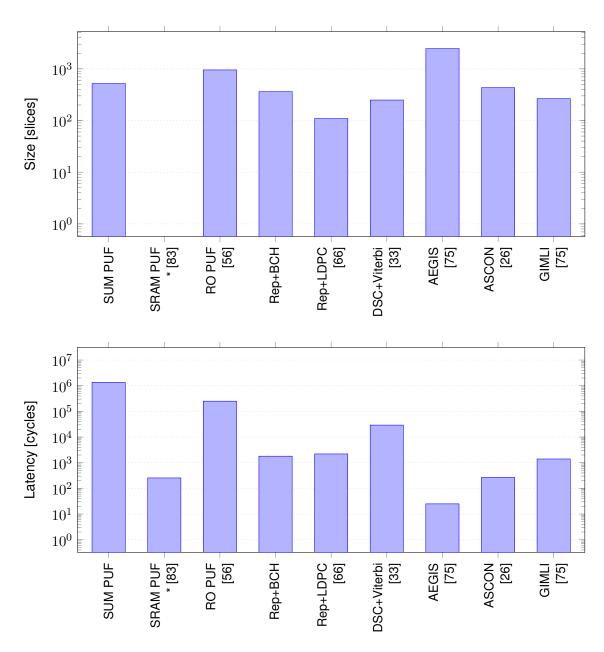

The  $\psi$  step applies the ICEPOLE S-box to each 5-bit row of the slice. Therefore, 4 instances of the ICEPOLE S-box are needed to process all 20 bits of one slice. Each S-Box takes 5 consecutive bits of the vector v as input. The output of the S-box is concatenated to form a 20-bit vector again. In a 20-bit slice architecture, the constants of  $\kappa$  must be serialized as the state words can only be addressed bit-wise. Alternatively, the constant can be generated on-the-fly with a non linear shift register as discussed in [76]. The output of  $\kappa$  is XORed with v[0] = S[0][0] one bit per clock cycle.