# TECHNISCHE UNIVERSITÄT MÜNCHEN

### Lehrstuhl für Realzeit-Computersysteme

# Hybrid Optimization Techniques for Multi-Domain Coupling in Cyber-Physical Systems Design

Debayan Roy

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs (Dr.-Ing.)**

genehmigten Dissertation.

Vorsitzender: Prof. Dr.-Ing. habil. Gerhard Rigoll

Prüfer der Dissertation:

1. Prof. Dr. sc. Samarjit Chakraborty, University of North

Carolina at Chapel Hill, North Carolina, USA

2. Prof. Dr. Andreas Herkersdorf

Die Dissertation wurde am <u>22.04.2020</u> bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am <u>30.10.2020</u> angenommen.

## **Abstract**

In a cyber-physical system (CPS), the physical process is controlled by a software algorithm running on a hardware platform, where there is a *tight coupling* between the physical behavior of the system, the hardware, and the software. These systems are often *safety-critical* and have stringent performance requirements (e.g., faster stabilization after a disturbance). Many of them are also *cost-sensitive* and need to be implemented using limited platform resources (e.g., less number of communication slots or lower energy dissipation). However, the comprehensive design of a CPS requires the integration of *heterogeneous models* coming from different engineering domains, e.g., mechanical processes, electrical and electronic devices, control algorithms, and software implementations. Therefore, the design of high-performance yet resource-efficient CPSs leads to *challenging optimization problems*.

Challenges towards multi-domain coupling in CPSs design: There are several challenges to the comprehensive modeling and design of CPSs. First, it is not trivial to represent heterogeneous models in a *unified* framework. For example, a physical system evolves continuously according to a set of differential equations while the corresponding controller might be dispatched periodically and for each dispatch, it contests for the resource based on a certain scheduling policy that can be represented using a finite-state machine. Note that the theory of hybrid systems is often applied to tackle such a heterogeneity, however, such an approach often faces scalability issues. Second, with increasing *size* and *complexity* of industrial CPSs (like modern cars), the integrated design space grows exponentially, and therefore, the design problem can easily become intractable. Third, the requirements from different design domains might *conflict* with each other, e.g., improving control performance is often possible at the cost of more resources. Lastly, CPSs design typically involves a *disjoint set of tools* offered by different suppliers. It is non-trivial to develop an automated toolchain offering state-of-the-art design techniques while seamlessly interfacing the existing tools and preserving their advantages.

This thesis outlines our efforts in handling the aforementioned challenges using customized hybrid optimization techniques and novel design flows. We take automotive systems for our case study because they represent safety-critical, resource-constrained, and distributed CPSs.

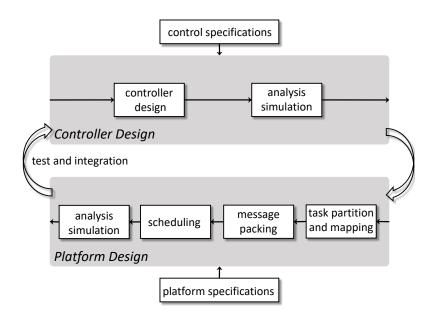

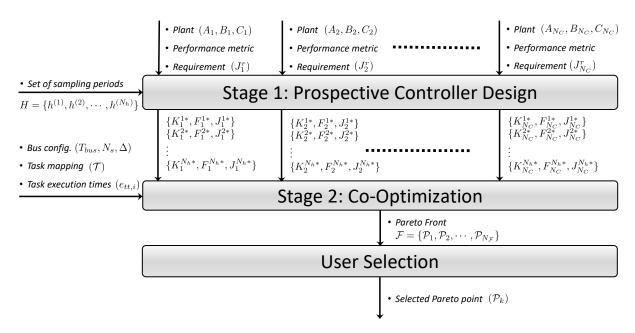

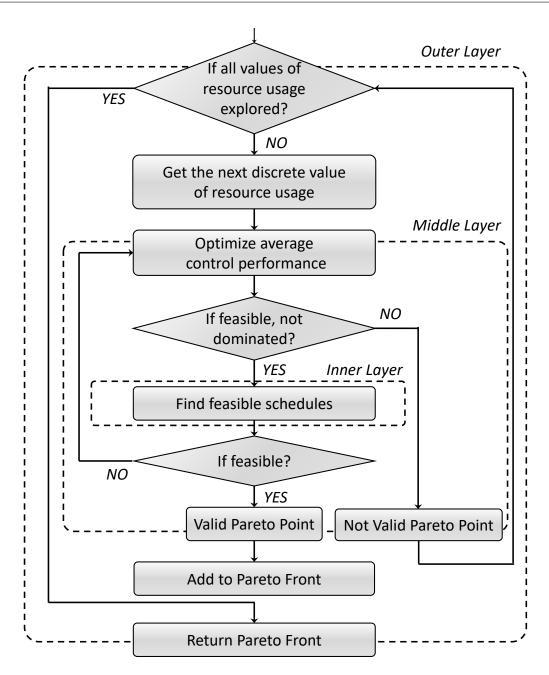

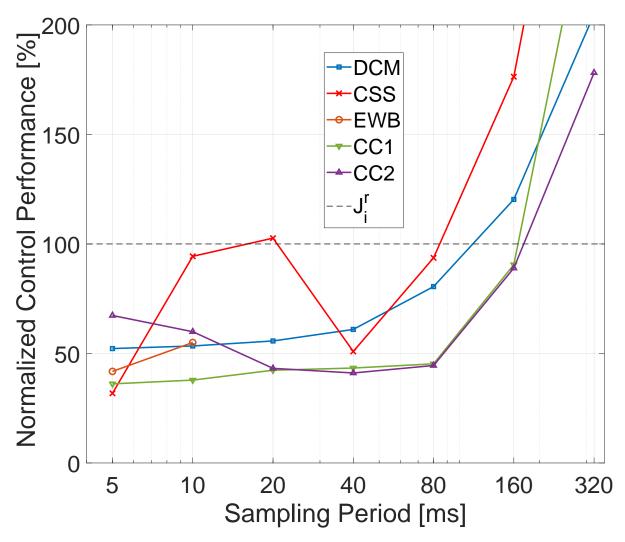

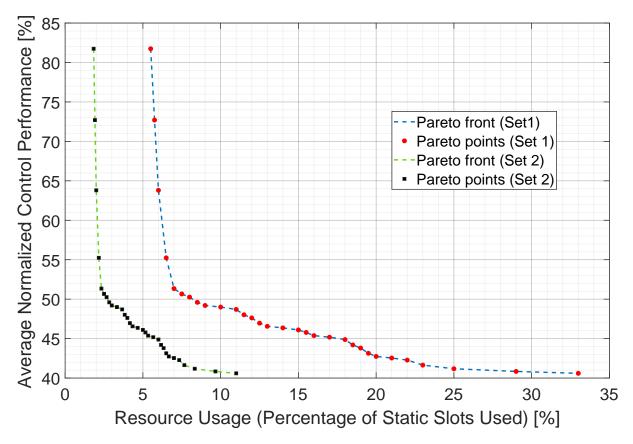

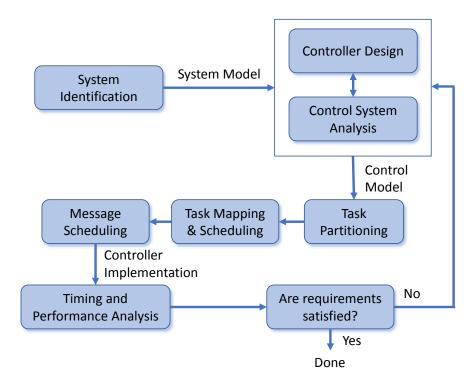

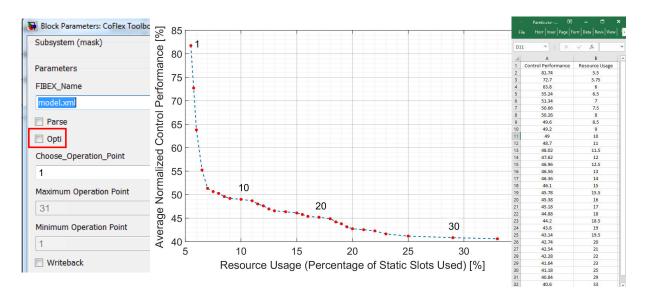

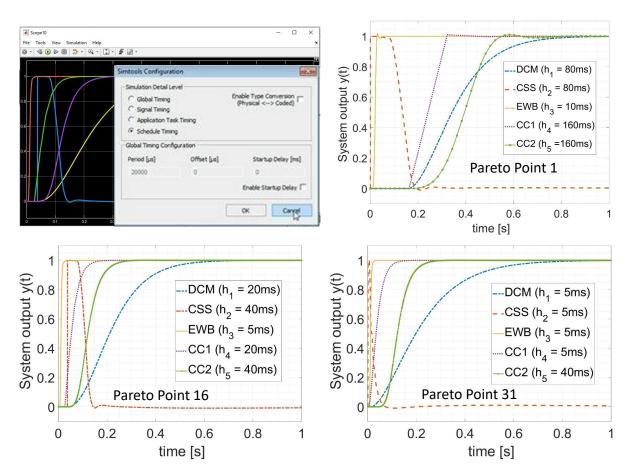

**Multi-objective co-optimization for distributed CPSs:** Traditionally, in a CPS, control and platform designs are carried out in their isolated design trajectories and then integrated. This leads to an error-prone design or a long debugging and integration phase. In this context, we study a specific automotive setting where multiple distributed control applications share a FlexRay communication bus and propose a *correct-by-construction co-design approach* that simultaneously synthesizes control and platform parameters. In the emerging area of control-platform co-design, for the first time, we consider to *co-optimize* control performance and resource usage, thereby, obtaining a *Pareto front* where each Pareto point is a valid design configu-

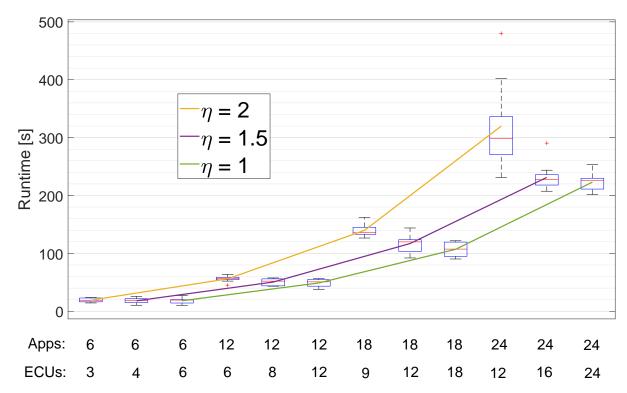

ration representing a trade-off between the two design objectives. While such a co-optimization problem is often intractable, we explore the large design space using a tailor-made *two-stage optimization* technique. In the first stage, for each application, we design *prospective* optimal controllers using different amounts of resources considering constraints imposed by the FlexRay protocol. In the second stage, we employ a nested *three-layer* optimization technique to determine the Pareto front. In the outermost layer, we iterate through different possible values of resource usage. In the second layer, we solve a *mixed-integer linear programming (MILP)* problem to determine an optimal set of controllers that uses the given amount of resources and maximizes the system performance. In the innermost layer, we try to find a feasible schedule for the selected set of controllers by solving an *integer linear programming (ILP)* problem. Results show that for a relatively small case study comprising 5 applications mapped on to 3 electronic control units (ECUs), the average control performance can be improved by 41.14% of the required value at the cost of 27.5% more communication resource, i.e., there is a significant trade-off opportunity. Our approach also scales to a bus cluster comprising 24 applications.

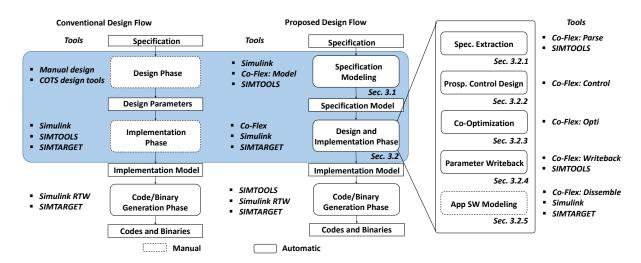

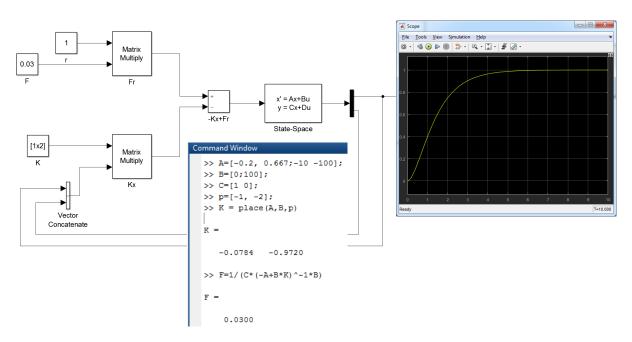

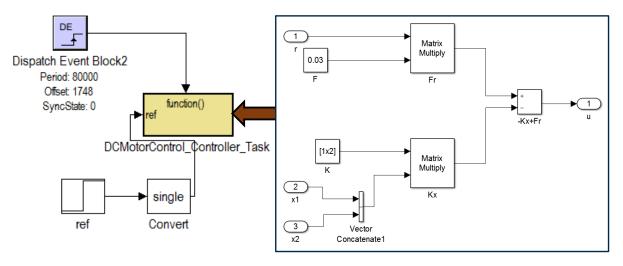

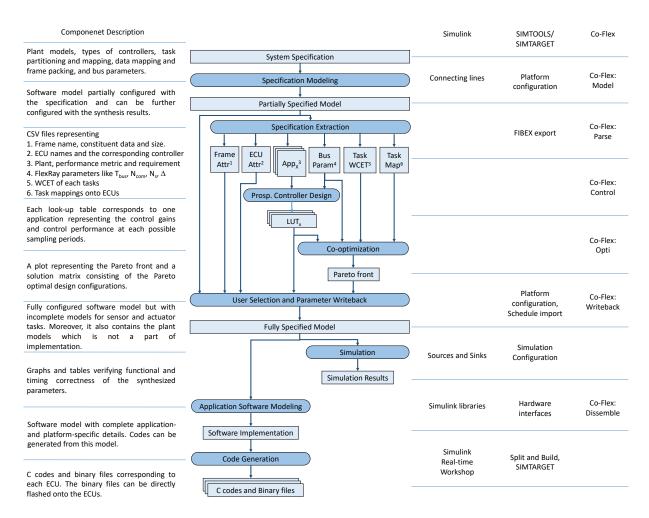

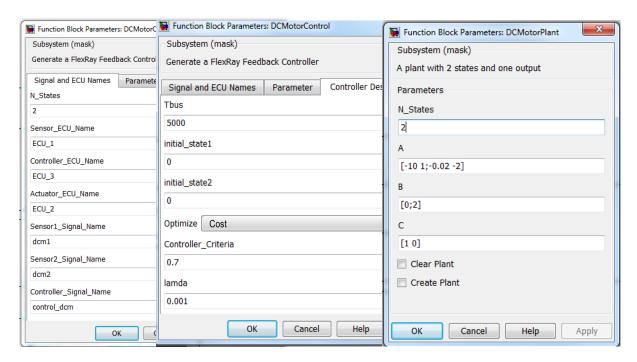

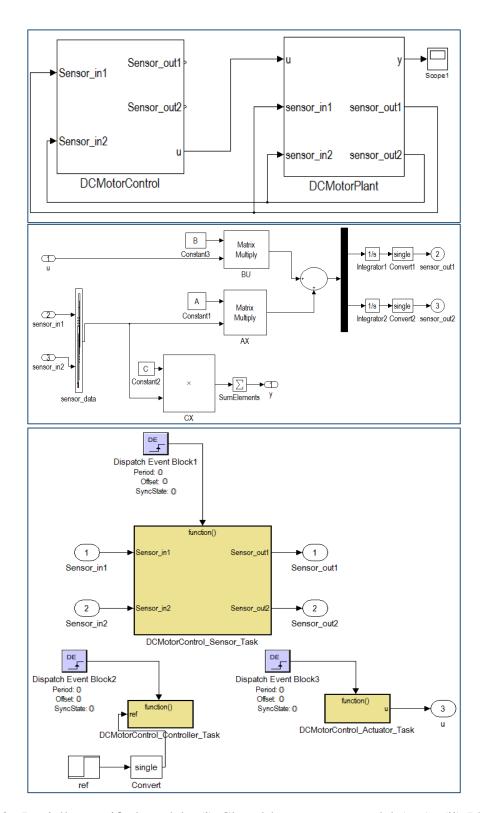

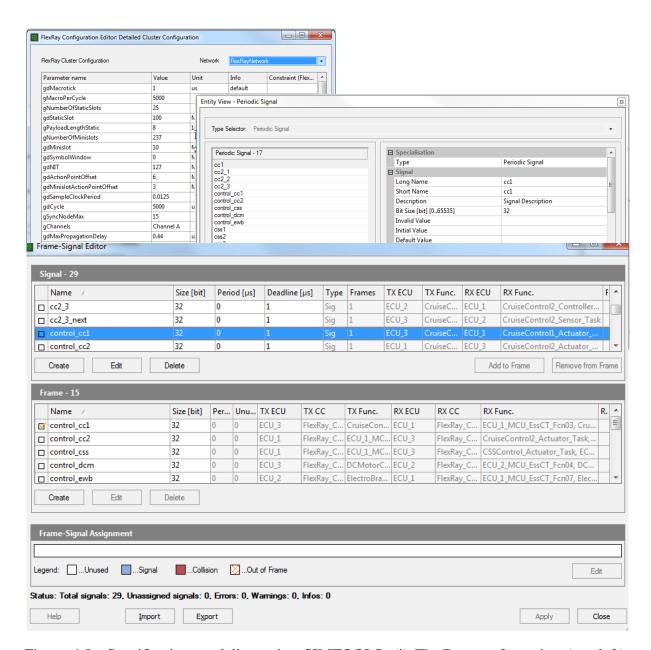

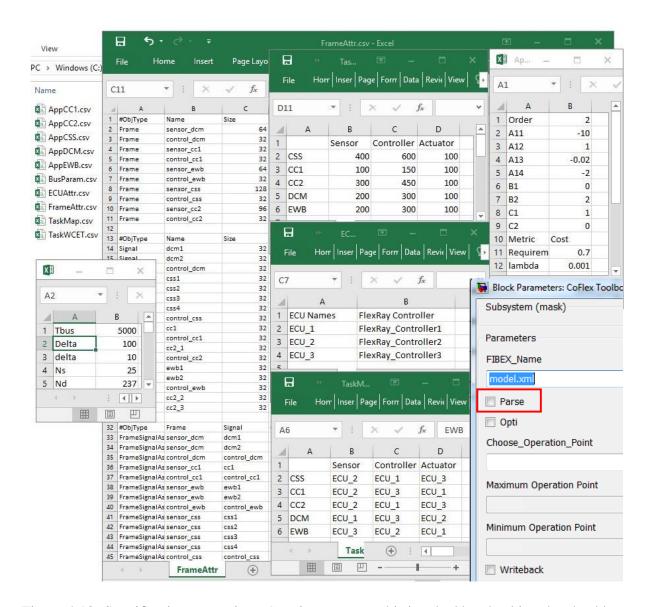

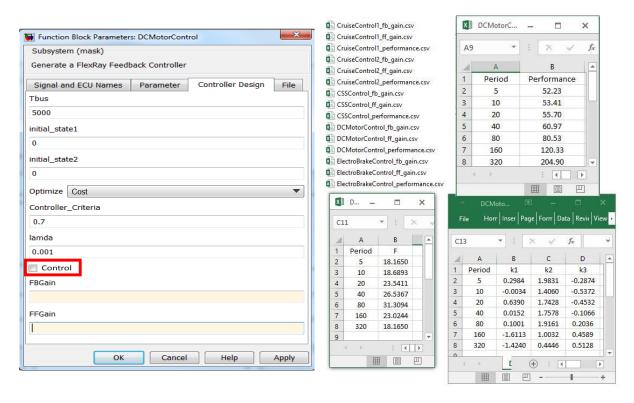

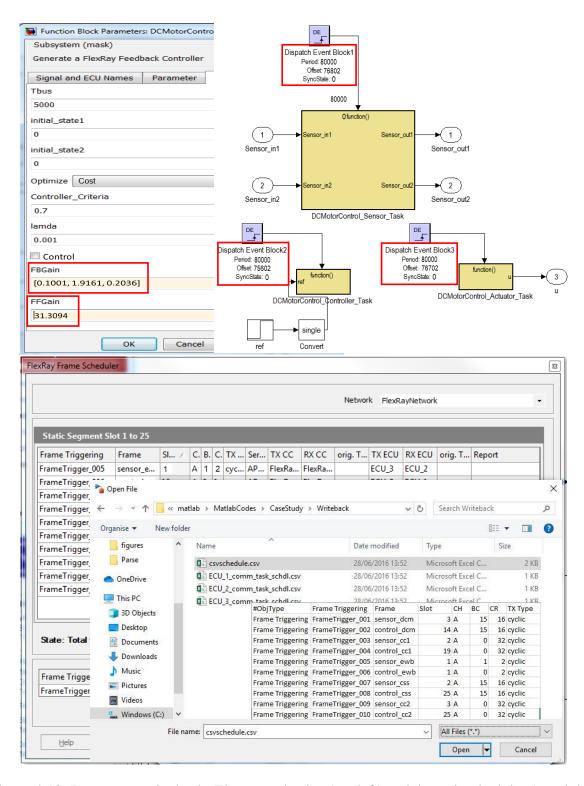

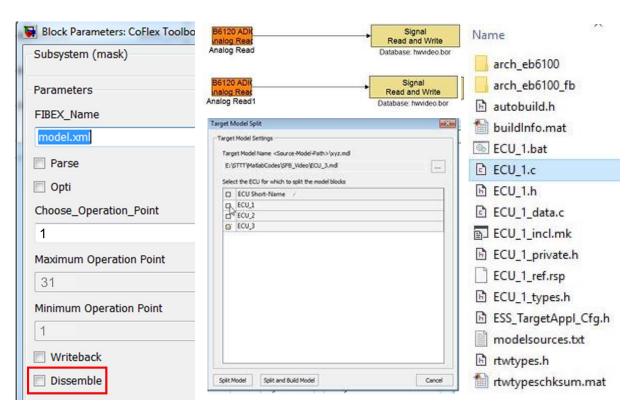

Tool integration for automated synthesis and implementation of distributed CPSs: While we have developed a state-of-the-art co-design approach for FlexRay-based distributed automotive CPSs, the lack of integrated industrial tools prevents it to be evaluated in industrial settings. In effect, this leads to a *gap* in the state-of-the-art and the state-of-practice. Towards bridging this gap, we have developed a *toolchain* by integrating the proposed co-optimization approach into commercially available tools. This toolchain uses MATLAB/Simulink for modeling control systems and SIMTOOLS/SIMTARGET (offered by Elektrobit) for modeling the distributed embedded platform. Besides exploiting the functionalities of existing tools, we also offer tools that automate specification extraction, control-platform co-design, and parameter configuration. Therefore, the proposed toolchain enables *design automation* and therefore, allows convenient design and implementation of FlexRay-based systems. Corresponding to the proposed toolchain, we also introduce a customized methodology to develop control software using a correct-by-construction technique.

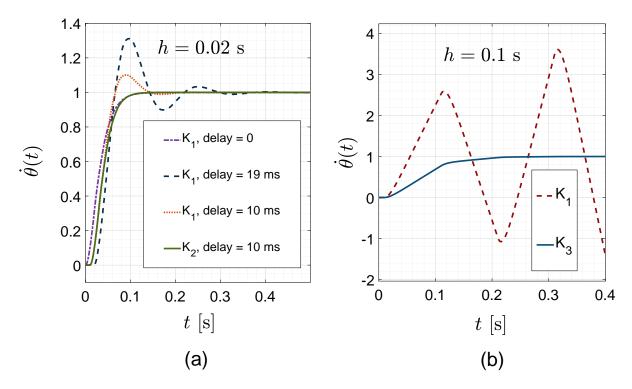

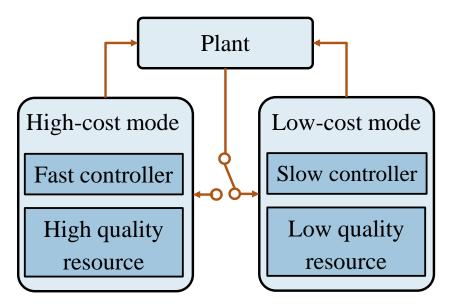

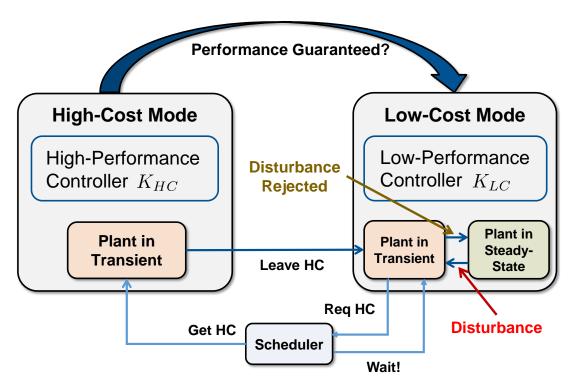

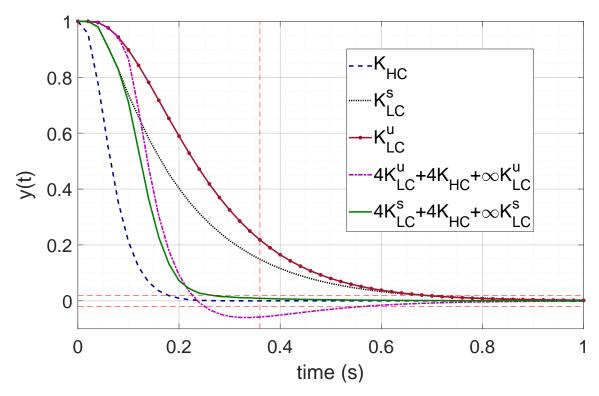

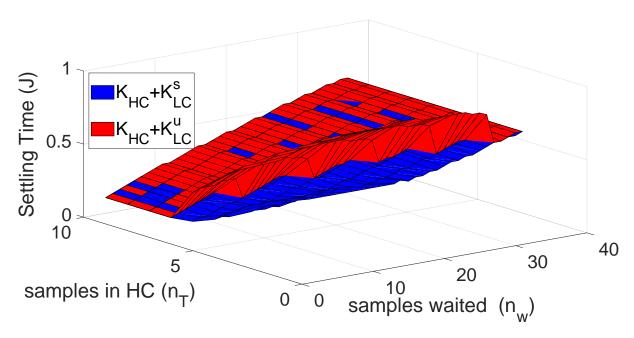

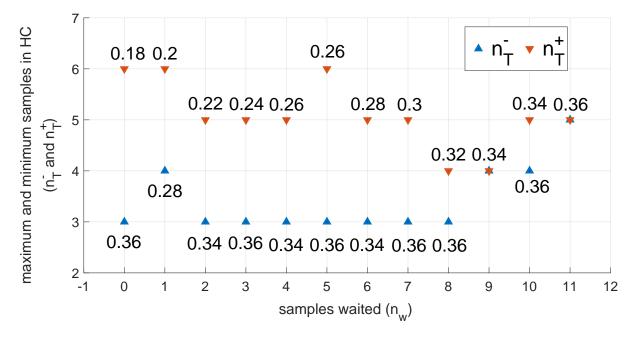

Tighter dimensioning of multi-resource CPSs with control performance guarantees: We consider a multi-resource CPS setup comprising high- and low-quality platform resources. While a high-quality resource offers timing guarantees, and hence, a higher control performance, they are significantly expensive. In cost-sensitive CPS domains like automotive, it is desirable to optimize the usage of such expensive resources. Towards this goal, we study a control scheme that comprises two modes using high-quality and low-quality resources respectively. We propose cost-efficient yet safe static and dynamic scheduling strategies to allocate high-quality resources to the bimodal controllers. For each application, we first study the switching control dynamics to derive the minimum requirement for high-quality resources based on control specification. Subsequently, we formulate a Satisfiability Modulo Theories (SMT) problem to statically allocate the required resources to the applications while maximizing the extensibility of the schedule. Furthermore, for each application, we derive: (i) the maximum time for which the controller can wait for high-quality resources without violating the performance constraint, and (ii) for certain wait time, the minimum and the maximum time for which the controller can use the high-quality resources continuously. Using these timing information, we devise a safe switching scheme for the controllers and a scheduling policy based on dynamically computed priorities of the applications. The resource dimensioning problem for the dynamic scheduling is solved in two nested layers where the outer layer is a *first-fit heuristic* while in the inner layer we formally verify a network of *timed-automata* representing the applications and the scheduler. Results suggest that resource dimensioning can be significantly *tightened* (i.e., 50% in certain cases) using the proposed scheduling strategies compared to existing approaches.

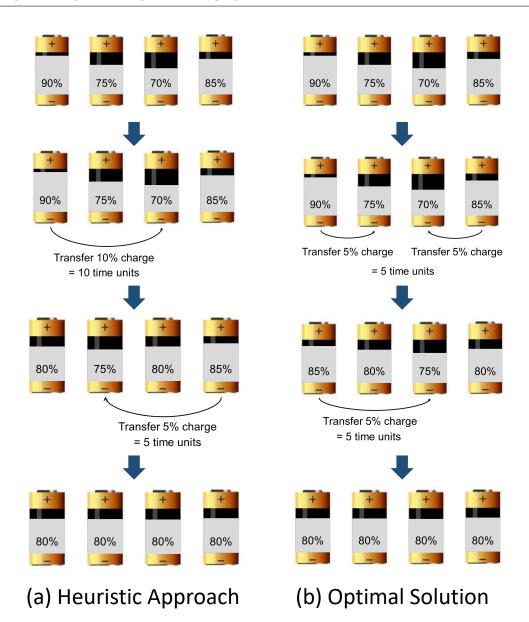

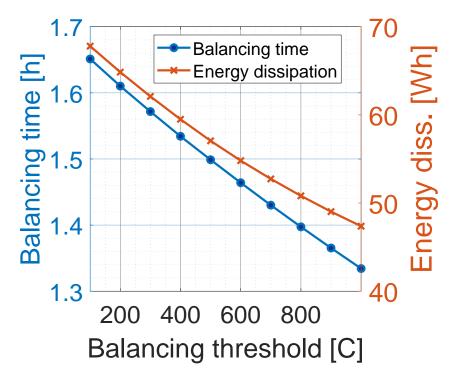

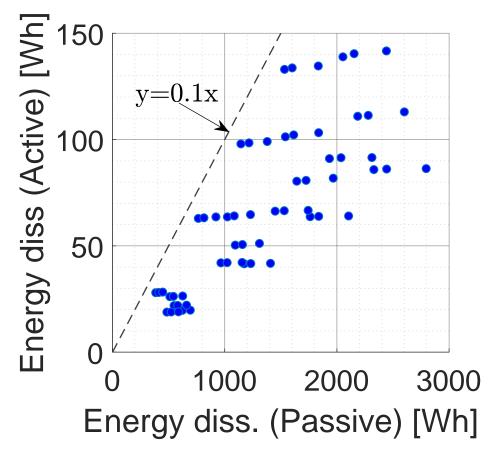

Energy- and time-optimal active cell balancing in battery packs: Electric vehicles (EVs) are becoming the mainstream in the automotive industry. In EVs, high-power battery packs, comprising several hundreds of cells in series and parallel, act as the main energy source. Safety and performance of such a pack are ensured by a hardware/software system, i.e., the battery management system (BMS). Cell balancing is a crucial task of BMSs that maximizes the usable capacity of the pack. In active cell balancing, the charge is transferred between series-connected cells such that the charge levels of all cells become equal. The problem of cell balancing has been primarily studied in the power-electronics community where low-power charge transfer circuits have been proposed. However, control algorithms operating these circuits have relied only on heuristics. No results on optimal cell balancing with respect to energy dissipation and balancing time respectively were known prior to our work. We, for the first time, formulate the cell balancing problem from a real-time CPS perspective and propose control algorithms that minimize energy dissipation and balancing time respectively. We show that holistic optimization is possible by integrated modeling of the cell chemistry, charge transfer process, charge equalization, and the constraints imposed by the charge transfer circuit and by the BMS architecture. We partition the cell balancing problem into two stages without losing any optimality guarantee. In the first stage, we formulate MILP problems to determine the time- and the energy-optimal sets of charge transfers respectively that will realize charge equalization. In the second stage, we formulate a minimum vertex coloring (MVC) problem to schedule the charge transfer sets obtained in the first stage. Using the proposed optimization, balancing time can be improved from 11.04 h to 4.82 h and energy dissipation can be reduced from 211 Wh to 133 Wh for certain balancing scenarios. Our proposed technique has real benefits in *improving* the charging time and extending the driving range of EVs.

**Summary:** This thesis shows that *holistic optimization* is possible in the design of CPSs when models from different engineering domains are considered in an *integrated* framework. Towards the optimal design of CPSs, it is important to determine the *interplay* between different design domains. Exploiting the interplay and by studying the characteristics of the design problems, customized optimization techniques are developed towards *efficient and scalable design space exploration (DSE)* for CPSs.

# Kurzfassung

In einem cyber-physischen System (CPS) wird der physikalische Prozess durch einen Software-Algorithmus gesteuert, der auf einer Hardware-Plattform läuft. Es existiert eine enge Kopplung zwischen dem physikalischen Verhalten des Systems, der Hardware und der Software. Derartige Systeme sind oft sicherheitskritisch und haben strenge Leistungsanforderungen (z.B. schnelle Stabilisierung nach einer Störung). Häufig sind solch Systeme auch kosten-kritisch und müssen mit begrenzten Plattform Ressourcen auskommen (z.B. eine geringe Zahl Kommunikationsslots oder geringe Verlustenergie). Der umfassende Entwurf eines CPS erfordert jedoch die Integration heterogener Modelle, die aus verschiedenen Engineering-domänen stammen, z.B. mechanische Prozesse, elektrische und elektronische Geräte, Regelungsalgorithmen und Software-Implementierungen. Daher führt der Entwurf von hochleistungsfähigen und dennoch ressourceneffizienten CPS zu anspruchsvollen Optimierungsproblemen.

Herausforderungen bei der Multi-Domain-Kopplung beim Entwurf von CPS: Die umfassende Modellierung und der Entwurf von CPS sind mit mehreren Herausforderungen verbunden. Erstens ist es nicht trivial, heterogene Modelle in einem einheitlichen Framework darzustellen. Beispielsweise entwickelt sich ein physikalisches System kontinuierlich gemäß eines Satzes von Differentialgleichungen, während der entsprechende Controller möglicherweise periodisch operiert, und bei jedem Einsatz konkurriert er um die Ressourcen je nach der eingesetzen Scheduling Policy, die mit einem endlichen Zustandsautomat dargestellt werden kann. Es ist zu beachten, dass häufig Hybridsystem-Theorie angewandt wird, um eine solche Heterogenität zu bewältigen, wobei ein solcher Ansatz jedoch oft mit Skalierbarkeitsproblemen einhergeht. Zweitens wächst mit zunehmender Größe und Komplexität industrieller CPS (wie sie bei modernen Fahrzeugen eingesetzt werden) der integrierte Designraum exponentiell an, so dass das Designproblem leicht unlösbar werden kann. Drittens könnten die Anforderungen aus verschiedenen Designbereichen miteinander in Konflikt geraten, z. B. ist die Verbesserung der Steuerungsleistung oft auf Kosten von mehr Ressourcen möglich. Schließlich beinhaltet der Entwurf von CPS in der Regel einen disjunkten Satz von Werkzeugen, die von verschiedenen Anbietern angeboten werden. Es ist nicht trivial, eine automatisierte Toolchain zu entwickeln, die modernste Entwurfstechniken bietet und gleichzeitig eine nahtlose Verbindung zu den bestehenden Werkzeugen herstellt und deren Vorteile bewahrt.

Diese Arbeit beschreibt unsere Bemühungen zur Bewältigung der oben genannten Herausforderungen unter Verwendung maßgeschneiderter hybrider Optimierungstechniken und neuartiger Design-Flows. Wir nehmen Automobilsysteme für unsere Fallstudie an, weil sie sicherheitskritische, ressourcenbeschränkte und verteilte CPS darstellen.

**Pareto-Optimierung für verteilte CPS:** Traditionell findet beim Design von CPS die Entwicklung von Regelung und Plattform getrennt statt. Erst am Ende werden beide Entwürfe integriert.

Dies führt zu einem fehleranfälligen Design oder zu einer langen Debugging- und Integrationsphase. In diesem Zusammenhang untersuchen wir eine spezifische Automobilumgebung, in der sich mehrere verteilte Steuerungsanwendungen einen FlexRay-Kommunikationsbus teilen, und schlagen einen Correct-by-Construction-Co-Design-Ansatz vor, bei dem Steuerungs- und Plattformparameter gleichzeitig synthetisiert werden. Im noch jungen Gebiets des Co-Designs von Steuerungsplattformen erwägen wir zum ersten Mal, die Steuerungsleistung und den Ressourcenverbrauch zu optimieren und dadurch eine Pareto-Front zu erhalten, bei der jeder Pareto-Punkt eine gültige Designkonfiguration darstellt, die einen Kompromiss zwischen den beiden Designzielen darstellt. Während ein solches Co-Optimierungsproblem oft unlösbar ist, untersuchen wir den großen Designraum mit einer maßgeschneiderten zweistufigen Optimierungstechnik. In der ersten Phase entwerfen wir für jede Anwendung potentielle optimale Controller unter Verwendung unterschiedlicher Ressourcenmengen und unter Berücksichtigung der durch das FlexRay-Protokoll auferlegten Einschränkungen. In der zweiten Stufe verwenden wir eine verschachtelte drei-stufige Optimierungstechnik zur Bestimmung der Pareto-Front. In der ersten Stufe iterieren wir durch verschiedene mögliche Werte der Ressourcennutzung. In der zweiten Stufe lösen wir ein MILP-Problem (Mixed-Integer Linear Programming), um einen optimalen Satz von Controllern zu bestimmen, der die gegebene Menge an Ressourcen nutzt und die Systemleistung maximiert. In der letzten Stufe versuchen wir, durch die Lösung eines ganzzahligen linearen Programmierungsproblems (ILP-Problems) eine realisierbaren Schedule für den ausgewählten Satz von Controllern zu finden. Die Ergebnisse zeigen, dass bei einer relativ kleinen Fallstudie mit 5 Anwendungen, die auf 3 elektronische Steuergeräte (ECUs) abgebildet werden, die durchschnittliche Regelleistung um 41,14% des erforderlichen Wertes verbessert werden kann, und das bei Kosten von 27,5% mehr Kommunikationsressourcen. D.h. es besteht ein erheblicher Spielraum für Kompromisslösungen. Unser Ansatz lässt sich auch auf ein Bus-Cluster mit 24 Anwendungen skalieren.

Tool-Integration für die automatisierte Synthese und Implementierung verteilter CPS: Wir haben einen hochmodernen Co-Design-Ansatz für FlexRay-basierte verteilte CPS in der Automobilindustrie entwickelt, jedoch verhindert das Fehlen integrierter industrieller Tools eine Evaluierung in industriellen Umgebungen. Tatsächlich führt dies zu einer Lücke im Stand der Technik und in der Anwendungspraxis. Um diese Lücke zu überbrücken, haben wir eine Toolchain entwickelt, indem wir den vorgeschlagenen Co-Optimierungsansatz in kommerziell verfügbare Werkzeuge integriert haben. Diese Toolchain verwendet MATLAB/Simulink für die Modellierung von Steuerungssystemen und SIMTOOLS/SIMTARGET (von Elektrobit) für die Modellierung der verteilten eingebetteten Plattformen. Neben der Nutzung der Funktionalitäten bestehender Werkzeuge bieten wir auch Werkzeuge an, die die Extraktion von Spezifikationen, das Co-Design von Steuerungsplattformen und die Parameterkonfiguration automatisieren. Daher ermöglicht die vorgeschlagene Werkzeugkette die Automatisierung des Designs und damit bequemen Entwurf und Implementierung von FlexRay-basierten Systemen. Entsprechend der vorgeschlagenen Toolchain führen wir auch eine angepasste Methodik zur Entwicklung von Steuerungssoftware mit einer Correct-by-Construction-Technik ein.

Engere Dimensionierung von Multi-Ressourcen-CPS mit Kontrollleistungsgarantien: Wir betrachten einen Multi-Ressourcen-CPS-Aufbau mit hochwertigen und minderwertigen Plattformressourcen. Eine qualitativ hochwertige Ressource bietet zwar Timing-Garantien und damit eine höhere Steuerungsleistung, ist aber erheblich teurer. In kostensensiblen CPS-

Anwendungsgebieten wie der Automobilindustrie ist es wünschenswert, den Einsatz solch teurer Ressourcen zu optimieren. Um dieses Ziel zu erreichen, untersuchen wir ein Kontrollschema, das zwei Modi umfasst, die qualitativ höherwertige bzw. qualitativ minderwertige Ressourcen nutzen. Und wir schlagen kosteneffiziente und dennoch sichere statische und dynamische Planungsstrategien vor, um den bi-modalen Steuerungseinheiten qualitativ hochwertige Ressourcen zuzuweisen. Für jede Anwendung untersuchen wir zunächst die Schalt-Regeldynamik, um auf der Grundlage der Regelspezifikation die Mindestanforderung an hochwertige Ressourcen abzuleiten. Anschließend formulieren wir ein Problem der Satisfiability Modulo Theories (SMT) um den Anwendungen die erforderlichen Ressourcen statisch zuzuweisen und gleichzeitig die Erweiterbarkeit des Schedulers zu maximieren. Darüber hinaus leiten wir für jede Anwendung folgendes ab: (i) die maximale Zeitspanne, während welcher der Controller auf qualitativ hochwertige Ressourcen warten kann ohne die Leistungsbeschränkung zu verletzen, und (ii) für bestimmte Wartezeiten die minimale und maximale Zeitspanne, während welcher der Controller die qualitativ hochwertigen Ressourcen kontinuierlich nutzen kann. Unter Verwendung dieser Zeitinformationen entwickeln wir ein sicheres Umschaltschema für die Controller und eine Planungsrichtlinie, die auf dynamisch berechneten Prioritäten der Anwendungen basiert. Das Ressourcendimensionierungsproblem für das dynamische Scheduling wird in zwei verschachtelten Schichten gelöst, wobei die äußere Schicht eine First-Fit-Heuristik ist, während wir in der inneren Schicht ein Netzwerk von timed automata, die die Anwendungen und den Scheduler repräsentieren, formal verifizieren. Die Ergebnisse deuten darauf hin, dass die Ressourcendimensionierung mit den vorgeschlagenen Scheduling Strategien im Vergleich zu bestehenden Ansätzen deutlich (d.h. in bestimmten Fällen um 50%) gestrafft werden kann.

Energie- und zeitoptimales aktives Cell Balancing in Akkupacks: Elektrofahrzeuge (Electric Vehicles, EVs) werden mehr und mehr zum Mainstream in der Automobilindustrie. In EVs dienen Hochleistungsbatteriepakete, die aus mehreren hundert Zellen bestehen, welche in Serie sowie parallel geschaltet sind, als Hauptenergiequelle. Sicherheit und Leistung eines solchen Packs werden durch ein Hardware/Software-System, d. h. das Batteriemanagementsystem (BMS), gewährleistet. Das Ausgleichen der Batteriezellen (cell balancing) ist eine entscheidende Aufgabe der BMS, die die nutzbare Kapazität des Packs maximiert. Beim aktiven Cell Balancing wird die Ladung zwischen in Reihe geschalteten Zellen so übertragen, dass die Ladungsniveaus aller Zellen ausgeglichen werden. Das Problem des Cell Balancings wurde vor allem in der Leistungselektronik untersucht, wo Ladungsübertragungsschaltungen mit geringer Leistung vorgeschlagen wurden. Die Steueralgorithmen, die diese Schaltkreise betreiben, haben sich jedoch nur auf Heuristiken gestützt. Vor unserer Arbeit waren keine Ergebnisse zum optimalen Cell Balancing in Bezug auf Energiedissipation bzw. Ausgleichsdauer bekannt. Zum ersten Mal formulieren wir das Cell Balancing Problem aus einer Echtzeit-CPS-Perspektive und schlagen Regelalgorithmen vor, die die Energiedissipation bzw. die Ausgleichsdauer minimieren. Wir zeigen, dass eine ganzheitliche Optimierung durch integrierte Modellierung der Zellchemie, des Ladungstransferprozesses, des Ladungsausgleichs und der durch die Ladungsübertragungsschaltung und die BMS-Architektur auferlegten Einschränkungen möglich ist. Wir teilen das Problem des Cell Balancing in zwei Phasen auf, ohne dabei die Garnatie auf Optimalität zu verlieren. In der ersten Stufe formulieren wir MILP-Probleme, um die zeit- bzw. energieoptimalen Mengen von Ladungstransfers zu bestimmen, die einen Ladungsausgleich realisieren. In der zweiten Stufe formulieren wir ein MVC-Problem (Minimum Vertex Coloring), um

die in der ersten Stufe erhaltenen Ladungstransfermengen zu planen. Mit der vorgeschlagenen Optimierung kann die Balancing Dauer von 11,04 h auf 4,82 h verbessert und die Energiedissipation für bestimmte Ausgleichsszenarien von 211Wh auf 133Wh reduziert werden. Die von uns vorgeschlagene Technik hat als Vorteile, dass sie sowohl die Ladezeit verbessert als auch die Reichweite von EVs erhöht.

**Zusammenfassung:** Diese Arbeit zeigt, dass eine ganzheitliche Optimierung bei der Gestaltung von CPS möglich ist, wenn Modelle aus verschiedenen Engineering-Domänen in einem integrierten Framework betrachtet werden. Für die optimale Entwicklung von CPS ist es wichtig, das Zusammenspiel zwischen verschiedenen Entwurfsbereichen zu bestimmen. Unter Ausnutzung des Zusammenspiels und durch Untersuchung der Charakteristika der Entwurfsprobleme werden maßgeschneiderte Optimierungstechniken zur effizienten und skalierbaren Design Space Exploration (DSE) für CPS entwickelt.

# Acknowledgements

At the end of 4 years 7 months 19 days, finally I get an opportunity to reflect on my journey as a researcher so far. During this journey, there are several people who has supported me in different ways, and I would like to thank them all.

First and foremost, I am grateful to Samarjit Chakraborty for his constant guidance, support, and encouragement. He interviewed me for my master's admission at TU Munich, and then, co-incidentally, we met on the very first week I landed in Munich, and since then I have always looked up to him as my advisor. He offered me a HiWi position soon after and now, I am employed at the Institute of Real-Time Computer systems for more than 6 years. As a doctoral advisor, he always had excellent inputs in my research. His constant determination to solve challenging problems and do high-quality research has motivated me to publish in top-ranked conferences and journals. I am also grateful to him for having me introduced to academics around the world with whom I have had successful collaborations. Nevertheless, during these years, we have had several disagreements. I must admit that he has always understood my position and supported my decision. I apologize for the inconveniences caused to him.

Furthermore, I am thankful to Prof. Herkersdorf for agreeing to examine my thesis. Coming from a more traditional electrical engineering background, the courses he offered during my master's have helped me to develop a good background on processor architecture and scheduling, memory architecture, and hardware/software co-design. This has helped me a lot in my research. Also, a hearty thank to Prof. Rigoll for agreeing to head the examination committee. He always comes across as a very nice person.

Sincere thanks to the co-authors of the publications I have had. Licong Zhang has mentored me in my early days as a researcher. I have revisited control theory using Dip Goswami's teaching material and also had several enriching discussions with him. Wanli Chang and Swaminathan Narayanaswamy have been excellent to work with. I am grateful to Prof. Sanjoy Mitter to have spent so much time with me discussing research ideas, while also hosting me at MIT. I greatly appreciate Qi Zhu to have hosted me at the Northwestern University and I hope to follow up soon and write some papers from the collaboration. I would also like to mention Anuradha Annaswamy, Xiaobo Sharon Hu, Thomas Heurung, Michael Balszun, Alma Pröbstl, Anna Minaeva, Soumyajit Dey, and Sumana Ghosh for successful research collaborations.

The research for this doctoral thesis has been conducted in the Institute of Real-Time Computer System at TU Munich. Thanks to Irene Dippold, Renate Schwarz, Kathrin Schmöller, and Reinald Gfüllner for their help and support in conducting operations in the institute including teaching, organizing travels, claiming expenses, among others. A special thank to each and every colleague at RCS as I am sure I have received help at some point in time during these years. I would like to mention Alma Pröbstl with whom I have shared office. Besides research collab-

orations, she has been of great help especially with my poor German skills. Thanks to Philipp Kindt, Daniel Yunge, Nils Heitmann, and Martin Geier for several enriching discussions and to Nadja Heitmann for her help regarding administrative and several other important matters.

The superstar in this journey who has contributed to each and every achievement I have had until now without asking for a credit has been my wife, Mallika Dey. I cannot thank her enough for her constant support. Samarjit has never been a nagging supervisor (of course I am not complaining), however, she always kept me on my toes to produce results before submission deadlines. She always lent ears to my ideas and with her background in computer science, discussions with her have always been productive. In retrospect, I would add her as a co-author in a couple of my publications. The biggest thank goes to our tiny 4-month old daughter, Raima Roy, to have fought the bravest battle after her birth. She has been the greatest encouragement towards writing and submitting my thesis in the past few months.

My sincere gratitude to my father, Aloke Kumar Roy, to have encouraged me in the best way he could, to pursue higher studies in Germany. I hope my mother, Debahuti Roy, is blessing me from wherever she is now, and I believe that she is making unexpected things happen for me by coaxing the almighty. I have a great family who always keep me amused. My brother, Debalok Roy, my cousins and my sisters-in-law never fail to entertain me whenever I am down.

I do not expect anyone to read this far, however, if you have and have not found your name, I apologize and would like to thank you as I am sure you are my well wisher.

# Contents

| Abstract         |                               |         | iii                                                         |    |  |

|------------------|-------------------------------|---------|-------------------------------------------------------------|----|--|

| Kı               | Kurzfassung (German abstract) |         |                                                             |    |  |

| Acknowledgements |                               |         |                                                             | xi |  |

| 1                | Intr                          | oductio | n                                                           | 1  |  |

|                  | 1.1                           | Autom   | notive Cyber-Physical Systems                               | 3  |  |

|                  |                               | 1.1.1   | Electronic Control Units                                    | 4  |  |

|                  |                               | 1.1.2   | Communication Buses                                         | 5  |  |

|                  |                               | 1.1.3   | Automotive Software                                         | 8  |  |

|                  |                               | 1.1.4   | Battery Packs                                               | 9  |  |

|                  |                               | 1.1.5   | Battery Management Systems                                  | 11 |  |

|                  | 1.2                           | Motiva  | ation and Challenges                                        | 13 |  |

|                  |                               | 1.2.1   | Motivation towards Multi-Domain Coupling in CPSs Design     | 14 |  |

|                  |                               |         | 1.2.1.1 Distributed control systems: A motivational example | 15 |  |

|                  |                               |         | 1.2.1.2 Active cell balancing: A motivational example       | 18 |  |

|                  |                               | 1.2.2   | Challenges towards Multi-Domain Coupling in CPSs Design     | 20 |  |

|                  | 1.3                           |         | tion of Design Approaches for CPSs                          | 21 |  |

|                  |                               | 1.3.1   | Separation of Concerns                                      | 21 |  |

|                  |                               | 1.3.2   | CPS-Oriented Design Approaches                              | 23 |  |

|                  |                               | 1.3.3   | Control-Platform Co-Synthesis for CPSs                      | 26 |  |

|                  | 1.4                           |         | butions and Organization                                    | 28 |  |

|                  | 1.5                           |         | graphic Notes                                               | 31 |  |

|                  |                               | 1.5.1   | Thesis-Related Publications                                 | 31 |  |

|                  |                               | 1.5.2   | Other Publications                                          | 33 |  |

| 2                | Mathematical Background       |         |                                                             |    |  |

|                  | 2.1                           | Feedba  | ack Control Systems                                         | 35 |  |

|                  |                               | 2.1.1   | Continuous-Time State-Space Model                           | 36 |  |

|                  |                               | 2.1.2   | Discrete-Time State-Space Model                             | 38 |  |

|                  |                               | 2.1.3   | Delayed Discrete-Time State-Space Model                     | 39 |  |

|                  |                               | 2.1.4   | Stability of Discrete-Time Systems                          | 41 |  |

|                  |                               | 2.1.5   | Controller Design                                           | 42 |  |

|                  | 2.2                           | Distrib | outed Controller Implementation                             | 44 |  |

xiv CONTENTS

|   |      | 2.2.1 Time-Triggered Tasks                                                |

|---|------|---------------------------------------------------------------------------|

|   |      | 2.2.2 FlexRay Communication                                               |

|   | 2.3  | Charge Transfer Circuits for Active Cell Balancing                        |

|   |      | 2.3.1 Charge Transfer Circuit Architectures                               |

|   |      | 2.3.2 Modeling of Charge Transfer                                         |

|   | 2.4  | Optimization and Verification                                             |

|   |      | 2.4.1 Linear Programming                                                  |

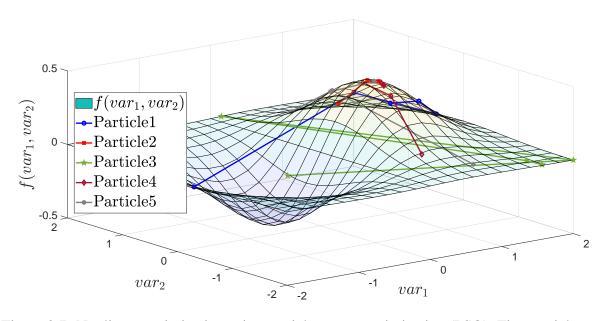

|   |      | 2.4.2 Particle Swarm Optimization                                         |

|   |      | 2.4.3 Satisfiability Modulo Theories                                      |

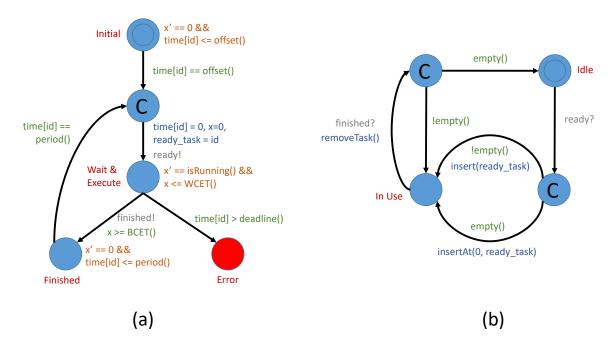

|   |      | 2.4.4 Timed Automata                                                      |

|   |      | 2.4.5 Minimum Vertex Coloring                                             |

|   |      |                                                                           |

| 3 |      | ti-Objective Co-Optimization for Distributed Cyber-Physical Systems  67   |

|   | 3.1  | Introduction                                                              |

|   | 3.2  | Control-Platform Co-Design Problem                                        |

|   |      | 3.2.1 Problem Setting                                                     |

|   |      | 3.2.2 Problem Definition                                                  |

|   |      | 3.2.3 Proposed Design Flow                                                |

|   | 3.3  | Stage 1: Prospective Controller Design                                    |

|   | 3.4  | Stage 2: Constrained Optimization Problem                                 |

|   |      | 3.4.1 Constraints                                                         |

|   |      | 3.4.2 Optimization Objectives                                             |

|   | 3.5  | Stage 2: Proposed Multi-Layer Hybrid Optimization                         |

|   |      | 3.5.1 Outer Layer                                                         |

|   |      | 3.5.2 Middle and Inner Layers                                             |

|   | 3.6  | Experimental Results                                                      |

|   |      | 3.6.1 A Case Study                                                        |

|   |      | 3.6.2 Scalability Analysis                                                |

|   | 3.7  | Related Works                                                             |

|   | 3.8  | Conclusion                                                                |

| 4 | Tool | Integration for Automated Synthesis and Implementation                    |

|   |      | istributed Cyber-Physical Systems 101                                     |

|   | 4.1  | Introduction                                                              |

|   | 4.2  | Conventional Design and Implementation of Distributed Automotive CPSs 105 |

|   |      | 4.2.1 Design Phase                                                        |

|   |      | 4.2.2 Implementation Phase                                                |

|   |      | 4.2.3 Code Generation and Hardware Implementation Phase 109               |

|   |      | 4.2.4 Limitations of the Conventional Approach                            |

|   | 4.3  | Automated Software Synthesis using the Proposed Integrated Toolchain 109  |

|   |      | 4.3.1 Specification Modeling                                              |

|   |      | 4.3.2 Design and Implementation                                           |

|   |      | 4.3.2.1 Specification Extraction                                          |

|   |      | 4.3.2.2 Prospective Controller Design                                     |

|   |      | IIOSPITAI CONMONDI DUIGNIII III III III III III III III                   |

CONTENTS

|   |     |          | 4.3.2.3 Co-Optimization                                                | 16 |  |  |  |

|---|-----|----------|------------------------------------------------------------------------|----|--|--|--|

|   |     |          | 4.3.2.4 Parameter Writeback                                            | 18 |  |  |  |

|   |     |          | 4.3.2.5 Application Software Modeling                                  | 19 |  |  |  |

|   | 4.4 | A Case   | e Study                                                                | 20 |  |  |  |

|   | 4.5 |          | d Works                                                                |    |  |  |  |

|   | 4.6 |          | asion                                                                  |    |  |  |  |

| 5 | 9   |          |                                                                        |    |  |  |  |

|   | Con | trol Per | formance Guarantees 13                                                 | 33 |  |  |  |

|   | 5.1 | Introdu  | uction                                                                 | 33 |  |  |  |

|   | 5.2 | Proble   | m Setting                                                              | 38 |  |  |  |

|   |     | 5.2.1    | Heterogeneous Resources                                                | 38 |  |  |  |

|   |     | 5.2.2    | Bimodal Control Strategy                                               | 40 |  |  |  |

|   | 5.3 | Statica  | ally Scheduling the Bimodal Controllers                                | 42 |  |  |  |

|   |     | 5.3.1    | Stage 1: Deriving Minimum Resource Requirements                        | 43 |  |  |  |

|   |     | 5.3.2    | A Motivational Example                                                 | 46 |  |  |  |

|   |     | 5.3.3    | Stage 2: Optimal Allocation of the TDMA Slots                          | 48 |  |  |  |

|   | 5.4 | Dynan    | nically Scheduling the Bimodal Controllers                             | 51 |  |  |  |

|   |     | 5.4.1    | Switching Strategy                                                     | 51 |  |  |  |

|   |     | 5.4.2    | Scheduling Policy                                                      | 53 |  |  |  |

|   |     | 5.4.3    | A Motivational Example                                                 | 55 |  |  |  |

|   | 5.5 | Resour   | rce Dimensioning for Dynamic Scheduling                                | 56 |  |  |  |

|   |     | 5.5.1    | Inner Layer: Verifying Control Performance                             | 57 |  |  |  |

|   |     | 5.5.2    | Outer Layer: Mapping Applications to Slots                             | 51 |  |  |  |

|   | 5.6 | Experi   | mental Results                                                         | 52 |  |  |  |

|   | 5.7 | Relate   | d Works                                                                | 58 |  |  |  |

|   | 5.8 | Conclu   | asion                                                                  | 70 |  |  |  |

| 6 | Ene | -        | d Time-Optimal Active Cell Balancing                                   | _  |  |  |  |

|   | 6.1 |          | uction                                                                 |    |  |  |  |

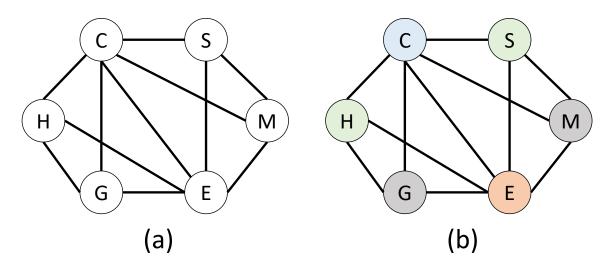

|   | 6.2 | Constr   | aint Formulation for Charge Equalization                               |    |  |  |  |

|   |     | 6.2.1    | Feasible Pairs of Cells for Charge Transfer                            |    |  |  |  |

|   |     | 6.2.2    | Charge Transfer Cycles                                                 |    |  |  |  |

|   |     | 6.2.3    | Balanced Battery Pack                                                  |    |  |  |  |

|   | 6.3 | Minim    | nizing Energy Dissipation                                              | 30 |  |  |  |

|   |     | 6.3.1    | Stage 1: Determining Optimal Charge Transfers                          | 30 |  |  |  |

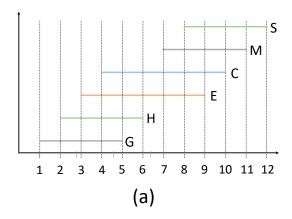

|   |     | 6.3.2    | Stage 2: Scheduling Charge Transfers                                   | 31 |  |  |  |

|   |     |          | 6.3.2.1 Concurrent Charge Transfers                                    | 31 |  |  |  |

|   |     |          | 6.3.2.2 Equivalent Vertex Coloring Problem for Schedule Synthesis . 18 | 32 |  |  |  |

|   | 6.4 | Minim    | nizing Balancing Time                                                  | 34 |  |  |  |

|   |     | 6.4.1    | Modeling Balancing Time                                                | 34 |  |  |  |

|   |     |          | 6.4.1.1 Proof of Chordality                                            | 35 |  |  |  |

|   |     |          | 6.4.1.2 Identifying Maximal Cliques                                    | 35 |  |  |  |

|   |     | 6.4.2    | Stage 1: MILP formulation                                              | 38 |  |  |  |

| •      |          |

|--------|----------|

| XV1    | CONTENTS |

| /1 V I | COLLIE   |

|                | 6.5             | Efficient Implementation of Minimum Vertex Coloring | 190 |  |  |  |  |

|----------------|-----------------|-----------------------------------------------------|-----|--|--|--|--|

|                | 6.6             | Experimental Results                                | 193 |  |  |  |  |

|                | 6.7             | Related Works                                       |     |  |  |  |  |

|                | 6.8             | Conclusion                                          | 207 |  |  |  |  |

| 7              | Conc            | cluding Remarks                                     | 209 |  |  |  |  |

| •              | 7.1             | Lessons Learnt                                      |     |  |  |  |  |

|                | 7.2             |                                                     |     |  |  |  |  |

| Bił            | Bibliography    |                                                     |     |  |  |  |  |

| List of Tables |                 |                                                     |     |  |  |  |  |

| Lis            | List of Figures |                                                     |     |  |  |  |  |

| Lis            | List of Symbols |                                                     |     |  |  |  |  |

| Ab             | Abbreviations   |                                                     |     |  |  |  |  |

# Introduction

The term "cyber-physical system" was coined by Helen Gill in 2006 at the National Science Foundation in the United States [1]. In a cyber-physical system (CPS), the physical process is controlled by a hardware/software (cyber) system. That is, the controller, monitoring the physical process and taking suitable control actions, is implemented as software components on the hardware platform. These software components (or tasks) are executed using computation and memory resources. In a distributed setting, these tasks are mapped on different processing units and data transmission between them uses communication resources.

Traditionally, control engineers design controllers taking into consideration the dynamical models of the controlled plants. On the other hand, computer engineers are only focussed on developing algorithms that enable efficient usage of hardware resources (i.e., computation, memory, and communication resources). However, for a CPS, there is a strong interplay between the control algorithm, the physical dynamics of the controlled plant and the hardware resources. It is very important to consider this interplay while designing the CPSs [2].

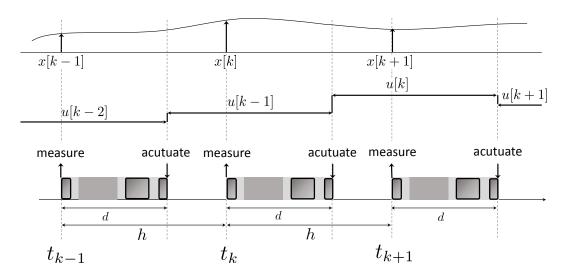

Due to the aforementioned interplay, the physical behavior of a CPS depends not only on the plant dynamics and the control law, but also on how the controller is implemented on the hardware platform, i.e., the types of hardware resources (i.e., time- or event-triggered resources) used and how the resources are allocated (i.e., the schedule) to the controller. In other words, the choice of an optimal controller depends on the dynamical model of the controlled plant and the timings of the control software [3]. Thus, for designing the controller, the relevant software timing information are as follows: (i) What kind of sampling periods are possible? (ii) What is the delay between sampling and actuation? (iii) How much is the sampling jitter? (iv) How much is the output jitter?

Note that the above timing details are typically obtained based on the platform implementation of the controller and they might not be known apriori during the controller design. In that case, certain assumptions are made on the controller implementation. These assumptions must be then considered as specification while implementing the controller [4]. In the event when a

timing assumption made during controller design could not be realized in the implementation, the control guarantees provided during the controller design might not be preserved in the implementation and safety can be jeopardized [5]. For example, the controller optimized based on a sampling period of  $5~\rm ms$ , when implemented using a control task that runs every  $10~\rm ms$ , may jeopardize the stability of the closed-loop system. In the same vein, an optimal controller, designed considering a sampling period of  $10~\rm ms$ , might become sub-optimal when implemented by a control task scheduled every  $5~\rm ms$ .

CPSs are common in domains such as automotive, avionics, industrial automation, energy, health care, and defense. Some examples of CPSs are as follows:

- Adaptive Cruise Control Systems: Modern cars are equipped with the adaptive cruise control feature, i.e., the speed of the car is automatically controlled to maintain a safe distance from the car in front.

- Cyber-Physical Traffic Control Systems: In modern transportation networks, signalized intersections are controlled based on real-time traffic information (i.e., queue lengths at incoming and outgoing roads) and they have proved to be more efficient in reducing traffic delays.

- Artificial Pancreas Systems: In patients with type 1 diabetes, artificial pancreas systems track blood glucose level continuously and automatically delivers hormone insulin when necessary.

- Heating, Ventilation and Air-Conditioning (HVAC) Systems: In smart homes and modern cars, HVAC systems are used to monitor the ambience of the interior and provide thermal comfort and ensure good indoor air quality.

- *Smart Grids*: In smart grids, advanced monitoring and forecasting is performed to deliver energy reliably and with high operation efficiency for generators and distributors.

- *Swarm Robotics*: In swarm robotics, a group of co-ordinated robots are released in a physical environment to gather information and take necessary control actions. For example, in smart agriculture, a number of unmanned aerial vehicles can be deployed in large farmlands to gather real-time information about plant health and soil quality and these information can then be used to automatically water the plants, and provide fertilizers and pesticides. Besides, swarm robotics has found its application in the field of health care, defense, smart manufacturing, among others.

Chapter organization: The rest of this chapter is organized into five sections. Section 1.1 briefly describes the automotive CPS setup considered in this thesis. In Section 1.2, we first motivate that a holistic approach is necessary integrating models from different design domains towards safe and efficient design of CPSs. We further study the challenges towards multidomain coupling in CPSs. Section 1.3 outlines the evolution of design paradigms for CPSs. In Section 1.4, we mention the scientific contributions of this thesis and provide the structure of this thesis. Section 1.5 provides a list of publications that this thesis and other associated works led to.

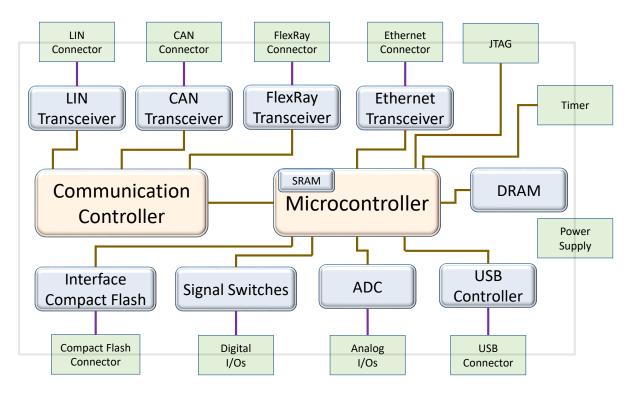

Figure 1.1: A schematic of an automotive electronic control unit (ECU).

## 1.1 Automotive Cyber-Physical Systems

This thesis mainly studies automotive systems. Modern automotive electrical and electronic (E/E) architectures are highly complex and heterogeneous with up to 100 electronic control units (ECUs) connected over a communication network [6, 7]. The communication network comprises various communication buses like FlexRay, CAN, and more recently also automotive Ethernet. Several hundred million lines of software code are running on an automotive E/E platform [8]. In these systems, software components typically implement control functions that determine the physical dynamics of the car. The control applications come from various domains [9] - like basic automotive functionality (brake control, engine control), advanced driver assistance systems (cruise control, lane control), and also comfort features (like vibration control). In electric vehicles (EVs), the battery pack is the main source of energy. It powers the car, thereby, determining the maximum accerleration and the driving range of the car. These high-power battery packs are typically provided with a hardware/software system called the battery management system (BMS) [10]. The main functions of a BMS include monitoring the state of the battery pack, maintaining its safe operation and ensuring the desired usable capacity of the pack [11]. In this section, different components of automotive CPSs will be briefly discussed.

#### 1.1.1 Electronic Control Units

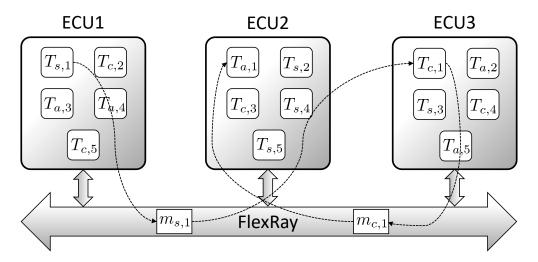

Typically, as shown in Figure 1.1, an ECU in a modern car comprises a core (i.e., a microcontroller), memory resources (i.e., SRAM and Flash), inputs (i.e., supply voltage, digital outputs, analog inputs), outputs (i.e., relay drivers, H bridge drivers, logic outputs, injector drivers), communication controller (i.e., an FPGA or a micro-controller), and network interfaces (i.e., transceivers) [7]. Thus, software gets information about the physical system from the sensors connected to the inputs of the ECU. Based on the inputs, software runs using the computation and memory resources in the ECU. Control decisions taken by the software are then applied to the physical system using the outputs of the ECU. In case of a distributed software implementation, software components communicate by sending data using the communication controllers and transceivers (on sending and receiving side respectively) over the communication bus.

Communication controllers perform communication based on the corresponding communication protocol. For example, E-Ray IP module supports FlexRay v2.1 [12]. Communication data, are therefore, first sent to the communication controller, where they are packetized into communication frames as allowed in the protocol. Then, these frame are sent over the communication bus based on their respective schedules and the scheduling policy of the protocol. For example, in case of FlexRay protocol, a frame will be sent only when the current slot id matches the slot id assigned to the frame. On the receiving ECU, the communication controller monitors network activities. When there is a frame that is sent to the host micro-controller, it receives the frame, depacketizes the frame to get the data and transmit the corresponding data to the host micro-controller.

In the automotive industry, there is a large variation in the capabilities of the available ECUs. For example, a low-end ECU might only have a 8 bit processor with 8 MHz, 4 kB flash memory, and 256 byte RAM while a top-end automotive ECU might have a 32 bit multi-core processor with 200 MHz, 6 MB flash memory, and 384 kB RAM<sup>1</sup>.

Typically, the software running on an ECU might be composed of several functions. For example, a combustion engine controller implements various independent functions, such as the adjustment of the fuel injection while monitoring the rotational speed of the turbo charger [13]. In the current state-of-practice, these functions do not run on the bare metal. Automotive ECUs run a real-time operating system (RTOS) that manages the system resources. Thus, the software functions mapped on to an ECU are scheduled based on the RTOS employed.

**OSEK/VDX**: In 1993, German automotive consortium (inlcuding BMW, Robert Bosch GmbH, DaimlerChrysler, Opel, Siemens and Volkswagen Group) and the University of Karlsruhe founded OSEK (Offene Systeme und deren Schnittstellen für Elektronik in Kraftfahrzeugen) towards standardizing the software architecture [14]. In 1994, French car manufacturers Renault and PSA Peugeot Citroën merged their project Vehicle Distributed eXecutive (VDX) with OSEK, and formulated OSEK/VDX [15]. This group specified a standard for automotive RTOS (Offene Systeme und deren Schnittstellen für Elektronik in Kraftfahrzeugen (OSEK)-OS) [16] that has been widely deployed in automotive ECUs. OSEK-OS provides standards for task management, synchronization, interrupt management, alarms, intra-processor message handling, and error treatment. The earlier specification supported the event-triggered scheduling

<sup>&</sup>lt;sup>1</sup>Data for Freescale automotive micro-controllers *S08QD* and *MPC5676R*, taken from http://cache.freescale.com/files/microcontrollers/doc/roadmap/BRAUTOPRDCTMAP.pdf.

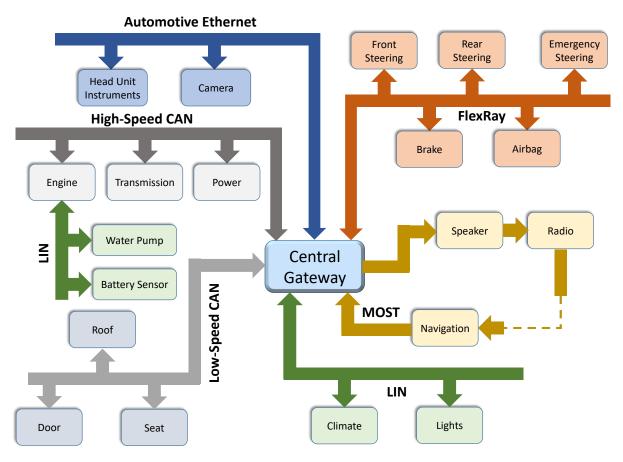

Figure 1.2: An automotive E/E architecture comprising different communication buses including High-Speed and Low-Speed CAN, FlexRay, LIN, MOST, and Automotive Ethernet.

of software tasks only, which is also extended later to OSEK time [17] to support the time-triggered scheduling scheme.

#### 1.1.2 Communication Buses

Automotive E/E systems are composed of several functional domains [9]: (i) Powertrain domain including engine and transmission control; (ii) Chassis domain, e.g., steering and brake control; (iii) Body and comfort domain including the control of doors, seats, lights, HVAC, among others; (iv) Infotainment domain including telematics and entertainment. The large spectrum of software applications has led to diverse requirements from the underlying E/E architecture, in particular, the communication network architecture. The design of automotive in-vehicle networks depends on the nature of data to be transmitted. For example, safety-critical control data in the chassis domain must satisfy real-time properties and reliability requirements while infotainment and camera-based driver assistance data require high network bandwidth [18]. As a result, the E/E system has several subnetworks connected via gateways, as shown in Figure 1.2. These subnetworks offer different network bandwidth and implements different communication protocol. Each subnetwork serves several applications belonging to a specific functional

domain, e.g., FlexRay or High-Speed CAN for the chassis domain, High-speed CAN for the powertrain domain, Low-Speed CAN and LIN for the body domain, and MOST and Ethernet for the infotainment domain [19].

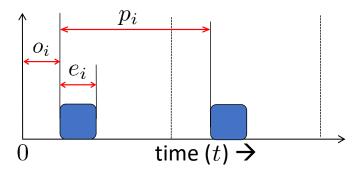

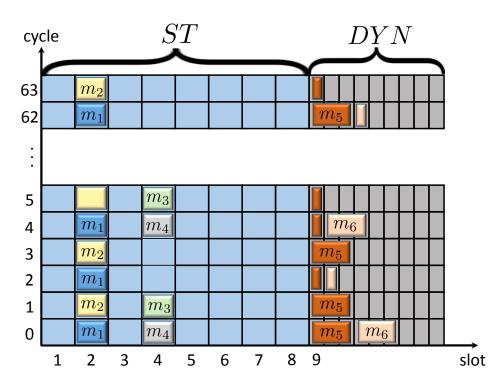

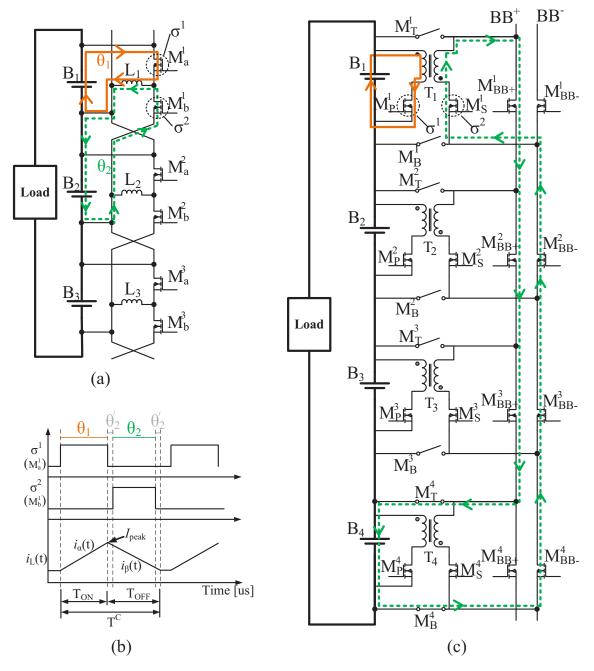

FlexRay: FlexRay communication bus is a deterministic, fault-tolerant and high-speed bus system developed by the FlexRay consortium. FlexRay protocol v2.1 [20] was first published in 2005 followed by FlexRay protocol v3.0 [21] in 2010. FlexRay is a hybrid communication protocol, in which each communication cycle is partitioned into a static and a dynamic segment. The static segment is composed of equal length time-division multiple access (TDMA) slots. Each data frame mapped onto a static slot will be sent exactly within the assigned slot. Due to time-deterministic communication in the static segment, it is used for the transmission of safety-critical data with strict timing requirement [13]. On the other hand, dynamic segment is composed of equal-length minislots where the size of a slot is larger (10 times or more) than that of a minislot, and a frame mapped to the dynamic segment can take more than one minislot for transmission. Thus, the dynamic segment offers flexible TDMA (FTDMA) where each frame is assigned a slot number, however, the slot counter is incremented only after a message is completely sent or after an empty slot. Thus, the exact time when a frame is transmitted in the dynamic segment depends on the size of the frames that are assigned lower slot numbers. While the static segment allows time-deterministic communication, the communication in the dynamic segment can have jitters (i.e., there is a best- and a worst-case delay). On the other hand, if there is no new data to be sent on a static slot the whole slot is wasted, while for the dynamic segment, in the absence of a new data, only a minislot is wasted. Thus, the dynamic segment is more resource-efficient than the static segment. As FlexRay supports TDMA, the clocks of all FlexRay nodes in a network is synchronized, and therefore have the same notion of time. FlexRay bus offers two communication channels that can be either used to multiply bandwidth or for redundancy [22]. In each channel, a data rate of 10 Mbit/s is offered. Despite the advantages, the usage of FlexRay in automotive systems is mostly limited to the chassis domain due to the higher cost and complex parametrization when compared to CAN [13].

Controller Area Network (CAN): CAN [23] has been the de facto standard for in-vehicular communication since it was introduced by Robert Bosch GmbH in 1986. CAN offers the maximum data rate of 1 Mbit/s. *High-Speed CAN* [24] with a common data rate of 500 kbit/s and *Low-Speed CAN* [25] with a common data rate of 125 kbit/s are commonly used in automotive systems. CAN frames can traditionally support a payload size of 8 bytes. However, this limits its usage in advanced driver-assistance systems (ADASs), and therefore, CAN Flexible Data-Rate (CAN FD) [26] has been developed that allows a payload of size up to 64 bytes. CAN allows event-triggered communication, where a collision between two CAN frames is resolved using carrier-sense multiple access/collision resolution (CSMA/CR) [27]. That is, each CAN frame is assigned a priority apriori and when two CAN data frames are sent simultaneously, the higher-priority frame will transmit first while the lower-priority one waits. There have been efforts to extend CAN to allow time-deterministic communication in time-triggered CAN (TTCAN) [28]. However, due to limitation of the data rate, TTCAN is not widely used in modern automotive systems [29].

**Local Interconnect Network**: LIN [30] is a time-triggered low-speed bus that has been developed as a cheaper alternative to CAN bus to connect to sensors and actuators in the body domain

for the control of doors and seats [13]. LIN offers a maximum data rate of 20 kbit/s and is based on master/slave communication. In a LIN bus cluster, the master node polls each slave node periodically using an empty frame, where the header contains the id (or number) of the slave being polled and the slave adds data to the empty frame [31]. There is no collision possible in this polling-based communication because each slave has a different id, and therefore, only one slave responds at a time.

**Media-Oriented Systems Transport (MOST)**: It is mainly used for multimedia and telematics applications. It supports high data rates of 25 Mbit/s (MOST25), 50 Mbit/s (MOST50), and 150 Mbit/s (MOST150) [32]. It supports both time-triggered (i.e., audio and video data) and event-triggered (i.e., navigation data) communication [13, 31]. It also follows a master-slave communication like LIN, where a dedicated master ECU creates the message frames in which the slave ECU can send their messages.

**Automotive Ethernet**: Ethernet has been widely used in local area networks (LANs), metropolitan area networks (MANs), and wide area networks (WANs). However, the traditional Ethernet protocol cannot be deployed in automotive systems due to the following reasons: (i) it is susceptible to noise from other electronic devices, (ii) it cannot provide timing guarantees in the order of microseconds, (iii) it supports only asynchronous communication, and (iv) there is no means to prioritize communication traffics.

The first shortcoming, i.e., higher communication noise in high-speed Ethernet, is addressed by using *BroadR-Reach* [33], the standard for the physical layer developed by Broadcom for Ethernet. *BroadR-Reach* uses a robust and efficient three-level pulse-amplitude modulation (*PAM-3*) signaling scheme that has a high spectral efficiency and therefore, enables a lower signal bandwidth (33.3 MHz). This reduces crosstalk and and also ensures that electromagnetic interference (EMI) requirements of automotive industry is met [34].

The primitive Ethernet protocol is based on carrier-sense multiple access with collision detection (CSMA/CD) with half-duplex links, which is not time-deterministic. In CSMA/CD, when multiple Ethernet frames are sent at the same time, they will collide, and then each Frame is sent again after a random back-off period [35]. Thus, there is no guarantee on how many maximum retransmissions are needed to send a frame reliably.

Towards a more reliable communication, first, full-duplex links are used to allow simultaneous bi-directional communications [36] and, second, switches are introduced in the communication path to forward frames. In full-duplex switched Ethernet network [37], only two nodes share a communication link, and therefore, there is no collision between Ethernet frames. Furthermore, IEEE 802.3br [38], an amendment to Ethernet protocol, make provision for *Express Traffic* or high-priority traffic. High-priority frames can preempt other frames, and thus, have latency of less than a microsecond.

The IEEE 802.1 Audio Video Bridging (AVB) Task Group, later renamed to Time-Sensitive Networking (TSN) Task Group [39], has proposed several amendments to the Ethernet protocol towards addressing further limitations. For example, (i) IEEE 802.1AS provides a standard for time synchronization in Ethernet networks [40], (ii) IEEE 802.1Qat specifies a standard to reserve bandwidth for traffic streams [41], and (iii) IEEE802.1Qav defines a standard for queueing and forwarding of time-sensitive frames [42]. These aforementioned amendments

enable time-triggered communication, while the traditional best-effort communication is also supported.

Currently, Ethernet is deployed primarily in the infotainment systems of modern cars and might even replace MOST [13, 43]. However, it is envisioned that Ethernet can serve as the backbone network connecting different application domains [44] and time-triggered communication in Ethernet [45] can also be used for safety-critical systems.

#### 1.1.3 Automotive Software

In recent years, increasingly more software applications are being deployed in the automotive systems, including, e.g., applications for driver assistance systems, infotainment, and safety-critical control systems. This trend is easily observed in the increasing number of ECUs, communication buses, communication signals, lines of software code, among others [46]. However, this trend is not sustainable using the existing federated architecture of the automotive E/E systems, where each ECU runs software pertaining to one application only [47]. Thus, automotive industry is moving towards *ECU consolidation*, where multiple functions can be integrated into one ECU, to efficiently utilize the hardware resources in future automotive systems [48]. However, to handle such software complexity, a sophisticated software architecture needs to be considered [49, 50].

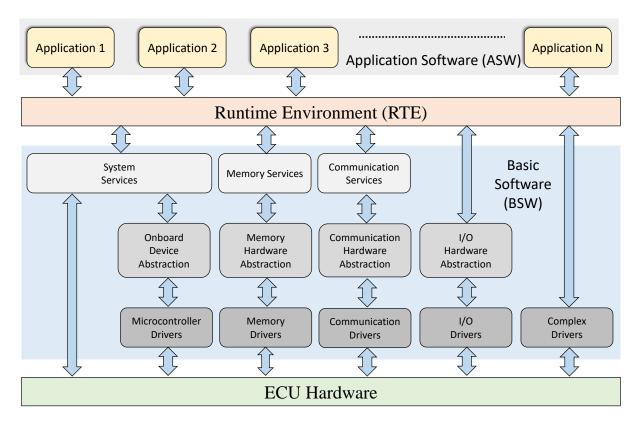

AUTomotive Open Software ARchitecture (AUTOSAR): A worldwide partnership of vehicle manufacturers, suppliers, service providers, and companies from the automotive electronics, semiconductor and software industry was formed to develop AUTOSAR [53]. It defines an open industry standard for the automotive software architecture [54]. It specifies the software architectural components, their interfaces, and a standard design and implementation methodology. It allows development of high level application software independent of underlying implementation details. The AUTOSAR ECU software consists of three components, as shown in Figure 1.3. (i) The basic software (BSW) layer provides the basic services (including memory, communication, input-output, system calls, among others) and abstracts the hardware resources by means of drivers and operating system (OS). Here, AUTOSAR-OS is backward compatible with the OSEK-OS. BSW is further partitioned into micro-controller abstraction, ECU abstraction and complex drivers, and services. (ii) The application software (ASW) layer represents the software components that define the functionality of an ECU by means of runnables, e.g., steering control software. (iii) The runtime environment (RTE) layer defines the communication between ASW and BSW. Here, RTE allows development of application software independent of hardware as it contains the details about when the runnables use the drivers. Therefore, if a runnable is removed or added then the RTE must also change. This implies that the basic software and RTE along with all existing applications have to be rebuilt in case a new application is added in AUTOSAR classic platform [51].

Besides, the software components, AUTOSAR also defines the communication interfaces between the components as *ports*. There are different types of ports (e.g., sender-receiver and client-server) realizing different communication relations. The communication between components is realized based on the configuration of the ports via the *virtual functional bus* (VFB) [52]. VFB abstracts the actual implementation of the communication that depends on the mapping of the software components, i.e., VFB can represent communication bus systems if the soft-

Figure 1.3: The automotive software architecture as defined by AUTOSAR. It consists of three layers, namely, the application software (ASW), the runtime environment (RTE), and the basic software (BSW). This figure is reproduced from [51] and [52].

ware components are mapped on different ECUs, while it can even represent communication via RTE and the local memory if the software components are in the same ECU. Complying with AUTOSAR standard makes automotive software highly modular, thus reducing the complexity while also allowing reusability. Thus, the basic software and the application software can be developed by different suppliers and then integrated by the original equipment manufacturer (OEM). Moreover, different applications mapped on to the same ECU can be developed by different suppliers. Even an application software can be reused for a new vehicle variant with different E/E architecture by properly configuring the RTE.

## 1.1.4 Battery Packs

Towards a pollution free and sustainable transportation solution, battery packs are used in EVs and hybrid electric vehicles (HEVs) as a source of energy [55]. Batteries are widely used to store electrical energy due to their high energy (and power) density and high specific energy (and specific power), which correlates to a lower required installation volume and a lower weight respectively, compared to other electrical energy storage (EES) solutions such as supercapacitors [56]. Moreover, batteries can be tailored to meet the specific requirements of the application such as fast charging, longer shelf life, and higher power rating [55].

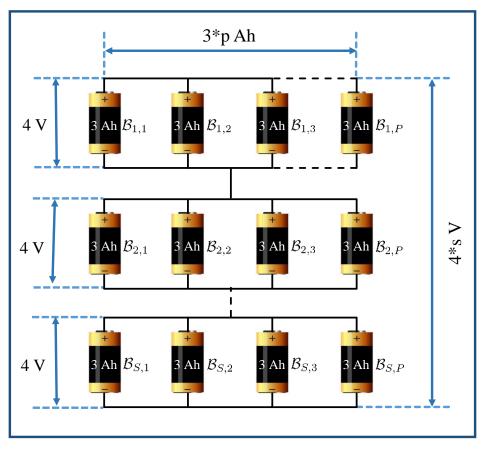

12\*p\*s Wh

Figure 1.4: Series and parallel connection of electrochemical cells to form high-power battery packs. Series connection enables the pack to operate at high voltage while parallel connection increases the capacity to drive higher load currents. Here, p cells are first connected in parallel to form a group and then s such groups are connected in series.

Batteries are composed of electrochemical cells [57], where a chemical reaction can cause an electron transfer. These cells consist of a positive electrode (i.e., cathode), a negative electrode (i.e., anode), and an electrolyte that facilitates the movement of charge carriers between electrodes. In general, batteries are broadly classified into primary (non-rechargeable) and secondary (rechargeable). The primary non-rechargeable batteries comprise galvanic cells that can be used only once. They are discarded when the active chemical materials (generating electricity) in the cells are fully utilized. By contrast, the secondary rechargeable batteries comprise cells that can operate both as galvanic and electrolytic cell and are therefore, based on reversible chemical reactions. The secondary batteries can be charged and discharged several times. During charging, positive ions (M+) are generated at the cathode that move to the anode through the electrolyte. During discharging, the opposite reaction takes place where positive ions move from the anode to the cathode. Note that electrons  $(e^-)$  move in the opposite direction to that of the ions through the outer circuit, which results in the charging and the discharging current in the respective phases. For EES, the secondary rechargeable batteries are preferred since they

allow to store (charge) and use (discharge) the electrical energy without the necessity to replace the battery itself.

Several different cell chemistries are available for rechargeable batteries [58, 59]. Examples include: (i) Nickel-metal hydride (NiMH) cells consist of nickel oxide hydroxide as the cathode, a hydrogen absorbing alloy as the anode, and potassium hydroxide as the electrolyte. (ii) Lead-acid cells have lead-dioxide as the cathode, metallic lead as the anode, and sulphuric acid solution as the electrolyte. (iii) In lithium ion (Li-ion) cells, the cathode is a lithium compound (e.g., lithium magnesium oxide, lithium cobalt oxide, and lithium iron phosphate), the anode is typically graphite, and the electrolyte comprises lithium salt in an organic solvent.

Compared to other rechargeable cell chemistries, batteries that consist of Li-ion cells have the following advantages [60]: (i) They perform better in terms of energy and power densities because the electrochemical potential of lithium is higher compared to other materials. Therefore, Li-ion cells can be manufactured in smaller size and weight for the same energy and power requirements of the application. Additionally, Li-ion cells can be manufactured in several shapes, and therefore, can be organized in a battery pack compactly. (ii) Li-ion cells have no memory effect and thus have a longer cycle life compared to NiMH and nickel-cadmium (NiCd) where, due to the memory effect, energy capacity reduces with repeated charging after partial discharges. (iii) Li-ion cells are generally stable to high currents. Thus, battery packs composed of Li-ion cells are typically used in EVs and HEVs, where high currents are experienced during acceleration and braking. (iv) Li-ion cells have a high coulombic efficiency and a low self-discharge rate, and thus, they are energy-efficient.

Typically, battery packs for EVs and HEVs must operate at a high voltage ( $\approx 450\,\mathrm{V}$ ) and have a high capacity ( $\approx 200\,\mathrm{Ah}$ ). However, the voltage and capacity of a single Li-ion cell is insufficient to meet the aforementioned requirements. Therefore, automotive battery packs are composed of a number of series- and parallel-connected Li-ion cells, as shown in Figure 1.4. In order to drive a higher current, multiple Li-ion cells are connected in parallel and the high operating voltage is obtained by series-connection of the cells [11]. Examples of automotive battery packs include: (i) The Tesla Model-S uses a  $85\,\mathrm{kWh}$  battery pack [61] that comprises Panasonic "18650" Li-ion cells where each cell has a capacity of  $3.2\,\mathrm{Ah}$ . The battery pack is composed of 16 series-connected module and each module consists of 6 series-connected groups of 74 cells that are connected in parallel. (ii) The battery pack in Nissan Leaf has 48 series-connected modules where each module has 2 groups of 2 cells in parallel [62]. Here, sheet-shaped Li-ion cells are used that have a cell capacity of  $32.5\,\mathrm{Ah}$ . (iii) The BMW i3 battery pack comprises 8 series-connected modules where each module has 12 series-connected cells [63]. Here,  $60\,\mathrm{Ah}$  prismatic cells are used.

#### 1.1.5 Battery Management Systems

Typically, battery packs used in high-power automotive applications are provided with a hard-ware/software system, i.e., the *battery management system* (BMS), to maintain their safety and performance [64]. Despite the advantages offered by the Li-ion cells, they are sensitive to their operating conditions in terms of voltage, current, and temperature, and thus, these parameters must be tightly monitored and controlled to ensure safety [65]. Furthermore, the state of the

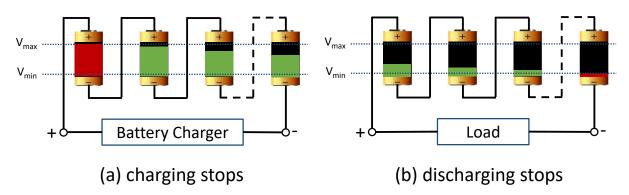

Figure 1.5: Charge variation in a battery pack results in reduced usable capacity. (a) A battery pack with series-connected cells cannot be charged further, if a cell has reached the maximum threshold of charge, despite there are cells in the pack that are not fully charge. (b)A battery pack with series-connected cells cannot be discharged further, if a cell has reached the minimum threshold of charge, despite there are cells in the pack that can still drive current.

cells i.e., the state-of-charge (SoC) and the state-of-health (SoH), in a battery pack must be controlled such that the maximum performance (i.e., energy output) can be obtained [64].

Safety concerns [65]: Li-ion cells have a defined set of safe operating conditions and operation outside the specified limits can severely damage the cells, reduce their lifetime, and even cause fire or explosion due to thermal runaway. (i) The minimum and maximum operating voltage of most Li-ion cells are in the range of 2.7 V and 4.2 V respectively. Charging a Li-ion cell with a voltage higher than that specified can cause lithium plating on the anode surface, reducing the availability of lithium ions and thus, resulting in an irreversible capacity loss. Lithium plating can also lead to an internal short-circuit of the cell causing excessive temperature that damage the cell. Similarly, discharging a Li-ion cell below its minimum threshold voltage results in a gradual breakdown of the internal cell electrodes, reducing their lifetime. (ii) The maximum current with which a cell can be charged depends upon the design of the electrodes. Increasing the charging current significantly increases the temperature of the cell. In certain cases, the cells experience an increased pressure at higher currents and start to swell due to generation of gases inside the cell. If the mechanical clearance between cells in the pack is not adequate, it will result in a short circuit situation. Likewise, discharging the cell with higher currents results in an inherent capacity loss, which is referred to as the rate capacity effect. (iii) Temperature influences the safety and performance of the battery. On one hand, at low temperatures, the speed of chemical reactions slows down that results in a reduced current carrying capacity of the pack. Prolonged operation at reduced temperatures (below 0 °C) will result in a premature capacity loss of the pack. On the other hand, increased temperatures will result in catastrophic effects causing fire or explosion.

**Performance concerns**: As mentioned in Section 1.1.4, automotive battery packs comprise multiple series-connected Li-ion cells. The usable capacity (or the maximum energy output) of such a pack is limited by the cell with the minimum charge level or SoC, compared to other series-connected cells [66]. Thus, it is desirable to charge each cell to the maximum SoC threshold to maximize the usable capacity. However, the charging process stops when a cell in the

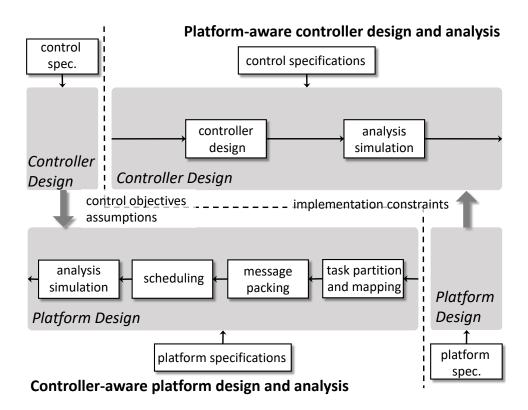

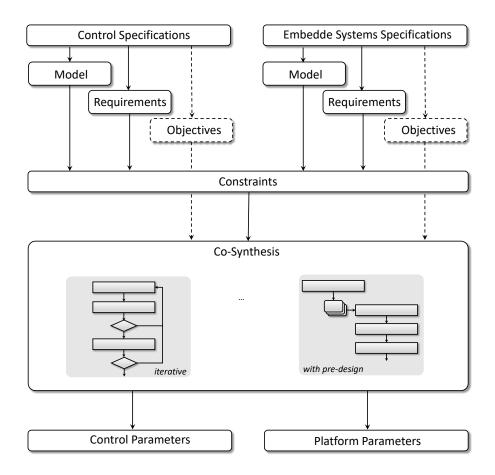

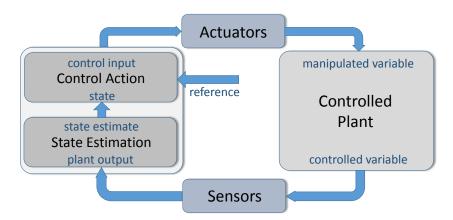

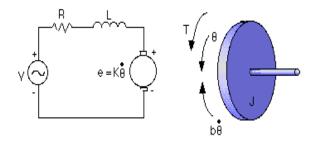

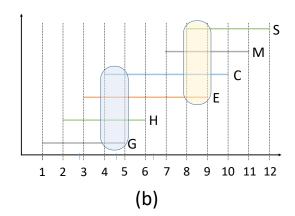

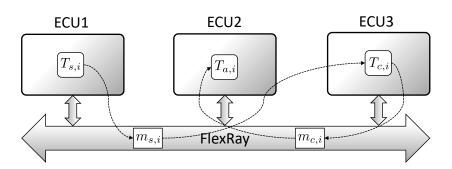

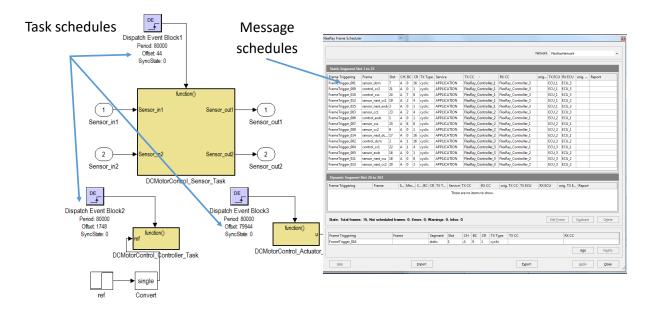

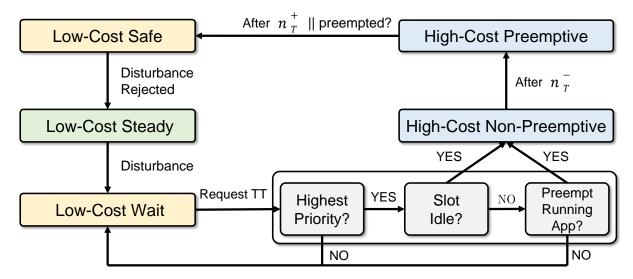

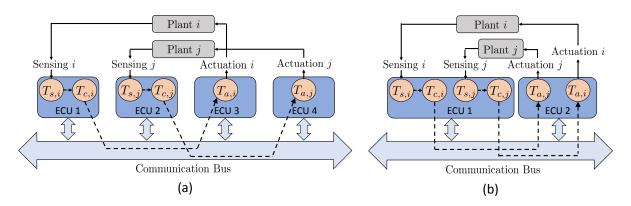

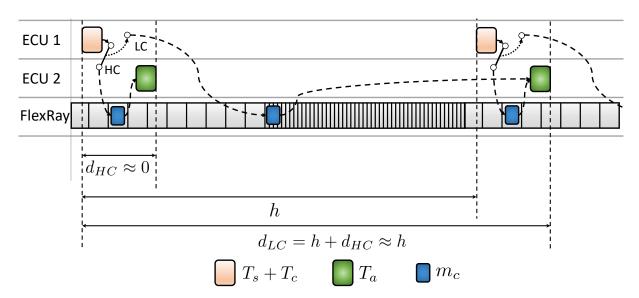

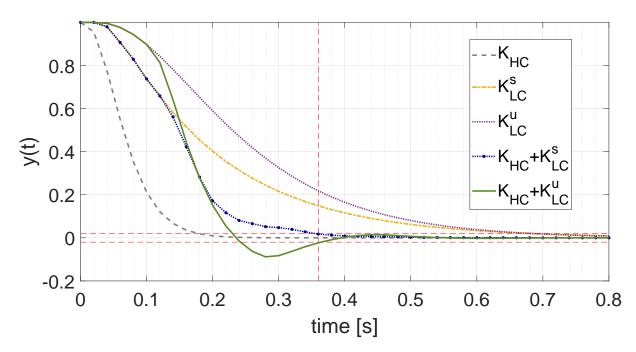

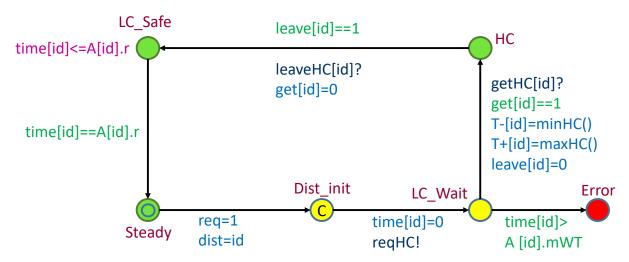

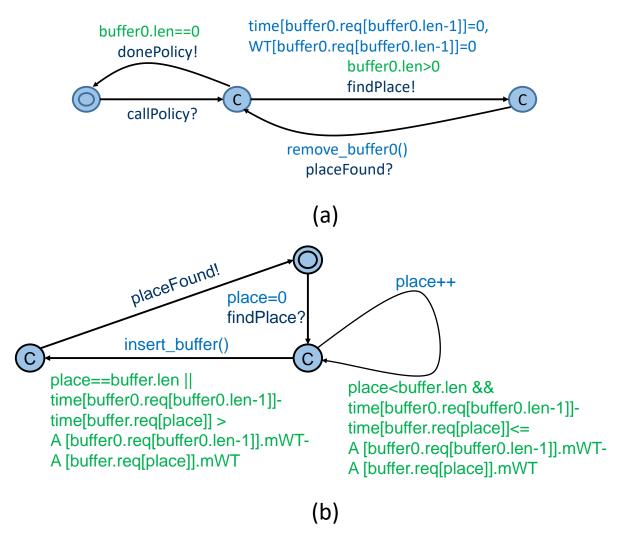

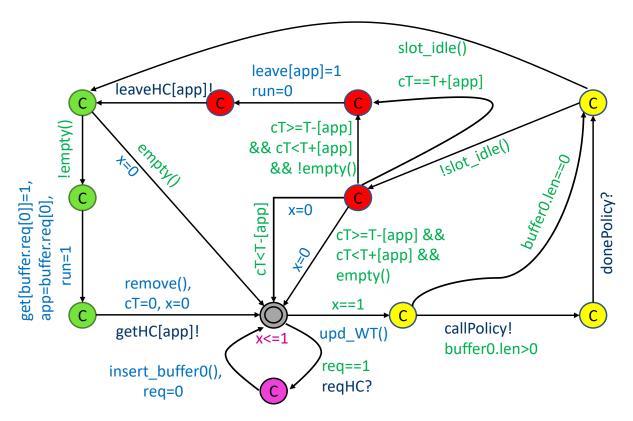

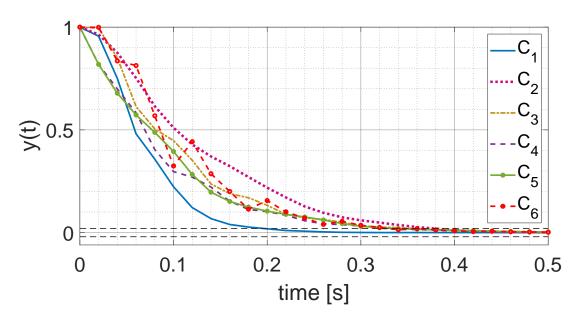

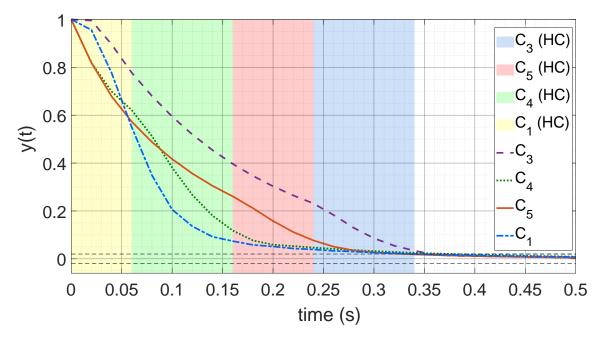

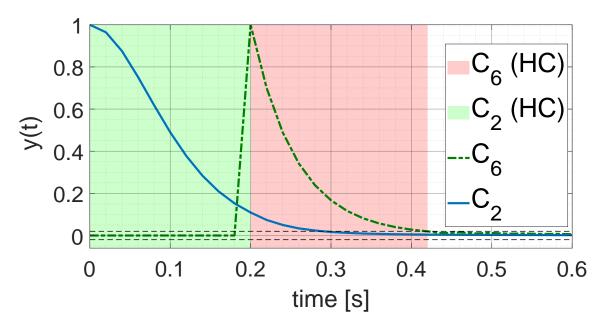

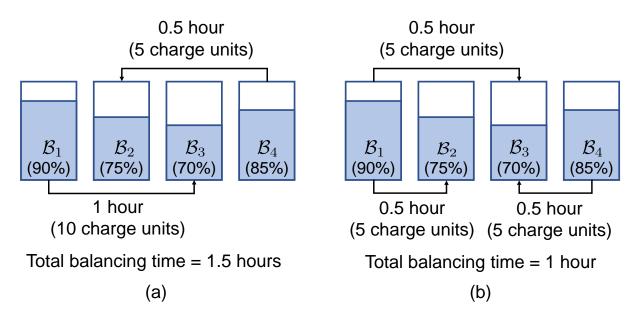

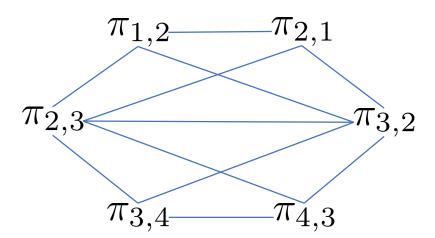

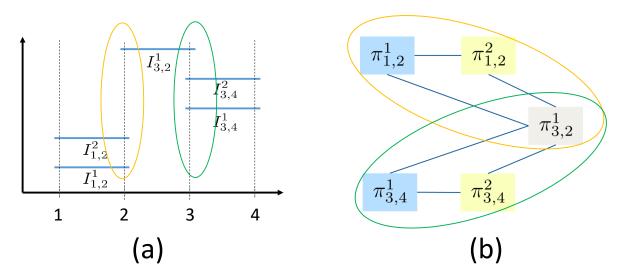

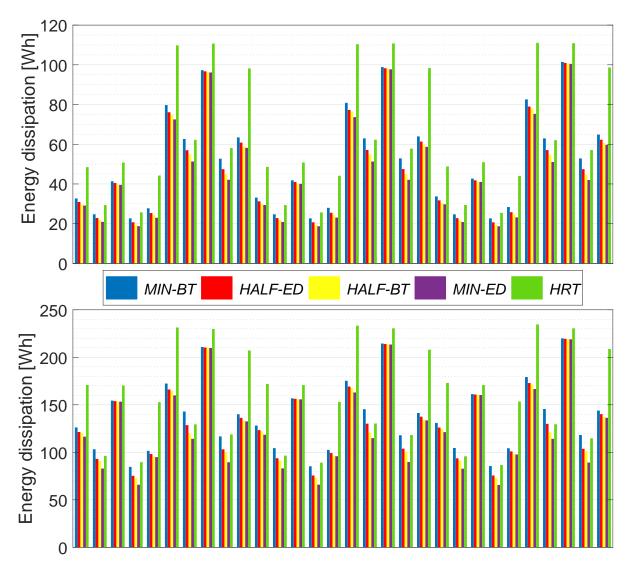

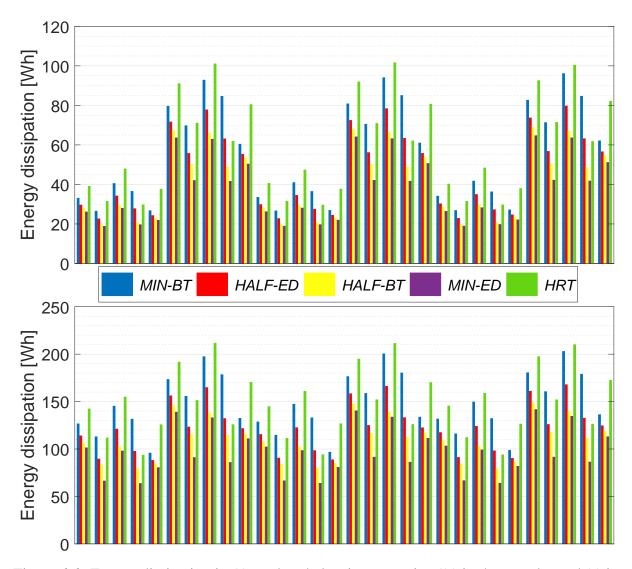

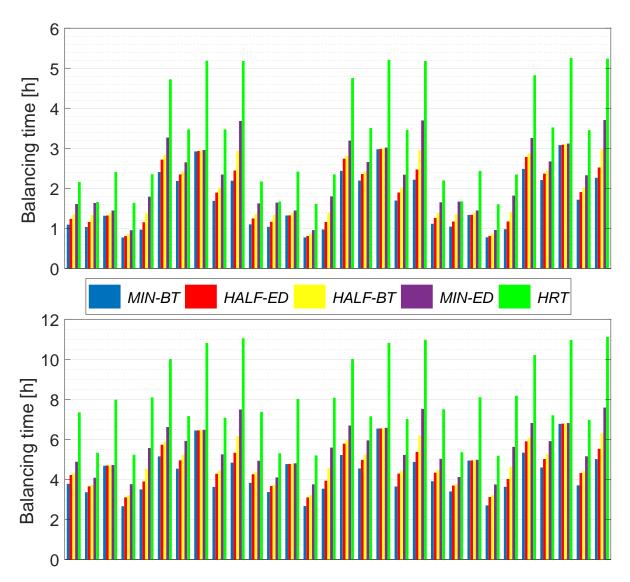

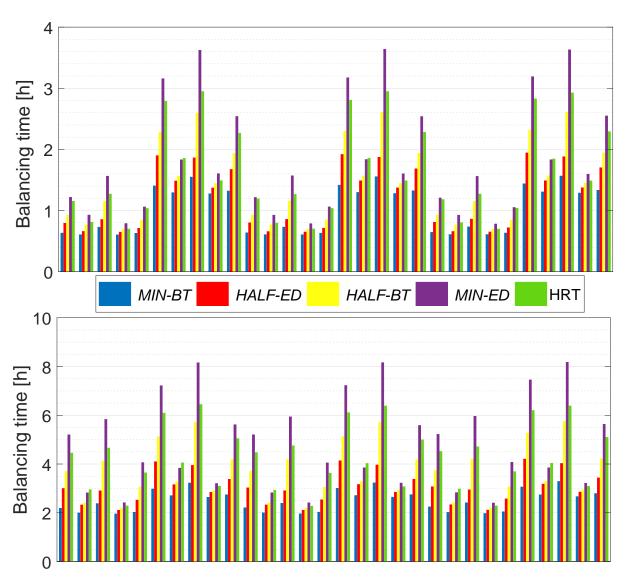

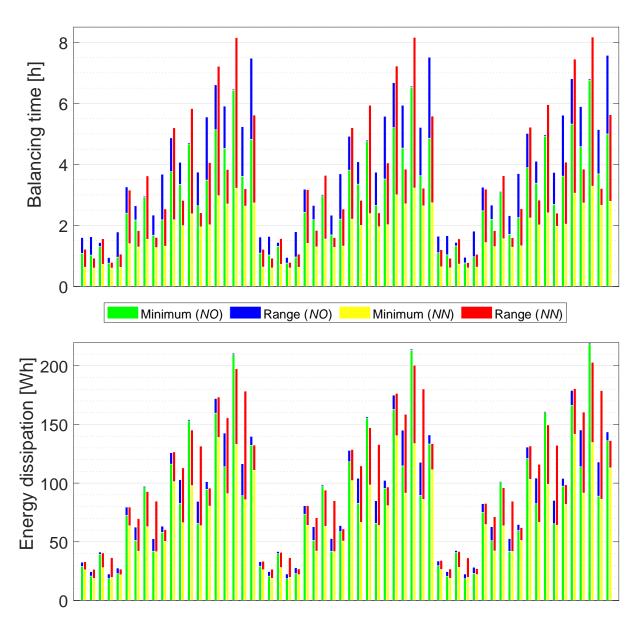

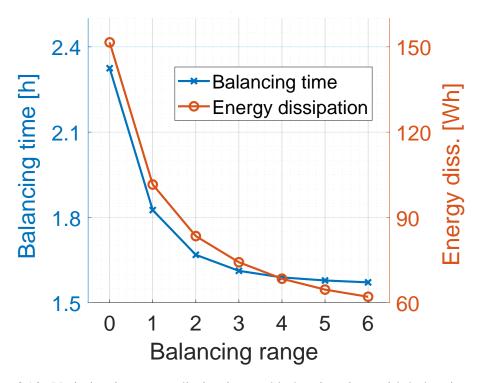

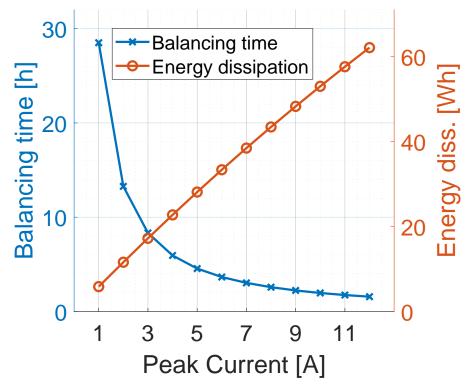

pack reaches the maximum SoC threshold despite other cells not being fully charged [67], as shown in Figure 1.5a. Similarly, during discharging, when a cell reaches the minimum SoC threshold, no more power can be drawn, despite there is residual charge in the other cells of the pack, as illustrated in Figure 1.5b. Note that when all cells in the battery pack have identical charge/discharge characteristics, this imbalance in the SoCs is not observed. However, realistically, there is a variation in the SoCs primarily due to the following reasons: (i) There might be a variation in cell characteristics (up to 10%) due to manufacturing variances [68,69]. A Li-ion cell is manufactured by mixing granular raw materials to form a slurry [70]. The variation in the shape or size of the grains or in the composition of the slurry can lead to different characteristics of the manufactured cells [71]. These differences become more profound when these cells age. (ii) Non-uniform temperature distribution is also a major reason for the variation in the SoC levels in the pack. It has been observed that the temperature closer to the cooling inlet is more than 10 °C lower than the temperature farthest away [72]. Arrhenius' law states that the rate of chemical reactions doubles with every 10 °C rise in temperature [73]. Thus, with non-uniform temperature distribution, each cell will have a different discharge characteristic. Moreover, the internal resistance and the self-discharge rate of a cell also vary with temperature [74].