# Technische Universität München Fakultät für Elektrotechnik und Informationstechnik Lehrstuhl für Schaltungsentwurf

# Concepts for Multi-Level Cell Operation of Embedded Flash in Automotive Applications

### Sebastian Kiesel

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs**

genehmigten Dissertation.

Vorsitzender: Prof. Dr.-Ing. Ralph Brederlow

Prüfer der Dissertation:

1. apl. Prof. Dr.-Ing. habil. Helmut Gräb

2. Prof. Dr.-Ing. Bernhard Wicht

Die Dissertation wurde am 25.09.2019 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 10.02.20 angenommen.

# Abstract

The advance in automotive technology results a large scope of applications for microcontroller units (MCUs) with growing complexity. Trends like autonomous driving and sensor fusion are pushing the demand for high performance controllers with increased embedded memory capacity, for code and data storage. The storage of multiple bits in one memory cell (multi-level cell (MLC) operation) is a proven method to increase memory density and hence reduce cost for a required amount of memory. Due to high requirements regarding temperature range, long operating lifetimes and absolute code integrity, MLC operation has not been applied for embedded Flash (eFlash) memories in automotive applications, so far.

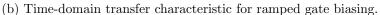

This work evaluates different Flash cell biasing schemes for the usage in a sensing scheme for MLC eFlash targeting automotive requirements. Besides the implementation complexity and area consumption, sensing robustness and speed are analyzed. For this purpose, a time-domain voltage sensing principle is chosen, and the analytically derived transfer characteristics of the investigated biasing approaches are taken for assessment.

Based on the findings of the investigation, a novel time-domain sensing scheme using a ramped gate cell biasing is introduced. It comprises an improved voltage mode sense amplifier design with offset compensation capability for better distinction of multiple programmed cell states at high speed operation. The components of the sensing scheme's implementation, including sense amplifier, ramp generation and strobing circuitry are presented and analyzed. Measurements conducted on a test chip verify the functionality and reveal the overall read performance of the sensing scheme, which is compared to state-of-the-art memory designs.

Further, the biasing scheme's implications on the programming performance is investigated and disturbing effects like cell-to-cell interference and temperature shifts are highlighted. According to the outcome of the conducted measurements, guidelines for development of an efficient programming algorithm are given.

The present work demonstrates that modern eFlash technology is capable for robust MLC operation that meets stringent automotive requirements. The advance towards multiple bits per cell is a viable option for memory density increase and cost reduction in eFlash for automotive applications. iv

# Contents

| 1        | Intr              | roduction 1                                                                                               | -      |

|----------|-------------------|-----------------------------------------------------------------------------------------------------------|--------|

|          | 1.1               | Evolution of Multi-Level Flash Memory                                                                     | -      |

|          | 1.2               | Contribution of This Work                                                                                 | Į      |

|          | 1.3               | Outline of the Thesis                                                                                     | ,<br>) |

| <b>2</b> | Fun               | damentals of Multi-Level Cell Flash Memories 7                                                            | •      |

|          | 2.1               | Cell Technologies for Multibit Storage                                                                    | 7      |

|          | 2.2               | Sensing Principles                                                                                        | )      |

|          |                   | 2.2.1 Voltage Sensing                                                                                     | L      |

|          |                   | 2.2.2 Current Sensing                                                                                     | 2      |

|          |                   | 2.2.3 Time-Domain Sensing                                                                                 | Ł      |

|          | 2.3               | Incremental Step Pulse Programming                                                                        | 7      |

|          | 2.4               | Summary                                                                                                   | -      |

| 0        | <b>Ъ</b> <i>Т</i> |                                                                                                           |        |

| 3        |                   | mory Cell Biasing 23                                                                                      |        |

|          | 3.1               | Concepts                                                                                                  |        |

|          |                   | 3.1.1 Fixed Gate Biasing                                                                                  |        |

|          |                   | 3.1.2 Stepped Gate Biasing                                                                                |        |

|          |                   | 3.1.3 Ramped Gate Biasing                                                                                 |        |

|          | 3.2               | Speed Considerations                                                                                      |        |

|          |                   | 3.2.1 Wordline Model                                                                                      | )      |

|          |                   | 3.2.2 Access Time                                                                                         | )      |

|          |                   | $3.2.3  \text{Comparison}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $               | )      |

|          | 3.3               | Time-Domain Transfer Characteristic                                                                       | )      |

|          |                   | 3.3.1 Fixed Gate Biasing                                                                                  | ;      |

|          |                   | 3.3.2 Ramped Gate Biasing                                                                                 | ;      |

|          |                   | 3.3.3 Comparison $\ldots \ldots 40$ | )      |

|          | 3.4               | Summary                                                                                                   | )      |

| 4             |       | ne-Domain Ramped Gate Sensing for MLC Operation               | 45    |

|---------------|-------|---------------------------------------------------------------|-------|

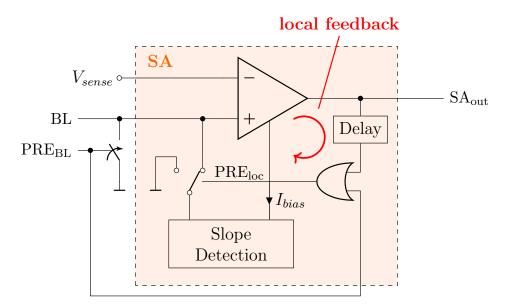

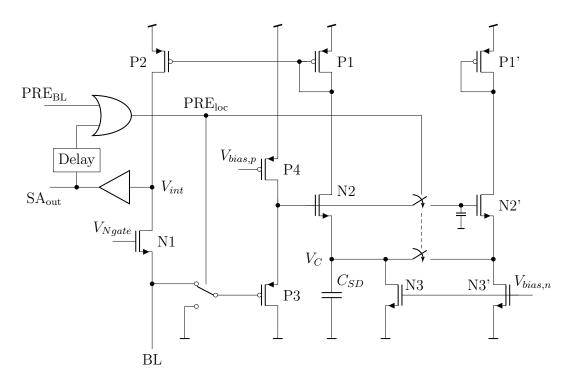

|               | 4.1   | Time-Domain Sense Amplifier                                   | 45    |

|               |       | 4.1.1 Voltage-Biased Slope Detection vs. Current-Biased slope | . 47  |

|               |       | detection                                                     |       |

|               |       |                                                               |       |

|               | 4.2   | 4.1.3 Sense Amplifier Circuit                                 |       |

|               | 4.2   | Ramp Generation Circuitry                                     |       |

|               |       | 4.2.1Load Requirements                                        |       |

|               | 4.3   | ő                                                             |       |

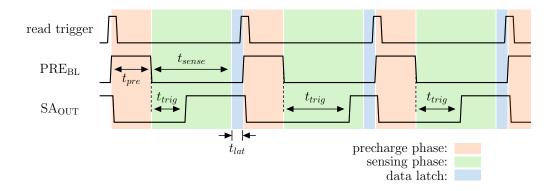

|               | 4.0   | Strobing Concept                                              |       |

|               |       | 8                                                             |       |

|               | 4 4   |                                                               |       |

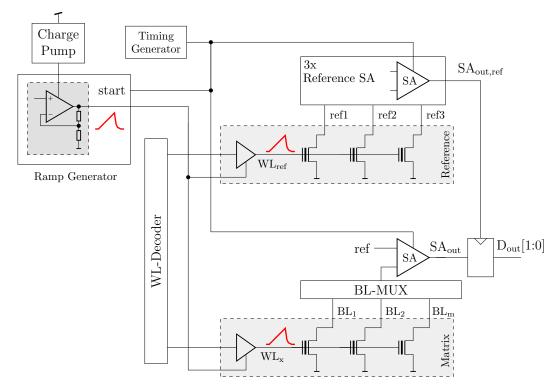

|               | 4.4   | Sensing Architecture and Measurement Results                  |       |

|               |       | 4.4.1 Test Chip Architecture                                  |       |

|               |       | 4.4.2 Time-Domain Transfer Function                           |       |

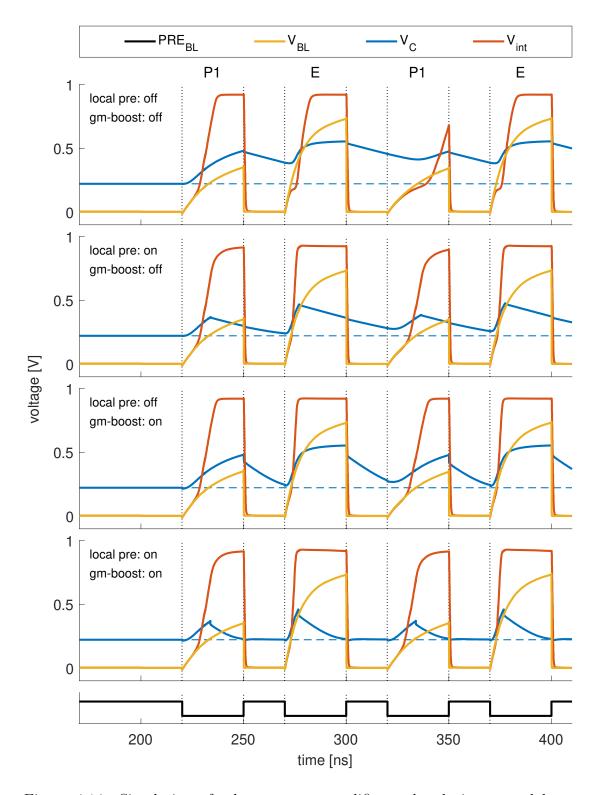

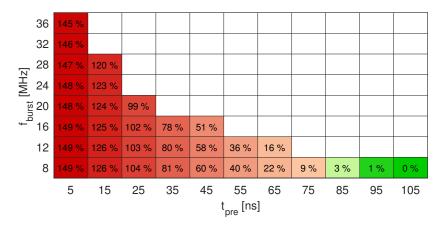

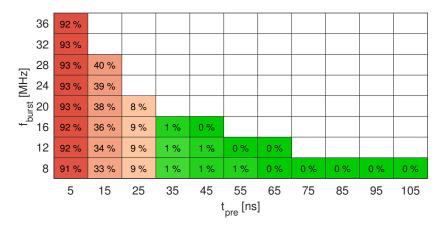

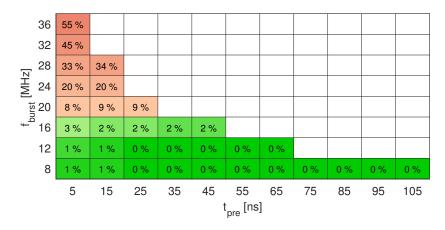

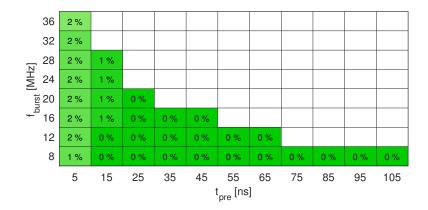

|               |       | 4.4.3 Precharge Acceleration                                  |       |

|               | 4 5   | 4.4.4 Read Access Time                                        |       |

|               | 4.5   | Summary                                                       | . 91  |

| <b>5</b>      | Dist  | tribution Shaping                                             | 93    |

|               | 5.1   | Cell Programming Algorithm                                    | . 94  |

|               |       | 5.1.1 Cell Biasing During Program Verify                      | . 94  |

|               |       | 5.1.2 Programming Order                                       | . 97  |

|               | 5.2   | Temperature Shift                                             | . 101 |

|               | 5.3   | Summary                                                       | . 104 |

| 6             | Con   | clusion and Outlook                                           | 107   |

| $\mathbf{A}$  | Tim   | ne-Domain Transfer Function                                   | 109   |

|               | A.1   | Derivation for Scenario Without Sense Amplifier Bias Current  | 109   |

|               |       | A.1.1 Fixed Gate Biasing                                      |       |

|               |       | A.1.2 Ramped Gate Biasing                                     |       |

|               | A.2   | Derivation for Scenario With Sense Amplifier Bias Current     |       |

|               |       | A.2.1 Fixed Gate Biasing                                      |       |

|               |       | A.2.2 Ramped Gate Biasing                                     |       |

| A             | crony | vms                                                           | 117   |

| $\mathbf{Li}$ | st of | Figures                                                       | 119   |

| Li            | st of | Tables                                                        | 123   |

vi

| Contents                   | vii |

|----------------------------|-----|

| Publications of the Author | 125 |

| Bibliography               | 128 |

Contents

viii

# Chapter 1 Introduction

# 1.1 Evolution of Multi-Level Flash Memory

In the mid-1980s, a new type of non-volatile memory evolved from the predominant erasable programmable read only memory (EPROM). In search of a relief from the lengthy erase procedure, Masuoka et al. from Toshiba introduced the first modern electrically erasable programmable read only memory (EEPROM) in 1984 [1]. The memory array was erased within one operation rather than byte per byte, as it was common for conventional EEPROMs. It was given the name "Flash", as it could be erased within less than a second; fully electrical and without need for ultraviolet (UV) light. With this evident advantage, Flash memory quickly displaced the EPROM in embedded applications, requiring economical reprogramming. New features like independently erasable blocks and an embedded high voltage supply enabled Flash to become more than an EPROM replacement and it quickly entered other markets. In the 1990s, digital cameras, portable MP3 players and cell phones were the drivers for the rapidly growing Flash market. Today, Flash has become a multi-billion dollar business.

With different requirements, two major Flash memory technologies evolved. The NOR-type Flash was the first one in the market. It provides fast random read access and good reliability. Consequently, it is well suited as code memory for direct code execution (Execute-in-place). The NAND-type Flash, which was introduced later, has its benefits in fast write operation and high-density storage. Though it has a slow random access time, its sequential read bandwidth and programming throughput is very good, which makes it the ideal candidate for data storage.

To reduce cost per bit, the memory transistor was scaled down aggressively. In the early 1990s, engineers put a lot of effort in the development of technologies for storage of multiple bits per memory cell, to accelerate the cost reduction even

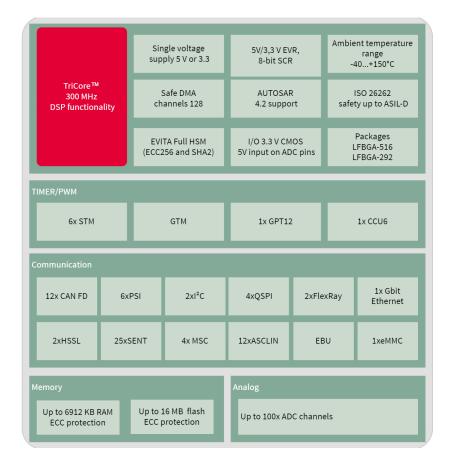

Figure 1.1: Feature set of the AURIX<sup>TM</sup> TC39x automotive microcontroller. Source: Infineon Technologies AG

more. In 1995 the breakthrough was accomplished, and Intel presented their first MLC product with 32 Mbit stored as 2-bit/cell [2]. From then on, MLC technology evolved rapidly and many features and improvements were added. For NOR-type Flash, sensing speed was increased by introduction of new sensing schemes, that used parallel comparison against multiple references [3] or a serial sensing, selecting the reference in binary search fashion [4, 5]. Further, biasing schemes with variable voltage were developed [6, 7], to improve the sensing robustness at continuously shrinking Flash cell size. Advances in NAND-type Flash were achieved in the increase of memory density and programming throughput. The All Bit Line architecture, introduced by Cernea et al. [8] boosted the programming speed significantly by raising the parallelism of the verify read. Together with several improvements including novel programming algorithms [9, 10], this enabled the development of NAND Flash memories with triple-level cell (TLC)- (three bits per cell) and even quad-level cell (QLC)-operation (four bits per cell).

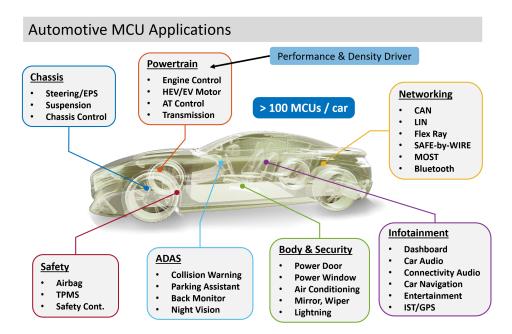

Figure 1.2: Application scope of automotive microcontrollers in a modern car. Image source: Pixabay.com

Microcontrollers have gained in importance, as their range of applications is continuously growing. Industrial, Internet of Things (IoT) and automotive are important market segments, that gather pace as society is moving forward into a digital future with autonomously driving vehicles. Besides SRAM, eFlash is the predominant memory used in MCUs. As relevant performance factors for eFlash are fast random access and absolute code integrity, mainly NOR-type Flash is used [11]. Automotive microcontrollers have the highest requirements regarding operation conditions. Very low failure rates must be guaranteed over lifetimes of 15-20 years and operation at junction temperatures up to 175 °C must be supported. An example for a state-of-the-art microcontroller for automotive application is the Infineon AURIX<sup>TM</sup> TC39x. Figure 1.1 shows the feature set of the MCU. It is fabricated in 40 nm technology and includes six cores, operated with 300 MHz. The embedded memory comprises up to 6912 kB of SRAM and 16 MB of Flash. It is equipped with high performance, numerous analog to digital converter channels and various communication protocols to address in particular automotive requirements.

One of the factors driving the market for eFlash of automotive MCUs is their growing scope of applications (see Fig. 1.2). In a modern vehicle today, over 100 MCUs are operated within its control units for powertrain, chassis, body, airbag etc. [12]. The rising requirement for more personalization, comfort and safety, but also the trend towards autonomous driving, including Advanced Driver Assistance Systems (ADAS) and sensor fusion will increase this amount and it will push the application complexity [13]. The main drivers for performance and memory density are powertrain and transmission. Current high-end microcontrollers for this application scope comprise flash memories of 8 MB to 16 MB. To meet the needs, upcoming generations of automotive microcontrollers have to be equipped with larger memories. Embedded Flash memories with a density up to 32 MB are already in development, to be integrated into future MCUs [14] and the requirements will continue to rise.

As in standalone NOR and NAND Flash memories, the cost position of high density eFlash for automotive application could also be drastically improved with multi-level cell operation. However, the high requirements for read performance and data integrity have prevented the usage of MLC technology for automotive MCUs so far. Consequently, research for reliable memory technologies and sensing schemes with increased robustness are required to bring MLC operation into high-end MCUs for automotive applications.

### 1.2 Contribution of This Work

The scope of this work is the development and analysis of concepts and circuits for the MLC operation of eFlash in automotive applications. Thereby, the focus is put on a robust sensing scheme that is able to meet the speed and reliability requirements of automotive applications. The main contributions of this work can be summarized as follows:

- A new time-domain voltage sensing method for MLC operation is developed, that uses dynamic voltage ramps at the Flash cells' control gates.

- The time-domain transfer characteristics of ramped gate biasing and fixed gate biasing is derived analytically. Both characteristics are compared regarding their suitability for MLC operation.

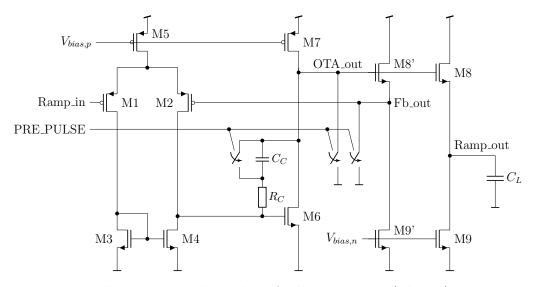

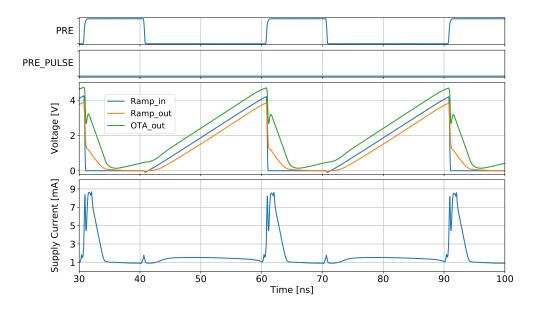

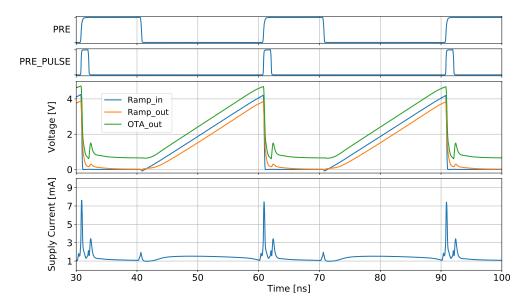

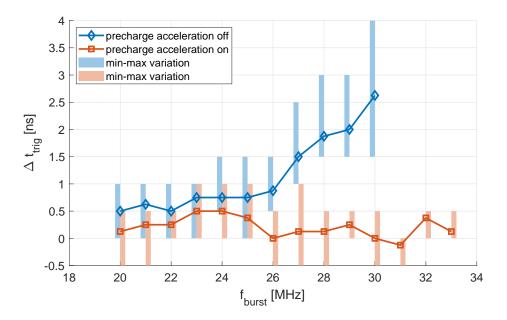

- An enhanced voltage mode sense amplifier design is presented, which extends a state-of-the-art design with an offset compensation and precharge acceleration mechanisms. Its improved sensing accuracy is shown in simulation.

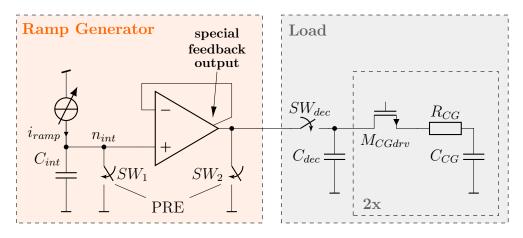

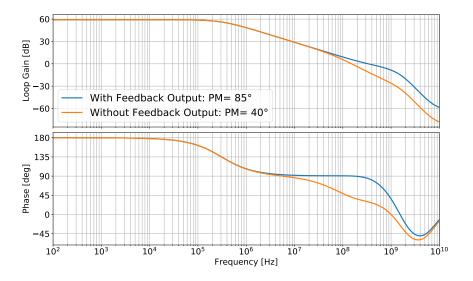

- A ramp generator design with fast recovery from discharge is presented. It implements the ramped gate biasing.

- A time-domain strobing concept is presented, which allows to analyze the sensing scheme with a time scan method.

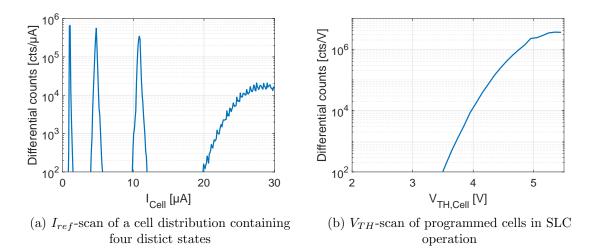

- The analytically derived transfer characteristic of the ramped gate biasing is verified by measurement.

- Experimental results demonstrate the functionality and performance of the sensing scheme, including the sense amplifier enhancements.

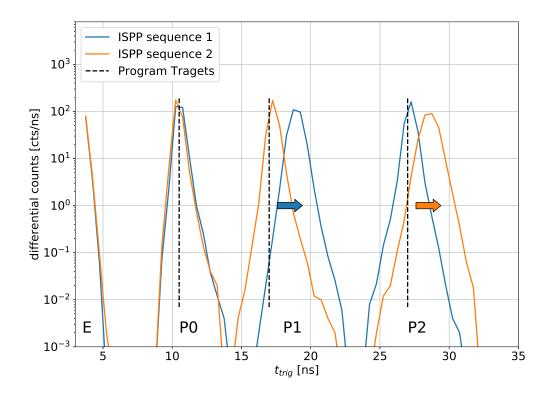

- The impact of the cell's control gate biasing on the programming is analyzed. The benefits of the ramped gate biasing are shown with measurement.

- Guidelines for the design of an efficient programming algorithm are developed.

#### 1.3 Outline of the Thesis

The thesis is organized as follows: Chapter 2 introduces the basic principles for storage and readout of multiple bits per Flash memory cell. Different MLC cell types are presented and techniques for sensing and programming are explained.

Chapter 3 gives an overview of the state-of-the art cell biasing schemes and compares them with respect to complexity, area and their suitability for high speed MLC operation. To assess the sensing robustness of the biasing approaches, their time-domain transfer characteristic is derived analytically.

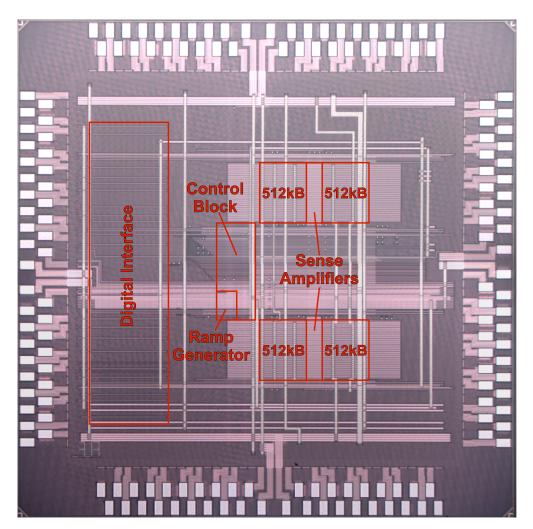

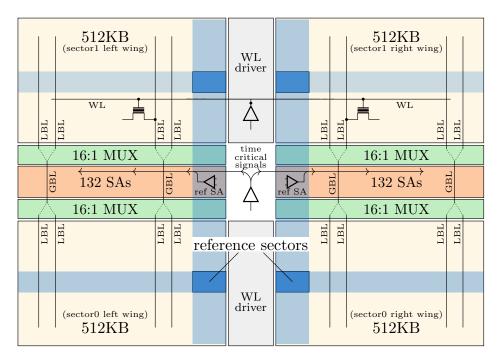

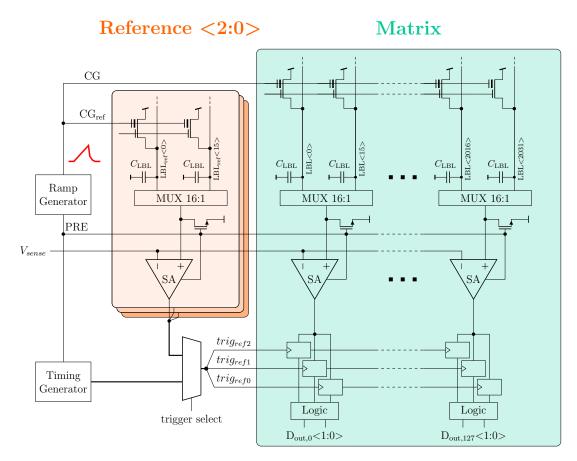

Chapter 4 describes the MLC sensing scheme developed in this work. The sense amplifier design using a current-biased slope detection is introduced and its improvements over the state-of-the-art voltage-biased design are analyzed. Mechanisms for acceleration of the sense amplifier's precharge process are presented and its high speed capability is shown. Further, the design of the deployed ramp generator for implementation of the ramped gate cell biasing is explained. The strobing concept of the sensing scheme is introduced and the analysis features implemented for investigation of the sensing performance are explained. Finally, the sensing architecture of the implemented test chip is discussed and measurement results are shown.

Chapter 5 discusses important aspects for the development of a precise programming algorithm for placement of multiple cell states. The impact of the used memory cell biasing on the programming performance is analyzed by means of experiments conducted on the fabricated test chip.

Chapter 6 summarizes the thesis' results and gives a short outlook on embedded memory technologies for future applications.

6

# Chapter 2

# Fundamentals of Multi-Level Cell Flash Memories

## 2.1 Cell Technologies for Multibit Storage

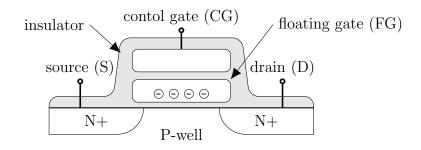

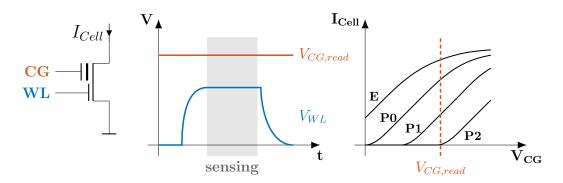

The floating gate field effect transistor was proposed by Kahng and Sze in 1967 [15]. It established the basis for all modern flash memories. The underlying principle is the storage of charge on a fully insulated electrode, located in between the channel and the normal gate electrode of a metal-oxide-semiconductor field effect transistor (MOSFET). The intermediate electrode, called floating gate (FG), usually is made of polysilicon. Since it is completely encapsulated by isolating layers, it can retain the stored charge for a very long period, which allows to store data, without need of constant power (non-volatility). The upper gate electrode is called control gate (CG). The voltage applied at this node shifts the potential of the FG by capacitive coupling and therefore controls the forming of a conducting channel in between the transistors drain and source contacts. Figure 2.1 shows the cross section of a floating gate transistor. It has the same characteristics as a

Figure 2.1: Cross section of a floating gate transistor. Electrons are stored on the fully isolated FG.

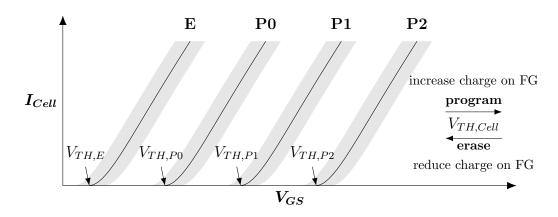

Figure 2.2: Current-voltage characteristics of four distinct cell states (2 bit per cell). Threshold variations due to inaccurate programming are highlighted in gray.

common MOS transistor, except for its variable threshold voltage  $(V_{TH,Cell})$ , which is modulated by the amount of charge that is stored on the floating gate. The threshold voltage change effectively results in a parallel shift of the transistor's transfer curve, as it can be seen in Fig. 2.2. It calculates as

$$\Delta V_{TH} = -\frac{\Delta Q_{FG}}{C_{tot}} \tag{2.1}$$

with the change of floating gate charge  $\Delta Q_{FG}$ , and the total floating gate capacitance  $C_{tot}$ , which calculates from the sum of all coupling capacitances between floating gate to the other transistor nodes. To program the cell, electrons have to be injected into the floating gate, resulting in a positive threshold shift. Therefore, high voltages have to be applied to allow the electrons to overcome or tunnel through the energy barrier in between channel and floating gate. Channel hot-electron (CHE) injection and Fowler-Nordheim (FN) tunneling are the two common programming mechanisms used. For erasure of the cell, voltage polarities are reversed, and electrons can exit the floating gate again; the threshold voltage reduces. The most common mechanism used for erase is FN tunneling [16, 17]. Typical voltages and durations for the programming/erase mechanisms are listed in Table 2.1. FN tunneling is slow, but very power efficient. CHE injection is the faster mechanism, but it is power inefficient, as just a few of the electrons traveling through the conducting channel are injected into the FG.

The floating gate transistors can be arranged to a memory array in various ways. The predominant two types used today are NOR Flash and NAND Flash. The NOR architecture connects the cells of each column with their drain terminal to the same bitline (BL). The source terminal of all cells is connected to one common source line. In this way each cell can be addressed individually, resulting in a byte-oriented memory. The NAND architecture contains strings of cells (typical

|                                | CG             | D             | S        | P-well         | Duration            |

|--------------------------------|----------------|---------------|----------|----------------|---------------------|

| Programming with CHE injection | $10\mathrm{V}$ | $5\mathrm{V}$ | 0 V      | 0 V            | ${\sim}1\mu s$      |

| Programming with FN tunneling  | $20\mathrm{V}$ | 0 V           | 0 V      | 0 V            | $\sim 1\mathrm{ms}$ |

| Erasing with FN tunneling      | 0 V            | floating      | floating | $20\mathrm{V}$ | $\sim 1\mathrm{ms}$ |

Table 2.1: Typical bias conditions and durations for the most common programming and erasing mechanisms.

string lengths are 8,16 or 32), that are connected in between BL and source line. Both string ends have an additional select transistor (string select and ground select). This array organization yields a higher packing density than achieved with the NOR organization. However, cells cannot be addressed individually, but in blocks, resulting in a block-oriented memory.

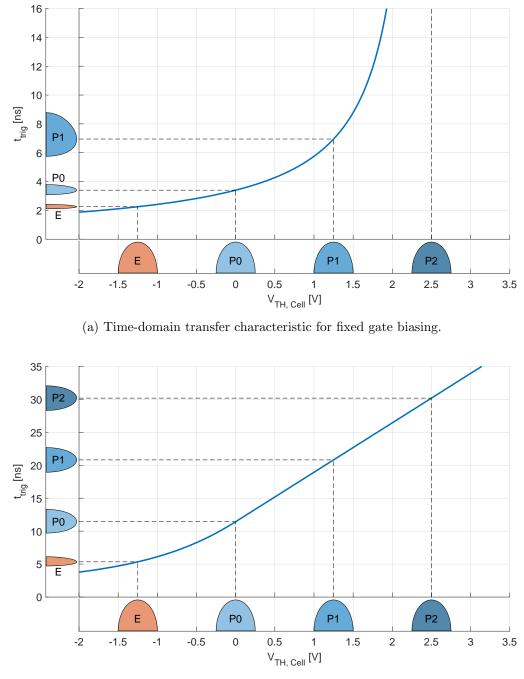

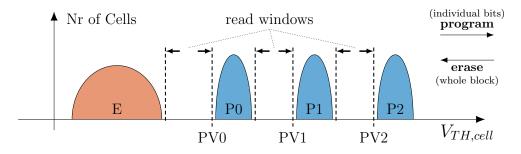

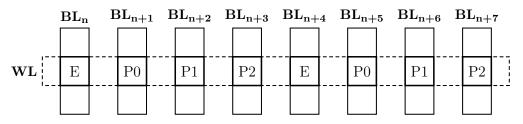

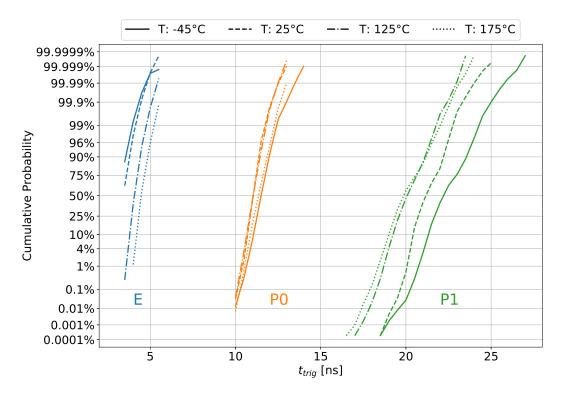

Since the amount of charge on the floating gate can be varied continuously, the storage principle of floating gate flash memories is perfectly suitable for MLC operation. That means every memory cell can store more than one bit of data, by modulating its threshold such that multiple distinct  $V_{TH}$  ranges can be distinguished. The storage of two bit per cell for example requires four distinct memory states. In Fig. 2.2 the shifted I-V characteristics needed for a 2 bit per cell operation is shown. With precise placement of charge  $Q_{FG}$ , the cells' thresholds are shaped to four groups representing the four cell states E, P0, P1, P2, which can be mapped to the 2-bit binary representation: 00, 01, 10, 11. The areas highlighted in grey indicate the uncertainty of the cell states arising from inaccurate programming. For reliable multilevel operation it is important to achieve very narrow  $V_{TH}$ distributions, to improve read windows. The distribution widths can be reduced by finer voltage stepping used for programming or sophisticated algorithms [9]. This aspect is discussed in Chapter 5. However, factors like random telegraph signal (RTS) [18] or inaccuracy of the sense amplifiers limit the precise placement of the cell threshold voltage.

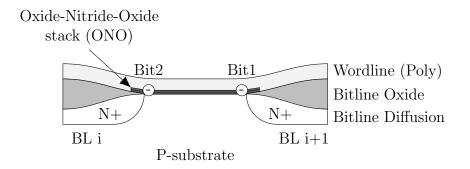

Besides the floating gate technology, NROM [19] is a further Flash memory technology which is capable of MLC operation. The memory cell differs from the conventional floating gate transistor in the used charge storage medium. Instead of a polysilicon floating gate electrode, an oxide-nitride-oxide (ONO) stack is placed above the channel. It stores charge localized inside nitride traps. Figure 2.3 shows a cross section of an NROM cell. By programming with CHE injection, the electrons are trapped in the nitride above the channel close to the junctions. This spatially confined injection of charges allows to store two bits of data inside one cell, physically separated at both ends of the N-channel transistor. The second bit

Figure 2.3: Cross section of an NROM cell along a wordline. Electrons are stored in the ONO stack.

is stored by reversal of the BL bias voltages for programming. The concept uses a reverse read method. That means the current direction through the channel during read operation is inverse to the direction during programming. In this way, the addressed bit is located at the electrical source of the cell during read operation. The large depletion zone induced by the high drain voltage at the opposite junction suppresses the second bit's channel impact and hence screens it out. This "local drain-induced barrier lowering effect" (DIBL) allows a reliable readout without significant cross talk between the bits [20]. It has been shown that the NROM cell is capable to store even 4 bit of data [21]. The high density is achieved by combining the concept of two spatially separated storage locations inside one cell with the concept of multiple charge levels programmed to the storage medium. In this way only four different charge states have to be distinguished at each end of the channel region. A conventional floating gate approach would require 16 distinct charge levels. However, the close proximity of both storage regions requires a special programming algorithm to overcome the cross talk issue (2nd bit effect) [22].

#### 2.2 Sensing Principles

The readout of data from a memory cell, called sensing, is performed by a sense amplifier (SA). Two different sensing approaches used with flash memories are state-of-the-art, current and voltage sensing. Both methods are based on a measurement of current flowing through the memory cell. The only difference basically is their way to convert the cell current into a voltage, that then is amplified to full logic level and latched as digital data.

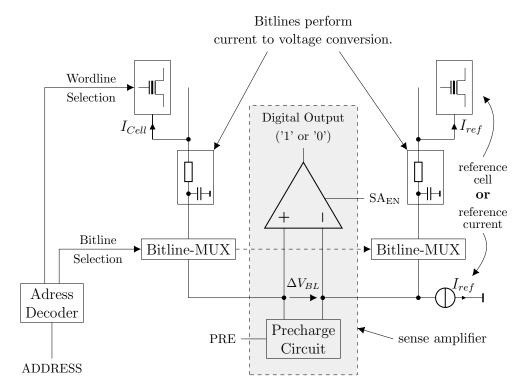

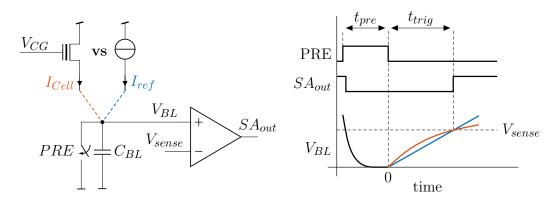

#### 2.2.1 Voltage Sensing

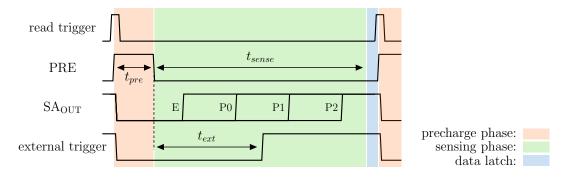

Figure 2.4 shows the typical voltage sensing principle. The read operation is split into two phases, a precharge phase and a sensing phase. At the beginning of the precharge phase the new address is decoded and the cells in the selected row (wordline) and column (bitline) are connected to the sense amplifier such that the cell current  $I_{Cell}$  can flow. Furthermore, a reference bitline is connected to the other input of the differential sense amplifier. Usually a normal bitline from another part of the memory array serves as reference here. In this way, good matching with respect of capacitance and resistance is achieved and the sense amplifier has symmetrical conditions at its input. The sensing works with reference cells or with a reference current. In the latter case, all cells along the reference bitline have to be deselected to prevent any extra current charging this node. At the same time, a precharge circuit preconditions both selected bitlines to a read bias voltage. When all voltages in the sensing path have settled, the precharge phase ends (stop of signal PRE) and the sensing phase starts. Both currents  $I_{Cell}$  and  $I_{ref}$ are converted into a voltage by integration on the bitline capacitance. Hence the current difference translates into a differential voltage  $\Delta V_{BL}$ . The sense amplifier is activated, detects the voltage difference and amplifies it to a digital output

Figure 2.4: Block diagram of the voltage sensing principle.

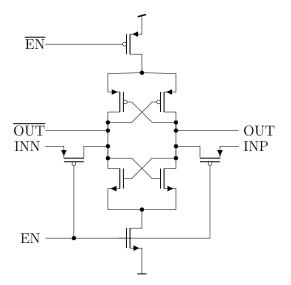

Figure 2.5: Latch type voltage comparator (dyamic comparator).

signal. It basically acts as simple voltage comparator, outputting a logic '1' or '0', depending on which of both bitline voltages is higher.

Voltage sensing is widely used in single-level cell (SLC) flash memory designs [23, 24, 25]. It works with a low complexity sense amplifier and can achieve highspeed read operation. A latch-type voltage comparator as shown in Fig. 2.5 is commonly used for sensing. However, the achievable sensing speed is limited by long bitlines with high capacitance. A long integration time is required to develop sufficient voltage difference  $\Delta V_{BL}$  at the comparator's input before sensing can be finished. Many designs additionally deploy an offset compensation to overcome missmatch between the transistors inside the latch and hence to reduce the voltage difference required for proper amplification. For MLC operation the sensing procedure described above has to be executed several times either with different reference currents or different cell bias. In Chapter 3 this aspect is discussed in more detail. Different to MLC NAND flash designs [26], voltage sensing is rarely used in MLC NOR flash designs. For this type of memory, the approach of choice is current sensing.

#### 2.2.2 Current Sensing

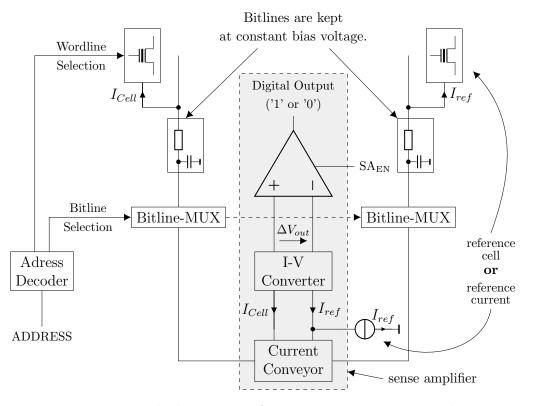

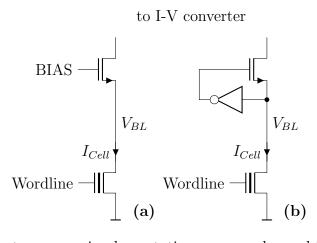

The current sensing approach performs the current to voltage conversion inside the sense amplifier. Figure 2.6 shows the basic current sensing principle. A current conveyor circuit first precharges the bitline up to its bias level right after the address change. For the rest of the read operation, it keeps the bitline voltage constant and passes both input currents on to a current-to-voltage converter cir-

cuit. Here the difference between both currents  $(I_{Cell} \text{ and } I_{ref})$  is translated to

Figure 2.6: Block diagram of the current sensing principle.

a voltage difference  $\Delta V_{out}$ . Finally, this difference is detected and amplified by a voltage comparator (as in voltage sensing) and afterwards latched as digital data. The sensing method also works with a current generated by a reference cell or with a constant reference current source. If no reference cells are used, the whole reference bitline path including conveyor can be omitted.

To keep the bitline voltage constant, the current conveyor needs an output impedance as small as possible. Common current conveyor implementations used for current sense amplifiers can be found in references [27, 28]. The most commonly used current conveyor for sensing in flash memories is the bitline voltage clamp, implemented as simple cascode (see Fig. 2.7). The scheme, often referred to as drain biasing, can be operated either with a fixed gate bias (static BL clamp) or regulated cascode with negative feedback inverter (dynamic bitline clamping). The latter implementation speeds up the bitline precharge at the cost of additional area and power overhead.

The voltage-to-current conversion is performed by a load attached to the current conveyor output. Typical loads found in sense amplifiers for non-volatile

Figure 2.7: Current conveyor implementations commonly used in flash memories: (a) Static BL clamping; (b) Dynamic BL clamping.

memory designs are simple resistor loads [29, 4], diode-connected transistor loads [30] or current mirror loads [31]. The most flexible of them is the current mirror load. It additionally allows to amplify the cell current and to distribute it to multiple voltage comparators. This is necessary if a multi-level cell is to be read with a parallel sensing scheme [3], where the cell current is compared simultaneously with multiple reference currents. Current sensing has a speed advantage over voltage sensing when the memory array has long bitlines with high capacitance [32]. Since the bitlines are kept at constant voltage and the voltage difference only develops between low capacitive internal nodes, the sensing operation is very fast. However, in comparison to that, precharging the bitline before the actual sensing takes long and is associated with significant power consumption. It makes up most of the timing budget of the whole read operation and hence has to be optimized in order not to lose the speed advantage. Furthermore, the constant operation condition of the cell is of advantage for small current windows between the cell states. Cell current stays constant during the whole read operation. With voltage sensing, it drops with the falling bitline voltage and hence results an effectively smaller current window. This is one of the reasons why current sensing is mostly used with MLC flash memories.

#### 2.2.3 Time-Domain Sensing

Current and voltage sensing differ in the way of biasing the memory cells and the location of the performed current to voltage conversion. However, they have in common that the voltage comparator inside the sense amplifier is activated at a specific point in time during the read operation. This activation time depends on the precharge duration of the bitline and the time needed for development of a sufficiently high differential voltage  $\Delta V_{BL}$  or  $\Delta V_{out}$ . Once activated, the latch-type sense amplifier very quickly falls into one of its stable states and the read operation is finished. Therefore, both sensing approaches have a well-defined sensing duration.

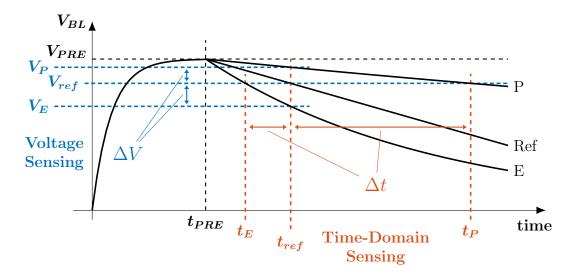

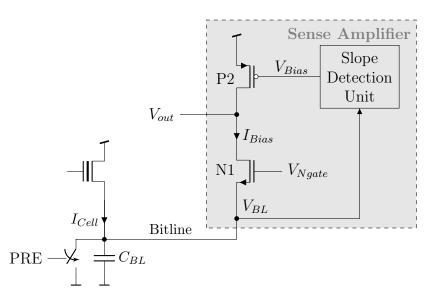

Time-domain sensing is a method that has a variable sensing duration. It can be combined with voltage or current sensing. In both cases a sense amplifier is used that is active during the whole sensing phase, continuously monitoring the bitline voltage (when combined with voltage sensing) or the cell current (when combined with current sensing). The more obvious approach is the combination with voltage sensing. Figure 2.8 shows the basic differences between conventional voltage sensing and time-domain voltage sensing. First, all bitlines are precharged to a common value  $V_{PRE}$ . After settling, the bitlines are released and hence discharged by the cell current or the reference current. Programmed cells (P) conduct almost no current and discharge the bitline very slowly. Erased cells (E) conduct more than the reference current and hence discharge the bitline faster. In the case of conventional voltage sensing, the sense amplifier is enabled at a certain time  $t_{ref}$ , when a sufficiently high voltage difference  $\Delta V$  with regard to the reference has developed. The voltage comparator then detects whether the input voltage is higher (programmed cell) or lower (erased cell) compared to the reference. Timedomain voltage sensing deploys a voltage comparator, that instantly reacts on the bitline voltage crossing a reference voltage  $V_{ref}$ . This leads to sense amplifier output signals carrying the information in their timing. Erased cells produce a signal

Figure 2.8: Comparison of conventional voltage sensing and time-domain voltage sensing.

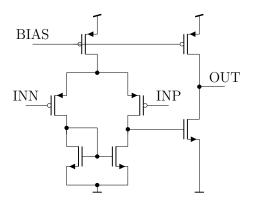

Figure 2.9: Continuous time voltage comparator (static comparator).

with short delay  $t_E$ , whereas programmed cells generate signals with long delay  $t_P$ . The data can be reconstructed from the time difference  $\Delta t$  towards the reference using a time to digital converter. Common latch type voltage comparators as used in conventional voltage and current sensing are not suitable for this operation, since they are clocked and hence cannot directly react on a voltage crossing at the input. Instead, static voltage comparators have to be used for this sensing approach. A suitable comparator implementation widely discussed in literature is an uncompensated two-stage operational amplifier [33, 34] (see Fig. 2.9).

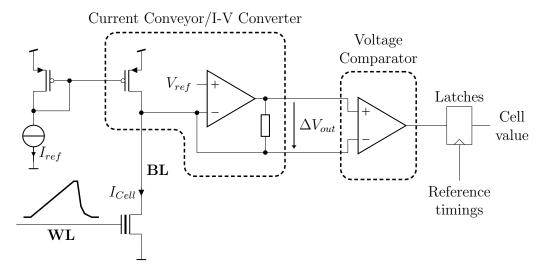

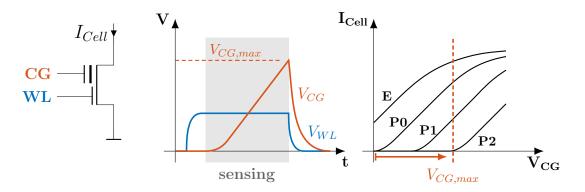

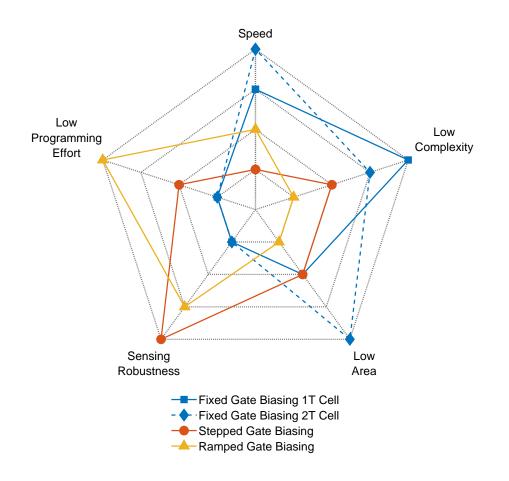

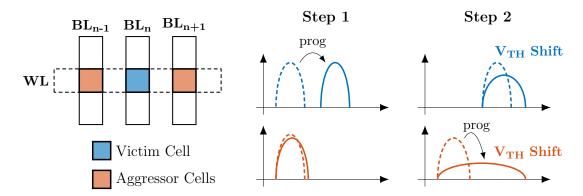

Conventional current sensing cannot directly be combined with the time-domain principle. Since cell bias conditions are kept constant (including the cell current), there is no time varying trigger condition to be monitored by the sense amplifier. To enable time-domain current sensing, the cell bias can be varied dynamically. Figure 2.10 shows an approach that uses a linear voltage ramp at the control gate to combine advantages from current and time-domain sensing [35]. With the ramp, the cell current rises dynamically during the sense operation and triggers a current mode sense amplifier once it reaches the reference level  $I_{ref}$ . The first stage implements a current conveyor that precharges the bitline and converts the current difference  $\Delta I = I_{Cell} - I_{ref}$  into a voltage difference  $\Delta V_{out}$ . This voltage is detected by a voltage comparator, whose digital output then is evaluated in the time-domain. As in time-domain voltage sensing, the deployed sense amplifier has to have a static output stage and cannot use a clocked latch type voltage comparator.

In general, time-domain sensing benefits from the local translation of the cell state (either by cell current or bitline voltage) to a digital signal carrying the information in its timing. The concept is robust since the sensing decision is taken in the digital domain, and it allows an efficient reference distribution throughout the memory module [36]. As described in Section 4.3.2, the reference time can be generated very flexibly and not necessarily is linked to reference cells or a reference

Figure 2.10: Time-domain current sensing scheme using a linear voltage ramp at the word line [35].

current like used in conventional current or voltage sensing.

### 2.3 Incremental Step Pulse Programming

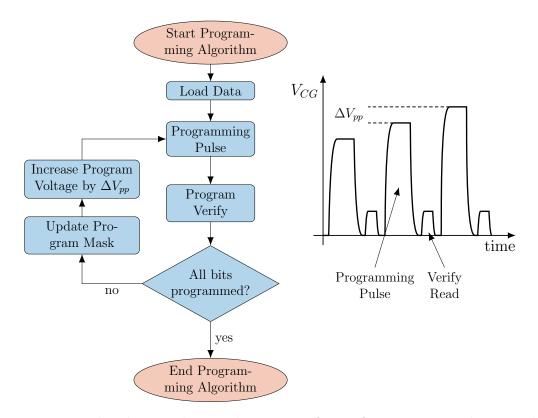

The key for a reliable MLC operation is a well-controlled threshold voltage  $(V_{TH})$ distribution of the memory cells. That means, the threshold voltage of each cell representing one memory state (E, P0, P1, P2) has to stay within a certain range, in order to prevent the states to overlap each other. Early SLC NAND EEPROM designs faced this issue already in the late 1980s. To program the  $V_{TH}$  of the cells to a range in between 0 V and the supply voltage  $V_{CC} = 5$  V or 3 V, programming techniques including verify mechanisms were developed [37, 38]. Their underlying principle is a series of short programming pulses (steps) each followed by a verify read, which is a normal read operation executed at the target CG bias. As this verify read is intended to check whether a cell's  $V_{TH}$  is programmed sufficiently, it is referred to as program verify. With the program verify, the algorithm excludes cells which already reached the target  $V_{TH}$  from further programming pulses. If the program verify yields zero fails, the programming operation is finished and the sequence can proceed to the next memory address to be programmed. With this technique much tighter  $V_{TH}$  distributions could be achieved since program duration was controlled individually, which could compensate for varying cell parameters and varying program voltage levels. A tight threshold control however required many programming steps leading to a low programming throughput. To optimize programming speed, a scheme with quasi-logarithmically increasing pro-

Figure 2.11: Flowchart and control gate waveform of an incremental step pulse programming algorithm.

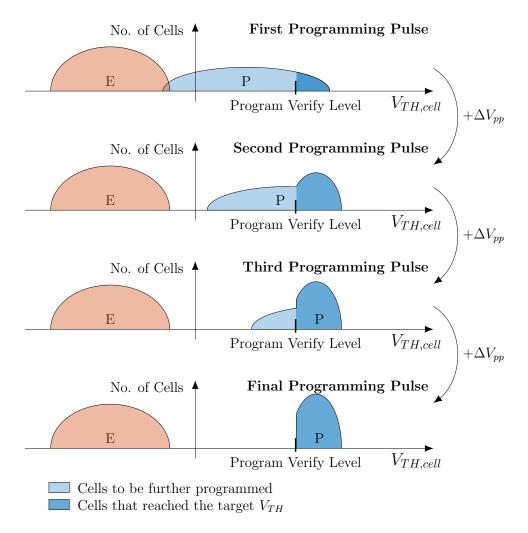

gramming pulse width was introduced, which reduced the verification overhead by two orders of magnitude [39]. The CG voltage applied during the programming pulses (program voltage or  $V_{pp}$ ) remained constant. In the mid of the 1990s, a scheme combining the program verify methodology with a step by step increasing program voltage was introduced [40]. It formed the basis for all modern, sophisticated incremental step programming pulse (ISPP) schemes. The program verify prevents the fast cells to be overprogrammed, whereas the increased voltage of the subsequent pulses accelerates the programming of the slow cells. Figure 2.11 shows the basic ISPP algorithm. After each program verify the cells which already reached the program verify level are excluded from the subsequent programming pulse (masked out), the program voltage is increased by  $\Delta V_{pp}$  and the next programming step is executed started. In theory, this approach yields threshold distributions with a width of  $\Delta V_{pp}$ . Real designs however do not achieve this theoretical minimum. Their distribution width is wider due to inaccuracies in the sensing path, deviations of the  $V_{pp}$  level and RTS [41]. The process of forming a narrow program distribution (distribution of the cell threshold voltages of all cells in the programmed state) step by step, starting from a broad erase distribu-

Figure 2.12: Distribution compaction during the incremental step pulse programming algorithm. Starting from the erased state (E), the cells to be programmed (P) get shifted step by step to their target threshold voltage, above the program verify level.

tion (distribution of the cell threshold voltages of all cells in the erased state) is illustrated in Fig. 2.12. Staring from the erased state (E), the threshold voltages of cells to be programmed (P) are shifted step by step to the right. Once they reach the program verify level, they are masked out and their  $V_{TH}$  remains at this position. After the final step, all cells to be programmed have a  $V_{TH}$  above the program verify level.

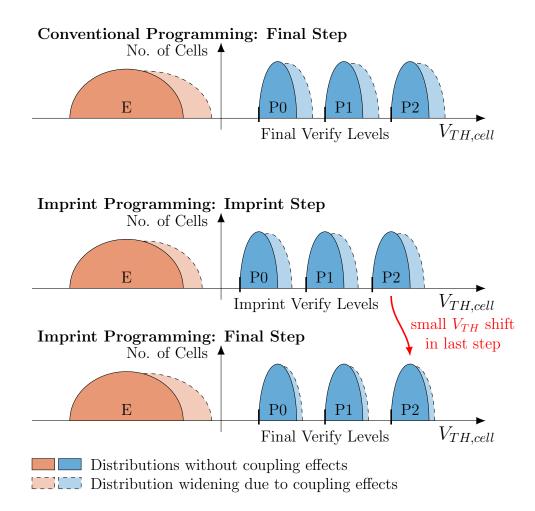

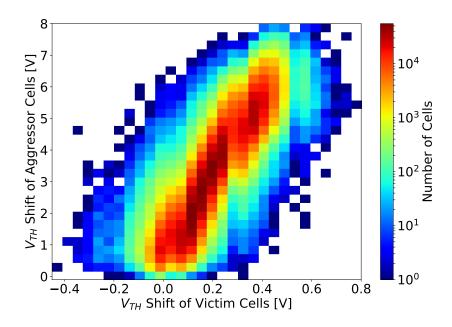

The storage of multiple bits per memory transistor in very dense cell arrays requires to consider interferences between adjacent cells, like floating gate to floating gate coupling. Due to the diminishing space for placement of multiple threshold

Figure 2.13: Methodology of imprint programming: Programming overshoot is reduced by minimizing the  $V_{TH}$  shift caused by the final programming step.

distributions,  $V_{TH}$ -shifts caused by programming of adjacent cells have to be minimized, to keep up the already narrow read windows. At the top of Fig. 2.13 the impact of coupling effects on the read window can be seen. Basically, there are two algorithm related measures to reduce the shifts. The first one is a width reduction of the initial erase distribution which reduces the  $V_{TH}$  difference between deeply erased cells and strongest programmed cells. A control of the erase distribution can be realized by a erase-verify methodology in the same manner as the ISPP. The other measure is an imprint programming method [42]. It is depicted in the lower two diagrams of Fig. 2.13.

The idea is to program the cells of multiple, physically adjacent pages to a lower target level (the imprint level) first. After this, the cells are shifted to their final  $V_{TH}$  level within one last programming operation. In this way, a margin for coupling effects is left in the first step (Imprint Step). The  $V_{TH}$ -shift of the last programming step is minimized and hence an overshoot due to FG coupling is reduced. Over the years, algorithms for ISPP have been consequently improved to increase programming throughput, reduce bit error rate to allow for three or even four bit per cell operation [43, 9, 10].

#### 2.4 Summary

The floating gate field effect transistor and NROM are two non-volatile memory technologies that are suitable for storage of multiple bits of data per cell. Both are based on shifting the threshold voltage of a field effect transistor by introduction of charge carriers into a layer above the channel. Either the amount of charge or its specific location can modulate multiple cell states and hence enable multi-level operation. The NROM transistor allows to combine both parameters to achieve a density of 4 bit per cell with 2 bits at each end of its channel.

There are two sensing methods commonly used to read out flash memory cells, voltage sensing and current sensing. With voltage sensing, the cell current and the reference current both are integrated on a separate bitline. The resulting voltage difference is sensed by a voltage comparator. The approach can be realized with low complexity. It reaches fast sensing speeds when bitline capacitances are low. In NOR flash designs, voltage sensing is only rarely used in combination with multi-level cell operation, since it can only be realized in a serial sensing manner. In current sensing, the cell bias conditions are kept constant and the cell current is compared directly inside the current sense amplifier. This enables accurate sensing even with small current windows and fast sensing at long bitlines with high capacitance. It is the common sensing approach for MLC NOR flash designs. Time-domain sensing can be combined with both voltage and current sensing. It uses a time continuous sense amplifier, which triggers when the bitline breaks though a reference voltage or when the cell current breaks through a reference level. The sensing decision is done by a time to digital converter in fully digital fashion. It allows for a flexible and robust distribution of the reference signal.

A good control of the programmed threshold is the key for a robust multi-level operation. ISPP is the method for shaping of narrow threshold distributions. It is based on a programming algorithm, which increases the program voltage from step to step and excludes cells from subsequent programming pulses, once their threshold is shifted to the target value. To handle multiple threshold distributions in dense cell arrays, effects of floating gate to floating gate coupling are reduced by introduction of methods like erase threshold control or imprint programming. Over time, programming throughput and bit error rates have been optimized by various sophisticated programming algorithms.

# Chapter 3 Memory Cell Biasing

Flash memory cells can provide long data retention time, provided that they are biased correctly to ensure a reliable programming, erasing and read operation. Depending on cell and memory technology type, biasing schemes differ in complexity. Cell operations in NAND-type flash memories generally have more complex schemes than in NOR-type memories. The NAND arrangement in strings requires all unselected cells in the selected string to be biased in on-state to allow readout of the selected cell. NOR-type memories have to select only one wordline at a time, but on the other hand have to cope with an overerase issue, if 1-transistor cells (1T cells) are used. Hence, measures like preprogramming or soft programming [44] have to be deployed and the control gate voltage has to be chosen carefully. Use of 2-transistor cells (2T cells) eliminate the need for a controlled erase threshold and their suitability for low voltage read operation [45] makes them a good choice for embedded Flash memory application. However, no matter which cell type is used, the voltages conditions applied to the cell terminals during read operation are decisive for the usable read window, which is of big importance for MLC memories. This chapter discusses the impact of different cell biasing schemes on the read conditions of NOR-type Flash cells and investigates their suitability for MLC operation. For assessment of the resulting sensing robustness, the time-domain transfer characteristic obtained with the different cell biasing schemes is derived analytically.

### 3.1 Concepts

An important aspect of a biasing scheme is the voltage applied to the CG terminal of a memory cell. According to this aspect, the schemes from literature shall be classified in three major groups.

#### 3.1.1 Fixed Gate Biasing

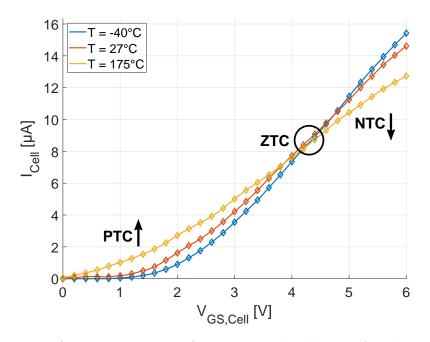

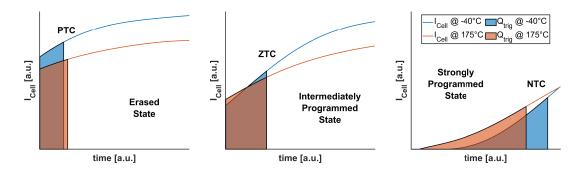

The simplest CG biasing approach is to use one constant voltage level  $V_{CG,read}$ during read operation. This method is widely used in SLC as well as MLC applications. The voltage level is placed between the threshold voltages of erased and programmed cells. In this way, cells with a threshold voltage  $V_{TH,Cell}$  lower than  $V_{CG,read}$  - erased cells (E) - will conduct a high current and programmed cells (P2) with a threshold higher than  $V_{CG,read}$  will conduct virtually no current (see Fig. 3.1). The resulting relative cell current window calculates as

$$W_{I,rel} = \frac{I_{Cell,LVT} - I_{Cell,HVT}}{I_{Cell,LVT}},$$

(3.1)

where  $I_{Cell,LVT}$  corresponds to the current of the cell state with lower threshold and  $I_{Cell,HVT}$  to the current of the cell state with higher threshold. For SLC flash memories, this leads to a comfortable window close to 100%, since the current of the programmed cell is zero with a correct placement of  $V_{CG,read}$ . To distinguish multiple cell states with only one bias voltage, it has to be placed in between the threshold distributions of the two stronger programmed states (P1, P2), as it is shown in Fig. 3.1. The result is several cell current levels that have to be distinguished. Either, this is accomplished by comparing those currents to multiple reference currents sequentially (serial sensing scheme) [4, 46, 31] or in parallel (parallel sensing scheme) [3]. The latter implementation has to provide parallel sensing and reference structures and hence has significant area overhead. However, it can cut down access time by up to a factor of three within a 2 bit per cell operation. For distinction of the high current states (E, P0), the constant biasing provides a significantly reduced relative cell current window, which is the major issue with this approach, when used for MLC implementations. 2T cell configurations suffer most from this penalty, as their available cell current range is

Figure 3.1: Gate voltages and operation point during a read operation with fixed gate biasing concept (2T cell).

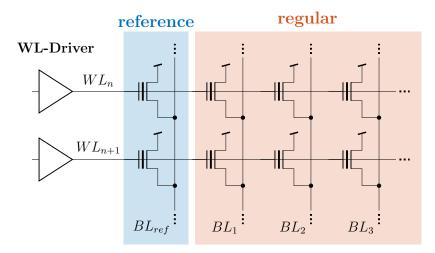

Figure 3.2: Simplified structure of a fixed gate biasing scheme using split-gate 2-transistor flash cells.

limited by the select device of the cell (select transistor) connected to the wordline (WL) (which can be seen in Fig. 3.1 from the saturating transfer curve of the states E and P0). Hence, a precise SA with larger dynamic range is needed to ensure robust read operation. Another drawback are the voltage drops in the array as well as at selection transistors, caused by high cell currents. Also cell gain variations have a big impact on the current in this operating point. Both effects broaden the distributions and are temperature dependent. So, the read windows severely degrade, which further complicates distinction.

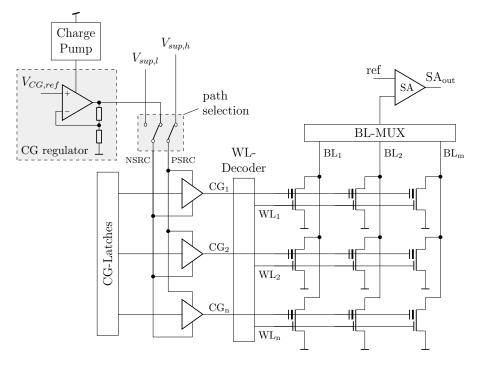

Figure 3.2 shows the simplified architecture with a constant CG biasing using split gate, 2T cells. A single voltage regulator is capable to supply the bias voltages for normal read mode as well as for verify modes as used in a ISPP algorithm. The voltage level is distributed via the decoding path to each of the array's CG lines. Depending on the range of voltage level, either the NMOS path (NSRC, used for lower range) or the PMOS path (PSRC, used for upper range) of the driver is chosen. Read or verify levels that exceed the supply voltage of the chip have to be provided by a charge pump, which is also required for programming the flash cells in case of common supply levels. When 2T cells are used, the row selection is done with the select transistor at the WL [47] and the driving strength of the CG path, which has to be designed for high voltage operation, can be reduced to a minimum,

as all CG terminals globally stay at  $V_{CG,read}$  during read mode. Programming and erasing are slow speed operations (in the range of micro seconds) and hence do not require strong drivers. To avoid sudden erroneous switching within the high voltage modes, the CG selection signals usually are latched. Latching is required for parallel erasing of multiple blocks, too. The WL-decoder needed for row selection can be designed in a lower voltage domain and hence does not contribute much to the area consumption. Therefore, this biasing scheme has a big area advantage over other schemes; the slow high voltage path is fully decoupled from the fast row selection path. This advantage in area disappears with the use of 1T cells. Here, the row selection for read and programming operations are done via the same drivers, which require them to be big, due to large high voltage (HV) devices and high W/L for low ohmic read.

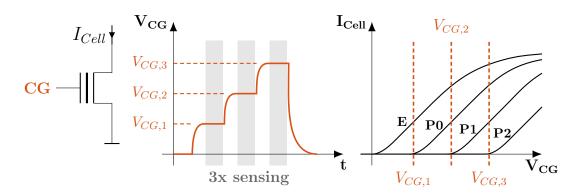

#### 3.1.2 Stepped Gate Biasing

Biasing schemes with variable CG voltage aim for a better operating point of the memory cell during read operation. Stepped gate biasing schemes therefore apply multiple read voltages sequentially to the control gate [6, 48]. For each sense operation, a specific level is chosen, which is optimal for distinction of two adjacent cell states (see Fig. 3.3). With a CG voltage just below the threshold of the stronger programmed cell, the relative cell current window gets close to 100%. Thus, the dynamic range requirement of the sense amplifiers is heavily reduced compared to an approach using fixed gate biasing. Each comparison can be carried out with one very low reference current, which considerably reduces the impact of resitive voltage drops in the read path and cell gain variations. The use of multiple cell operation points requires a serial sensing scheme and hence suffers from large time overhead compared to fixed gate biasing. Therefore, it is not fully

Figure 3.3: Gate voltages and operation point of a read operation with steppedgate biasing concept (1T cell).

Figure 3.4: Simplified structure of a stepped gate biasing scheme using 1-transistor flash cells.

suitable for high speed operation. Tightly spaced threshold distributions and the requirement of very low read currents make this the state of the art approach for high density NAND flash memories achieving up to four bits per cell [43].

The implementation of a serial sensing with stepped CG bias voltage can be done in a similar way as the fixed gate biasing. Figure 3.4 illustrates a typical stepped gate biasing setup [6, 48]. The most critical aspect for fast memory access is the change of  $V_{CG}$  within every read operation. Each individual voltage level has to be provided by its own regulator. A source follower output ensures a low output impedance and the capacitance along the wordline selection path is reduced by a partitioning into small memory blocks, that are all, except the selected one, separated from the voltage supplies. A separation between slow HV path for programming and fast selection path during read operation is not possible here. Therefore, independent of the used flash cell type (1T or 2T), the WL-driver has to be designed with high driving strength. Otherwise, its RC time constant becomes too big for quick voltage stepping. Consequently, this biasing approach requires more area than the fixed gate schemes. Furthermore, a logic is needed, which consecutively selects the different bias levels and triggers the individual sense operations. As long as there is sufficient wait time for all changing nodes to settle, an exact synchronization is not needed. The complexity added by this sequencing logic therefore is low.

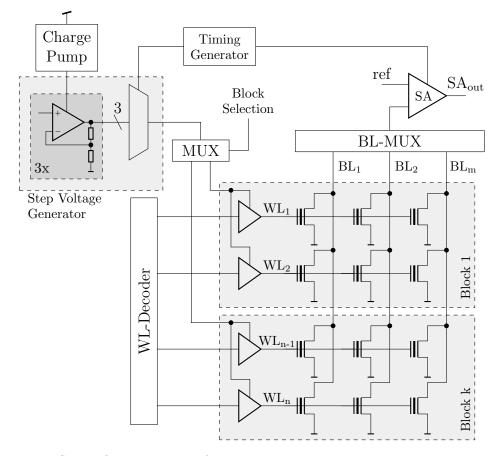

#### 3.1.3 Ramped Gate Biasing

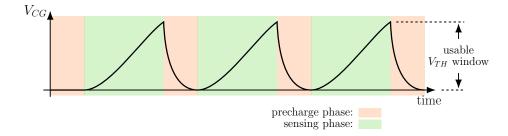

The third biasing scheme found in literature dynamically applies a linear voltage ramp to the cells' CG terminals [7, 35]. After a precharge phase, the ramp starts at the beginning of the sensing phase and varies the cell biasing during the whole operation (see Fig. 3.5). In this way, erased cells start with an initial current which increases with time. Programmed cells start with zero current and reach conductivity once the bias ramp hits their threshold voltage. Hence the comparison between different cell states cannot be done in terms of the cell current level itself. The decision has to be transferred into the time domain. This can be done by integrating the cell current on the BL capacitance (or on another dedicated integration capacitance) up to a certain voltage level (time-domain voltage sensing) or by directly comparing the instantaneous current against a certain level (time-domain current sensing). With its inherent time-domain nature, the ramped gate biasing is capable of parallel sensing; multiple sense operations, including precharge phase, are not needed. Therefore, low access times can be achieved. In addition, the advantages of an increased CG bias range apply for this biasing scheme. It provides a compromise between sensing speed and accuracy and is well suited for the use in MLC flash memories.

The structural difference between a ramped gate and a stepped gate biasing

Figure 3.5: Gate voltages and operation point of a read operation with ramped gate biasing concept (2T cell).

Figure 3.6: Simplified structure of a ramped gate biasing scheme including reference path.

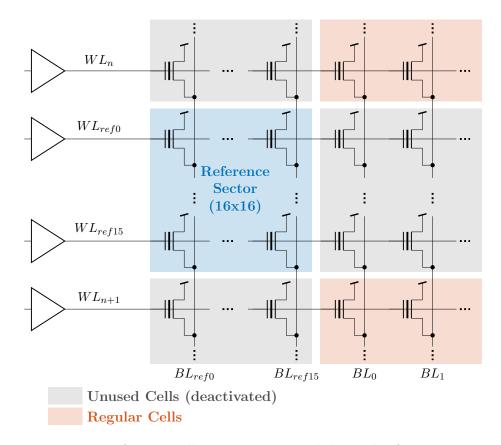

implementation is small. However, the linear voltage ramp requires more complex row selection and sensing circuitry. Figure 3.6 shows a corresponding implementation. To propagate the voltage ramp quickly, strong WL-drivers are as important for this approach as for stepped gate biasing schemes. As the threshold voltage of the erased state (lowest  $V_{TH}$  state) usually is negative for embedded NOR Flash cells, it is a good choice to start the ramp at 0 V. Therefore it has to be transferred to the CG via the NMOS path of the driver or via a special transmission gate. In the first case, a sufficient gate overdrive has to be provided, which might require a pumped voltage. The latter solution considerably increases the area of the HV driver structure.

For best match to cell properties, reference cells should be used and sensing paths (matrix and reference) have to be matched in terms of resistance and capacitance, when a ramped gate biasing is deployed. With the dynamic CG biasing, this task requires special attention, as there are transient events both on WL and BL that have to be properly synchronized. Since both circuit parts (WL-driver and SA) are not necessarily located nearby, their signal paths should be well aligned. Timing signals, like the precharge enable, the SA strobes and the voltage ramp itself, hence should have the same traveling directions and a matched RC delay along the memory array. The reference cell array and the highly dynamic ramp generator lead to a considerable circuit and testing overhead. Reference cells have to be preconditioned and afterwards protected against any disturbance, since they must not change their properties during the whole lifetime. These requirements make this approach the most expensive in terms of area and complexity.

### **3.2** Speed Considerations

Depending on its application, a flash memory faces different speed requirements. One key performance parameter is the read throughput, which is significant for storage applications with large and preferably linearly accessed data. It is mainly increased by parallelization of read accesses, requiring more sense amplifiers and a faster data bus to transfer the data. The memory's read latency, described by its random access time  $t_{acc}$ , is another important performance parameter. It has large relevance in applications with many random memory accesses. Execution of code directly from the non-volatile memory (Execute-in-place), as commonly done inside MCUs, also requires a fast random memory access with low latency. Both performance parameters, read throughput and read latency, are affected by precharge duration of the memory cells in the array, but the latter one cannot be improved by placing more sense amplifiers in parallel. Latency is only dependent on the access time of one single read. Therefore, the impact of the three different cell biasing schemes on the achievable access time shall be analyzed.

The speed of the variable CG voltage bias schemes is mainly limited by the dynamics of the CG lines. Within this section they are referred to as wordlines, although in 2T cell configurations the select gate is associated with this term. As the dynamics of the select gate usually is higher compared to the CG, they are not included in the speed considerations.

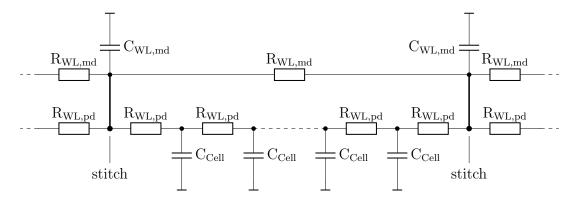

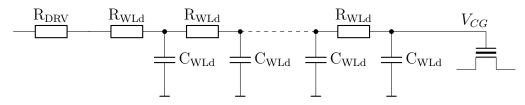

#### 3.2.1 Wordline Model

The wordline of a flash array consists of a high resistive poly silicon line, with equally spaced contacts (stitches), connecting to a low resistive metal line, that is routed over the whole width of the array. Figure 3.7 shows a part of a wordline model using two distributed RC lines for metal and poly routing, regularly interconnected with metal stitches.  $R_{WL,md}$  represents the metal resistance,  $C_{WL,md}$  the metal capacitance per unit length. The poly resistance in between the cells is modeled by  $R_{WL,pd}$  and the cells' gate capacitance by  $C_{Cell}$ . Coupling capacitances to adjacent BLs are included in this value. With a resistance  $R_{WL,pd}$  in the range of kilo ohms, the poly line RC time constant quickly becomes dominant and hence

Figure 3.7: Delay line WL model including metal and polysilicon path regularly connected by stitches.

Figure 3.8: Simplified delay line WL model including driver resistance.

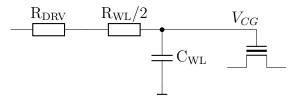

limits the dynamics of the cells' control gate voltage. To allow quick changes of the CG potential, the distance of the stitches has to be low, in order to achieve a poly line delay, which is small compared to the total RC time constant of the WL. Thus, the model can be simplified significantly, by merging all capacitances into one lumped capacitor  $C_{WL,d}$  per stitch. This simplification results in the model shown in Fig. 3.8. It includes the wordline driver resistance  $R_{DRV}$ . The floating gate transistor symbolizes the cell at the far end of the wordline. It experiences voltage changes with the worst-case delay. To get an appropriate estimation, the delay line can be modeled using a first order  $\pi$ -approximation [49]. Neglecting the source resistance (internal resistance of the driving source), the time constant of the distributed RC line then is described by its lumped resistance  $R_{WL}$  and its lumped capacitance  $C_{WL}$  as

$$\tau_{WL} = \frac{R_{WL}C_{WL}}{2}.\tag{3.2}$$

Though the settling time of the step response is overestimated, using this approximation, it gets more accurate, as the source resistance rises. Since the WL-driver uses high voltage transistors,  $R_{DRV}$  accounts for the major portion of the path resistance, making it a good approximation for the source resistance. A reasonable estimation of the settling time hence can be obtained replacing the RC line

Figure 3.9: Strongly simplified, lumped WL model including driver resistance.

by the resistance  $R_{WL}/2$  and the capacitance  $C_{WL}$ . With this strongly simplified WL-path model shown in Fig. 3.9, the time needed for proper control gate voltage changes can easily be compared among the different biasing schemes. Its overall RC time constant calculates as

$$\tau_{CG} = \left(R_{DRV} + \frac{R_{WL}}{2}\right)C_{WL}.$$

(3.3)

The error introduced by the simplifications made above, does mainly affect the cells that are located far from the WL stitches. They experience the changing bias voltage with a slightly higher delay than the cells directly at the stitches. For a general comparison of the different biasing schemes, this is of lower relevance, but anyhow has to be considered for the design of the memory array.

#### 3.2.2 Access Time

#### **Fixed Gate Biasing**

A constant CG voltage scheme using a 1T cell requires the WL to be raised to its bias level for every read operation. Consequently, a precharge time of at least three times  $\tau_{CG}$  has to be spent prior to the sense phase, to ensure sufficient settling. For typical values ( $C_{WL} = 1 \text{ pF}$ ,  $R_{DRV} = 2 \text{ k}\Omega$ ,  $R_{WL} = 1 \text{ k}\Omega$ ) the precharge time needed yields  $t_{pre,WL,fix} = 3\tau_{CG} = 7.5 \text{ ns}$ . The BL is precharged simultaneously. As the BL does not consist of polysilicon but of metal, it is precharged faster. Thus, the read access can be approximated to

$$t_{acc} = t_{pre,WL} + t_{sense}.$$

(3.4)

The sense delay  $t_{sense}$  represents the time needed by the sense amplifier to compare the cell current to the reference current. A typical sense delay of  $t_{sense} = 10 \text{ ns} [50]$ would then result in an access time of  $t_{acc,fix,1T} = 17.5 \text{ ns}$ . The sense delay of an MLC memory will not be the same as in an SLC implementation like referenced from [50], since the current read windows are much tighter and the respective signals (e.g. cell current differences) are smaller. However, it affects the absolute duration of the read access for all biasing schemes the same and hence this assumption still is suited for a comparison among the three different approaches. Using a 2T cell yields the advantage that the whole array can be biased at the target control gate voltage during read mode and the row selection is done with the select devices. Since these are typically lower voltage class devices, they can be selected much faster. In this case, the BL precharge usually defines the precharge duration and the result is an access time of about

$$t_{acc,fix,2T} = t_{pre,BL} + t_{sense} < t_{pre,WL} + t_{sense} = 17.5 \,\mathrm{ns},$$

(3.5)

depending on the time needed for BL precharge  $t_{pre,BL}$ .

#### Stepped Gate Biasing

The stepped gate approaches change the CG voltage multiple times for one read. Given there is sufficient gate overdrive for the WL-driver, the same values as above can be taken for calculation of the precharge time needed. A two bit per cell operation requires three consecutive sense operations each preceded by a precharge phase. So every read requires in total a precharge time of

$$t_{pre,step} = 3t_{pre,WL,fix} = 22.5 \,\mathrm{ns.}$$

(3.6)

This time only considers the stepping of the WL. Charging of the path from step voltage generator to the selected row driver (compare Fig. 3.4) might prolong the needed wait time. To estimate the possible read access time, three times the sense delay has to be added. Considering the changed bias conditions for each consecutive sensing, the relative current read window is better than in the fixed gate scheme. Absolute cell currents however are in the same range as the current of the intermediately programmed cells (P1) when using only one gate bias (compare Figs. 3.1 and 3.3). So, the sensing gets more robust, but the sensing delay will stay in the same ballpark. Therefore, the same sense delay is assumed, which results in a total access time of

$$t_{acc,step} = t_{pre,step} + 3t_{sense} = 52.5 \,\mathrm{ns.} \tag{3.7}$$

#### **Ramped Gate Biasing**

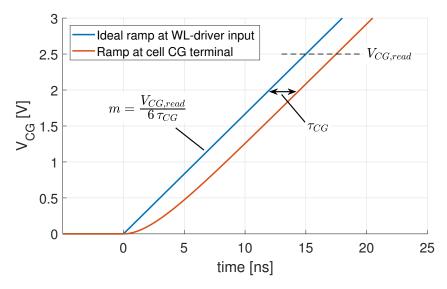

Ramping the CG voltage yields a compromise between sensing speed and optimum read bias. In contrast to the stepped gate scheme, it is not necessary to wait for the settling of the bias voltage. Instead, sensing phase can start simultaneously with the rise of the applied voltage ramp. However, the selected CG terminals end at a high voltage level after each read operation and they have to be precharged at least once, in order to ensure same starting conditions for each ramp. Using the same resistance and capacitance values as above results in  $t_{pre,ramp} = 3\tau_{CG} = 7.5$  ns. After this wait time the ramp generator starts to raise the voltage. Along the path from the generator to the cells (compare Fig. 3.6), the ramp gets delayed. In general, the major part of the delay is caused by the WL-driver and the WL itself. WL-drivers are placed at every WL and thus contribute significantly to the total area, the remaining blocks however are placed less often and hence can be scaled up sufficiently. So the delay is determined by the RC time constant  $\tau_{CG}$ from (3.3). To get to the WL's response to a linear voltage ramp at its input, we start with the step response of the RC lowpass with  $V_{CG}(t=0) = 0$  [51]:

$$V_{CG,step}(t) = V_{CG,read} \left( 1 - \exp\left(-\frac{t}{\tau_{CG}}\right) \right).$$

(3.8)

Since a linear ramp input signal  $v(t) = m \cdot t$  is obtained by integration of a step signal with height m, the ramp response of the RC lowpass can be calculated using the integration property of linear time-invariant systems [52]. So the ramp response results from the integration of (3.8) to

$$V_{CG,ramp}(t) = m \cdot t - m \cdot \tau_{CG} \left( 1 - \exp\left(-\frac{t}{\tau_{CG}}\right) \right)$$

(3.9)

with  $m = V_{CG,read}$ . Under the condition that the input voltage ramp lasts long enough compared to the time constant of the wordline  $(t > 3\tau_{CG})$ , the exponential term approaches zero and simply leaves a delayed version of the input. This means that as long as the ramp slope is chosen moderately, as

$$m = \frac{V_{CG,read,max}}{6\tau_{CG}} \tag{3.10}$$

for example, the signal reaches the control gates of the memory cells with a delay of  $\tau_{CG}$  approaching the same slope (see Fig. 3.10). Since the sensing phase starts simultaneously with the ramp start, the read access is finished latest one sense delay after the control gate voltage reached the maximum read bias target  $V_{CG,read}$ (corresponding to the third read bias level in the stepped gate approach; compare Figs. 3.1 and 3.5). According to (3.9) and the required precharge time  $t_{pre,ramp}$ , this accumulates to an access time of

$$t_{acc,ramp} = t_{pre,ramp} + 6\tau_{CG} + \tau_{CG} + t_{sense} = 10\tau_{CG} = 35 \,\mathrm{ns.}$$

(3.11)

Figure 3.10: Ramp propagation on WL according to lumped RC model.

#### 3.2.3 Comparison

Comparison of the calculated read access times shows a clear speed advantage of the constant gate bias scheme. Especially when using a 2T flash cell type with low voltage select transistor, this biasing reduces the speed limitation of the WL-path to a minimum and read speed becomes determined by the BL precharge and sensing speed. Stepped gate approaches suffer from significant time penalty due to their need of multiple precharge phases. They benefit from better cell biasing, but their total sensing time remains high. A good compromise between both is given with the ramped gate system, which merges all sensing phases into a long one, eliminating the required wait time of all intermediate precharge phases. The sensing operations are delayed by the slowly rising gate bias. This preserves the better cell biasing conditions and yet allows simultaneous sensing of all cell states. However, both schemes with variable CG voltage have to ensure a proper connection of step voltage generator and ramp generator to the WL-driver. Otherwise they lose additional time during change of the cell bias, which is the major contributor of time overhead here.

## 3.3 Time-Domain Transfer Characteristic

To compare all three biasing schemes with respect to their sensing robustness with MLC operation, a common sensing method has to be selected. The ramped gate biasing scheme requires to use a timing-based concept. Therefore a time-domain

Figure 3.11: Basic principle of the analyzed time-domain voltage sensing.

voltage sensing approach as used in [53, 21] is taken for assessment (see Fig. 2.8).

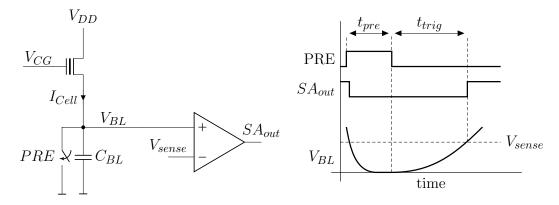

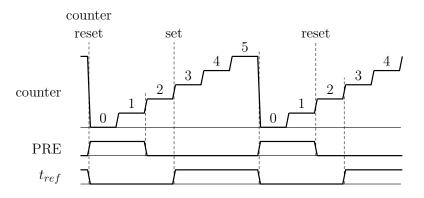

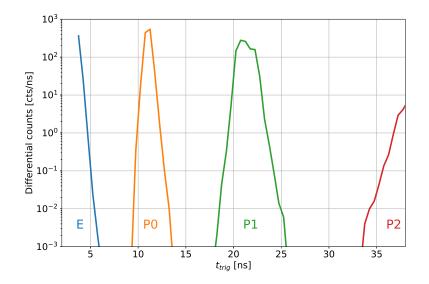

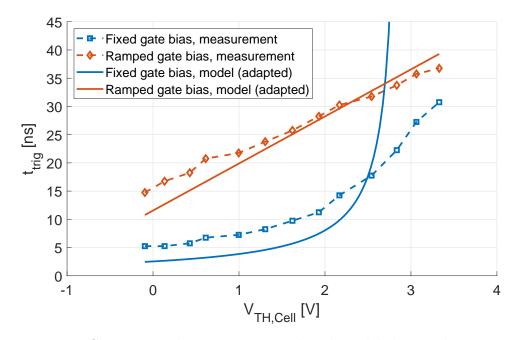

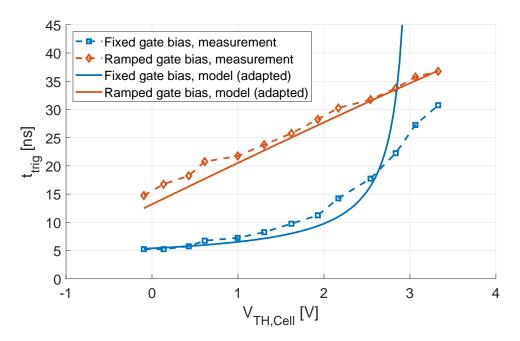

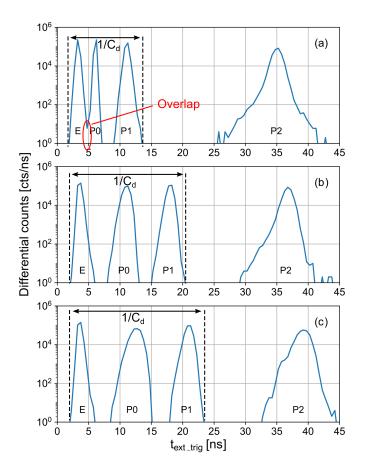

Figure 3.11 depicts the principle of the cell current to time conversion, which establishes the basis of the analyzed sensing scheme. At the beginning of each read operation the bitline is discharged to  $V_{SS}$ . The actual sensing is started by disabling the discharge switch, and the cell current  $I_{Cell}$  accumulates charge on the bitline capacitance  $C_{BL}$ . As soon as the bitline voltage  $V_{BL}$  reaches the reference level  $V_{sense}$ , the sense amplifier output  $SA_{out}$  flips from low to high and the sense operation is completed. The time elapsed between the start of integration and the trigger event shall be defined as trigger time  $t_{trig}$ .

As evaluation criterion for the sensing robustness of all three biasing approaches, the transfer characteristic from cell threshold  $V_{TH,Cell}$  to trigger time  $t_{trig}$  (time-domain transfer characteristic) is derived in the following. The calculations are done for two different CG stimuli: a constant voltage bias (fixed gate biasing) and a linear voltage ramp (ramped gate biasing). For assessment of the robustness obtained by stepped gate biasing, the characteristic of fixed gate biasing can be taken three times, each with a different bias level  $V_{CG,read}$ . This section includes only the initial assumptions of the derivation, the important steps for solving of the problem and the final result. A detailed description of the derivation can be found in Appendix A.

With the assumption of no current flowing into the sense amplifier's input terminals, the transient behavior of the bitline voltage during sensing phase is described by the differential equation

$$\frac{dV_{BL}}{dt} = \frac{I_{Cell}(t)}{C_{BL}}.$$

(3.12)

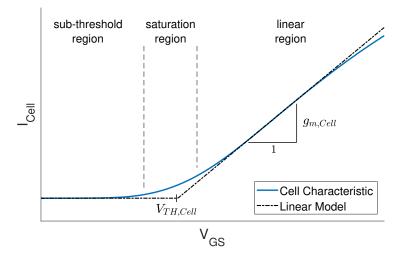

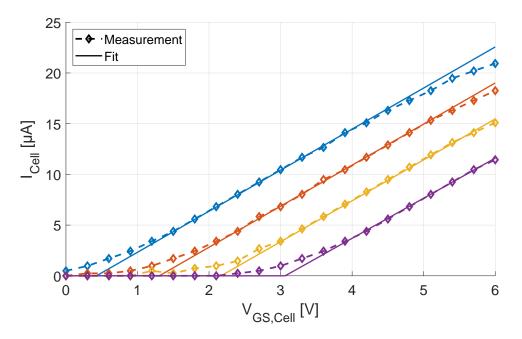

In order to relate  $V_{TH,Cell}$  with  $V_{BL}$ , the I-V-characteristic of the flash cell is needed. Advanced eFlash cell types usually are operated with low drain-source

Figure 3.12: Simple model for the I-V-characteristic of a flash cell with low drainsource bias.

bias voltage in read operation [45]. Hence the CG voltage range of their saturation region is very small and a simple piecewise linear model can sufficiently describe the I-V-characteristic of the flash cell. As shown in Fig. 3.12, it is described by the following equations:

$$I_{Cell}(V_{CG}) = \begin{cases} (V_{CG} - V_{BL} - V_{TH,Cell}) \cdot g_{m,Cell} & \text{for } V_{CG} - V_{BL} \ge V_{TH,Cell} \\ 0 & \text{for } V_{CG} - V_{BL} \le V_{TH,Cell} \end{cases}$$

(3.13)

Combining (3.12) with the cell current in the conducting case yields the first-order linear differential equation

$$\frac{dV_{BL}}{dt} = \alpha \left( V_{CG}(t) - V_{BL}(t) - V_{TH,Cell} \right) \quad \text{with} \quad \alpha = \frac{g_{m,Cell}}{C_{BL}}.$$

(3.14)

Without knowledge of the particular waveform of  $V_{CG}(t)$ , (3.14) can be solved for  $V_{BL}(t)$  resulting in

$$V_{BL}(t) = e^{-\alpha t} \int \alpha e^{\alpha t} \left( V_{CG}(t) - V_{TH,Cell} \right) dt + c_1 e^{-\alpha t}.$$

(3.15)

Further analysis requires the integral to be solved for both input stimuli.

#### 3.3.1 Fixed Gate Biasing

For a constant control gate biasing,  $V_{CG}(t)$  simply is replaced by  $V_{CG,read}$ . With the boundary condition  $V_{BL}(t=0) = 0$ , (3.15) can then be solved as

$$V_{BL}(t) = (V_{CG,read} - V_{TH,Cell}) \cdot (1 - e^{-\alpha t}).$$

(3.16)

Evaluating (3.16) for  $V_{BL}(t_{trig}) = V_{sense}$  finally results the transfer function that connects the cell threshold voltage  $V_{TH,Cell}$  and the trigger time  $t_{trig}$

$$t_{trig}(V_{TH,Cell}) = -\frac{1}{\alpha} \cdot \ln\left(1 - \frac{V_{sense}}{V_{CG,read} - V_{TH,Cell}}\right).$$

(3.17)

It only yields a valid result if the logarithm's argument becomes positive. This is reasonable, since a threshold voltage, which is too close to the read bias  $V_{CG,read}$ , does not deliver a cell current and thus would theoretically never cause a trigger event. Cell thresholds above the read bias result in negative trigger times having no causal relation. (3.17) describes the transfer characteristic for constant CG bias within the range of  $-\infty < V_{TH,Cell} < V_{CG,read} - V_{sense}$ .

#### 3.3.2 Ramped Gate Biasing

For the second scenario, a dynamic linear voltage ramp is applied to the control gate. Defining the start of the integration as t = 0, a voltage ramp with slope m, starting at  $V_{CG}(0) = 0$  can be described by  $V_{CG}(t) = m \cdot t$ . Inserted in (3.15), the BL voltage is then be solved as

$$V_{BL}(t) = c_1 e^{-\alpha t} + m \cdot t - \left(V_{TH} + \frac{m}{\alpha}\right).$$

(3.18)

In order to eliminate coefficient  $c_1$ , again, the boundary conditions have to be considered. Since the control gate voltage now changes dynamically, the conditions are more complex. Two cases leading to different boundary conditions can be distinguished:

#### Case I

The cell's threshold voltage is below the initial control gate voltage and the cell current flows immediately:

$$V_{TH,Cell} < V_{CG}(0) \implies V_{BL}(t=0) = 0.$$

(3.19)

Then, the bitline voltage starts at zero and rises continuously in the integration phase. Using this boundary condition, (3.18) yields the constant  $c_1 = \frac{m}{\alpha} + V_{TH,Cell}$  and thus results in

$$V_{BL}(t) = \left(\frac{m}{\alpha} + V_{TH,Cell}\right) \cdot \left(e^{-\alpha t} - 1\right) + m \cdot t \tag{3.20}$$

for the bitline voltage curve.

#### Case II

The cell's threshold voltage is above the initial control gate voltage and the cell current starts flowing only after the voltage ramp crosses the threshold voltage

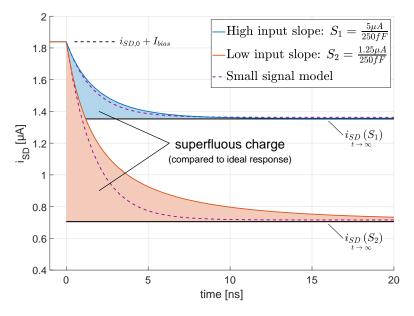

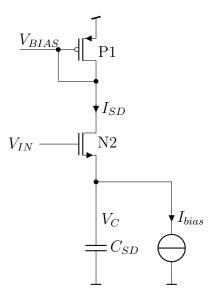

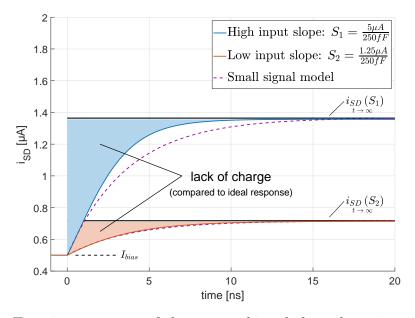

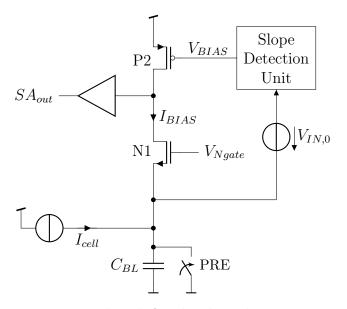

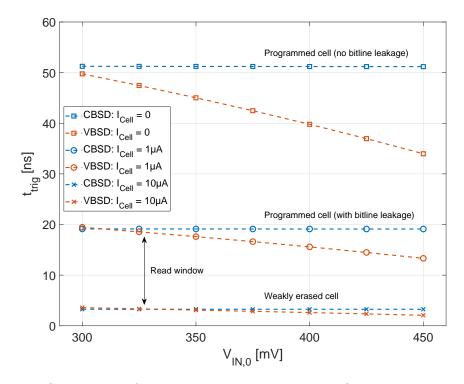

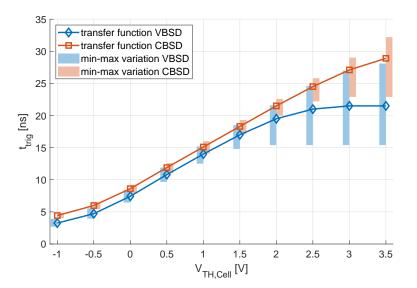

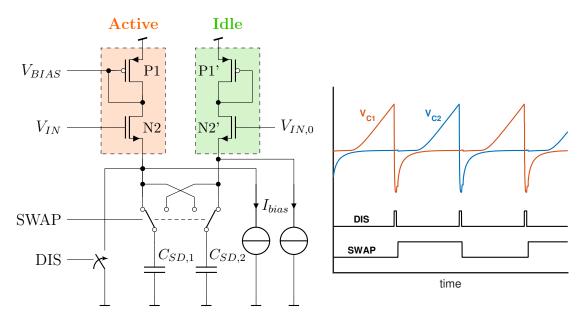

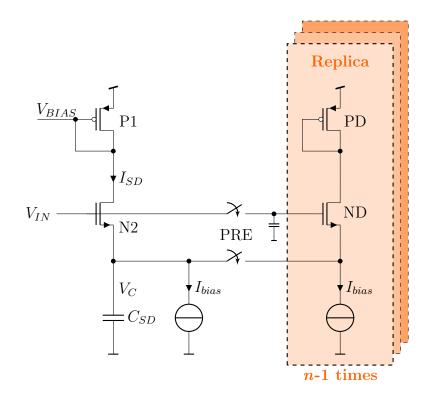

$$V_{TH,Cell} \ge V_{CG}(0) \implies V_{BL}(t \le t_0) = 0$$