Fakultät für Informatik der Technischen Universität München

Lehrstuhl für Sicherheit in der Informatik

# Leveraging Logical and Physical Separation for Mobile Security

Julian Maxim Horsch

Dissertation

## Fakultät für Informatik der Technischen Universität München

# Lehrstuhl für Sicherheit in der Informatik

# Leveraging Logical and Physical Separation for Mobile Security

Julian Maxim Horsch

Vollständiger Abdruck der von der Fakultät für Informatik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender:Prof. Dr.-Ing. Jörg OttPrüfer der Dissertation:1. Prof. Dr. Claudia Eckert2. Prof. Dr. Uwe Baumgarten

Die Dissertation wurde am 02.04.2019 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 25.07.2019 angenommen.

### Abstract

The importance of mobile computing and the number of mobile computing devices have both grown strongly over the recent years. Mobile devices, such as smartphones, laptops, tablets, and also wearables, show an interesting combination of traits. They are, as the name suggests, mobile, massively connected, gather valuable data with various sensors, and can typically be customized with apps. Together, those characteristics make mobile devices very popular among users and a prime attack target. More specifically, their mobility exposes mobile devices to a variety of, possibly hostile, environments, putting them at risk of loss and, thus, physical attacks. Their connectivity exposes them to numerous remote attacks via one of their various wireless interfaces. In reaction to this increasing threat potential, mobile devices and their CPUs gain more and more security functions. While some of those functions fulfill a very specific purpose, such as the secure boot, guaranteeing the integrity of the boot chain, others are very versatile and not fixed to a specific use case. This especially includes new functions for *logical separation*, such as Trusted Execution Environments (TEEs) and hardware-assisted virtualization, providing multiple isolated execution contexts inside the same CPU core. Logical separation enables novel, powerful security concepts, but can be overcome, for example, by cache timing attacks, raising the need for additional physical separation to protect high-value secrets.

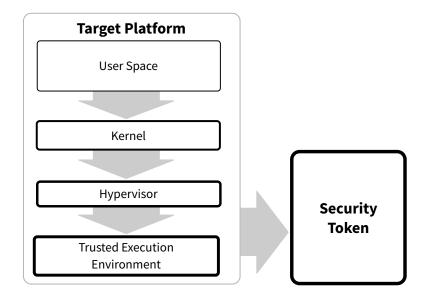

In this work, we explore ways to leverage both logical and physical separation to improve a mobile device's confidentiality and integrity against remote and physical attackers. We define a system architecture consisting of the mobile *target platform* and a physically separated *security token*, connected to the target platform, storing high-value secrets. In order to enable the token to protect itself and its assets against a compromised target platform, we first propose a software-based trusted boot process for ARM application processors. Using a timing-based primitive for externally verifiable execution, this boot process allows the token to gain trust in the boot integrity of the target platform without relying on pre-shared or trusted key material, building the basis for all following tokenbased security concepts.

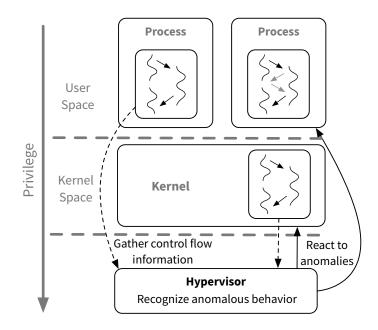

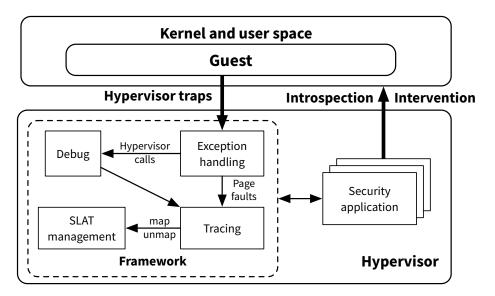

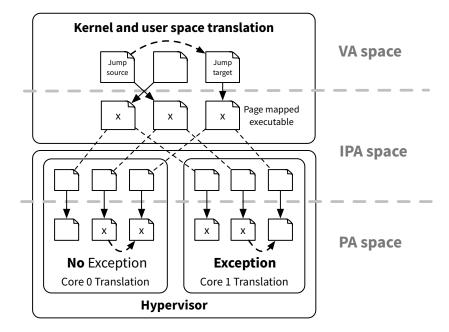

A remote attacker typically tries to exploit a vulnerability to take control over a process communicating via one of the target platform's interfaces. In order to detect and eventually prevent such remote attacks, we present a framework for transparent kernel and user space execution tracing from a minimal hypervisor. The framework leverages hardware-assisted virtualization in modern ARM CPUs to transparently restrict the target platform to a small set of executable memory pages, gathering control flow information on each resulting page fault in the hypervisor. The page-granular control flow data can be used as basis to detect and prevent control flow hijacking attacks and, thus, protect the target platform's run-time integrity.

Run-time integrity does not necessarily protect a system against physical attacks. A physical attacker might, for example, still be able to extract valuable data from the main memory of a system via DMA or cold boot attacks. In order to protect a target platform

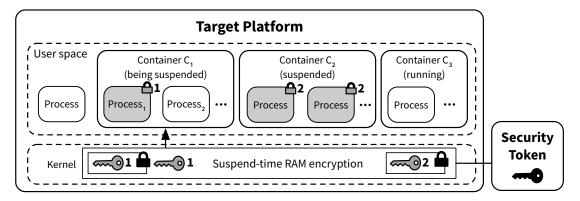

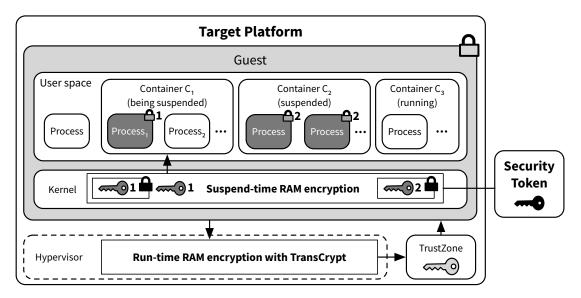

against such memory attacks, we present a concept for run-time kernel and user space main memory encryption from a minimal hypervisor. Like our execution tracing framework, our memory encryption scheme leverages hardware-assisted virtualization to transparently restrict the system to a small working set of recently accessed pages. By encrypting other pages, using a key stored in a TEE, our concept is able to effectively protect a running system against memory attacks. To provide stronger protection against attacks breaking logical separation, we furthermore propose the combination with a suspend-time memory encryption scheme, able to encrypt suspended processes with keys stored securely in the security token. Finally, to put our software-based encryption schemes into perspective, we present an attack on AMD Secure Encrypted Virtualization (SEV), a hardware-based memory encryption mechanism in recent AMD CPUs.

Recent years have shown that logical separation, even when provided by TEEs, can be broken by advanced attackers in various ways. Apart from exploiting software bugs, attackers can perform microarchitectural attacks, for example, using cache timing, to extract secrets, even from bug-free, logically separated contexts. In order to protect valuable symmetric keys, such as the target platform's Full Disk Encryption (FDE) key, against such attacks, we present a concept that leverages physical separation and partially moves the required cryptographic operations to our token, in a way fast enough for dataintensive applications. Our concept forces the target platform and token to cooperate during data encryption and decryption and binds encrypted data to the specific token used for its encryption. In order to protect user identities against advanced attackers, we propose a concept for deriving and using IDs in form of asymmetric key pairs, storing them securely on our physically separated token. Our concept is able to securely derive trusted IDs from a RootID device into the token, even when a completely compromised target platform brokers their communication with each other and the user.

We show the feasibility of all our concepts by presenting prototype implementations. Our performance and security evaluations confirm that our concepts are able to effectively and efficiently improve a mobile device's integrity and confidentiality against different remote and physical attackers.

### Zusammenfassung

Die Wichtigkeit und Verbreitung mobiler Computernutzung hat in den vergangenen Jahren stark zugenommen. Die dabei verwendeten mobilen Geräte sind tragbar, besitzen eine große Anzahl zumeist drahtloser Kommunikationsschnittstellen und Sensoren und sind durch benutzerdefinierte Software flexibel einsetzbar. Diese Eigenschaften machen mobile Geräte höchst populär und zu einem bevorzugten Ziel für Angriffe. Aufgrund ihrer Mobilität sind die Geräte oft wechselnden Umgebungen und erhöhter Verlust- bzw. Diebstahlgefahr und damit physischen Angriffen ausgesetzt. Durch ihre hohe Konnektivität sind die Geräte zudem von einer Vielzahl an entfernten Angriffen bedroht. Als Reaktion auf diese Entwicklung werden die Geräte zunehmend mit neuen Sicherheitsfunktionen ausgestattet. Während einige dieser Funktionen einem ganz bestimmten Zweck dienen, wie zum Beispiel der sichere Bootprozess, der die Integrität von Boot-Komponenten sicherstellt, sind andere sehr flexibel einsetzbar. Hierzu zählen insbesondere neue Funktionen zur logischen Separierung, d.h. zur Unterteilung des CPU-Kerns in mehrere isolierte Ausführungsumgebungen. Logische Separierung, zum Beispiel durch Trusted Execution Environments (TEEs) oder Hardwarevirtualisierung, ermöglicht die Umsetzung neuartiger und mächtiger Sicherheitskonzepte, kann allerdings unter bestimmten Umständen von starken Angreifern umgangen werden. Zum Schutz von wertvollen Daten ist daher eine zusätzliche physische Separierung sinnvoll.

In dieser Arbeit erforschen wir die Nutzung logischer und physischer Separierung zum Schutz der Integrität und Vertraulichkeit mobiler Geräte gegen physische und entfernte Angreifer. Wir definieren zunächst eine Systemarchitektur bestehend aus einer mobilen *Zielplattform* und einem verbundenen, jedoch eigenständigen *Sicherheitstoken* für die Speicherung von Geheimnissen. Zum Schutz des Tokens vor einer kompromittierten Zielplattform stellen wir das Konzept eines softwarebasierten vertrauenswürdigen Bootprozesses für ARM Anwendungsprozessoren vor. Ohne zuvor geteiltes Schlüsselmaterial schafft der Bootprozess mittels eines zeitbasierten Verfahrens ein initiales Vertrauen des Tokens in die Integrität der auf der Zielplattform geladenen Komponenten und damit die Basis für weitere Token-basierte Konzepte.

Entfernte Angriffe nutzen typischerweise Sicherheitslücken in nach außen kommunizierenden Prozessen, um deren Kontrollfluss zu übernehmen. Um solche Angriffe zu erkennen und letztlich zu verhindern, stellen wir ein Framework zur transparenten Überwachung der Programm- und Kernelausführung aus einem minimalen Hypervisor vor. Das Framework nutzt hardwareunterstützte Virtualisierungsfunktionen, um die Zielplattform auf eine kleine Menge an ausführbaren Speicherseiten zu beschränken. Die Fehler, die beim Ausführen von Seiten außerhalb dieser Menge entstehen, werden vom Hypervisor abgefangen und zur Gewinnung von seitengranularen Kontrollflussinformationen genutzt. Diese können wiederum als Basis für die Verhinderung von Angriffen und daher dem Schutz der Laufzeitintegrität der Zielplattform dienen.

Ein laufzeitintegres System ist nicht notwendigerweise gegen physische Angriffe geschützt. Ein physischer Angreifer ist, zum Beispiel, möglicherweise weiterhin in der Lage mittels einer Kaltstart- oder DMA-Attacke Daten aus dem Hauptspeicher zu entwenden. Zum Schutz gegen solche Speicherangriffe stellen wir ein Konzept für Hauptspeicherverschlüsselung zur Laufzeit aus einem minimalen Hypervisor vor. Das Konzept nutzt, ebenso wie unser Framework zur Ausführungsüberwachung, Funktionen der hardwarebasierten Virtualisierung, um die Zielplattform transparent auf eine kleine Menge zuletzt zugegriffener Seiten zu beschränken. Durch die Verschlüsselung von Seiten außerhalb dieser Menge mit einem durch eine TEE geschützten Schlüssel, schützt unser Konzept laufende Systeme effektiv gegen Speicherangriffe. Zum Schutz vor Angriffen auf die dabei genutzte logische Separierung präsentieren wir darüber hinaus die Kombination mit einem unterbrechungsbasierten Konzept zur Speicherverschlüsselung, welches ergänzend in der Lage ist, temporär unterbrochene Prozesse mit Token-geschützten Schlüsseln zu verschlüsseln. Zur Einordnung unserer softwarebasierten Konzepte in einen größeren Kontext präsentieren wir zum Abschluss einen Angriff auf AMD Secure Encrypted Virtualization (SEV), einen hardwarebasierten Mechanismus zur Speicherverschlüsselung.

Die vergangenen Jahre haben eine Vielzahl von Angriffen hervorgebracht, die sogar von TEEs bereitgestellte logische Separierung erfolgreich umgehen. Neben Angriffen, die Softwarebugs ausnutzen, sind insbesondere mikroarchitekturelle Angriffe in der Lage, Geheimnisse aus separierten Kontexten zu entwenden ohne dabei auf Implementierungsfehler angewiesen zu sein. Zum Schutz wichtiger symmetrischer Schlüssel der Zielplattform vor ebendiesen Angriffen, zum Beispiel für die Festplattenverschlüsselung, präsentieren wir ein Konzept, welches die auszuführenden kryptographischen Operationen teilweise auf das physisch separierte Token verlagert, ohne dabei zuviel Geschwindigkeit einzubüßen. Unser Konzept zwingt die Zielplattform und das Token zur Zusammenarbeit während Ver- und Entschlüsselung und verknüpft die verschlüsselten Daten untrennbar mit dem spezifischen Token, das zur Verschlüsselung genutzt wurde. Zum Schutz von Nutzeridentitäten präsentieren wir ein Konzept zur Ableitung und Verwendung von IDs basierend auf asymmetrischen Schlüsseln. Unser Konzept ist in der Lage, vertrauenswürdige IDs von einem RootID-Gerät abzuleiten und diese sogar dann sicher im Token abzulegen, wenn die Zielplattform, welche die Verbindung zwischen beiden Geräten und dem Nutzer herstellt, kompromittiert ist.

Die praktische Umsetzbarkeit unserer Sicherheitskonzepte zeigen wir mit prototypischen Implementierungen. Unsere Geschwindigkeits- und Sicherheitsevaluationen bestätigen darüber hinaus, dass unsere Konzepte in der Lage sind, die Integrität und Vertraulichkeit mobiler Geräte effektiv und effizient zu verbessern.

## Acknowledgements

First of all, I would like to thank Prof. Dr. Claudia Eckert for giving me the opportunity to pursue a doctoral degree in a field as fascinating and challenging as IT security. Her guidance and supervision, as well as her constant support and encouragement have been a great help in writing this thesis.

I would also like to thank Prof. Dr. Uwe Baumgarten for his interest in my work and for being the second examiner of this thesis.

Further, I would like to thank all current and former colleagues at Fraunhofer AISEC for inspiring discussions, trusting companionship, and support in major and minor questions. In particular, I would like to thank Dr. Michael Velten, Manuel Huber, Sascha Wessel, Dr. Steffen Wagner, Dr. Michael Weiß, Philipp Zieris, Dieter Schuster, Mathias Morbitzer, Konstantin Böttinger, and Dr. Frederic Stumpf.

Almost last but certainly not least, I would like to thank my family, extended family, and friends for their unconditional love and support and for always putting things into greater perspective.

Finally, I would like to thank Lisa, my partner and best friend, for her patience, wisdom, and strength, her constant encouragement, unwavering confidence in my abilities, and for, literally and figuratively, traveling with me on this journey.

# Contents

| Lis | List of Figures xi |         |                                       |      |  |

|-----|--------------------|---------|---------------------------------------|------|--|

| Lis | .ist of Tables xv  |         |                                       |      |  |

| Lis | t of L             | istings |                                       | xvii |  |

| 1   | Intro              | oductio | n                                     | 1    |  |

|     | 1.1                | Resear  | ch Questions                          | 5    |  |

|     | 1.2                | Contri  | butions                               | 6    |  |

|     | 1.3                | Publica | ations                                | 9    |  |

|     | 1.4                | Outlin  | e                                     | 11   |  |

| 2   | Back               | ground  | I                                     | 13   |  |

|     | 2.1                | ARM A   | architecture                          | 13   |  |

|     |                    | 2.1.1   | Execution States and Instruction Sets | 15   |  |

|     |                    | 2.1.2   | Privilege and Exception Model         | 15   |  |

|     |                    | 2.1.3   | Memory Model                          | 17   |  |

|     | 2.2                | Virtual | ization                               | 19   |  |

|     |                    | 2.2.1   | Forms of Virtualization               | 19   |  |

|     |                    | 2.2.2   | Hardware-assisted Virtualization      | 21   |  |

|     |                    | 2.2.3   | AMD SEV and SME                       | 23   |  |

|     | 2.3                | Truste  | d Execution Environments              | 24   |  |

|     |                    | 2.3.1   | ARM TrustZone                         | 26   |  |

|     |                    | 2.3.2   | Intel SGX                             |      |  |

|     | 2.4                | Boot Iı | ntegrity and Attestation              | 30   |  |

|     |                    | 2.4.1   | Secure Boot                           | 30   |  |

|     |                    | 2.4.2   | Measured Boot                         | 31   |  |

| 3   | Syst               |         | nitecture                             | 33   |  |

|     | 3.1                | Target  | Platform                              | 33   |  |

## CONTENTS

|   | 3.2  | Securi   | ty Token                               | 36 |

|---|------|----------|----------------------------------------|----|

|   | 3.3  | Generi   | c Attacker Model                       | 37 |

|   | 3.4  | Summ     | ary                                    | 40 |

| 4 | Esta | blishing | g Trusted Boot-time Integrity          | 41 |

|   | 4.1  | -        | are-based Trusted Boot                 | 42 |

|   | 4.2  |          | er Model and Assumptions               | 43 |

|   | 4.3  |          | d Work                                 | 44 |

|   | 4.4  |          | are-based Trust Anchor                 | 45 |

|   |      | 4.4.1    | Hardware Architecture                  |    |

|   |      | 4.4.2    | Software Architecture and Protocol     | 46 |

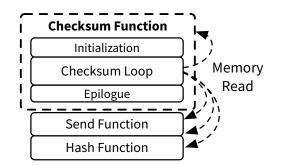

|   |      | 4.4.3    | Checksum Function Design               | 47 |

|   | 4.5  | Cortex   | -A8 Checksum Function                  | 49 |

|   |      | 4.5.1    | Hardware Characteristics               | 50 |

|   |      | 4.5.2    | Hardware Initialization                | 50 |

|   |      | 4.5.3    | Basic Algorithm                        | 51 |

|   |      | 4.5.4    | Main Loop Implementation               | 52 |

|   | 4.6  | Except   | ion Protection                         | 55 |

|   |      | 4.6.1    | ARM Exception Handling                 | 56 |

|   |      | 4.6.2    | Uninterruptible Execution Environment  | 57 |

|   |      | 4.6.3    | Protection during Checksum Calculation | 59 |

|   | 4.7  | Prototy  | уре                                    | 60 |

|   | 4.8  | -        | mental Results                         |    |

|   | 4.9  | Summ     | ary                                    | 63 |

| 5 | Mon  | itoring  | and Protecting Run-time Integrity      | 65 |

|   | 5.1  | -        | er Model and Attacks on Control Flow   | 67 |

|   | 5.2  | Relate   | d Work                                 | 68 |

|   | 5.3  | Hyperv   | visor-based Monitoring Framework       | 70 |

|   |      | 5.3.1    | Hardware Requirements                  | 70 |

|   |      | 5.3.2    | Architecture                           | 71 |

|   |      | 5.3.3    | Initialization                         | 72 |

|   |      | 5.3.4    | Tracing Mechanism                      | 73 |

|   |      | 5.3.5    | Multi-core Tracing                     | 73 |

|   |      | 5.3.6    | Write XOR Execute Protection           | 75 |

|   | 5.4  | Frame    | work-provided Data                     | 76 |

|   | 5.5  | Frame    | work Applications                      | 78 |

|   | 5.6  | Implen   | nentation                              | 80 |

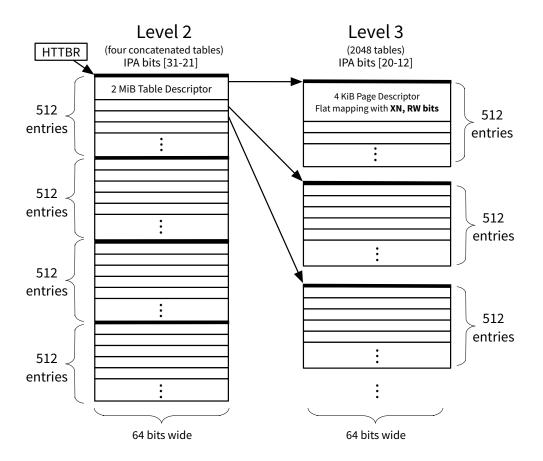

|   |      | 5.6.1    | Memory Management                      | 80 |

|   |      | 5.6.2    | Tracing Framework Implementation       | 82 |

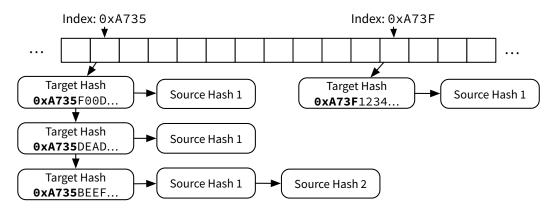

|   | 5.7  | Page H   | Iash-based CF Protection               | 82 |

|   |      |          |                                        |    |

х

|   |            | 5.7.1          | Jump Table Generation                         | 83  |

|---|------------|----------------|-----------------------------------------------|-----|

|   |            | 5.7.2          | Implementation                                | 84  |

|   |            | 5.7.3          | Discussion                                    | 84  |

|   | 5.8        | Perfor         | mance Evaluation                              | 85  |

|   |            | 5.8.1          | Linux and Android Boot Time                   | 86  |

|   |            | 5.8.2          | CoreMark Benchmark                            | 89  |

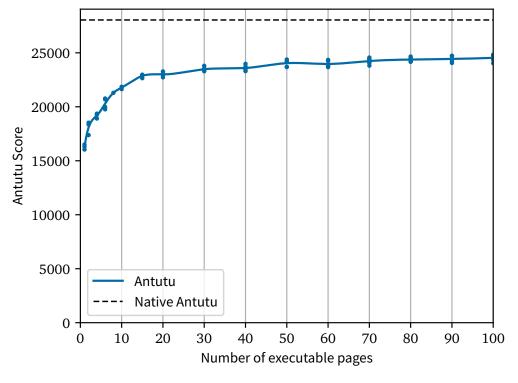

|   |            | 5.8.3          | Antutu Benchmark                              | 90  |

|   |            | 5.8.4          | Discussion                                    | 91  |

|   | 5.9        | Summ           | ary                                           | 92  |

|   |            |                |                                               |     |

| 6 |            | -              | Main Memory Confidentiality                   | 93  |

|   | 6.1        |                | ter Model and Memory Attacks                  |     |

|   | 6.2        |                | d Work                                        |     |

|   | 6.3        |                | Crypt: Run-time Main Memory Encryption        |     |

|   |            | 6.3.1          | Hardware Requirements                         |     |

|   |            | 6.3.2          | Architecture                                  |     |

|   |            | 6.3.3          | Definitions and Initialization                |     |

|   |            | 6.3.4          | Basic Mechanism                               |     |

|   |            | 6.3.5          | Page Encryption                               |     |

|   |            | 6.3.6          | Unencrypted Page Set Size                     |     |

|   |            | 6.3.7          | Multi-core Design                             |     |

|   |            | 6.3.8          | Special Pages                                 |     |

|   | 6.4        |                | Crypt: Implementation                         |     |

|   |            | 6.4.1          | Initialization                                |     |

|   |            | 6.4.2          | Basic Mechanism                               |     |

|   | < <b>-</b> | 6.4.3          | Special Page Detection                        |     |

|   | 6.5        |                | Crypt: Evaluation                             |     |

|   |            | 6.5.1          | Security                                      |     |

|   |            | 6.5.2          | Performance                                   |     |

|   | ~ ~        | 6.5.3          | Discussion                                    |     |

|   | 6.6        | -              | nd-time Main Memory Encryption                |     |

|   |            | 6.6.1          | Architecture and Encryption Concept           |     |

|   |            | 6.6.2<br>6.6.3 | Implementation and Performance                |     |

|   |            |                | Combination with TransCrypt                   |     |

|   | 67         | 6.6.4          | Security Discussion                           |     |

|   | 6.7        | 5Evere 6.7.1   | ed: An Attack on Hardware-based VM Encryption |     |

|   |            | 6.7.1          | Evaluation                                    |     |

|   |            | 6.7.2<br>6.7.3 | Discussion and Countermeasures                |     |

|   | 6.8        |                | Discussion and Countermeasures                |     |

|   | 0.0        | Summ           | iar y                                         | 129 |

### CONTENTS

| 7  | Protecting Keys and Identities |         |                                                | 131 |  |

|----|--------------------------------|---------|------------------------------------------------|-----|--|

|    | 7.1                            | Attack  | er Model                                       |     |  |

|    | 7.2                            | CoKey   | r: Fast Token-based Symmetric Cryptography     |     |  |

|    |                                | 7.2.1   | Related Work                                   |     |  |

|    |                                | 7.2.2   | Architecture and Design                        |     |  |

|    |                                | 7.2.3   | Implementation                                 |     |  |

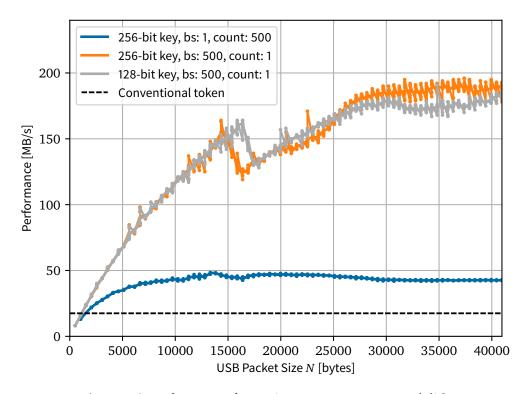

|    |                                | 7.2.4   | Performance Evaluation                         |     |  |

|    |                                | 7.2.5   | Security Discussion                            |     |  |

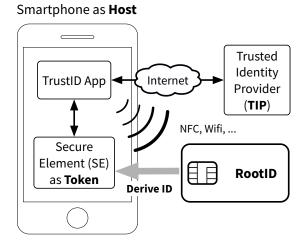

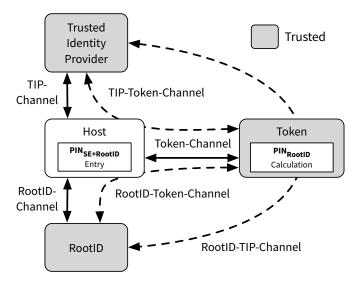

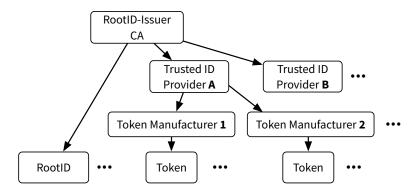

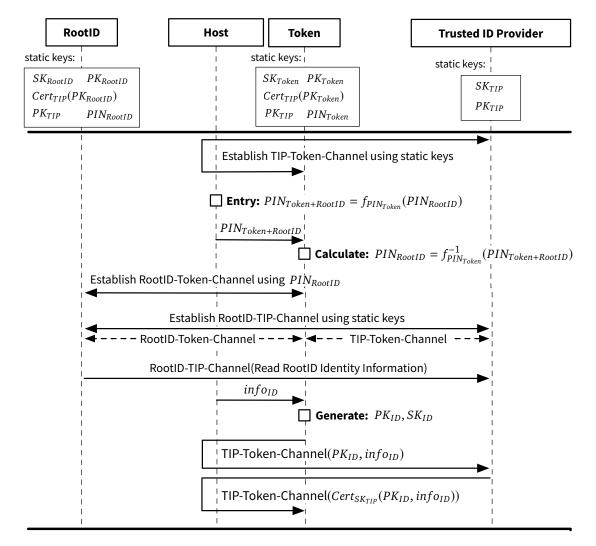

|    | 7.3                            | TrustI  | D: Token-based Identity Derivation and Storage |     |  |

|    |                                | 7.3.1   | Related Work                                   |     |  |

|    |                                | 7.3.2   | Architecture                                   |     |  |

|    |                                | 7.3.3   | Protocol Prerequisites                         |     |  |

|    |                                | 7.3.4   | Protocol                                       |     |  |

|    |                                | 7.3.5   | ID Usage                                       |     |  |

|    |                                | 7.3.6   | Implementation                                 |     |  |

|    |                                | 7.3.7   | Security Discussion                            |     |  |

|    | 7.4                            | Summ    | ary                                            | 164 |  |

| 8  | Con                            | clusion |                                                | 165 |  |

|    | 8.1                            | Contri  | butions                                        |     |  |

|    | 8.2                            | Future  | e Research Directions                          |     |  |

| Ac | Acronyms                       |         |                                                |     |  |

| Bi | bliogi                         | raphy   |                                                | 179 |  |

xii

# **List of Figures**

| 1.1 | Logical and physical separation of security-critical components | 6  |

|-----|-----------------------------------------------------------------|----|

| 1.2 | Visual outline of the thesis                                    | 11 |

| 2.1 | Architecture of a typical ARM SoC                               |    |

| 2.2 | Exception and privilege levels of an ARMv8-A CPU                | 16 |

| 2.3 | Exception and privilege levels of an ARMv7-A CPU                | 17 |

| 2.4 | Address translation regimes in an ARMv8.4-A processor           | 18 |

| 2.5 | Different layers of virtualization in a single system           | 20 |

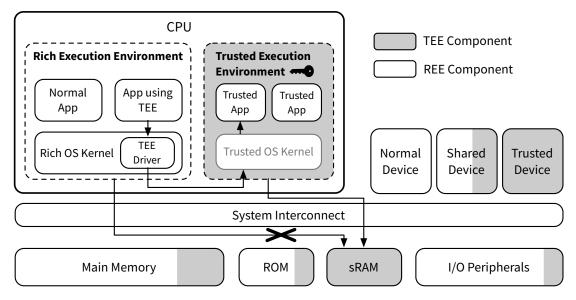

| 2.6 | Typical architecture of a system with TEE                       | 25 |

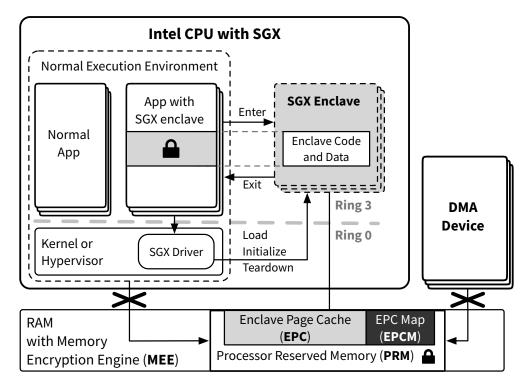

| 2.7 | Architecture of an SGX-enabled Intel system                     | 28 |

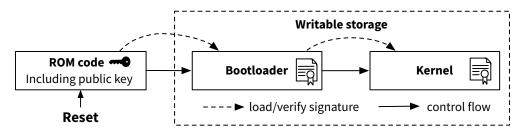

| 2.8 | Basic concept of a secure boot                                  | 30 |

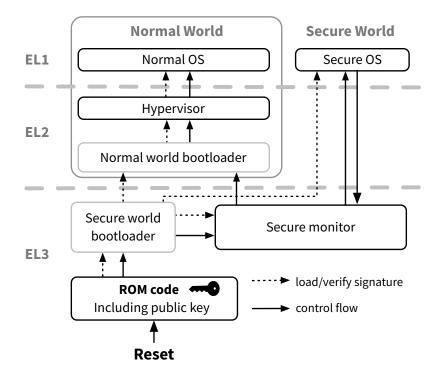

| 2.9 | Typical secure boot on an ARMv8-A CPU                           | 31 |

| 3.1 | Generic system architecture                                     |    |

| 3.2 | Generic attacker model                                          | 38 |

| 4.1 | Software-based trusted boot process                             |    |

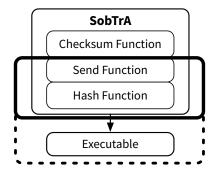

| 4.2 | SobTrA architecture and protocol                                | 46 |

| 4.3 | SobTrA checksum function structure                              | 47 |

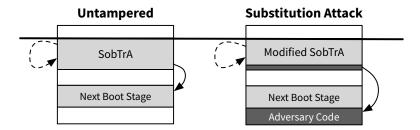

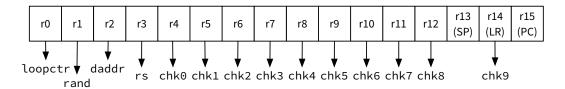

| 4.4 | Substitution attack example                                     | 48 |

| 4.5 | Two types of memory copy attacks                                | 48 |

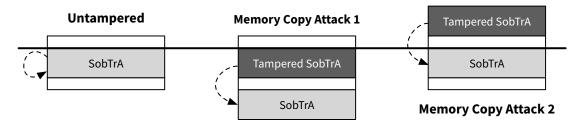

| 4.6 | Register allocation in the SobTrA checksum function             | 53 |

| 4.7 | Uninterruptible SobTrA execution environment                    |    |

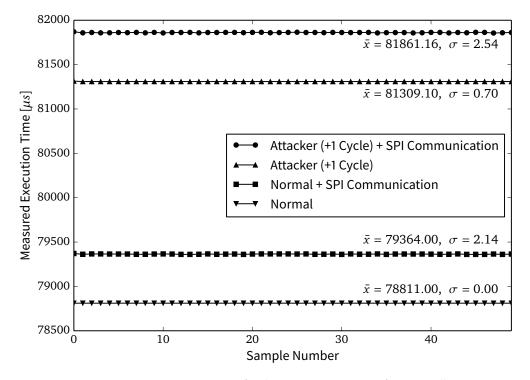

| 4.8 | SobTrA execution time measurements                              | 62 |

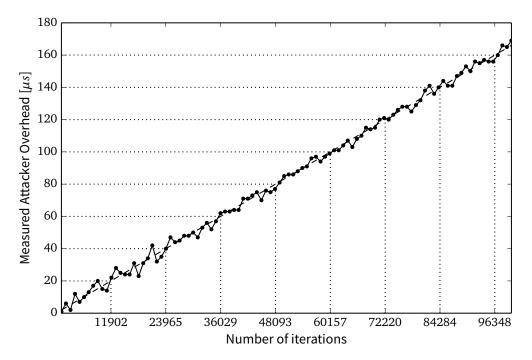

| 4.9 | Measured SobTrA attacker overhead                               | 63 |

| 5.1 | Hypervisor-based control flow integrity protection              |    |

| 5.2 | Basic idea and memory layout of a ROP attack                    |    |

| 5.3 | Monitoring framework architecture                               |    |

| 5.4 | Gathering control flow data in a multi-core system              | 74 |

| 5.5  | PL0/1 Stage 2 translation tables in the prototype implementation | 81  |

|------|------------------------------------------------------------------|-----|

| 5.6  | Jump table data structure                                        | 83  |

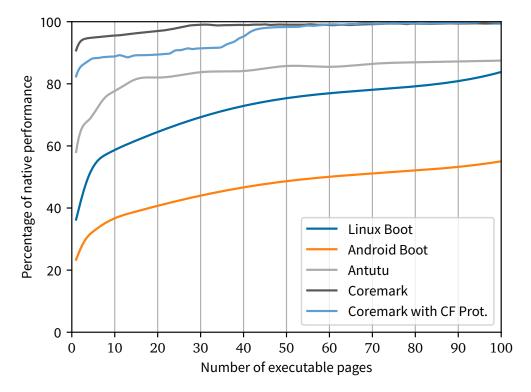

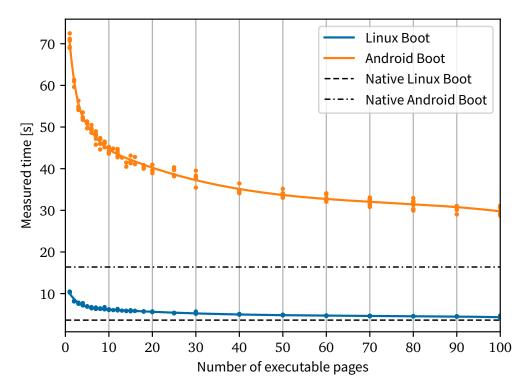

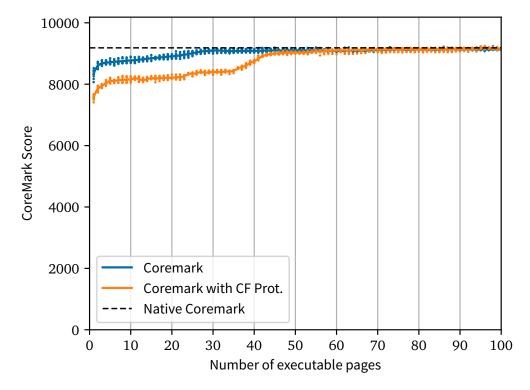

| 5.7  | Tracing framework performance benchmark results                  | 86  |

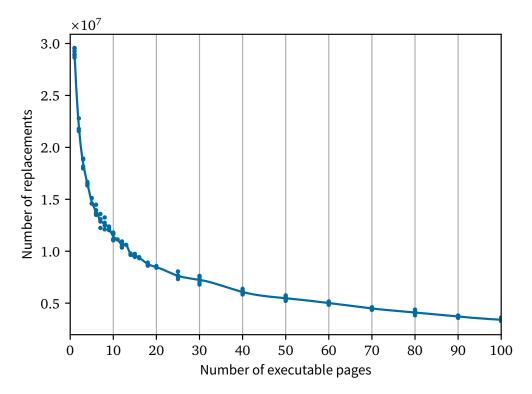

| 5.8  | Linux and Android boot time measurements                         | 87  |

| 5.9  | Executable page replacements during Android boot                 | 88  |

| 5.10 | CoreMark benchmark results                                       | 90  |

| 5.11 | Antutu benchmark results                                         | 91  |

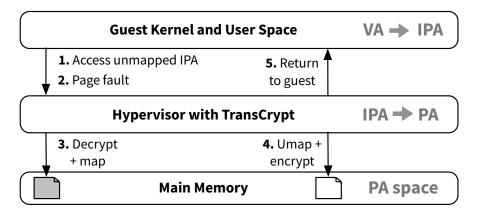

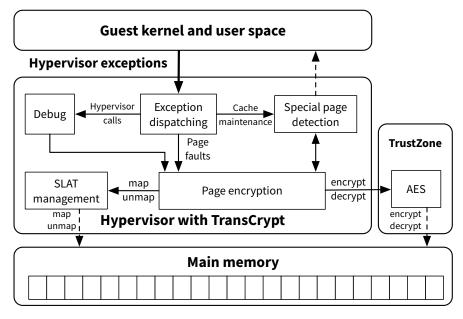

| 6.1  | TransCrypt memory encryption concept                             | 99  |

| 6.2  | Architecture of the TransCrypt hypervisor                        | 100 |

| 6.3  | TransCrypt encryption and translation mechanism                  | 103 |

| 6.4  | Hypervisor-based DMA page detection                              | 108 |

| 6.5  | Architecture of the suspend-time memory encryption system        | 117 |

| 6.6  | Combination of suspend- and run-time memory encryption           | 119 |

| 6.7  | Architecture and mechanism of the SEVered attack                 | 122 |

| 7.1  | CoKey conceptual overview                                        | 135 |

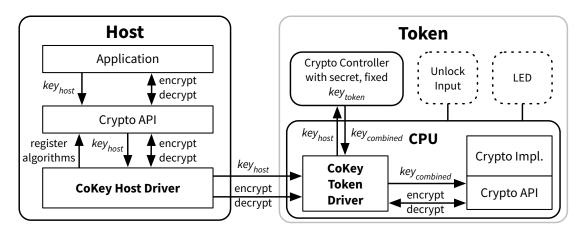

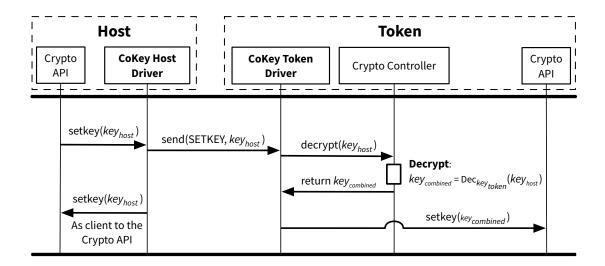

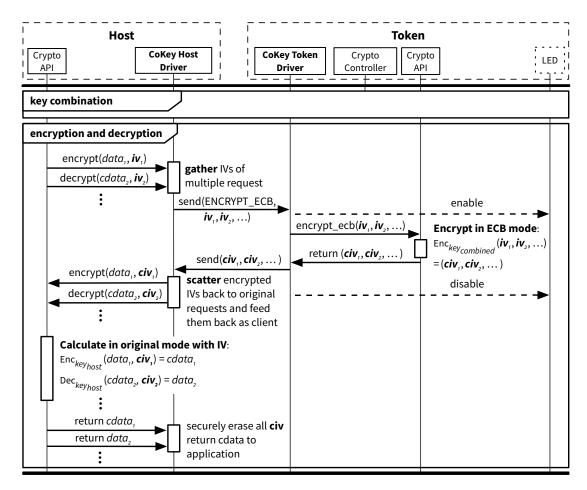

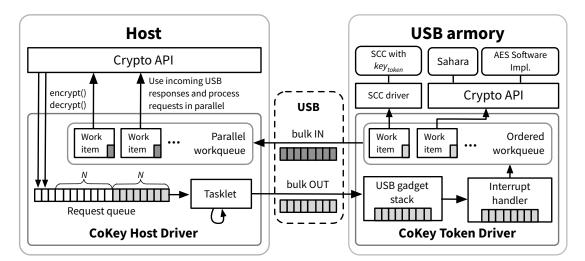

| 7.2  | CoKey architecture                                               | 138 |

| 7.3  | CoKey key combination                                            | 139 |

| 7.4  | CoKey external cryptography                                      | 141 |

| 7.5  | Architecture of the CoKey prototype implementation               | 143 |

| 7.6  | Performance of dd writes on a CoKey-encrypted disk               | 147 |

| 7.7  | TrustID application scenario                                     | 152 |

| 7.8  | TrustID system architecture                                      | 154 |

| 7.9  | TrustID PKI example                                              | 156 |

| 7.10 | TrustID identity derivation protocol                             | 157 |

| 7.11 | Relay attack and TrustID defense                                 | 162 |

# **List of Tables**

| 5.1 | Key figures of the boot process with control flow protection    | . 89  |

|-----|-----------------------------------------------------------------|-------|

| 6.1 | TransCrypt page statistics for Android boot                     | 112   |

| 6.2 | TransCrypt E-mail password encryption statistics                | 113   |

| 6.3 | TransCrypt performance benchmark results                        | 114   |

| 6.4 | SEVered resource identification evaluation results              | 127   |

| 6.5 | SEVered extraction speed                                        | . 128 |

| 7.1 | Comparison of attack potential for CoKey and related approaches | 149   |

# **List of Listings**

| 4.1 | SobTrA checksum function algorithm        | 51  |

|-----|-------------------------------------------|-----|

| 4.2 | SobTrA pseudorandom update implementation | 54  |

| 4.3 | SobTrA data address update implementation | 54  |

| 4.4 | SobTrA checksum update implementation     | 55  |

| 5.1 | Tracing framework exception handlers      | 76  |

| 6.1 | TransCrypt page fault handler             | 106 |

# Introduction

In recent years, mobile computing has become ubiquitous. Personal mobile computing devices, such as smartphones, laptops and tablets are heavily used<sup>1</sup> by an already vast and ever-increasing number of people<sup>2</sup>. Furthermore, the trend towards the Internet of Things (IoT) causes also mobile everyday objects to gain more and more computing and communication capabilities<sup>3</sup>. This results in a huge number of additional mobile devices, including small, personal ones, such as smartwatches and other wearables, but also larger, safety-critical devices like intelligent cars. A slow-down of the mobile computing growth is not to be expected<sup>4</sup>.

While some mobile devices, such as laptops, resemble traditional PCs, most mobile devices are, by definition, *embedded devices* in the sense that they are highly integrated, combining computing components with peripherals and mechanical components to fulfill a specific function. Depending on the actual use case, embedded devices are typically driven by low-performance *microcontrollers* or high-performance *Systems on a Chip (SoCs)*, integrating multiple processor cores with other components, such as memory and peripheral devices, on a single die. Smartphones and tablets typically use high-performance ARM SoCs, whose performance is comparable to laptop processors by now. Despite those technical differences, a lot of mobile embedded devices are, in fact, capable of general-purpose computing, being fixed to a specific function only by their software. This means that, despite the strict definition of embedded devices, mobile devices are much more similar to each other and constitute a more homogeneous device class with regard to their complexity, versatility and attack surface than it might initially seem.

Mobile devices share a unique set of characteristics that makes them an interesting attack target and *mobile security* challenging. First of all, as the name suggests, they

<sup>&</sup>lt;sup>1</sup>At the end of 2016, according to StatCounter [Sta16], the Internet usage from mobile devices exceeded desktop computers for the first time.

<sup>&</sup>lt;sup>2</sup>As of 2016, 78 percent of the adult population in Germany use a smartphone [Bit17]

<sup>&</sup>lt;sup>3</sup>The Bluetooth SIG predicts 4 billion devices with Bluetooth technology to ship in 2018 [Blu18].

<sup>&</sup>lt;sup>4</sup>In 2019, Cisco predicted [Cis19] that by 2022, wireless and mobile devices will be responsible for 71 percent of the total IP traffic. According to Cisco, smartphones alone will account for 44 percent of the traffic.

are *mobile* and, hence, exposed to changing, possibly hostile environments and at risk of getting lost or stolen<sup>1</sup>. They are *massively connected*, almost exclusively using wireless communication technologies, such as mobile networks, Wi-Fi and Bluetooth, offering a variety of remote attack vectors. Typically being equipped with various sensors, mobile devices are *aware of their environment*, gathering very personal or valuable data. Especially smartphones nowadays provide a variety of sensors including cameras, GPS receivers, microphones, gyroscopes, accelerometers and even biometric sensors, such as fingerprint readers. Last but not least, mobile devices typically can be *customized with apps* installed by their users. All those properties make mobile devices extremely *versatile* and the primary, most personal computing devices for most of their users. Consequentially, mobile devices carry a lot of valuable data, such as payment information, biometrics, and cryptographic keys and identities. The recent years have shown that the combination of being extremely exposed and carrying valuable data indeed makes mobile devices, especially smartphones, prime targets for attackers<sup>2</sup>.

Many attacks on mobile devices take advantage of one or more of their specific characteristics. In contrast to other device classes, such as desktops, mobile devices are at higher risk of getting lost or stolen, opening them up to *physical* attacks. An attacker gaining possession of a running device might, for example, try to extract data from its main memory using a Direct Memory Access (DMA) or cold boot attack. In a *DMA attack*, the attacker typically uses a peripheral port of the device with DMA capability, such as FireWire or Thunderbolt, for data extraction [Boi06; BDK05; SB12; Mar+19]. In a *cold boot attack*, the attacker physically moves the device's memory to another machine or reboots the device into a custom bootloader to extract data [Hal+09; Gut01]. While cold boot typically targets traditional PCs or laptops, it has been shown to be effective against smartphones as well [MS13; Tau+15].

Their mobility and various wireless communication interfaces, furthermore, open mobile devices up for *proximity attacks*, exploiting a vulnerability in the hardware, implementation or protocol of a wireless interface from a relatively close distance. *Key Reinstallation Attacks (KRACKs)* [VP17] target the Wi-Fi Protected Access 2 (WPA2) 4-way handshake used to join a Wi-Fi network. In a KRACK attack, the attacker takes a Man-in-the-Middle (MitM) position and re-installs a key that is already in-use, resetting nonces and counters. With a following known-plaintext attack, the attacker can then decrypt packages. While this attack does not target the device directly and most importantly does not allow for Remote Code Execution (RCE), it still illustrates the specific challenges of mobile security. *Broadpwn* [Art17] is another recent proximity attack, which exploits

<sup>&</sup>lt;sup>1</sup>In 2014, the FCC reported more than a million stolen smartphones per year in the US [Fed14]. In the UK, almost half a million mobile phone thefts were reported in the year ending march 2016 [Off16]. In Germany, in 2013 almost a quarter million mobile phones were reported stolen [Bun14].

<sup>&</sup>lt;sup>2</sup>In 2017, with over 800 by far the most Common Vulnerabilities and Exposuress (CVEs) of any software product were reported for Android [CVE]. With almost 400 CVEs iOS, the other important mobile Operating System (OS), occupies the third place.

Broadcom Wi-Fi chipsets, widely used in smartphones. By exploiting a flaw in the implementation of the Wi-Fi association protocol, Broadpwn achieves RCE on the Wi-Fi chip itself without user interaction. From there, it can attack the device, for example, using the Wi-Fi chip's DMA access to extract main memory data remotely. *Blueborne* [SV17] is a collection of vulnerabilities and exploits targeting Bluetooth stacks on desktops and mobile devices. From within Bluetooth range, at the time of its discovery, Blueborne could exploit vulnerabilities in the complex Bluetooth software stack to achieve RCE on Android and iOS, among others. While all three presented vulnerabilities are fixed in current versions of the affected devices and software, they illustrate how large and diverse the attack surface of mobile devices actually is.

The versatility and complexity of mobile device software also results in an increased number of *remote exploits*. Compared to proximity and physical attacks, remote exploits are typically rather traditional but can have a huge impact considering today's prevalence of mobile devices and the value of the data at risk. *Pegasus* [Baz+16], discovered in 2016, is a highly developed iOS malware, able to spy on the user of an infected device. The malware distribution is initiated as a *phishing* attack. As soon as the user visits a specially crafted website, the attack exploits the browser and achieves RCE. Two further vulnerabilities are then used for privilege escalation, persisting the malware and enabling it to gather sensitive data. *Stagefright* [ADB15] is a well-known group of vulnerabilities and corresponding exploits in the Android multimedia framework. At the time of its discovery, Stagefright allowed an attacker to achieve RCE on a victim's device using numerous ways, including Messengers, Email and Bluetooth. The Pegasus and Stagefright exploits are patched in current versions of iOS and Android, but they are being followed by newer, more complex attacks, using advanced techniques such as Return-Oriented Programming (ROP) [Sha07; Kor10], emphasizing the need for advanced mobile security.

On the other hand, the security of mobile devices improves constantly. While some improvements are completely based in software, such as sandboxing and the use of safe programming languages, software security features are often directly or indirectly driven by new hardware features. The introduction of virtual memory and relative addressing enabled Position-Independent Code (PIC) and, thus, *Address Space Layout Randomization (ASLR)*, a widely used defensive mechanism that impedes ROP and other Code-Reuse Attacks (CRAs)<sup>1</sup>. Access permissions on virtual memory pages enabled *Data Execution Prevention (DEP)* and *Write XOR Execute (W^X)*, powerful basic techniques, preventing an attacker from injecting new or modifying existing code. While those techniques were originally introduced on traditional computers first, they are, by now, standard on high-performance mobile device, as well. Other hardware-driven security features were first introduced on mobile devices, such as the *secure boot*, enabling systems that exclusively boot and run signed software. Another mobile-driven technique is the usage of device-unique,

<sup>&</sup>lt;sup>1</sup>While ASLR, for example, helps to prevent Stagefright, as a probabilistic method it is often considered an insufficient defense against advanced attackers [Sha+04].

secret hardware keys that cannot be extracted by software. Those allow, for example, for the encryption of secondary storage without an attacker being able to brute-force the encryption off-device. These are only a few examples of hardware features driving the development of new security mechanisms.

In a relatively recent development, mobile Central Processing Units (CPUs) gain more *logical separations*, i.e., separated code execution contexts typically associated with a privilege level of the software running in them. Traditionally, a CPU at least separates user and kernel space. Trusted Execution Environments (TEEs), such as ARM TrustZone [AF04] and Intel Software Guard Extensions (SGX) [McK+13], additionally partition a system into a *secure world* and a *normal world*. Hardware-assisted virtualization extensions introduce new CPU modes and features to enable efficient platform virtualization. While the latter has traditionally been a feature of server CPUs, it has, by now, found its way into high-performance mobile ARM CPUs [MN11]. Besides their intended uses, for example, for platform virtualization, those new logical separations offer interesting possibilities for novel mobile security mechanisms. In this thesis, we want to leverage those possibilities to protect a mobile device against different remote and physical attackers.

While logical separation is invaluable for protecting the integrity and confidentiality of most devices, in some cases it is not sufficient to protect high value secrets. First of all, bugs in privileged components are frequent [Ros14; Ben17] and typically expose secrets protected by the separation. But also without exploiting software bugs, logical separation can be overcome by advanced attackers. First, a separation may be crossed by physical attackers, for example, by using cold boot or DMA attacks as discussed before. But more importantly, a whole class of *microarchitectural attacks* can exploit the fact that logically separated contexts still share most hardware components of the system, such as cache, branch predictor and Dynamic Random Access Memory (DRAM), to leak secrets. This way, basic cache timing side channels [Ber05; YF14] can extract keys from separated contexts. Furthermore, recently discovered attacks Meltdown [Koc+18; Hor18] and Spectre [Lip+18b; Hor18] leverage speculative execution on modern, high-performance CPUs for cache timing attacks that can read arbitrary data from privileged contexts, including TEEs [Che+18]. Finally, Rowhammer attacks break logical separation in main memory by leveraging a physical property of DRAM, which, when accessing a specific DRAM address in rapid succession, can show bit flips in nearby memory cells [Kim+14]. Rowhammer attacks have been shown to be effective on mobile devices [Vee+16], can be used for privilege escalations [Sea15], remotely [Lip+18a; Tat+18] and can be able to cross the strong logical isolation by TEEs [Car17]. Those attacks illustrate that, while sufficient for most data, some high value secrets, such as keys and user identities, require stronger protection than provided by logical separations in modern CPUs. Hence, as another part of this thesis, we want to explore new ways to leverage physical separation to protect valuable secrets.

#### 1.1. RESEARCH QUESTIONS

### 1.1 Research Questions

It should be clear by now that mobile devices are exposed to a large variety of attacks making mobile security challenging. Often, the ultimate goal of an attacker is to extract valuable user data, keys or identities. Based on the discussion in the previous section, in this thesis, we want to explore new ways to use *features of modern CPUs*, especially *logical and physical separations*, to improve the security of mobile devices against physical and remote attackers. More specifically, we want to answer the following research questions:

- How can we monitor and protect run-time integrity? A remote attacker typically gains access to a mobile device by exploiting a process via one of the remote communication interfaces. Controlling a user space process, the attacker typically tries to elevate his privileges to gain access to the kernel space and, ultimately, extract secrets and data from the device. Monitoring the execution of the system is the first step to protection. Monitoring execution from a privileged, separated context could result in a protection mechanism that works transparently and independently of the device's OS. Hence, we want to explore ways to use the new logical separations in modern CPUs, more specifically hardware-assisted virtualization, to monitor and, ultimately, protect the run-time execution of a device.

- How can we protect data in main memory? Without relying on software bugs, strong physical attackers might be able to extract valuable user data from main memory of a mobile device, for example, via a cold boot or DMA attack. While Full Disk Encryption (FDE) is widely used on mobile devices, Random Access Memory (RAM) is typically unencrypted. Hence, we want to explore ways to protect the confidentiality of main memory, at run-time *and* while the device is suspended. Again, we want to leverage logical and physical separation to develop new approaches and to improve the security of existing ones.

- How can we protect keys and identities? While logical, in-CPU separation is essential for most security concepts, and new logical separations allow for novel approaches, in some cases, the achieved security is not sufficient. Software bugs in privileged software, physical attacks and microarchitectural attacks might be able to break through logical separation, emphasizing the need for stronger protections. Especially for small, high value secrets, such as cryptographic keys and identities, better protections seem feasible and necessary. Hence, we want to explore ways to leverage physical separation to protect keys for symmetric cryptography *and* asymmetric keys used as user identities.

Securing mobile devices poses some unique challenges. By answering our research questions, we want to approach some of these challenges and improve overall mobile security, especially the confidentiality of valuable user data and secrets.

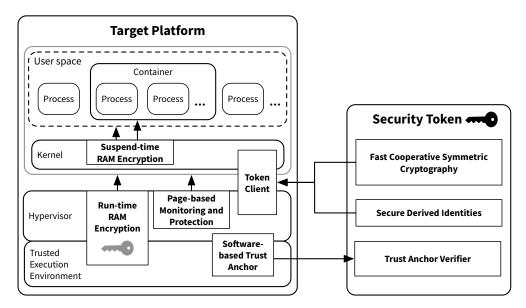

Figure 1.1: Logical and physical separation of security-critical components.

## 1.2 Contributions

In order to find answers to our research questions, we want to follow a basic scheme for our security concepts. Based on the assumptions that complex software always contains vulnerabilities proportional to the code size, we want to move security-critical code and assets into separated contexts, isolating them from the majority of software running on a mobile device and reducing the Trusted Computing Base (TCB) for our concepts.

Our goal is to protect a high-performance mobile device, our *target platform*, against different physical and remote attackers, as described before. To achieve this, we want to use all logical, in-CPU separations available and develop novel concepts that leverage their specific features. The separations include the kernel layer, the virtualization layer and the secure world of a TEE. As explained before, for some valuable assets, the isolation provided by a logical separation might be insufficient. Hence, we extend our architecture with a dedicated, physical security device, the *security token*, providing an additional, *physical* separation for some of our concepts. Our basic vision is summarized in Figure 1.1, showing the logical and physical separations in our two-part system architecture.

The main contributions in this thesis towards reaching this vision are summarized in the following:

**Page-granular transparent tracing of code execution.** We present a framework for logically separated kernel and user space execution tracing as a basis for protecting a target platform against remote attackers. Our framework uses hardware-assisted virtualization features to restrict the number of executable pages in a guest from a

#### **1.2. CONTRIBUTIONS**

custom minimal hypervisor. The framework analyzes the resulting page faults to infer information about the guest's control flow. Based on this, we furthermore propose a concept using the framework to transparently enforce a particular page-granular control flow in the guest. We present a prototype implementation on an ARM Cortex-A15 development board running Android OS. Based on our prototype, we conduct a detailed performance evaluation of our tracing framework and hardware-assisted virtualization on ARM in general.

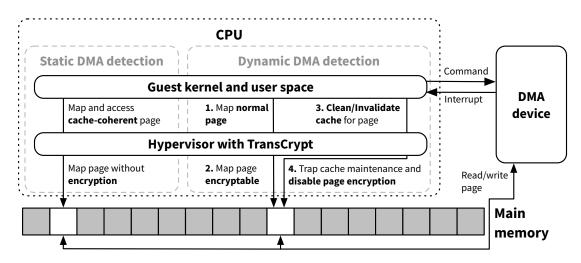

Publication: [HW15]

**Run-time main memory encryption.** We present a run-time memory encryption scheme protecting data confidentiality of processes and kernel running on our target platform against physical attackers. We leverage hardware-assisted virtualization and use a minimal hypervisor to restrict a guest, including kernel and user space, to a small working set of recently accessed pages, while keeping other pages encrypted. The mechanism is transparent and works independently of the guest OS. We, furthermore, propose a mechanism to transparently detect and exclude pages for which the encryption would lead to malfunction, for example, because they are shared with DMA devices. Based on our fully functional prototype implementation on an ARM Cortex-A15 development board running Android OS, we present a detailed evaluation of our run-time memory encryption.

Publication: [HHW17a]

**Combination of run- and suspend-time memory encryption.** Typically, not all functions of a mobile device are required at all times and many components can be safely suspended until needed. In order to provide even stronger protection for the data of suspended components, we describe the combination of our run-time memory encryption approach with a suspend-time memory encryption scheme, which is the result of joint work research. We describe how the suspend-time encryption scheme is able to protect data of suspended processes or process groups on our target platform against strong physical attackers using our token as physically separated key storage. The mechanism is orthogonal to the run-time encryption and leverages Linux functions for process grouping and suspension.

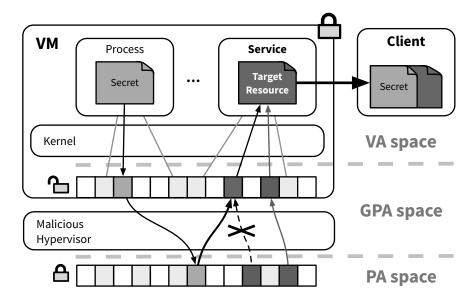

Our approach competes with recent hardware-assisted memory encryption schemes. Hence, additionally, as the result of joint work, we provide a security analysis of AMD's virtual machine encryption. The scheme aims to protect the data confidentiality of virtual machines against a malicious hypervisor. We describe and realize an attack able to extract memory contents from a virtual machine encrypted with this mechanism using a malicious hypervisor. Our successful attack shows that concepts that try to remove privileged components from the TCB are hard to realize.

Publication: [HHW17a]

Joint work publications: [HHW17b; Hub+17; Hub+18; Mor+18]

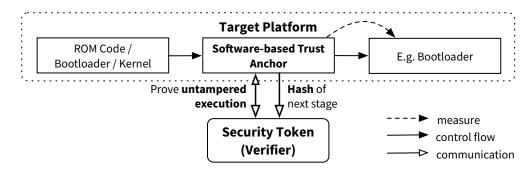

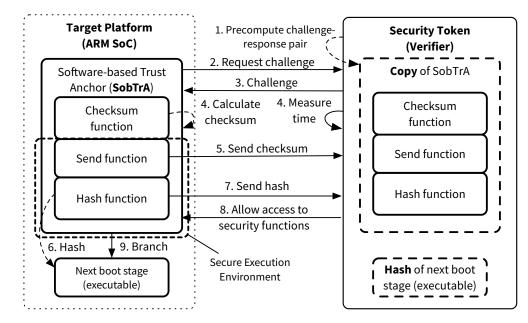

Externally verifiable execution on ARM. To protect valuable assets of our target platform against attacks breaking logical separation, we introduce an additional, physical separation in form of our security token. In order to protect the assets on the token against a compromised target platform, we want the token to be able to verify the integrity of the target platform's boot process before unlocking its security functions. To achieve this without requiring special attestation hardware and key material in the target platform, we introduce a timing-based software primitive that enables the token to verify that a specific piece of code is executed unmodified on our target platform. This primitive must be specifically designed for the target platform's CPU, i.e., in our case an ARM Cortex-A mobile processor. Based on this primitive, we introduce a *software-based trusted boot* process which proves the target platform's boot time integrity towards the token. We present a full implementation of the primitive and the boot process with an ARM Cortex-A8 development board as target platform. Based on our prototype, we provide a detailed experimental evaluation of the concept, showing that malicious modifications of the boot-integrity can be detected reliably.

Publication: [Hor+14b]

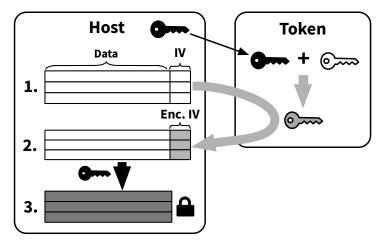

**Fast token-based external symmetric cryptography.** In order to protect valuable symmetric keys of the target platform, for example, for FDE, against attacks breaking logical separation, we want to leverage the physically separated token. Moving the keys from the target platform to the token protects them but executing all related cryptographic operations externally is too slow for data-intensive use cases, such as FDE. To solve this problem, we propose a concept that *partially* moves those cryptographic operations to the token, ensuring the security of the externally stored keys while still offering comparably high performance. Our concept combines keys of both entities and forces the target platform and token to cooperate during data encryption and decryption. The key combination, furthermore, binds the encrypted data to the specific token used for its encryption. We present a complete prototype implementation and a detailed performance evaluation showing that our prototype is fast enough for data-intensive use cases.

Publication: [HWE16]

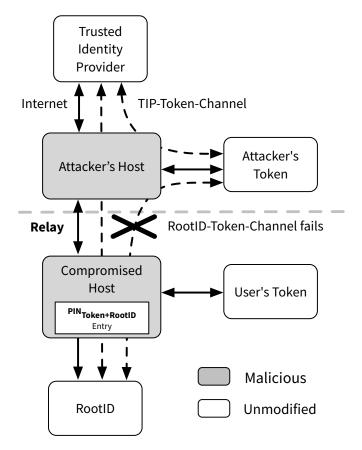

**Token-based identity derivation and usage.** Mobile devices are often very personal devices and, hence, typically store a lot of user authentication credentials. As an alternative to, for example, passwords, the authentication can be secured using asymmetric cryptography Identities (IDs), i.e., a key pair and a certificate trusted by the targeted service. Those IDs can be protected against attacks on logical separation by storing them on our token. Asymmetric cryptography used for authentication happens much less frequently and, therefore, in contrast to the symmetric case, the operation can be fully moved to the token without performance issues. But the

#### 1.3. PUBLICATIONS

challenge remains how to securely generate IDs on the token that are immediately trusted by a service the users wants to authenticate to. To solve this problem, we extend our architecture with a trusted *RootID* device and propose a protocol able to securely *derive* trusted IDs from the RootID into the token, even when assuming a completely compromised target platform. We, furthermore, present a protocol for securely *using* derived IDs for authentication. Our prototype implementation confirms the feasibility of our approach.

Publication: [Hor+14a]

# 1.3 Publications

Parts of the contributions in this thesis have been published in the following scientific, peerreviewed articles. Some of the publications contain additional contributions not covered in this thesis.

| [Hor+14a] | Julian Horsch, Konstantin Böttinger, Michael Weiß, Sascha Wessel, and Frederic<br>Stumpf. "TrustID: Trustworthy Identities for Untrusted Mobile Devices". In: <i>Pro-</i><br><i>ceedings of the 4th ACM Conference on Data and Application Security and Privacy</i> .<br>CODASPY '14. San Antonio, Texas, USA: ACM, Mar. 2014, pp. 281–288.                |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [HHW17a]  | Julian Horsch, Manuel Huber, and Sascha Wessel. "TransCrypt: Transparent Main<br>Memory Encryption Using a Minimal ARM Hypervisor". In: <i>Proceedings of the 16th</i><br><i>International Conference on Trust, Security and Privacy in Computing and Communi-</i><br><i>cations.</i> TrustCom '17. Sydney, Australia: IEEE, Aug. 2017, pp. 152–161.       |

| [HW15]    | Julian Horsch and Sascha Wessel. "Transparent Page-Based Kernel and User Space<br>Execution Tracing from a Custom Minimal ARM Hypervisor". In: <i>Proceedings of</i><br><i>the 14th International Conference on Trust, Security and Privacy in Computing and</i><br><i>Communications</i> . TrustCom '15. Helsinki, Finland: IEEE, Aug. 2015, pp. 408–417. |

| [HWE16]   | Julian Horsch, Sascha Wessel, and Claudia Eckert. "CoKey: Fast Token-based Cooperative Cryptography". In: <i>Proceedings of the 32nd Annual Conference on Computer Security Applications</i> . ACSAC '16. Los Angeles, California, USA: ACM, Dec. 2016, pp. 314–323.                                                                                       |

| [Hor+14b] | Julian Horsch, Sascha Wessel, Frederic Stumpf, and Claudia Eckert. "SobTrA: A Software-based Trust Anchor for ARM Cortex Application Processors". In: <i>Proceedings of the 4th ACM Conference on Data and Application Security and Privacy</i> . CODASPY '14. San Antonio, Texas, USA: ACM, Mar. 2014, pp. 273–280.                                       |

| [Hub+17]  | Manuel Huber, Julian Horsch, Junaid Ali, and Sascha Wessel. "Freeze & Crypt: Linux Kernel Support for Main Memory Encryption". In: <i>14th International Conference on Security and Cryptography (SECRYPT 2017)</i> . INSTICC. ScitePress, 2017.                                                                                                           |

| [Hub+18]  | Manuel Huber, Julian Horsch, Junaid Ali, and Sascha Wessel. "Freeze and Crypt:<br>Linux Kernel Support for Main Memory Encryption". In: <i>Computers &amp; Security</i><br>(2018).                                                                                                                                                                         |

- [HHW17b] Manuel Huber, Julian Horsch, and Sascha Wessel. "Protecting Suspended Devices from Memory Attacks". In: *Proceedings of the 10th European Workshop on Systems Security*. EuroSec'17. Belgrade, Serbia: ACM, Apr. 2017, 10:1–10:6.

- [Mor+18] Mathias Morbitzer, Manuel Huber, Julian Horsch, and Sascha Wessel. "SEVered: Subverting AMD's Virtual Machine Encryption". In: Proceedings of the 11th European Workshop on Systems Security. EuroSec'18. Porto, Portugal: ACM, Apr. 2018.

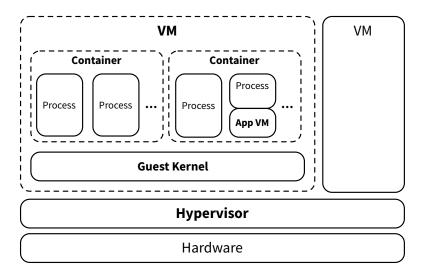

**Other publications.** Additionally, we published articles whose contributions are not part of this thesis. In [Hub+15], we propose a secure architecture for OS-level virtualization for mobile devices. Our approach allows multiple Linux-based OS instances, such as Android, to run simultaneously on a single physical device. We isolate those instances from each other by restricting them to their minimally required functionality and permitting communication only through well-defined channels. Our architecture is able to keep user data secure even if large parts of the rest of the system are compromised.

In [ZH18], we propose a novel compiler-based approach to protect programs written in unsafe languages, such as C and C++, against attacks corrupting return addresses. By storing return addresses on a second, *safe stack*, we effectively prevent various attacks, ranging from simple code injections to advanced techniques like ROP. In contrast to other *dual stack* schemes, our safe stack is protected against information disclosure attacks. With an average overhead of no more than 2.7%, our approach is well usable in real-world scenarios.

In [MHH19], we propose a concept for locating memory pages containing valuable secrets, such as keys, in encrypted virtual machines, only by observing page faults and certain I/O events. In our prototype implementation, we combine this knowledge with our method for extracting data from encrypted memory presented in this thesis, to efficiently extract valuable keys from an encrypted virtual machine.

- [Hub+15] Manuel Huber, Julian Horsch, Michael Velten, Michael Weiß, and Sascha Wessel. "A Secure Architecture for Operating System-Level Virtualization on Mobile Devices".

In: Information Security and Cryptology 11th International Conference, Inscrypt 2015, Beijing, China, November 1-3, 2015, Revised Selected Papers. Vol. 9589. Lecture Notes in Computer Science. Springer, 2015, pp. 430–450.

- [ZH18] Philipp Zieris and Julian Horsch. "A Leak-Resilient Dual Stack Scheme for Backward-Edge Control-Flow Integrity". In: Proceedings of the 2018 ACM Asia Conference on Computer and Communications Security. ASIA CCS '18. Incheon, Republic of Korea: ACM, June 2018.

- [MHH19] Mathias Morbitzer, Manuel Huber, and Julian Horsch. "Extracting Secrets from Encrypted Virtual Machines". In: *Proceedings of the 9th ACM Conference on Data and Application Security and Privacy*. CODASPY '19. Richardson, Texas, USA: ACM, Mar. 2019.

Figure 1.2: Visual outline of the thesis.

### 1.4 Outline

The remainder of the thesis is organized as follows. In Chapter 2, we introduce existing technologies and concepts that are necessary or helpful as background for understanding our contributions. First, we discuss fundamentals of the ARM architecture, the predominant CPU architecture for mobile devices. Then, we cover virtualization concepts, especially platform virtualization as logical separation in modern CPUs. Afterwards, we introduce TEEs as hardened logical CPU separation and boot integrity mechanisms, i.e., secure and measured boot.

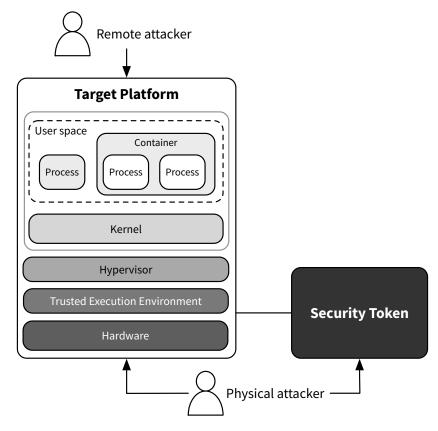

In Chapter 3, we first introduce our generic system architecture used throughout the thesis. We discuss both physical entities of the architecture and the hardware requirements imposed on them by our different security concepts. We conclude the chapter introducing a generic attacker model building the basis for the specific attacker models in the following chapters.

Chapters 4, 5, 6 and 7 build the main contributions of the thesis. Figure 1.2 visualizes the main topics of those chapters in the context of our system architecture. In Chapter 4, we introduce our software-based trusted boot process which allows the target platform to prove its boot-time integrity towards the token without requiring shared key material. The mechanism is based on SobTrA, our primitive for externally verifiable execution on ARM, which we present as main part of the chapter. After introducing a specific attacker model and discussing related work, we present the SobTrA design, our implementation on Cortex-A8 CPUs and experimental results from our prototype. The proof of the target

platform's boot time integrity guarantees the token that the following security concepts on the target platform are active at run-time.

In Chapter 5, we present our transparent, virtualization-based framework for pagegranular tracing execution of kernel and user space on our target platform. As framework application with the goal to protect the run-time integrity of our target platform, we propose a concept for enforcing a particular page-granular control flow. After introducing typical attacks and related work, we present conceptual and implementation details of our tracing framework. Then, we introduce our run-time integrity application and its implementation. Finally, we conclude the chapter with a detailed performance analysis based on our prototype implementation.

In Chapter 6, we introduce our concepts to protect the confidentiality of the target platform's main memory. We first discuss memory attacks, able to extract data from main memory, and, based on them, specify an attacker model. Then, we introduce TransCrypt, our virtualization-based approach for encrypting the main memory of kernel and user space at run-time. We describe conceptual details of TransCrypt and its prototype implementation and, afterwards, evaluate the prototype regarding security and performance. Then, we introduce our Linux-based suspend-time encryption scheme and discuss the combination of both our run-time and suspend-time approaches. Finally, we conclude the chapter with a security analysis of AMD SEV, a hardware-based mechanism for memory encryption, presenting SEVered, an attack with which we are able to subvert SEV.

In Chapter 7, we propose two concepts that externalize highly valuable secrets from the target platform to the token to protect them against attacks breaking logical separations in the target platform's CPU. After detailing those attacks, we first introduce CoKey, our approach for protecting symmetric keys by forcing the target platform and token to cooperate during encryption and decryption. Then, we present TrustID, our concept for securing user identities with the token. For both approaches, we cover conceptual details and the respective prototype implementations before discussing the security gained through each concept.

We conclude the thesis in Chapter 8, where we summarize and assess our contributions before sketching possible future research topics in the field of mobile security.

# Background

In this chapter, we introduce basic technologies and concepts important for understanding the rest of the thesis. While some, more specific aspects of the topics are introduced later where needed, the information given in this chapter is typically useful for more than one chapter of the thesis.

# 2.1 ARM Architecture

The ARM architecture is a widely used Reduced Instruction Set Computing (RISC) design for CPUs. ARM processors provide some characteristic features typical for RISC architectures:

- Many general-purpose registers, which can, in most cases, be freely used in threeoperand instructions.

- Memory contents are only read and written using explicit load and store instructions (*Load-Store* architecture).

- Simple addressing modes for load/store where addresses are only generated based on register contents and immediates.

The ARM architecture is versioned, with ARMv8 being the latest version at the time of writing. Furthermore, ARM differentiates between three architecture *profiles*:

- **A Application.** Profile for traditional application processors. Provides support for virtual memory with an Memory Management Unit (MMU).

- **R Real-time.** Profile for processors in safety-critical environments. Provides support for memory protection with a Memory Protection Unit (MPU).

- **M Microcontroller.** Profile for microcontrollers, optimized for low-latency interrupt handling. Supports a variant of the R-profile MPU.

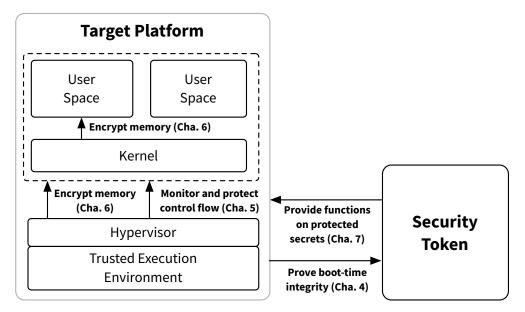

Figure 2.1: Architecture of a typical ARM SoC.

In this work, we focus on the two latest versions of the A-profile architecture, namely ARMv8-A [ARM17] and ARMv7-A [ARM14]. ARM, furthermore, specifies extensions to the architecture, for example, the ARMv7-A Virtualization Extensions [ARM14] and ARMv8 Cryptographic Extensions. For ARMv8, ARM also specifies updates to the architecture in form of sub-versions, e.g., ARMv8.3-A [ARM17]. The following descriptions refer to ARMv8-A without extensions and are based on information from the ARMv8-A reference manual [ARM17], if not stated otherwise.

Aside from specifying the ARM architecture, ARM develops designs for actual CPUs implementing the architecture. Those *Cortex* processors typically follow a simple naming scheme including the architecture profile and a number. For example, the Cortex-A53 processor implements the ARMv8-A architecture. An ARM Cortex-A CPU is typically part of an embedded SoC, containing not only multiple CPU cores but also bus systems, co-processors, caches, peripherals, Graphics Processing Units (GPUs) and other components in a single die. Figure 2.1 depicts a typical, yet simplified SoC architecture. In the following, we discuss the basic architectural concepts of an ARM application processor core.

#### 2.1. ARM ARCHITECTURE

#### 2.1.1 Execution States and Instruction Sets

ARMv8-A [ARM17] defines two *execution states* for a CPU: AArch64 and AArch32. While AArch32 is a 32-bit state backward-compatible to ARMv7-A, AArch64 is a complete 64-bit redesign of the architecture. Since AArch32, apart from some additions for interprocessing with AArch64, basically equals ARMv7-A, we use both terms interchangeably. The execution state determines several important properties of the CPU's execution environment:

- The supported Instruction Set Architectures (ISAs) and register set.

- Significant aspects of the exception, programmers' and memory model.

The ARMv8-A execution states support different *instruction sets*, i.e., ISAs. While the backward-compatible AArch32 state supports *A32* and *T32*, which are basically the ARM and Thumb-2 ISAs specified by ARMv7, AArch64 only supports the new *A64* ISA.

- **A32.** The A32 instruction set uses fixed-length 32-bit wide instructions and 32-bit registers. It is compatible to the ARMv7 ARM instruction set.

- **T32.** The T32 instruction set uses the same 32-bit registers as the A32 ISA but a mixture of 32- and 16-bit wide instructions to increase code density. T32 is compatible to the ARMv7 Thumb-2 instruction set.

- **A64.** The A64 instruction set uses fixed-length 32-bit wide instructions and, primarily, 64-bit registers.

The AArch32 state and its ISAs use a register set that contains thirteen 32-bit generalpurpose registers and some special registers, such as *Program Counter (PC)*, *Stack Pointer (SP)* and *Link Register (LR)*. The AArch64 state uses 31 64-bit general-purpose registers, a PC, and several SPs and LRs. In AArch64, components of the program state (PSTATE), such as the arithmetic flags, are directly and independently modified using special instructions. AArch32 additionally supports a backward-compatible mechanism for modifying the entire program state by accessing the *Current Program Status Register (CPSR)*. Furthermore, while in ARMv7 and AArch32 system registers, such as the *System Control Register (SCTLR)*, are accessed with co-processor instructions, AArch64 allows named access to those.

The exception and memory models of the ARMv8-A execution states are discussed in the following.

#### 2.1.2 Privilege and Exception Model

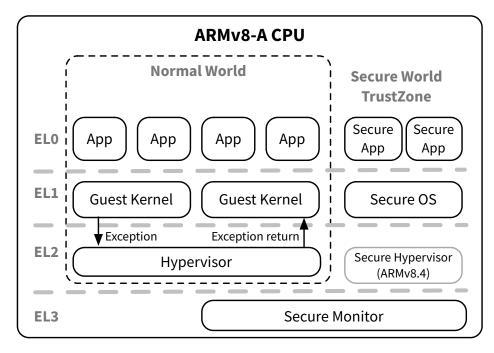

ARM application processors implement multiple privilege levels for logical separation of different types of software running on the CPU. Figure 2.2 shows the logical separations inside an ARMv8-A processor. ARMv8-A defines four Exception Levels (ELs), EL0-3. The EL determines the privilege of the software running in it, i.e., its Privilege Level (PL).

Figure 2.2: Exception and privilege levels of an ARMv8-A CPU.

The higher the EL, the more privileged, with EL3 being the highest privilege and EL0 the lowest, also known as *unprivileged* execution. EL0-2 are mirrored in normal and secure state versions. As shown in Figure 2.2, applications typically run in EL0, OS kernels in EL1 and hypervisors or Virtual Machine Monitors (VMMs) in EL2. EL3 typically houses firmware and code for switching between normal and secure world, building ARM's TEE TrustZone, discussed later in this chapter. Both, EL2 and EL3, are architecturally optional and may be omitted in an ARMv8-A processor.

**Transfers.** Transfers between ELs happen via exceptions. When an exception occurs, the execution is transferred from, i.e., *taken from*, the current EL *to* the same or a higher EL to a code location previously specified in the *exception vector table* of the target EL. After handling the exception, the execution is usually returned to the location and EL it was taken from. In a multi-core system, each core executes and transfers between the ELs independently. ARM differentiates between synchronous and asynchronous exceptions. A *synchronous exception* is a direct result of an (attempted) execution of an instruction. Such an exception is triggered, for example, when an unprivileged application running in EL0 tries to execute a privileged instruction or issues a system call using SVC. *Asynchronous exceptions* or *interrupts* are not the direct result of an instruction but other, often external, events, such as peripheral devices signaling incoming data.

Figure 2.3: Exception and privilege levels of an ARMv7-A CPU.

**Interprocessing.** ELs *use* execution states, i.e., AArch32 or AArch64. An ARMv8-A CPU can run ELs with different execution states and change them when changing the EL, which is called *interprocessing*. Interprocessing may only change state from AArch32 to AArch64 when taking an exception to a higher EL and from AArch64 to AArch32 when returning from an exception into a lower EL. For example, an OS kernel running in AArch64 might be able to support AArch32 applications, but an AArch32 kernel only runs AArch32 applications. This also means that running AArch32 EL3 software forces all ELs to use AArch32 resulting in a CPU that is completely compatible to an ARMv7-A CPU.

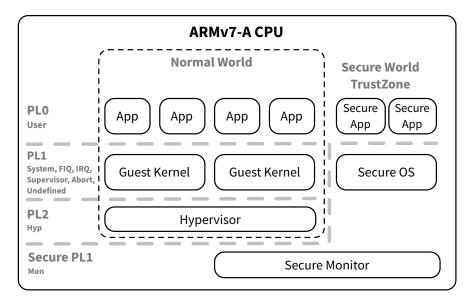

**ARMv7-A exception model.** Figure 2.3 shows the exception and privilege model of an ARMv7-A CPU or an ARMv8-A CPU running AArch32 EL3 software. Here, the CPU supports different *modes*, which are mapped to privilege levels PL0-2. While the other PLs each only contain one mode, PL1 provides a mode for each type of exception it handles. The ARMv7-A model does *not* contain an extra privilege level for the secure monitor. Instead, the corresponding Monitor mode shares the Secure PL1 domain with the Secure OS, both handling different exceptions using distinct exception vector tables.

### 2.1.3 Memory Model

ARM application processors use virtual memory. All instructions use Virtual Addresses (VAs) translated by one or more logical MMUs into Physical Addresses (PAs) before being used for accessing the system interconnect, for example, to load a value from volatile

Figure 2.4: Address translation regimes in an ARMv8.4-A processor.

memory. The main difference between AArch64 and AArch32 is the size of the VAs used. AArch64 uses 64-bit and AArch32 32-bit virtual addressing.

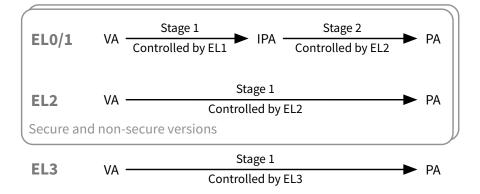

**Translation regimes.** Depending on the EL a VA is accessed from, the VA is translated using one of multiple *translation regimes*. The translations regimes of an ARMv8.4-A processor are visualized in Figure 2.4. Translation regimes are configured using translation tables, which are multi-level memory structures allowing page-granular mapping of input to output addresses. The CPU provides separate regimes for EL0/1 and EL2 in both secure and non-secure versions and a single regime for EL3. This means that the same VA can be translated to five different PAs based on in which of these contexts the accessing software is running.

A translation regime can have one or two stages. A stage 1 translation translates from Virtual Addresses (VAs) to *either* Physical Addresses (PAs) or Intermediate Physical Addresses (IPAs)<sup>1</sup>. A stage 2 translation *always* translates from IPAs to PAs. In virtualization terms, a stage 2 translation is a *Second Level Address Translation (SLAT)*. As such, it allows a hypervisor to run multiple Virtual Machines (VMs) in the same guest-physical address space, as detailed in Section 2.2.2. Each stage of a regime is configured independently and from a specific EL. Stage 1 translations are normally controlled by the EL the regime belongs to, whereas stage 2 translations are controlled by a higher privileged EL.

The shown ARMv8.4-A model provides a superset of the regimes of previous architecture versions. Previous versions of ARMv8-A do not provide a secure EL2. Hence, the corresponding EL2 regime and the secure EL0/1 stage 2 regime are not present there. In ARMv7-A, additionally, EL3 and its translation regime are omitted.

<sup>&</sup>lt;sup>1</sup>Intermediate Physical Address (IPA) is the term ARM uses for what is commonly referred to as *Guest-Physical Address (GPA)* in an abstract virtualization context. We use both terms interchangeably.

### 2.2. VIRTUALIZATION

**Attributes and permissions.** Translations are configured using translation tables. Aside from the target address, a Page Table Entry (PTE), controlling the translation of a single page, is configured with attributes and access permissions for the underlying memory. With its *attributes*, the controlling entity can specify if a page should be cacheable and if it is shared by multiple cores. *Access permissions* determine which types of accesses are allowed to the memory of a page. Besides the typical *read* and *write* permissions, the execution of a page can be restricted using the Execute Never (XN) flag. Furthermore, execution can be restricted based on the executing context using the Privileged Execute Never (PXN) and Unprivileged Execute Never (UXN) permissions.

The secure and non-secure worlds can have different *physical* address spaces. For example, some of the system's memory might only be accessible to the secure world. Therefore, each translation is additionally associated with a Non-Secure (NS) flag with which secure ELs may specify if the corresponding memory should be accessed as secure memory. For non-secure translations, the flag is ignored and accesses are always non-secure.

In translation regimes with two stages, attributes and permissions of both stages are combined so that always the more restrictive setting applies. For example, this allows a hypervisor to prevent a guest from executing memory the guest marked as executable.

# 2.2 Virtualization