Technische Universität München

Lehrstuhl für Sicherheit in der Informationstechnik an der Fakultät für Elektrotechnik und Informationstechnik

## Curve Based Cryptography: High-Performance Implementations and Speed Enhancing Methods

## **Claus Philipp Koppermann**

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines **Doktor-Ingenieurs (Dr.-Ing.)** genehmigten Dissertation.

| Vorsitzender:            |    | Prof. DrIng. Dr. rer. nat. Holger Boche |

|--------------------------|----|-----------------------------------------|

| Prüfer der Dissertation: | 1. | Prof. DrIng. Georg Sigl                 |

|                          | 2. | Prof. Dr. rer. nat. Marian Margraf      |

Die Dissertation wurde am 17.01.2019 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 13.05.2019 angenommen.

## Abstract

Key exchange algorithms based on public-key cryptography are a crucial component in modern communication systems because they enable two parties to securely derive a shared secret over a public channel. Unfortunately, the popular public-key cryptosystem RSA suffers in speed and requires large key sizes. New arising technologies put high demands on latency and throughput characteristics that catalyze the need for fast key exchange implementations. This thesis deals with high-performance implementations and speed enhancing methods of *curve based cryptography* that is composed of elliptic, hyperelliptic, and isogeny-based curve cryptography.

Elliptic and hyperelliptic curve cryptography are both based upon a fast modular arithmetic that make them appealing for securing communications with high-performance requirements. Many modern curves are defined over so-called Mersenne prime fields that feature an efficient reduction procedure. As modular multiplication is a performance critical operation, a novel speed enhancing architecture is introduced for multiplying two elements in a Mersenne prime field. Using this modular multiplier, two highly-optimized key exchange implementations are evaluated on an FPGA based on two different types of curves: Curve25519, a popular elliptic curve, and Gaudry and Schost's Kummer surface of a genus-2 curve, a novel hyperelliptic variant. Both implementations are analyzed and compared regarding their performance and implementation security. The Curve25519 implementation is optimized for low-latency applications and uses randomized projective coordinates to thwart specific side-channel attacks. Though, the performance results of our high-speed Kummer variant outperform all previous prime field curve implementations in terms of latency and throughput. The implemented Kummer architecture smartly interleaves two scalar multiplications at a time, which can be used to double the throughput or enable an inherent countermeasure against fault attacks. Compared to elliptic curve cryptography, the hyperelliptic variant achieves improved area and performance results due to a smaller field size.

It is well known that the continuous progress in the development of a quantum computer threatens the secure application of elliptic and hyperelliptic curve cryptography. Combined with the advent of the Internet of Things, thousands of interconnected nodes that process sensitive information are threatened. Therefore, the applicability and implementation security of the quantum-secure supersingular isogeny Diffie-Hellman (SIDH) key exchange is examined for the embedded scenario. SIDH attracted considerable interest in the research community due to its small key sizes when compared to other post-quantum primitives. While several works already presented speed-optimized FPGA implementations, it remains unclear whether it is suitable for resource-constrained devices. Hence, we provide a software implementation of SIDH over a 751-bit wide extension field, which is considered to provide a quantum-security level of at least 128-bit. Our software implementation is assembly optimized and trimmed towards maximum speed targeting a 32-bit ARM Cortex-M4 and a 16-bit TI MSP430 architecture. However, an ephemeral key exchange still requires more than 18 seconds for the Cortex-M4 and more than 11 minutes for the MSP430. With respect to the chosen parameters, this shows that SIDH is unsuitable for most real-life applications when implemented on small embedded devices.

## Kurzfassung

Schlüsselaustauschprotokolle basierend auf Public-Key Kryptographie sind essentiell in modernen Kommunikationsnetzwerken, weil sie zwei Teilnehmern erlauben sich über einen öffentlichen Kanal auf ein gemeinsames Geheimnis zu einigen. Jedoch ist das bekannteste Public-Key Kryptosystem RSA aufwendig in seiner Berechnung und benötigt große Schlüssel. Insbesondere neue Technologien stellen hohe Performance Anforderungen, was die Notwendigkeit von schnellen Schlüsselaustausch Implementierungen katalysiert. Diese Arbeit beschäftigt sich mit hochoptimierten Implementierungen und beschleunigenden Methoden für *kurvenbasierte Kryptographie*, welche sich in elliptische, hyperelliptische und isogeniebasierte Kurven Kryptographie untergliedert.

Elliptische und hyperelliptische Kurven Kryptographie zeichnet sich durch eine schnelle modulare Arithmetik aus, die sie besonders interessant für Implementierungen mit hohen Performance Anforderungen macht. Viele moderne Kurven sind über so genannte Mersenne Primzahl Körper definiert, die über eine effiziente Methode zur modularen Reduktion verfügen. Da die modulare Multiplikation eine zeitkritische Operation ist, wird zunächst eine neue Hardware Architektur für die modulare Multiplikation in Mersenne Primzahl Körpern vorgestellt. Unter Verwendung dieses Multiplizierers werden zwei Schlüsselaustausch Implementierungen für einen FPGA beschrieben, die auf verschiedenen Kurventypen basieren: Curve25519, eine bekannte elliptische Kurve, und Gaudy und Schosts kummersche Fläche einer Kurve vom Geschlecht 2, eine neue hyperelliptische Variante. Beide Implementierungen werden hinsichtlich ihrer Performance und Implementierungssicherheit analysiert und verglichen. Die Curve25519 Implementierung ist für Anwendungen mit niedrigen Latenz Anforderungen optimiert und verwendet randomisierte projektive Koordinaten um bestimmte Seitenkanal Angriffe zu verhindern. Allerdings übertrifft die Kummer Variante alle Performance Ergebnisse früherer Kurven Implementierungen über Primzahl Körper. Darüber hinaus kombiniert die Kummer Architektur zwei skalare Multiplikationen was entweder den Durchsatz verdoppelt oder eine Gegenmaßnahme für Fehlerangriffe ermöglicht. Aufgrund eines kleineren Körpers, erreicht die hyperelliptische Variante bessere Flächen und Performance Ergebnisse.

Der kontinuierliche Fortschritt in der Entwicklung des Quantencomputers bedroht die sichere Verwendung von elliptischer und hyperelliptischer Kurven Kryptographie. Unter Berücksichtigung aktueller Trends wie beispielsweise dem der Internet der Dinge, sind in Zukunft potentiell tausende verbundene Knoten bedroht. Daher wird die Anwendbarkeit und Implementierungssicherheit des quantensicheren supersingulären Isogenie Diffie-Hellman (SIDH) Schlüsselaustausch für eingebettete Sys-SIDH ist von besonderem Interesse, da es verglichen teme untersucht. zu anderen Post-Quanten Verfahren relativ kleine Schlüssel verwendet. Während diverse Arbeiten bereits geschwindigkeitsoptimierte Hardware Architekturen vorgestellt haben, bleibt es bis heute unklar wie sich eine Anwendung auf kleinen ressourcenbeschränkten Geräten darstellt. Um diese These zu überprüfen wird eine Assembler-optimierte SIDH Implementierung vorgestellt und deren Performance auf einem 32-Bit ARM Cortex-M4 und auf einem 16-Bit TI MSP430 evaluiert. Die vorgestellte Software realisiert SIDH über ein 751-bit großen Erweiterungskörper mit dem ein Quanten Sicherheitslevel von mindestens 128-bit erreicht wird. Ein ephemeral Schlüsselaustausch benötigt auf einem Cortex-M4 mehr als 18 Sekunden und auf einem MSP430 mehr als 11 Minuten. Mit Bezug auf die gewählten Parameter, zeigt dies dass die Laufzeit von SIDH auf einem eingebetteten Controller für reale Anwendungen noch zu lange ist.

## Acknowledgements

Firstly, I would like to express my sincere gratitude to Prof. Dr.-Ing. Georg Sigl for giving me the chance to pursue my Ph.D. at the Technische Universität München (TUM) and Prof. Dr. rer. nat. Marian Margraf for being my second examiner.

My special thanks goes to Dr.-Ing. Johann Heyszl, who provided me the opportunity to join the Hardware Security department at Fraunhofer AISEC, and his valuable scientific guidance.

I especially thank my former supervisor Dr.-Ing. Fabrizio De Santis for introducing me to cryptography and contributing to my research.

I thank my colleagues at Fraunhofer AISEC: Robert Hesselbarth, Stefan Hristozov, Dr. rer. nat. Katja Miller, Carsten Rolfes, Marc Schink, Bodo Selmke, Robert Specht, Martin Striegel, Florian Unterstein, Andreas Zankl, and in particular Nisha Jacob for their feedback, cooperation, and friendship.

I thank my students who supported my research in various ways: Abhijith Chikrapla Danappa, Zohaib Khan, and Eduard Pop.

Last but not least, I would like to thank my partner, family, and close friends for supporting me throughout the writing process of this thesis and my life in general. vi

# Contents

| Al            | ostra                                         | $\operatorname{ct}$                                                                                                                                                                                                                                                                                                                                                | i                                                                    |

|---------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Kı            | urzfa                                         | ssung                                                                                                                                                                                                                                                                                                                                                              | iii                                                                  |

| A             | cknov                                         | wledgements                                                                                                                                                                                                                                                                                                                                                        | $\mathbf{v}$                                                         |

| No            | omen                                          | nclature                                                                                                                                                                                                                                                                                                                                                           | ix                                                                   |

| $\mathbf{Li}$ | st of                                         | Figures                                                                                                                                                                                                                                                                                                                                                            | xiii                                                                 |

| $\mathbf{Li}$ | st of                                         | Tables                                                                                                                                                                                                                                                                                                                                                             | xv                                                                   |

| $\mathbf{Li}$ | st of                                         | Algorithms                                                                                                                                                                                                                                                                                                                                                         | cvii                                                                 |

| 1             | <b>Intr</b><br>1.1<br>1.2<br>1.3              | The Diffie-Hellman Key Exchange1.1.1Elliptic Curve Cryptography1.1.2Hyperelliptic Curve Cryptography1.1.3Isogeny-Based CryptographyContributionOutline                                                                                                                                                                                                             | 1<br>2<br>3<br>4<br>5<br>6<br>8                                      |

| 2             | Mul<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | Itiplication in Mersenne Prime Fields         Preliminaries         Hardware Multipliers         Multiplication and Crandall's Reduction Combined         Fast Multiplication on FPGAs         Related Work         2.5.1         Asymmetric Tiling         2.5.2         Regrouping Digit-Products         Design Automation for Combined Reduction         2.6.1 | <b>9</b><br>10<br>11<br>14<br>15<br>16<br>16<br>16<br>17<br>18<br>18 |

|          |      | 2.6.2 Digit-Product Splitting                                                                                                               | 19        |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|          |      | 2.6.3 Rearrange Sliced Digit-Products                                                                                                       | 21        |

|          | 2.7  | Hardware Design and Analysis                                                                                                                | 22        |

|          |      | 2.7.1 Results                                                                                                                               | 23        |

|          | 2.8  | Conclusions                                                                                                                                 | 24        |

| 3        | Elli | ptic Curve Cryptography                                                                                                                     | <b>27</b> |

|          | 3.1  | Introduction to Elliptic Curves                                                                                                             | 27        |

|          |      | 3.1.1 Short Weierstrass Form                                                                                                                | 28        |

|          | 3.2  | Scalar Multiplication and the Elliptic Curve Diffie-Hellman                                                                                 |           |

|          |      | Key Exchange                                                                                                                                | 28        |

|          |      | 3.2.1 Group Law on Elliptic Curves                                                                                                          | 29        |

|          | 3.3  | Choice of Coordinates                                                                                                                       | 30        |

|          |      | 3.3.1 Affine Coordinates                                                                                                                    | 30        |

|          |      | 3.3.2 Projective Coordinates                                                                                                                | 31        |

|          | 3.4  | Montgomery Ladder                                                                                                                           | 32        |

| <b>4</b> | X25  | 5519 DH Key Exchange on an FPGA                                                                                                             | 35        |

|          | 4.1  | Background                                                                                                                                  | 35        |

|          | 4.2  | Algorithmic Description                                                                                                                     | 36        |

|          | 4.3  | Pseudo Mersenne Prime Field Arithmetic                                                                                                      | 37        |

|          |      | 4.3.1 Addition and Subtraction                                                                                                              | 37        |

|          |      | 4.3.2 Multiplication                                                                                                                        | 39        |

|          |      | $4.3.3  \text{Inversion} \dots \dots$ | 39        |

|          | 4.4  | Hardware Architecture                                                                                                                       | 40        |

|          |      | 4.4.1 Montgomery Ladder                                                                                                                     | 41        |

|          | 4.5  | Results                                                                                                                                     | 41        |

|          | 4.6  | Conclusions                                                                                                                                 | 44        |

| <b>5</b> | Hyj  | perelliptic Curve Cryptography                                                                                                              | 45        |

|          | 5.1  | Group Law for Hyperelliptic Curves                                                                                                          | 46        |

|          |      | 5.1.1 The Jacobian Variety                                                                                                                  | 47        |

|          |      | 5.1.2 Addition on the Jacobian                                                                                                              | 49        |

|          | 5.2  | Montgomery Arithmetic for Genus-2 Curves over Prime Fields                                                                                  | 51        |

|          |      | 5.2.1 The Kummer Surface                                                                                                                    | 52        |

| 6        | Ku   | mmer Surface Based DH Key Exchange on an FPGA                                                                                               | 55        |

|          | 6.1  | Introduction                                                                                                                                | 55        |

|          | 6.2  | Preliminaries                                                                                                                               | 57        |

|          |      | 6.2.1 Gaudry and Schost's Genus-2 Hyperelliptic Curve                                                                                       | 58        |

|          | 6.3  | Compression and Scalar Multiplication                                                                                                       | 58        |

viii

### CONTENTS

|    | 6.4   | Hardware Architectures                                                                              | 59  |

|----|-------|-----------------------------------------------------------------------------------------------------|-----|

|    |       | 6.4.1 Memory                                                                                        | 60  |

|    |       | 6.4.2 Datapath                                                                                      | 61  |

|    |       | 6.4.3 Control Logic                                                                                 | 66  |

|    |       | 6.4.4 Multi-Core Architecture                                                                       | 67  |

|    | 6.5   | Results and Analysis                                                                                | 69  |

|    | 6.6   | Conclusions                                                                                         | 71  |

| 7  | Isog  | eny-Based Cryptography                                                                              | 73  |

|    | 7.1   | Preliminaries                                                                                       | 73  |

|    |       | 7.1.1 Isogenies                                                                                     | 74  |

|    |       | 7.1.2 Supersingular Curves                                                                          | 74  |

|    |       | 7.1.3 $\ell$ -Torsion Subgroups                                                                     | 74  |

|    | 7.2   | The Supersingular Isogeny DH Key Exchange                                                           | 75  |

|    |       | 7.2.1 Public Parameters                                                                             | 75  |

|    |       | 7.2.2 Key Generation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 75  |

|    |       | 7.2.3 Shared Secret Computation                                                                     | 76  |

|    |       | 7.2.4 Large Degree Isogeny Computation                                                              | 76  |

|    | 7.3   | Complexity Considerations                                                                           | 78  |

| 8  | SID   | H Key Exchange on Embedded Devices                                                                  | 81  |

|    | 8.1   | Introduction                                                                                        | 81  |

|    | 8.2   | Related Hardware Implementations                                                                    | 82  |

|    |       | 8.2.1 Architecture                                                                                  | 82  |

|    |       | 8.2.2 Results                                                                                       | 84  |

|    | 8.3   | Embedded Implementations                                                                            | 84  |

|    |       | 8.3.1 Platform Independent Design Decisions                                                         | 85  |

|    |       | 8.3.2 Microcontrollers                                                                              | 86  |

|    |       | 8.3.3 Finite Field Operations                                                                       | 87  |

|    |       | 8.3.4 Results for the Assembly Optimized Field Operations .                                         | 89  |

|    | 8.4   | Results and Analysis of Constant-Time Implementations                                               | 89  |

|    | 8.5   | Implementation Security                                                                             | 92  |

|    |       | 8.5.1 Randomized Projective Coordinates to Thwart DPA .                                             | 92  |

|    | 8.6   | Conclusions                                                                                         | 94  |

| 9  | Con   | clusions                                                                                            | 97  |

| Bi | bliog | graphy                                                                                              | 101 |

|    | C     | · • •                                                                                               |     |

CONTENTS

Х

# Nomenclature

### Abbreviations

| ASIC                           | Application-specific integrated circuit                                                            |

|--------------------------------|----------------------------------------------------------------------------------------------------|

| CC                             | Cycle count                                                                                        |

| DH                             | Diffie-Hellman                                                                                     |

| DLP                            | Disrete logarithm problem                                                                          |

| DPA                            | Differential power analysis                                                                        |

| DSP                            | Digital signal processing                                                                          |

| ECC                            | Elliptic curve cryptography                                                                        |

| ECDH                           | Elliptic curve Diffie-Hellman                                                                      |

| ECDLP                          | Elliptic curve discrete logarithm problem                                                          |

|                                |                                                                                                    |

| EM                             | Electromagnetic                                                                                    |

| EM<br>FA                       | Electromagnetic<br>Full adder                                                                      |

|                                |                                                                                                    |

| FA                             | Full adder                                                                                         |

| FA<br>HA                       | Full adder<br>Half adder                                                                           |

| FA<br>HA<br>HECC               | Full adder<br>Half adder<br>Hyperelliptic curve cryptography                                       |

| FA<br>HA<br>HECC<br>IoT        | Full adder<br>Half adder<br>Hyperelliptic curve cryptography<br>Internet of Things                 |

| FA<br>HA<br>HECC<br>IoT<br>LUT | Full adder<br>Half adder<br>Hyperelliptic curve cryptography<br>Internet of Things<br>Lookup table |

| RCA                         | Ripple-carry adder                              |

|-----------------------------|-------------------------------------------------|

| ROM                         | Read-only memory                                |

| RSA                         | Rivest Shamir Adleman                           |

| SIDH                        | Supersingular isogeny Diffie-Hellman            |

| SoC                         | System on chip                                  |

| TP                          | Throughput                                      |

| VLSI                        | Very-large-scale integration                    |

| Mathematica                 | l symbols                                       |

| [k]P                        | Scalar multiplication                           |

| $\infty$                    | Point-at-infinity                               |

| $\kappa(P)$                 | Image of $P$ on $\mathcal{K}$                   |

| $\langle P \rangle$         | Linear combination of point $P$                 |

| k                           | Bit length of positive integer $k$              |

| $\mathbb{F}$                | Finite field                                    |

| $\mathbb{F}_p$              | Prime field                                     |

| $\mathbb{P}$                | Projective space                                |

| С                           | General hyperelliptic curve                     |

| ${\cal H}$                  | Hadamard transform                              |

| $\mathcal{J}_{\mathcal{C}}$ | Jacobian associated with curve ${\cal C}$       |

| $\mathcal{K}_{\mathcal{C}}$ | Kummer surface associated with curve ${\cal C}$ |

| $\mathcal{O}$               | Identity element                                |

| $\overline{P}$ or $-P$      | Point opposite to $P$                           |

| $\phi$                      | Isogeny                                         |

| D                           | Divisor                                         |

| $D_1 \oplus D_2$            | Addition of two divisors $D_1, D_2$             |

|                             |                                                 |

xii

### NOMENCLATURE

| E            | Elliptic curve                                       |

|--------------|------------------------------------------------------|

| $E[\ell]$    | $\ell\text{-torsion}$ subgroup of elliptic curve $E$ |

| $G \cong H$  | Group $G$ is isomorphic to group $H$                 |

| $G \times H$ | Direct sum of two groups $G, H$                      |

| K            | Field                                                |

| $M_p$        | Mersenne prime                                       |

| N            | Multiplier width                                     |

| 0            | Big $O$ notation                                     |

| Р            | Point on elliptic curve or partial-product           |

| p            | Prime number                                         |

| x(P)         | x-coordinate of point $P$                            |

| А            | Modular addition                                     |

| Ι            | Modular inversion                                    |

| М            | Modular multiplication                               |

| $M_{c}$      | Constant modular multiplication                      |

| S            | Modular Squaring                                     |

| Z            | Modular subtraction                                  |

### NOMENCLATURE

xiv

# List of Figures

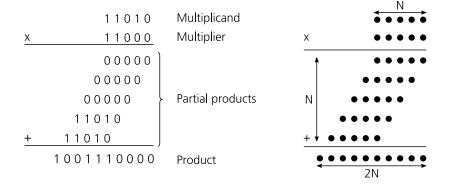

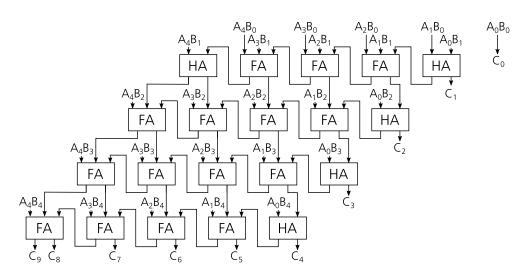

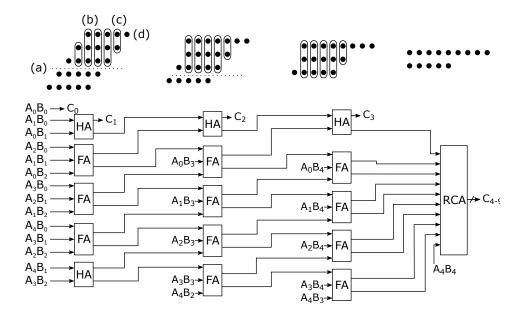

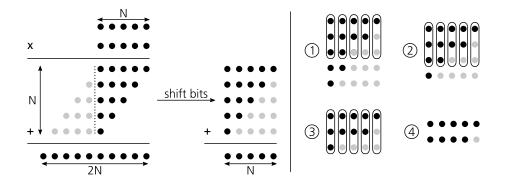

| Right: Corresponding dot-representation.112.2Architecture of a hybrid 5-bit array multiplier.122.3Constructing a 5-bit Wallace tree multiplier. Explanation of<br>(a), (b), (c), and (d) is found below.132.4Wallace tree construction for a 5-bit multiplication combined<br>with Crandall's reduction method.132.4Wallace tree construction for a 5-bit multiplication combined<br>with Crandall's reduction method.132.5Multiplication with asymmetric tiling [1].172.6Diagonal grouping for reducing the adder tree depth [1].182.7Adder tree optimized towards high-performance. Left: Digit-<br>products generated for $m = 4$ , $n = 2$ and $M_7 = 2^7 - 1$ . Right:<br>Rearranged sliced digit-products to partial-products with<br>combined fast reduction.202.8Hardware architecture of high-performance modular multiplier<br>using optimized adder tree.223.1ECC group law on $E: y^2 = x^3 - x + 1$ over the field $\mathbb{R}$ . Left:<br>Point addition. Right: Point doubling.304.1X25519 architecture, which contains all control and datapath<br>logic for computing Algorithm 5 (x25519_ladder).405.1Left: Group operation for an elliptic curve using the chord-<br>and-tangent rule. Right: Illustrating how the chord-and-<br>tangent rule is ineffective for a genus-2 hyperelliptic curve.465.2Group law for a genus-2 hyperelliptic curve over $\mathbb{R}$ .505.3Formulas for differential addition and doubling on the fast<br>Kummer surface.536.1Single-core architecture, which contains all control and data-<br>path logic for computing Algorithm 8 (sc | 2.1 | Left: Schoolbook multiplication as 5-bit binary multiplication.             |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------|----|

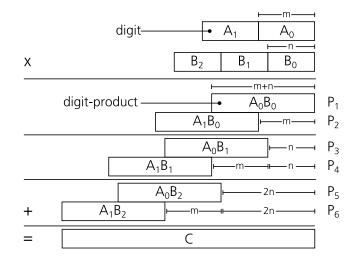

| <ul> <li>2.3 Constructing a 5-bit Wallace tree multiplier. Explanation of <ul> <li>(a), (b), (c), and (d) is found below.</li> <li>2.4 Wallace tree construction for a 5-bit multiplication combined with Crandall's reduction method.</li> <li>2.5 Multiplication with asymmetric tiling [1].</li> <li>2.6 Diagonal grouping for reducing the adder tree depth [1].</li> <li>2.7 Adder tree optimized towards high-performance. Left: Digit- products generated for m = 4, n = 2 and M<sub>7</sub> = 2<sup>7</sup> - 1. Right: Rearranged sliced digit-products to partial-products with combined fast reduction.</li> <li>20</li> <li>2.8 Hardware architecture of high-performance modular multiplier using optimized adder tree.</li> <li>22</li> <li>3.1 ECC group law on E : y<sup>2</sup> = x<sup>3</sup> - x + 1 over the field R. Left: Point addition. Right: Point doubling.</li> <li>30</li> <li>4.1 X25519 architecture, which contains all control and datapath logic for computing Algorithm 5 (x25519_ladder).</li> <li>40</li> <li>5.1 Left: Group operation for an elliptic curve using the chord- and-tangent rule. Right: Illustrating how the chord-and- tangent rule is ineffective for a genus-2 hyperelliptic curve.</li> <li>46</li> <li>5.2 Group law for a genus-2 hyperelliptic curve.</li> <li>5.3 Formulas for differential addition and doubling on the fast Kummer surface.</li> <li>5.3 Single-core architecture, which contains all control and datapath hogic for computing Algorithm 8 (scalar_mult).</li> <li>61</li> </ul></li></ul>               |     | Right: Corresponding dot-representation                                     | 11 |

| <ul> <li>(a), (b), (c), and (d) is found below</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.2 | Architecture of a hybrid 5-bit array multiplier                             | 12 |

| <ul> <li>2.4 Wallace tree construction for a 5-bit multiplication combined with Crandall's reduction method</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.3 | Constructing a 5-bit Wallace tree multiplier. Explanation of                |    |

| <ul> <li>with Crandall's reduction method</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | (a), (b), (c), and (d) is found below. $\ldots$ $\ldots$ $\ldots$           | 13 |

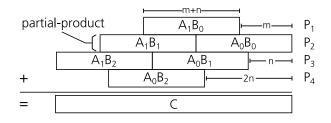

| <ul> <li>2.5 Multiplication with asymmetric tiling [1]</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2.4 | Wallace tree construction for a 5-bit multiplication combined               |    |

| <ul> <li>2.6 Diagonal grouping for reducing the adder tree depth [1] 18</li> <li>2.7 Adder tree optimized towards high-performance. Left: Digit-products generated for m = 4 , n = 2 and M<sub>7</sub> = 2<sup>7</sup> - 1. Right: Rearranged sliced digit-products to partial-products with combined fast reduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | with Crandall's reduction method                                            | 15 |

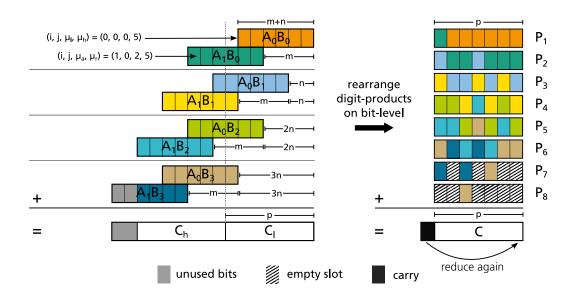

| <ul> <li>2.7 Adder tree optimized towards high-performance. Left: Digit-products generated for m = 4, n = 2 and M<sub>7</sub> = 2<sup>7</sup> − 1. Right: Rearranged sliced digit-products to partial-products with combined fast reduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.5 | Multiplication with asymmetric tiling [1]                                   | 17 |

| <ul> <li>products generated for m = 4, n = 2 and M<sub>7</sub> = 2<sup>7</sup> - 1. Right:<br/>Rearranged sliced digit-products to partial-products with<br/>combined fast reduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.6 | Diagonal grouping for reducing the adder tree depth [1]                     | 18 |

| <ul> <li>Rearranged sliced digit-products to partial-products with combined fast reduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.7 | Adder tree optimized towards high-performance. Left: Digit-                 |    |

| <ul> <li>combined fast reduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | products generated for $m = 4$ , $n = 2$ and $M_7 = 2^7 - 1$ . Right:       |    |

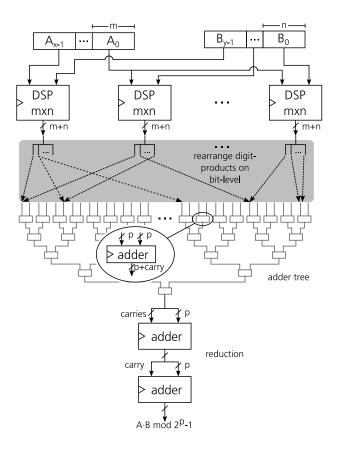

| <ul> <li>2.8 Hardware architecture of high-performance modular multiplier using optimized adder tree</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | Rearranged sliced digit-products to partial-products with                   |    |

| <ul> <li>using optimized adder tree</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |                                                                             | 20 |

| <ul> <li>3.1 ECC group law on E: y<sup>2</sup> = x<sup>3</sup> - x + 1 over the field R. Left:<br/>Point addition. Right: Point doubling</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.8 | Hardware architecture of high-performance modular multiplier                |    |

| <ul> <li>Point addition. Right: Point doubling</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | using optimized adder tree                                                  | 22 |

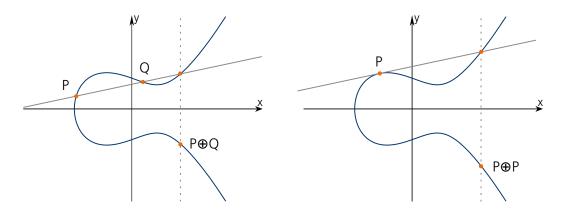

| <ul> <li>Point addition. Right: Point doubling</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21  | ECC group law on $F: u^2 = r^3$ $r + 1$ over the field $\mathbb{P}$ . Left: |    |

| <ul> <li>4.1 X25519 architecture, which contains all control and datapath logic for computing Algorithm 5 (x25519_ladder)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.1 | ·                                                                           | 30 |

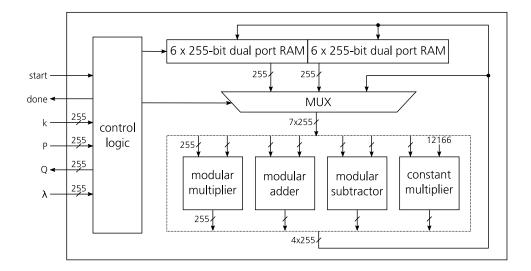

| <ul> <li>logic for computing Algorithm 5 (x25519_ladder)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | Tomt addition. Right. Fomt doubling                                         | 00 |

| <ul> <li>5.1 Left: Group operation for an elliptic curve using the chord-and-tangent rule. Right: Illustrating how the chord-and-tangent rule is ineffective for a genus-2 hyperelliptic curve</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.1 | X25519 architecture, which contains all control and datapath                |    |

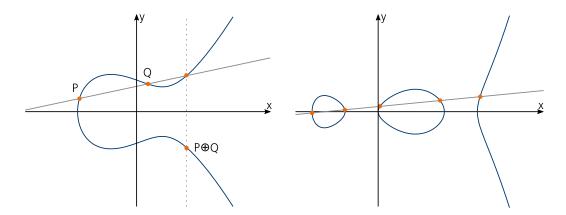

| <ul> <li>and-tangent rule. Right: Illustrating how the chord-and-tangent rule is ineffective for a genus-2 hyperelliptic curve</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | logic for computing Algorithm 5 (x25519_ladder)                             | 40 |

| <ul> <li>and-tangent rule. Right: Illustrating how the chord-and-tangent rule is ineffective for a genus-2 hyperelliptic curve</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | F 1 |                                                                             |    |

| <ul> <li>tangent rule is ineffective for a genus-2 hyperelliptic curve 46</li> <li>5.2 Group law for a genus-2 hyperelliptic curve over R 50</li> <li>5.3 Formulas for differential addition and doubling on the fast<br/>Kummer surface</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5.1 | •••••                                                                       |    |

| <ul> <li>5.2 Group law for a genus-2 hyperelliptic curve over R 50</li> <li>5.3 Formulas for differential addition and doubling on the fast<br/>Kummer surface</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | ° °                                                                         | 10 |

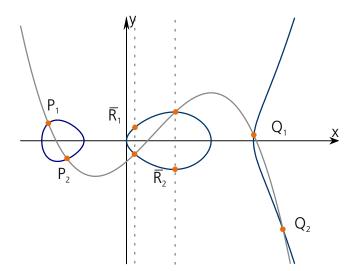

| <ul> <li>5.3 Formulas for differential addition and doubling on the fast<br/>Kummer surface.</li> <li>6.1 Single-core architecture, which contains all control and data-<br/>path logic for computing Algorithm 8 (scalar_mult).</li> <li>6.1 Single-core architecture, which contains all control and data-<br/>path logic for computing Algorithm 8 (scalar_mult).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.0 |                                                                             |    |

| <ul> <li>Kummer surface</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |                                                                             | 50 |

| 6.1 Single-core architecture, which contains all control and data-<br>path logic for computing Algorithm 8 (scalar_mult) 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.3 | 0                                                                           | 50 |

| path logic for computing Algorithm 8 (scalar_mult) 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | Kummer surface.                                                             | 53 |

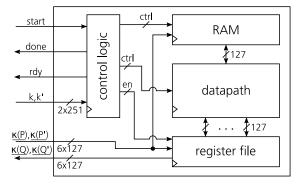

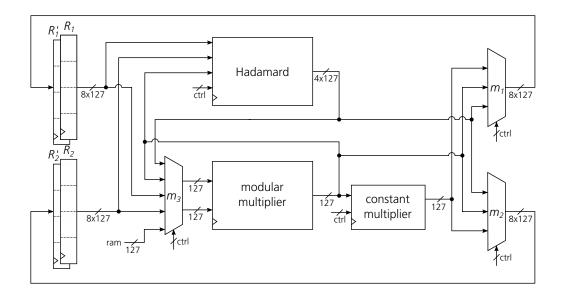

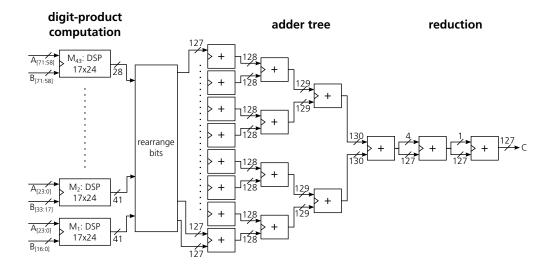

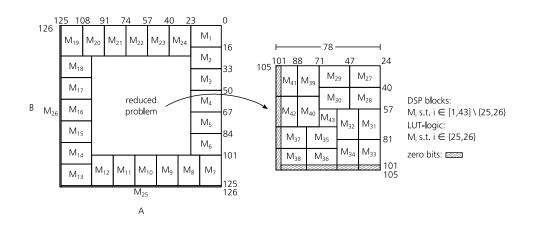

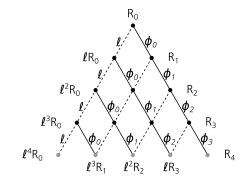

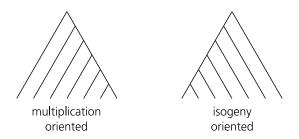

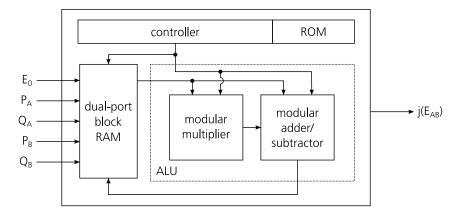

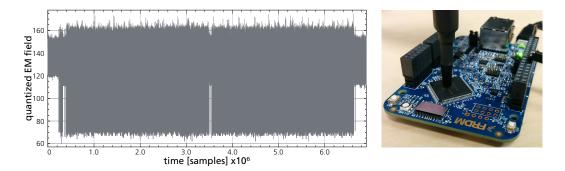

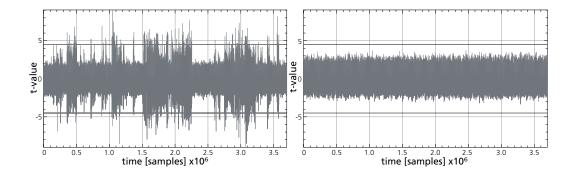

| path logic for computing Algorithm 8 (scalar_mult) 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6.1 | Single-core architecture, which contains all control and data-              |    |