## Interactive Software Parallelization Based on Hybrid Analysis and Software Architecture Reconstruction

Andreas Johannes Wilhelm

## Interactive Software Parallelization Based on Hybrid Analysis and Software Architecture Reconstruction

## Andreas Johannes Wilhelm

Vollständiger Abdruck der von der Fakultät für Informatik der Technischen Universität München zur Erlangung des akademischen Grades eines

### Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender: Prof. Dr. Bernd Brügge

#### Prüfende der Dissertation:

- 1. Prof. Dr. Hans Michael Gerndt

- 2. Prof. Dr. Felix Wolf, Technische Universität Darmstadt

Die Dissertation wurde am 15.01.2019 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 24.03.2019 angenommen.

To Rafael, Samuel, and Verena

## Zusammenfassung

Die kontinuierliche Entwicklung im Bereich moderner Mehrkernprozessoren stellt die Software Industrie vor große Herausforderungen. Es zwingt die Entwickler bestehende Anwendungen zu parallelisieren, damit sie von der zusätzlichen Leistungsfähigkeit dieser Prozessoren profitieren können. Eine solche Modifikation ist jedoch äußerst aufwendig, da industrielle Bestandssoftware in den meisten Fällen sehr umfangreich und komplex ist. Automatische Ansätze zur Parallelisierung sind hier nicht effektiv, da solche Anwendungen nur wenig reguläre Berechnungen enthalten, welche für diese Ansätze günstig sind. Manuelle Verfahren sind hingegen langwierig und fehleranfällig, da skalierbare Lösungen detailliertes Domänenwissen sowie umfangreiche Kenntnisse der zugrundeliegenden Software Architektur und dessen Verhalten voraussetzen. In dieser Arbeit stellen wir einen interaktiven Ansatz zur Identifikation möglicher Parallelität auf verschiedenen Abstraktionsebenen vor. Zur Unterstützung dieses Ansatzes haben wir Parceive implementiert, ein Werkzeug für die Analyse von Software auf Binärcode-Ebene. Parceive sammelt während der Laufzeit der Programme Daten zu deren Verhalten und kombiniert diese mit strukturellen Informationen bezüglich der zugrundeliegenden Software Architektur. Die resultierenden Modelle werden anschließend mit Hilfe mehrerer für Parallelisierung relevanter Ansichten visualisiert. Die meisten Architekturen und Implementierungen industrieller Anwendungen unterscheiden sich gravierend voneinander. Um dieser Varianz gerecht zu werden, schlagen wir außerdem eine regelbasierte Sprache vor, um verschiedene Sichten der implementierten Architektur zu rekonstruieren. Diese Technologie erlaubt Abhängigkeitsanalysen auf unterschiedlichen Granularitätsstufen zur Identifikation verschiedener Parallelisierungsmuster. Wir demonstrieren den effektiven Nutzen dieser Methoden anhand von zwei Fallbeispielen mit Software aus dem Open-Source Spektrum.

## Abstract

Continuous advances in multicore processor technology have placed immense pressure on the software industry. Developers are forced to parallelize their legacy applications to make them scalable. However, such applications are often very large and inherently complex; here, automatic parallelization methods are inappropriate and manual parallelization is tedious and error-prone. A dependable software redesign towards scalable parallelism rather requires an in-depth understanding of the problem domain, the underlying software architecture, and its dynamic behavior. We propose an interactive approach to support identification of parallelization scenarios at various levels of abstraction. Thus, we implemented Parceive, an interactive tool that operates on user applications in binary form. Parceive collects behavior information during run-time and combines it with structural information at architecture level to provide useful visualizations and analyses relative to parallelization. Industrial applications differ widely in terms of architectural and implementation styles; thus, we additionally propose a rule-based language to extract and reconstruct various views on the implemented software architecture. This enables multi-granular and iterative dependency analysis, which is crucial to identify efficient parallelization scenarios. We demonstrate the usefulness of our approach on two case studies with open source applications.

## Acknowledgments

First and foremost, I would like to thank my advisor Michael Gerndt who taught me how to do research that matters. I am indebted for his guidance and experience, for pushing me out of my comfort zone and become independent in pursuing my goals.

I would like to thank Felix Wolf for being in my dissertation committee. It is an honor to get the input and criticism of such world-class experts.

I would like to thank Tobias Schüle, my mentor at Siemens Corporate Technology, for all the advice and the support he gave me. I feel very fortunate to having worked with him and I wouldn't have gotten this far without this mentorship. Many ideas in this dissertation developed from our lengthy discussions.

All the work presented here is the result of collaboration with many incredibly bright people. I am grateful to Efe Amadasun, Samya Bagchi, Sharma Bharatkumar, Faris Čakarić, Daniel Hogrebe, Yousef Kandalaft, Ranajoy Malakar, Krishna Prasad, Victor Savu, Adriaan Schmidt, and Marcus Winter for their tenacious help with Parceive. Additionally, I would like to thank the numerous great students who participated in our Parallel Programming classes. They helped me to realize the central issues of parallel programming and to shape effective tools to tackle them.

My PhD experience was defined by the interactions I had with the phenomenal team in the Chair of Computer Architecture and Parallel Systems. I am truly grateful to Andreas Hollmann, Madhura Kumaraswamy, Robert Mijaković, Yury Oleynik, Amir Raoofy, Josef Weidendorfer, and Dai Yang for the inspiring moments and making the Chair a fun place to be.

I thank Siemens for generously supporting my research and their important financial support. I thank TUM for providing me a unique working environment and unparalleled resources to pursue my work.

## Contents

| 1 | Intr | oduction 1                                        |

|---|------|---------------------------------------------------|

|   | 1.1  | Motivation                                        |

|   | 1.2  | Contributions                                     |

|   | 1.3  | Structure of the Dissertation                     |

| 2 | Bacl | kground and Related Work 5                        |

|   | 2.1  | Introduction                                      |

|   | 2.2  | Interactive Parallelization                       |

|   |      | 2.2.1 Vocabulary and Notations                    |

|   |      | 2.2.2 Pattern-based Parallelization               |

|   | 2.3  | Tools for Dynamic Parallelism Discovery 13        |

|   |      | 2.3.1 Automatic Parallelism Discovery Tools       |

|   |      | 2.3.2 Tools for Assisting Parallelism Discovery   |

|   |      | 2.3.3 Summary                                     |

|   | 2.4  | Software Architecture Reconstruction              |

|   |      | 2.4.1 SAR Processes                               |

|   |      | 2.4.2 Techniques                                  |

|   |      | 2.4.3 Software Architecture Visualization         |

|   | 2.5  | Related Tools for SAR                             |

|   |      | 2.5.1 Exploratory SAR Tools                       |

|   |      | 2.5.2 Dynamic SAR Tools                           |

|   | 2.6  | Conclusion                                        |

| • |      |                                                   |

| 3 |      | oroach 30                                         |

|   | 3.1  | Introduction                                      |

|   | 3.2  | Software Architecture Reconstruction              |

|   |      | 3.2.1 Binary Relational Algebra 32                |

|   |      | 3.2.2 Formalization of Software Architectures     |

|   |      | 3.2.3 Rules for SAR                               |

|   |      | 3.2.4 Our SAR Language                            |

|   | 3.3  | Interactive Software Parallelization              |

|   |      | 3.3.1 Finding Concurrency                         |

|   |      | 3.3.2 Finding Concurrency with Parceive           |

|   |      | 3.3.3 Validate and Refine Scenarios               |

|   |      | 3.3.4 Validate and Refine Scenarios with Parceive |

|   |      | 3.3.5 Restructuring                               |

|   |      | 3.3.6 Parallelization                             |

|   |      | 3.3.7 Validate, Verify, and Profile               |

|   | 3.4        | Conclusion                                 | 60       |

|---|------------|--------------------------------------------|----------|

| 4 | Desi       | n and Implementation of Parceive           | 61       |

|   | 4.1        | Introduction                               | 61       |

|   | 4.2        | Design Overview                            | 62       |

|   | 4.3        | Requirements                               | 63       |

|   |            | 4.3.1 Functional Requirements              | 63       |

|   |            | 4.3.2 Non-functional Requirements          | 64       |

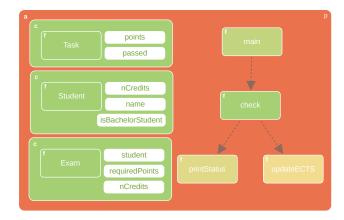

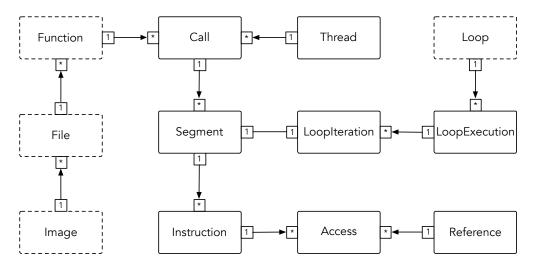

|   | 4.4        | Meta Model                                 | 64       |

|   |            | 4.4.1 Overview                             | 64       |

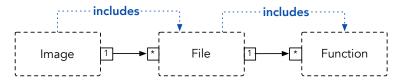

|   |            | 4.4.2 Image Files                          | 65       |

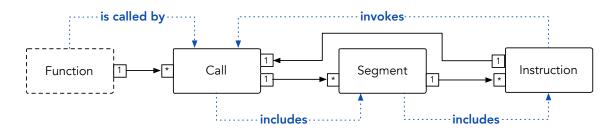

|   |            | 4.4.3 Function Calls                       | 65       |

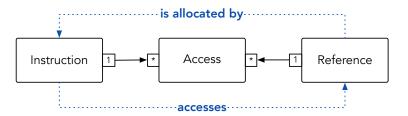

|   |            | 4.4.4 Memory Accesses                      | 66       |

|   |            | 4.4.5 Threads and Processes                | 67       |

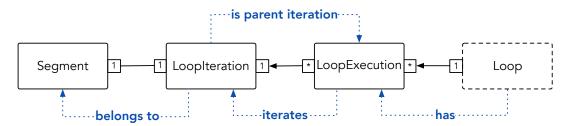

|   |            | 4.4.6 Loops                                | 67       |

|   | 4.5        | Backend                                    | 67       |

|   |            | 4.5.1 Design                               | 68       |

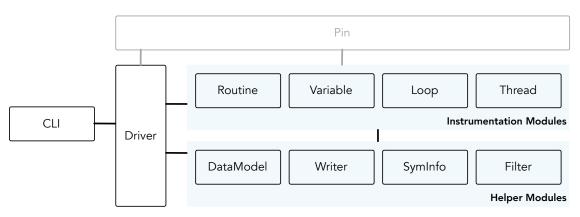

|   |            | 4.5.2 Instrumentation Modules              | 69       |

|   |            | 4.5.3 Helper Modules                       | 71       |

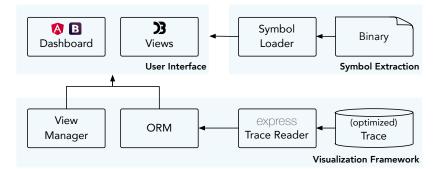

|   | 4.6        | Frontend                                   | 72       |

|   | 4.0        | 4.6.1 Dashboard                            | 72       |

|   |            | 4.6.2 Visualization Infrastructure         | 74       |

|   |            | 4.6.3         Views                        | 75       |

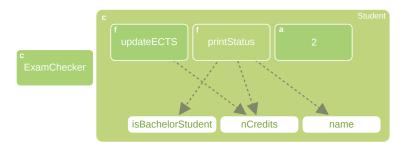

|   | 4.7        | Software Architecture Reconstruction       | 78       |

|   | 4./        | 4.7.1 Overview                             | 78       |

|   |            | 4.7.2 Parser                               | 78<br>79 |

|   |            |                                            | 81       |

|   | 4.8        |                                            | 83       |

|   | 4.0        | Conclusion                                 | 83       |

| 5 | Case       | Studies                                    | 84       |

|   | 5.1        | WMSim                                      | 84       |

|   |            | 5.1.1 Justifying Parallelization Potential | 87       |

|   |            | 5.1.2 Partitioning                         | 87       |

|   |            | 5.1.3 Validation and Redefinition          | 90       |

|   |            | 5.1.4 Restructuring                        | 95       |

|   |            | 5.1.5 Parallelization                      | 97       |

|   |            | 5.1.6 Discussion                           | 98       |

|   | 5.2        | CPPCheck                                   | 99       |

|   |            | 5.2.1 Overview                             | 99       |

|   |            | 5.2.2 Partitioning                         | 100      |

|   |            | 5.2.3 Validation                           |          |

|   |            | 5.2.4 Redefinition                         |          |

|   |            | 5.2.5 Discussion                           |          |

| _ | <i>_</i> . |                                            |          |

| 6 |            |                                            | 105      |

|   | 6.1        |                                            |          |

|   | 6.2        | Future Directions                          | 106      |

# List of Figures

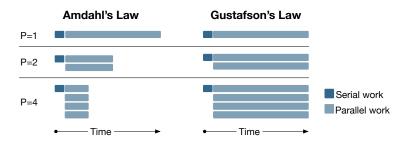

| 2.1  | Conceptual comparison of Amdahl's law (left) and Gustafson's law (right).                    | 8  |

|------|----------------------------------------------------------------------------------------------|----|

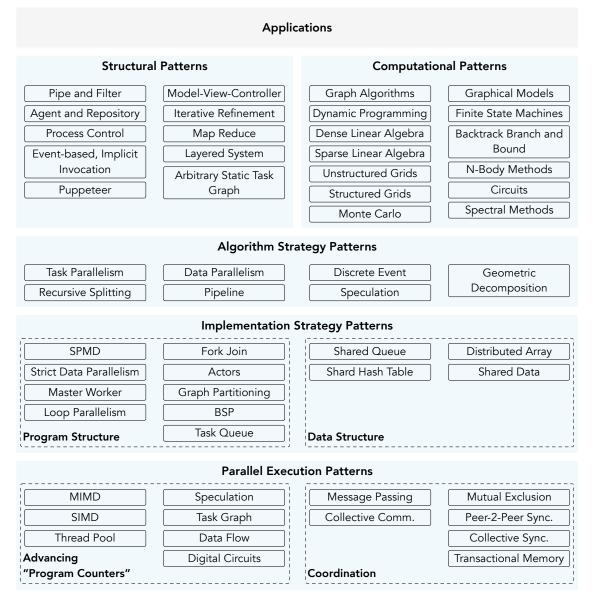

| 2.2  | Parallel patterns language OPL [1]                                                           | 10 |

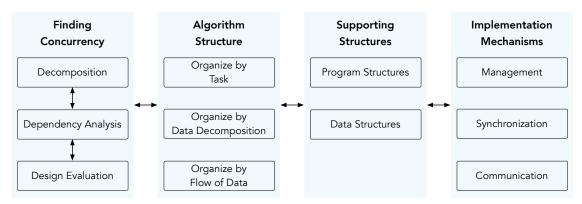

| 2.3  | Design spaces of the PLPP pattern language [87].                                             | 12 |

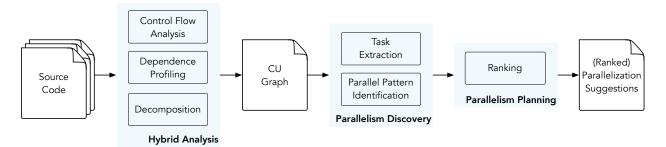

| 2.4  | DiscoPoP's workflow for parallelism discovery [75, 64].                                      | 14 |

| 2.5  | Kremlin's workflow for parallelism discovery [43].                                           | 15 |

| 2.6  | SLX's workflow for parallelism discovery.                                                    | 15 |

| 2.7  | Major components of the SUIF Explorer [76]                                                   | 16 |

| 2.8  | Parallelization workflow of the Intel <sup>®</sup> Threading Advisor [27]                    | 17 |

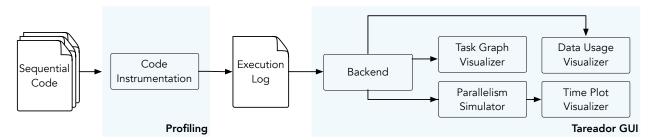

| 2.9  | Tareador's workflow for interactive parallelization [8].                                     | 18 |

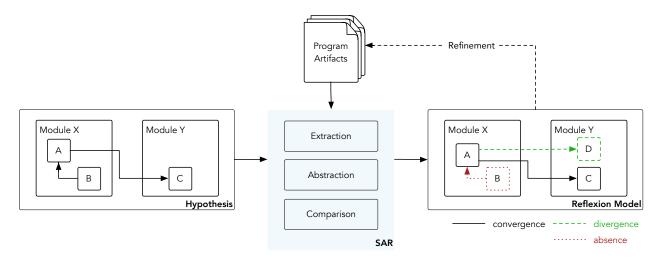

| 2.10 | The Reflexion Model, a top-down process for SAR.                                             | 21 |

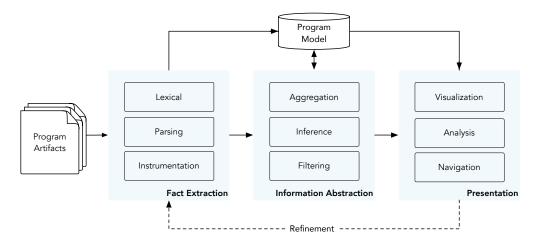

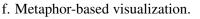

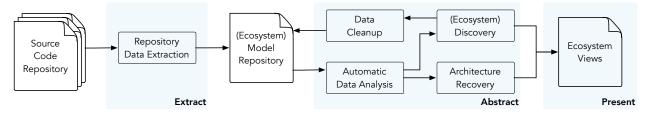

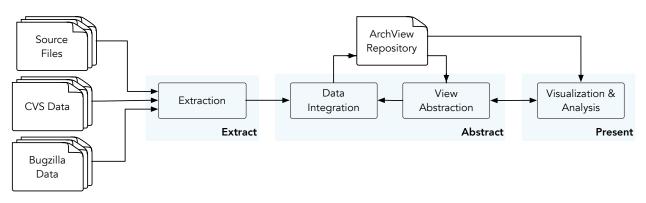

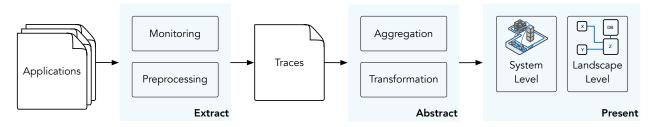

| 2.11 | The extract-abstract-present process of SAR approaches.                                      | 21 |

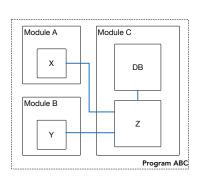

| 2.12 | Software architecture visualizations of a simple software system.                            | 24 |

| 2.13 | Softwarenaut's process for reverse engineering [80]                                          | 26 |

|      | ArchView's process for reverse engineering [40].                                             |    |

| 2.15 | Nimeta's process for reverse engineering [102].                                              | 27 |

| 2.16 | ExplorViz's process for reverse engineering [36].                                            | 28 |

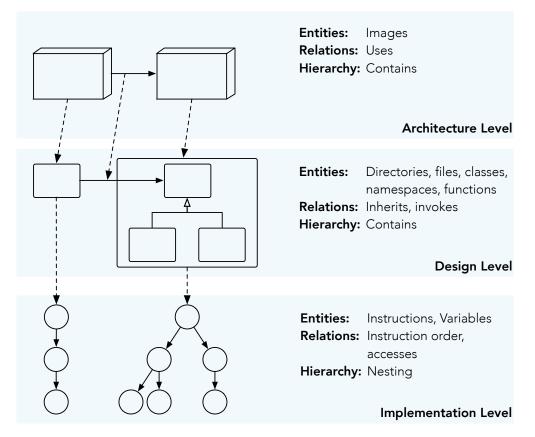

| 3.1  | Abstraction levels with corresponding entity and relation types. Dotted arrows indicate map- |    |

|      | pings between entities and relations from different abstraction levels                       | 32 |

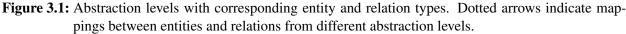

| 3.2  | An example for a typed graph represented as containment tree [58]                            | 35 |

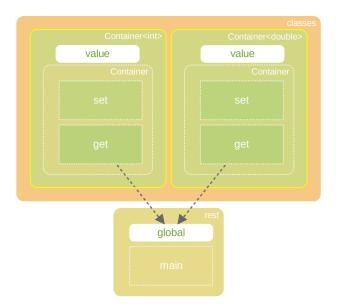

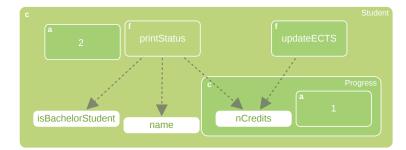

| 3.3  | Architecture View showing artifact nodes and memory accesses of the global variable          | 42 |

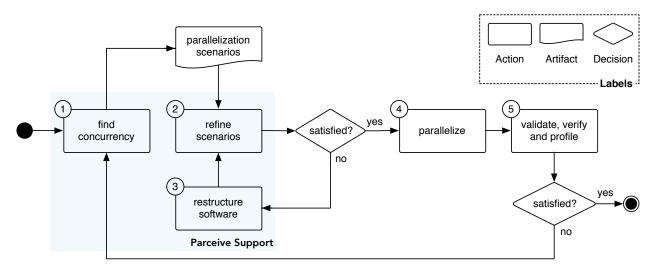

| 3.4  | Our proposed parallelization methodology comprising five steps                               | 43 |

| 3.5  | The finding concurrency step of our approach.                                                | 44 |

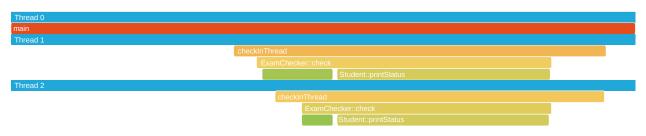

| 3.6  | The Trace View showing call nodes and a loop of a small example in a timeline                | 46 |

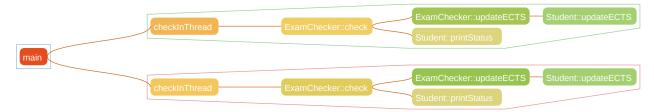

| 3.7  | The CCT View showing the example from Figure 3.6                                             | 47 |

| 3.8  | The Architecture View showing the artifacts of an extracted architecture                     | 48 |

| 3.9  | The refinement step of our approach for parallelization scenarios                            | 49 |

| 3.10 | The CCT View after applying a multi-level dependency analysis on three call nodes            | 50 |

| 3.11 | The Architecture View showing function call relationships as edges                           | 51 |

|      | Architecture View for the example from Listing 1                                             | 54 |

|      | Architecture View for the example from Listing 2                                             |    |

| 3.14 | The Architecture View for the example from Listing 3                                         | 57 |

| 3.15 | The Architecture View for the example from Listing 4                                         | 58 |

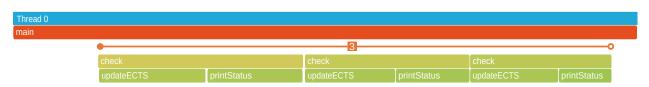

| 3.16 | Trace View showing a multi-threaded program.                                                 | 59 |

| 3.17 | Trace View showing a multi-threaded program.                                                 | 60 |

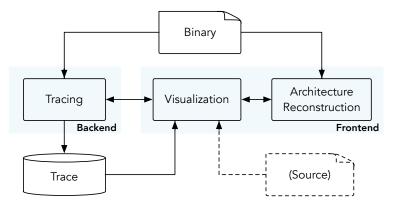

| 4.1  | Parceive's typical workflow.                                                                 | 62 |

| 4.2  | Main components of Parceive.                                                                 | 62 |

| 4.3  | Parceive's meta model including entity tables as nodes and relations as edges                | 65 |

| 4.4  | Excerpt of Parceive's meta model for capturing images.                                         | 65  |

|------|------------------------------------------------------------------------------------------------|-----|

| 4.5  | Excerpt of Parceive's meta model for capturing function calls.                                 | 66  |

| 4.6  | Excerpt of Parceive's meta model for capturing memory accesses.                                | 66  |

| 4.7  | Excerpt of Parceive's meta model for capturing threads and processes.                          | 67  |

| 4.8  | Excerpt of Parceive's meta model for capturing loops.                                          | 67  |

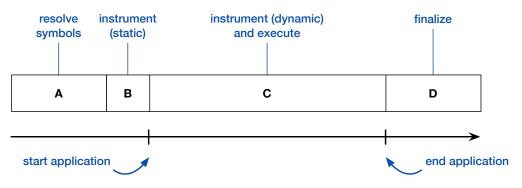

| 4.9  | Analysis phases of Parceive's backend.                                                         | 68  |

| 4.10 | Parceive's backend architecture.                                                               | 69  |

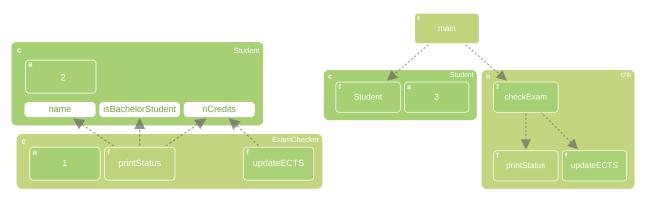

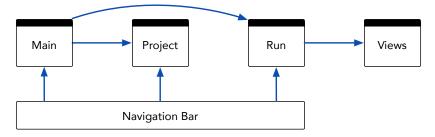

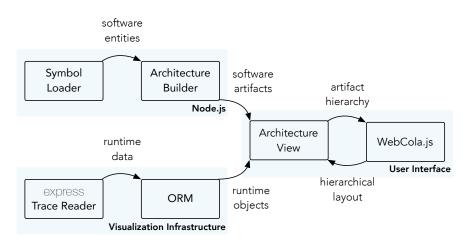

| 4.11 | Software architecture of Parceive's frontend component.                                        | 72  |

| 4.12 | Dialogues (rectangles) and interactions (edges) of Parceive's dashboard                        | 73  |

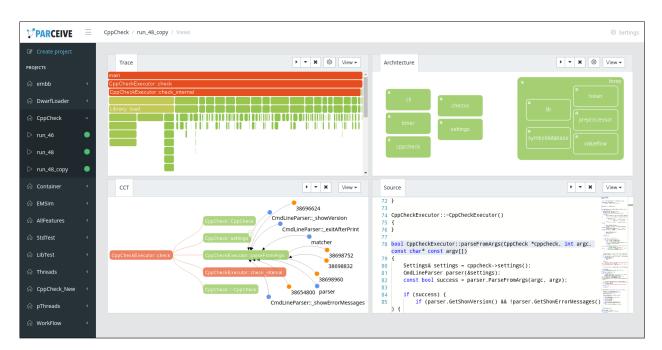

| 4.13 | Parceive's dashboard with four active visualizations: (top left) Trace View; (top right) Ar-   |     |

|      | chitecture View; (bottom left) CCT View; and (bottom right) Source Code View                   | 74  |

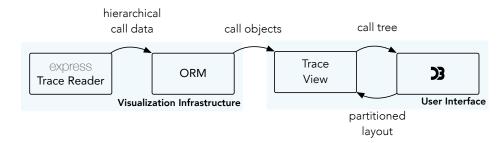

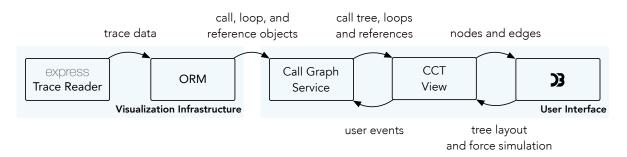

|      | Data flow for Parceive's Trace View.                                                           | 76  |

| 4.15 | Data flow for Parceive's CCT View.                                                             | 76  |

|      | Data flow for Parceive's Architecture View.                                                    | 77  |

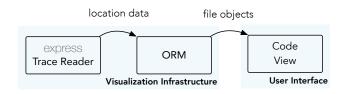

| 4.17 | Data flow for Parceive's Source View.                                                          | 78  |

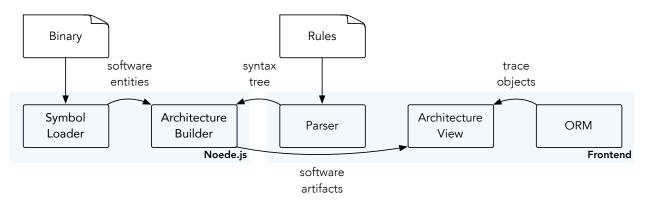

| 4.18 | Data flow for Parceive's SAR process.                                                          | 78  |

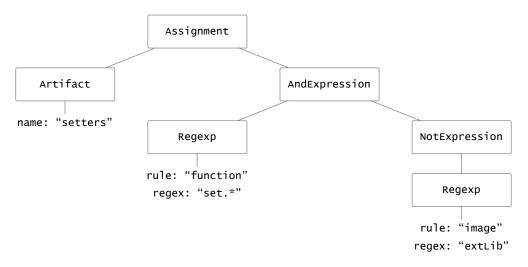

| 4.19 | <pre>Syntax tree for the rule setters := function("set.*") &amp;&amp; !image("extLib")</pre>   | 81  |

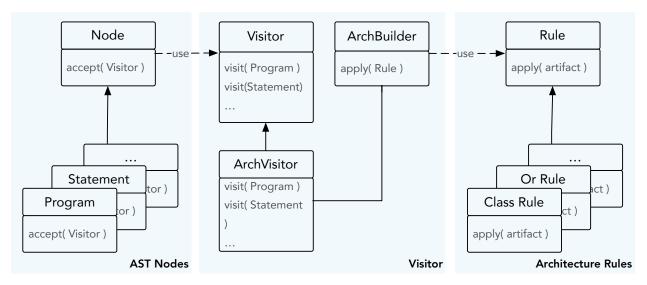

| 4.20 | Visitor pattern used for Parceive's SAR approach.                                              | 82  |

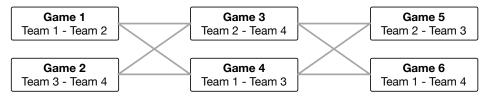

| 5.1  | Matches and dependencies of the soccer World Cup's group stage                                 | 85  |

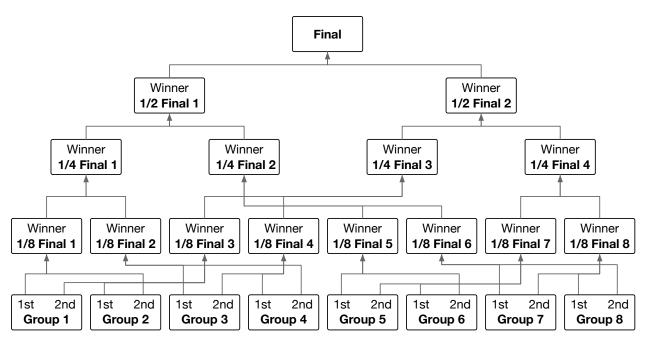

| 5.2  | The knockout stage of the 2018's soccer World Cup.                                             | 86  |

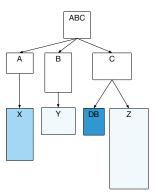

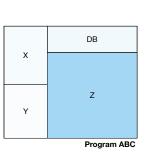

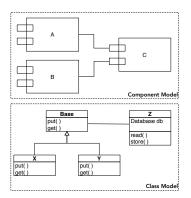

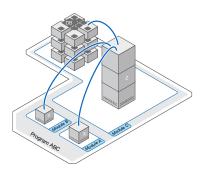

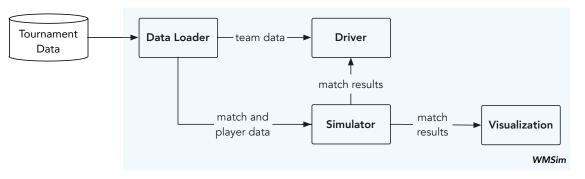

| 5.3  | The software architecture of WMSim                                                             |     |

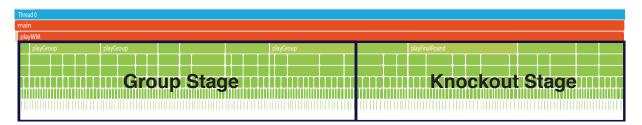

| 5.4  | Parceive's Trace View for a traced execution of WMSim.                                         | 87  |

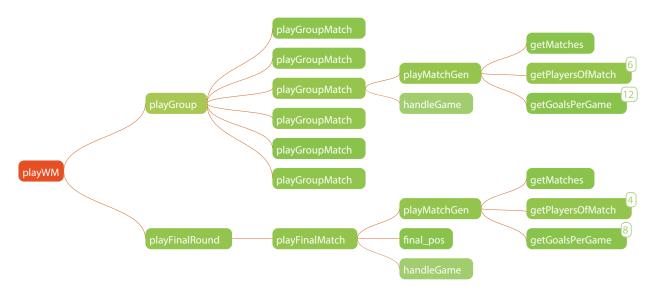

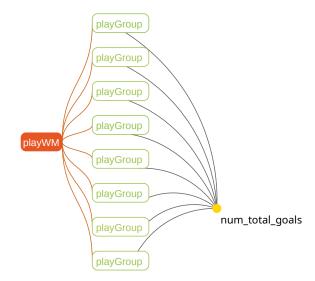

| 5.5  | Parceive's CCT View showing the top of WMSim's function call hierarchy.                        | 88  |

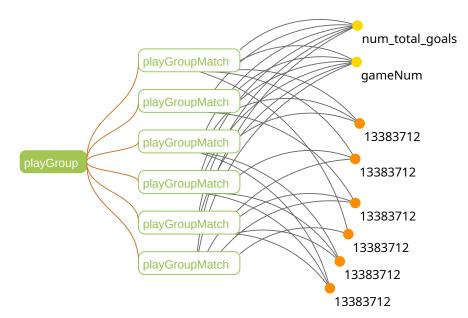

| 5.6  | Parceive's CCT View showing more details of WMSim's function call hierarchy.                   | 89  |

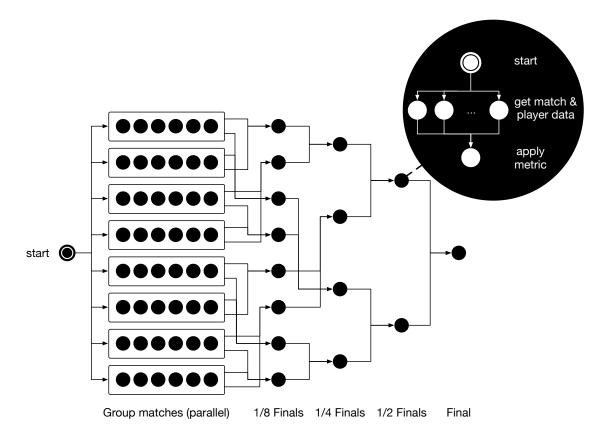

| 5.7  | The task graph for WMSim's match simulation, as proposed by scenario S3                        | 91  |

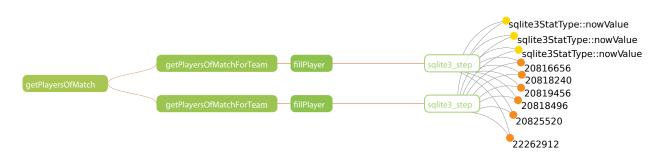

| 5.8  | Parceive's CCT View showing data dependencies between sqlite3 library calls                    | 92  |

| 5.9  | Parceive's CCT View shows common data accesses between calls of playGroup                      | 92  |

| 5.10 | Parceive's CCT View shows common data accesses between function calls of playFinalMatch.       | 93  |

|      | CCT View showing common data accesses between calls of function $playGroupMatch.$              | 95  |

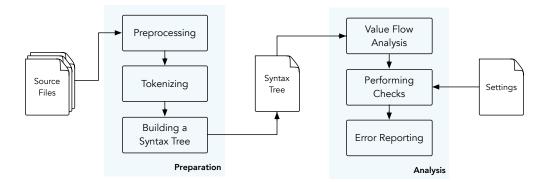

|      | CppCheck's workflow for static analysis                                                        |     |

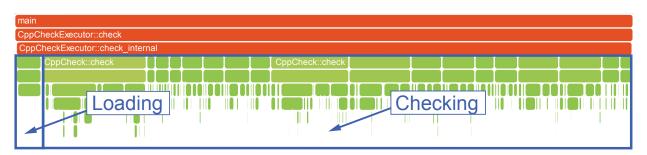

|      | Performance View showing hierarchical nodes to represent function executions                   |     |

|      | CCT View showing a calling context tree and accesses to shared memory locations                | 102 |

| 5.15 | Parceive's Architecture View (excerpt) that shows the library artifact, inheritances relations |     |

|      | (solid arrows), and memory accesses (dashed arrows) for an execution of CppCheck               | 103 |

# List of Listings

| 1 | Example code for the <i>extract function</i> refactoring                             | 54 |

|---|--------------------------------------------------------------------------------------|----|

| 2 | Examples for the <i>combine functions to class / namespace</i> refactorings          | 55 |

| 3 | Example for the <i>move function</i> refactoring                                     | 56 |

| 4 | Example for the <i>move function</i> refactoring                                     | 57 |

| 5 | The calls of function playGroup within a loop                                        | 88 |

| 6 | The function calls of playFinalMatch for every final stage                           | 93 |

| 7 | Excerpt of the playGroupMatch function that simulates matches during the group stage | 94 |

| 8 | The <i>extract function</i> refactoring for WMSim.                                   | 96 |

## Introduction

"Forget for a while about computers and computer programming, and think instead about objects in the world around us, which act and interact with us and with each other in accordance with some characteristic pattern of behavior."

- C.A.R. Hoare

## **1.1 Motivation**

Stunning advances in information technology transformed how we work and live. The rapid growth in computer performance enables applications that where unthinkable roughly 70 years ago when the first general-purpose computer was built. Face recognition, natural language processing, or self-driving cars are examples for the computational capability of today's systems. Much of this progress was achieved in the last two decades of the 20th century when single-processor performance improved by a factor of 10,000 - an annual rate of over 50% [55]. That growth stemmed from steadily increasing the number and speed of transistors on a processor chip by shrinking their size. Most programmers have enjoyed the regular performance boost and added further levels of abstraction while preserving a sequential programming model.

The situation has changed since the early 21st century when transistor sizes reached dimensions that hit fundamental limits of power efficiency [31]. As a consequence, the microprocessor industry was forced to use multiple efficient processor cores instead of single inefficient processors. That change in hardware shifted the responsibility of ever-increasing performance characteristics to the programmers. They must design their applications using parallel programming models to fully utilize the potential of multicore processors. The increasingly slowing of *Moore's Law* in recent years further strengthened the need for more software parallelism. To satisfy performance expectations for next-generation applications, new types of heterogeneous architectures and domain-specific processing units appeared [55]. This trend results in computer systems that are naturally parallel; consequently, this must also hold for the programs running on those systems.

Unfortunately, parallel programming is notoriously tedious and error-prone. Despite having a plethora of existing parallel programming models and languages, only few programmers can realize the full power of

parallelism; most programmers only achieve a small fraction of the potential performance gains [104]. The difficulties are related to the inherent complexity of parallel programming and the lack of appropriate tools. The main complexity arises from programmer's experience with sequential problem solving. For decades, professionals were trained to create algorithms built upon consecutive and deterministic instructions. However, designing efficient programs requires parallel thinking that accepts the concurrent, non-deterministic nature of computational problems. The programmer's task is to structure programs with concurrent elements that may operate simultaneously. What is needed - besides education - are appropriate tools to support with parallel thinking by facilitating program comprehension and discovery of parallelization opportunities.

Parallelization of existing legacy software adds an extra level of complexity. Besides concurrency issues, programmers must cope with large and unfamiliar code bases with no or obsolete documentation, missing tests, and situations where software architects have left the company. Typically, industrial applications comprise various components at different levels of abstraction that heavily interact with each other. Examples are client-server applications that process numerous simultaneous requests. These applications usually contain database managers, message queues, central logging facilities, and actual business logic. To exploit parallelism and achieve good scalability, those components must concurrently interact with each other. However, necessary restructuring requires a solid understanding of the problem domain, the overall software architecture, and inherent dependencies at implementation level. Consequently, parallelization of industrial applications is very time-consuming and complicated. Increasing the effectiveness of this process is inevitable for ensuring sustainable software systems. For that purpose, programmers depend upon tools to make informed design decisions about program parallelization.

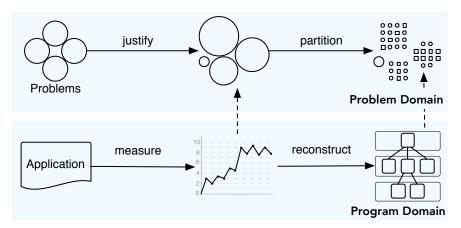

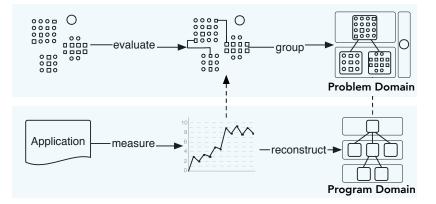

While some parallelization tools address parallelism discovery, they are rarely designed to analyze architectural aspects of software. This makes their findings hard to understand and less expressive as the used abstractions do not conform with the programmer's mental models. Furthermore, their basic assumption - that substantial parallelism can be recovered from serial implementations - does not generally hold. Solutions designed with the sequential programming model in mind may not provide enough concurrency for efficient parallelism. On the other hand, tools for software architecture reconstruction disclose program structures at high levels of abstraction but rarely combine the resulting models with behavioral information relevant for parallelization. Additionally, those tools are known to suffer from significant inaccuracies, mainly caused by two challenges: first, there is no construct in any major programming language to express architectural elements (e.g., "layer" or "component"). Second, the great diversity of implementation and architectural styles in real-world applications requires sophisticated analyses. In conclusion, there is a serious abstraction gap between the problem and program domain, and existing tools for supporting programmers with parallelization.

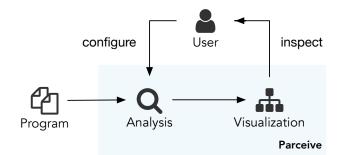

In this thesis we propose a tool-based approach for interactive software parallelization. Its objective is to improve programmer's software comprehension, which is required to identify possible parallelization opportunities. The proposed tool collects information about program behavior during run-time and combines it with software architecture information. The user provides a set of architecture rules to automatically extract and recover architectural elements at different levels of abstraction. Analysis results are then used to provide effective visualizations and analyses that facilitate parallel computational thinking. The resulting parallelization scenarios represent a blueprint for potential software restructurings.

## **1.2 Contributions**

The contributions of this thesis can be classified into three categories: methods and techniques, tools, and case studies.

#### **Methods and Techniques**

- *Defining the abstraction gap problem* of existing tools for parallelism discovery that operate on diverging abstractions relative to the programmer's mental models.

- *Providing a methodology for interactive parallelization* based on an iterative, pattern-based approach. The methodology emphasizes the importance of analyses and scenarios at different levels of granularity [124].

- *Specifying a meta model for hybrid analysis* to enable precise and versatile execution traces optimized for efficient analysis queries. The meta model is tailored towards data dependency analysis at different levels, ranging from single instructions to architectural elements [124].

#### **Case Studies**

• *Presenting two programs as case studies.* The first case study originates in our institute and exemplifies all steps of our approach on a small but for this format manageable scale. The second case study is a medium-size open source application that shows the practical characteristics of our tool-based approach, such as scalability.

#### Tools

- *Parceive* is a parallelization tool that supports dependency analyses at different granularity through visualization and exploration. We integrated the aforementioned techniques into Parceive and validated them with case studies from open source projects and software systems from our industry partner Siemens.

- A visualization framework for parallelization to provide a common interface for accessing large trace files and support a wide variety of visualizations. The framework includes various optimization and abstraction techniques to ensure responsiveness and scalability, e.g., on-demand loading, caching, or interactions across visualizations [123].

- A technique for semi-automatic extraction of architectural representations from existing software systems. The technique is based on a new language for specifying architectural rules to steer the extraction process and provide effective filter mechanisms for run-time tracing [122].

## **1.3 Structure of the Dissertation**

This dissertation illustrates software architecture analysis for parallelization by proposing guidelines for a pattern-oriented approach and using them to design and evaluate an interactive parallelization tool, called Parceive. The remainder is structured as follows.

- **Chapter 2** presents an overview of related work in interactive software parallelization. Although we are not aware of work that treats software architecture as first class entity for parallelization, our approach is closely related to parallelism discovery, software architecture reconstruction, and software visualization. The chapter surveys relevant theory and work in these areas.

- **Chapter 3** introduces our proposed pattern-based parallelization approach. We give an overview of its workflow before describing the individual steps, and how Parceive supports their typical use cases. The chapter presents our proposed language and technique for software architecture reconstruction together with decisive visualizations and analyses of the tool.

- **Chapter 4** illustrates important design decisions in Parceive's architecture and implementation. Our objective is to provide enough insights for solid reproducibility of our findings and support effective maintenance of our tool. Thus, we first describe the tool's overall software architecture and highlight essential interactions between major components. Then, we provide more details of the backend, frontend, and the component for software architecture reconstruction, respectively.

- **Chapter 5** introduces two case studies for interactive parallelization of sequential programs. The first program is a soccer simulator developed at our institute. During the case study we show how Parceive provided active support with the identification and realization of parallelization scenarios. The second program is a static program analysis tool by the open source community. Here, we highlight the benefits of having dependency information at architectural levels.

- **Chapter 6** concludes our work by discussing our approach and the lessons we learned. We then present a set of research directions that are opened by this thesis.

## Background and Related Work

"If you find that you're spending almost all your time on theory, start turning some attention to practical things; it will improve your theories. If you find that you're spending almost all your time on practice, start turning some attention to theoretical things; it will improve your practice."

- Donald Ervin Knuth

## **2.1 Introduction**

The proposed tool-based approach touches a wide range of research areas, such as parallelization, software architecture reconstruction, and software visualization. We are not aware of existing approaches that cover these research areas collectively; however, several approaches share similar objectives with ours.

## 2.2 Interactive Parallelization

Parallelization is the process of transforming a sequential program to exploit parallel hardware. This process is based on the distribution of computational problems among multiple processing units, such as CPU or GPU cores. Parallelization results in a parallel program; a specification of execution units (e.g., software entities to execute instructions) that operate simultaneously and communicate among each other to solve the computational problems.

Parallelization can improve many program qualities, such as latency, throughput, or the software design. Reduced latencies lets parallel programs solve their computational problems faster than the sequential counterparts. Parallel software with increased throughput is more scalable, solves larger problems, or produces results with higher resolution. Finally, a parallel software design ideally reflects the inherent parallelism of computational problems. This helps to naturally express the behavior of a program, reduces the accidental complexity of its source code, and improves its understandability.

Unfortunately, parallelization is recognized as a tedious and error-prone activity. It requires a greater effort for the programmers, who must consider the peculiarities of parallel execution environments. Proven techniques for validation, verification, and optimizations are not directly applicable to parallel programming. These techniques depend upon deterministic program execution, which is not given with parallel execution environments. Additionally, existing issues may be exposed a long time after deployment.

Various approaches to help programmers in parallelizing applications have been proposed. For example, automatic parallelization has been considered as the silver bullet [20, 10, 126]. Automatic parallelization approaches allow programmers to use their existing sequential programming models for exploiting the benefits of modern computer architectures. To preserve application semantics, the employed analyses must make conservative decisions; thus, automatic parallelization is only applicable to small code blocks and simple loops without intricate dependencies [99]. Semi-automatic parallelization leverages the programmer's knowledge to enable additional parallelism [16, 46]. Here, user input informs the tools which dependencies can be safely ignored. Unfortunately, identifying such dependencies is not trivial and sometimes impossible without major software redesign toward concurrency. A promising alternative are interactive procedures, which give the developer full control over parallelization. Interactive parallelization essentially requires tools for parallelism discovery, i.e., tools that support programmers with identifying dependencies and estimating the efficiency of parallel software solutions.

Parallelism discovery tools rely on static and dynamic software analysis to detect problematic dependencies and estimate potential speedup. These techniques differ in the time of their data acquisition; static analysis collects information before program execution and dynamic analysis during program execution. Consequently, static methods analyze program specifications (e.g., source code) whereas dynamic analyses record run-time events (e.g., memory accesses). This implies diverging qualities of both methods. Static analyses can efficiently inspect different control flow paths but must rely on imprecise assumptions about potential program states. Those assumptions lead to false-positive results, i.e., static analysis records precise program states during execution but is limited to the traversed control flow paths. Thus, those analyses can return false-negative results, i.e., they potentially miss parallelism-inhibiting dependencies and their results must be double-checked. Our proposed tool uses a combination of static analysis (a so-called *hybrid analysis*) for parallelism discovery.

In the remainder we summarize important vocabulary and notations relative to interactive parallelization. Afterwards, we introduce generic design patterns before presenting important pattern languages for parallelization.

## 2.2.1 Vocabulary and Notations

Parallelism discovery is based on two important theories: performance estimation and dependency detection. We now provide relevant foundations used in this thesis.

### **Parallel Performance**

A main purpose of parallelization is to improve a program's performance. Two important performance aspects are *latency* and *throughput*. Latency is important for reactive systems; it describes the unit of time (e.g., execution time) that is necessary to complete a task. Throughput is the rate at which a series of tasks can be completed. It is measured as units of work per unit of time. Parallel programming can improve latency and throughput by computing sub-problems simultaneously. However, some parallel software designs improve the latency of certain computations but decrease the overall throughput, or vice versa.

Relevant performance metrics for parallelization are *speedup*, *efficiency*, and *scalability*. Speedup compares the latency of the sequential program with latencies of the parallel program computing the same problem on P processing units. Assuming  $T_0$  is the latency of the (fastest) sequential program, and  $T_P$  is the latency of the parallel program on P processing units, then:

$$S_P = \frac{T_0}{T_P}$$

(speedup)

Note that the baseline of  $S_P$  is derived from the sequential program. This is a fair method since it shows the absolute speedup by parallelization. Sometimes we are more interested in the relative speedup effects caused by synchronization, communication, or load balancing. A workable approach is to execute (or simulate) a serialization of the parallel program and use the resulting latency (denoted as  $T_1$ ) as the dividend.

Efficiency is speedup divided by the number of processing units P:

$$E_P = \frac{S_P}{P} = \frac{T_0}{PT_P}$$

(efficiency)

The efficiency of a parallel program measures its utilization of processing units. Optimal efficiency is 1 (mostly reported as 100%), where the speedup is linear to the processing units. Usually, efficiency decreases as the number or processing units increases, i.e., the speedup is sublinear. The main reason for sublinear speedup is parallelism overhead, such as task management, synchronization, or communication. Note that there can be situations that result in super-linear speedup (i.e.,  $S_P > P$  and  $E_P > 1$ ), such as beneficial cache effects (more processing units have more cache memory) or algorithms that solve inherently parallel problems more effectively.

Before starting a (complex) parallelization task, programmers must estimate the expected speedup. For a fixed problem size and a varying number of processing units P, the speedup can be computed with Amdahl's law [4]. This is sometimes called *strong scaling*. Gene Amdahl's observation was that programs usually contain inherently sequential operations that are non-parallelizable. Hence, the law separates execution time  $T_0$  into two categories: time that is spent doing serial work, and time that is spent doing parallelizable work. Assuming s is the serial fraction of  $T_0$ , then:

$$S_P \le \frac{1}{s + (1 - s)/P}$$

(Amdahl's law)

Amdahl's law has serious consequences for the efficiency of parallel algorithms. For example, assume a program that spends 90% of its execution time with perfectly parallel work. When the parallel program is executed on a system with four processing units, it runs over three times faster and has a notable efficiency of 77% (left part of Figure 2.1). But the situation gets worse when executed on systems with more parallelism. When using 32 processing units, the expected efficiency drops already below 25%. Even if we would assume infinite hardware resources, the achievable speedup is limited to 10.

Note that Amdahl's law assumes the same problem size for the sequential and the parallel program. John Gustafson noted that this assumption does not hold for more complex applications that solve increasingly larger problems [52]. Here, the parallelizable part of the problem frequently grows much faster than the serial part. With increasing work the serial fraction of the execution time gets more insignificant and the speedup raises. Assuming *s* is the serial fraction of  $T_P$ , and the problem size increases linearly with the number of processing units *P*, then:

$$S_P \le s + (1-s) * P$$

(Gustafson's law)

The resulting speedup results are sometimes called *weak scaling*. Using the same ratios as above (i.e., s = 0.1), our example program runs 3.9 times faster on a system with four processing units (right part of

Figure 2.1: Conceptual comparison of Amdahl's law (left) and Gustafson's law (right).

Figure 2.1). This is an efficiency of 98%, resulted by the four times larger (parallel) problem size. Using a parallel system with 32 processing units raises the efficiency even to 99,7%.

Both Amdahl's law and Gustafson's law are valid methods for speedup estimation. It depends on the computational problems and the input data which one is more appropriate. Unfortunately, both methods compute speedups too optimistic since they neglect any parallelism overhead. Although there are more elaborate methods to determine upper (and lower) bounds of speedup (e.g., the work-span model [15]), the presented laws suffice to identify good parallelization opportunities in most cases. We apply the methods to justify parallelization opportunities within the presented case studies (Chapter 5).

#### **Data Dependency**

A data dependency is a situation where two code regions access the same memory location. For sequential programs this is no issue; the statements are always executed in the same order, resulting in deterministic memory accesses. However, concurrent programs comprise non-deterministic memory accesses. Their order depend on the relative timing between interfering threads and differs for various program executions. Thus, data dependencies between concurrent code regions can lead to different computational results. These situations are called *race conditions* [95]. They become critical bugs when the order of execution is not intended by programmers, producing issues that are hard to reproduce and debug. Hence, knowing data dependencies is essential for parallelization. Our approach relies on a more formal definition to identify data dependencies.

Assume  $R_1$  and  $R_2$  are code regions; then,  $R_2$  depends on  $R_1$  if one or more of the following conditions hold:

| $O(R_1) \cap I(R_2) \neq \emptyset$ | (flow dependency)   |

|-------------------------------------|---------------------|

| $I(R_1) \cap O(R_2) \neq \emptyset$ | (anti dependency)   |

| $O(R_1) \cap O(R_2) \neq \emptyset$ | (output dependency) |

where:

- $I(R_i)$  is the set of memory locations read by  $R_i$ .

- $O(R_i)$  is the set of memory locations written by  $R_i$ .

- There is a feasible execution path from  $R_1$  to  $R_2$ .

These conditions are called Bernstein Conditions [13]. They essentially state that  $R_1$  and  $R_2$  can be safely executed in parallel if there is no (data) dependency between them, i.e., if

$$O(R_1) \cap I(R_2) \cup I(R_1) \cap O(R_2) \cup O(R_1) \cap O(R_2) = \emptyset$$

Note that the formalization is not limited to the granularity of code regions. The conditions can be applied to various levels of abstraction, such as single statements or whole components of the software architecture. Our approach relies on this property for analyzing data dependencies between arbitrary software elements.

The dependency types are not equally critical for concurrent programs. In case of anti and output dependencies, the second memory access is a write operation and determines the final value of the memory location. Usually, these dependencies can be resolved by memory duplication. Unfortunately, this approach is not valid in case of flow dependencies, where the second memory access reads the written value of the first memory access. These dependencies must be satisfied in concurrent programs to preserve the results.

## 2.2.2 Pattern-based Parallelization

*Design patterns* are textual representations of proven solutions for frequently occurring problems. Originally intended for civil engineering [3], design patterns enjoy great popularity in the object-oriented computing community [42, 22]. They capture expert's knowledge and vocabulary to design dependable software and foster communication among stakeholders. A typical formalism for design patterns contains six parts: a description of (1) the problem, (2) the proposed solution, (3) the problem's context, (4) relevant forces that must be considered, (5) few examples to illustrate the pattern, and (6) a final discussion that draws connections to related patterns.

A *pattern language* describes a structured collection of related design patterns. The objective is to cover a broad range of granularity levels to design complex systems. At each decision point, the designer chooses an appropriate pattern to solve a specific problem. Every design pattern can lead to other patterns at different granularity levels until reaching a final design. In retrospectives, design decisions are often obscured by complex code; pattern languages make these decisions explicit and comprehensible. Additionally, using a web of patterns facilitates communication about various levels of software design by providing a common vocabulary.

Pattern languages for parallel programming describe models on how to create parallel software designs [87, 88, 105]. They comprise patterns at different levels of abstraction, ranging from low-level algorithms to architectural patterns. Those languages aim for composable patterns to apply them at most parallelization tasks. Our tool-based approach facilitates pattern-oriented parallelization by analyses and visualizations that provide enough flexibility to consider arbitrary patterns.

Although most parallel pattern languages focus on creating parallel programs from scratch [85], their proposed patterns are equally suited for parallelization of existing software. However, there are two important differences between working on green-field projects and existing code. First, programmers who conduct parallel programming for new software mostly belong to the original development team whereas parallelization of legacy code is often done by people without detailed knowledge of important design decisions. Missing information about relevant program parts complicates the identification of the right patterns and prolongs validation processes. Second, fresh software designs can be easily adapted to new requirements and parallel computing. On the other hand, existing software architectures may not match the design of parallel patterns. Adapting these architectures often requires restructuring the software or even some tedious re-engineering.

In the remainder we introduce OPL (Our Pattern Language) [1], a pattern language that heavily influenced our approach. It focuses on important programming structures and processes for parallel programming.

### **Example: OPL**

The newest version of the OPL resulted from merging two projects: the PLPP (Pattern Language for Parallel Programming) project, which focuses on a pattern based procedure [87], and a research initiative centered at the UC Berkeley to consider the larger problem of well-engineered parallel software architectures [66].

OPL comprises 56 patterns, organized into five categories: structural, computational, algorithm strategy, implementation, and parallel execution (Figure 2.2). Each category addresses a specific level of the design problems, such that patterns from different categories can be flexibly combined. The intention is to encompass the complete parallel design of software systems, ranging from their overall organization at an architectural level to the low-level details of the parallel algorithm.

Figure 2.2: Parallel patterns language OPL [1].

1. *Structural Patterns* describe the overall structure of a program at software architecture level. Inspired by architectural styles [107, 44], those patterns define a set of high level components and their interactions. Patterns construct a supportive framework for the program's computational elements. Parallelism is not explicitly integrated into the resulting software architectures; rather, the architectures support and simplify parallelization implied by patterns from lower categories. For example, layered systems restrict interactions between specific abstraction levels, leading to software architectures that are relatively easy to understand and maintain. These qualities ease identification of appropriate com-

putational patterns and relevant dependencies. Maintainers may iteratively adjust these patterns and the layered system until a proper design is found.

- 2. Computational Patterns describe proven solutions for important computational problems. They originate from previous work that identified essential problems which benefit from parallelism [6]. Solutions for different computational problems may be composed to form structural patterns. Furthermore, computational patterns may itself comprise lower-level patterns. As with structural patterns, parallelism is not directly expressed within this category. However, the computational structure proposed by those patterns fosters essential task and data decomposition for parallel execution. This consequently requires strategy and execution patterns from OPL's lower levels. Examples are Monte Carlo simulations, which run independent experiments to statistically sample the solution space. Possible solutions build upon the structural *Map Reduce* pattern [29], where different experiments are conducted by separate tasks in the map phase and the results are accumulated in the reduce phase.

- 3. Algorithm Strategy Patterns specifies high-level strategies to solve individual computational problems. Here, the programmer's key issue is to find most appropriate parallelization strategies for the given problem and software structures. Besides efficiency, scalability, simplicity, and portability, good algorithm strategies must consider the organization of the problem, i.e., if the problem is decomposed into tasks, data, or streams of data. Most effective strategies may combine different parallelization strategies at different hierarchy levels. For example, algorithms that perform subsequent computations on data streams can be parallelized using a combination of the *Pipeline* [120] and *Task Parallelism* patterns. Independent computations operating on different streams are performed by multiple pipeline stages simultaneously. Additionally, operations of single computations may run in parallel by multiple tasks. For each parallel algorithm there may be multiple implementation strategies that may fit, which are concerned by lower-level patterns.

- 4. Implementation Strategy Patterns describe how individual processes and threads execute the chosen algorithm designs. They can be divided into patterns for program structure and data structure. Program structure patterns define processing elements that are executed in parallel, their relations and interactions. For example, the Master Worker pattern provides good load balancing for multiple (mostly independent) tasks. It comprises two types of processing elements, a master that distributes work packages, and workers that operate on these work packages and collect their results after completion. On the other hand, data structure patterns are concerned with the mechanics of sharing data between processes or threads. They describe concurrent data containers including their interfaces, suitable contexts, and their progress guarantees (e.g., blocking, lock-free, or wait-free [56]). For example, the Shared Queue pattern specifies a queue container that provides safe thread management. Often, multiple program and data structure patterns can be implemented or combined; thus, programmers must accurately weigh their concrete advantages and disadvantages. The patterns also inevitably express a bias towards particular programming models. For example, the SPMD pattern is mostly implemented with a message passing framework, such as MPI. Hence, the decisions made during this level highly influences the parallel programming model.

- 5. Parallel Execution patterns define how software elements are mapped to hardware for exploiting parallelism. At this level, programmers can estimate (and measure) the resulting performance of different realizations. The patterns are divided into two categories: process and thread control, and coordination. The former category comprises patterns for advancing control flows of concurrent program executions. For example, thread pools avoid time-consuming operations to create and destroy threads. Whenever a new thread is needed, one is used from the pool (if available). Whenever a thread gets destroyed, it is returned to the pool. As opposed to the execution of threads and processes, the second pattern category is concerned with their coordination. The comprised patterns define different

mechanics for communication and synchronization of concurrent software elements. Message passing and mutual exclusion are typical examples for these two categories, respectively. The former lets different processes coordinate their work by explicit communication messages passed over interconnection networks. The latter synchronizes accesses to shared resources (e.g., memory locations) by restricting simultaneous execution of containing code regions to single threads or processes. Most of the parallel execution patterns are included within major parallel programming models, such as OpenMP, or MPI. Some patterns are native to specific programming models but foreign to others.

Besides the described patterns, OPL includes a procedure model to support parallel programmers through the entire development process. Here, designers iteratively move between different design spaces to find patterns that constitute the best parallel software architecture. The procedure model originates from the PLPP pattern language [87], which is organized into four design spaces (Figure 2.3):

Figure 2.3: Design spaces of the PLPP pattern language [87].

1. *Finding Concurrency*. This design space is concerned with analyzing and structuring computational problems to exploit concurrency. Here, designers aim to understand relevant key features in the problem domain and justify the effort for parallel programming. To support this process, the design space contains several patterns organized into three related categories: decomposition, dependency analysis, and design evaluation. The decomposition patterns are intended to split the problem into multiple sub-problems that may execute simultaneously. Dependency analysis patterns help to group tasks and analyze dependencies among them. Design evaluation compares different decompositions relative to different qualities, such as suitability (for the target platform), flexibility, efficiency, or simplicity.

Note that the design space abstractly describes parallel computations and is not concerned with algorithms or implementation details. We use the same distinction in our approach to define parallelization scenarios (Section 3.3).

2. Algorithm Structure. Here, the intended software design is refined towards a parallel program by mapping concurrency onto multiple units of executions. This mapping can be done in numerous ways; however, related patterns mostly follow one of three major organizing principles: organization by task, organization by data decomposition, or organization by data flow. The patterns of this design space are similar to Algorithm Structure patterns from the OPL An organization by task is recommended if the execution of tasks constitute the best algorithmic principle. An organization by data decomposition is the best choice if data is the major principle in understanding the concurrency. Finally, if the flow of data imposes an ordering or grouping of tasks, an organization by data flow is recommended.

Our parallelization approach considers algorithmic strategy patterns during the identification of parallelization scenarios and a (potential) software restructuring (Section 3.3). 3. Supporting Structures. This step represents an intermediate stage between the problem-oriented patterns of the Finding Concurrency design space and the programming techniques in the Implementation Mechanisms design space. The contained patterns correspond to OPL's Implementation Strategy patterns and are grouped into program and data structuring patterns. Patterns in the first group describe code structures to define concurrent software elements. Examples are SPMD, Master/Worker, Loop Parallelism, etc. Patterns in the second group have to do with managing data dependencies between multiple tasks. The Shared Data pattern deals with the generic case, the other patterns describe other frequently used data structures (e.g., queues or hash tables).

The design space exclusively corresponds to the restructuring stage of our approach (Section 3.3). Depending on the selected patterns, existing programs require substantial restructuring to integrate the program and data structures. For example, the SPMD pattern requires dividing loop-based algorithms that operate on single data structures into parallel computations that solely communicate via explicit messages.

4. *Implementation Mechanisms* are concerned with program's source code and low-level operations to manage parallelism. The contained patterns are principally comparable to OPL's Parallel Execution patterns; however, these patterns are categorized differently. The distinction is made between management, synchronization, and communication of execution units. OPL combines the latter two categories into a group called Coordination.

We do not explicitly consider those implementation mechanisms within our approach since they are implied by major parallel programming models.

## 2.3 Tools for Dynamic Parallelism Discovery

Tools for identifying exploitable parallelism have been developed in academia and industry. These tools heavily rely on dependency analysis techniques to detect independent software elements. Purely static approaches for these analyses are overly conservative; hence, recent approaches have increasingly relied on dynamic information gathered during program execution. In this section we cover two categories of tools that are most closely related to Parceive: quasi-automatic and annotation-based parallelism discovery.

## 2.3.1 Automatic Parallelism Discovery Tools

Tools within this category automatically detect and evaluate potential parallelization opportunites in sequential programs. The user is responsible to select and implement appropriate suggestions, based on detailed feedback from those tools about potential speedup and detected obstacles for parallelization. The required information is typically acquainted by profiling and tracing to capture run times and dependencies during program execution, respectively.

### DiscoPoP

DiscoPop [75] is a tool to assist programmers with identifying and exploiting parallelism. The tool discovers parallelization opportunities and rank them according to their parallelism potential. Unlike conservative approaches [126, 33], the method is not limited to loop parallelism and enables identification of parallel tasks that are not well aligned with the source code structure.

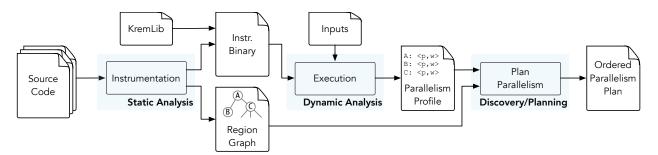

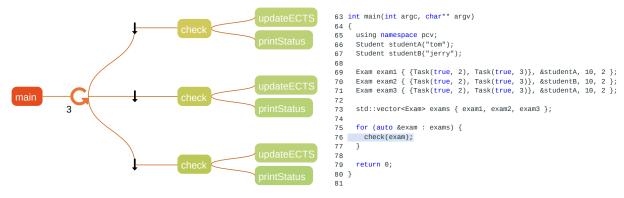

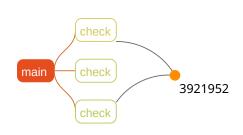

DiscoPoP's workflow for parallelism discovery comprises two major steps: a hybrid analysis to build a dependency graph, and a step for discovering and ranking of parallelization opportunities (Figure 2.4).

Figure 2.4: DiscoPoP's workflow for parallelism discovery [75, 64].

In the first step, control flow analysis is used to determine boundaries of control regions (e.g., loops) within a program's source code<sup>1</sup>. Then, the code is instrumented and executed to obtain its control and data dependencies. The final step of the hybrid analysis decomposes the profiled program into a graph of *computational units* (CUs), the author's basic blocks for building parallel programs. CUs are collections of instructions following a read-compute-write pattern. A CU graph represents a program with CUs as nodes and dependencies between them as edges.

During the second step, the tool searches for potential parallelism in the user program by merging CUs and partitioning the CU graph. Task extraction and pattern identification detect the following parallel patterns in the CU graphs: DOALL loops, DOACROSS loops, SPMD tasks, and MPMD tasks. After finding pattern occurrences, those are then ranked and suggested to the user according to their resulting speedup and parallelism-inhibiting dependencies [61].

DiscoPoP's parallelism discovery abilities exceed Parceive's features. Their automatic pattern detection and ranking algorithms alleviate the user from manually identifying concurrent software elements. Some extensions (not shown in Figure 2.4) transform user code into parallel versions [129] and validate them relative to concurrency issues [62, 63]. Finally, data dependency profiling in DiscoPoP is more efficient than our used models by relying on a signature algorithm, dependency merging, and static instrumentation. However, the latter technique limits dependency analyses to software modules with available source code. Hence, data accesses within many third-party libraries (e.g., container libraries) - which are often essential for parallelization - are not captured.

### Kremlin

Kremlin [43] discovers parallelism by detecting the (hierarchical) critical path for all code regions of a program. The tool uses this information to compute the *self-parallelism* of code regions, a metric to rate the inherent parallelism potential. The tool returns a *parallelism plan*, an ordered list of code regions that are favorable for parallelization (e.g., regions with loop parallelism or task parallelism). The programmer is responsible to determine how to expose the underlying parallelism detected by Kremlin.

The tool's workflow comprises three phases for parallelism discovery: static analysis, dynamic analysis, and parallelism planning (Figure 2.5). During the static analysis phase, Kremlin inserts specific callback functions into program's source code by performing critical path instrumentation and region instrumentation. The first step establishes a profiling infrastructure for critical path analysis while the second step instruments and extracts the region structure to localize parallelism. During the dynamic analysis phase, the tool executes the instrumented binary (linked with the KremLib instrumentation library) with a sample input to produce parallelism profiles for each program region. These profiles contain the total amount of work

<sup>&</sup>lt;sup>1</sup>more concretely: the resulting LLVM IR [73] generated from program's source code.

Figure 2.5: Kremlin's workflow for parallelism discovery [43].

and the computed parallelism excluding any from subregions. During the final phase, Kremlin computes a parallelism plan by relying on the extracted region structure and the parallelism profiles. The tool therefore considers target-specific (e.g., OpenMP) and machine-specific parameters (e.g., the number of CPU cores) to estimate speedup results based on Amdahl's law.

Similar to DiscoPoP and Parceive, Kremlin performs dependency analyses to detect (true) data and control dependencies. However, the collected information is exclusively used for implicit parallelism planning; Kremlin does not explicitly highlight those parallelization obstacles for the suggested parallelization opportunities. Thus, programmers are forced to discover these dependencies manually when exploiting the parallelism.

#### SLX

SLX is a "multicore development tool" [48]; a tool suite assisting with software parallelization tailored for embedded platforms, such as a multiprocessor system on chip (MPSoC) or FPGAs. The tool suite is developed by Silexica, a start-up company that origins from the MAPS research project [24]. MAPS aims at parallelizing C applications for MPSoC platforms.

SLX belongs to the class of quasi-automatic dynamic parallelism discovery tools since it provides *parallelization hints*: identified parallelization opportunities that are ordered by their relative and absolute speedup and by detected dependencies. For that purpose, SLX uses a pattern-based framework to identify parallelism at task level, pipeline level, and data level.

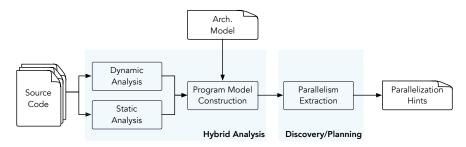

Figure 2.6: SLX's workflow for parallelism discovery.

The workflow expects sequential source code as input and applies a set of static and dynamic analyses based on compiler-based instrumentation (Figure 2.6). Then, the gained information (e.g., structural information and trace data) and a given hardware architecture model is used to generate a program model. That hardware architecture model contains relevant information of the intended target platform for speedup estimations, such as the number of CPU cores, execution costs for the instruction set and for communication, or the memory architecture. Finally, several visualizations present the simulation results, such as a graphical call graph and a source code visualization with annotated speedup results and dependency information.

### Alchemist

Alchemist [128] uses dynamic binary instrumentation for its analyses to unveil parallelization opportunities across loops, function calls, and if-statements. The tool detects code constructs that can run asynchronously with its context, similar to *futures* [9]. Alchemist thus profiles the duration of executed code constructs and between conflicting memory references from inside these constructs to their continuation. This is conducted by an online algorithm that manages an index tree for currently active code constructs to detect all data dependencies between them. After completion, the tool provides a ranked list of code constructs together with an estimation of the required work for manual parallelization (i.e., the number and type of found data dependencies).

Similar to Parceive, Alchemist is not restricted to specific parallelization patterns or programming models. This implies more effort for the developer yet it allows more flexibility in the design of parallel software.

### 2.3.2 Tools for Assisting Parallelism Discovery

Tools within this category rely on the knowledge of programmers and architects to evaluate their program's parallelism potential. As opposed to quasi-automatic approaches, identification of parallelization opportunities is conducted by the user. The tools assist this procedure with profiling results, pattern detection, and detailed information about potential implications, such as estimated speedup, problematic dependencies, or required transformations.

#### **SUIF Explorer**

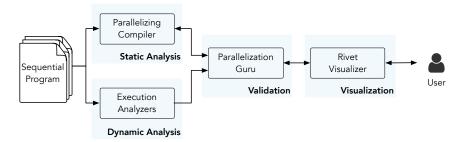

The SUIF Explorer [76] is among the first parallelization tools that incorporate user interaction. It actively guides programmers to decide on proper program transformations for loop parallelization. The tool combines analysis results from an own compiler with dynamic program profiles and represents them with interactive visualization techniques.

Figure 2.7: Major components of the SUIF Explorer [76].

During the parallelizing process, the tool first invokes a compiler [126] that automatically parallelizes loops without loop-carried dependencies (Figure 2.7). Then, the parallel program is instrumented and executed to collect profiling information and data dependencies. The Parallelization Guru module analyzes static and dynamic information to identify long-running sequential loops that would benefit from parallelization. The user is involved in the parallelization process by the Rivet visualization. It pinpoints the identified loops and the dependency information concisely presented by program slicing techniques. By adding annotations to the source code (or manually transforming source code), the compiler can consequently parallelize loops.

The SUIF Explorer enables - as Parceive - dependency analyses across arbitrary deep levels of function calls. However, the author's system perform these analyses strictly on loops, which excludes other higher-level programming models. Due to the underlying compiler infrastructure, the SUIF Explorer provides many useful features which might improve Parceive's effectiveness. For example, the compiler uses interprocedural analysis and alias analysis to statically detect data dependencies. Although static analysis potentially returns false-positive results, the gained information would favorably extend the dynamic data dependencies found by Parceive.

#### Intel<sup>®</sup> Threading Advisor

The Advisor XE [27] is a well-established proprietary tool suite for parallelism discovery. Besides abilities for vectorization optimization and flow graph analysis, the suite contains a prototyping tool to model threaded software designs called Threading Advisor. The two main features of this tool are detection of performance bottlenecks using the roofline model [125] and what-if analysis for predicting data sharing problems among user-selected code regions.

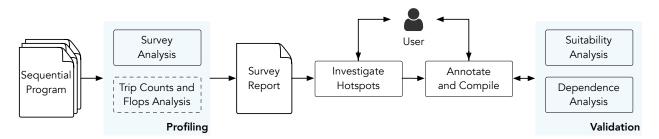

Figure 2.8: Parallelization workflow of the Intel® Threading Advisor [27].

The tool's workflow comprises three phases: profiling, investigation and annotation, and parallelism validation (Figure 2.8). During the profiling phase, a Survey Analysis identifies loops and functions with a substantial run time and aggregates the loop's trip counts. The result is a Survey Report, a visualization of beneficial code regions for data parallelism, loop parallelism, and task parallelism. In the second phase, the user annotates selected code regions based on the profiling report (we give more details on these annotations below). During the final phase, the Suitability Analysis executes the annotated program binary to estimate the parallel performance characteristics of annotated regions, i.e., scalability ranges for various target models specifying the processor types, the number of cores, or the programming model. Additionally, the Advisor performs deep dependency analyses within the annotated parallel regions based on dynamic binary instrumentation.

The Advisor's approach shares many aspects of Parceive; most notable is its idea of annotation-based dependency analysis. As opposed to Parceive's visualization-based parallel region selection, the tool from Intel accepts the following types of source code annotations:

- 1. *Parallel site and task annotations*. Parallel sites are named code regions containing at least one task that executes concurrently with other tasks of the same site. The tasks are itself code regions, e.g., loops or a set of consecutive instructions. Parceive's users can perform equivalent analyses on call and loop level by selecting the respective nodes in the CCT View (Section 3.3). Our tool does not support instruction-based dependency analysis.

- 2. *Lock annotations*. These are explicit synchronization annotations that are hints for the dependency analysis to ignore specific data dependencies. This feature is not supported by Parceive since we do not provide multi-pass analyses.

- 3. *Pause and resume annotations*. These annotations let the user pause and resume the collection of data accesses within parallel regions during analysis runs. This improves the analysis performance

and reduces the amount of shown (incidental) data races. Parceive provides similar functionality on function level (and above) through static and dynamic filter rules (Section 4.7).

4. *Special-purpose annotations*. Recently, the Threading Advisor has been extended by interesting annotations for special purposes. The underlying use cases partly follow the same insights for parallelization as we identified. For example, a particular annotation let programmers identify all accesses to a specific (heap) memory region. Parceive provides an equivalent feature on call and architecture level (Section 3.3).

As opposed to Parceive, the Advisor uses a multi-pass analysis, i.e., the tool performs separate executions for profiling and dependency analysis. This reduces the overhead incurred by dynamic binary instrumentation frameworks; however, it requires a recompilation due to source code annotations, which may be infeasible in some industrial settings. Additionally, the savings in slowdown may be negligible for programs with substantial parallelism. More run time spent in parallel regions requires more overall analysis time.

### Tareador

Tareador [8] is a framework to support parallelization that was developed for educational purposes. It provides an application programming interface (API) to annotate user tasks similar to the approach from the Intel<sup>®</sup> Threading Advisor. Annotated task regions are used by the author's framework to estimate the resulting parallelism and highlight problematic data dependencies. For speedup estimations, Tareador relies on the OpenMP programming model with explicit support for loop level parallelism. Tareador also offers a set of trace visualizations which allow the programmer to understand the actual behavior of the parallel decomposition.

As opposed to the Advisor's two-pass methodology, Tareador relies on a single pass workflow for parallelism discovery (Figure 2.9). The programmer starts with annotating the source code with three types of functions: scoping the analysis, defining task boundaries, and hints for data dependency analysis. The annotated code is executed sequentially and the tasks are executed in the invocation order. During this execution, Tareador collects an execution trace with data regions accessed by each potential task. The backend component reads this trace and feeds three different visualizations. First, a usage visualization of the data accessed by each task. Second, a task dependency graph with all tasks represented hierarchically. Third, time-plots showing the potential parallel execution produced by a parallelism simulator.

Figure 2.9: Tareador's workflow for interactive parallelization [8].

Although the functionality of Tareador is below the one of Advisor (e.g., the specialized annotations for locking or dependency analysis), the framework facilitates useful features for parallelism comprehension. For example, the task graph visualization supports the user with identification of execution patterns, such as recursive graph algorithms. This information may be very insightful to elaborate more efficient parallelization opportunities or consider specialized parallel programming models. Parceive shares this idea of visual pattern recognition by its provided visualizations.

### 2.3.3 Summary

In this section we have introduced state-of-the-art tools for dynamic parallelism discovery. Based on available information from published research papers and documentation, we now summarize the most notable findings.

The presented tools differ widely in the concerned parallelism types and the targeted levels of abstraction<sup>2</sup> (Table 2.1). As parallelism on loop and function levels is relatively easy to detect, it is supported by all parallelism discovery approaches. Parallelism that is unaligned with the given source code structure requires different models for detection; appropriate tools must consider concurrency in non-continuous code regions. Parceive supports parallelism discovery at various levels, ranging from call to architectural levels.

|                                                                | Ó,     | BO Fre      | in st       | $\mathcal{A}_{C_{\mathcal{K}}}$ | S. C. S. | Adr. Color  | sot fair         | addi e           |

|----------------------------------------------------------------|--------|-------------|-------------|---------------------------------|----------------------------------------------|-------------|------------------|------------------|

| Architecture Level<br>Design Pattern Level                     | -<br>1 | -           | -           | -<br>-                          |                                              | -           | -                | ✓<br>✓           |

| Loop Level<br>Function Level<br>Instruction Level<br>Unaligned |        | ✓<br>✓<br>✓ | ✓<br>✓<br>✓ | \<br>\<br>\<br>\<br>\           | ✓<br>✓<br>-<br>-                             | ✓<br>✓<br>✓ | ✓<br>✓<br>-<br>- | ✓<br>✓<br>-<br>✓ |

**Table 2.1:** Comparison of parallelization tools by parallelism type.

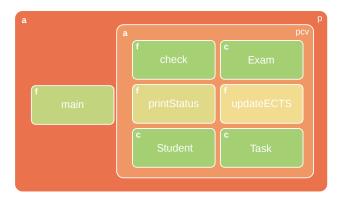

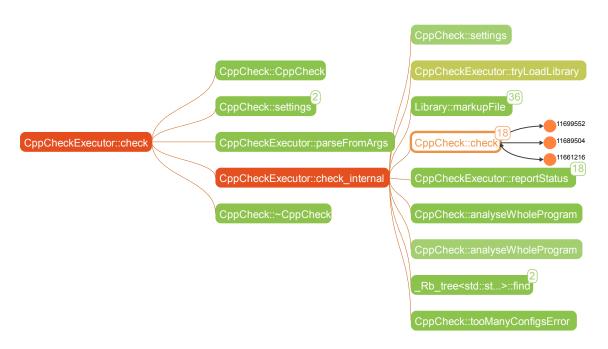

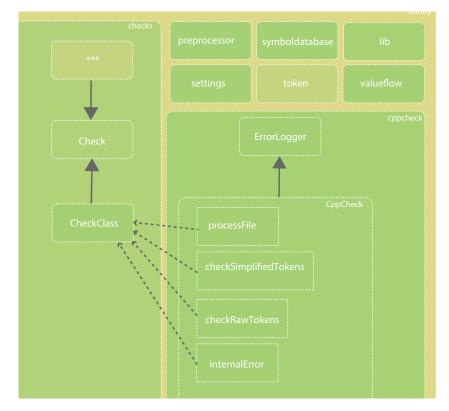

As opposed to existing parallelization tools, Parceive considers architectural structures as first class elements for parallelism discovery. This entails additional flexibility to identify and validate parallel patterns without the limitation on single programming models. Parceive's provided visualizations enable users to explore their software systems (Section 3.2). This facilitates program comprehension and software restructuring as it gives detailed insights at different perspectives of the software.