# TECHNISCHE UNIVERSITÄT MÜNCHEN

Lehrstuhl für Realzeit-Computersysteme

# Synthesizing Communication-Centric Automotive Cyber-Physical Systems

Licong Zhang

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

# Doktor-Ingenieurs (Dr.-Ing.)

genehmigten Dissertation.

| Vorsitzender:<br>Prüfer der Dissertation: |    | Prof. DrIng. Andreas Jossen                          |

|-------------------------------------------|----|------------------------------------------------------|

|                                           | 1. | Prof. Dr. sc. Samarjit Chakraborty                   |

|                                           | 2. | Prof. Dr. Petru Eles, Linköping University, Schweden |

Die Dissertation wurde am 31.07.2017 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 23.05.2018 angenommen.

# Abstract

Recent development in the automotive industry is currently revolutionizing the functionality of modern vehicles. Especially in the domain of infotainment and driver assistance systems, increasingly more new functions are being developed to make the cars safe, intelligent, convenient and comfortable for the drivers and passengers. With this enrichment of functionality, the E/E architecture of such system has also grown substantially in both size and complexity. This development introduces new challenges for meeting traditional requirements like real-time capability, resource efficiency due to the increasing size and complexity as well as emerging requirements like flexibility, adaptability, safety and security. To be able to address these challenges and scale into the future, the automotive E/E architecture also has to evolve. Towards this, several developing trends have been gathering increasing momentum, including, e.g., ECU consolidation, application of automotive Ethernet, adaptive platform, connectivity and Cyber-Physical System (CPS). Simultaneously, new design/synthesis approaches as well as frameworks need to be developed to facilitate the evolution of the E/E architecture along these directions and meet the existing and emerging design requirements.

This thesis addresses the problem of synthesizing communication-centric automotive CPS. The automotive E/E architecture is of a distributed nature where the Electronic Control Units (ECUs) are connected through different bus systems. The communication system plays an important role in the functional performance and non-functional properties of the applications and often becomes the bottleneck problem in the design of such systems. This thesis investigates the design of automotive CPS with the focus on the communication bus systems. In particular, it proposes three approaches addressing broadly three different requirements in the design of such systems, namely the real-time capability, flexibility/reconfigurability and resource efficiency.

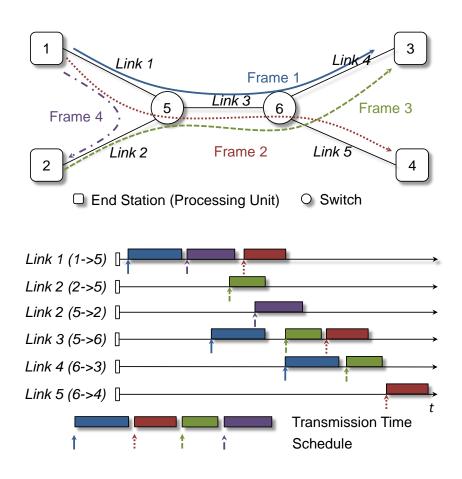

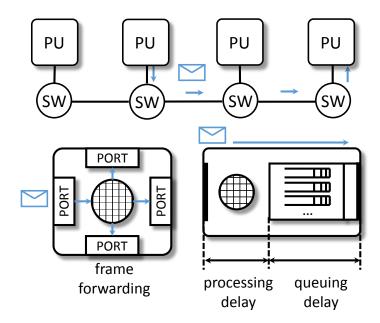

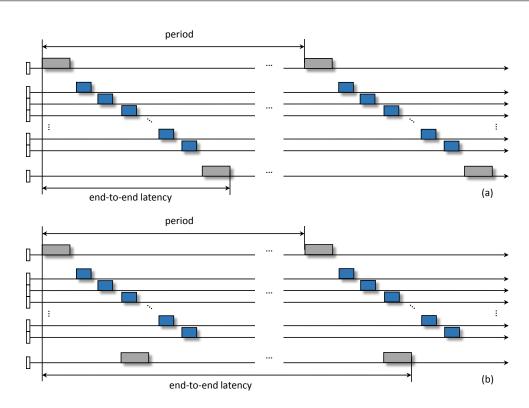

The first approach addresses the problem of co-synthesizing task and communication schedules for an Ethernet-based time-triggered system. Ethernet has recently emerged as one promising candidate for the next generation automotive communication system. Towards the real-time requirements, some recent Ethernet protocols like the Time-Sensitive Networking (TSN) offer time-triggered communication, which is suitable for safety-critical and time-critical applications with stringent timing requirements. The proposed approach combines the task scheduling and communication scheduling in a synchronized manner and optimizes schedules according to application-level timing objectives. It further takes into account a number of Ethernet-specific timing parameters such as synchronization precision. The schedule synthesis problem is translated into a Mixed-Integer Programming (MIP) problem. This approach is able to handle one or multiple timing objectives such as application response time, end-to-end delay and their combinations and is scalable to systems of industrial size.

The second problem addressed in this thesis is the schedule management for the case of Plug-and-Play (PnP) and software update. In recent years, increasingly more new software

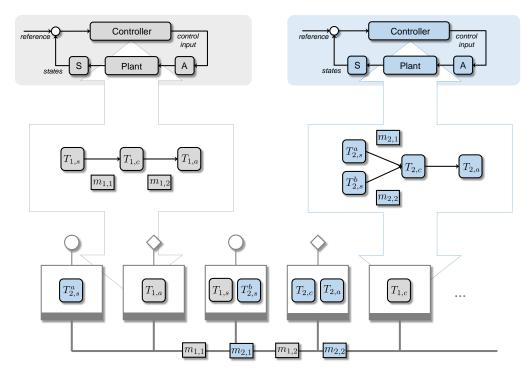

applications are deployed in cars and this trend is expected to continue. However, the design and development cycle of software is much shorter than the life cycle of a vehicle and thus the functionality of a car could easily become outdated. Therefore, there have been emerging requirements on the software update and deployment of new software applications after sales. Towards this, the underlying E/E architecture has to offer a certain level of flexibility. One important issue here is the allocation of computation and communication resources. Addressing this problem, this thesis proposes a schedule management framework to obtain, synthesize and manage schedules efficiently online for Ethernet-based time-triggered systems in the automotive context. This framework is based on a client-server architecture and each side consists of a web module, a synthesis module and a configuration pool. It utilizes the Internet access of modern vehicles to exploit the computation and storage capacity on the server in a cloud-computing manner and can facilitate the reuse of generated schedule sets. In the synthesis module, a four-stage strategy is introduced to reduce the synthesis time and the disturbance to existing applications.

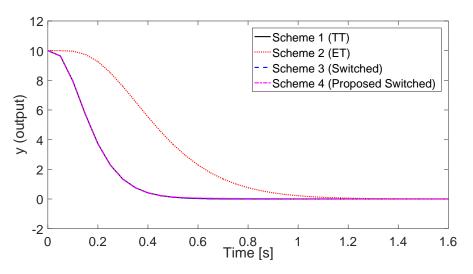

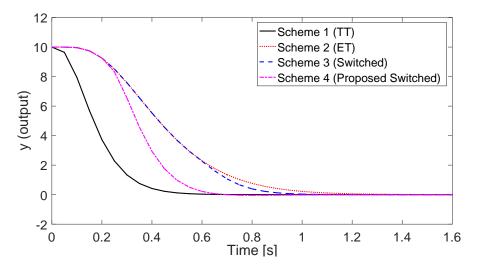

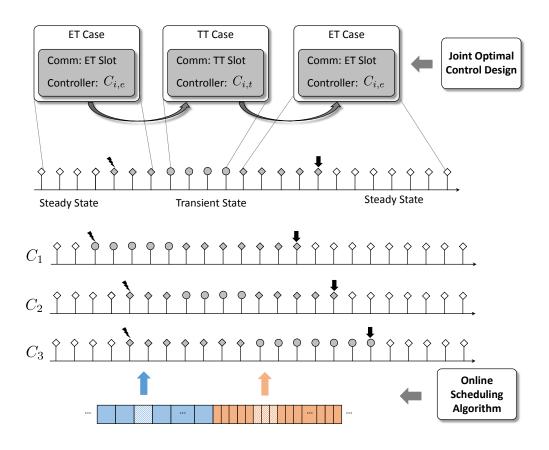

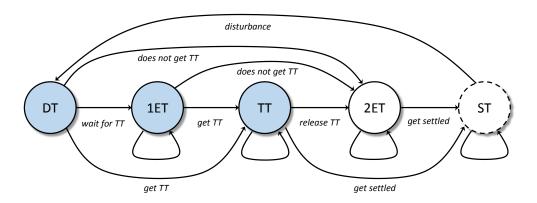

A further problem considered is the resource-efficient design in the context of CPS. Towards this, an approach to design resource-aware CPS over hybrid communication bus is proposed. Such a bus protocol offers both time-triggered (TT) and event-triggered (ET) communication. The TT communication offers higher timing predictability, which can potentially be translated into better control performance. However, such resource is often quite limited. Towards this, a resource-aware switching scheme for distributed embedded control applications is introduced in this thesis and illustrated using the FlexRay protocol. In the proposed approach, a combination of TT and ET communication is used to reject a disturbance and the strategy allows a control application to reside on the TT communication for an amount of samples that would be optimal for the overall control performance. Furthermore, it allows a control application to release TT resource before it is settled to make more efficient utilization of the resource. The proposed scheme involves both a control design method that optimizes the control performance and guarantees the switching stability and an online scheduling algorithm to dynamically determine the allocation of the TT communication to multiple control applications at run-time to optimize overall control performance. It further addresses the implementation challenges of the dynamic switching between TT and ET communication on the FlexRay protocol.

In summary, this thesis addresses the design/synthesis of the distributed automotive CPS. It proposes three new design approaches that address mainly the requirements on real-time capability, flexibility/reconfigurability and resource efficiency respectively. The approaches target at emerging fields like automotive Ethernet, Plug-and-Play and CPS and therefore quite relevant for the future. The methods proposed in this thesis might serve as the basis for further design solutions towards new in-vehicle communication architectures, adaptive platforms and cross-layer design in the CPS oriented fashion for the next generation E/E architecture that scales to the evolving requirements in the automotive domain.

# Kurzfassung (German Abstract)

Die jüngste Entwicklung in der Automobilindustrie revolutioniert derzeit die Funktionalität moderner Fahrzeuge. Vor allem im Bereich der Infotainment- und Fahrerassistenzsysteme werden immer mehr neue Funktionen entwickelt, um die Autos sicher, intelligent und bequem für die Fahrer und die Passagiere zu machen. Mit dieser Anreicherung der Funktionalität ist die E/E-Architektur eines solchen Systems auch in Größe und Komplexität erheblich gewachsen. Diese Entwicklung stellt neue Herausforderungen für die Erfüllung traditioneller Anforderungen wie Echtzeitfähigkeit, Ressourceneffizienz durch die zunehmende Größe und Komplexität und auch entstehender Anforderungen wie Flexibilität, Adaptivität, Safety und Security vor. Um diese Herausforderungen zu begegnen und in die Zukunft zu skalieren, muss sich auch die E/E-Architektur weiterentwickeln. Auf diese Weise haben einige Entwicklungstrends an Schwung gewonnen, darunter z.B. ECU-Konsolidierung, Einsatz von Automotive Ethernet, adaptive Plattform, Konnektivität und Cyber-Physisches System (CPS). Gleichzeitig müssen neue Design-/Syntheseansätze sowie Frameworks entwickelt werden, um die Evolution der E/E-Architektur in diesen Richtungen zu erleichtern und die bestehenden und aufkommenden Designanforderungen zu erfüllen.

Die vorliegende Doktorarbeit befasst sich mit dem Problem der Synthese von kommunikationszentrierten Automotiven CPS. Die Automotive E/E-Architektur hat eine verteilte Struktur, wo die Steuergeräte (ECUs) über unterschiedliche Bussysteme verbunden sind. Das Kommunikationssystem spielt eine wichtige Rolle bei der funktionalen Leistung und den nicht funktionalen Eigenschaften der Applikationen und wird oft zum Engpassproblem bei der Entwurf solcher Systeme. Diese Doktorarbeit untersucht den Entwurf von Automotiven CPS mit dem Fokus auf die Kommunikationssysteme. Insbesondere sind drei Ansätze beim Entwurf solcher Systeme vorgestellt, die sich mit drei verschiedener Anforderungen beschäftigen, nämlich der Echtzeitfähigkeit, der Flexibilität/Rekonfigurierbarkeit und der Ressourceneffizienz.

Der erste Ansatz befasst sich mit dem Problem der Co-Synthese von Task- und Kommunikationsschedules für ein auf Ethernet-basiertes zeitgesteuertes System. Ethernet hat sich kürzlich als ein vielversprechender Kandidat für die nächste Generation Automotive Kommunikationssystem entstanden. Für die Echtzeitanforderungen bieten einige neuere Ethernet-Protokolle wie Time-Sensitive Networking (TSN) eine zeitgesteuerte Kommunikation an, das für sicherheitskritische und zeitkritische Anwendungen mit strengen Timing-Anforderungen geeignet ist. Der vorgestellte Ansatz kombiniert die Task-Scheduling und die Kommunikationsscheduling in einer synchronisierten Weise und optimiert die Schedules nach den Timing-Zielen auf der Anwendungsebene. Eine Reihe von Ethernet-spezifischen Timing-Parametern wie Synchronisationsgenauigkeit werden auch berücksichtigt. Das Problem der Schedule-Synthese wird in ein Mixed-Integer Programming (MIP) Problem übersetzt. Dieser Ansatz ist in der Lage, ein oder mehrere zeitliche Ziele wie Reaktionszeit der Anwendung, End-to-End-Latenz und ihre Kombinationen zu behandeln und ist skalierbar auf Systeme der industriellen Größe.

Das zweite Problem, das in dieser Doktorarbeit behandelt ist, ist das Schedule-Management für den Fall von Plug-and-Play (PnP) und Software-Update. In den vergangenen Jahren werden immer mehr neue Softwareanwendungen in Autos eingesetzt und dieser Trend wird voraussichtlich fortsetzen. Allerdings ist der Entwurfs- und Entwicklungszyklus von Software viel kürzer als der Lebenszyklus eines Fahrzeugs und somit könnte die Funktionalität eines Autos leicht veraltet sein. Daher gibt es neue Anforderungen an Software-Update und die Installation neuer Software-Applikationen nach dem Verkauf. Zu diesem Zweck muss die zugrunde liegende E/E-Architektur ein gewisses Maß an Flexibilität anbieten. Ein wichtiges Thema hierbei ist die Allokation von Berechnungs- und Kommunikationsressourcen. Angesichts dieses Problems stellt diese Arbeit ein Schedule-Management-Framework vor, um Schedules effizient online für Ethernet-basierte zeitgesteuerte Systeme im automobilen Kontext zu erhalten, zu synthetisieren und zu verwalten. Dieses Framework basiert auf einer Client-Server-Architektur und jede Seite besteht aus einem Webmodul, einem Synthesemodul und einem Konfigurationspool. Es nutzt den Internet-Zugang von modernen Fahrzeugen, um die Berechnungs- und Speicherkapazität auf dem Server in einer Cloud-Computing Weise auszunutzen und die Wiederverwendung von generierten Schedules zu erleichtern. Im Synthesemodul wird eine vierstufige Strategie eingeführt, um die Synthesezeit und die Störung auf bestehende Anwendungen zu reduzieren.

Ein weiteres Problem, das behandelt ist, ist der ressourcenbewusste Entwurf in Kontext von CPS. Ein Ansatz zum Entwurf von ressourcenbewussten CPS über Hybrid-Kommunikationsbus ist vorgestellt. Ein solches Bus-Protokoll bietet sowohl zeitgesteuerte (TT) als auch ereignisgesteuerte (ET) Kommunikation. Die TT-Kommunikation bietet eine höhere Timing-Vorhersagbarkeit, die potenziell in ein besseres Regelverhalten umgesetzt werden kann. Allerdings ist diese Ressource oft sehr begrenzt. Zu diesem Zweck wird in dieser Doktorarbeit ein ressourceneffiziente Switchingsschema für verteilte eingebettete Regelungsapplikationen eingeführt und mit dem FlexRay Protokoll verdeutlicht. Bei dem vorgestellten Ansatz wird eine Kombination aus TT- und ET-Kommunikation verwendet und die Strategie ermöglicht es, dass eine Regelungsanwendung auf der TT-Kommunikation für eine Menge von Samples liegt, die für das gesamte Regelungsverhalten optimal ist. Darüber hinaus ermöglicht er eine Regelungsanwendung, TT-Ressource freizugeben, bevor sie eingeschwungen wird, um eine effizientere Nutzung der Ressource zu ermöglichen. Das vorgestellte Schema beinhaltet sowohl eine Regelerentwurfsmethode, die das Regelsverhalten optimiert und die Switchingstabilität gewährleistet, und einen Online-Scheduling-Algorithmus, um die Allokation der TT-Kommunikation zu mehreren Regelungsapplikationen zur Laufzeit dynamisch zu bestimmen, um das gesamte Regelverhalten zu optimieren. Der Ansatz befasst sich darüber hinaus mit der Implementierungsherausforderung der dynamischen Umschaltung zwischen TT und ET Kommunikation auf dem FlexRay Protokoll.

Zusammenfassend behandelt diese Doktorarbeit die Entwurf/Synthese der verteilten Automotiven CPS. Die stellt drei neue Entwurfsansätze vor, die vor allem die Anforderungen an Echtzeitfähigkeit, Flexibilität/Rekonfigurierbarkeit und Ressourceneffizienz behandeln. Die Ansätze zielen auf entstehende Felder wie Automotive Ethernet, Plug-and-Play und CPS, und deswegen sind für die Zukunft relevant. Die in dieser Doktorarbeit vorgestellten Methoden könnten als Grundlage für weitere Lösungen für neue Kommunikationsarchitekturen, adaptive Plattformen und CPS-orientiertes Cross-Layer-Design für die E/E-Architektur der nächsten Generation dienen, die die wandelnde Anforderungen in dem Automobilbereich erfüllen wird.

# Acknowledgements

This thesis is the result of the research work conducted at the Chair of Real-Time Computer Systems at the Technical University of Munich. It would not have been possible without the support of many people.

First of all, I would like to express my sincere gratitude to Prof. Samarjit Chakraborty for his guidance, support, advice and also encouragement. I would like to thank him for introducing me into this interesting topic and guiding me through the whole research work. I would also like to thank Prof. Petru Eles for agreeing to be the reviewer and co-examiner of this thesis and Prof. Andreas Jossen for heading the examination committee.

I would also like to thank all my colleges at the Chair of Real-Time Computer Systems. It has been a great pleasure to know them and work with them. Many research works have resulted from the discussions and collaborations with them. In addition, they have made the work at RCS much more enjoyable.

I am also grateful for the colleges that I have worked with from the RACE project and from other institutions that I have collaborated with. I have certainly benefited a lot from the collaborations on various challenging and interesting topics.

Finally, I would like to thank my family for the continuous support as well as encouragement.

# Contents

| Abstract         | iii |

|------------------|-----|

| Kurzfassung      | v   |

| Acknowledgements | ix  |

| 1        | Intr             | roduction                                                    | 1  |  |  |

|----------|------------------|--------------------------------------------------------------|----|--|--|

|          | 1.1              | Motivation                                                   | 2  |  |  |

|          | 1.2              | Background                                                   | 3  |  |  |

|          |                  | 1.2.1 Automotive E/E Architecture                            | 3  |  |  |

|          |                  | 1.2.2 In-Vehicle Communication and Bus Systems               | 5  |  |  |

|          |                  | 1.2.3 Software Architecture                                  | 9  |  |  |

|          | 1.3              | Trends, Requirements and Challenges                          | 11 |  |  |

|          |                  | 1.3.1 Current and Future Trends                              | 11 |  |  |

|          |                  | 1.3.2 Design Requirements and Challenges                     | 15 |  |  |

|          | 1.4              | Scheduling and Schedule Synthesis                            | 20 |  |  |

|          | 1.5              | Design of CPS                                                | 25 |  |  |

|          | 1.6              | Thesis Contributions                                         | 27 |  |  |

|          | 1.7              | Organization and Publications                                | 30 |  |  |

|          |                  | 1.7.1 Organization                                           | 30 |  |  |

|          |                  | 1.7.2 Publications                                           | 30 |  |  |

| <b>2</b> | $\mathbf{Sch}$   | edule Co-Synthesis for Ethernet-based Time-Triggered Systems | 33 |  |  |

|          | 2.1 Introduction |                                                              |    |  |  |

|          | 2.2              | Related Work                                                 | 37 |  |  |

|          | 2.3              |                                                              |    |  |  |

|          | 2.4              | Approach                                                     | 41 |  |  |

|          |                  | 2.4.1 Constraints                                            | 41 |  |  |

|          |                  | 2.4.2 Constraint Formulation as MIP                          | 44 |  |  |

|   |     | 2.4.3   | Objectives                                                                                                                               | 5 |

|---|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------|---|

|   |     | 2.4.4   | Objective Formulation as MIP                                                                                                             | 6 |

|   |     | 2.4.5   | Generalized Constraints and Objectives                                                                                                   |   |

|   | 2.5 |         | imental Results                                                                                                                          |   |

|   |     | 2.5.1   | Case Study                                                                                                                               |   |

|   |     | 2.5.2   | Results and Discussions                                                                                                                  |   |

|   |     | 2.5.3   | Scalability Analysis                                                                                                                     |   |

|   | 2.6 |         | iding Remarks                                                                                                                            |   |

| 3 | Sch | edule I | Management for Cloud-based Automotive Software Systems 5'                                                                                | 7 |

|   | 3.1 | Introd  | uction $\ldots \ldots 5$ | 8 |

|   | 3.2 | Relate  | d Works                                                                                                                                  | 1 |

|   | 3.3 | Proble  | em Formulation                                                                                                                           | 2 |

|   |     | 3.3.1   | Architectural Setting                                                                                                                    | 2 |

|   |     | 3.3.2   | Schedule Management Problem                                                                                                              | 5 |

|   | 3.4 | Appro   | ach $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $6$                                                                                     | 6 |

|   |     | 3.4.1   | Request and Configuration                                                                                                                | 6 |

|   |     | 3.4.2   | Client-Server Architecture                                                                                                               | 7 |

|   |     | 3.4.3   | Configuration Pool                                                                                                                       | 7 |

|   |     | 3.4.4   | Web Module                                                                                                                               | 8 |

|   |     | 3.4.5   | Synthesis Module                                                                                                                         | 8 |

|   |     | 3.4.6   | Request-based Schedule Management Flow                                                                                                   | 1 |

|   | 3.5 | Experi  | imental Results                                                                                                                          | 3 |

|   | 3.6 | Conclu  | uding Remarks                                                                                                                            | 9 |

| 4 |     |         | Resource-aware CPS over Hybrid Communication Networks 8                                                                                  |   |

|   | 4.1 |         | uction                                                                                                                                   |   |

|   | 4.2 |         | d Works                                                                                                                                  |   |

|   | 4.3 |         | em Formulation                                                                                                                           |   |

|   |     | 4.3.1   | FlexRay-based ECU Network                                                                                                                |   |

|   |     | 4.3.2   | Distributed Feedback Control Systems                                                                                                     |   |

|   |     | 4.3.3   | Motivational Example and Problem Formulation 9                                                                                           |   |

|   |     | 4.3.4   | Problem Formulation                                                                                                                      |   |

|   | 4.4 |         | bl Design                                                                                                                                |   |

|   |     | 4.4.1   | Switching Stability                                                                                                                      |   |

|   |     | 4.4.2   | Controller Design                                                                                                                        |   |

|   | 4.5 |         | rce-Aware Switching Scheme                                                                                                               |   |

|   |     | 4.5.1   | The Proposed Switching Scheme                                                                                                            |   |

|   |     | 4.5.2   | Offline Evaluation of Switching Sequences                                                                                                |   |

|   |     | 4.5.3   | Online Switching based on Performance Prediction 10                                                                                      |   |

|   |     | 4.5.4   | Middleware-based Slot Sharing 10                                                                                                         |   |

|   | 4.6 | -       | imental Results                                                                                                                          |   |

|   |     | 4.6.1   | Case Study                                                                                                                               | 5 |

|          | 4.7 | 4.6.2 Results and Discussions |     |

|----------|-----|-------------------------------|-----|

| <b>5</b> | Con | cluding Remarks               | 111 |

|          | 5.1 | Summary                       | 111 |

|          | 5.2 | Future Works                  | 113 |

|          | 5.3 | Outlook                       | 115 |

| Bibliography    | 117 |

|-----------------|-----|

| List of Figures | 127 |

| List of Tables  | 133 |

# Chapter

# Introduction

Modern vehicles are becoming increasingly safer, more intelligent and driver friendly. In recent years, increasingly more new functions in domains like telematics/infotainment, Advanced Driver Assistance System (ADAS) are deployed in cars to assist the drivers. Examples of such functions include the navigation system, better Human Machine Interface (HMI), head-up display, surround view, parking assistant, Adaptive Cruise Control (ACC), Lane Departure Warning (LDW), etc. This trend of increase and enhancement of functionality is going to continue and autonomous and self-driving vehicles will soon become a reality. Underneath these functions that can be experienced by the user lies the Electrical/Electronic (E/E) architecture, which provides the basic services like the computation and communication for these functions. To keep up with the development pace on the functional level and be able to scale to the future, the underlying E/E architecture also has to evolve. Towards this, the requirements and challenges out of the recent development trends have to be addressed. These requirements include, e.g., real-time capability, resource-efficiency, flexibility, adaptivity, safety, security, etc. This thesis at hand proposes approaches to address several such design requirements and challenges on the topic of synthesis of communication-centric automotive Cyber-Physical System (CPS). In particular, these approaches synthesize schedules and partly also control parameters for distributed automotive E/E systems based on Ethernet and FlexRay towards real-time capability, reconfigurability and resource-efficiency. This chapter provides an introduction to the background, problem setting and the motivation of the thesis.

**Chapter outline:** This chapter is organized as follows. Firstly, the motivation of this thesis is explained in Section 1.1. This is followed by the introduction to the background in Section 1.2, including the automotive E/E architecture, the in-vehicle communication networks and the software architecture. Then a summary of the of the current and future development trends as well as the design requirements and challenges is provided in Section 1.3. Section 1.4 and Section 1.5 explain respectively two central topics related to this thesis, namely the scheduling and schedule synthesis problem and the design of CPS. Section 1.6 then summarizes the main contributions of this thesis. Finally, the organization of the thesis and the list of corresponding publications are provided in Section 1.7.

# 1.1 Motivation

The automotive E/E system is currently at the forefront of innovations from various disciplines like computer science, electrical engineering, control and mechanical engineering. Modern vehicles are being equipped with software-based applications of increasing sophistication, intelligence and connectivity, which considerably enhance the safety, convenience and comfort of the driving experience. Vehicle dynamics control systems, ADASs, navigation and connected telematics systems are just a few examples of such applications. On the functional level, more efficient algorithms in areas like computer vision, machine learning, Global Positioning System (GPS), augmented reality have contributed much to the rapid development in the domain of telematics, ADAS and autonomous driving. On the system level, the development and deployment of these software applications are made possible by more powerful hardware devices [1], better communication technologies and the advancement in software technologies.

The drastic growth of number and complexity of applications on the functional level has also profound influence on the underlying E/E architecture. Firstly, as a result of such development, the size and complexity of the automotive E/E architecture has been steadily increasing. Already in 2009, a premium-class vehicle could contain up to 100 Electronic Control Units (ECUs) running about 100 million lines of code [2]. As this trend of increasing size and complexity continues, and it will certainly do [3, 4], there will be many challenges that need to be addressed for the E/E architecture to be scalable for the future. Such challenges are on a wide spectrum of aspects, for example communication network, software architecture, Operating System (OS), hardware, etc. New or stronger requirements on issues like real-time capability, flexibility, scalability, resource-efficiency, safety and security need to be met.

On the other hand, the recent developments both inside and outside the automotive domain also offer opportunities and new technologies that can be leveraged on to address the challenges. For example, the development in the topic of connectivity has enabled modern cars the connection to other cars, intelligent infrastructure units and even backend servers. This connectivity can be utilized to get access to information and outsource computation or storage demands. A further one is the development in the communication technologies. The communication system in the automotive domain has been restricted to the domain-specific protocols like Controller Area Network (CAN), FlexRay and Media Oriented Systems Transport (MOST), which are tailored to the specific requirements in the automotive domain. However, increasingly more communication technologies from other domains can be applied to the automotive systems, for example Ethernet and higher layer protocols like Transmission Control Protocol (TCP), User Datagram Protocol (UDP), Internet Protocol (IP) and Service Oriented Communications (SOC) can be either directly used in or adapted to the automotive domain. Thirdly, control applications take up a fair amount of applications in a car. Recent development in CPS-oriented design methods might also contribute to the cross-layer design in automotive E/E systems for more efficient design. Besides these, the safety topic can be approached by methods inspired from the avionics domain (like redundancy, Safety Integration Levels (SILs)), and to address the security topic, existing methods in network security can be exploited.

The automotive E/E architecture is a broad field and it is difficult to address all the aforementioned problems and aspects within the scope of one thesis. In the context of this thesis, the main focus is on the aspects of real-time capability, flexibility/reconfigurability and resource-efficiency. The real-time capability is one essential requirements in industrial embedded systems, because many of the applications here are safety- and time-critical. For these applications, not only the functional correctness, but also the non-functional correctness like timing need to be guaranteed. Flexibility/reconfigurability of the E/E system is a relatively new yet increasingly more important topic. New functionalities, particularly in the ADAS and infortainment domain, are developed with an accelerating pace. The ability of automotive E/E system to allow software updates and installation of new functions has therefore become an important future requirement. Furthermore, as the system grows in size and complexity and as increasingly more applications are integrated and consolidated on the processing units, resource-efficient design represents another essential design requirement. Therefore, this thesis presents three approaches related to the synthesis of schedules for the software tasks and the messages in the automotive E/E, with a particular focus on the communication network. These three approaches cover the three aforementioned fronts of design requirements and address the corresponding design and engineering challenges.

# 1.2 Background

# 1.2.1 Automotive E/E Architecture

The automotive E/E system consists of different electrical, electronic and software components. The architecture of such a system can be divided into several layers. For example, [3] describes four different layers of the E/E architecture, namely the function scope, the

function and software architecture, the communication architecture, the component architecture. The functional scope [3] deals with the functional software, which can directly be experienced by the customers. Below the function scope is the function and software architecture [3], where the software functions are treated as blocks with input and output interfaces and several blocks may have data dependency between them. Here the actual function a software block is performing is abstracted and only the interfaces and the dependencies are important. On the communication architecture layer [3], the software blocks are then partitioned and mapped onto the ECUs. The data between the blocks are mapped onto the communication buses. The lowest layer is the topology component layer [3], where the ECUs are connected by bus systems and the power supply networks. In the scope of this thesis, we are primarily concerned with the function and software architecture layer and the communication layer.

The E/E architecture of a vehicle consists mainly of a number of ECUs, which are processors that the computation part of the E/E system is mapped on. These ECUs are connected through bus systems, where data between the ECUs are transmitted. The ECUs are typically organized in several different clusters (or functional domains [5, 6]), where each cluster is responsible for a specific category of applications. Examples of functional domains include the powertrain domain (e.g., engine and transmission control), the chassis domain (e.g. steering and braking control), the body and comfort domain (e.g., the control of doors, seats, lighting and air conditioning) and the infotainment domain (e.g., telematics and entertainment). In general, different functional domains have different requirements on the communication [6]. For example, in the chassis domain, the data for control applications are transmitted. These data are usually small (e.g., several bytes) but have stringent requirement on the timing properties (e.g., latency, jitter, etc.). On the other hand, the amount of data that needs to be transmitted on the bus systems in the infotainment domain is much larger, but the requirement on the timing properties is less strict. Therefore, the bus system used to connect different clusters are usually different.

A software *application* can consist of one or more software components that are executed on the ECUs. The whole application performs an independent function, e.g., a control loop. Each software component is a sub-module of an application and the components may have data dependencies. The application can be aggregated on one single ECU or distributed over multiple ECUs. The software components are implemented as *tasks*, where each task represents the execution of a piece of software code. If the component is executed more than once, each execution instance can be referred to as a *task instance*, denoting one occurrence of the task. A task can be periodic, i.e., triggered periodically by a schedule table, or event-triggered, i.e., it gets triggered only by the occurrence of specific events. The data between the tasks are transmitted over the communication system. Therefore the ECUs in each cluster are connected through one or more bus systems. The software on the ECUs consists of multiple layers. The software applications performing the actual functions, e.g., related to the control of the vehicle or interaction with the driver, are on the *application software layer*. Below the applications, there could also be one or

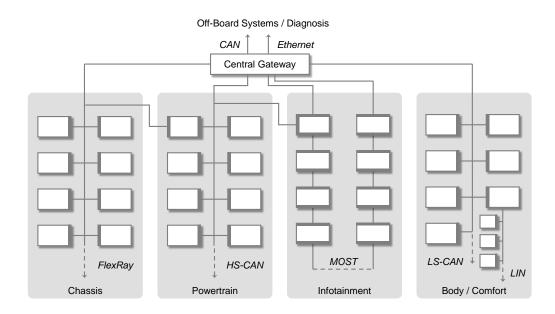

Figure 1.1: This figure shows a schematic example of an automotive E/E architecture in terms of communication bus systems. This figure is adapted from [7].

more layers of software components that provide the basic services to the application software, e.g., operating system, communication driver and Input/Output (I/O) drivers. The in-vehicle communication and the software architecture will be explained in detail in the following part of this chapter.

# 1.2.2 In-Vehicle Communication and Bus Systems

Typical bus protocols include CAN, Local Interconnect Network (LIN), MOST, FlexRay and Ethernet. Each bus protocol has its advantages and is suitable for functional domains with certain requirements. For example, the FlexRay or High-Speed-CAN is primarily used for the chassis domain, High-Speed CAN for the powertrain, Low-Speed CAN and LIN for the body domain and MOST and Ethernet for the infotaiment domain. The ECU/bus clusters are then connected to a central gateway, through which the data can be forwarded between different clusters, as shown in Figure 1.1. The in-vehicle communication forms one of the most important design aspects of the automotive E/E architecture.

# FlexRay

FlexRay is a bus protocol developed by the FlexRay consortium and published in 2005 as version 2.1 [8] and in 2010 as version 3.0 [9]. It is hybrid protocol offering both timetriggered and event-triggered communication. It is organized as a series of communication cycles. In each cycle, a static segment implements the Time Division Multiple Access (TDMA) scheme, where messages are assigned pre-defined time slots. An optional dynamic segment employs the event-triggered Flexible Time Division Multiple Access (FTDMA) scheme. Therefore, the FlexRay protocol combines both the advantages like determinism of the time-triggered communication and those like efficient resource utilization of the eventtriggered communication. To support the time-triggered scheme, the clocks of the network nodes are synchronized to provide a global time. FlexRay allows the use of line topology as well as star topology and provides two channels (Channel A and B) that could be utilized either for bandwidth enhancement or redundancy [10, 11]. Due to the deterministic nature of the FlexRay (static segment), it is suitable for transmission of safety-critical data with strict timing requirements. On the other hand, due to the higher cost, compared to, e.g., CAN bus, its usage is still quite limited. However, FlexRay still gains ground in the chassis domain [10] in many types of cars produced by Original Equipment Manufacturers (OEMs) like BMW [7].

#### Ethernet

Ethernet is originally widely used for connecting computers and has a long history dating back to 1973 [12]. The Ethernet protocol has undergone a long process of development. Originally the Ethernet protocol features a Carrier Sense Multiple Access/Collision Detection (CSMA/CD) Media Access Control (MAC) with half-duplex links, where messages have to content for channel access and in the case of a collision, all messages will wait for a random backoff period [12]. Therefore, the message transmission of the CSMA/CD based Ethernet is not deterministic at all. Since then, full-duplex links are introduced to detach the sending and receiving link and switches (or bridges) are introduced to forward the Ethernet frames. In addition, priority operation is introduced to differentiate frames of different timing requirements [13]. Therefore, full-duplex switched Ethernet becomes a point-to-point network and has no collision between the network nodes anymore. The contention for communication bandwidth is transformed into the queueing time of messages in the output port of the switches.

Recent development of the IEEE protocol family include Audio Video Bridging (AVB), Time-Sensitive Networking (TSN) protocols, where both are a collection of amendments to the existing Ethernet protocols. The AVB, incorporated in the IEEE802.1Q standard [14], introduces several new features like clock synchronization, stream reservation protocol and the credit-based shaper. The AVB thus allows bandwidth reservation for the streams (e.g., of audio and video data) and avoids the starvation of low priority traffic by the streaming data using the credit-based fair queueing. The TSN [15] protocol is the successor of AVB and offers new features to improve the real-time capability of the network. Currently, the TSN protocols have not yet been fully specified, but some parts are published, including, amongst others, the Enhancements for Scheduled Traffic (IEEE802.1Qbv) [16] and the Frame Preemption (IEEE802.1Qbu) [17]. The IEEE802.1Qbv amendment introduces the mechanism supporting scheduled time-triggered transmission of messages. This is achieved by closing the gates of transmission control for the non-time-triggered queues when timetriggered traffic arrives and opening the gates again once the transmission is finished [16]. The frame preemption allows more critical messages to preempt less critical messages so that the *blocking time* is reduced [17]. Both mechanisms are targeted at improving the

real-time properties of time-critical messages and can be used either individually or in combination [17].

Besides the IEEE protocol family, there are also several proprietary Ethernet protocols. The most notable of them are PROFINET [18] and EtherCAT [19] in the industrial automation domain and the Avionics Full Duplex Switched Ethernet (AFDX) [20] and AS6802 (TTEthernet) [21] primarily targeted at the avionics domain. These protocols offer tailored solutions to the individual domain or application system. In general, the PROFINET and AS6802 protocols show some similarities to the TSN protocol, where the network traffic is divided into several categories and for the applications with most stringent real-time requirements, the time-triggered (or scheduled) traffic is used.

Currently, Ethernet is already used for diagnosis and applied in the infotainment domain, having the potential to replace MOST [11, 22]. In the future, it is considered a promising candidate for serving as the backbone between domains [23], and even be applied in the safety-critical domains. There are also already research platforms employing Ethernet as the dominant communication system [24]. However, there are still several hurdles to overcome for a wide application of Ethernet in the automotive domain. Firstly, the new Ethernet protocols like AVB and TSN are still relatively new. The suitability of these protocols are still yet to be proved, especially for the safety-critical domains, where real-time capability is usually an important requirement. Furthermore, compared to conventional bus systems, there are still not sufficient work on the design and analysis methods as well as tool support. Finally, cost reason also plays an important role, due to the cost-sensitive nature of the automotive industry. Implementing Ethernet means also making the corresponding hardware and software compatible. This introduces considerable cost on hardware/software components as well as the cost for development, testing and validation. The cost issue is partly addressed by the introduction of BroadR-Reach technology [25], featuring a Physical (PHY) layer based on an unshielded single twisted pair of wire, thus considerably reducing the wiring cost. Currently 100 Mbit/s is already available and deployed in some vehicles with an upgrade to 1 Gbit/s in the near future [26].

# CAN, LIN and MOST

CAN bus was introduced by Robert Bosch GmbH in 1986 and has since then become one of the most widely used bus systems in automobiles. CAN offers different versions of data rates up to 1 Mbit/s [26]. Most used versions of CAN are the *High-Speed-CAN* [27] with a common data rate of 500 kbit/s [11] and the *Low-Speed-CAN* [28] with a common data rate of 125 kbit/s [11], although a range of different data rates are supported by the both. A payload size of up to 8 bytes per message is supported by CAN. The actual use of CAN in different domains depends strongly on the manufacturer and the vehicle type. In general, this bus finds prevalent deployment in the powertrain domain (High-Speed-CAN), the body domain (Low-Speed-CAN) and sometimes also in the chassis domain (High-Speed-CAN). CAN implements an event-triggered communication scheme and is a decentralized broadcast bus. The collision between different senders are resolved through the collision resolution mechanism known as Carrier Sense Multiple Access/Collision Resolution (CS-MA/CR). Pre-defined priorities are assigned to CAN messages and when two messages are sent simultaneously, the one with higher priority will gain access of the bus. Although CAN has been the most prevalent bus system used in the automotive domain, it has several limitations, which constrain its potential for recent and future applications like ADAS. One limitation is the limited bandwidth and payload size. Towards this, the extension of CAN with Flexible Date-Rate (CAN FD) [29] has been developed that increases the payload size to 64 bytes without increasing the transmission time. This is achieved by using a new frame format and switching the data rate inside a frame. This protocol is also backward compatible with CAN [26]. The other limitation is the non-determinism and possible long latencies and large jitter, especially for lower priority messages on a loaded bus, although timing analysis techniques for CAN are commonly known [30]. There have also been efforts addressing this issue. A notable extension is the Time Triggered CAN (TTCAN) [31] protocol. The TTCAN employs both time-triggered communication based on TDMA and event-triggered communication based on CSMA/CR. The time is organized in cycles and in each cycle, some time slots are reserved for certain ECUs for time-triggered transmission and some are offered for contention-based transmission. For the TDMA scheme, the network nodes are synchronized. However, due to no enhancement of the data rate and other reasons, TTCAN is not widely implemented [26]. It is expected that CAN will be replaced by FlexRay in the domain of chassis and powertrain [11].

The development of LIN started in the later 1990s by the LIN consortium to find a cheaper alternative to the Low-Speed-CAN bus for the body domain to connect simple nodes like doors, seats, etc. [11] The current version of the specification is Version 2.1 released in 2006. The LIN bus offers a bandwidth of up to  $20 \ kBits/s$  and implements a master/slave based communication [3, 11]. One LIN cluster consists of one master node and multiple slave nodes. The communication is primarily based on a polling mechanism where the master node sends periodically a header with message ID and the corresponding slave node sends the data in the response field. The header and the response together form a LIN frame and the time slots are configured to accommodate the frames. Such a frame is called an *unconditional frame*. The communication relation is pre-configured and defined in the LIN Description File (LDF). Since only one slave node is responding to a header simultaneously, there is not collision in this case. To support also event-triggered communication, the latest version of LIN has also added other frame types like the *event-triggered* frame, sporadic frame and diagnostic frame [11]. The event-triggered frame allows multiple slave nodes to respond simultaneously and if a collision is detected, the master node will initialize a round of polling with unconditional frame through all the slave nodes.

MOST is another commonly used bus protocol, primarily targeted at telematics and multimedia applications [11]. The most commonly used topology in MOST is a ring topology where the ECUs are connected point-to-point with a direction [11, 32]. One ECU serves as the *Master* and sends frames. The rest (*slaves*) synchronize to the master and read or write data into the frames [11]. The supported data rates of MOST are 25 Mbit/s (*MOST25*), 50 Mbit/s (*MOST50*) and 150 Mbit/s (*MOST150*). The protocol

supports both time-triggered (synchronous) and event-triggered (asynchronous) communication. MOST is expected to be replaced by Ethernet in the infotainment domain [11, 22].

## SOC and Middleware Solutions

Traditionally the configuration of the communication network in vehicles is quite static. Communication signals are mapped into Protocol Data Units (PDUs) and then into frames. The communication relation (e.g., the sender and receivers) and the schedules (or priorities) are pre-defined at design and development phase and usually cannot be changed afterwards. This paradigm might not be suitable for future applications and E/E architecture, which demand a more flexible communication paradigm. Therefore, there have been some efforts to apply and adapt SOC and middleware solutions for the in-vehicle communication. Examples of such efforts include the Scalable service-oriented Middleware over IP (SOME/IP) [33] and Data Distribution Service (DDS) [34]. Such protocols are based on the publish/subscribe mechanism and a network node can offer service of certain data (or *topic*) and others can subscribe and de-subscribe this data. Many of such protocols are based on Ethernet. But there are also solutions that are based on existing automotive bus protocols like CAN [35].

# 1.2.3 Software Architecture

A modern ECU is becoming increasingly complex in terms of software. For example, an ECU can contain multiple software components of different applications. In addition, an ECU needs to have I/Os and connection to the bus system. Therefore, besides the functional software components, there is a need for basis software components like OS and drivers and services for the I/Os and the bus protocols. To handle this complexity, the software of an ECU is usually divided into different layers. For example, there is usually a basis software layer between the hardware, i.e., the microcontroller, and the application software that implements the basic software components for the scheduling, I/Os and communication services, so that the microcontroller and the basic services are abstracted from the application software. Optionally there could also be an Runtime Environment (RTE) layer to handle the coordination and communication between the software components. Another important issue that needs to be addressed is the reusability of the the software. To address these issues, the automotive industry has spent much effort in standardizing the software architecture.

# **OSEK/VDX**

In the 1990s, some Germany automotive OEMs and suppliers have formed the Offene Systeme und deren Schnittstellen fur die Elektronik in Kraftfahrzeugen (OSEK) consortium towards standardizing the software architecture [3]. Later this was merged with the french effort Vehicle Distribution eXecutive (VDX) and resulted in the OSEK/VDX standards [37]. The OSEK/VDX specifies several aspects of the software architecture, including the OS (OSEK-OS and OSEK-Time), the communication module (OSEK-COM), the

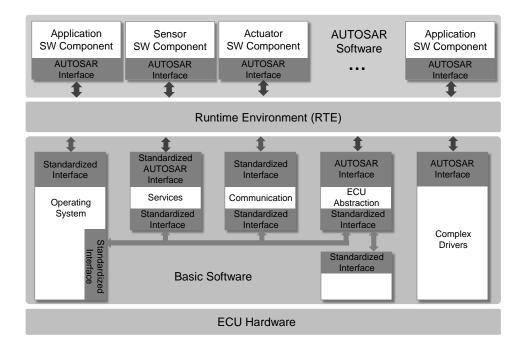

Figure 1.2: This figure shows the reference architecture from Automotive Open System Architecture (AUTOSAR). This architecture consists of three software layers, namely the basic software layer, the runtime environment and the application software layer. The interfaces between the software components are standardized. This figure is reproduced from [36].

network management (OSEK-NM) and the implementation language (OSEK-OIL). The OSEK-OS implements the event-triggered scheduling scheme [3, 38]. The OSEK-TIME is the time-triggered version of OSEK-OS [3].

# AUTOSAR

The AUTOSAR standards were published by a world wide partnership [39]. Amongst other aspects, the AUTOSAR standards define a reference software architecture, the interfaces between the different components and development methods [39]. In terms of OS, the AUTOSAR-OS is backward compatible with the OSEK-OS. The reference architecture defined in the AUTOSAR standards is shown in Figure 1.2, where the software of an ECU is divided into three layers, namely the *basic software layer*, the *RTE* and the *application software layer*. The basic software layer provides the basic services and abstracts these services from the application software components. This layer can be further divided into the *Microcontroller Abstraction Layer*, the *ECU Abstraction Layer* and the *Service Layer*. The RTE serves as the coordination of the communication between the application software components and between the application software and basic software. The application software layer contains mainly the software components that perform actual functions, e.g., engine control software module. The communication interfaces between the software components are also defined by AUTOSAR. Here the interfaces are defined as *ports* and there are different types of ports, depending on the communication relationship, e.g., *senderreceiver* or *client-server*. The communication and data exchange between the components are defined using the *Virtual Functional Bus (VFB)*. The VFB is a concept abstracted from the actual implementation of the communication, e.g., through different bus systems or inside the RTE, which depends on the actual mapping of the software components on the ECUs and the available communication bus systems. Through the standardization of the architecture and the component interfaces, modularity of the software components is achieved and as a result, it allows the reuse of software components and reduction of the complexity. For example, the basic as well as the application software components can be developed by different suppliers and integrated by the OEM. Furthermore, for different vehicle variants, where the underlying ECUs and buses are different, the same application software components can be reused.

# 1.3 Trends, Requirements and Challenges

# 1.3.1 Current and Future Trends

The automotive systems are currently undergoing rapid development and changes. These new developments are both on the application level and the system level. On the application level, increasingly more software-based systems are replacing those that are traditionally implemented with mechanical and hydraulic systems. Furthermore, new areas like the ADAS and autonomous driving, Car2X technology and connectivity as well as E-mobility are drawing increasingly more attention and are at the forefront of the innovations in the automotive domain. On the system level, topics like ECU consolidation, the introduction of Ethernet, Service Oriented Architecture (SOA) as well as safety and security are moving to the center of the stage. Here a few of the most important development trends, both on the application and system level that are related to the context of this thesis are listed and explained below. Certain topics also of significance, e.g., functional safety, security and E-mobility, are not explained here since they are not within the scope of this thesis.

#### Increasing Complexity and ECU Consolidation

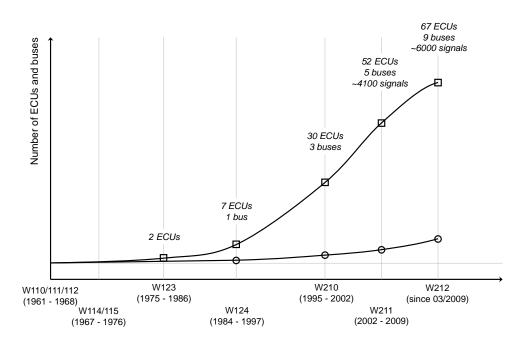

One of the most obvious trend in the automotive embedded systems is the increase of the size and complexity of the E/E system, as shown in Figure 1.3, which is the result of increasingly more software applications deployed in vehicles. This trend is reflected in the steadily increasing number of ECUs, bus systems, signals and lines of software code in modern vehicles. The main challenge here is that this increase is not sustainable with current *federated* [40] architecture, where each ECU performs only specific functions. This is due to the reason of complexity management, limited resources (e.g., communication resource), cost and ultimately the weight and space in the vehicle. One possible way to address this

Figure 1.3: This figure shows the evolution of the E/E architecture of the Mercedes-Benz E-class in terms of number of ECUs, buses and signals. The data are provided in [3, 26].

problem is ECU consolidation [4, 41]. As pointed out in [40], in the future, the automotive E/E architecture is moving from the federated architecture towards an *integrated* architecture, where the ECUs are treated as computing platforms and multiple functions can be integrated onto one single ECU. With the ECU consolidation, the increase in the number of ECUs could be curbed and the centralization of the software functions also helps managing the complexity. Towards this, more sophisticated software architecture and middleware solutions are required to integrate the software applications. One example of such architecture is the system developed in the RACE project [24, 42]. The AUTOSAR standards also contribute to this topic by standardizing the interfaces of software components and specifying the reference software architecture.

## **ADAS** and Autonomous Driving

ADAS and autonomous driving is one topic that certainly stands at the center of the stage in the automotive industry in the recent years. The development of ADAS roots back to 1978, where the first Anti-lock Braking System (ABS) system was deployed. Since then, increasingly more functions like Traction Control System (TCS), Electronic Stability Program (ESP) have been developed to help the drivers maintain and control the dynamics of the vehicle. These systems are also referred to as active safety systems. It is only recently, that more driver assistance systems like ACC, assistent/autonomous parking, traffic sign recognition, LDW, etc., are developed and deployed in the vehicles. These driver assistance systems are based primarily on cameras (mono-camera or stereo-camera), radars and Light Detection and Ranging (LIDAR) sensors. Recently, companies like Google [43] and Tesla also offer commercial autonomous driving vehicles [44, 45]. Besides the large impact of the ADAS and the autonomous driving systems on the safety and comfort of the driving experience, they also have profound impact on the underlying E/E architectures. Firstly, the rapid development in this domain means increasingly more software components, hardware components and data are being added to the E/E systems, contributing considerably to the increase in size and complexity. Secondly, the ADAS functions are usually computationand data-intensive functions which requires much longer execution time and much larger data amount that needs to be processed and possibly transferred. Although, currently sensor data like camera images are not directly sent on the bus systems, such possibility still exists and need to be considered in the design trade-offs. Thirdly, though not all ADASs are safety-critical, many of them are. This means that the requirements of these applications on aspects like real-time capability, safety, reliability and security need to be met. Finally, current automotive E/E architectures are grouped into domains, and all the domains are connected to a central gateway, where the inter-domain communication is limited. However, many of the ADAS functions are cross-domain in nature [46]. These would introduce new challenges to the current domain-based architecture.

# Plug-and-Play (PnP) and Software Update

Increasingly more new and advanced functions are being developed and deployed in vehicles, especially in the ADAS and infotainment domain. However, the design and development cycle of software and electronics is much shorter than the life cycle of a car, which can be up to about 15 years [1], not to mention the additional years of the design and development of the car. Therefore, with the current static architecture, it is difficult for a vehicle to be equipped with the newest software functions. It would be advantageous for the customer, if the new software functions can be installed or existing software functions be updated after the car has been sold. This topic is commonly referred to as software update and PnP. Currently, software updates are already available for some vehicles. However, this update is currently only limited to some specific ECUs, e.g., the Headunit. The software update and PnP of new applications are currently not yet standard practice. To enable this, there are several challenges that need to be addressed, including the connectivity for software download and dynamic platform that supports the deployment of the software and the reconfiguration of the system, e.g., the re-allocation of the computation and communication resources.

#### Connectivity

Another important trend in modern automotive industry is connectivity. Modern car now connect to other cars, road infrastructure units through wireless technologies [47]. This family of technologies are often referred to as Car2X technologies or Intelligent Transportation System (ITS). The connectivity of course offers a lot of advantages and at the same time brings new design challenges to the E/E systems. On one hand, the connectivity enables cars to connect to other vehicles and road side units in the surroundings for driver assistance or vehicle coordination functions. It also allows the vehicles the connection to the cloud and back-end servers, which can provide live information, online software updates and even

computation capacity to the vehicles. On the other hand, it also poses challenges in terms of security, reliable communication and extra latencies if some functions are cloud-based.

#### Automotive Ethernet

Conventional bus systems in the automotive domain include CAN, LIN, MOST and FlexRay. These protocols are very different in nature and are designed to accommodate requirements of applications in different domains. Although these bus protocols were tailored to fulfill the requirements of their corresponding domain, as the size and complexity of the system increase, these bus protocols are slowly reaching their limits, and not meeting the future requirements in terms of higher bandwidth, flexibility, scalability, etc. Furthermore, although updating the current bus systems is possible (e.g., CAN FD and TTCAN), they do not provide a solution that can be scaled into the future. Therefore, the automotive industry has been exploring a new bus protocol that are sufficiently tested and proved and meet the steadily more complex requirements in the automotive domain. One promising candidate is the Ethernet protocol, which has been widely used in the Internet and office networks. Recent development in the Ethernet protocols like AVB [14] and TSN [15] can possibly also meet the requirements of the applications in the automotive domain. Another major advantage of Ethernet is that it is used and supported by a much larger community than the automotive industry. This means that the methods, tools, experiences and expertise of the other communities can be transferred to the automotive domain. One example is that the BroadR-Reach technology [25], which is de-factor standard PHY layer technology in automotive Ethernet, was developed by Broadcom. Although there has been a lot of work going on in the automotive Ethernet in recent years, there is, however, not yet a clear and standardized definition of what is automotive Ethernet. Instead, there are a collection of many relevant IEEE standards [14, 16, 17] that offer a wide spectrum of features and not all of the features are implemented in vehicles and which features to implement might depend on the OEMs. In addition, although there has been predictions that Ethernet is going to replace current bus systems, it is still not clear about the time line and art of this. It is, however, expected [11, 22] that Etherent will firstly replace MOST in the infotainment domain, then serve as a back-bone between the different domains [23]. Since the recent standards of Ethernet have only been finalized recently (AVB in 2011 and TSN only partially finalized in 2015 and 2016), there still needs to be considerable effort in the design, analysis methods and tool support for these new protocols before Ethernet can be deployed in full fledge in vehicles.

# $\mathbf{CPS}$

CPSs has emerged as one important research domain in the past decade [48–51]. The motivation behind this domain is that currently increasingly more control-centric embedded systems are deployed in real-life applications. As conventional embedded systems focus more on the side of the embedded computing units, the CPS paradigm emphasizes on the tight interaction between the computational units and the physical processes to be controlled. This paradigm enables the consideration of control design and embedded platform design in a holistic manner, thus preventing false assumptions of the other side and reducing the design conservativeness. By employing the CPS-oriented methods, it is usually possible to optimize the control and system design jointly according to certain objectives like control performance, resource utilization, etc [52, 53].

## **1.3.2** Design Requirements and Challenges

The developing trends in the automotive domain mentioned above bring new opportunities to explore and at the same time introduce new challenges to be addressed in the E/E systems. Important requirements as well as challenges concerning this thesis are listed as the following.

#### **Real-Time Requirements**

Real-time requirements refer mainly to the requirements on the timing properties of applications. These properties include for example the response time of the software tasks, the transport latency of the messages, the end-to-end latency and response time of the distributed applications, the jitter and etc. For applications with real-time requirements, some or all of these timing properties need to fulfill certain requirements, e.g., the values are smaller than a given threshold value, which is also known as the deadline.

Increasingly more applications in the automotive domain are control applications. Many of such applications are safety- and time-critical and therefore the real-time capability that the underlying E/E system can provide is one of the major requirements that need to be fulfilled. For example, for a given feedback control loop, the sampling period [54, 55] and the end-to-end delay [56–58] plays an important role in the performance of these applications. The airbag system is another example of application with stringent timing requirements, where the airbag needs to be activated fast enough after the crash to protect the driver and the passengers and the failure to comply with this requirement will lead to catastrophic results. A further reason for the real-time capability is the possibility of the optimization of the functional performance. The functional design of the applications sometimes relies on the timing properties that can be guaranteed by the software implementation of the applications [55, 56]. If better real-time properties can be provided, it is possible to design functions that can achieve better performance.

The real-time capability has always been one of the major requirements in the automotive embedded systems. However, as increasingly more safety-critical control applications are implemented in the vehicles and many of such applications are time-critical, further challenges are imposed. Firstly, increasingly more software and messages bring growing complexity for the design methods [26, 59]. Secondly, there are increasingly more applications that are of inter-domain nature [23, 46], e.g., some ADAS systems. This requires the cross-domain communication, which spans over two or more (heterogeneous) bus clusters thus complicates the design and analysis since possibly different bus protocols, gateways and processor scheduling schemes need to be considered.

# Design and Analysis for Communication Protocols

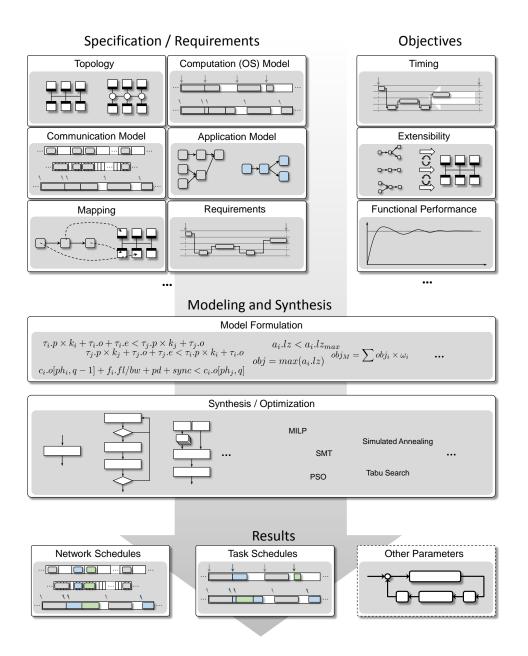

The design and analysis for the communication protocols is an essential topic for the automotive E/E architecture. There could be several aspects of requirements on the communication bus systems. One of the most important is the timing properties. These include, e.g., the transport latency and jitter. Other important requirements include the bandwidth, fault-tolerance, cost, etc [11]. The communication protocols like CAN and FlexRay specify the basic mechanisms. However, there are still a number of parameters to be configured, e.g., priority, schedule, signal-to-frame mapping, etc. The analysis refers to the process of determining whether the requirements are met given a set of values for the parameters. For example, one important analysis here is the timing analysis. For safety- and time-critical systems, the worst-time timing guarantee needs to be provided to ensure the non-functional safety of the system. There have been numerous works on the timing analysis of bus protocols, including CAN [30], FlexRay [60, 61] and Ethernet [62–64], and end-to-end timing analysis methods [65-67]. The design of the communication refers to the process of choosing the values of the parameters so that the requirements are met, and possibly some objectives can be optimized. Towards this, efficient design methods are important. Manual or ad hoc design of the parameters can be a tedious and error-prone process. Automated design approaches are more efficient and safe in comparison. One important set of design methods is the synthesis methods. These methods usually model the communication protocols and, based on the models, use different synthesis or optimization methods to obtain the desired parameters [55, 59, 68, 69]. The actual method used depends a lot on the nature of the protocol. Section 1.4 will provide a detailed description of the synthesis methods.

There are several challenges for this aspect. Firstly, new protocols introduce new models, which need to be derived and efficiently formulated. For example, the modeling of the switched Ethernet is different from conventional broadcast bus systems. AVB and TSN standards introduce further features, which are quite challenging to model, both for the analysis and for the design problem. Secondly, the evolving requirements and increasing size also pose additional challenges. It is known that for both design and analysis methods, the computational effort required increases as the size of the system increases. Therefore, as the size of the system increases, the problem could become intractable using the existing methods. Timing analysis techniques usually involves a certain level of pessimism and this pessimism could also grow with the size of the system. More complex requirement, e.g., in the ADAS domain, also poses challenges. Furthermore, in future applications where the connection with the cloud is involved, the parameters and timing between the vehicle and the cloud need to be considered. In addition, incremental design is yet another challenge. The design of automotive systems usually follows an iterative design paradigm [70, 71]. This means that when new components are added to the system, the design of the existing components are kept as less changed as possible, to reduce the cost of re-design, re-test and re-validation. Such a scheme requires also extensible design [70, 72] as well as efficient incremental design methods [71].

## **Resource-Efficient Design**

There are several types of resources in embedded systems, including, e.g., the computation resources, the memory resources, the communication resources and battery resources [52, 73]. The computation resource refers to the computation capacity of the processors. In the case of a single-core processor, the computation resource can be translated into the computation time. The execution of each software task requires a certain amount of time, and in the case of multiple tasks running on the same processor, a specific computation time needs to be allocated to each. There are typically two levels of memory on a processor, the cache, or on-chip memory, and the main memory. The cache is faster but of higher cost, and therefore can only be equipped with limited size [74]. The communication resource refers to the resource that is used to send messages between the processors and can generally be interpreted as the bandwidth of a communication bus or a network link. It should be pointed out that the exact definition of the computation, memory and communication resource depends strongly on the underlying mechanism or protocol (e.g., OS for the computation resource and bus protocol for the communication resource).

Resource limitation is one common problem in embedded systems. This is especially true for the cost-sensitive automotive industry. Aligned with the trend of ECU consolidation, there are increasingly more software components sharing the same processor or the same bus system. Although the processors are also becoming more powerful, computation resources are still limited. The communication resource on the other hand, can become a bottleneck problem even more easily. The processors can be replaced by more powerful ones and even additional processors can be added. The bus protocol specification usually stays static and adding an extra bus requires considerable more effort (e.g., in design, development, testing and validation). Therefore, the communication resources easily becomes scarce. Hence, the automotive industry has to adopt extensions like CAN FD or new communication protocols like Ethernet. In addition, the design and development in the automotive domain usually follows an iterative approach, where the existing configurations are usually inherited by later design series and only changed when necessary to save the cost for test and validation. Therefore, the resource-efficiency not only needs to be considered for the current design, but potentially also for future design [71]. A third reason is that there are usually some design conservativeness for safety purposes. Engineers for the function design and the system design need to take some assumption of the other side. In safety-critical applications, this assumption tends to be conservativeness so that the safety can be guaranteed [53, 73]. This design margin also consumes certain amount of embedded resources. Finally, as mentioned by some research works [54], sometimes some trade-off between different requirements can be made between the resource consumption and the functional performance. Therefore, when complying with the functional requirements, it would be possible to trade some functional performance with resource conservation.

The resource-efficient design also faces some challenges. The first challenge is due to the growing size and complexity of the system again, which makes the modeling and optimization more difficult. The other challenge is ensuring the safety of the system. When not adequate resources are provided because of resource conservation, the functional and non-functional correctness of the application can be jeopardized, thus leading to severe consequences for the safety-critical systems.

#### Flexible and Reconfigurable Design

Flexibility and adaptivity is another requirement that is becoming increasingly evident in the automotive domain. Traditionally, the configuration of the E/E system has been quite static. On the ECU side, the software components are compiled with the operating system into one single binary file and flashed onto the hardware and the software on most ECUs does not change during the entire life cycle of the vehicle. Similarly for the communication bus systems, the communication relationship between the ECUs and the mapping from signal-to-frame and frame-to-schedule- (or priority) are statically configured. The reason for this is that for safety-critical systems, the reduction of uncertainty contributes to the verifiability and determinism of the system [75].

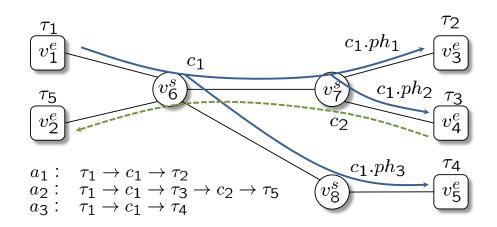

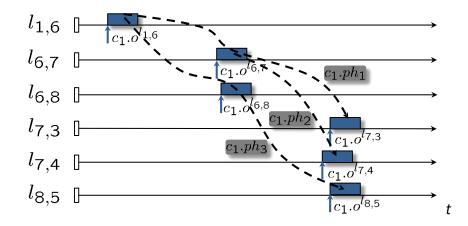

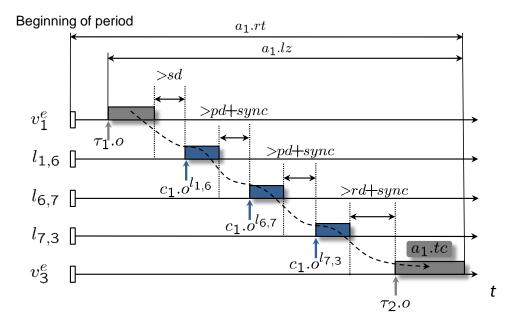

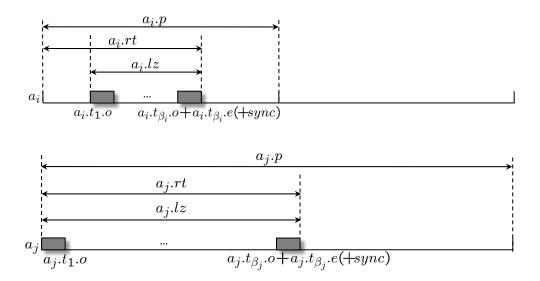

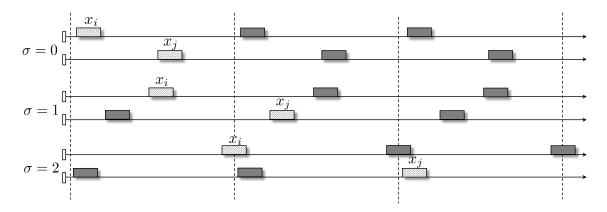

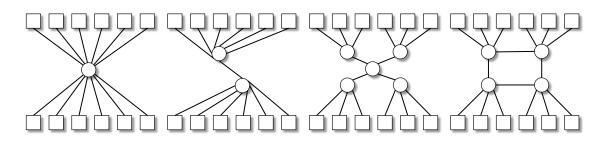

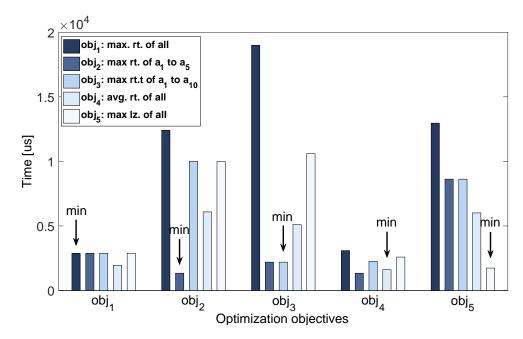

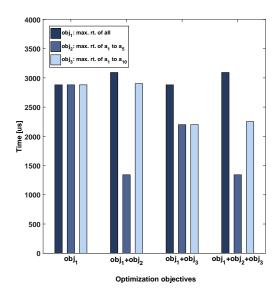

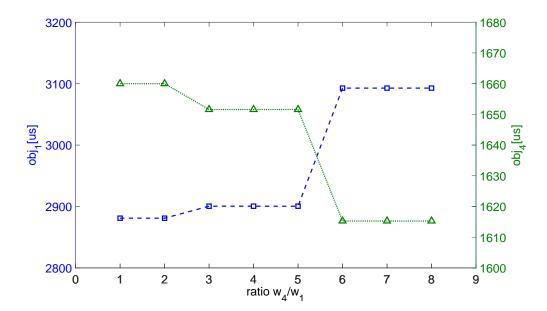

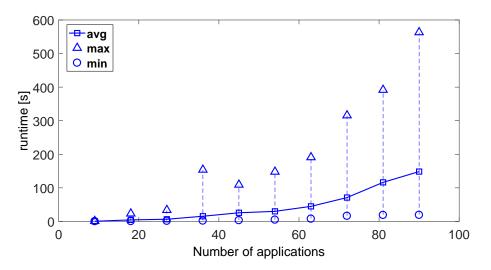

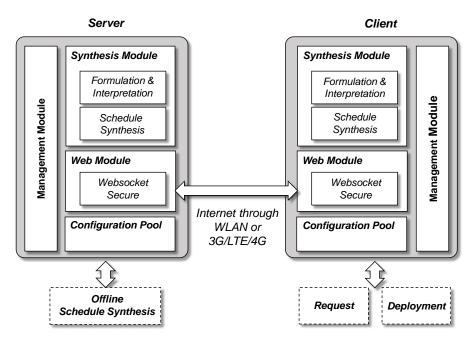

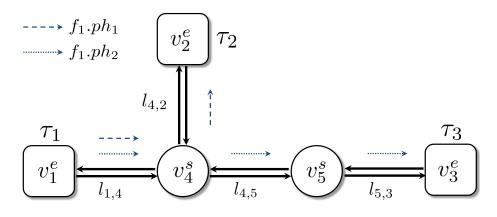

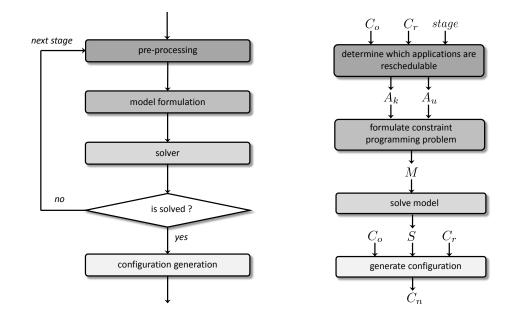

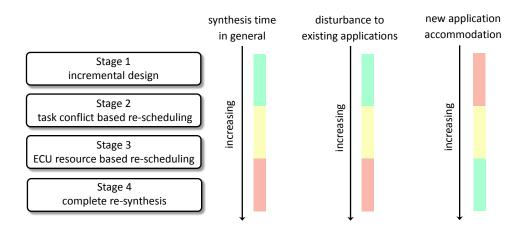

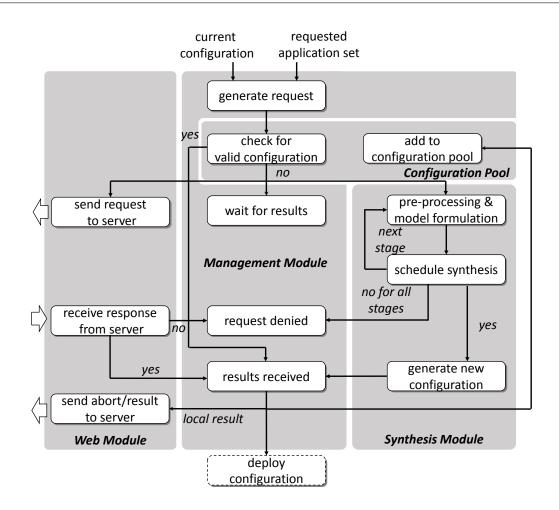

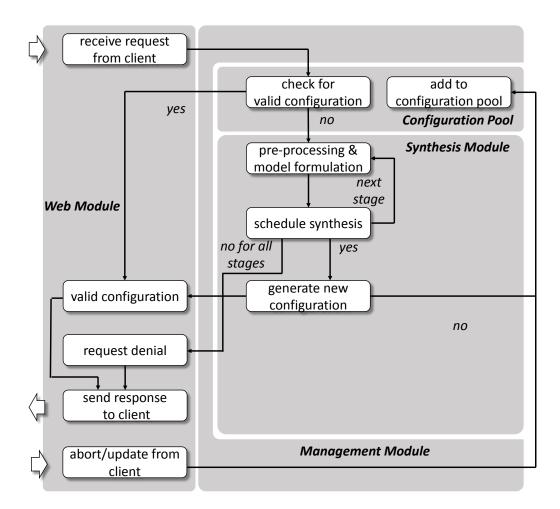

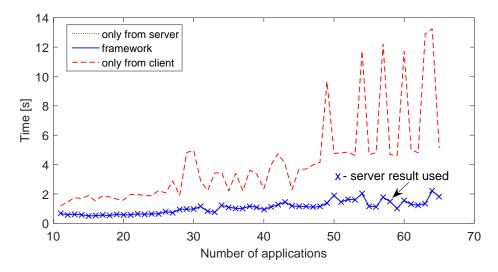

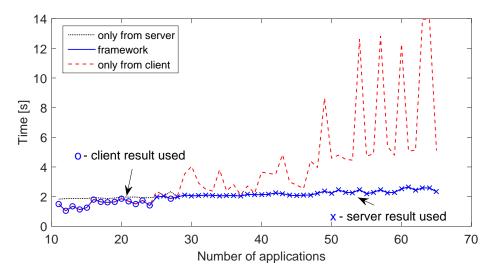

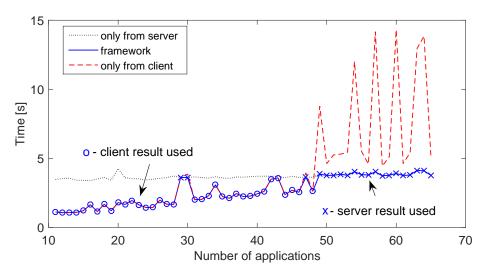

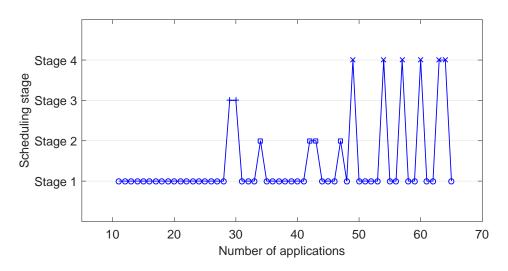

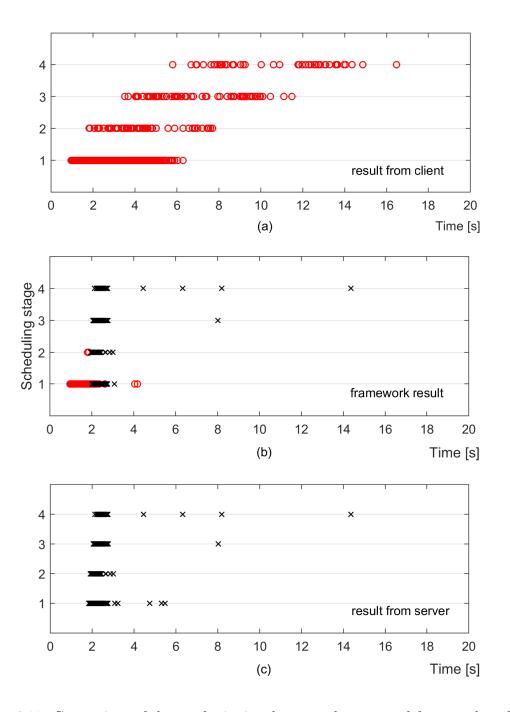

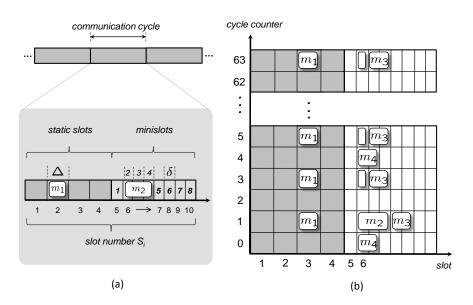

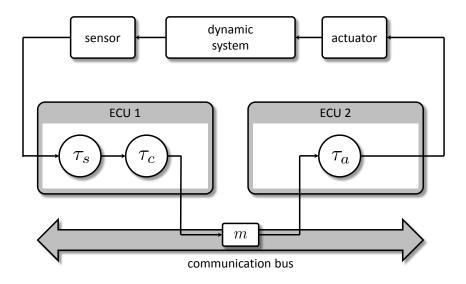

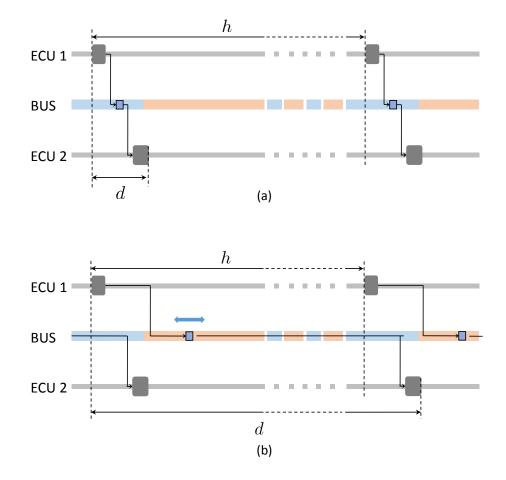

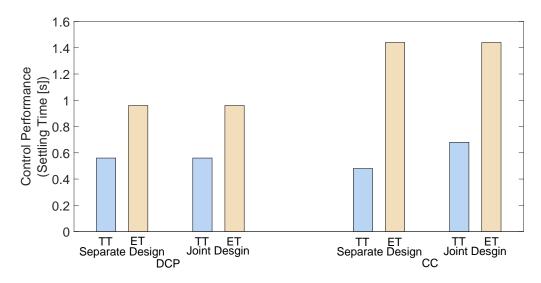

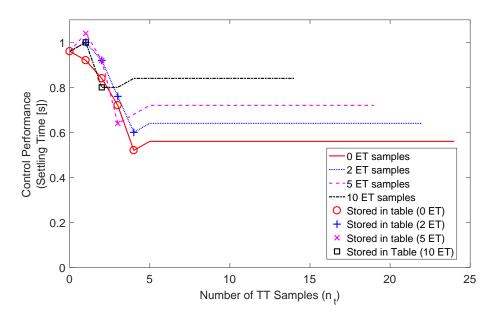

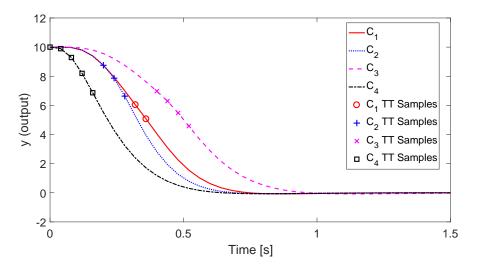

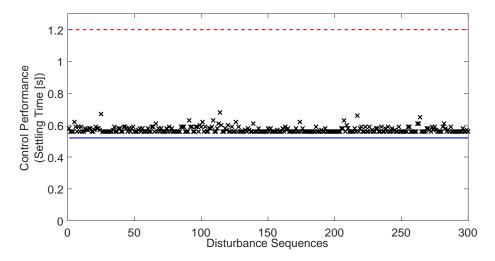

However, this static paradigm might not be suitable for future requirements anymore. First of all, the rapid development in the ADAS and infotainment domain leads to increasingly more software functions developed in recent years. However, the design and development cycle of software is much shorter than the life cycle of a car. Therefore, the software functions of a car can easily become 'outdated'. It would be advantageous for the customer, if newly developed applications can be downloaded and installed on vehicles already sold. This ability is also known as PnP [4, 24, 76]. Furthermore, as the vehicle becomes increasingly software-intensive, the necessity of constant software updates has become obvious. These software updates can be used to fix flaws or add additional features. For example, Tesla has enabled the autonomous driving feature by remote software updates [44, 45]. To enable the software updates and PnP, the underlying system needs to possess certain level of flexibility and re-configurability, so that software can be updated, exchanged, installed and the necessary resources for them can be allocated and re-allocated. Secondly, there are increasingly more software applications that are multi-mode applications. Different operating modes might require different level of embedded resources. Towards resource-efficient design, it would be advantageous, if the embedded resources can be re-allocated. Both of the aforementioned aspects are reinforced by the increasing complexity and the ECU consolidation, where more applications are sharing the same resources.