## Mitigating and Resolving Performance Isolation Issues of PCIe Passthrough and SR-IOV in Multi-Core Virtualization

Andre Oliver Richter

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

### Doktor-Ingenieurs (Dr.-Ing.)

genehmigten Dissertation.

Vorsitzender:

Prof. Dr.-Ing. Wolfgang Kellerer

### Prüfende der Dissertation:

- 1. Prof. Dr. sc. techn. Andreas Herkersdorf

- 2. Prof. Dr.-Ing. Dr. h. c. Jürgen Becker, Karlsruher Institut für Technologie (KIT)

Die Dissertation wurde am 24.04.2017 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 27.10.2017 angenommen.

# Danksagung

Zuallererst möchte ich meinem Doktorvater Prof. Dr. sc. techn. Andreas Herkersdorf für die Betreuung dieser Arbeit danken. Er hat es mir ermöglicht an einem spannenden und für die weitere Zukunft sehr relevanten Thema zu forschen und damit den Grundstein für diese Arbeit gelegt. Seine Ideen in technischen Meetings halfen mir, sehr schnell ein passendes Gebiet zu identifizieren, auf dem ich forschen konnte. Hervorheben möchte ich auch Prof. Herkersdorfs menschliche Führung, die seinen Lehrstuhl zu einem angenehmen und vertrauensvollen Arbeitsumfeld für mich machte.

Besonderer Dank gilt auch Prof. Dr.-Ing. Dr. h. c. Jürgen Becker als Zweitprüfer dieser Arbeit und Prof. Dr.-Ing. Wolfgang Kellerer für den Vorsitz der Prüfungskommission.

Weiterer Dank gilt:

Dr.-Ing. Thomas Wild für seinen Input in technischen Meetings und seine Hilfe bei organisatorischen Dingen aller Art, vor allem im ARAMiS Projekt. Außerdem für die Möglichkeit der Tutorentätigkeit im Praktikum VHDL und die dortige Betreuung, durch die ich den Lehrstuhl schon als Student kennen lernen konnte.

Christian Herber, mit dem ich über die Jahre stets effektiv zusammen an diversen Publikationen und im ARAMiS Projekt gearbeitet habe und bei unseren Dienstreisen immer eine gute Zeit hatte.

Holm Rauchfuss, der beigetragen hat, dass der Lehrstuhl Partner im ARAMiS Projekt wurde. Dadurch konnte die Stelle geschaffen werden, auf der ich eingestellt wurde. Des Weiteren für die Betreuung während meiner Werkstudententätigkeit, welche meine erste Arbeitsstelle am Lehrstuhl war.

Allen anderen Kollegen für die gute Zeit, die lockere Atmosphäre, den guten Umgang, die vielen Dart Matches und natürlich die hitzigen Debatten (nicht zwangsweise immer nur über Forschung).

Meiner Frau Susanne, die mich immer aufs Neue motiviert hat, und vor allem gegen Ende eine große Unterstützung in jeglicher Hinsicht war. Zu guter Letzt meinen Eltern, für ihre Geduld und ihr Vertrauen während der Schulzeit und die bedingungslose Unterstützung während dem Studium. Ihr habt diesen Weg geebnet.

# Zusammenfassung

Leistungsisolierung ist eine zentrale Herausforderung in virtualisierten Multicore Systemen. Sie beschreibt die Fähigkeit eines Wirtsystems zur Verhinderung oder Limitierung von Leistungsinterferenzen zwischen mehreren Virtuellen Maschinen (VMs), welche auf einem Wirtsystem ausgeführt werden und sich dessen Hardware-Ressourcen teilen. Ist nur unzureichende Isolierung geboten, wird es möglich, dass bösartige oder defekte VMs Leistung von nebenläufigen VMs oder dem Wirtsystem selbst stehlen oder vermindern. In der Cloud-Computing Domäne, in der virtualisierte Multicore Server dem aktuellen Stand der Technik entsprechen, kann dies zu Vertragsverletzungen zwischen Kunden und Anbieter führen. In der Domäne für eingebettete Systeme, in welcher virtualisierte Multicore Systeme in naher Zukunft auftauchen werden, können Probleme mit der Leistungsisolierung sogar zur Verletzung von Realzeitanforderungen führen, was letztendlich die Systemsicherheit gefährden könnte. Da virtualisierte Systeme viele gemeinsam-benutzte Ressourcen verwenden, z.B. CPU-Kerne, Caches oder I/O Geräte, muss Leistungsisolierung immer individuell bewertet werden.

Diese Arbeit präsentiert Forschungsbeiträge zur Leistungsisolierung der neusten Generation von I/O Virtualisierungstechnologie, namentlich PCIe passthrough und Single Root I/O Virtualization (SR-IOV). Diese Virtualisierungstechnologie ermöglicht niedrige Latenzen und hohe Leistung, und ist bereits in kommerziellen Geräten erhältlich. Die Arbeit zeigt auf, dass die Leistungsisolierung von PCIe passthrough und SR-IOV durch Denial-of-Service (DoS) Angriffe bösartiger oder defekter VMs gebrochen werden kann, indem passthrough und SR-IOV Hardware mit sinnlosen PCIe Paketen überflutet wird. Zum Beispiel führt ein DoS-Angriff auf einen SR-IOV-fähigen Zweiport Gigabit Ethernet Adapter zu einer Verminderung des Durchsatzes von 941 Mbit/s zu 615 Mbit/s (-35%) Derselbe Angriff führt zu einer Verminderung der SSD-Leistung des Wirtsystems um 77%. Diese Arbeit untersucht diesen Angriffsvektor gründlich, steuert eine Klassifikation verschiedener DoS-Angriffstypen bei und präsentiert ein Modell, welches die architekturellen Probleme in aktueller Hardware beschreibt, die die DoS-Angriffe ermöglichen.

Des Weiteren werden zwei domänenspezifische Lösungen präsentiert, welche die entdeckten Isolierungsprobleme abschwächen oder lösen. Die Lösung für die Cloud Domäne verwendet schlanke Hardware-Monitoring Erweiterungen in passthrough Geräten, um DoS-Angriffe zu entdecken und mit Software-Scheduling abzuschwächen. Zum Beispiel ermöglicht sie die Leistung einer Apache Webserver VM von 51.3% während eines DoS-Angriffs zurück auf 97% zu heben. Als Lösung für Embedded Systeme werden zwei integrierte Hardware-Architekturen vorgeschlagen. Diese funktionieren optionale und bis dato vernachlässigte QoS Erweiterungen der PCIe Spezifikation so um, dass der DoS-Angriffsvektor geschlossen wird und Angriffe komplett verhindert werden. Die erste Ar-

#### Zusammenfassung

chitektur ist für Scheduling-Freiheit optimiert, die zweite für minimale Hardwarekosten. Die Vor- und Nachteile der beiden Architekturen werden anhand von Evaluierungsergebnissen diskutiert.

Nach meinem Wissen sind die Beiträge, welche in dieser Arbeit präsentiert werden, die ersten die eine umfassende Untersuchung von DoS-Angriffen auf PCIe passthrough und SR-IOV anstellen, und Beiträge zur Lösung der entdeckten Leistungsisolierungsprobleme leisten.

# Abstract

Performance isolation is a key challenge in virtualized multi-core systems. It describes a host system's capability to prevent or limit performance interference between multiple Virtual Machines (VMs) that execute on it and share its hardware resources. If a host system provides insufficient performance isolation, it is possible for malicious or malfunctioning VMs to degrade or steal performance from concurrent VMs or the host itself. In the cloud computing domain, where virtualized multi-core servers are state-ofthe-art, performance interference could result in broken service level agreements between providers and customers. In the embedded computing domain, where virtualized multicore systems will surface in the near future, performance isolation issues might even result in violation of real-time requirements and therefore compromise system safety. As virtualized systems employ many shared resources, e.g. CPU cores, caches or I/O devices, performance isolation must be assessed individually.

This thesis contributes research on performance isolation of PCIe passthrough and Single Root I/O Virtualization (SR-IOV), which is the latest generation of I/O virtualization technology. It enables low latency, high performance virtual I/O and is already implemented in commercial off-the-shelf devices. The thesis shows that performance isolation of PCIe passthrough and SR-IOV can be broken with Denial-of-Service (DoS) attacks from malicious or malfunctioning VMs that flood passthrough and SR-IOV hardware with spurious PCIe packets. For example, DoS attacks on an SR-IOV capable dualport gigabit Ethernet adapter cause a throughput degradation from 941 Mbit/s down to 615 Mbit/s (-35%). The same attack causes a 77% performance degradation of the host system's SSD storage. The thesis thoroughly investigates this attack vector, contributes a classification of different DoS attack types and presents a model that explains the architectural shortcomings in current hardware that enable the attacks.

Additionally, two domain specific solutions for cloud and embedded systems are presented, which mitigate and resolve the discovered performance isolation issues. The cloud solution utilizes lightweight hardware monitoring extensions within passthrough I/O devices to detect attacker VMs and mitigate their DoS attacks with software scheduling. For instance, performance of an Apache webserver VM is restored from 51.3% during DoS attacks back to 97%. The solution for embedded systems proposes two integrated hardware architectures that repurpose optional and neglected QoS extensions of the PCIe specification in order to close the attack vector and completely prevent DoS attacks. The first architecture is optimized for scheduling freedom, the second for minimal hardware costs. Results of an evaluation are used to discuss pros and cons of both architectures.

To the best of my knowledge, work presented in this thesis is the first that comprehensively investigates DoS attacks on PCIe passthrough and SR-IOV, and contributes towards solving the resulting performance isolation issues.

# Contents

| Danksagung |                   |         |                                                                                             |     |   | iii  |  |  |  |  |

|------------|-------------------|---------|---------------------------------------------------------------------------------------------|-----|---|------|--|--|--|--|

| Ζι         | Zusammenfassung v |         |                                                                                             |     |   |      |  |  |  |  |

| Ał         | Abstract          |         |                                                                                             |     |   |      |  |  |  |  |

| Co         | Contents          |         |                                                                                             |     |   |      |  |  |  |  |

| Lis        | st of             | Figures | 5                                                                                           |     |   | xiii |  |  |  |  |

| Lis        | st of             | Tables  |                                                                                             |     |   | xv   |  |  |  |  |

| Ac         | crony             | ms      |                                                                                             |     |   | xvii |  |  |  |  |

| 1          | Intro             | oductio | on                                                                                          |     |   | 1    |  |  |  |  |

|            | 1.1               | Proble  | em Statement                                                                                |     |   | 2    |  |  |  |  |

|            | 1.2               | Contri  | ibutions                                                                                    |     |   | 3    |  |  |  |  |

|            | 1.3               | Outlin  | ne                                                                                          | ••• | • | 5    |  |  |  |  |

| 2          | Stat              | e of th | ie Art                                                                                      |     |   | 7    |  |  |  |  |

|            | 2.1               | Platfo  | rm Virtualization                                                                           |     | • | 7    |  |  |  |  |

|            |                   | 2.1.1   | Spatial Isolation                                                                           |     | • | 8    |  |  |  |  |

|            |                   | 2.1.2   | Performance Isolation                                                                       |     | • | 9    |  |  |  |  |

|            |                   | 2.1.3   | Cloud Computing                                                                             |     | • | 9    |  |  |  |  |

|            |                   | 2.1.4   | Embedded Virtualization                                                                     |     | • | 10   |  |  |  |  |

|            | 2.2               | Softwa  | are-based I/O Virtualization                                                                |     | • | 11   |  |  |  |  |

|            |                   | 2.2.1   | Emulation                                                                                   |     | • | 11   |  |  |  |  |

|            |                   | 2.2.2   | Paravirtualization                                                                          |     | • | 13   |  |  |  |  |

|            |                   | 2.2.3   | Performance, Pros and Cons                                                                  |     | • | 14   |  |  |  |  |

|            |                   | 2.2.4   | Performance Isolation Approaches                                                            |     | • | 15   |  |  |  |  |

|            | 2.3               |         | vare-based I/O Virtualization: Passthrough I/O with PCIe and S                              | R-  |   |      |  |  |  |  |

|            |                   | IOV     | •••••••••••••••••••••••••••••••••••••••                                                     |     |   | 16   |  |  |  |  |

|            |                   | 2.3.1   | PCI Express (PCIe)                                                                          |     |   | 17   |  |  |  |  |

|            |                   |         | $2.3.1.1  \text{Topology}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |     |   | 17   |  |  |  |  |

|            |                   |         | 2.3.1.2 Link Parameters and Bit Rates                                                       |     |   | 18   |  |  |  |  |

|            |                   |         | 2.3.1.3 PCIe Functions, Memory Mapped I/O and Drivers .                                     |     |   | 18   |  |  |  |  |

|            |                   |         | 2.3.1.4 Transaction Characteristics and Flow Control                                        |     | • | 20   |  |  |  |  |

### Contents

|   |      | 2.3.2    | PCIe Single Root I/O Virtulization (SR-IOV) 20                                                             |

|---|------|----------|------------------------------------------------------------------------------------------------------------|

|   |      |          | 2.3.2.1 Physical and Virtual Functions                                                                     |

|   |      |          | 2.3.2.2 Adoption                                                                                           |

|   |      | 2.3.3    | Performance, Pros and Cons                                                                                 |

|   |      | 2.3.4    | Performance Isolation Approaches                                                                           |

| 3 | Inve | stigatio | on of PCIe Passthrough and SR-IOV Performance Isolation Issues 27                                          |

|   | 3.1  | _        | t Model $\ldots \ldots 27$    |

|   | 3.2  |          | mentation of DoS Attacks                                                                                   |

|   | 3.3  | -        | ation Platform                                                                                             |

|   | 3.4  | Evalua   | ation Methodology $\ldots \ldots 31$ |

|   |      | 3.4.1    | Latencies of 32 bit PCIe Read Transactions                                                                 |

|   |      | 3.4.2    | Network Performance – TCP and UDP Throughput                                                               |

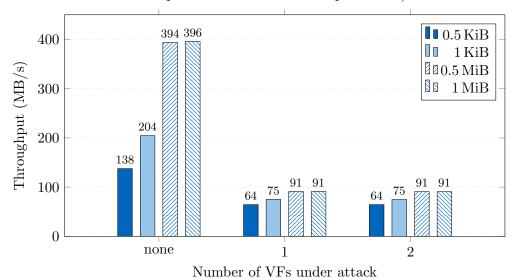

|   |      | 3.4.3    | Storage Performance – SSD Throughput                                                                       |

|   | 3.5  | Exper    | iments and Results                                                                                         |

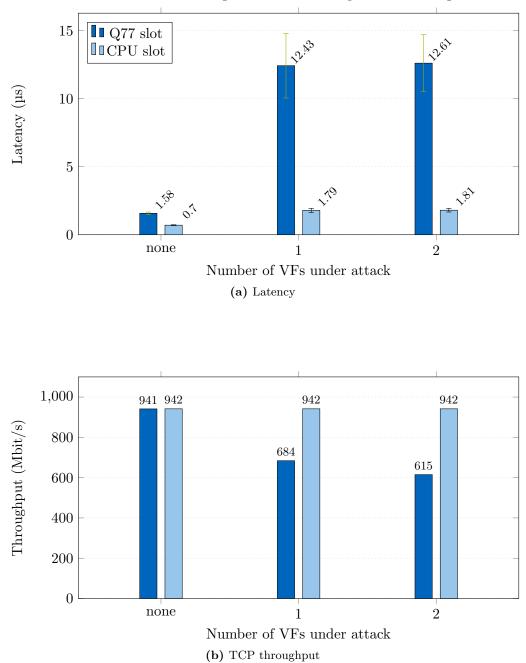

|   |      | 3.5.1    | Experiment 1: Attacking SR-IOV Virtual Functions                                                           |

|   |      |          | 3.5.1.1 Baseline Performance                                                                               |

|   |      |          | 3.5.1.2 Experimental Setup and Results                                                                     |

|   |      |          | 3.5.1.3 Second-Order Effects                                                                               |

|   |      |          | 3.5.1.4 Summary                                                                                            |

|   |      | 3.5.2    | Experiment 2: Influence of the DoS Victim's Processing Speed 37                                            |

|   |      |          | 3.5.2.1 Fine-Grained Runtime-Configurable Processing Speeds<br>via FPGA                                    |

|   |      |          | 3.5.2.2 Experimental Setup and Results                                                                     |

|   |      |          | 3.5.2.3 Processing Speed Variations in COTS Devices 41                                                     |

|   |      |          | 3.5.2.4 Summary                                                                                            |

|   |      | 3.5.3    | Experiment 3: Influence of Switching Intermediaries                                                        |

|   |      |          | 3.5.3.1 Experimental Setup and Results                                                                     |

|   |      |          | 3.5.3.2 Summary                                                                                            |

|   |      | 3.5.4    | Experiment 4: Degradation of Chipset Disk I/O                                                              |

|   |      |          | 3.5.4.1 Experimental Setup and Results                                                                     |

|   |      |          | 3.5.4.2 Summary                                                                                            |

|   | 3.6  | System   | n Model for PCIe DoS Attacks on Ethernet NICs                                                              |

|   | 3.7  | DoS A    | Attack Classification                                                                                      |

|   |      | 3.7.1    | Inter-Device Attack                                                                                        |

|   |      | 3.7.2    | Intra-Device Attacks                                                                                       |

|   |      |          | 3.7.2.1 Inter-Function Attack                                                                              |

|   |      |          | 3.7.2.2 Intra-PF Attack                                                                                    |

|   |      |          | 3.7.2.3 Inter-PF Attack                                                                                    |

|   |      | 3.7.3    | Combinations                                                                                               |

|   | 3.8  | Summ     | ary                                                                                                        |

|   |      |          |                                                                                                            |

| 4 | Miti |          | Performance Isolation Issues Through Monitoring and Scheduling |    |

|---|------|----------|----------------------------------------------------------------|----|

|   | 4.1  | Goals a  | and Requirements                                               | 55 |

|   |      | 4.1.1    | Goals                                                          | 55 |

|   |      | 4.1.2    | Requirements                                                   | 56 |

|   | 4.2  | Design   | and Exploration                                                | 57 |

|   |      | 4.2.1    | Monitoring and DoS Attack Detection                            | 57 |

|   |      | 4.2.2    | Exploration of Monitoring Alternatives                         | 58 |

|   |      |          | 4.2.2.1 Monitoring in CPUs                                     | 58 |

|   |      |          | 4.2.2.2 Monitoring in I/O Devices                              | 60 |

|   |      |          | 4.2.2.3 Monitoring in Intermediaries                           | 61 |

|   |      | 4.2.3    | Mitigation                                                     | 61 |

|   |      |          | 4.2.3.1 Isolation via Freeze or Migration                      | 61 |

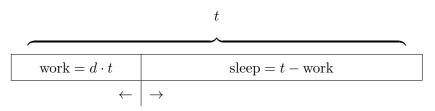

|   |      |          | 4.2.3.2 Attack Throttling via Scheduling                       | 62 |

|   | 4.3  | -        | nentation                                                      | 63 |

|   |      | 4.3.1    | Overview                                                       | 63 |

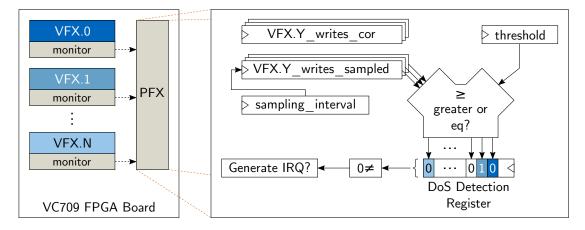

|   |      | 4.3.2    | Monitoring and DoS Detection on FPGA                           | 64 |

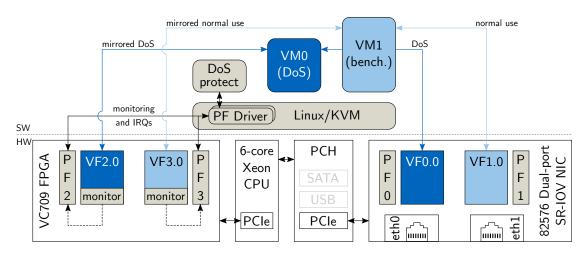

|   |      | 4.3.3    | VC709 PF Driver and DoS Protect Process                        | 65 |

|   |      | 4.3.4    | System Software and Emulation of Monitoring in the 82576       | 66 |

|   | 4.4  |          | ution                                                          | 67 |

|   |      | 4.4.1    | Benchmarks                                                     | 68 |

|   |      | 4.4.2    | DoS Attack Parameters                                          | 68 |

|   |      | 4.4.3    | DoS Detection Threshold                                        | 69 |

|   |      | 4.4.4    | Memcached and Apache Results                                   | 70 |

|   |      | 4.4.5    | Netperf Results                                                | 72 |

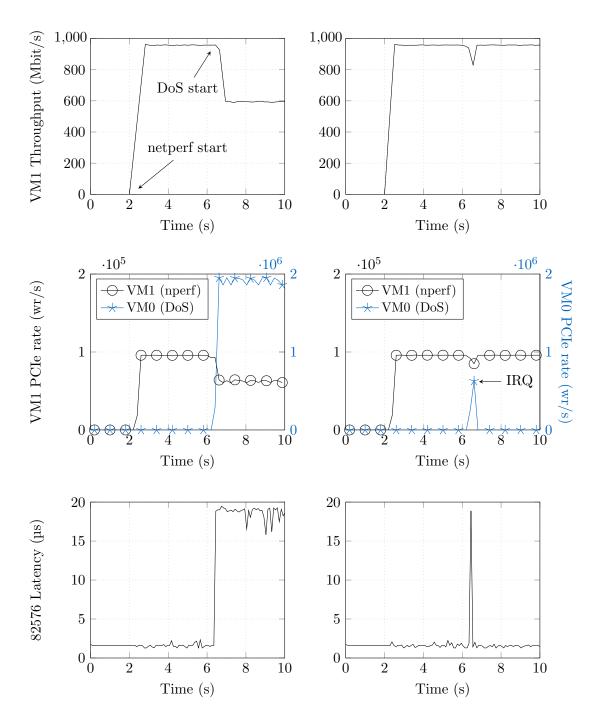

|   |      | 4.4.6    | Trace of DoS Detection and Attacker Freeze                     | 74 |

|   |      |          | 4.4.6.1 Baseline Trace                                         | 74 |

|   |      |          | 4.4.6.2 Mitigation Trace                                       | 76 |

|   |      |          | 4.4.6.3 Optimization Tradeoffs                                 | 76 |

|   |      | 4.4.7    | Mirroring Overhead                                             | 76 |

|   |      |          | 4.4.7.1 Benchmark Overhead                                     | 77 |

|   |      | a        | 4.4.7.2 DoS Attack Overhead                                    | 77 |

|   | 4.5  | Summa    | ary                                                            | 78 |

| 5 | Reso | olving P | Performance Isolation Issues Through PCIe QoS Extensions       | 81 |

|   | 5.1  | -        | and Requirements                                               | 82 |

|   |      | 5.1.1    | Goals Goals                                                    | 82 |

|   |      | 5.1.2    | Requirements                                                   | 82 |

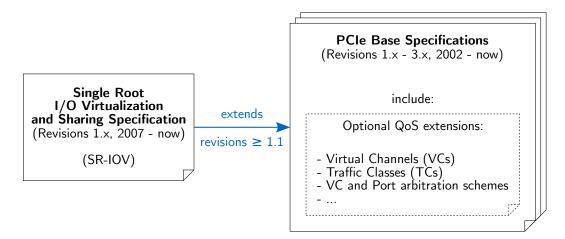

|   | 5.2  | Quality  | y-of-Service Extensions in the PCIe Specification              | 83 |

|   |      | 5.2.1    | Contribution of this Thesis                                    | 83 |

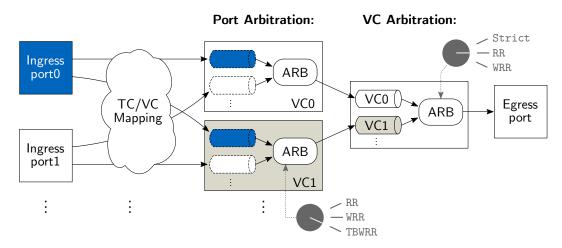

|   |      | 5.2.2    | Overview of the PCIe Specification's QoS Extensions            | 84 |

|   |      |          | 5.2.2.1 TC/VC Mapping                                          | 85 |

|   |      |          | 5.2.2.2 Arbitration                                            | 86 |

|   | 5.3  | System   | nC TLM 2.0 Model of QoS-enabled PCIe Components                | 87 |

|   |      | 5.3.1    | Model Verification Approach                                    | 90 |

### Contents

|    |       | 5.3.2 V   | Verification I | Results . |        |        |       |      |     |     |     |     |   |   |       |   | 90  |

|----|-------|-----------|----------------|-----------|--------|--------|-------|------|-----|-----|-----|-----|---|---|-------|---|-----|

|    | 5.4   | Multi-V   | C Architectu   | ıre       |        |        |       |      |     |     |     |     |   |   |       |   | 93  |

|    |       | 5.4.1     | Architecture   |           |        |        |       |      |     |     |     |     |   |   |       |   | 93  |

|    |       | 5.4.2 I   | Evaluation     |           |        |        |       |      |     |     |     |     |   |   |       |   | 95  |

|    |       | 5.4.3 I   | Multi-VC Ar    | chitectu  | re Sun | nmary  | •     |      |     |     |     |     |   |   |       |   | 97  |

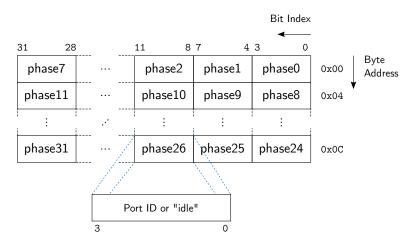

|    | 5.5   | Time-ba   | ased Weighte   | d Roun    | d-Robi | n Arc  | hitec | ture |     |     |     |     |   |   |       |   | 98  |

|    |       | 5.5.1 A   | Architecture   |           |        |        |       |      |     |     |     |     |   |   |       |   | 98  |

|    |       | 5.5.2 I   | Evaluation     |           |        |        |       |      |     |     |     |     |   |   |       |   | 100 |

|    |       | 5.5.3     | FBWRR Are      | hitectu   | re Sum | mary   |       |      |     |     |     |     |   |   |       |   | 102 |

|    | 5.6   | Summar    | ry             |           |        |        | •••   | •••  |     |     |     | •   |   | • |       | • | 102 |

| 6  | Con   | clusion a | nd Outlook     |           |        |        |       |      |     |     |     |     |   |   |       |   | 105 |

|    | 6.1   | Conclus   | ion            |           |        |        |       |      |     |     |     |     |   |   |       |   | 105 |

|    | 6.2   | Outlook   |                |           |        |        | •••   | •••  |     |     |     |     |   | • | <br>• | • | 108 |

| Bi | bliog | raphy     |                |           |        |        |       |      |     |     |     |     |   |   |       |   | 111 |

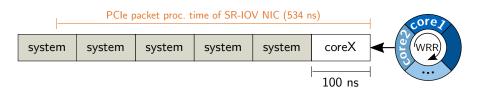

| Α  | Арр   | roximatir | ng Packet P    | rocessir  | ng Tim | ies of | сот   | s f  | PCI | e C | )ev | ice | s |   |       |   | 123 |

# List of Figures

| 1.1  | Overview of contributions                                                                                   | 4  |

|------|-------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Comparison of classic hypervisor types                                                                      | 8  |

| 2.2  | I/O device emulation in a type 1 hypervisor                                                                 | 11 |

| 2.3  | I/O device emulation with type 1 hypervisor and trusted VM                                                  | 12 |

| 2.4  | I/O device emulation in hosted hypervisors                                                                  | 13 |

| 2.5  | Paravirtualized I/O with trusted VM                                                                         | 14 |

| 2.6  | Example of passthrough I/O                                                                                  | 16 |

| 2.7  | Example PCIe topology                                                                                       | 17 |

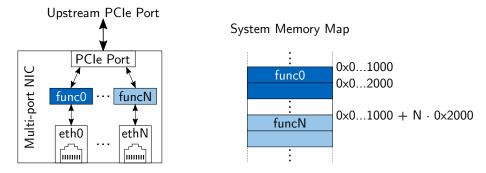

| 2.8  | PCIe multi-function Endpoint                                                                                | 19 |

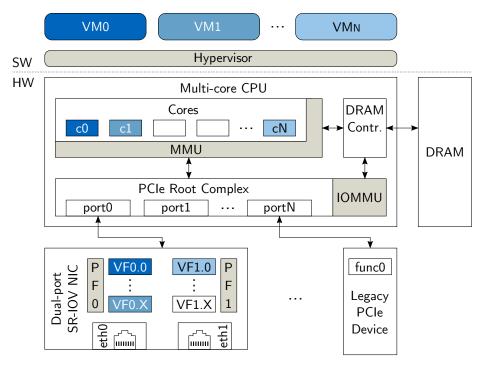

| 2.9  | Virtualized system with SR-IOV device                                                                       | 21 |

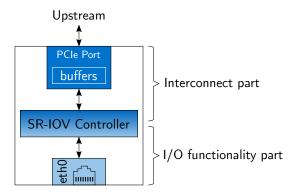

| 2.10 | Dependency between interconnect and I/O functionality $\ldots \ldots \ldots$                                | 24 |

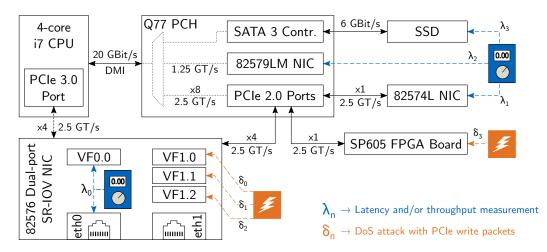

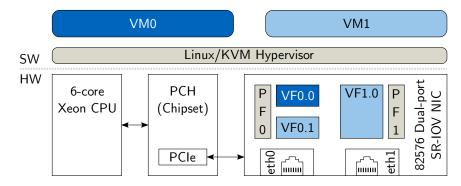

| 3.1  | Block diagram of passthrough/SR-IOV evaluation platform                                                     | 30 |

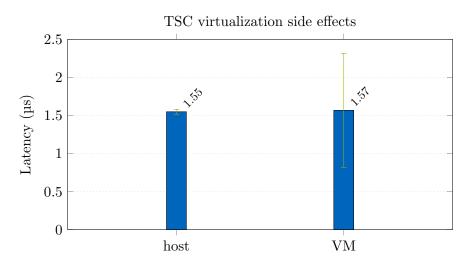

| 3.2  | TSC virtualization side effects                                                                             | 32 |

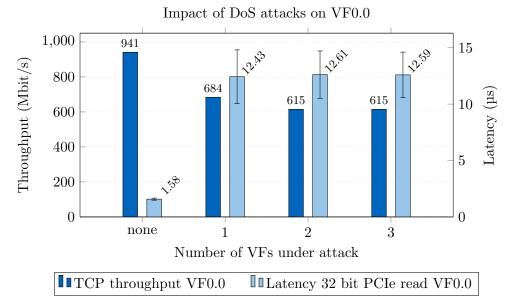

| 3.3  | Impact of DoS attacks on VF0.0                                                                              | 35 |

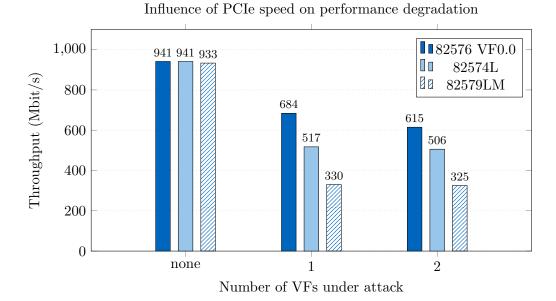

| 3.4  | Influence of PCIe speed on performance degradation                                                          | 36 |

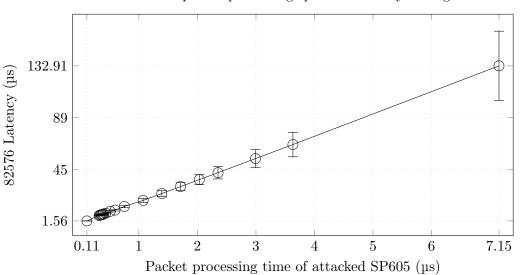

| 3.5  | Influence of packet processing speed on latency during DoS                                                  | 39 |

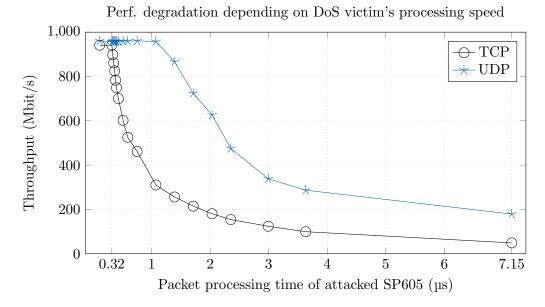

| 3.6  | Perf. degradation depending on DoS victim's processing speed                                                | 40 |

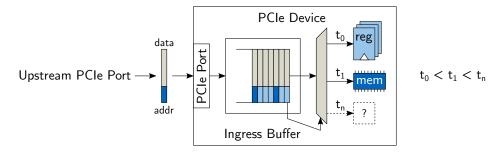

| 3.7  | PCIe device multiple processing speeds                                                                      | 41 |

| 3.8  | Influence of switching intermediaries on performance degradation                                            | 44 |

| 3.9  | Impact of DoS attacks on chipset disk I/O $\hfill \ldots \ldots \ldots \ldots \ldots \ldots$                | 46 |

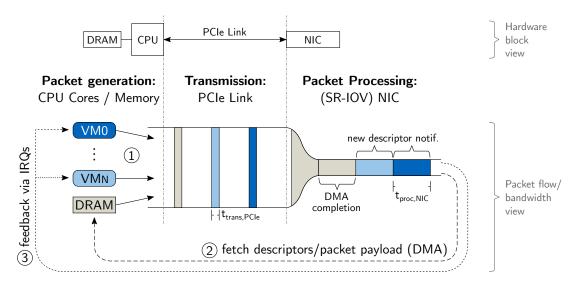

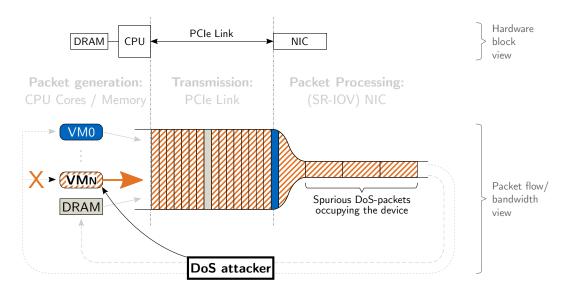

| 3.10 | System model for legal software-NIC communication                                                           | 47 |

| 3.11 | System model for software-NIC communication with a malicious VM                                             | 49 |

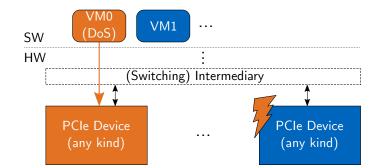

|      | $Inter-device \ attack \ \ \ldots $ | 50 |

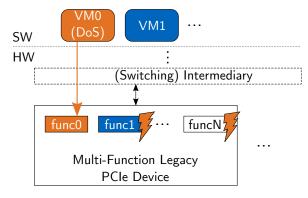

|      | $Inter-function \ attack \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                            | 51 |

| 3.14 | Intra-PF attack                                                                                             | 52 |

|      | Inter-PF attack                                                                                             | 52 |

| 3.16 | DoS attack combinations                                                                                     | 53 |

| 4.1  | High-level design of HW/SW monitoring/mitigation design                                                     | 57 |

| 4.2  | Overview of x86 performance monitoring facilities                                                           | 59 |

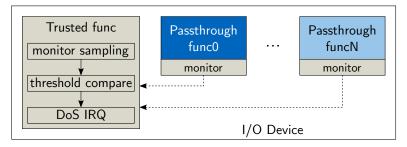

| 4.3  | Design for DoS detection in I/O devices                                                                     | 60 |

| 4.4  | Throttling malicious VMs via scheduling                                                                     | 62 |

| 4.5  | Prototype implementation for mitigating DoS attacks                                                         | 63 |

| 4.6  | Implementation of hardware monitoring and DoS detection on the Virtex-                                      |    |

|      | 7 FPGA                                                                                                      | 64 |

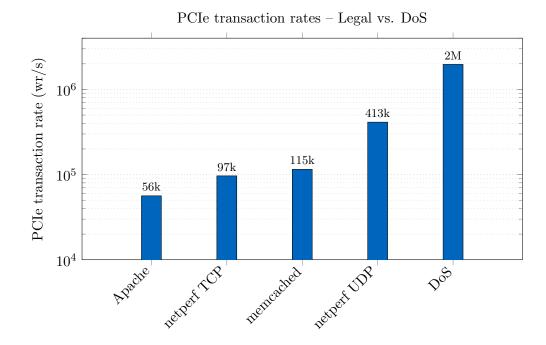

| 4.7  | PCIe transaction rates – Legal vs. DoS                                                                      | 70 |

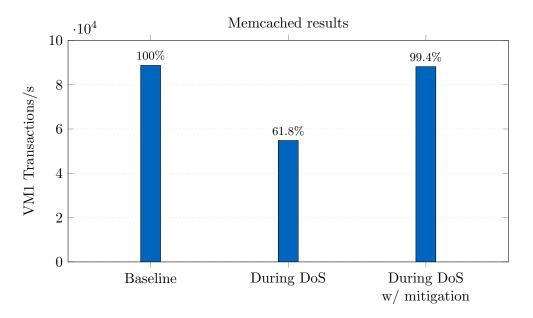

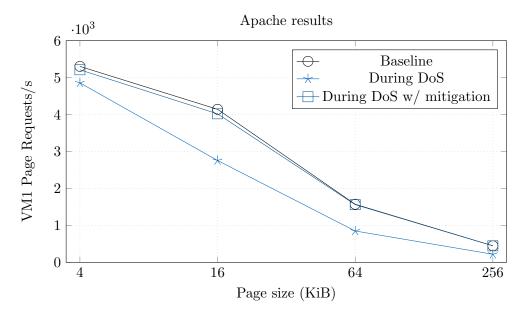

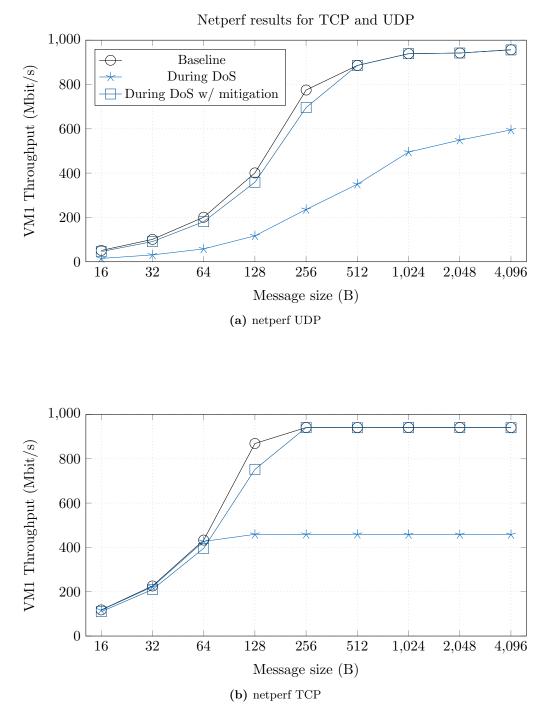

| 4.8  | Memcached results                                                    |

|------|----------------------------------------------------------------------|

| 4.9  | Apache results                                                       |

| 4.10 | Netperf results for TCP and UDP                                      |

| 4.11 | A trace of DoS attack mitigation by freezing the attacker            |

| 5.1  | Relationship between PCIe, its optional QoS extensions and SR-IOV 84 |

| 5.2  | PCIe QoS extensions                                                  |

| 5.3  | TBWRR arbitration table example                                      |

| 5.4  | Block diagram of the real-world lab-setup                            |

| 5.5  | The PCIe hierarchy of the SystemC model                              |

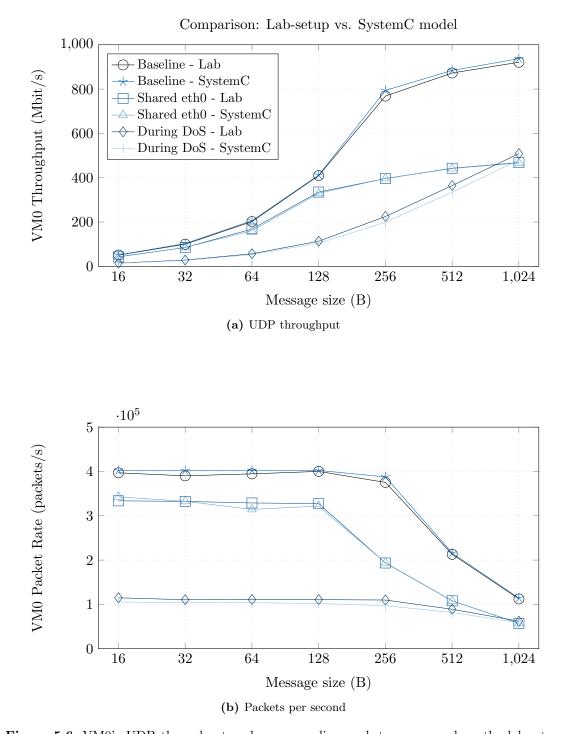

| 5.6  | Comparison: Lab-setup vs. SystemC model                              |

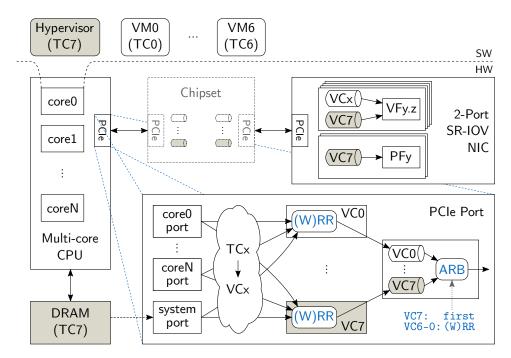

| 5.7  | Multi-VC architecture                                                |

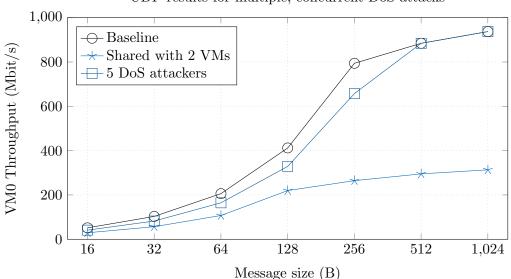

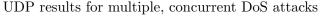

| 5.8  | UDP results for multiple, concurrent DoS attacks                     |

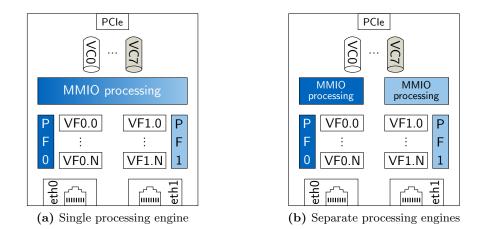

| 5.9  | Comparison of processing engine designs for SR-IOV devices           |

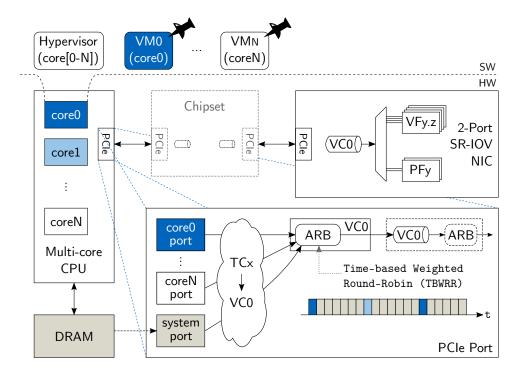

| 5.10 | TBWRR architecture                                                   |

| 5.11 | TBWRR table tailored to the 82576 NIC                                |

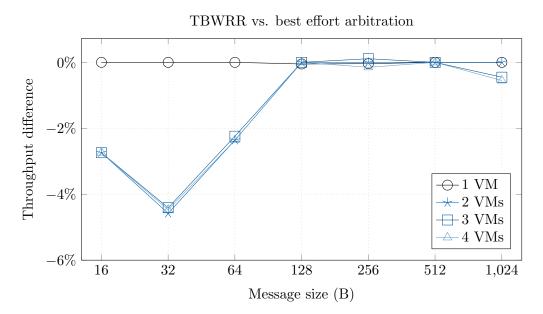

| 5.12 | TBWRR vs. best effort arbitration                                    |

|      | TBWRR table with idle cores                                          |

| 5.14 | TBWRR table with two stage arbitraion                                |

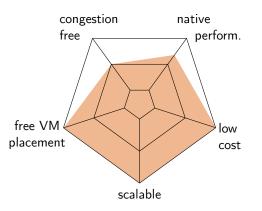

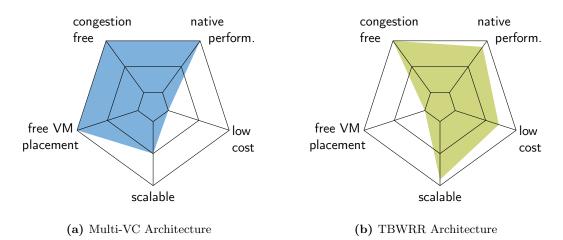

| 6.1  | Characteristics of the cloud computing solution                      |

| 6.2  | Characteristics of the solutions for embedded virtualization         |

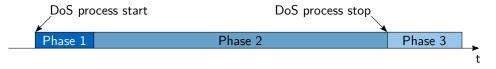

| A.1  | Three phases of a DoS attack                                         |

# List of Tables

| 2.1          | Performance parameters by PCIe version                                                                    | 18 |

|--------------|-----------------------------------------------------------------------------------------------------------|----|

| 3.1          | Transfer times for a 1500 byte Ethernet payload                                                           | 37 |

|              | Latencies for reading from a 82576 NIC VF with and without concurrent DoS attack on VF0.0                 |    |

| $5.1 \\ 5.2$ | Two examples for TC/VC mapping for a port with two VCs Downstream PCIe packet sources classified by trust |    |

# Acronyms

| API   | Application Programming Interface.       |

|-------|------------------------------------------|

| ARI   | Alternative Routing-ID Interpretation.   |

| ARINC | Aeronautical Radio, Incorporated.        |

| ASIC  | Application-Specific Integrated Circuit. |

| BAR   | Base Address Register.                   |

| BIOS  | Basic Input/Output System.               |

| CAN   | Controller Area Network.                 |

| COTS  | Commercial off-the-shelf.                |

| CPU   | Central Processing Unit.                 |

| DMA   | Direct Memory Access.                    |

| DMI   | Direct Media Interface.                  |

| ECU   | Electronic Control Unit.                 |

| EPT   | Extended Page Tables.                    |

| FPGA  | Field-Programmable Gate Array.           |

| GPU   | Graphics Processing Unit.                |

| I/O   | Input/Output.                            |

| IDD   | Integrated Driver Domain.                |

| IOMMU | Input/Output Memory Management Unit.     |

| IP    | Internet Protocol.                       |

| IRQ   | Interrupt Request.                       |

| KVM   | Kernel Virtual Machine.                  |

| LLC   | Last Level Cache.                        |

| MDD   | Malicious Driver Detection.              |

| MMIO  | Memory Mapped I/O.                       |

| MMU   | Memory Management Unit.                  |

| MTU   | Maximum Transmission Unit.               |

| NIC                                                      | Network Interface Card.                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMA                                                     | Non-Uniform Memory Access.                                                                                                                                                                                                                                                                                      |

| OS                                                       | Operating System.                                                                                                                                                                                                                                                                                               |

| PCH<br>PCI<br>PCI-SIG<br>PCIe<br>PF<br>PID<br>PMC<br>PMU | <ul> <li>Platform Controller Hub - The chipset of a computer.</li> <li>Peripheral Component Interconnect.</li> <li>PCI Special Interest Group.</li> <li>PCI Express.</li> <li>Physical Function.</li> <li>Process ID.</li> <li>Performance Monitoring Counter.</li> <li>Performance Monitoring Unit.</li> </ul> |

| QEMU                                                     | Short for Quick Emulator - An open-source hypervisor.                                                                                                                                                                                                                                                           |

| RAM                                                      | Random Access Memory.                                                                                                                                                                                                                                                                                           |

| RR                                                       | Round-Robin.                                                                                                                                                                                                                                                                                                    |

| SR-IOV                                                   | Single Root I/O Virtualization.                                                                                                                                                                                                                                                                                 |

| SSD                                                      | Solid-State Drive.                                                                                                                                                                                                                                                                                              |

| TBWRR                                                    | Time-based Weighted Round-Robin.                                                                                                                                                                                                                                                                                |

| TC                                                       | Traffic Class.                                                                                                                                                                                                                                                                                                  |

| TCP                                                      | Transmission Control Protocol.                                                                                                                                                                                                                                                                                  |

| TSC                                                      | Time-Stamp Counter.                                                                                                                                                                                                                                                                                             |

| UDP                                                      | User Datagram Protocol.                                                                                                                                                                                                                                                                                         |

| UIO                                                      | Userspace I/O.                                                                                                                                                                                                                                                                                                  |

| VC                                                       | Virtual Channel.                                                                                                                                                                                                                                                                                                |

| VF                                                       | Virtual Function.                                                                                                                                                                                                                                                                                               |

| VHDL                                                     | Very High Speed Integrated Circuit Hardware Description Language.                                                                                                                                                                                                                                               |

| VM                                                       | Virtual Machine.                                                                                                                                                                                                                                                                                                |

| WCET                                                     | Worst-Case Execution Time.                                                                                                                                                                                                                                                                                      |

| WRR                                                      | Weighted Round-Robin.                                                                                                                                                                                                                                                                                           |

# **1** Introduction

Virtualization of multi-core server systems is a key enablement technology for the modern cloud computing landscape [1]. Using the virtualization capabilities of modern CPUs [2, 3], it is possible to encapsulate whole Operating Systems (OSs), together with user-applications that run on top of these OSs, into so-called Virtual Machines (VMs). Multiple VMs can execute concurrently on the same physical server and share its hardware, therefore making virtualization an effective method for increasing the utilization of today's multi-core servers. As VMs can be generated, destroyed and migrated on demand, they also introduce flexibility to datacenter operators. These features are also important from an economic perspective. On the one hand, they enable cloud computing providers to boost the efficiency of their expensive hardware by consolidating VMs of multiple customers on a single physical machine. On the other hand, they allow providers to introduce fine-grained and flexible pricing models, which are attractive to customers. For instance, customers can lease virtual servers in the form of access to VMs, which are guaranteed certain shares of a physical server's hardware, e.g. a specific number of cores of a multi-core CPU or a specific share of the server's main memory (RAM). Two prominent cloud computing services offering these pricing models are the Amazon Elastic Compute Cloud (EC2) and Microsoft Azure.

However, this multi-tenancy model can only work if strong inter-VM isolation in two dimensions is in place. First of all, VMs must be isolated in the spatial domain. On consolidated servers, VMs from unknown origins execute concurrently, which means that they cannot trust each other. Even the cloud computing provider cannot trust the VMs it is hosting, because the customers are free to execute whatever software they want inside their VMs. Hence, it must be guaranteed that potentially malicious VMs cannot (1) spy on memory that belongs to another customer's VM or the host and (2) it is impossible for VMs to overwrite foreign memory locations in order to provoke crashes of other VMs or even the server's control software that hosts the VMs. Nowadays, modern CPUs fulfill this requirement with hardware-assist for virtualization in their memory management subsystems [4, 5]. This also facilitates fault isolation, which means that failures that crash one VM do not propagate to other concurrent VMs, and the underlying hardware remains operational.

The second domain that must be covered by inter-VM isolation is the temporal domain. Temporal isolation, or **performance isolation**, has to guarantee that timesharing of shared resources between VMs results in performance that is in accordance with the expectations of the tenants. It should be avoided that one VM executes malicious or uncooperative workloads that impair or steal performance from other concurrent VMs. If performance isolation is implemented poorly, the system becomes prone to performance interference. For instance, if a tenant leases a VM with 1 Gbit/s Ethernet

#### 1 Introduction

connectivity, it should not be possible for other VMs to steal or degrade bandwidth from this tenant's VM. Hence, strong performance isolation is important to cloud computing providers in order to offer good service level agreements, which in turn attract customers. In research, performance isolation has been a topic of study since the early days of virtualization [6, 7].

Although starting out as a server technology, the spatial and performance isolation properties of virtualization recently also caught attention in the embedded computing domain. Here, the technology promises to enable multi-core embedded systems that consolidate different sub-systems in isolated environments while reducing overall costs at the same time [8]. For example, in the automotive domain, Electronic Control Units (ECUs) could use virtualization to share multi-core hardware between mixed-criticality functions [9, 10, 11], e.g. infotainment and instrument cluster applications [12]. Besides costs, this approach would also reduce weight and cabling, and save installation space. The same goals could be achieved by consolidating multiple legacy functions, which historically run on their own ECUs, into a single but powerful virtualized multi-core ECU. Similar considerations are made for embedded systems in the avionics domain [13, 14, 15]. In contrast to the server and cloud computing landscape, inter-VM isolation requirements for embedded systems are even more strict due to additional real-time and safety requirements.

### 1.1 Problem Statement

While the problem of spatial isolation in virtualized systems can be considered as solved since the introduction of respective hardware-assist [4, 5], performance isolation is still work in progress. In contrast to spatial isolation, which describes a single problem for a single shared resource (restricting processes from accessing certain memory locations), performance isolation is a multi-dimensional problem. This is because modern multi-core systems inherently employ multiple shared resources, for example CPU cores, caches, interconnects or I/O devices. For each of these resources, there are multiple architectural mechanisms that can affect performance isolation [16], which aggravates the complexity of the overall problem. For some resources, solutions have significantly advanced in the meantime. For example, performance isolation issues regarding CPU caches have been recognized and acknowledged by hardware manufacturers, which resulted in the recent introduction of hardware-assist for CPU cache monitoring and allocation [17]. With its help, cache-related performance interference between multiple concurrent CPU processes like VMs can now be prevented.

Performance isolation for I/O devices, in contrast, is still a field of active research. Additionally, it is a particularly diverse problem, because there are multiple approaches and implementations for virtualizing I/O. With emulation and paravirtualization, two legacy, software-based approaches exist, which utilize a trusted software layer for relaying and multiplexing I/O of VMs to physical hardware. The latest generation of I/O virtualization is PCIe passthrough and Single Root I/O Virtualization (SR-IOV). It uses hardware-assist to self-virtualize I/O devices (SR-IOV) and directly connect the virtual I/O device instances to VMs (passthrough). This removes the computational overhead of the software-based relaying and multiplexing layers in the host, which makes PCIe passthrough and SR-IOV the currently best-performing solution for I/O virtualization [18, 19, 20], and therefore superior to emulation and paravirtualization.

In literature, research on performance isolation of both software-based I/O virtualization approaches is plentiful, and can be categorized into three types. Studies of the first type collected data on performance isolation issues of certain virtualization solutions. This was achieved by running multiple diverse workloads or benchmarks in VMs and quantifying performance interference effects between them [6, 7, 21, 22]. Others focused on specific I/O resources like storage [23] or networking [24]. Studies of the second type contain approaches for improving isolation, mostly by enhancing different aspects of VM scheduling. For example, by fairly accounting for VM-demand of CPU cycles [25, 26], adapting to the communication behavior and need of VMs [27, 28, 29], or by optimizing placement of tasks or VMs in the virtualized server or datacenter [30, 31, 32]. The third type investigates means to deliberately degrade performance of concurrent VMs [33, 34].

However, until now, little work exists on performance isolation for the latest generation of I/O virtualization, PCIe passthrough and SR-IOV. Research on this topic is important, because the technology has already been deployed by cloud computing providers like Amazon, and it is also considered for future embedded systems in the automotive domain [12].

### 1.2 Contributions

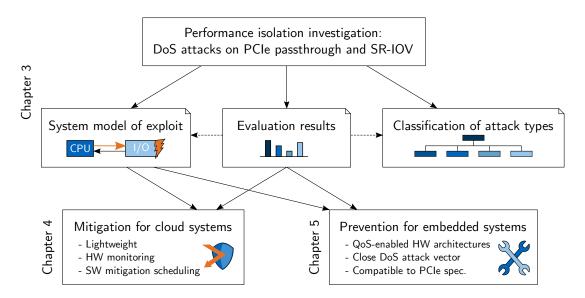

The goals of this thesis are to (1) provide a comprehensive investigation about performance isolation issues of PCIe passthrough and SR-IOV, and to (2) introduce domainspecific solutions for cloud computing and embedded systems that mitigate and resolve performance isolation shortcomings of current implementations.

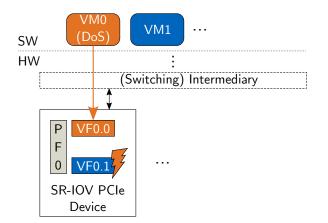

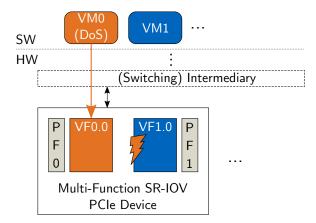

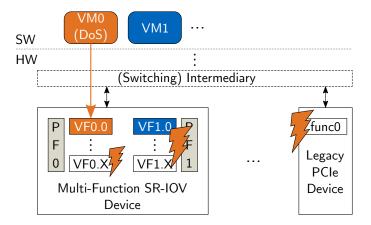

First, based on work in [35, 36], it is introduced that performance isolation of PCIe passthrough and SR-IOV can be broken with Denial-of-Service (DoS) attacks from malicious or buggy VMs, which flood passthrough and SR-IOV hardware with spurious PCIe packets. Accordingly, a threat model is formulated and a sample implementation of a DoS attack is presented. Results from four experiments on a system comprised of commercial-off-the-shelf hardware are presented. They demonstrate that latencies and throughput of different shared resources degrade significantly during DoS attacks on an SR-IOV capable 1 Gbit/s Ethernet NIC. Insights from the experiments are used to construct an abstract system model that gives a concise overview of architectural issues within PCIe passthrough and SR-IOV, which enable the DoS attack exploit. Furthermore, a classification of DoS attacks into four types is presented, which can be used in future work to communicate the impact and severeness of a specific DoS attack.

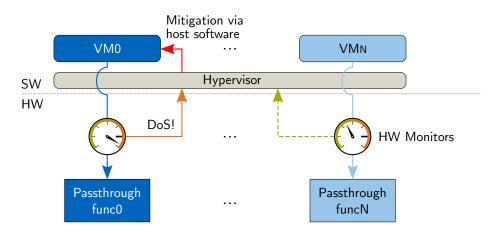

Second, based on work in [37], a lightweight solution that mitigates performance isolation attacks in cloud computing systems is proposed. The decision to follow a mitigation approach is motivated with domain-specific requirements. A design is presented that extends current cloud computing systems with lightweight hardware monitoring

#### 1 Introduction

that detects DoS attacks in a live system and reports attacker VMs to the host. The latter invokes scheduling extensions that mitigate the performance isolation attack. A successful prototype implementation of this design using an SR-IOV capable FPGA development board, which is installed together with the proposed software extensions on real hardware, proves the feasibility of the approach. Finally, results of an evaluation of the prototype are presented. The evaluation was conducted using three network-based cloud computing benchmarks.

Third, based on work in [38], solutions for completely preventing DoS attacks are proposed. They are intended for use in embedded systems with strong isolation requirements that cannot be fulfilled by software-based mitigation. Therefore, two integrated hardware architectures for multi-core platforms are proposed. They are optimized for different goals; Scheduling freedom or minimal hardware costs. To achieve its specific goal, each architecture utilizes a different subset of the optional Quality-of-Service (QoS) extensions of the PCIe specification. It is determined which extensions are needed, and how virtualized multi-core CPUs have to interface and implement them. The latter aspect is explicitly not covered in the PCIe specification. An evaluation of both architectures, conducted on a SystemC model of a real-world system with SR-IOV hardware, shows that the proposed architectures successfully close the DoS attack vector. The results are also used to compare and discuss the pros and cons of each individual approach.

The contributions and results of this thesis were published at three international conferences [35, 37, 38] and in one journal article [36]. To the best of my knowledge, the presented work is the first that comprehensively investigates DoS attacks on PCIe passthrough and SR-IOV, and contributes towards solving the resulting performance isolation issues. A graphical representation of the contributions is depicted in Figure 1.1.

Figure 1.1: Contributions to the field of performance isolation for virtualized multi-core systems using PCIe passthrough and SR-IOV.

## 1.3 Outline

The remaining part of this thesis is structured as follows: Chapter 2 provides state-of-theart on relevant technologies and computing domains. The investigation of performance isolation issues of PCIe passthrough and SR-IOV is presented in Chapter 3. Chapter 4 introduces the lightweight hardware/software approach for mitigating performance isolation attacks in cloud computing systems. Performance isolation solutions for virtualized embedded systems are presented in Chapter 5. Finally, Chapter 6 concludes this thesis by comparing and discussing all presented solutions and giving an outlook on future work on this topic.

# 2 State of the Art

This chapter introduces the state of the art in platform virtualization and I/O performance isolation. It is structured in a top-down fashion. First, Section 2.1 presents how platform virtualization in general enables sharing of modern multi-core hardware between multiple Virtual Machines. Next, spatial isolation and performance isolation are introduced, and the computing domains that have adopted virtualization technology are presented. Afterwards, virtualization technologies for I/O are introduced in Sections 2.2 and 2.3, together with current approaches and research results that investigate and/or improve their performance isolation. The I/O virtualization technologies are presented in the chronological order they surfaced: Emulation, paravirtualization and passthrough I/O with Single Root I/O Virtualization (SR-IOV).

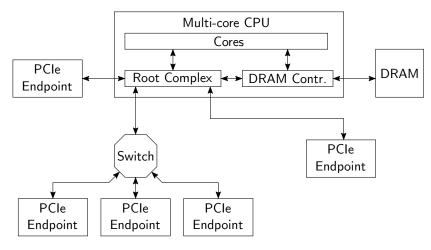

As this thesis contributes to the latter approach (passthrough I/O), it is the most extensively covered part in this chapter. At the time of writing, commercial off-theshelf (COTS) passthrough I/O devices are mainly provided for the PCIe interconnect. This is a result of x86, which traditionally employs PCIe, being the dominant processor architecture in cloud computing, a domain in which platform virtualization was a key enabling technology [1]. For these reasons, this thesis primarily focuses the x86 family of processor architectures and PCIe-based I/O devices and virtualization technology.

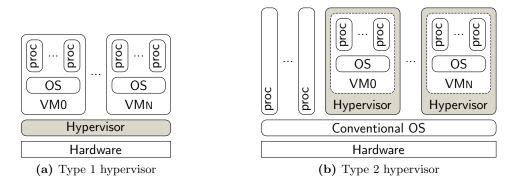

### 2.1 Platform Virtualization

Platform virtualization enables the generation of simulated environments of real computer hardware. These environments are called Virtual Machines (VMs). VMs can be dynamically created and destroyed during runtime by a trusted software layer that is usually called hypervisor, or simply the host (both terms are used interchangeably in the following). Correspondingly, VMs may also be called guests or guest software. Inside VMs, it is possible to execute any kind of software, including whole Operating Systems (OSs), and it is possible to host multiple VMs on the same physical hardware. Virtualization also offers fault isolation: Critical faults inside VMs only crash the software that is running encapsulated inside the faulting VM; Other VMs or the host are not affected. The concept of virtualization has been around since the 1970s. At the beginning, hypervisors were categorized into two types [39]. Type 1 hypervisors (bare metal) run directly on physical hardware, while type 2 hypervisors (hosted) execute as userspace processes within a conventional OS. A block diagram of both types is depicted in Figure 2.1.

In the past, type 1 hypervisors had better overall performance because the hypervisor software layer executes in kernel mode and could be specifically designed to multiplex hardware access between multiple VMs with low overhead. Xen [40] is an example of a

Figure 2.1: Comparison of classic hypervisor types.

type 1 hypervisor. In contrast, type 2 hypervisors needed to execute hardware multiplexing through the interfaces of a conventional host OS. These interfaces were not optimized for such tasks, which resulted in more overhead and therefore less VM performance [41]. VMware Workstation [42] is an example of a type 2 hypervisor. Nowadays, however, the picture has changed. Since the advent of hardware assist for virtualization [2, 3], it is no longer possible to clearly label hypervisors as type 1 or type 2. For example, KVM-accelerated QEMU [43, 44] on Linux consists of a userspace process (QEMU) and a kernel module (KVM). This combination shows traits of both hypervisor types. On the one hand, QEMU is hosted by the Linux kernel (type 2), on the other hand, it also uses the KVM module that effectively converts Linux to a type 1 hypervisor. Furthermore, it is no longer possible to infer performance differences between hypervisors solely from their type. It is rather the case that overhead incurred by different hypervisors varies depending on application type and used resources [45].

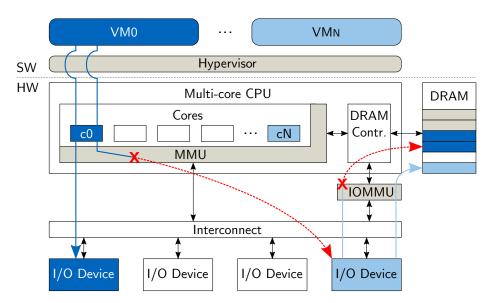

#### 2.1.1 Spatial Isolation

Spatial isolation must ensure that it is not possible for one VM to willingly or unwillingly read or alter any kind of memory resource that is assigned to another VM or the host. This affects the system's main memory (RAM) and I/O device memory such as configuration registers. This must be ensured for both, direct (CPU cores) and indirect (DMA) memory transactions. In other words, it is a security requirement that has to prevent malicious VMs from executing CPU instructions that read foreign memory that belongs to concurrent VMs or the host. The same is true for write instructions that could corrupt foreign memory and potentially crash concurrent VMs or the whole host system. Fortunately, this kind of isolation is inherently provided by the technologies that enable platform virtualization in the first place: In order to run multiple VMs on the same physical machine, it is necessary that the hypervisor partitions the machine's memory and exposes only a private and exclusive share to each VM. This is realized by virtualizing the platform's MMU subsystems. In the past, a software emulation technique called shadow page tables [46] was used. Nowadays, there is hardware-assist for virtualization in most x86 MMUs [4, 5], which is significantly faster than employing shadow page tables in most cases [47]. Virtualized MMUs in recent server CPUs using modern hypervisors almost reach bare metal performance, incurring less than 5% overhead [48]. Hardware-assist for I/O virtualization has also been introduced for IOMMUs [49, 50]. These VM-isolation properties made virtualization "the primary security mechanism in today's clouds", according to [51].

#### 2.1.2 Performance Isolation

Temporal isolation, also called performance isolation, describes the capability of a host system to prevent or limit performance interference amongst VMs. It is naturally caused by time-sharing of shared resources between multiple VMs. If the sharing implementation of the host lacks proper isolation or partitioning capabilities, it is possible that the performance of one VM degrades due to uncooperative or malicious usage of shared resources in another VM. A prominent example is sharing the last level cache (LLC) of multi-core CPUs. If two VMs concurrently run memory intensive workloads, data from one VM is constantly evicted by the other, and vice versa, which results in performance interference [52, 53, 54, 55]. The problem has been solved recently by integrating hardware-assist for cache monitoring and partitioning into CPUs [17]. Similar interference effects can surface for virtualized I/O. Here, the state-of-the-art in performance isolation will be reviewed in detail in the following Sections 2.2 and 2.3.

### 2.1.3 Cloud Computing

Platform virtualization was, and still is, an important enablement technology for Cloud Computing [1], especially, but not exclusively, for the Infrastructure-as-a-Service (IaaS) service model. This becomes apparent from The National Institute of Standards and Technology (NIST) definition of cloud computing [56], which defines IaaS as follows:

"The capability provided to the consumer is to provision processing, storage, networks, and other fundamental computing resources where the consumer is able to deploy and run arbitrary software, which can include operating systems and applications. The consumer does not manage or control the underlying cloud infrastructure but has control over operating systems, storage, and deployed applications; [...] "

Additionally, the NIST definition demands that provisioning must feature dynamic and on-demand characteristics. All of this can be conveniently realized with virtualization. Hypervisors of the cloud computing providers can dynamically generate VMs that provide the consumer's requested hardware resources (number of CPU cores, amount of storage, etc.), and consumer software can then be executed inside the VMs.

This model is also beneficial to the cloud computing provider itself. It enables multitenancy by consolidating multiple VMs onto the same physical machine through partitioning and sharing of hardware resources. This results in high utilization of hardware, which significantly improves efficiency. Additionally, the option to perform VM live migration [57] facilitates fault management, load balancing and hardware maintenance, while downtimes for customers are reduced.

#### 2.1.4 Embedded Virtualization

Platform virtualization technology is also seeing more and more adoption in the embedded computing domain. In [8], Gernot Heiser argues that the technology will help to enable future embedded systems where different sub-systems can co-exist in isolated environments, while overall system costs are reduced at the same time. He presents three use cases for embedded virtualization: (1) Consumer-electronics devices, like smartphones, where real-time environments (e.g. baseband software) are co-located with rich OSs (e.g. Android or iOS). (2) Devices with isolated environments for safety- or security-critical components, e.g. secure communication devices or medical devices. (3) Cars, where infotainment software and automotive control and convenience functionality is consolidated on a single Electronic Control Unit (ECU).

In fact, a virtualized phone has already been launched by Motorola [58]. Frameworks for smartphone virtualization were also presented by VMware [59] and Lang et al. [60]. In the automotive domain, recent research suggests that the isolation properties of virtualization are a reasonable means to exploit the power of multi-core CPUs by consolidating multiple functions of mixed-criticalities on a shared multi-core ECU [9, 10, 11]. For instance, work in [12] presents the consolidation of a virtualized general purpose Android infotainment application and a virtualized instrument cluster application on a shared x86 automotive ECU. Here, virtualization isolates potential faults from the untrusted Android application from the trusted code of the car manufacturer, which runs in the instrument cluster application. Consolidation could also be realized with legacy functions that historically run on their own ECUs. In both cases, installation space, weight and cabling are reduced, and therefore overall costs are reduced and efficiency is increased at the same time. In [61], additional benefits of virtualization for automotive embedded systems, besides isolated consolidation, are presented. In the avionics domain, virtualization is seen as a suitable approach to implement the spatial and temporal isolation requirements of the ARINC 653 standard. Virtualization based implementations are presented in [13, 14, 15].

In contrast to hypervisors that are employed in the server and cloud computing domain, additional real-time and safety requirements are in place for embedded hypervisors, which motivates the development of more specialized or extended solutions. A comprehensive and detailed collection on the state of the art of real-time issues in embedded virtualization is presented by Gu et al. in [62]. The paper contains information on the availability of commercial hypervisors for hard real-time virtualization in safetycritical systems, e.g. OpenSynergy Coqos<sup>1</sup> or SYSGO PikeOS<sup>2</sup>, as well as work that improves the real-time behavior of general purpose hypervisors like Xen and KVM, e.g. RT-Xen [63]. As this thesis has a clear focus on I/O, techniques for virtualizing I/O devices and related work on enforcing performance isolation for virtualized I/O will be presented in the following sections.

<sup>&</sup>lt;sup>1</sup>http://www.opensynergy.com/en/products/coqos/

<sup>&</sup>lt;sup>2</sup>https://www.sysgo.com/products/pikeos-hypervisor/

### 2.2 Software-based I/O Virtualization

All software-based I/O virtualization techniques share the common characteristic that I/O of VMs is, in one form or another, relayed via trusted host software. This software executes the requested I/O operations on the physical hardware on behalf of the VMs, and returns eventual results to the respective requesters. Due to the relay, the host can ensure that spatial isolation is enforced, because it can check and verify each VM access. The host is also responsible for multiplexing requests from multiple VMs if a device is to be shared. In the following, the two concepts of emulation and paravirtualization for I/O are presented.

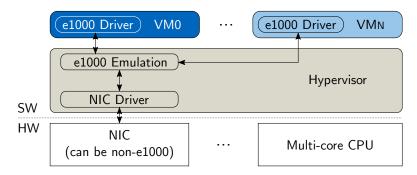

#### 2.2.1 Emulation

Using emulation, the host is able to create a VM that emulates the existence of a certain I/O device. Generally, it is beneficial to emulate a device that is wide-spread and popular in the real-world, so that there is a high chance for out-of-the-box support by many OSs that come into question for running as guests inside VMs. Typical examples for emulated devices are the popular Intel e1000 or the Realtek RTL8139 family of Ethernet adapters. If the guest OS is then executed inside the VM, no further modifications are needed to enable I/O, because it already possesses a driver for this emulated version of a physical I/O device.

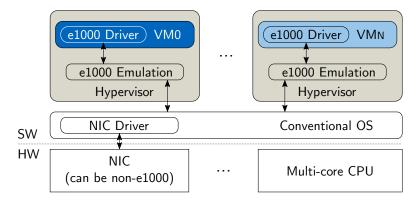

The host uses a trap and emulate mechanism to catch any VM interactions with the emulated device. It then executes the wanted interaction on behalf of the VM on its physical hardware, and finally returns control to the VM, also emulating potential return values. If multiple VMs are running on the host, a software bridge can be interposed between the emulation layer and the host device driver, so that host hardware can be shared. I/O device emulation can be implemented in various ways, resulting in different trade-offs. In the following, three popular implementations and their pros and cons are presented. First, emulation inside a type 1 hypervisor is presented. A corresponding block diagram is depicted in Figure 2.2.

Figure 2.2: I/O device emulation in a type 1 hypervisor.

Using this design, both the emulation layer and the device driver for the physical hardware reside in the hypervisor. VMware ESX [64], for example, employed this design.

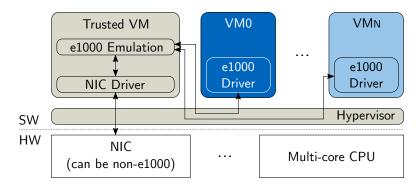

It facilitates good performance, because it requires only a small amount of VM exits and entries (CPU context switches between VM and hypervisor contexts), which are the main source of overhead in platform virtualization [65] (exits due to I/O are particularly expensive [66]). On the downside, the design defeats the paradigm of having a small trusted computing base (TCB) in order to satisfy security requirements. Here, the hypervisor has to include code for emulation and device drivers. This bloats the codebase of the trusted part of the system, which increases the probability of bugs, which in turn enlarges the attack surface. Additionally, support for hardware is constraint by the availability of respective device drivers in the hypervisor. These problems can be addressed by employing a trusted VM, like depicted in Figure 2.3.

Figure 2.3: I/O device emulation with type 1 hypervisor and trusted VM.

The trusted VM is intended to assist the hypervisor. It usually runs a modified version of a conventional OS like Linux, which provides broader driver support than a specialized hypervisor. Xen [40] is a typical example that uses a trusted VM<sup>3</sup>. Physical I/O devices are directly exposed to and handled by drivers in the trusted VM, which therefore increases hardware support and slims down the codebase of the hypervisor. Further slim-down is realized by also offloading the emulation layer to the trusted VM. In this design, the lean hypervisor is still trapping VM access to emulated I/O devices, but forwards the emulation work to the trusted VM. The drawback of this approach is more VM exits and entries, because there are additional switches between hypervisor and trusted VM, which ultimately result in less performance. A similar design is used in hypervisors that are hosted. This third design approach towards emulation is depicted in Figure 2.4.

Like in a trusted VM, emulation is also computed in a userspace process (the hypervisor process), but the actual device driver is provided by the conventional host OS. This increases hardware support even further, because the hypervisor code must only be compatible to the networking API of the host OS, which abstracts from the actual device driver. Hence, in contrast to the previous design, it must not be ensured that a trusted VM is available that provides driver support for the targeted hardware. The hypervisor can run on any hardware for which the host OS provides a driver, which also

<sup>&</sup>lt;sup>3</sup>In literature, many alternative names for this VM exist. For example, in the terminology of Xen, it may also be called privileged VM, integrated driver domain (IDD) or Dom0.

Figure 2.4: I/O device emulation in hosted hypervisors.

includes future hardware. On the downside, overall performance might be slightly worse because the hypervisor itself is hosted.

In conclusion, the choice of how to implement I/O device emulation is a trade-off between security (size of trusted code base), performance and hardware support. For sophisticated I/O devices like GPUs or network interface cards, however, all approaches have in common that emulation is inherently inefficient, because in contrast to native I/O with a single device driver, a lot of overhead is introduced. Emulated I/O must traverse the guest device driver, the emulation layer and finally the host device driver. This results in moderate performance and high CPU utilization due to the computational overhead in the emulation layers of the host. As a result, emulation is mostly employed for simple devices or peripherals, e.g. system timers.

#### 2.2.2 Paravirtualization

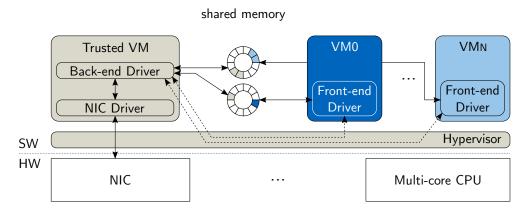

The unwanted overhead of emulation can be reduced by employing paravirtualized I/O, an approach that has been popularized by the Xen hypervisor [40, 67]. Paravirtualization lets guest OSs in VMs "cooperate" with the host software. The guest loads a so-called front-end driver that communicates with a back-end driver that is operated by the host. This is also called a split-driver structure. Payload data between frontand back-end drivers is transported via shared memory, and notifications about new data are exchanged via the hypervisor. This design is compatible to each of the three virtualization implementations that were presented in the previous section. Basically, the device driver in the guest OS is replaced by the front-end driver, and the emulation layer in the host is substituted by the back-end driver. To give an example, the resulting design for a virtualized system that utilizes a trusted VM is depicted in Figure 2.5.

The directed communication between VM and host removes the trap-and-emulate overhead of emulation solutions and therefore enhances performance. On the downside, paravirtualized I/O can only be used if there is a front-end driver available for the respective guest OS that is compatible to the host's back-end driver. While this was not always the case in the early days of (para)virtualization, it is less of a hurdle nowadays. Thanks to virtio [68], a de-facto standard for paravirtualized drivers has been established

#### 2 State of the Art

that is continuously improved and supported by most of the typical guest OSs like Windows and Linux.

Figure 2.5: Paravirtualized I/O with a trusted VM. Front-end and back-end drivers cooperatively exchange data via shared memory. Notifications about new data are communicated via the hypervisor.

#### 2.2.3 Performance, Pros and Cons

Like mentioned before, paravirtualization usually outperforms emulation as it incurs less computational overhead. For example, Barham et al. [40] showed that in a network TCP benchmark using an MTU of 1500 B, the original release of Xen, using its paravirtualized network drivers, was able to achieve the performance of a native Linux system (897 Mbit/s for both TX and RX). VMware workstation, using an emulated network device, achieved 68% less bandwidth for TX and 31% less for RX.

However, even paravirtualization suffers from performance degradation if platforms have sophisticated I/O configurations, despite various optimization efforts to identify [69] and reduce the computational overhead [70, 71]. For instance, if network subsystems are employed that go beyond bandwidths of 1 Gbit/s, CPU overhead is still a limiting factor. Like shown in [18], paravirtualization was not able to achieve native performance on a 10 Gbit/s Ethernet NIC in RX and TX throughput benchmarks for most of the employed message sizes. In RX tests with big message sizes, paravirtualization saturated around 6 Gbit/s compared to 9.3 Gbit/s for a non-virtualized setup. Consequently, research began shifting the focus on offloading virtualization overheads into the I/O hardware itself to alleviate the CPU overhead [72, 73, 74]. Despite further efforts to improve paravirtualization for high-performance I/O [75], commercial I/O devices with hardware support for virtualization finally surfaced. They will be covered in detail in Section 2.3.2.

An advantage of emulation and paravirtualization solutions for I/O is the abstraction from physical hardware. The state of guest OS I/O subsystems is entirely resident in memory, as there is no direct communication between guests and physical I/O devices. This enables flexible control, e.g. VMs can be started and stopped on-demand, and it facilitates live replication and migration of VMs between different physical hosts.

#### 2.2.4 Performance Isolation Approaches

Performance isolation for software-based I/O virtualization has been an active field of research ever since. Many studies focused on investigating performance interference effects between VMs that were running multiple diverse workloads or benchmarks, and therefore covered software-based I/O virtualization at least partially. Koh et al. [6] utilized an instrumented Xen to run a range of benchmarks, i.a. disk I/O workloads, in two VMs and collected performance metrics and runtime characteristics. They used the data to clusterize applications that generate certain performance interferences and developed mathematical models that predict application performance. Matthews et al. [7] designed a performance isolation benchmark that measures the impact of misbehaving VMs on concurrent VMs. The benchmark stresses different components like CPU, memory, disk and network I/O. They conducted their benchmarks on multiple virtualization solutions that also contained Xen and VMware Workstation. Further studies that cover performance isolation of software-based I/O virtualization can be found in [21, 22, 23, 24].