Technische Universität München Fakultät für Elektrotechnik und Informationstechnik Lehrstuhl für Entwurfsautomatisierung

# Verification and Synthesis of Analog Power-Down Circuits

Michael Alois Zwerger

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik zur Erlangung des akademischen Grades eines

**Doktor-Ingenieurs (Dr.-Ing.)**

genehmigten Dissertation.

Vorsitzender: Prof. Dr. Andreas Herkersdorf

Prüfer der Dissertation: 1. Prof. Dr.-Ing. Helmut Gräb

2. Prof. Dündar Günhan, Ph.D.

Die Dissertation wurde am 25.10.2016 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 23.01.2017 angenommen.

#### **Abstract**

This thesis investigates electronic design automation algorithms for the verification and synthesis of analog power-down circuits. The methods build upon a new structural graph model that models the static circuit behavior. The verification method detects floating nodes, leakage currents and reliability problems due to electrical stress. The synthesis method allows automatic computation of a complementary power-down circuit for a given circuit.

# Zusammenfassung

Diese Arbeit behandelt Entwurfsautomatisierungsalgorithmen zur Verifikation und Synthese analoger Power-Down-Schaltungen. Die Methoden bauen auf einem neuen strukturbasierten Graphmodell auf, welches das statische Verhalten der Schaltung modelliert. Die Verifikationsmethode erkennt Floating-Nodes, Leckströme und durch elekrischen Stress verursachte Zuverlässigkeitsprobleme. Die Synthesemethode berechnet automatisch die zu einer gegebenen Schaltung zugehörige Power-Down-Schaltung.

# Vorwort (Preface)

Diese Arbeit entstand im Rahmen meiner Tätigkeit als wissenschaftlicher Mitarbeiter am Lehrstuhl für Entwurfsautomatisierung, Technische Universität München. Eigentlich wollte ich mich mit analoger Layout-Synthese beschäftigen, doch es kam etwas dazwischen – analoge Power-Down-Schaltungen. Das Ergebnis sind die Algorithmen für Verifikation und Synthese in dieser Arbeit.

Ich möchte mich bei allen Kollegen des Lehrstuhls für die schöne Zeit am Institut und die hervorragende Arbeitsatmosphäre bedanken. Mein besonderer Dank gilt meinem Doktorvater Professor Helmut Gräb. Bedanken möchte ich mich auch bei allen Studenten, die im Rahmen einer Abschlussarbeit oder eines Praktikums einen Beitrag zu dieser Arbeit geleistet haben. Ganz besonderer Dank geht an Maximilian Neuner für seine unermüdliche und engagierte Unterstützung beim Verbessern und Implementieren der Algorithmen im Rahmen von Bachelorarbeit, Masterarbeit, Praktika und Werkstudententätigkeiten. Bedanken möchte ich mich auch bei meinem Vorgänger Dr. Michael Eick, dessen Software zur Strukturerkennung ich übernehmen konnte und dessen "Nachhilfestunden" ein sehr hilfreicher Beitrag zu einem zügigen Start des Projekts waren. Dank gilt auch allen Kollegen der Infineon Technologies AG mit denen ich im Rahmen des Forschungsprojektes "Rely" an der Verifikation analoger Power-Down-Schaltungen arbeiten konnte. Ganz besonders bedanken möchte ich mich bei Georg Georgakos für die wertvollen Diskussionen und die Möglichkeit die Algorithmen an Beispielen aus der Praxis zu testen und bei Professor Günhan Dündar von der Boğazici University Instanbul für die Begutachtung der Arbeit. Zu guter Letzt möchte ich mich bei meiner Familie für die Unterstützung bedanken, ohne die diese Arbeit sicherlich nicht möglich gewesen wäre.

Das Thema "analog power down" wurde bis dato in Wissenschaft und Praxis wenig unter dem Aspekt der Entwurfsautomatisierung (insbesondere Synthese) betrachtet. Ein solche Betrachtung bietet jedoch die Chance eine ständig wiederkehrende und an und für sich sehr systematische Aufgabe zu automatisieren. Ich hoffe, hierfür einen ersten Anstoß geleistet zu haben und würde mich freuen wenn der Leser in der vorliegenden algorithmischen Werkzeugkiste ein passendes Werkzeug findet.

München im März 2017

# **Contents**

| 1. | Intro | oductio | on                                                | 1       |

|----|-------|---------|---------------------------------------------------|---------|

|    | 1.1.  | Power-  | -Down Circuits                                    | 4       |

|    | 1.2.  | State   | of the Art and Contributions                      | 6       |

|    |       | 1.2.1.  | Verification of Analog Circuits                   | 6       |

|    |       | 1.2.2.  | Power-Down Verification                           | $^{14}$ |

|    |       | 1.2.3.  | Analog Circuit Synthesis                          | 15      |

|    |       | 1.2.4.  | Power-Down Synthesis                              | 16      |

|    | 1.3.  | Previo  | ous Publications                                  | 16      |

|    | 1.4.  | Overvi  | iew over this Thesis                              | 17      |

| 2. | Stru  | cture F | Recognition 1                                     | 9       |

|    | 2.1.  | Motiva  | ation and Problem Description                     | 19      |

|    | 2.2.  | Enhan   | aced State-of-the-Art Algorithm                   | 19      |

|    | 2.3.  |         |                                                   | 29      |

|    | 2.4.  | Experi  | imental Results for Industrial-Size Analog Blocks | 30      |

| 3. | Pow   | er-Dow  | vn Verification 3                                 | 3       |

|    | 3.1.  | Design  | Flow with Automatic Verification                  | 33      |

|    | 3.2.  | Detect  | tion of Floating Nodes and Short Circuits         | 34      |

|    |       | 3.2.1.  | Problem Description                               | 34      |

|    |       | 3.2.2.  | Overview                                          | 37      |

|    |       | 3.2.3.  | Definitions for the Graph Model                   | 37      |

|    |       | 3.2.4.  | 0 1 0                                             | 10      |

|    |       | 3.2.5.  | Short-Circuit-Path Search                         | 13      |

|    |       | 3.2.6.  | Floating Node and Short-Circuit Verification      | 17      |

|    |       | 3.2.7.  | 1                                                 | 50      |

|    | 3.3.  | Detect  | , 0 0 0                                           | 59      |

|    |       | 3.3.1.  | i                                                 | 59      |

|    |       | 3.3.2.  |                                                   | 61      |

|    |       | 3.3.3.  | Power-Down Signal Tracing                         | 57      |

|    |       | 3.3.4.  | 1                                                 | 72      |

|    |       | 3.3.5.  | 0                                                 | 74      |

|    |       | 3.3.6.  |                                                   | 32      |

|    |       | 3.3.7.  | Experimental Results                              | 34      |

| 4. | Pow   | er-Dow  | vn Synthesis 8                                    | 9       |

| Bi | Bibliography 143 |         |                                                         |   |          |  |

|----|------------------|---------|---------------------------------------------------------|---|----------|--|

| 5. | Con              | clusion |                                                         | 1 | 137      |  |

|    |                  | 4.4.6.  | Switch Sizing                                           | • | 129      |  |

|    |                  | 4.4.5.  | Low Voltage Differential Signaling Driver               |   |          |  |

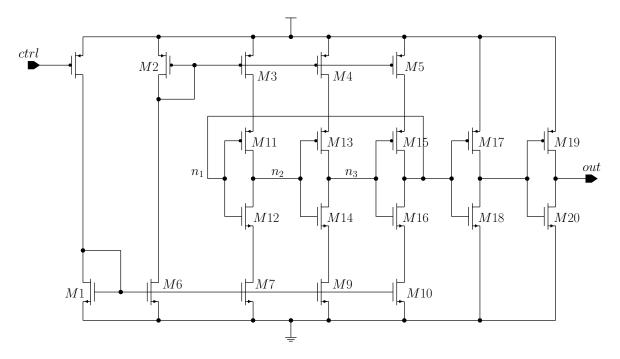

|    |                  | 4.4.4.  | Voltage Controlled Ring Oscillator                      | • | 128      |  |

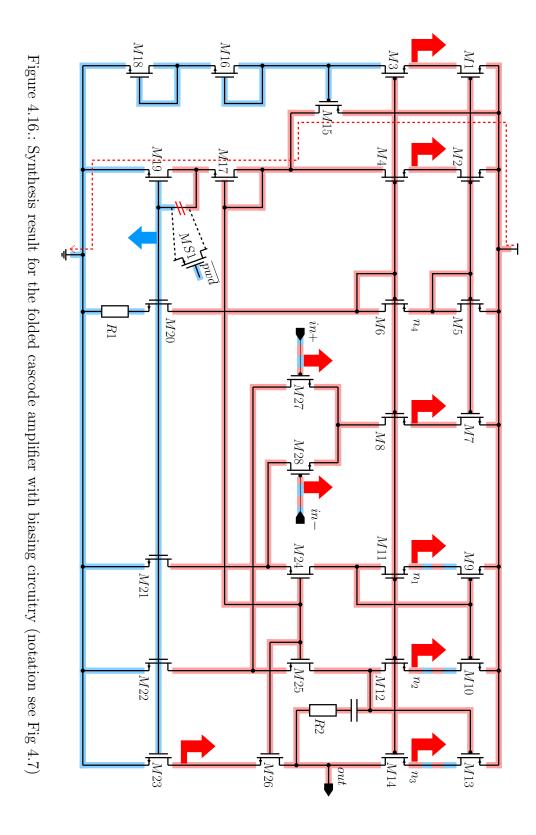

|    |                  | 4.4.3.  | Folded Cascode Amplifier with Biasing Circuitry         | • | 123      |  |

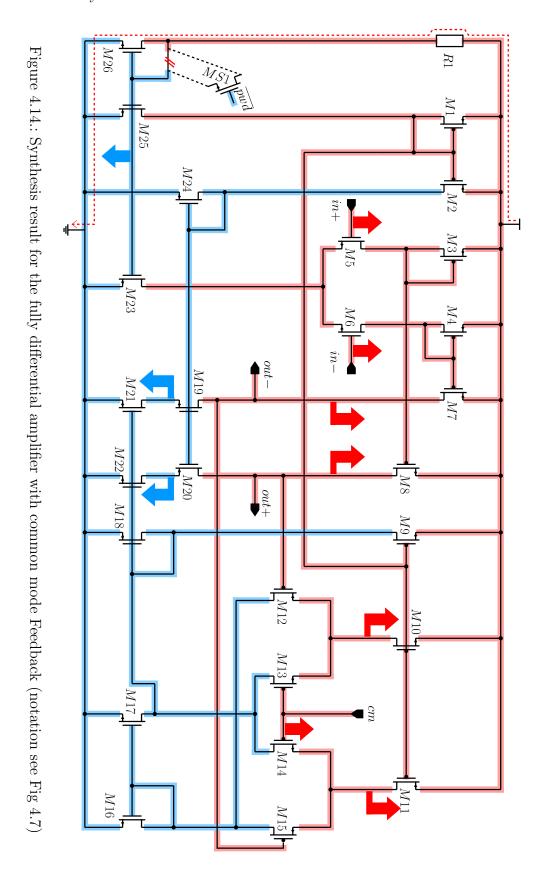

|    |                  | 4.4.2.  | Fully Differential Amplifier with Current Mode Feedback |   | 122      |  |

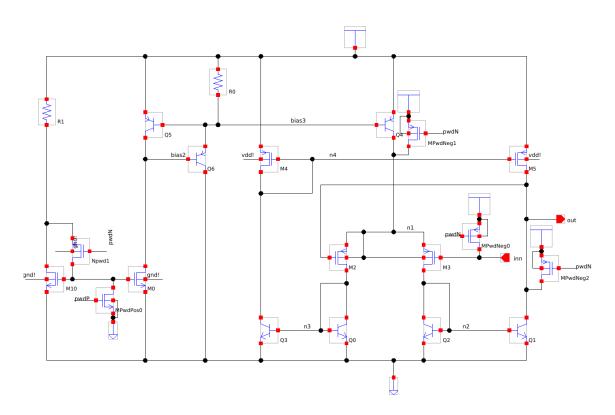

|    |                  | -       | Symmetrical BiCMOS Amplifier                            |   |          |  |

|    | 4.4.             |         | mental Results                                          |   |          |  |

|    |                  |         | Schematic Back Annotation                               |   |          |  |

|    |                  | 4.3.6.  | Automatic Selection of an Optimal Solution              |   |          |  |

|    |                  |         | Net Dependency Analysis by Constraint Programming       |   |          |  |

|    |                  | 4.3.4.  |                                                         |   |          |  |

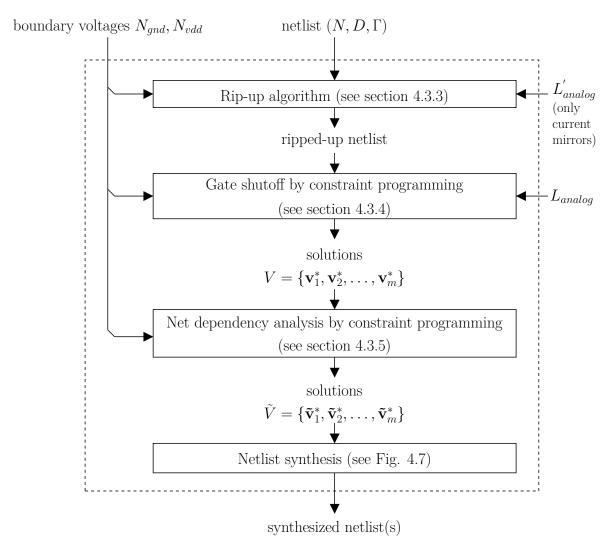

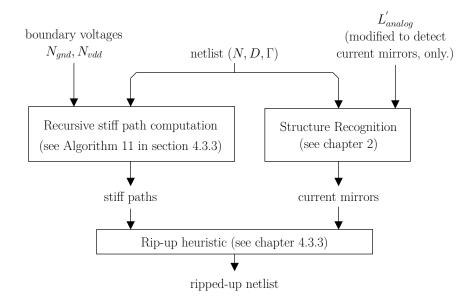

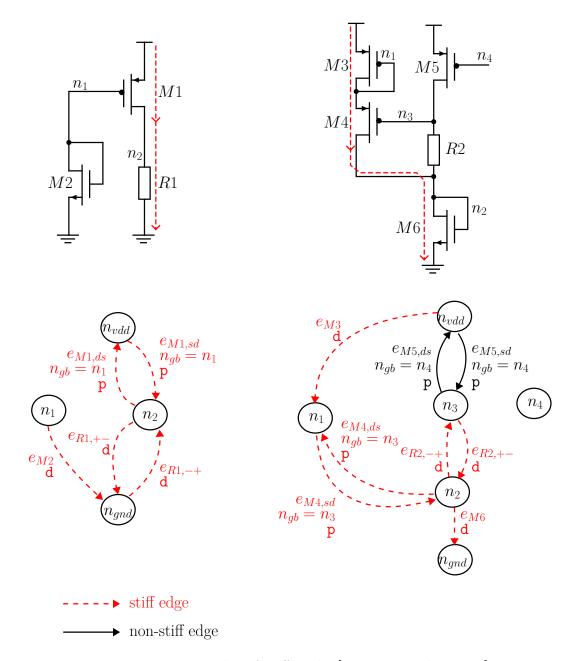

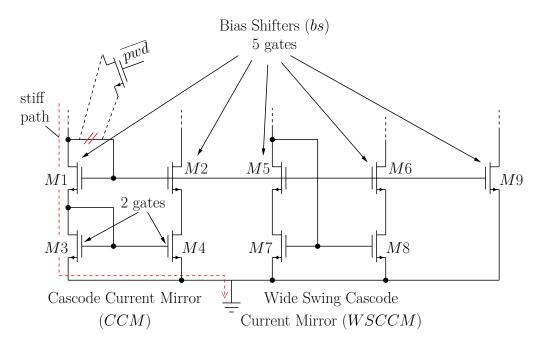

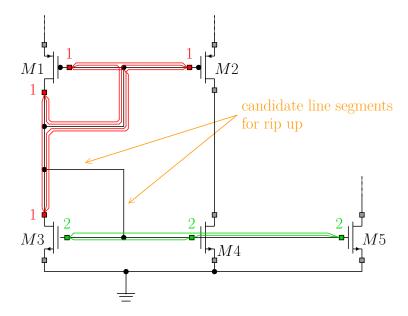

|    |                  | 4.3.3.  | Rip-Up Algorithm                                        |   |          |  |

|    |                  | 4.3.2.  | Overview                                                |   |          |  |

|    | 1.0.             |         | Shutoff Strategies                                      |   | 92       |  |

|    | 4.3.             |         | Down Synthesis Algorithm                                |   | 90<br>91 |  |

|    | 4.2.             |         |                                                         |   |          |  |

|    | 4.1.             | Design  | Flow with Automatic Synthesis                           |   | 89       |  |

The continuous shrinking of circuits has led to the integration of more and more subsystems on a single chip. The complexity of modern systems on chip (SoCs) keeps on increasing while an extremely competitive market imposes strict time-to-market requirements. Computer-Aided Design (CAD) is used in order to keep up with the growing complexity. The design chapter of the International Technology Roadmap for Semiconductors 2011 (ITRS) states that the main threat to continuation of the fast progress is still the cost of design. In the 2007 edition of the roadmap [ITRS, 2007], the productivity gap between technology capabilities and design productivity was identified as a major challenge for the semiconductor industry. The productivity gap is still growing [ITRS, 2011; Medea+/Catrene Office, 2009; Lourenço and Horta, 2012].

Modern SoCs incorporate subsystems of different domains (analog, digital, mixed-signal) on a single chip. Thereby, verification of the analog/mixed-signal (AMS) systems is becoming a major bottleneck. The ITRS 2011 lists AMS verification as "a bottleneck that has now reached crisis proportions". Furthermore, it lists "automated methods for AMS design" as needs to cope with the challenge of exponentially increasing design costs. The percentage of synthesized analog content should have reached 30 % by 2016 and is forecasted to increase to 60 % in 2022 according to the ITRS 2011 roadmap. A worldwide survey under 561 attendees of a Tech on Tour event organized by Cadence Design Systems in 2011 [Balasubramanian, 2016; Wang, 2015] identified "AMS verification" as the biggest mixed-signal methodology challenge (36 % of mentions) followed by "SoC Verification" (19 % of mentions). It can be concluded that there is an urgent need for further improved tool support for verification and synthesis of analog/mixed-signal circuits. This thesis addresses one important aspect of verification which is power-down mode verification for analog/mixed-signal designs.

Driven by the need for energy efficiency of mobile applications, medical applications, automotive applications, devices for the Internet of Things (IoT) or energy-efficient modern data centers, the complexity of the power management increases in line with the complexity of the system itself. A prerequisite for power-efficient SoCs is the availability of power-manageable modules [Medea+/Catrene Office, 2009]. This means that all modules, including analog/mixed-signal modules, have one or several power modes. Low-power design techniques are applied as power efficiency is nowadays a design goal as important as speed and area. On technology and circuit level, the techniques comprise measures like reduction of operating voltages or reduction of leakage currents by using devices with different threshold voltages (e.g. [Keating et al., 2007; Lee, 2012]). On system level, power efficiency can be increased by switching subsystems into power-down

or low-power modes while they are not in use. Techniques like frequency and voltage scaling or power gating are applied in the digital domain (e.g. Appendix III of [ITRS, 2011], [Keating et al., 2007; Lee, 2012]). The aim of frequency and voltage scaling is the reduction of dynamic currents during operation as they are the dominant cause of power consumption. In contrast, power gating aims at the reduction of static leakage currents. They are the dominant cause of power losses while the digital system is not in use. In the analog domain, power consumption can be reduced by operating the transistors in the subthreshold region. Furthermore, analog circuits are equipped with power-down circuitry that puts the circuit in a defined power-down state and cuts off the bias currents [Juneja, 2015; Blieck and Janssens, 1996; Zwerger and Graeb, 2012a].

The subsystems of an SoC can be powered down individually. However, they remain physically connected. The complexity arising from the interaction of the power-modes of different subsystems leads to high complexity of verification [Hogan, 2014]. Managing this complexity in a system with a large number of connected subsystems is challenging. Furthermore, the voltages in power-down mode can lead to device degradation due to electrical stress [Chen et al., 2001; Michael et al., 1992; Maricau and Gielen, 2011; Chouard et al., 2011; Schlunder et al., 2003; Chouard, 2012]. Reliability and device aging considerations have to be taken into account for analog/mixed-signal power-down circuitry especially for newer technologies [Zwerger and Graeb, 2015; Schlünder, 2010; Georgakos, 2014].

The complexity of power management is another brick in the wall of exploding complexity of analog/mixed-signal verification. The situation can be improved by supporting the designers with tools that take care of the systematic verification of the power-down circuitry. Additionally, it is possible to go one step beyond verification by reversing the problem: Instead of checking the correctness of a given power-down circuit, the power-down circuit can be synthesized with given requirements for a correct power-down mode. Synthesis of power-down circuitry takes away the time consuming and repetitive manual task of adding power-down switches to a given design from the designers. Advances in power-down verification and synthesis enable faster design cycles and help to avoid expensive respins due to overlooked errors.

In this thesis, new methods for the verification and synthesis of power-down circuitry for analog/mixed-signal circuits are presented. Chapter 3 describes new methods for systematic verification of analog power-down circuitry. The methods cover the verification of the basic functionality of the power-down mode ("all currents off") and reliability considerations. A new method for automatic fault-free synthesis of power-down circuitry is developed in chapter 4. It builds on the the systematic developed for verification. The methods described in this thesis help to tackle the challenge of increasing complexity of power-down circuitry and to speed up the analog design process.

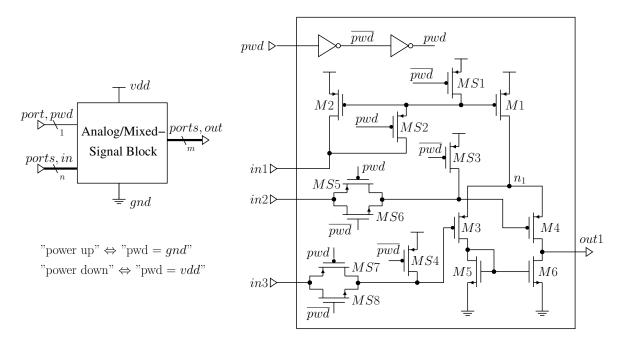

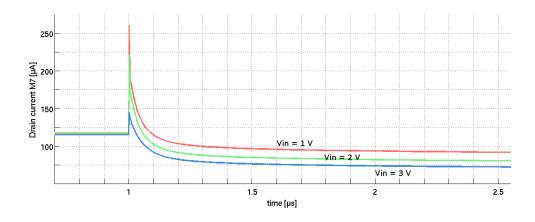

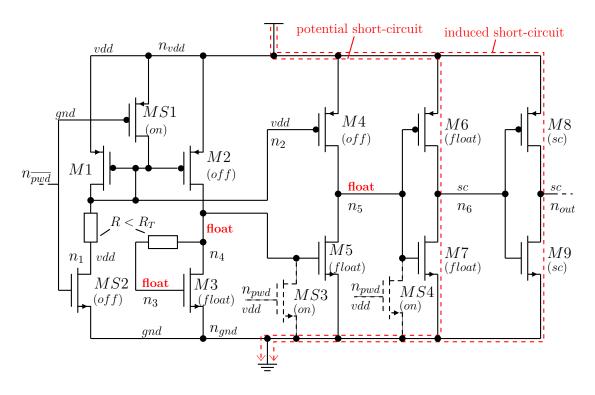

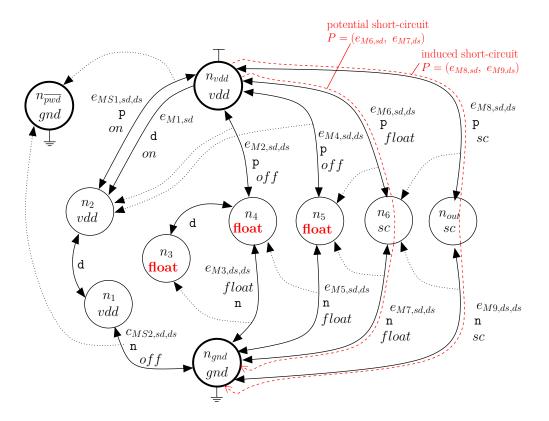

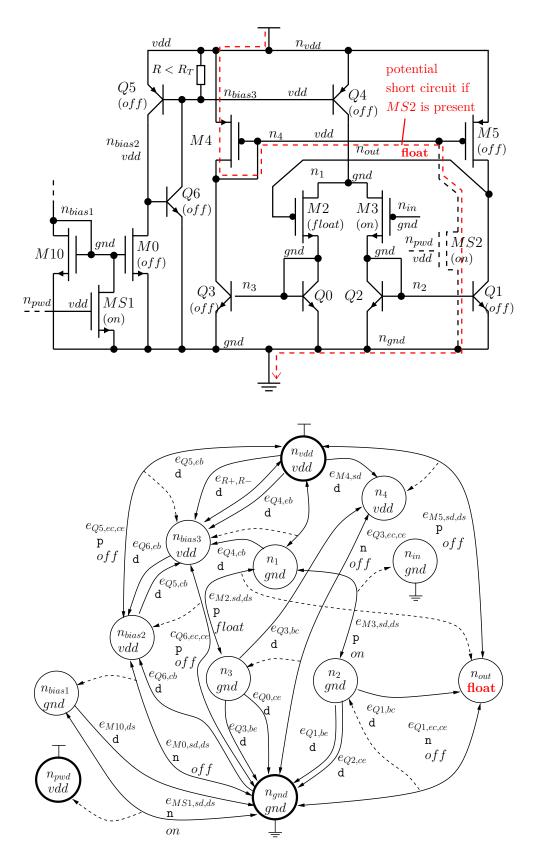

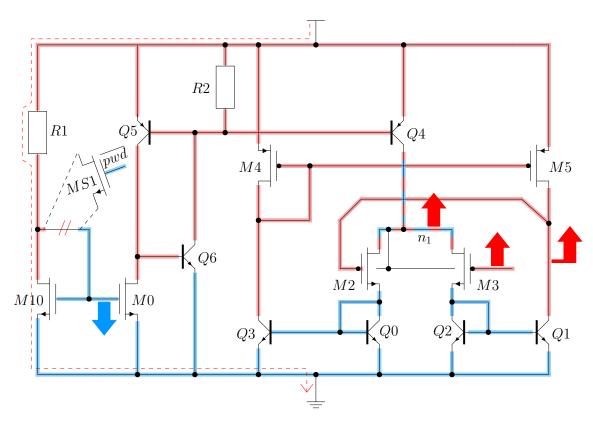

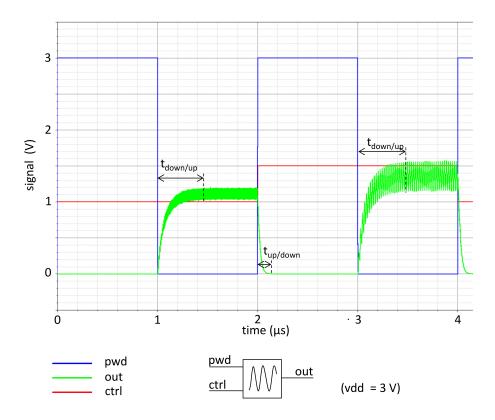

Figure 1.1.: Example of an analog/mixed-signal block with power-down circuit

| power-down $(pwd = vdd)$ : |            |            | p              | power-up $(pwd = gnd)$ : |            |            |

|----------------------------|------------|------------|----------------|--------------------------|------------|------------|

|                            | n          | p          |                |                          | n          | p          |

| pwd                        | conducting | off        | $\overline{p}$ | wd                       | off        | conducting |

| $\overline{pwd}$           | off        | conducting | $\overline{p}$ | $\overline{wd}$          | conducting | off        |

Table 1.1.: State of the power-down switches in dependence of the signal on the gate (rows), the type of transistor (columns) and the power-mode (left or right table)

# 1.1. Power-Down Circuits

An example of an analog/mixed-signal circuit block with power-down circuitry is shown in Fig. 1.1. The symbol of a circuit block is shown on the left. A differential amplifier with power-down circuitry is shown as example on the right. The circuit block is connected to other circuitry over ports. The analog/mixed-signal circuit block has n input ports and m output ports. Furthermore, it has a port labeled pwd that receives a power-down signal. This thesis follows the convention that pwd = vdd represents the power-down mode and pwd = gnd represents the power-up mode, i.e. the normal-operation mode of the circuit. The signal pwd is a digital signal with high level denoted as vdd and low level denoted as vdd and low level denoted as vdd and vdd refers to the supply voltage and vdd to the ground voltage. The inverted power-down signal is denoted as vdd and

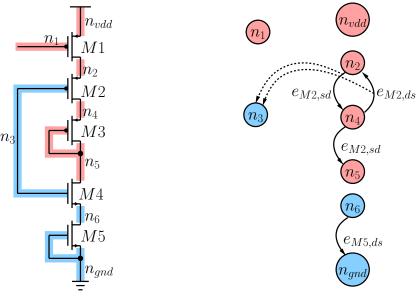

A simple amplifier circuit as shown on the right of Fig. 1.1 can be found in many designs. The example circuit receives a bias current over port in1. The differential input voltage between in2 and in3 is amplified to a single-ended output voltage between out1 and ground. The power mode is controlled by the signal on pin pwd.

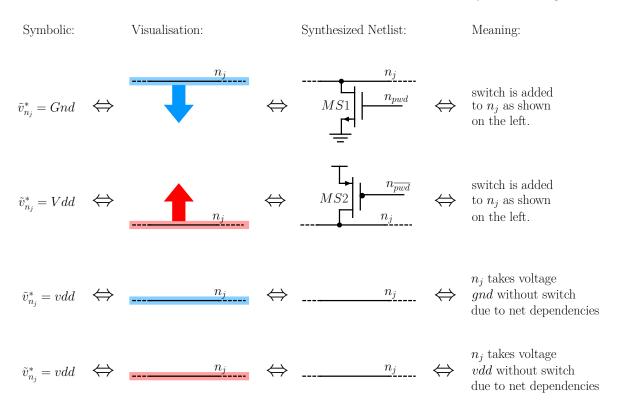

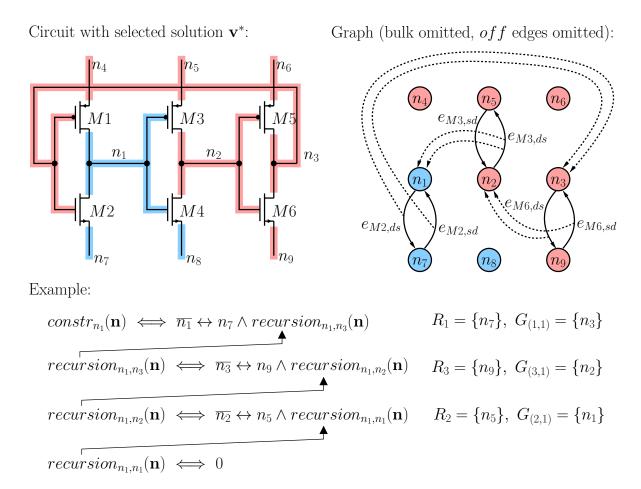

The core part of the circuit in Fig. 1.1 is given by the transistors M1 to M6. They implement a simple differential amplifier, i.e. the power-up functionality of the circuit. In contrast, the power-down circuitry is formed by the power-down switches MS1 to MS8. This thesis follows the convention that the transistors forming the power-up part of a circuit are labeled with Mx and the power-down switches are labeled with MSx where x is a number. Two inverters buffer the incoming pwd signal and generate the inverted signal  $\overline{pwd}$ . The buffered pwd signal as well as the inverted signal  $\overline{pwd}$  are connected to the gates of the power-down switches. The switches can be conducting or off depending on the signal on the gate of the switches. There are n-MOSFETs and p-MOSFETs. They can either have the signal pwd or  $\overline{pwd}$  connected to their gates. This leads to four possible combinations. The states of the power-down switches for those four combinations for power-up and power-down mode are given in Table 1.1. The left table shows the states for the power-down mode and the right one for the power-up mode.

The power-down circuitry for the differential amplifier shown in Fig. 1.1 works as follows: Power-down switch MS1 is conducting in power-down mode and therefore pulls the gates of M1 and M2 to vdd. Consequently, the bias current through those two transistors is off. Switch MS2 is added in order to avoid current flow from MS1 over in1 over external circuitry to ground. The switch isolates the gates of M1 and M2 from external circuitry connected to in1. In power-up mode, MS1 is off and has nearly no effect on the differential amplifier. MS2 is conducting and the transistors M1 and M2 act as a current mirror to bias the differential amplifier. The switch MS2 has only to charge the gates of M1 and M2. The static bias current through MS2 is zero. Furthermore, no AC signal is transferred over MS2. Consequently, MS2 has nearly no effect on the operation of the differential amplifier in power-up mode. To sum up, MS1 and MS2

implement shutdown of all bias currents in power-down mode and do not significantly interfere with the circuit in power-up mode.

The switches MS5/MS6 and MS7/MS8 isolate the differential input of the amplifier from external circuitry during power-down mode. Furthermore, the switches MS3 and MS4 pull the gates of M3 and M4 to a defined voltage (vdd). This has two advantages: First, it makes the behavior of the circuit more predictable than it would be with floating gates of MS3 and MS4. Second, it avoids transistor aging of MS3 and MS4 due to negative temperature instability (NBTI) [Chouard et al., 2011; Schlünder, 2010; Schlunder et al., 2003].

There is one more aspect of aging that is illustrated by the differential amplifier: The switches MS3 and MS4 ensure matched power-down voltages for the p-MOS differential pair M3/M4. Matching is an important design principle of analog circuits. Matched devices should be as identical as possible. Mismatch can occur due to manufacturing variations and due to electrical stress. Differential pairs like M3/M4 are typical examples for mismatch sensitive building blocks. Mismatch caused by stress is called time dependent mismatch [Chen et al., 2001; Michael et al., 1992; Maricau and Gielen, 2011]. Time dependent mismatch can occur due to electrical stress in power-down mode [Zwerger and Graeb, 2015; Georgakos, 2014. The likelihood of extreme stress voltages in power-down mode is even higher than during power-up mode as internal nodes of the circuit are pulled to the extreme voltages gnd and vdd. The pattern implemented by the switches MS3 to MS8 avoids time dependent mismatch caused by electrical stress during power-down mode. Therefore, it increases the lifetime and reliability of the circuit. It is a design decision if the extra effort is necessary. The decision depends on the design-style, the aging behavior of the used used technology and the reliability/lifetime requirements of the application.

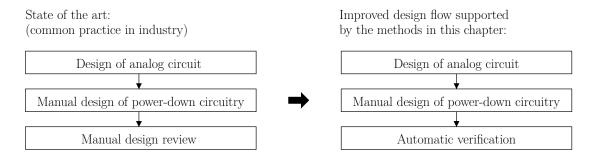

In power-down mode, internal nodes can be floating. A floating node is a node that has only high resistive connections to other nodes of the circuit. The voltages of floating nodes are hard to determine by numerical circuit simulation, e.g. SPICE [Nagel, 1975]. For instance, the internal node  $n_1$  in Fig. 1.1 is completely isolated from the rest of the circuit in power-down mode. Its voltage depends on the subthreshold behavior of M1, M3 and M4 and on possible other leakage paths on the chip (e.g. through the substrate). Voltages of floating nodes can be very sensitive to manufacturing variations and on circuit properties that are not modeled with sufficient accuracy, e.g. the subthreshold region of the transistors or parasitic resistances. Hence, the voltage calculated for a floating node like  $n_1$  by a numerical circuit simulator may not be trustworthy. It follows that verification of the circuit by numerical circuit simulation is problematic in presence of floating nodes. However, floating nodes in power-down mode can be determined by the circuit structure similarly to the way a designer would identify floating nodes by inspecting a circuit.

In this thesis, new methods for the verification and synthesis of analog power-down circuits are developed. The verification method takes into account the problems induced

by floating nodes as described in the previous paragraph. It further takes into account reliability considerations, i.e. transistor aging. The insights gained from formulating verification rules can be used as starting point for investigating the possibilities of automatic synthesis of power-down circuitry. Verification becomes obsolete if automatic synthesis is possible because the circuitry is systematically created by a computer program. Algorithms for both, verification and synthesis, should be easy to use. It is further desirable that they allow an interactive, semi-automatic design style. In the next section, the state of the art of analog power-down verification and synthesis is discussed and contributions of this thesis are highlighted.

#### 1.2. State of the Art and Contributions

Verification of the analog power-down mode and synthesis of analog power-down circuitry was not subject of intensive research so far. However, there are plenty of published methods for verification and synthesis of analog circuits. Consequently, those methods will be surveyed in the this section with respect to suitability to solve the analog power-down verification or synthesis task. The relationship of the established methods to the methods prensented in this work is pointed out. Contributions of this thesis to the state of the art are highlighted for each topic area if applicable.

# 1.2.1. Verification of Analog Circuits

## **Numerical Circuit Simulation**

Traditional analog verification builds on numerical circuit simulation. Numerical circuit simulation started with the SPICE simulator in the 1970s [Nagel, 1975]. Today, many commercial and mature simulation tools are available, e.g. [Cadence Design Systems, 2015b; Mentor Graphics, 2015b; Synopsys, 2015b]. Furthermore, there are nowadays simulators that are optimized for full-chip simulation. These simulators are usually referred to as "Fast Spice" simulators. They apply optimization techniques to speed up simulation in order to make full-chip simulation feasible [Rewienski, 2011]. There are also "Fast Spice variants" for each of the three commercial simulation tools mentioned above [Cadence Design Systems, 2015a; Mentor Graphics, 2015c; Synopsys, 2015a].

The behavior of the power-down mode can be characterized by the static behavior of the circuit. All nodes should settle at a defined value and the static current should be zero. Nodal analysis (DC analysis) as implemented by state-of-the-art circuit simulators can be considered for this verification task [Ho et al., 1975]. However, floating nodes cause values of node voltages that may not be trustworthy. This problem is especially significant if the power-down state of a circuit is examined. Many transistors will operate in the subthreshold region due to the nature of power-down mode: It cuts off the bias currents.

Modern simulators apply techniques like gmin-stepping or source stepping [Yilmaz and Green, 1999] in order to achieve convergence in presence of floating nodes. However, the problems mentioned in section 1.1 remain unresolved: The voltages of floating nodes can be highly dependent on manufacturing variances and effects like leakage currents that are very hard to model completely. An example of misleading DC simulation results is shown in section 3.2.7.

The transitions between power-up and power-down mode are characterized by the transient behavior of the circuit. The settling times of all nodes have to be appropriate for a given application. Floating nodes appear in the result waveforms of transient simulation [Cadence Design Systems, 2015b; Mentor Graphics, 2015b; Synopsys, 2015b] as nodes with extremely large settling times. It is non-trivial to write assertions that systematically discover those occurrences. An example is discussed in section 3.2.7. More importantly than the problem of defining adequate assertions, the problem of incomplete modeling and high sensitivity to manufacturing variances also applies for transient simulation. Additionally, transient simulation depends on the input stimuli. A complete verification by exhaustive transient simulation taking into account all (or approximately all) input stimuli is impossible due to exploding computational effort.

# Symbolic Analysis

Other circuit models than those used for numerical simulation, e.g. symbolic analysis, can be considered in order to avoid the above mentioned problems. Research on symbolic analysis was particularly active in the late 1980s and beginning of the 1990s. An overview is given in [Rutenbar et al., 2002]. Symbolic analysis does not solve equation systems or differential equations as it is done by numerical simulation. Instead, it tries to approximate the circuit behavior with symbolic expressions. A model of the the circuit is generated that gives insight in the dependencies between performances and parameters. The term symbolic analysis usually refers to methods that approximate AC transfer functions of the circuit, e.g. [Fernández et al., 1991; Starzyk and Konczykowska, 1986; Gielen et al., 1989; Li and Gu, 1992; Wambacq et al., 1995; Yu and Sechen, 1995; Wambacq et al., 1999; Shi and Tan, 2000. There are also methods that approximate the time-domain (transient) behavior of the circuit, e.g. [Kobylarz, 1969; Hassoun and Ackerman, 1990; Yu et al., 2014; Liu et al., 2012; Grabowski et al., 2006; Yang et al., 2005; Zhang and Shi, 2011]. Transient symbolic methods can be used for efficient characterization of the impact of process variations on the transient behavior [Yu et al., 2014; Liu et al., 2012; Grabowski et al., 2006. Two of the mentioned papers claim that the method is also capable of doing symbolic DC analysis in their abstract. However, in [Kobylarz, 1969] it is stated that currently only transient analysis is available and no DC results are shown. The method in [Hassoun and Ackerman, 1990] suggests that the frequency should be set to zero in AC analysis for a DC characterization. However, the presented results do not explicitly give insight in the DC behavior of the used example circuits.

It can be summarized that symbolic analysis mainly focuses on frequency domain behavior. The frequency domain methods are suitable for power-up mode characterization but not for power-down mode characterization. Methods for static and transient symbolic analysis can be considered to solve the power-down verification task. However, static methods are barely available and the available transient methods aim at a higher accuracy of characterization than actually needed to describe the power-down mode behavior. It will be shown in section 3.2 of this thesis that the power-down mode behavior of analog circuits can be meaningfully approximated by using discrete (digital) voltages and a static approach. The approximation uses values of vdd and ground to describe the power-down mode behavior. It turns out that a discrete approximation of the behavior is robust and does not generate misleading results as other methods may do in presence of floating nodes.

# State-Space Oriented Verification and Formal Methods

Above, the problem of exploding computational effort of transient analysis of large systems with many inputs and input stimuli was addressed. In analog verification, methods for state-space oriented verification are an active field of research (e.g. [Steinhorst and Hedrich, 2012c; Dastidar and Chakrabarti, 2005). Those methods are subject to the state-space explosion problem, i.e., it is practically impossible to cover the whole state-space with transient simulation. Consequently, those methods focus on intelligent measures to circumvent the problem, i.e. by intelligent stimuli generation [Steinhorst and Hedrich, 2010, 2012b; Ahmadyan et al., 2013; Yin et al., 2013]. On the other hand, if adequate coverage of the state-space is ensured, the remaining (non trivial) problem is checking if the circuit fulfills the specified (and sometimes non-specified but essential) requirements. The problem is addressed by formal verification methods for analog circuits. A survey is given in [Zaki et al., 2006]. It categorizes the methods into "equivalence checking", "model checking" and "reachability analysis", "runtime verification methods" and "deductive methods". In equivalence checking, the circuit is checked for equivalent behavior with a reference circuit or an abstract behavioral model. In model checking and reachability analysis, the reachable set of the state space is approximated. Those methods are suitable for ensuring that the system does not enter into a bad state. However, they suffer from the state-space explosion problem.

Runtime verification tries to overcome this problem by omitting the step of creating a computational model. The required properties of the circuit have to be monitored / asserted on the result waveforms as no model for comparison is available. The list of publications is long and the methods are diverse. For example, in [Steinhorst and Hedrich, 2012a] a method that applies verification in the state-space using the Analog Specification Language (ASL) is presented. In [Bonfini et al., 2006], a framework that helps to reuse techniques from state-of-the-art digital verification (e.g. automatic results collection, coverage elaboration, stimuli generation) is presented. In [Dastidar and Chakrabarti, 2005], an "Analog Conventional Temporal Logic (Ana CTL)" which

can be used to specify complex properties of the transient behavior of analog systems is presented. In [Maler and Nickovic, 2004], a temporal logic that is used for specifying the behavior of time discrete systems is adapted for the continuous case. More examples can, e.g., be found in [Zaki et al., 2006].

The last category of the analog formal verification methods mentioned in [Zaki et al., 2006] are the deductive methods. Deductive methods try to describe the circuit behavior with logic equations and use formal deduction to prove that the circuit implies the specified behavior. For instance, Hanna describes a predicate logic based on rectilinear specifications of the device behavior as a conservative approximation of the real device behavior [Hanna, 2000]. In [Ghosh and Vemuri, 1999], an approach for formal verification of the DC behavior of analog designs containing linear and piecewise linear components is presented. It checks the circuit against a user given specification using the higher order logic proof checker PVS. The principle of the logic description of the devices is similar to [Hanna, 2000]. However, the device equations on currents and voltages are used instead of rectangular approximations.

A deductive approach like [Ghosh and Vemuri, 1999] or [Hanna, 2000] can be considered for formal verification of the power-down mode behavior. A method for automatic deduction of the proposed logic and for automatic checking against the specification needs to be developed for this purpose. However, the method in [Hanna, 2000] is limited to the description of the theory. A case study showing the automated applicability of the rectilinear logic to larger circuits is missing. Such a case study is given for circuits containing up to five op amps in [Ghosh and Vemuri, 1999]. The examples are telephone receiver and transmitter circuits as well as a not further specified circuit named "Neural Contr". The runtimes are "of the order of a few minutes" on a Sun workstation of this era.

A formal specification of the power-down mode behavior is required if formal verification is used. Defining the specification is a non trivial task. To the best of my knowledge, there is no prior publication on this topic. The research for this thesis investigated if voltage propagation (see section 3.2) can be replaced by a description of the circuit in terms of logic equations [Vlachas, 2014]. Those equations should then be used to prove that no current is flowing and no floating nodes are present in power-down mode using a constraint program solver [Christian Schulte and Z.Lagerkvist, 2013]. Four different constraint programs have been investigated as alternative to the voltage propagation method described section 3.2. The investigations have shown that this approach is feasible, but finding the correct set of logic equations is a challenging task and the approach has the following limitations: The answer of the constraint-program solver is "false" if the circuit has a design error. No further information for diagnosis is available at this point and it is hard to locate the design error or to get further insight into the circumstances that caused the error. While working on this thesis, it was further investigated if this problem can be solved by adding further conditions for locating short-circuit paths in power-down mode. The results show that this is principally possible [Vlachas,

2014]. However, the automatic creation of the logic equations tends to become very complicated. The simplest, most robust and fastest constraint program was published in [Zwerger et al., 2015b]. The other three constraint programs documented in [Vlachas, 2014] can be seen as steps towards formal verification of the power-down mode. However, the voltage propagation method described in section 3.2 has proven to be the superior solution in terms of practicability and robustness. The main advantage of voltage propagation and short-circuit search as described in section 3.2 is the fact that intermediate results can be used for diagnosis in the case design errors are detected.

# Macromodeling

Macromodeling tries to abstract the circuit behavior by leaving out details in order to speed up the evaluation of the system performance. Macromodels can, e.g., be divided into black box models (e.g. [Boyle et al., 1974]) that model the dependence of performance attributes on design parameters and structural models [Ferent and Doboli, 2013; Wei and Doboli, 2008]. There are many diverse approaches for model generation. Following the introduction of [Ferent and Doboli, 2013], there are methods for modeling a large variety of performance attributes including AC performances, weakly nonlinear performances or large-signal nonlinear-related attributes. The models can be grouped by the used modeling techniques, e.g. regression analysis, symbolic analysis (as discussed above), neural networks, piecewise-linear approximation, optimization-based symbolic descriptions, support vector machines, system identification or model-order reduction. References to example methods are given in [Ferent and Doboli, 2013].

For power-down mode verification, we are mainly interested in methods that model the static behavior of the circuit without simulation. In [Wei and Doboli, 2008], it is concluded that "present modeling methods are mostly for black-box modeling in the frequency domain". Those models are not suitable for power-down verification. However, structural models are candidates for power-down mode modeling. A structural model for systematic comparison of circuits is presented in [Ferent and Doboli, 2013]. The comparison focuses on "DC gain, bandwidth, noise, CMRR and sensitivity", hence, on small signal features. In [Wei and Doboli, 2008], a structural model in the frequency domain is presented. To the best of my knowledge, there is no publication on macromodeling of static circuit performances that is not simulation based. However, there are other non-simulation based approaches for static analysis. Those are switch-level simulation and voltage propagation. Both approaches rely on some kind of static modeling. The approaches are described in the next two paragraphs.

## **Switch-Level Simulation**

"Modeling a MOS circuit as a network of simple switches began in 1979 with the development of the Mossim simulator. Since that time, dozens of switch-level simulators have

been implemented" [Bryant, 1987]. The survey of switch level algorithms in [Bryant, 1987] mentions "logic and fault simulation", "formal hardware verification", "timing analysis" and "automatic test pattern generation" as applications. Research on switch level simulation was particularly active during the late 1980s and early 1990s (e.g. [Adler, 1991; Meyer and Camposano, 1993; Blaauw et al., 1991; Vandris and Sobelman, 1990; Huang and Bryant, 1993; Dahlgren, 1995; Jones and Blaauw, 1994; Kravitz et al., 1991; Asai and Suzuki, 1992; Ramachandran, 1986; Svensson and Tjarnstrom, 1988; Hajj, 1990; Bryant, 1988; Yuan and Svensson, 1988]) The research focused on achieving speed-up / efficiency [Adler, 1991; Meyer and Camposano, 1993; Blaauw et al., 1991; Vandris and Sobelman, 1990; Jones and Blaauw, 1994; Kravitz et al., 1991; Asai and Suzuki, 1992; Bryant, 1988], improving the switch-level model [Huang and Bryant, 1993; Dahlgren, 1995; Ramachandran, 1986; Svensson and Tjarnstrom, 1988], investigating theoretic aspects [Hajj, 1990; Adler, 1991] or investigating other applications like speed optimization of CMOS circuits (e.g. [Yuan and Svensson, 1988]).

Switch level simulators model the static behavior of the circuit by a structural approach. Usually, the circuit node voltages are represented by ternary logic values, i.e. 0, X, and 1. The value X defines an undefined state (see e.g. [Bryant, 1984; Adler, 1991]). Furthermore, timing behavior can be modeled by taking into account node capacitances and a repeated evaluation of the static switch-level model. The ideas of switch-level simulation are candidate ideas to be adopted for power-down mode verification. There are similarities to the graph model presented in section 3.2. However, the difference between the models developed for switch level simulation and the graph model from section 3.2 are the properties that are abstracted. Switch level simulators abstract the logic behavior (including timing) of digital circuits whereas the graph model developed in section 3.2 abstracts the static DC behavior of an analog circuit. The commonly used approach to abstract the DC behavior of analog circuits used in state-of-the-art tools is voltage propagation. It is described in the next paragraph.

# **Voltage Propagation**

Voltage propagation is used in analog circuit verification for electrical rule checks. For instance, electrical rule checks can comprise checks for correct power-domain transitions, e.g. [Hogan, 2014; Medhat, 2009, 2012; Lescot et al., 2012; Pompl et al., 2006], or for correct protection against electro static discharge (ESD), e.g. [Darfeuille, 2012; Medhat, 2009; Ker et al., 2011; Lu and Bell, 2010; Pompl et al., 2006]).

Static checks and voltage propagation are implemented in commercial analog/mixed-signal verification tools. The tool "CustomSim Circuit Check (CCK)" from Synopsys implements, among other features, "Design and Electrical rule checks" and "Low-power design and leakage detection" [Synopsys, 2015]. The description of the "Design and Electrical rule checks" claims that the tool can, among other plausibility checks, detect floating gates before simulation. Furthermore, it monitors excessive currents during

simulation. The description of the "Low-power design and leakage detection" claims detection of leakage current paths, monitoring of standby current and identification of high-Z nodes during simulation. According to the product description, CCK's features are comparable to the voltage propagation and short-circuit detection presented in section 3.2 of this thesis. However, to the best of my knowledge, no public description of the details of the used methods is available. Furthermore, the tool still partially relies on numerical circuit simulation which can be problematic.

The tool PERC ("Programmable Electrical Rule Check") from Mentor graphics [Mentor Graphics, 2015a] features methods, among others, to detect electrical overstress (EOS) at thin-oxide devices, to verify ESD protection rules and electrical rule checks for multi power-domain designs [Mentor Graphics, 2016]. Applications of PERC are, e.g., described in [Lu and Bell, 2010; Hogan, 2014; Lescot et al., 2012]. PERC can propagate voltage in a vectorless mode as well as in a vectored mode. The vectored mode is comparable to the voltage propagation described in section 3.2 of this thesis. As PERC is programmable, the propagation rules are user input. To the best of my knowledge, no description of a rule set with similar completeness as the graph model described in section 3.2 is publicly available. It would be possible to implement the propagation rules of this thesis within the PERC framework. Evaluating potential runtime improvements of this approach compared to the experimental implementation in this thesis is left for future work. Furthermore, vectorless propagation was not investigated in this thesis. It is a candidate to solve the voltage enumeration problem described in section 3.3.6 in future work.

To the best of my knowledge, there is only one prior academic publication that describes a voltage propagation approach [Blieck and Janssens, 1996]. The algorithm was developed for power-down mode verification. The paper describes a basic version and an elaborated version of the algorithm. The basic version is limited to resistors and MOS devices, i.e., bulk diodes cannot be considered. Furthermore, there is no guarantee that all potential short-circuit paths are found. These limitations are solved by the elaborated version. It additionally supports diodes and guarantees the detection of all potential short-circuits. Compared to the elaborated version, the voltage propagation method described in section 3.2 of this thesis makes the following new contributions:

- A precise, unified, graph-based description of the algorithm is given.

- Propagation rules for all common analog components are given including diodes and bipolar transistors.

- Improved modeling of diode-connected and off-connected transistors.

- The runtime complexity is analyzed.

- The detected short-circuit paths are categorized into definite paths, potential paths and induced path in order ease locating the root cause of the problem for diagnosis.

- Experimental results for larger, hierarchical designs are given.

Voltage propagation is a fundamental basis for the verification of power-down reliability constraints as described in section 3.3. Voltage propagation and short-circuit detection

were originally published in [Zwerger and Graeb, 2012a,b, 2013]. Section 3.2 presents an extended version.

#### **Constraint-Driven Verification and Constraint Generation**

State-of-the-art design tools support constraint-driven design. An overview over this design paradigm can, e.g., be found in the introduction of [Meyer zu Bexten et al., 2015]. Constraint-driven design is supported by state-of-the-art design flows. For instance, the Cadence Virtuoso Design Framework that is one of the most popular development frameworks for full custom IC design provides functions to store, manage, create and verify design constraints. There are many different types of constraints, e.g. electrical constraints, placement constraints or routing constraints. A typical class of constraints are matching constraints which ensure matching between circuit elements. Matching constraints can be written down for sizing, layout, routing, etc. In this thesis, matching constraints for reliability of the power-down mode are developed. They are described in section 3.3 along with a method for automatic verification.

Constraints can be annotated manually by the designer or automatically generated. Symmetries in the circuit need to be computed for automatic generation of matching constraints. Basic symmetries can be computed for pairs of devices, e.g. for differential pairs. Therefore, basic building blocks (e.g. differential pairs) need to be detected in a given netlist. Pattern matching can be used for this purpose. It finds given subcircuits, i.e. building blocks, in a given netlist, e.g. [Lescot et al., 2012; Meyer zu Bexten et al., 2015; Pelz and Roettcher, 1994; Rubanov, 2006; Ohlrich et al., 1993; Ebeling, 1988]. Pattern matching usually faces the problem of ambiguities while detecting subcircuits. A specialized method that resolves ambiguities for different types of current mirrors and differential pairs was published in [Massier et al., 2008; Massier, 2010]. The original intent of this method was the automatic generation of sizing constraints. Nevertheless, the algorithms can also be used for automatic generation of other classes of matching constraints. The algorithm was extended for mixed-signal applications and improved in terms of efficiency in [Eick, 2013]. The development of the algorithm was continued for this thesis. In chapter 2 an improved version is presented. It meets the requirements of automatic constraint generation for power-down mode reliability for hierarchical designs.

The key contributions to structure recognition can be summarized as follows:

- The ambiguity arbitration mechanism of [Massier et al., 2008; Massier, 2010] and [Eick, 2013] is simplified/generalized without deteriorating recognition quality.

- A new library for detecting components forming the power-down signal path is developed.

- The implementation was improved. It was integrated into an industrial design flow using the Open Access Database [Si2 Consortium, 2013]. For the first time, the

efficiency of the method published in [Eick, 2013; Massier et al., 2008; Massier, 2010] is demonstrated by experimental results for industrial, hierarchical circuits.

The improved structure recognition and the voltage propagation from section 3.2 form the basis for the power-down reliability verification in section 3.3.

Hierarchical pattern matching is also subject of [Milošević, 2009]. The PhD thesis proposes "Virtually Flattened Views" that make hierarchical data accessible as it would be after flattening. The approach is a candidate for further speed-up of structure recognition in future work. The implementation of the structure recognition approach discussed in chapter 2 is able to read hierarchical circuits. The designs are internally flattened during a prepossessing step. Consequently, the implementation approach presented in [Milošević, 2009] is a candidate approach to be investigated for further speedup.

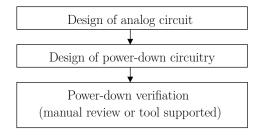

## 1.2.2. Power-Down Verification

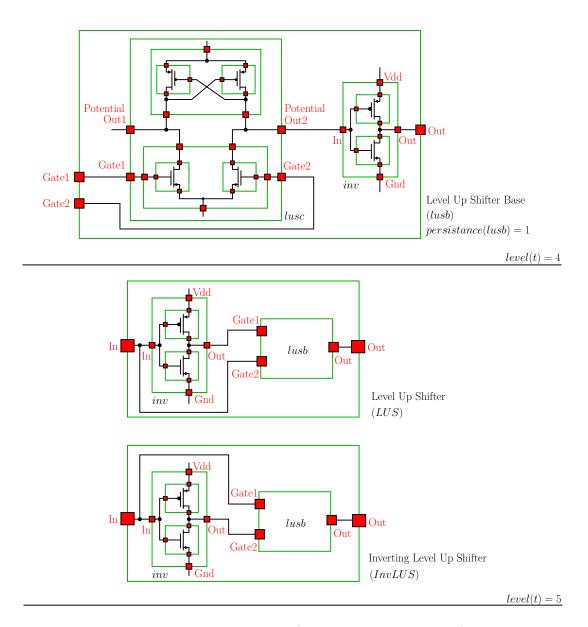

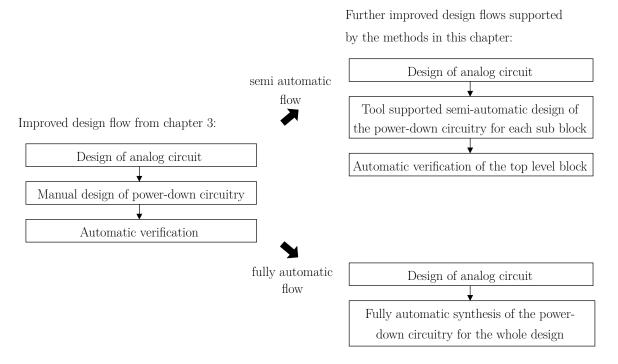

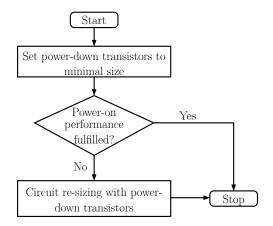

Fig. 1.2 shows a typical state-of-the-art design flow for analog power-down circuit design. First, the core part of the circuit that implements the basic analog functionality of the circuit block is designed. The power-down circuitry is manually added towards the end of the design process. The functionality of the power-down mode is then checked by a manual design review or by a tool supported flow using tools like Mentor PERC [Mentor Graphics, 2015a] or Synopsys Circuit Check [Synopsys, 2015]. The practices may vary from company to company and are not publicly documented. To the best of my knowledge, the only publication that explicitly deals with power-down verification is [Blieck and Janssens, 1996]. It describes a very basic voltage propagation approach as mentioned above. Furthermore, no previous publication on the verification of power-down reliability matching constraints is known to the author. Power-down reliability verification as described in section 3.3 was developed as part of a joint research project together with Infineon Technologies. It was first published in [Zwerger and Graeb, 2015]. The approach was patented in [Georgakos, 2014]. Section 3.3 presents an extended version of [Zwerger and Graeb, 2015].

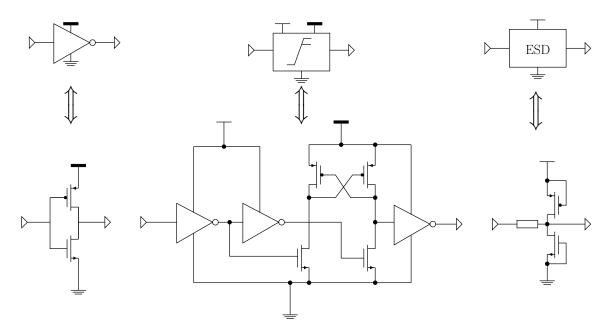

Figure 1.2.: Typical design flow for power-down circuitry

The state-of-the-art design flow shown in Fig. 1.2 will be extended in this thesis (see Figs 3.1 and 4.1). Improved tool support for power-down verification is subject of chapter 3 (see Fig 3.1).

The main contributions of this thesis to power-down verification can be summarized as follows:

- A new and complete method for floating node and short-circuit detection based on voltage propagation is presented

- The first method for reliability verification of the power-down mode is presented.

- The efficiency, effectiveness and practicability of the method is demonstrated on industrial example circuits.

# 1.2.3. Analog Circuit Synthesis

In chapter 4 (see Fig. 4.1), methods for power-down synthesis are discussed. Therefore, this section summarizes the state of the art in analog circuit synthesis.

Synthesis of analog circuits is a field of research that was particularly active in the 1990s. An overview over publications of this era, e.g. [Degrauwe et al., 1987; Harjani et al., 1989; Gielen et al., 1990; Harvey et al., 1992; Maulik et al., 1995; Antao and Brodersen, 1995; Kruiskamp, 1995; Plas et al., 2001; Crols et al., 1995; Medeiro et al., 1994; Ochotta et al., 1996; Phelps et al., 2000; Antreich et al., 2000; Hershenson et al., 2001; Koh et al., 1990], is given in [Rutenbar et al., 2002].

There are knowledge based approaches, optimization based approaches and approaches that are a mixture of both categories. Knowledge based approaches formalize expert knowledge in order to exploit it for automatic synthesis, e.g. [Degrauwe et al., 1987; Harjani et al., 1989]. The optimization based approaches can be classified with respect to the used optimization method and the used circuit model. Optimization approaches can be, e.g., simulated annealing, geometric programming, genetic algorithms or deterministic optimization methods. The circuit models can be, e.g., symbolic models, behavioral models or numerical models (see also section 1.2.1).

Research on analog circuit synthesis is still ongoing. For example: In [Jiao et al., 2015], new mining techniques for analog circuit design metaknowledge are proposed. A new reasoning-based method is proposed in [Ferent et al., 2012]. A new method based on evolutionary optimization and numerical simulation is presented in [Lourenço and Horta, 2012]. The introduction of the paper gives a comprehensive overview over previously published analog synthesis approaches including many of the above cited examples. A fully deterministic, rule-based, constructive synthesis method is proposed in [Meissner and Hedrich, 2015].

All the mentioned methods for analog circuit thesis have in common that they synthesize the power-up behavior of the circuit. None of the methods is dealing with analog powerdown circuit synthesis.

# 1.2.4. Power-Down Synthesis

Power optimization is incorporated into state-of-the-art digital synthesis tools [Keating et al., 2007]. However, digital power-optimization techniques require different approaches and should not be confused with power-down techniques. In the digital world, circuit blocks are usually powered down by power gating or clock gating. Retention cells are added at the block boundary in order to avoid problems in other blocks that are connected to the block that is powered-down.

The analog power-down mode has completely different requirements. Power gating would introduce head or food switches and reduce the available voltage swing. This is not feasible in times of ever shrinking supply voltages. Furthermore, special requirements like the reliability considerations from section 3.3 have to be taken into account.

To the best of my knowledge, no prior work on power-down circuit synthesis for analog circuits was published so far. The ideas presented in chapter 4 were originally published in [Zwerger et al., 2015a]. Chapter 4 presents an extended and improved version of the method.

The main contribution of this thesis to power-down synthesis can be summarized as follows:

- The first method for the synthesis of analog power-down circuits is presented.

- Experimental results demonstrate the effectiveness and efficiency of the method for amplifier circuits (CMOS and BiCMOS), an oscillator circuit and an industrial LVDS driver circuit.

- The practicability of the method is demonstrated. It is shown that the method can easily be adopted to augment state-of-the-art industrial design flows by adding a schematic backannotation step.

## 1.3. Previous Publications

Parts of the methods and ideas of this thesis were previously published. The voltage propagation based floating node and short-circuit verification from section 3.2 was originally published in [Zwerger and Graeb, 2012a,b, 2013]. A formal approach was investigated in [Zwerger et al., 2015b] as an alternative to voltage propagation. The method for power-down reliability verification described in section 3.3 was partially published in [Zwerger and Graeb, 2015]. The power-down synthesis approach described in chapter 4

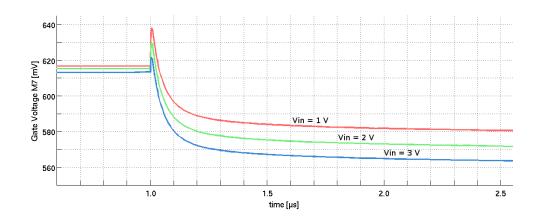

was partially published in [Zwerger et al., 2015a]. Simulation results for power-down synthesis were published in [Zwerger et al., 2016]. Student theses [Ferraria, 2013; Neuner, 2015; Shrivastava, 2016; Neuner, 2013; Schillmaier, 2014; Vlachas, 2014] and internship projects [Leitao, 2012b,a; Meyer-Jungclaussen, 2014; Mlayeh, 2012] contributed to the results presented in this work.

# 1.4. Overview over this Thesis

This thesis is structured as follows: Power-down verification is subject of chapter 3. The chapter deals with the following two main topics:

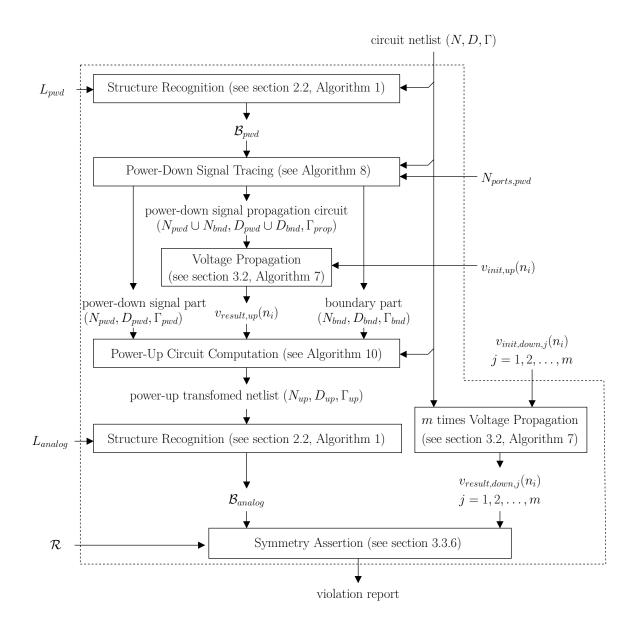

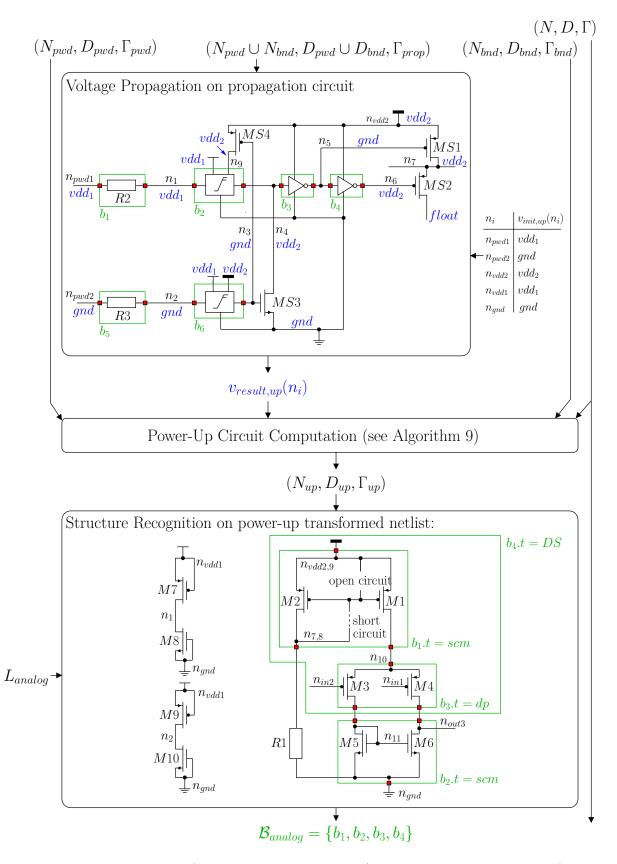

- 1. A method to detect floating nodes and short circuits in power-down mode is presented in section 3.2. It is based on a voltage-propagation method and circumvents the problems of numerical simulation. It uses a graph-based model to model the static behavior of the circuit in power-down mode.

- 2. A method for detecting asymmetric device stress in power-down mode is described in section 3.3. It requires a voltage propagation method (e.g. section 3.2) and a structure recognition method (e.g. chapter 2).

Chapter 4 presents the new method for power-down synthesis. The graph model from voltage propagation (section 3.2), structure recognition (chapter 2) and the rules developed for detecting asymmetric device stress (section 3.3.5) are the basis of the power-down synthesis method.

Experimental results for each of the mentioned methods are presented at the end of the corresponding sections/chapters. The experimental results for structure recognition are given in section 2.4. The experimental results for floating-node and short-circuit detection are described in section 3.2.7. Section 3.3.7 presents the results of the detection of asymmetric stress. The experimental results of power-down synthesis are discussed in section 4.4.

The thesis concludes with chapter 5.

# 2. Structure Recognition

# 2.1. Motivation and Problem Description

Structure recognition plays an important role in design automation for analog circuits. Typical applications are the automatic generation of constraints for a constraint-driven design style or for automatic sizing methods, e.g., [Massier et al., 2008]. Furthermore, structure recognition methods can be found in commercial verification tools (e.g. [Mentor Graphics, 2015a) to support verification tasks like electrical rule checking for reliability, ESD protection, voltage domain checks and other tasks. In this thesis, structure recognition is required for the detection of asymmetric voltages in power-down mode as described in section 3.3 and for power-down synthesis as described in chapter 4. For the detection of asymmetric voltages, common analog building blocks and blocks forming the power-down signal path need to be identified. Current mirrors need to be detected for the current mirror rip-up heuristic used in power-down synthesis (see section 4.3.3). In general, any structure identification method can be used for those applications. An algorithm based on the sizing rules method [Massier et al., 2008; Massier, 2010; Eick, 2013 is used in order to generate the experimental results presented in this thesis. The structure recognition method was refined in order to meet the requirements for large hierarchical circuits. Experimental results for circuits with sizes up to 20.000 devices are presented in section 2.4. Hence, this is the first work to present experimental results that demonstrate the efficacy and efficiency of the sizing rules method for industrial analog cells.

# 2.2. Enhanced State-of-the-Art Algorithm

In this chapter, the structure recognition algorithm used in this thesis is described. It is based on the sizing rules method. The sizing rules method was originally published in [Massier et al., 2008]. A more detailed description can be found in [Massier, 2010]. The original algorithm was refined in [Eick, 2013]. The algorithm presented in this section is based on the refined version. This chapter outlines the main ideas of structure recognition with emphasis on the enhancements that were made compared to the state-of-the-art versions.

#### Algorithm 1 StructureRecognition

```

Require: circuit netlist with devices D, supply rail information, Library L

1: // the building blocks of level 0 are the devices

2: \mathcal{B} := D

3:

4: // \text{ find arrays of devices on level } 1

6: for all array types t_{array} in hierarchy level L_1 do

\mathcal{B}_1 := \mathcal{B}_1 \cup \operatorname{FindArrays}(t_{array}, \mathcal{B}) / / \operatorname{see} [Eick, 2013], section 3.2.2

8: end for

9: \mathcal{B} := \mathcal{B} \cup \mathcal{B}_1

11: // find pairs on level 2 and above

12: for l = 2 to maxLevel(L) do

\mathcal{B}_l := \{\}

13:

for all pair types t_{pair} in hierarchy level L_l do

14:

\mathcal{B}_l := \mathcal{B}_l \cup \operatorname{FindPairs}(t_{pair}, \mathcal{B}) // see [Eick, 2013], section 3.2.1

15:

16:

end for

\mathcal{B} := \mathcal{B} \cup \mathcal{B}_l

17:

18:

// arbitration enhanced and simplified compared to [Eick, 2013]:

19:

\mathcal{B} := \operatorname{SelfArbitration}(\mathcal{B}, l) // \operatorname{Algorithm} 2

20:

\mathcal{B} := \operatorname{CrossCoupledPairArbitration}(\mathcal{B}, l) // Algorithm 3

21:

22: end for

23:

24: // final removal of uncertain building blocks

25: \mathcal{B} := \text{SelfArbitration}(\mathcal{B}, \text{maxLevel}(L) + 1)

26:

27: return \mathcal{B}

```

The main enhancements can be summarized as follows:

- The removal of uncertain building blocks described in [Eick, 2013] and the dominance relation introduced in [Massier et al., 2008; Massier, 2010] have been combined to a self arbitration step and a minimalistic dominance rule for the cross coupled pair.

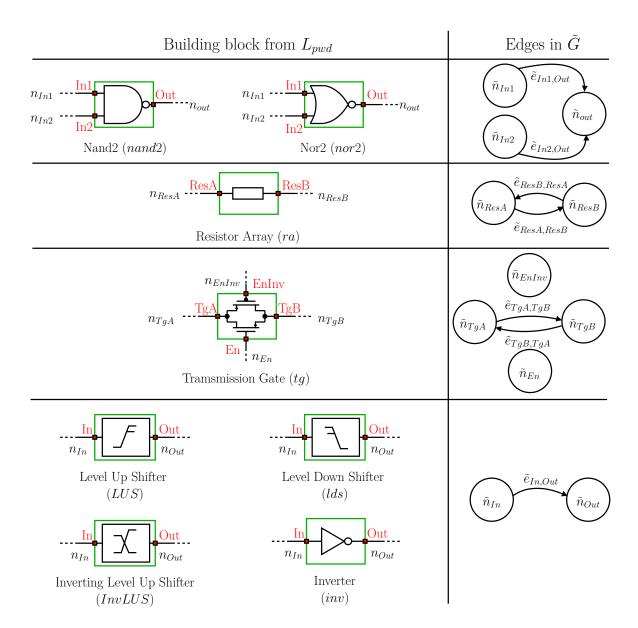

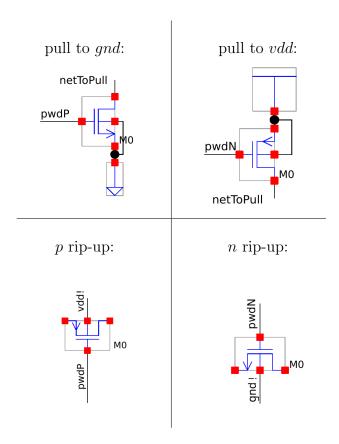

- A new building block library (see Figs. 2.2 and 2.3) for detecting building blocks forming the power-down signal path was developed.

- The implementation has been improved in terms of suitability for industrial sized hierarchical circuits. Experimental results demonstrate the efficiency of the method for industrial sized circuits.

The structure recognition algorithm is given in Algorithm 1. It finds the building blocks

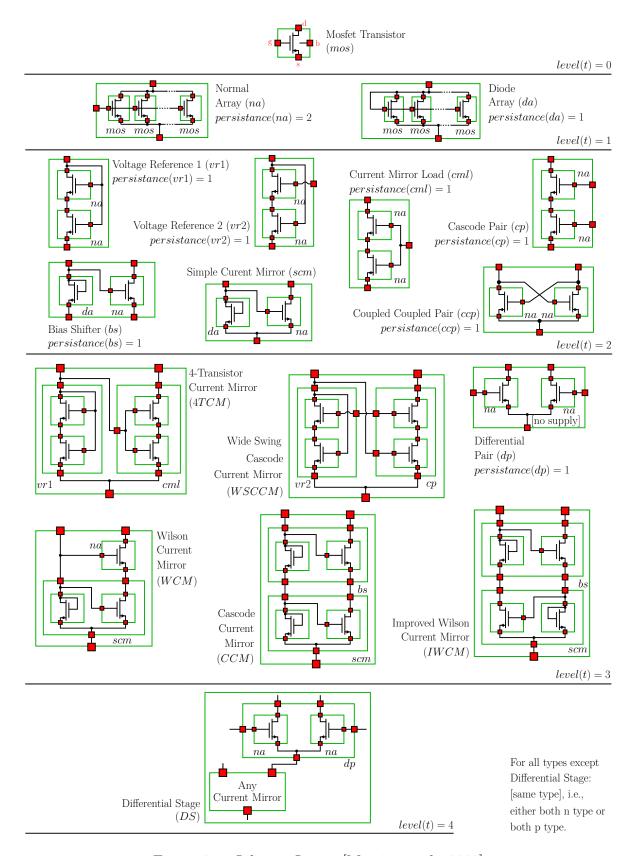

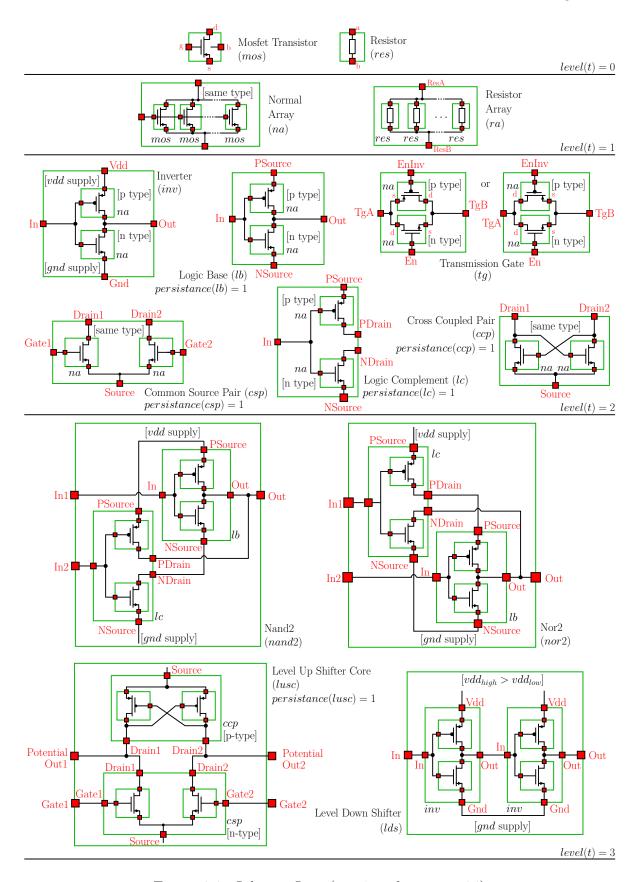

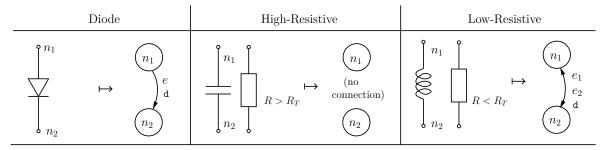

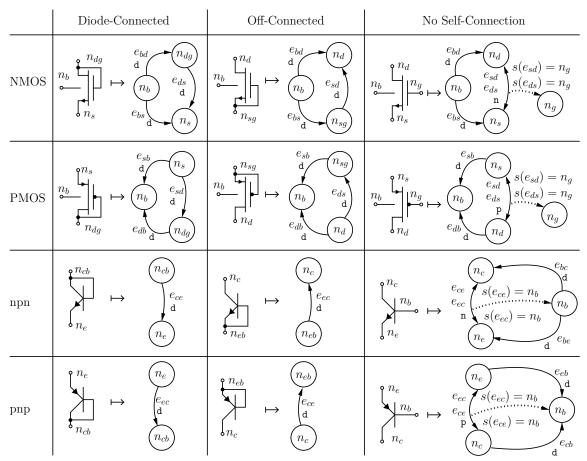

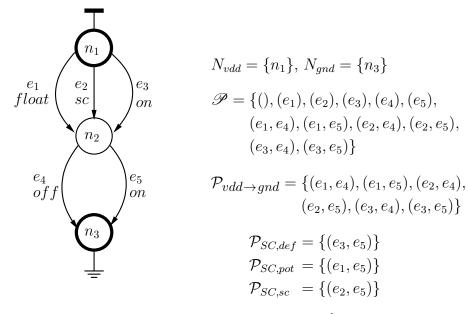

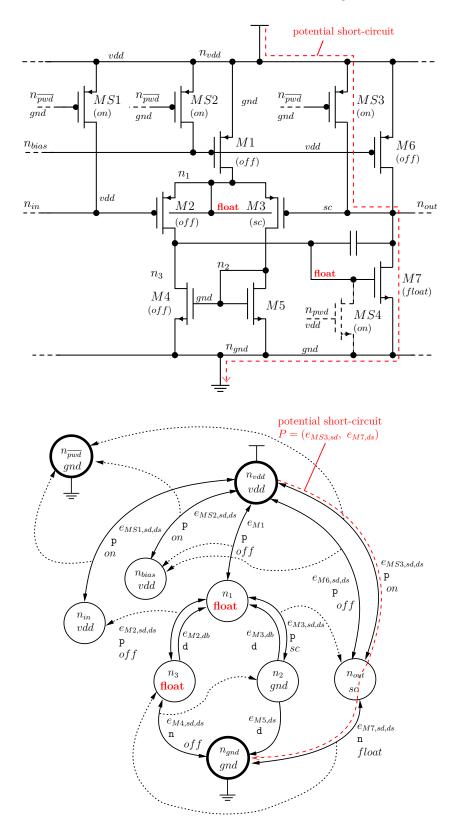

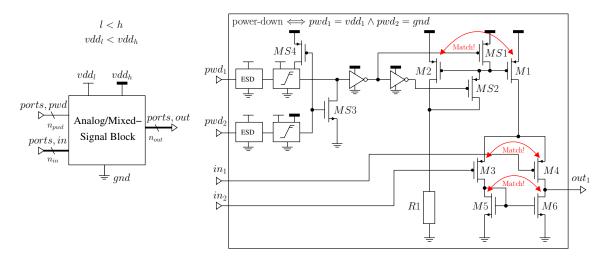

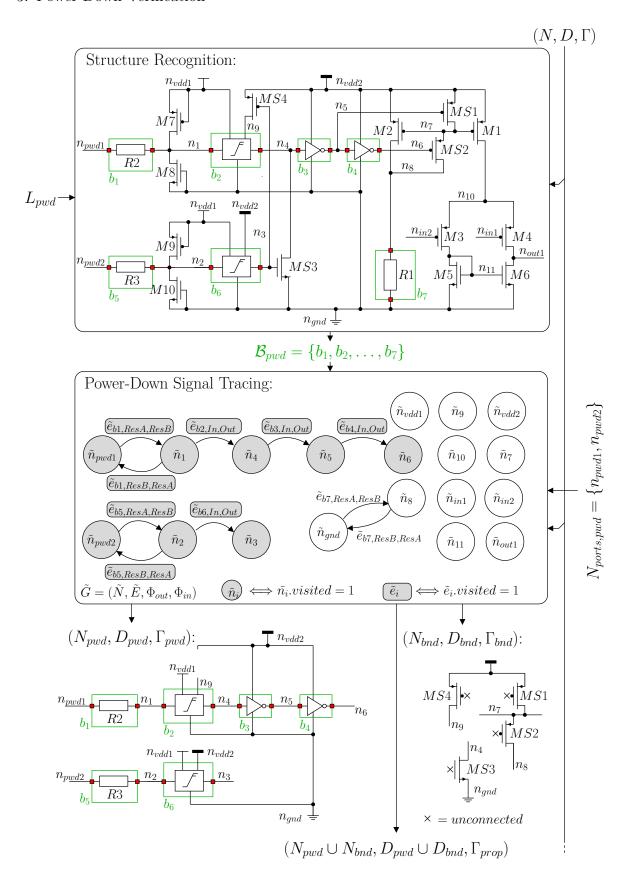

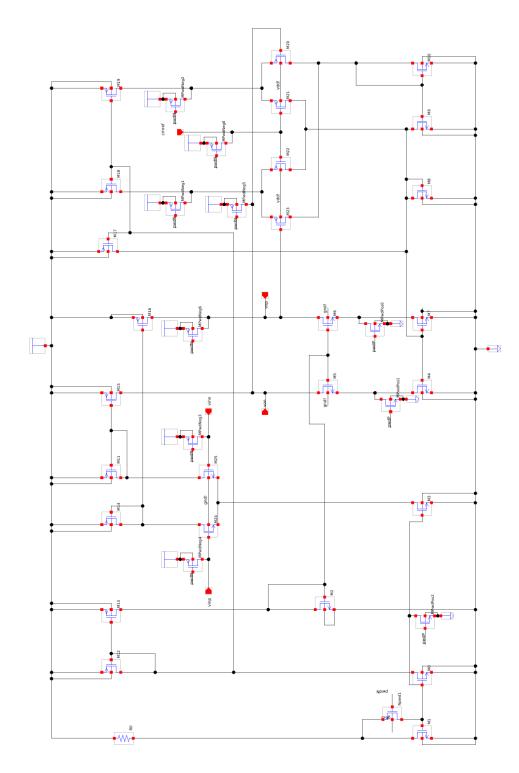

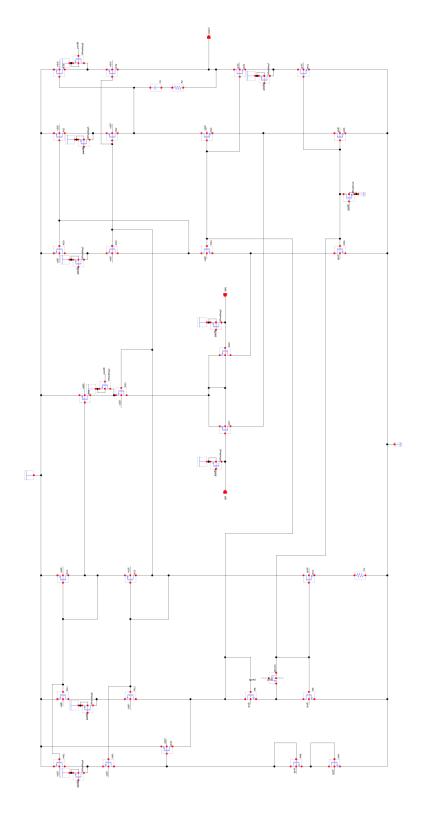

given in Figs. 2.1, 2.2 and 2.3. Fig. 2.1 shows the library  $L_{analog}$  to detect typical analog building blocks, i.e., different types of current mirrors and differential pairs. The library is based on the library presented for the sizing rules method [Massier et al., 2008]. An additional library  $L_{pwd}$  was developed for the detection of asymmetric voltages in power-down mode (section 3.3). It is illustrated in Figs. 2.2 and 2.3 and can be used to detect typical building blocks that can be found on the power-down signal path in an analog circuit. The libraries are organized in levels. Each building block only consists of building blocks from lower levels.

Algorithm 1 requires the circuit netlist with devices D, the supply rail information and a library L as input. The library L is either  $L_{analog}$  or  $L_{pwd}$ . The supply rail information is described later in this section. Building blocks are added to a set of building blocks  $\mathcal{B}$  during the recognition process. The algorithm starts with building blocks on the lowest level, i.e. on level l = 0. The building blocks in level 0 are given by the devices of the circuit D, i.e., they are resistors and transistors (line 2).

The algorithm continues with the detection of the array building blocks on level l=1. (see lines 4 to 9). Array building blocks are building blocks which are formed by n children of the same type. For both,  $L_{analog}$  and  $L_{pwd}$ , level l=1 consists of array building blocks only. For each array type  $t_{array}$  on level 1, i.e. for normal arrays (na) and diode arrays (da) in case of  $L_{analog}$  and for normal arrays (na) and resistor arrays (ra) in case of  $L_{pwd}$ , matching structures in the circuit are detected by the function FindArrays $(t_{array}, \mathcal{B})$  (see line 7). The details of the efficient rule checking procedure that is performed FindArrays $(t_{array}, \mathcal{B})$  are described in [Eick, 2013]. The function returns the recognized arrays. They are first added to the set of recognized building blocks on level 1, i.e. to  $\mathcal{B}_1$ , and then accumulated in  $\mathcal{B}$ .

On the levels l=2 and above, the libraries  $L_{analog}$  and  $L_{pwd}$  contain only pair building blocks. Pair building blocks are building blocks that consist of exactly two children. The pair building blocks of type  $t_{pair}$  are recognized for level 2 and above (lines 11 to 22). The algorithm is iterating from level 2 up to the highest level in the library. On each level, for each type  $t_{pair}$  on that level (as given in Figs. 2.1, 2.2 and 2.3), the matching structures in the circuit are detected by a function FindPairs( $t_{pair}$ ,  $\mathcal{B}$ ) (line 15). The details for the efficient rule checking that is performed in FindPairs( $t_{pair}$ ,  $\mathcal{B}$ ) are described in [Eick, 2013]. The function FindPairs( $t_{pair}$ ,  $\mathcal{B}$ ) returns the matching pair building blocks. They are first added to the set for the current level  $\mathcal{B}_l$  and then accumulated in  $\mathcal{B}$ .

So far, we have seen that the algorithm distinguishes between device, array and pair building blocks. Device building blocks do not have children as they are on the lowest hierarchy level. All building blocks on the hierarchy levels 1 and above, have only children of lower levels than their own. The arrays on level 1 have children that are devices from level 0. The pairs on level 2 and above have children from any level below, i.e. devices, arrays or pairs.

# 2. Structure Recognition

Figure 2.1.: Library  $L_{analog}$  [Massier et al., 2008]

# 2.2. Enhanced State-of-the-Art Algorithm

Figure 2.2.: Library  $L_{pwd}$  (continued on page 24)

# 2. Structure Recognition

Figure 2.3.: Library  $L_{pwd}$  (continued from page 23)

In Figs. 2.1, 2.2 and 2.3, recognition rules to be checked by the functions FindArrays( $t_{array}$ ,  $\mathcal{B}$ ) and FindPairs( $t_{pair}$ ,  $\mathcal{B}$ ) are given graphically. The borders of building blocks are drawn as green boxes. The pins of building blocks are drawn as red squares and are labeled in red.

The rules for the types of the child building blocks can be derived from the annotations next to the green boxes. Furthermore, connection rules can be derived from the wires that connect the pins. In addition to the type and connection rules, further rules for techtype (n-type or p-type) and for supplies can be specified. These rules are annotated in square brackets. Child building blocks can be required to be of n-type, i.e., n-MOS or npn transistors, or of p-type, i.e., p-MOS or pnp transistors. The rules [n-type] and [p-type] require a child to be of the corresponding type. The rule [same type] requires all children to be of either n- or p type. The techtype is propagated up the building block hierarchy as follows: A building block is techtype n or p, if all children are of type n or p, respectively. If the children are of mixed techtype, the building block's techtype is undefined. An undefined techtype can not fulfill any [n-type], [p-type] or [same type] rule.

The structure recognition takes supply net information as input. Additional supply net rules are specified in the library using this information. This is an enhancement over the original algorithms published in [Massier et al., 2008; Massier, 2010] and [Eick, 2013]. The supply net rules are used in  $L_{pwd}$  to detect basic logic gates and level shifters. Furthermore, experimental results show that the [no supply] rule for the source of differential pairs in  $L_{analog}$  drastically reduces the number of candidate pairs for differential pairs. The addition of this rule leads to a drastic speed-up for larger circuits.

The supply net information that is taken as input has the following format: Each circuit net that acts as a ground net is tagged with gnd. Each circuit net that corresponds to a supply rail is tagged with  $vdd_n$ , where  $n=1,2,\ldots,n_{supplies}$  and  $n_{supplies}$  is the number of different supply rails in the circuit. The supply rails as well as the voltage tags can be sorted according to their magnitude, e.g. a 5 V rail should get a tag with a higher index than a 3 V rail. Typically in this case, the 5 V rail would be assigned the tag  $vdd_2$  and the 3 V rail the tag  $vdd_1$ . In this way, the qualitative ordering of the supply voltages is made available as additional information to structure recognition while the quantitative nominal voltage values are abstracted. The following rules using the supply net information are used in  $L_{analog}$  and  $L_{pwd}$ :

- The rule [vdd supply] is fulfilled, if a net has a  $vdd_n$  tag.

- The rule [gnd supply] is fulfilled, if a net has a gnd tag.

- The rule  $[vdd_{high} > vdd_{low}]$  with high > low is fulfilled if the left net has a tag with higher index than the right net.

To sum up, a library L contains type rules, connection rules, tech-type rules and supply rules. The rules are illustrated by Figs 2.1, 2.2 and 2.3. More detailed definitions of the rules are published in [Eick, 2013].

# 2. Structure Recognition

In the following, definitions are made that are used to describe the structure recognition algorithm. A library is a set of types with corresponding recognition rules:

$$L = \{t_1, t_2, \dots, t_n\} \tag{2.1}$$

A library can be partitioned into subsets  $L_l$  for each hierarchy level l as follows:

$$L = \bigcup_{l=0,1,\dots,\max\text{Level}(L)} L_l \tag{2.2}$$

The function  $\max \text{Level}(L)$  returns the highest level in the library. For the two libraries discussed in this section, the highest levels are given as follows:

$$\max \text{Level}(L_{analog}) = 4 \quad \text{and} \quad \max \text{Level}(L_{pwd}) = 5$$

(2.3)

According to Fig. 2.1, the subsets  $L_{analog,l}$  for the analog library  $L_{analog}$  are given as follows:

$$\begin{split} L_{analog,0} &= \{mos\} \\ L_{analog,1} &= \{na, da\} \\ L_{analog,2} &= \{vr1, vr2, cml, cp, bs, scm, ccp\} \\ L_{analog,3} &= \{dp, 4TCM, WSCCM, WCM, CCM, IWCM\} \\ L_{analog,4} &= \{DS\} \end{split}$$

Similarly and according to Figs. 2.2 and 2.3, the subsets  $L_{pwd,l}$  for the power-down signal library  $L_{pwd}$  can be written down as given below:

$$\begin{split} L_{pwd,0} &= \{mos, res\} \\ L_{pwd,1} &= \{na, ra\} \\ L_{pwd,2} &= \{inv, tg, csp, lb, lc, ccp\} \\ L_{pwd,3} &= \{nor2, nand2, lusc, lds\} \\ L_{pwd,4} &= \{lusb\} \\ L_{mvd,5} &= \{LUS, InvLUS\} \end{split}$$

A level function can be defined which assigns a level to each type using the partitioning given above. It is defined as follows:

$$level: L \to \{0, 1, \dots, maxLevel(L)\}: t \mapsto level(t)$$

(2.4)

The level function is used in the following to describe the function SelfArbitration (Algorithm 2).

## Algorithm 2 SelfArbitration

```

Require: \mathcal{B}, l

1: repeat

2:

removed := 0

for all b in \mathcal{B} do

3:

if not hasParent(b) and l > level(type(b)) + persistence(type(b)) then

4:

\mathcal{B} := \mathcal{B} \setminus \{b\} // changes hasParent() of other building blocks

5:

removed := 1

6:

end if

7:

end for

8:

9: until removed = 0

10: return \mathcal{B}

```

# **Algorithm 3** CrossCoupledPairArbitration

```

Require: \mathcal{B}

1: for all b in \mathcal{B} do

2: if "a child of b is also child of a cross coupled pair (cc)" then

3: \mathcal{B} := \mathcal{B} \setminus \{b\}

4: end if

5: end for

6: return \mathcal{B}

```

Each recognized building block  $b \in \mathcal{B}$  is of one of the types given above. Therefore, a function can be defined that maps the building block to its type. It is defined as follows:

$$type: \mathcal{B} \to L: b \mapsto type(b)$$

(2.5)

The function is used in this thesis to refer to the type of a building block.

Ambiguities between building blocks can occur during the recognition process. Ambiguity means that a building blocks can be part of different building bocks without any rule violation. Those ambiguities need to be resolved, i.e., the correct type among all types with matching rules needs to be chosen and the wrong building blocks need to be removed from  $\mathcal{B}$ . The sizing rules method uses a predefined dominance relation in order to resolve ambiguities in the circuit [Massier et al., 2008; Massier, 2010]. Furthermore, rules for so called uncertain structures are used. These are structures that are frequently subject to ambiguities. Typically, uncertain structures are building blocks where the children have a low number of connected pins, e.g., the differential pair (dp) and the cascode pair (cp) of the library  $L_{analog}$ . For dp and cp, the children are only connected via one pin pair. In [Massier, 2010], uncertain building blocks are marked for manual review by the circuit designer for a final decision. In [Eick, 2013], uncertain building blocks are removed after the main loop if they are not part of another building

#### 2. Structure Recognition

block. In order to simplify the rules for ambiguity arbitration and to decrease the likelihood of false recognitions, ambiguity arbitration has been enhanced compared to the sizing rules method. The new ambiguity arbitration scheme is described by the function SelfArbitration (Algorithm 2). Additionally, the function CrossCoupledPairArbitration (Algorithm 3) implements a minimalistic dominance relation: The cross coupled pair (ccp) dominates all other building blocks. Both functions together define the arbitration scheme.

Self arbitration generalizes the principle of the removal of uncertain building blocks by introducing a persistence value for uncertain building blocks. The persistence values are annotated in Figs 2.1, 2.2 and 2.3. The function

$$persistence: L \to \{1, 2, \dots maxLevel(L)\} \qquad t \mapsto persistence(t)$$

(2.6)

assigns a persistence value to each type of the library. The default value is the highest level number. Only for types where the persistence value is lower, it is annotated in Figs 2.1, 2.2 and 2.3.

The persistence value controls the lifetime of a building block in  $\mathcal{B}$  while iterating up the hierarchy levels l. The function SelfArbitration (Algorithm 2) is called (line 20) in each iteration of the main loop in Algorithm 1. It filters out all building blocks  $b \in \mathcal{B}$  which were recognized more than persistence(type(b)) iterations ago and do not have a parent yet, i.e., have not become part of another building block yet. In this case, it is very likely that the building block is a false recognition. The persistence values in the libraries  $L_{analog}$  and  $L_{pwd}$  have been carefully chosen in order to resolve ambiguities. Experimental results show that a sophisticated predefined dominance relation as used in [Massier et al., 2008; Massier, 2010] is not required when the approach described in this section is used.

A hierarchy of building blocks is built up during the structure recognition process as described by Algorithm 1. The hierarchy can be described by child/parent relationships between the recognized building blocks. A building block  $b_{child}$  that is part of another parent building block  $b_{parent}$  is said to be a child of  $b_{parent}$ . Based on the child/parent relationships of the building blocks, the following logic predicate can be defined:

hasParent(b) = 1

$$\iff$$

"b is part of another building block  $b_{parent}$ " (2.7)

The function is used in function SelfArbitration (Algorithm 2).

The algorithm of this section is used for detecting asymmetric voltages in power-down mode (section 3.3) and for power-down synthesis (chapter 4). For the detection of asymmetric voltages in power-down mode, the library  $L_{pwd}$  is used to split the power-down signal path away from the rest of the circuit such that it can be analyzed for analog matched pairs with  $L_{analog}$ . For power-down synthesis, current mirrors are detected using  $L_{analog}$ .

# 2.3. New Power-Down Signal Path Library

As the library  $L_{pwd}$  (see Figs 2.2 and 2.3) was newly developed, a more detailed explanation of the library is given in this section. The goal of  $L_{pwd}$  is to provide a library to detect building blocks forming the power-down signal path as required by the method in section 3.3. A set of basic building blocks that covers all elements on the power-down signal path of the industrial circuits examined in section 3.3.7 has been identified. It can be listed as follows:

- Digital inverter circuits

- Nor/Nand gates with two inputs

- Transmission gates

- Signal level shifters for shifting the digital signal levels up or down (example see Fig. 3.11)

- ESD-protection as shown in Fig. 3.11

In general, the structure recognition method has to be replaced or completed by available other methods (e.g. [Lescot et al., 2012; Meyer zu Bexten et al., 2015; Pelz and Roettcher, 1994; Rubanov, 2006; Ohlrich et al., 1993; Ebeling, 1988; Eick, 2013]) if this set of structures is not sufficient for the given application.

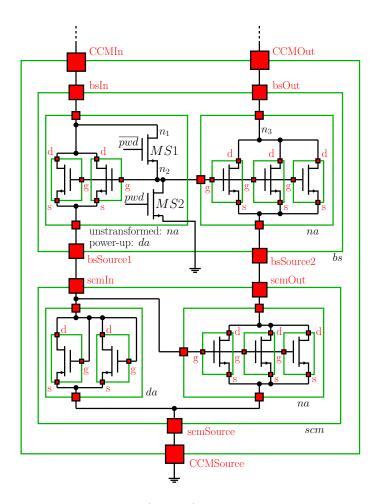

The library  $L_{pwd}$  recognizes the building blocks mentioned above. The recognized building blocks are input for a power-down signal tracing method. The method will be described later in section 3.3.3. Based on the detected building blocks, a signal tracing graph is built. Fig. 3.13 shows the types from  $L_{pwd}$  that are input of the signal-tracing method method. In the following, those types are called top level power-down signal blocks. They can be be listed as follows:

- 1. Resistor Array (ra)

- 2. Transmission Gate (tq)

- 3. Inverter (inv)

- 4. Nand2 (nand2) and Nor2 (nor2)

- 5. Level Down Shifter (lds)

- 6. Level Up Shifter (LUS) and Inverting Level Up Shifter (InvLUS)

The top level power-down signal blocks can also be found in  $L_{pwd}$  (see Figs 2.2 and 2.3). All other building blocks in  $L_{pwd}$  are required to recognize the top level power-down signal blocks. The relationships between the types in  $L_{pwd}$  are described in the following. The description is going through the list above from top to down.

- 1. The resistor array (ra) is formed by resistors (res).

- 2. The transmission gate (tg) is a pair two normal arrays (na), one of tech-type p and the other of techtype n. Two variants exist: "source and source connected" and "source and drain connected".

#### 2. Structure Recognition

- 3. The inverter (inv) is a pair of two normal arrays (na), one of tech-type p and the other of techtype n. It is equivalent to the logic base (lb) except the [gnd supply] and [vdd supply] rules.