Lehrstuhl für Integrierte Systeme

# Image Processing on Heterogeneous Multiprocessor System-on-Chip using Resource-aware Programming

### Johny Paul

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktor-Ingenieurs (Dr.-Ing.)

genehmigten Dissertation.

Vorsitzende(r): Prof. Dr.-Ing. Ulf Schlichtmann

Prüfer der Dissertation:

1. apl. Prof. Dr.-Ing. Walter Stechele

2. Prof. Dr.-Ing. Tamim Asfour

Die Dissertation wurde am 28.02.2017 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 29.06.2017 angenommen.

To my family.

### Abstract

**Multiprocessor system-on-chip** (MPSoC) designs offer a lot of computational power assembled in a compact design. The computing power of MPSoCs can be further augmented by adding massively parallel processor arrays (MPPA) and specialized hardware with instruction-set extensions. On-chip MPPAs can be used to accelerate low-level image-processing algorithms with massive inherent parallelism. With the arrival of new **heterogeneous MPSoCs**, various applications that run on dedicated compute units on humanoid robots like **ARMAR**, can now be combined and executed on a single-chip.

However, the presence of multiple processing elements (PE) with different characteristics raises issues related to programming and application mapping. The conventional approach used for programming heterogeneous MPSoCs results in a static mapping of various parts of the application to different PE types, based on the nature of the algorithm and the structure of the PEs. Yet, such a mapping scheme independent of the instantaneous load on the PEs may lead to under-utilization of some type of PEs while overloading others. At the same time it is difficult to dynamically control and distribute different types of resources among different applications running on a single chip, achieving high resource utilization under high-performance constraints.

This thesis focus on investigating the benefits and challenges of using a resource-aware programming model called *Invasive Computing* for dynamically mapping image-processing applications (used on humanoid robots) to different types of PEs available on a heterogeneous MPSoC named *InvasIC*. Different types of computer vision algorithms were investigated and implemented on the heterogeneous MpSoC. Based on the new model, the applications can dynamically acquire and release hardware resources, considering the level of parallelism available in the algorithm and time-varying load. Our results indicate that resource-aware programming helps to improve the **performance** (throughput and worst observed latency) of various computer vision applications along with better overall **workload distribution** within the heterogeneous MPSoC.

### Acknowledgment

I would like to express my gratitude to everyone, who have supported me in successfully realizing this thesis. First of all, I want to express my deep gratitude towards my advisor, Prof. Dr.-Ing. Walter Stechele for his exceptional support throughout my work at LIS, particularly for the freedom offered to me during my research and also for the constant feedback that I received. I am also grateful to Prof. Dr.-Ing. Tamim Asfour (our partner from the Karlsruhe Institute of Technology) for the feedback and suggestions I received during the past 5 years. Furthermore, I would like to thank Prof. Dr. sc.techn. Andreas Herkersdorf and Dr.-Ing. Thomas Wild for their guidance, support and suggestions during my work in the project Invasive Computing.

Finally I want to thank all my colleagues, especially my fellow doctoral candidates Aurang Zaib, David May and Ravi Kumar Pujari for the cooperation and fruitful discussion we had over the past several years. Additionally I would like to thank my colleagues outside LIS, especially from Karlsruhe Institute of Technology and University of Erlangen-Nuremberg, for providing necessary support at various levels including hardware and operating system layers. I would also like to thank the students who have contributed to my work with their Diplom- and master-thesis at LIS. Last but not the least, my gratitude goes towards my family, for their support during my stay and work in Germany.

> Munich, November 2015 Johny Paul

### Contents

| Ind | dexes | S                                              | xi |

|-----|-------|------------------------------------------------|----|

| 1.  | Intro | oduction                                       | 1  |

|     | 1.1.  | Outline of the Thesis                          | 2  |

|     | 1.2.  | Image Processing on Humanoid Robots            | 3  |

|     | 1.3.  | Multiprocessor System-on-Chip (MPSoC) Designs  | 5  |

|     | 1.4.  | Benefits of using MPSoCs on Robots             | 5  |

|     | 1.5.  | Potential Challenges in using MPSoCs on Robots | 7  |

|     | 1.6.  | Resource-aware Programming                     | 8  |

| 2.  | Rela  | ated Work                                      | 11 |

|     | 2.1.  | Various MPSoC Platforms                        | 11 |

|     | 2.2.  | Programming Models for MPSoCs                  | 16 |

|     |       |                                                |    |

| 3.  |       | sive Computing                                 | 19 |

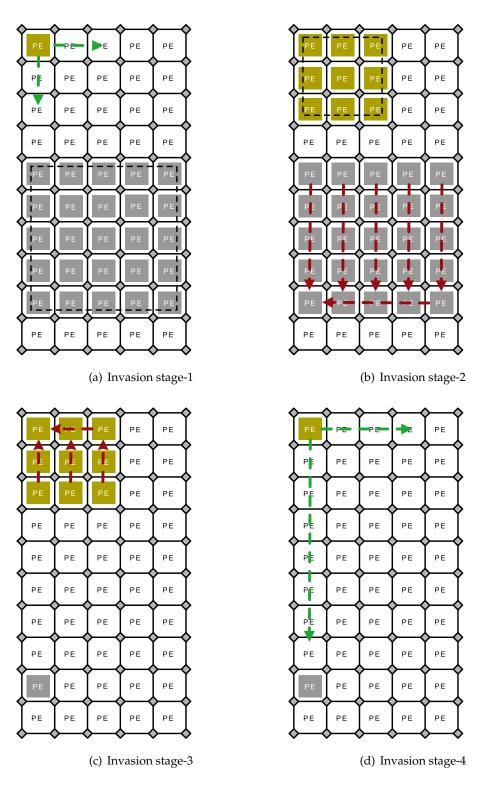

|     |       | Basic Principles                               | 19 |

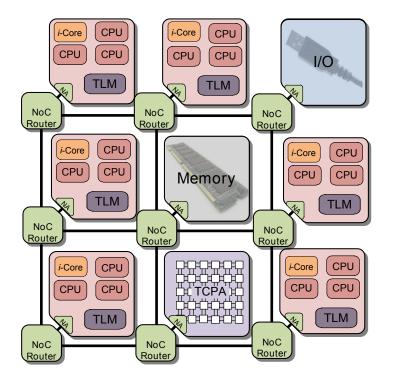

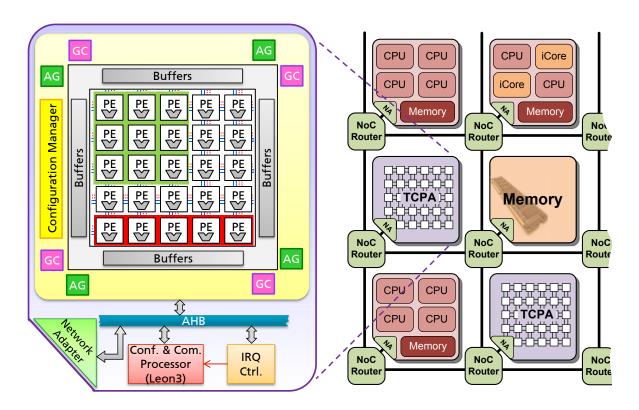

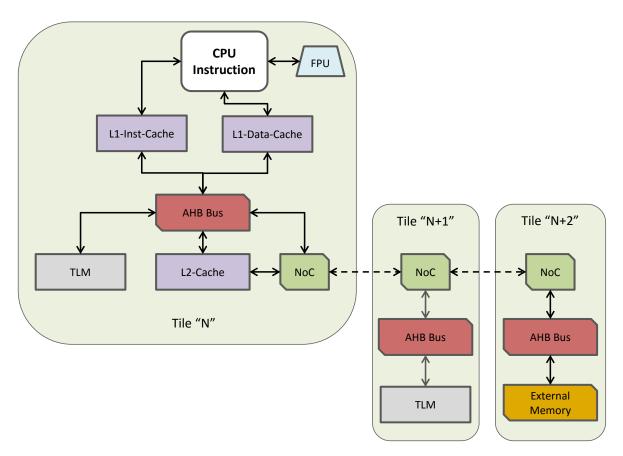

|     | 3.2.  | InvasIC - Hardware Architecture                | 21 |

|     |       | 3.2.1. InvasIC - Memory Hierarchy              | 21 |

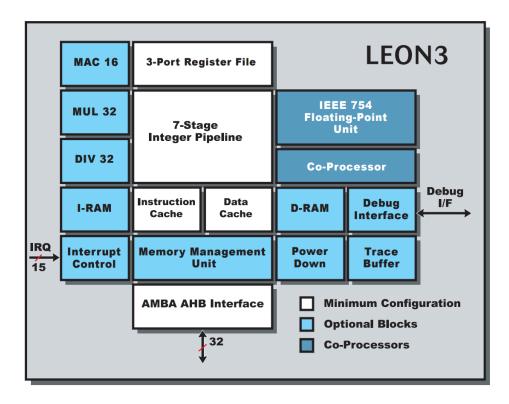

|     |       | 3.2.2. RISC Processors (LEON3)                 | 22 |

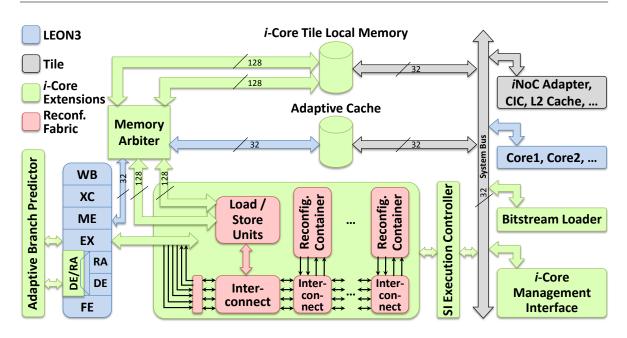

|     |       | 3.2.3. Invasive Cores ( <i>i</i> -Core)        | 23 |

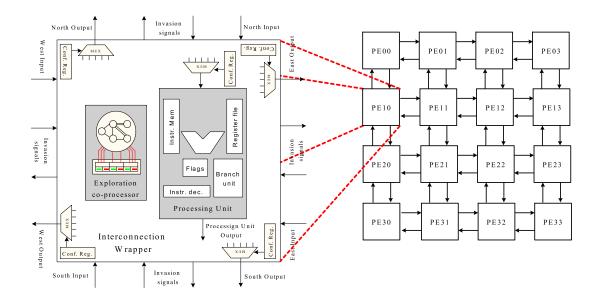

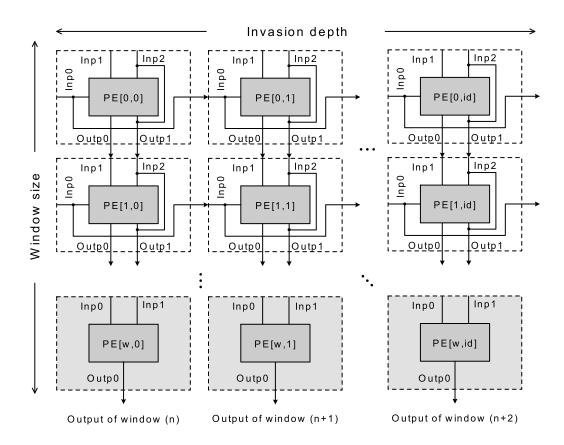

|     |       | 3.2.4. Tightly Coupled Processor Array (TCPA)  | 25 |

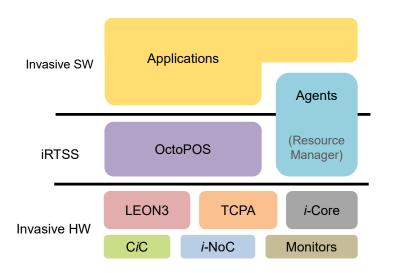

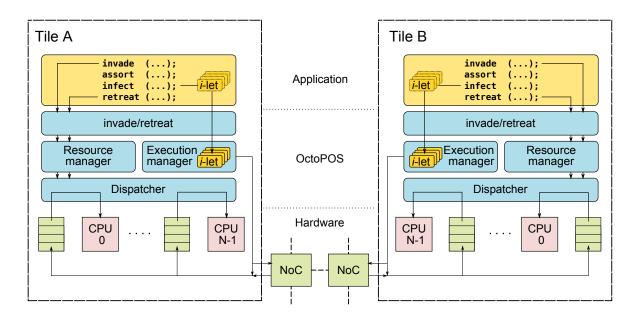

|     | 3.3.  | OctoPOS - A Resource-aware Operating System    | 29 |

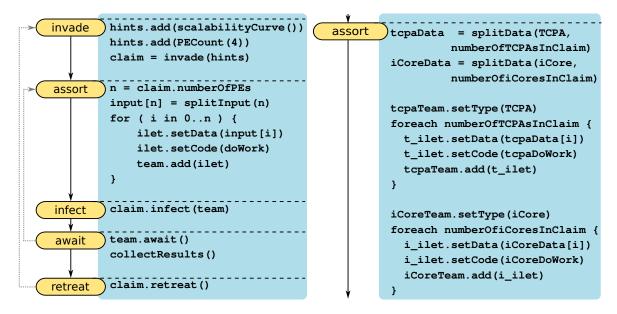

|     |       | 3.3.1. The Invasive Programming Model          | 31 |

|     |       | 3.3.2. OctoPOS - Design Principles             | 32 |

|     |       | 3.3.3. OctoPOS - Architectural Overview        | 33 |

| 4.  | Con   | nputer Vision Algorithms for Humanoid Robots   | 35 |

|     |       | Object Recognition                             | 35 |

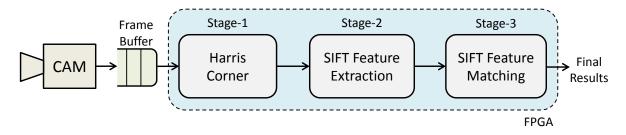

|     |       | 4.1.1. Harris Corner Detection                 | 37 |

|     |       | 4.1.2. SIFT Feature Extraction                 | 39 |

|     |       | 4.1.3. SIFT Feature Matching                   | 40 |

|     | 4.2.  | Optical Flow                                   | 43 |

|     |       |                                                |    |

| 5.1.3. Resource Allocation and Workload Distribution       52         5.1.4. Results       56         5.2. Resource-Aware KD-Tree Search       60         5.2.1. Conventional Approach for Accelerating NN-Search on KD-Trees       60         5.2.2. Challenges with conventional kd-tree search on shared MPSoC       61         5.2.3. Nearest-Neighbor Search on KD-Trees       63         5.2.4. Resource-Aware Nearest-Neighbor Search Algorithm       67         5.2.5. Evaluation & Results       71         5.2.6. Conclusion       74         6. Accelerating Image Processing using Specialized Hardware       75         6.1. InvasIC - Programmer's View       75         6.2. Harris Corner Detection on Tightly Coupled Processor Array       77         6.2.1. Conventional Approach       77         6.2.2. Results       78         6.3.3. Results       82         6.3.3. Results       82         6.3.3. Results       82         6.3.4. Algorithm       82         6.3.3. Results       87         6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4.1. MPPAs for Optical Flow Computation       91         6.4.2. Various Stages in Optical Flow Algorithm       92         6.4.3. Optical Flow in Invasive Notation <td< th=""><th>5.</th><th>Res</th><th>ource-Aware Algorithms</th><th>45</th></td<>                                                                   | 5. | Res  | ource-Aware Algorithms                                       | 45  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|--------------------------------------------------------------|-----|

| 5.1.2.       Extension to a Resource-Aware Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 5.1. | Resource-Aware Corner Detectors                              | 48  |

| 5.1.2.       Extension to a Resource-Aware Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |      | 5.1.1. Conventional Approach Towards Faster Corner Detection | 49  |

| 5.1.4. Results       56         5.2. Resource-Aware KD-Tree Search       60         5.2.1. Conventional Approach for Accelerating NN-Search on KD-Trees       60         5.2.2. Challenges with conventional kd-tree search on shared MPSoC       61         5.2.3. Nearest-Neighbor Search on KD-Trees       63         5.2.4. Resource-Aware Nearest-Neighbor Search Algorithm       67         5.2.5. Evaluation & Results       71         5.2.6. Conclusion       74         6. Accelerating Image Processing using Specialized Hardware       75         6.1. InvasIC - Programmer's View       75         6.2. Harris Corner Detection on Tightly Coupled Processor Array       77         6.2.1. Conventional Approach       77         6.2.2. Implementation on InvasIC       78         6.3.3. Results       82         6.3.3. Results       82         6.3.3. Results       82         6.3.3. Results       87         6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4.1. MPPAs for Optical Flow Computation       91         6.4.2. Various Stages in Optical Flow Algorithm       92         6.4.3. Optical Flow in Invasive Notation       97         6.4.4. Implementation       99         6.4.5. Results       104     <                                                                                                                                                     |    |      | 5.1.2. Extension to a Resource-Aware Model                   | 49  |

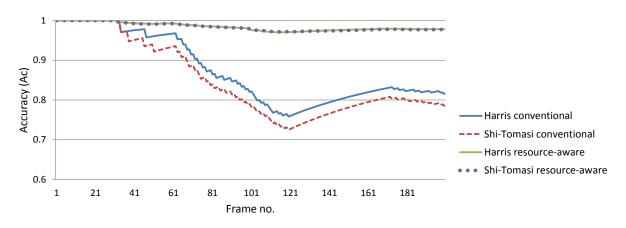

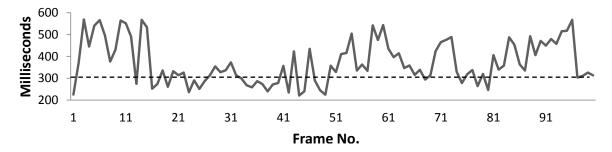

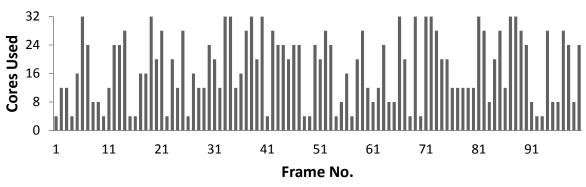

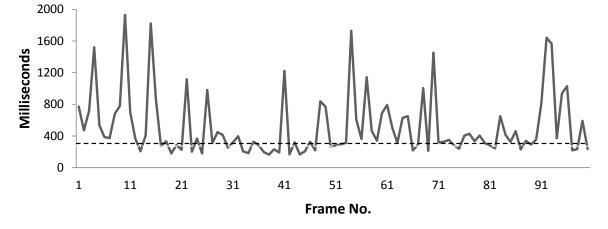

| 5.2. Resource-Aware KD-Tree Search       60         5.2.1. Conventional Approach for Accelerating NN-Search on KD-Trees       60         5.2.2. Challenges with conventional kd-tree search on shared MPSoC       61         5.2.3. Nearest-Neighbor Search on KD-Trees       63         5.2.4. Resource-Aware Nearest-Neighbor Search Algorithm       67         5.2.5. Evaluation & Results       71         5.2.6. Conclusion       74         6. Accelerating Image Processing using Specialized Hardware       75         6.1. InvasIC - Programmer's View       75         6.2. Harris Corner Detection on Tightly Coupled Processor Array       77         6.2.1. Conventional Approach       77         6.2.2. Implementation on InvasIC       78         6.2.3. Results       82         6.3. SIFT Feature Matching on <i>i</i> -Core       83         6.3.2. Accelerated Implementation on <i>i</i> -Gore       83         6.3.3. Results       87         6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4.1. MPPAs for Optical Flow Algorithm       92         6.4.2. Various Stages in Optical Flow Algorithm       92         6.4.3. Optical Flow in Invasive Notation       97         6.4.4.1 Implementation       99         6.4.5. Results       104                                                                                                                         |    |      | 5.1.3. Resource Allocation and Workload Distribution         | 52  |

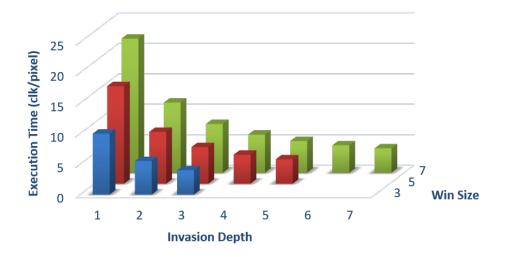

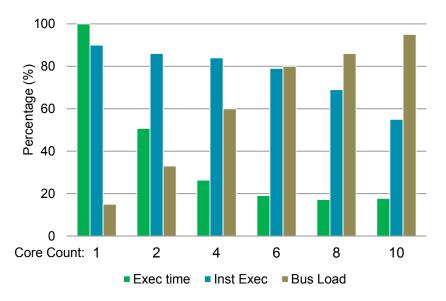

| 52.1. Conventional Approach for Accelerating NN-Search on KD-Trees       60         52.2. Challenges with conventional kd-tree search on shared MPSoC       61         52.3. Nearest-Neighbor Search on KD-Trees       63         52.4. Resource-Aware Nearest-Neighbor Search Algorithm       67         52.5. Evaluation & Results       71         52.6. Conclusion       74         6. Accelerating Image Processing using Specialized Hardware       75         6.1. InvasIC - Programmer's View       75         6.2. Harris Corner Detection on Tightly Coupled Processor Array       77         6.2. Implementation on InvasIC       78         6.3. SIFIT Feature Matching on <i>i</i> -Core       82         6.3. Accelerated Implementation on <i>i</i> -Core       83         6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4. Optical Flow in Invasive Notation       97         6.4. Optical Flow in Invasive Notation       97         6.4. Implementation       97         6.4. Implementation       97         6.4. Implementation       97 <th></th> <th></th> <th>5.1.4. Results</th> <th>56</th>                    |    |      | 5.1.4. Results                                               | 56  |

| 52.1. Conventional Approach for Accelerating NN-Search on KD-Trees       60         52.2. Challenges with conventional kd-tree search on shared MPSoC       61         52.3. Nearest-Neighbor Search on KD-Trees       63         52.4. Resource-Aware Nearest-Neighbor Search Algorithm       67         52.5. Evaluation & Results       71         52.6. Conclusion       74         6. Accelerating Image Processing using Specialized Hardware       75         6.1. InvasIC - Programmer's View       75         6.2. Harris Corner Detection on Tightly Coupled Processor Array       77         6.2. Implementation on InvasIC       78         6.3. SIFIT Feature Matching on <i>i</i> -Core       82         6.3. Accelerated Implementation on <i>i</i> -Core       83         6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4. Optical Flow in Invasive Notation       97         6.4. Optical Flow in Invasive Notation       97         6.4. Implementation       97         6.4. Implementation       97         6.4. Implementation       97 <th></th> <th>5.2.</th> <th>Resource-Aware KD-Tree Search</th> <th>60</th> |    | 5.2. | Resource-Aware KD-Tree Search                                | 60  |

| 5.2.2.       Challenges with conventional kd-tree search on shared MPSoC       61         5.2.3.       Nearest-Neighbor Search on KD-Trees       63         5.2.4.       Resource-Aware Nearest-Neighbor Search Algorithm       67         5.2.5.       Evaluation & Results       71         5.2.6.       Conclusion       74         6. Accelerating Image Processing using Specialized Hardware       75         6.1.       InvasiC - Programmer's View       75         6.2.       Harris Corner Detection on Tightly Coupled Processor Array       77         6.2.1.       Conventional Approach       77         6.2.2.       Implementation on InvasiC       78         6.3.3.       Results       82         6.3.3.       FJ Feature Matching on <i>i</i> -Core       82         6.3.1.       Algorithm       82         6.3.2.       Accelerated Implementation on <i>i</i> -Core       83         6.4.       Optical Flow Computation       91         6.4.1.       MPPAs for Optical Flow Computation       91         6.4.2.       Various Stages in Optical Flow Algorithm       92         6.4.3.       Optical Flow in Invasive Notation       97         6.4.4.       Implementation       99         6.4.5.       Resu                                                                                                                                                                                             |    |      |                                                              | 60  |

| 5.2.3. Nearest-Neighbor Search on KD-Trees       63         5.2.4. Resource-Aware Nearest-Neighbor Search Algorithm       67         5.2.5. Evaluation & Results       71         5.2.6. Conclusion       74         6. Accelerating Image Processing using Specialized Hardware       75         6.1. InvasIC - Programmer's View       75         6.2. Harris Corner Detection on Tightly Coupled Processor Array       77         6.2.1. Conventional Approach       77         6.2.2. Implementation on InvasIC       78         6.3.3. Results       82         6.3.3. Results       82         6.3.1. Algorithm       82         6.3.2. Accelerated Implementation on i-Core       83         6.3.3. Results       87         6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4.1. MPPAs for Optical Flow Computation       91         6.4.2. Various Stages in Optical Flow Algorithm       92         6.4.3. Optical Flow in Invasive Notation       97         6.4.4. Implementation       99         6.4.5. Results       104         6.5. Conclusion       109         7.4.1. Hardware Prototype       112         7.2.2. Multiple Applications on Heterogeneous Implementation       114         7.2.2. Mu                                                                                                                                                                          |    |      |                                                              | 61  |

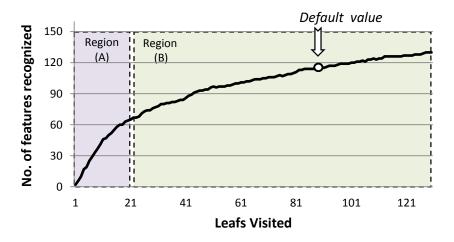

| 5.2.4. Resource-Aware Nearest-Neighbor Search Algorithm       67         5.2.5. Evaluation & Results       71         5.2.6. Conclusion       74         6. Accelerating Image Processing using Specialized Hardware       75         6.1. InvasIC - Programmer's View       75         6.2. Harris Corner Detection on Tightly Coupled Processor Array       77         6.2.1. Conventional Approach       77         6.2.2. Implementation on InvasIC       78         6.3.3. Results       82         6.3.3. Results       82         6.3.1. Algorithm       82         6.3.2. Accelerated Implementation on <i>i</i> -Core       83         6.3.3. Results       87         6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4.1. MPPAs for Optical Flow Computation       91         6.4.2. Various Stages in Optical Flow Algorithm       92         6.4.3. Optical Flow in Invasive Notation       97         6.4.4. Implementation       99         6.4.5. Results       104         6.5. Conclusion       109         7. Object Recognition on Heterogeneous MPSoC       111         7.1. Hardware Prototype       112         7.2.2. Multiple Applications on Heterogeneous MPSoC       115         7.3. Conclusion                                                                                                                                                                    |    |      | 0                                                            | 63  |

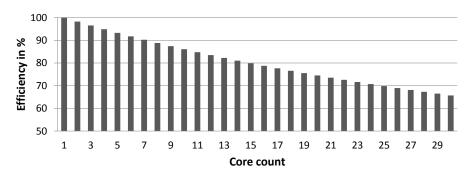

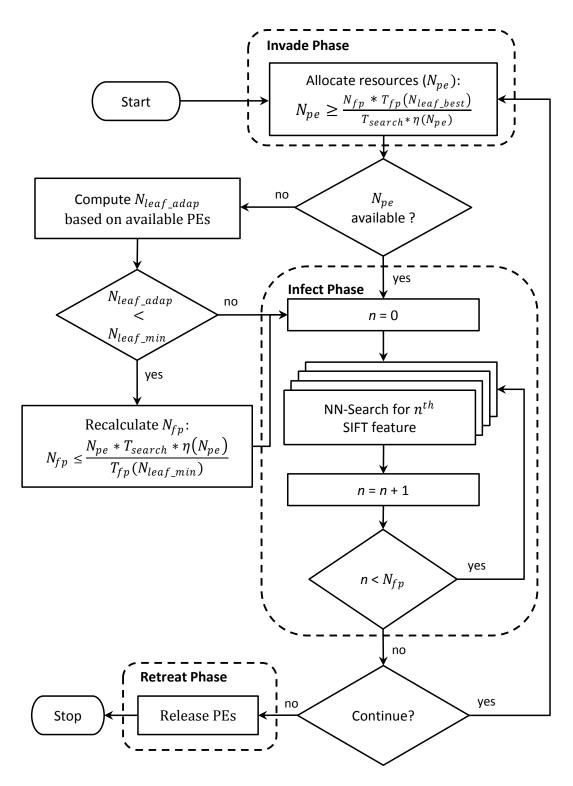

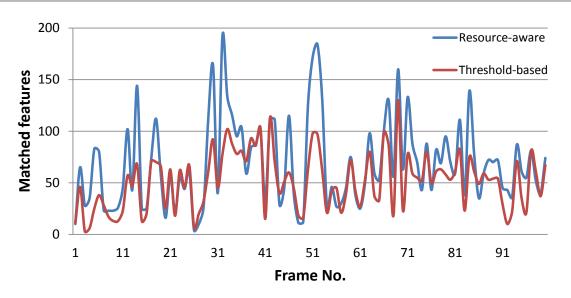

| 5.2.5.       Evaluation & Results       71         5.2.6.       Conclusion       74         6.       Accelerating Image Processing using Specialized Hardware       75         6.1.       InvasIC - Programmer's View       75         6.2.       Harris Corner Detection on Tightly Coupled Processor Array       77         6.2.1.       Conventional Approach       77         6.2.2.       Implementation on InvasIC       78         6.3.3.       Results       82         6.3.1.       Algorithm       82         6.3.2.       Accelerated Implementation on <i>i</i> -Core       83         6.3.3.       Results       87         6.4.1.       MPPAs for Optical Flow Computation       91         6.4.2.       Various Stages in Optical Flow Algorithm       92         6.4.3.       Optical Flow in Invasive Notation       97         6.4.4.       Implementation       99         6.4.5.       Results       104         6.5.       Conclusion       109         7.       Object Recognition on Heterogeneous MPSoC       111         7.1.       Hardware Prototype       112         7.2.1.       Homogeneous vs. Heterogeneous Implementation       114         7.2.2.<                                                                                                                                                                                                                                               |    |      |                                                              |     |

| 52.6. Conclusion       74         6. Accelerating Image Processing using Specialized Hardware       75         6.1. InvasIC - Programmer's View       75         6.2. Harris Corner Detection on Tightly Coupled Processor Array       77         6.2.1. Conventional Approach       77         6.2.2. Implementation on InvasIC       78         6.2.3. Results       82         6.3. SIFT Feature Matching on <i>i</i> -Core       82         6.3.1. Algorithm       82         6.3.2. Accelerated Implementation on <i>i</i> -Core       82         6.3.3. Results       87         6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4.1. MPPAs for Optical Flow Computation       91         6.4.2. Various Stages in Optical Flow Algorithm       92         6.4.3. Optical Flow in Invasive Notation       97         6.4.4. Implementation       99         6.4.5. Results       104         6.5. Conclusion       109         7. Object Recognition on Heterogeneous MPSoC       111         7.1. Hardware Prototype       112         7.2. Kultiple Applications on Heterogeneous MPSoC       115         7.2.3. Heterogeneous vs. Heterogeneous MPSoC       115         7.3. Conclusion       120         8. Conclusion a                                                                                                                                                              |    |      |                                                              | 71  |

| 6.1. InvasIC - Programmer's View756.2. Harris Corner Detection on Tightly Coupled Processor Array776.2.1. Conventional Approach776.2.2. Implementation on InvasIC786.2.3. Results826.3.3. Results826.3.1. Algorithm826.3.2. Accelerated Implementation on <i>i</i> -Core836.3.3. Results876.4. Optical Flow Computation on Tightly Coupled Processor Array916.4.1. MPPAs for Optical Flow Computation916.4.2. Various Stages in Optical Flow Algorithm926.4.3. Optical Flow in Invasive Notation976.4.4. Implementation996.4.5. Results1046.5. Conclusion1097. Object Recognition on Heterogeneous MPSoC1117.1. Hardware Prototype1127.2. Evaluation Models1137.2.3. Heterogeneous Vs. Heterogeneous MPSoC1157.3. Conclusion1208. Conclusion and Outlook123A. Hardware Monitoring Framework for InvasIC127A.1. Hardware Monitor Design128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |      |                                                              | 74  |

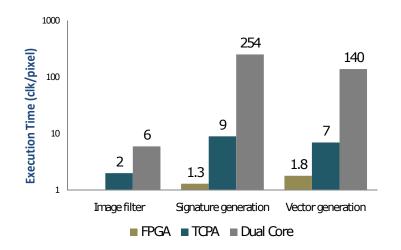

| 6.1. InvasIC - Programmer's View756.2. Harris Corner Detection on Tightly Coupled Processor Array776.2.1. Conventional Approach776.2.2. Implementation on InvasIC786.2.3. Results826.3.3. Results826.3.1. Algorithm826.3.2. Accelerated Implementation on <i>i</i> -Core836.3.3. Results876.4. Optical Flow Computation on Tightly Coupled Processor Array916.4.1. MPPAs for Optical Flow Computation916.4.2. Various Stages in Optical Flow Algorithm926.4.3. Optical Flow in Invasive Notation976.4.4. Implementation996.4.5. Results1046.5. Conclusion1097. Object Recognition on Heterogeneous MPSoC1117.1. Hardware Prototype1127.2. Evaluation Models1137.2.3. Heterogeneous Vs. Heterogeneous MPSoC1157.3. Conclusion1208. Conclusion and Outlook123A. Hardware Monitoring Framework for InvasIC127A.1. Hardware Monitor Design128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6. | Acc  | elerating Image Processing using Specialized Hardware        | 75  |

| 6.2. Harris Corner Detection on Tightly Coupled Processor Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •- |      |                                                              |     |

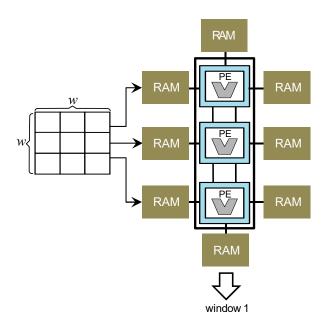

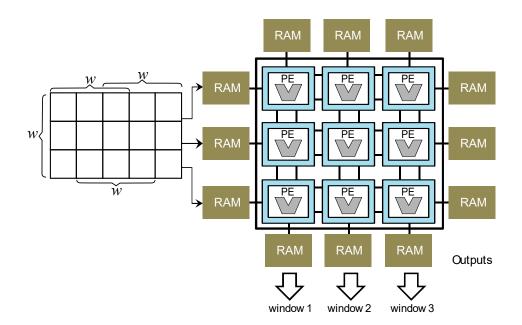

| 62.1. Conventional Approach       77         62.2. Implementation on InvasIC       78         62.3. Results       82         6.3. SIFT Feature Matching on <i>i</i> -Core       82         6.3. Algorithm       82         6.3. Accelerated Implementation on <i>i</i> -Core       83         6.3. Accelerated Implementation on <i>i</i> -Core       83         6.3. Accelerated Implementation on <i>i</i> -Core       83         6.3. Results       87         6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4.1. MPPAs for Optical Flow Computation       91         6.4.2. Various Stages in Optical Flow Algorithm       92         6.4.3. Optical Flow in Invasive Notation       97         6.4.4. Implementation       99         6.4.5. Results       104         6.5. Conclusion       109         7. Object Recognition on Heterogeneous MPSoC       111         7.1. Hardware Prototype       112         7.2. Evaluation Models       113         7.2.1. Homogeneous vs. Heterogeneous Implementation       114         7.2.2. Multiple Applications on Heterogeneous MPSoC       115         7.2.3. Heterogeneous MPSoC with Resource-aware Mapping       117         7.3. Conclusion       120         8. Conclusion and Out                                                                                                                                                  |    |      | 0                                                            | _   |

| 6.2.2. Implementation on InvasIC       78         6.2.3. Results       82         6.3. SIFT Feature Matching on <i>i</i> -Core       82         6.3. SIFT Feature Matching on <i>i</i> -Core       82         6.3.1. Algorithm       82         6.3.2. Accelerated Implementation on <i>i</i> -Core       83         6.3.3. Results       87         6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4.1. MPPAs for Optical Flow Computation       91         6.4.2. Various Stages in Optical Flow Algorithm       92         6.4.3. Optical Flow in Invasive Notation       97         6.4.4. Implementation       99         6.4.5. Results       104         6.5. Conclusion       109         7. Object Recognition on Heterogeneous MPSoC       111         7.1. Hardware Prototype       112         7.2. Evaluation Models       113         7.2.1. Homogeneous vs. Heterogeneous Implementation       114         7.2.2. Multiple Applications on Heterogeneous MPSoC       115         7.3. Conclusion       120         8. Conclusion and Outlook       123         A. Hardware Monitoring Framework for InvasIC       127         A.1. Hardware Monitor Design       128                                                                                                                                                                                                            |    | 0.2. |                                                              |     |

| 6.2.3. Results       82         6.3. SIFT Feature Matching on <i>i</i> -Core       82         6.3.1. Algorithm       82         6.3.2. Accelerated Implementation on <i>i</i> -Core       83         6.3.3. Results       87         6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4.1. MPPAs for Optical Flow Computation       91         6.4.2. Various Stages in Optical Flow Algorithm       92         6.4.3. Optical Flow in Invasive Notation       97         6.4.4. Implementation       99         6.4.5. Results       104         6.5. Conclusion       109         7. Object Recognition on Heterogeneous MPSoC       111         7.1. Hardware Prototype       112         7.2. Evaluation Models       113         7.2.1. Homogeneous vs. Heterogeneous Implementation       114         7.2.2. Multiple Applications on Heterogeneous MPSoC       115         7.3. Conclusion       120         8. Conclusion and Outlook       123         8. Conclusion and Outlook       123         A. Hardware Monitoring Framework for InvasIC       127         A.1. Hardware Monitor Design       128                                                                                                                                                                                                                                                                                |    |      |                                                              |     |

| 6.3. SIFT Feature Matching on <i>i</i> -Core826.3.1. Algorithm826.3.2. Accelerated Implementation on <i>i</i> -Core836.3.3. Results876.4. Optical Flow Computation on Tightly Coupled Processor Array916.4.1. MPPAs for Optical Flow Computation916.4.2. Various Stages in Optical Flow Algorithm926.4.3. Optical Flow in Invasive Notation976.4.4. Implementation996.4.5. Results1046.5. Conclusion1097. Object Recognition on Heterogeneous MPSoC1117.1. Hardware Prototype1127.2. Evaluation Models1137.2.1. Homogeneous vs. Heterogeneous Implementation1147.2.2. Multiple Applications on Heterogeneous MPSoC1157.3. Conclusion1208. Conclusion and Outlook123A. Hardware Monitoring Framework for InvasIC127A.1. Hardware Monitor Design128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |      |                                                              |     |

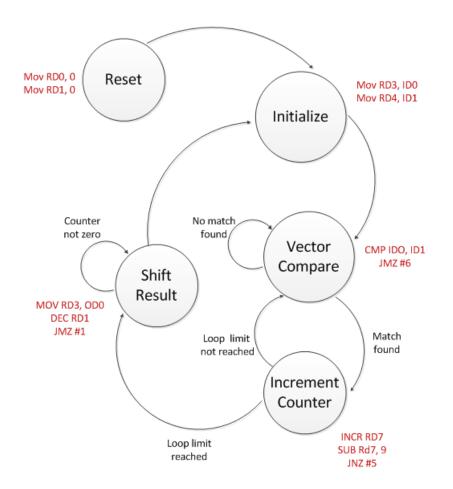

| 6.3.1. Algorithm826.3.2. Accelerated Implementation on <i>i</i> -Core836.3.3. Results876.4. Optical Flow Computation on Tightly Coupled Processor Array916.4.1. MPPAs for Optical Flow Computation916.4.2. Various Stages in Optical Flow Algorithm926.4.3. Optical Flow in Invasive Notation976.4.4. Implementation996.4.5. Results1046.5. Conclusion1097. Object Recognition on Heterogeneous MPSoC1117.1. Hardware Prototype1127.2. Evaluation Models1137.2.1. Homogeneous vs. Heterogeneous Implementation1147.2.2. Multiple Applications on Heterogeneous MPSoC1157.3. Conclusion1208. Conclusion and Outlook123A. Hardware Monitoring Framework for InvasIC127A.1. Hardware Monitor Design128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | 63   |                                                              |     |

| 6.3.2. Accelerated Implementation on <i>i</i> -Core       83         6.3.3. Results       87         6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4.1. MPPAs for Optical Flow Computation       91         6.4.2. Various Stages in Optical Flow Algorithm       92         6.4.3. Optical Flow in Invasive Notation       97         6.4.4. Implementation       99         6.4.5. Results       104         6.5. Conclusion       109         7. Object Recognition on Heterogeneous MPSoC       111         7.1. Hardware Prototype       112         7.2. Evaluation Models       113         7.2.1. Homogeneous vs. Heterogeneous Implementation       114         7.2.2. Multiple Applications on Heterogeneous MPSoC       115         7.3. Conclusion       120         8. Conclusion and Outlook       123         A. Hardware Monitoring Framework for InvasIC       127         A.1. Hardware Monitor Design       128                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 0.0. |                                                              |     |

| 6.3.3. Results       87         6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4.1. MPPAs for Optical Flow Computation       91         6.4.2. Various Stages in Optical Flow Algorithm       92         6.4.3. Optical Flow in Invasive Notation       97         6.4.4. Implementation       97         6.4.5. Results       104         6.5. Conclusion       109         7. Object Recognition on Heterogeneous MPSoC       111         7.1. Hardware Prototype       112         7.2. Evaluation Models       113         7.2.1. Homogeneous vs. Heterogeneous Implementation       114         7.2.2. Multiple Applications on Heterogeneous MPSoC       115         7.2.3. Heterogeneous MPSoC with Resource-aware Mapping       117         7.3. Conclusion       120         8. Conclusion and Outlook       123         A. Hardware Monitoring Framework for InvasIC       127         A.1. Hardware Monitor Design       128                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |      |                                                              |     |

| 6.4. Optical Flow Computation on Tightly Coupled Processor Array       91         6.4.1. MPPAs for Optical Flow Computation       91         6.4.2. Various Stages in Optical Flow Algorithm       92         6.4.3. Optical Flow in Invasive Notation       97         6.4.4. Implementation       97         6.4.5. Results       104         6.5. Conclusion       109         7. Object Recognition on Heterogeneous MPSoC       111         7.1. Hardware Prototype       112         7.2. Evaluation Models       113         7.2.1. Homogeneous vs. Heterogeneous Implementation       114         7.2.2. Multiple Applications on Heterogeneous MPSoC       115         7.3. Conclusion       117         7.3. Conclusion       120         8. Conclusion and Outlook       123         A. Hardware Monitoring Framework for InvasIC       127         A.1. Hardware Monitor Design       128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |      |                                                              |     |

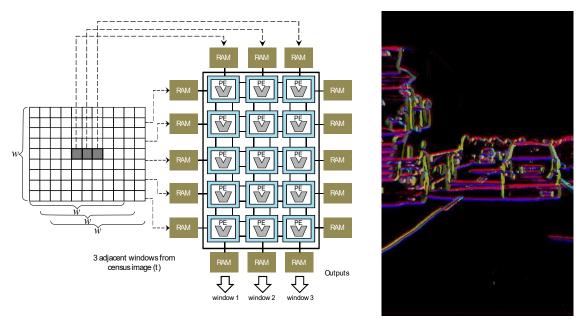

| 6.4.1. MPPAs for Optical Flow Computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 61   |                                                              |     |

| 6.4.2. Various Stages in Optical Flow Algorithm       92         6.4.3. Optical Flow in Invasive Notation       97         6.4.4. Implementation       99         6.4.5. Results       104         6.5. Conclusion       109 <b>7. Object Recognition on Heterogeneous MPSoC</b> 111         7.1. Hardware Prototype       112         7.2. Evaluation Models       113         7.2.1. Homogeneous vs. Heterogeneous Implementation       114         7.2.2. Multiple Applications on Heterogeneous MPSoC       115         7.3. Conclusion       120         8. Conclusion and Outlook       123         A. Hardware Monitoring Framework for InvasIC       127         A.1. Hardware Monitor Design       128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 0.4. |                                                              |     |

| 6.4.3. Optical Flow in Invasive Notation       97         6.4.4. Implementation       99         6.4.5. Results       104         6.5. Conclusion       109         7. Object Recognition on Heterogeneous MPSoC       111         7.1. Hardware Prototype       112         7.2. Evaluation Models       113         7.2.1. Homogeneous vs. Heterogeneous Implementation       114         7.2.2. Multiple Applications on Heterogeneous MPSoC       115         7.3. Conclusion       120         8. Conclusion and Outlook       123         A. Hardware Monitoring Framework for InvasIC       127         A.1. Hardware Monitor Design       128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |      | 1 1                                                          |     |

| 6.4.4. Implementation996.4.5. Results1046.5. Conclusion1097. Object Recognition on Heterogeneous MPSoC1117.1. Hardware Prototype1127.2. Evaluation Models1137.2.1. Homogeneous vs. Heterogeneous Implementation1147.2.2. Multiple Applications on Heterogeneous MPSoC1157.2.3. Heterogeneous MPSoC with Resource-aware Mapping1177.3. Conclusion1208. Conclusion and Outlook123A. Hardware Monitoring Framework for InvasIC127A.1. Hardware Monitor Design128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |      |                                                              |     |

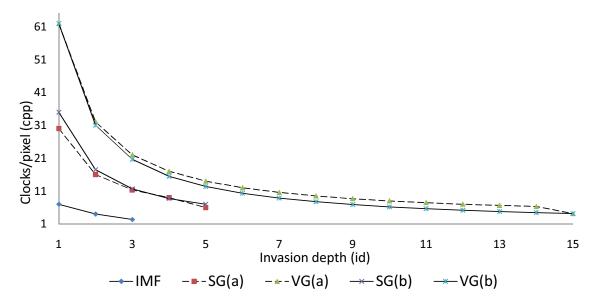

| 6.4.5. Results       104         6.5. Conclusion       109         7. Object Recognition on Heterogeneous MPSoC       111         7.1. Hardware Prototype       112         7.2. Evaluation Models       113         7.2.1. Homogeneous vs. Heterogeneous Implementation       114         7.2.2. Multiple Applications on Heterogeneous MPSoC       115         7.2.3. Heterogeneous MPSoC with Resource-aware Mapping       117         7.3. Conclusion       120         8. Conclusion and Outlook       123         A. Hardware Monitoring Framework for InvasIC       127         A.1. Hardware Monitor Design       128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |      |                                                              |     |

| 6.5. Conclusion       109         7. Object Recognition on Heterogeneous MPSoC       111         7.1. Hardware Prototype       112         7.2. Evaluation Models       113         7.2.1. Homogeneous vs. Heterogeneous Implementation       114         7.2.2. Multiple Applications on Heterogeneous MPSoC       115         7.3. Heterogeneous MPSoC with Resource-aware Mapping       117         7.3. Conclusion       120         8. Conclusion and Outlook       123         A. Hardware Monitoring Framework for InvasIC       127         A.1. Hardware Monitor Design       128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |      | 1                                                            |     |

| 7. Object Recognition on Heterogeneous MPSoC       111         7.1. Hardware Prototype       112         7.2. Evaluation Models       113         7.2.1. Homogeneous vs. Heterogeneous Implementation       114         7.2.2. Multiple Applications on Heterogeneous MPSoC       115         7.2.3. Heterogeneous MPSoC with Resource-aware Mapping       117         7.3. Conclusion       120         8. Conclusion and Outlook       123         A. Hardware Monitoring Framework for InvasIC       127         A.1. Hardware Monitor Design       128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 6 5  |                                                              |     |

| 7.1. Hardware Prototype       112         7.2. Evaluation Models       113         7.2.1. Homogeneous vs. Heterogeneous Implementation       114         7.2.2. Multiple Applications on Heterogeneous MPSoC       115         7.2.3. Heterogeneous MPSoC with Resource-aware Mapping       117         7.3. Conclusion       120         8. Conclusion and Outlook       123         A. Hardware Monitoring Framework for InvasIC       127         A.1. Hardware Monitor Design       128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    | 6.3. |                                                              | 109 |

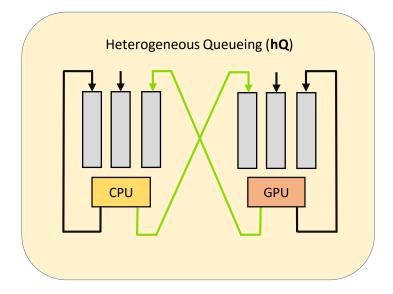

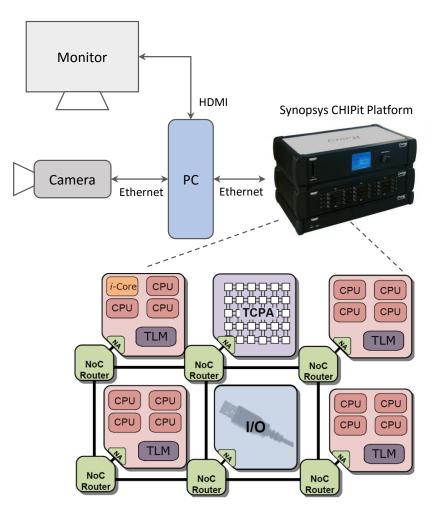

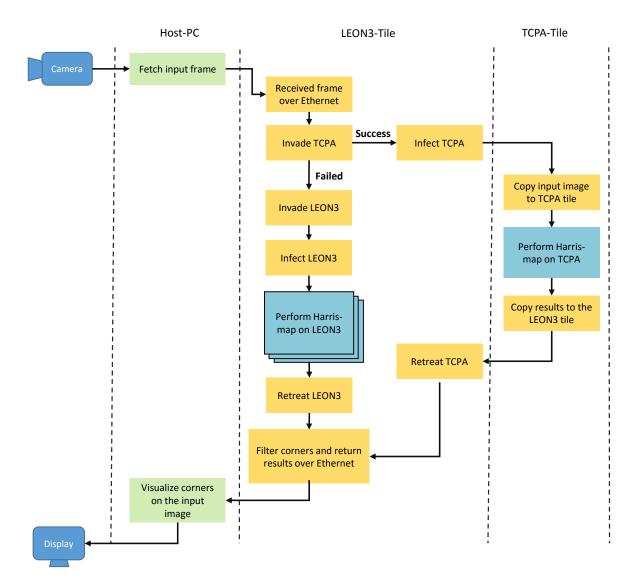

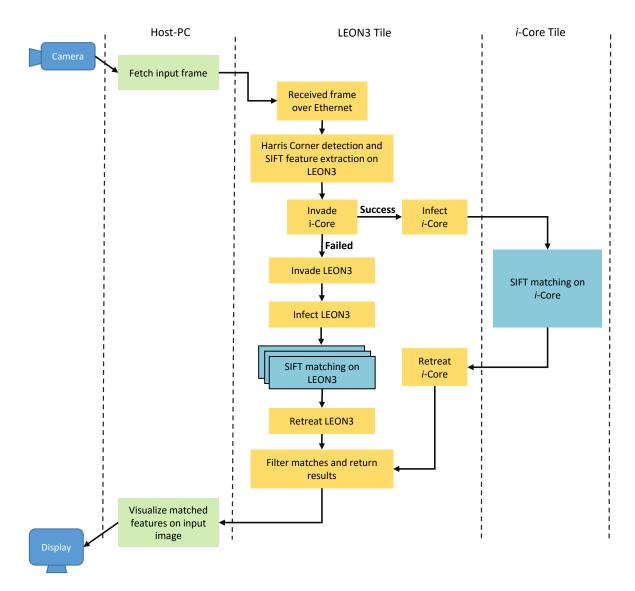

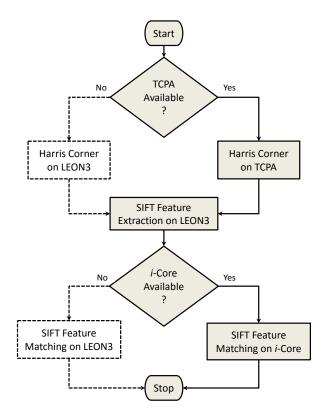

| 7.2. Evaluation Models       113         7.2.1. Homogeneous vs. Heterogeneous Implementation       114         7.2.2. Multiple Applications on Heterogeneous MPSoC       115         7.2.3. Heterogeneous MPSoC with Resource-aware Mapping       117         7.3. Conclusion       120         8. Conclusion and Outlook       123         A. Hardware Monitoring Framework for InvasIC       127         A.1. Hardware Monitor Design       128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7. | -    |                                                              |     |

| 7.2.1. Homogeneous vs. Heterogeneous Implementation       114         7.2.2. Multiple Applications on Heterogeneous MPSoC       115         7.2.3. Heterogeneous MPSoC with Resource-aware Mapping       117         7.3. Conclusion       120         8. Conclusion and Outlook       123         A. Hardware Monitoring Framework for InvasIC       127         A.1. Hardware Monitor Design       128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |      | 51                                                           |     |

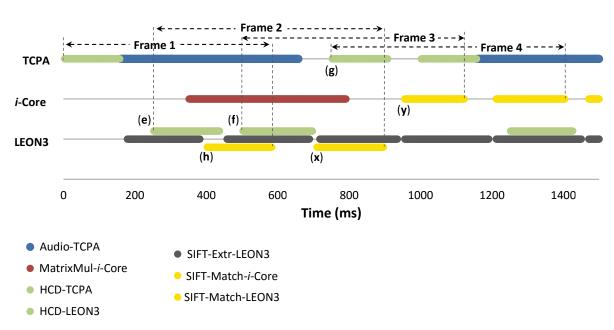

| 7.2.2. Multiple Applications on Heterogeneous MPSoC       115         7.2.3. Heterogeneous MPSoC with Resource-aware Mapping       117         7.3. Conclusion       120         8. Conclusion and Outlook       123         A. Hardware Monitoring Framework for InvasIC       127         A.1. Hardware Monitor Design       128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 7.2. |                                                              | 113 |

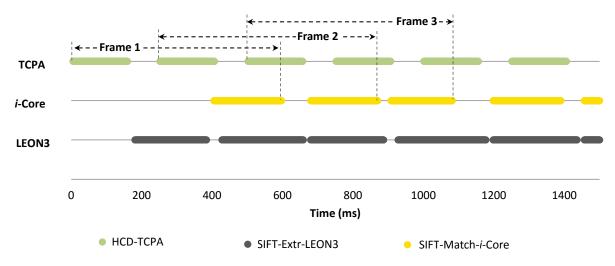

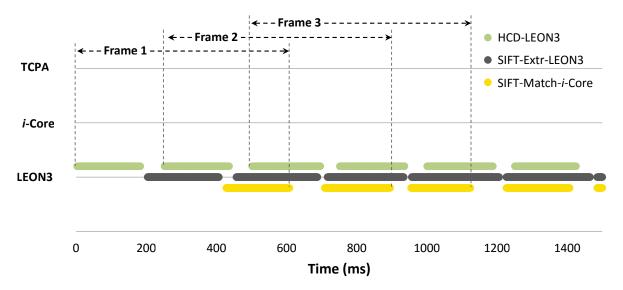

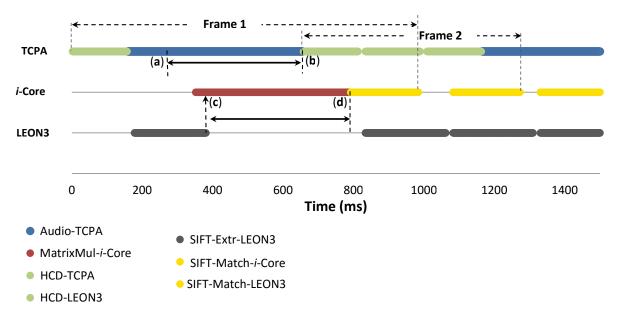

| 7.2.3. Heterogeneous MPSoC with Resource-aware Mapping       117         7.3. Conclusion       120         8. Conclusion and Outlook       123         A. Hardware Monitoring Framework for InvasIC       127         A.1. Hardware Monitor Design       128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |      |                                                              | 114 |

| 7.3. Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |      | 7.2.2. Multiple Applications on Heterogeneous MPSoC          | 115 |

| 8. Conclusion and Outlook       123         A. Hardware Monitoring Framework for InvasIC       127         A.1. Hardware Monitor Design       128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |      | 7.2.3. Heterogeneous MPSoC with Resource-aware Mapping       | 117 |

| A. Hardware Monitoring Framework for InvasIC       127         A.1. Hardware Monitor Design       128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | 7.3. | Conclusion                                                   | 120 |

| A.1. Hardware Monitor Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8. | Con  | clusion and Outlook                                          | 123 |

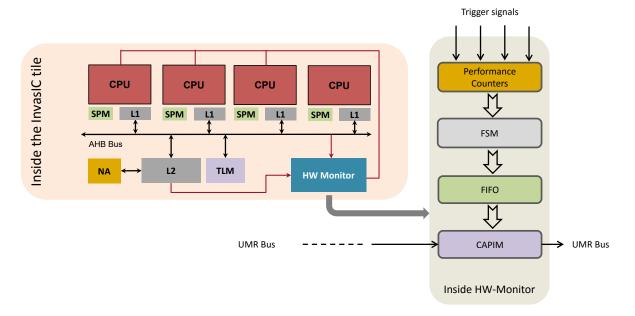

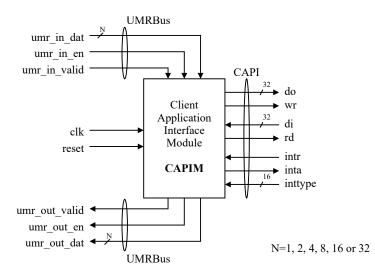

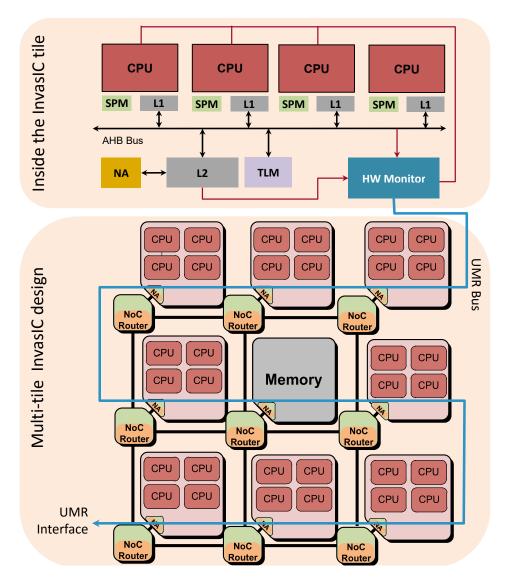

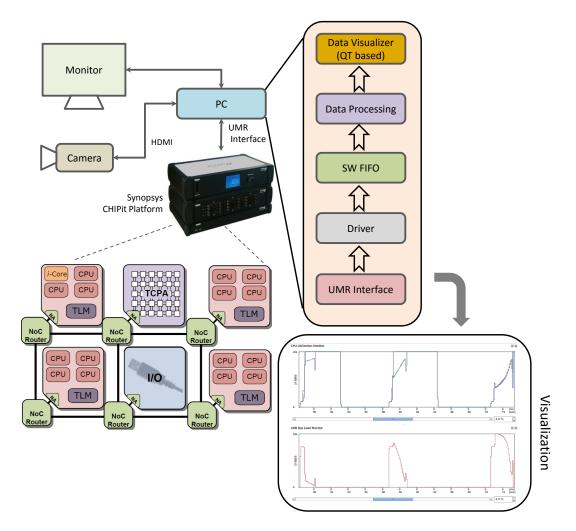

| A.1. Hardware Monitor Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Α. | Hard | dware Monitoring Framework for InvasIC                       | 127 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |      | •                                                            |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |      |                                                              |     |

#### Contents

| в. | Owr  | n Public | ations    |         |        |       |      |     |      |      |     |     |     |   |    |     |    |   |     |   |   |       | 141 |

|----|------|----------|-----------|---------|--------|-------|------|-----|------|------|-----|-----|-----|---|----|-----|----|---|-----|---|---|-------|-----|

|    | A.4. | Conclu   | ision     |         |        |       |      | • • | • •  |      | • • | •   | • • | • |    | •   |    | • | ••• | • | • | <br>• | 139 |

|    |      |          | Results   |         | -      |       |      |     |      |      |     |     |     |   |    |     |    |   |     |   |   |       |     |

|    |      |          | Evaluati  | 5       | 0      | ·     |      |     |      |      |     |     |     |   |    |     |    |   |     |   |   |       |     |

|    | A.3. | Applic   | ation An  | alysis  | using  | Ha:   | rdw  | are | Moi  | nitc | ors |     |     |   |    |     |    |   |     |   |   |       | 134 |

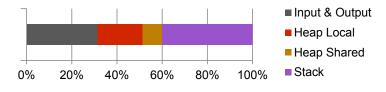

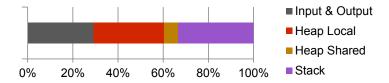

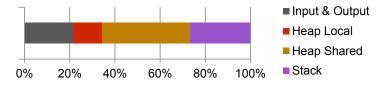

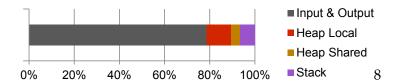

|    | A.2. | Stack a  | nd Heap   | Mapp    | ing u  | ising | , Hi | nts | fron | ۱H   | ard | lwa | are | М | on | ito | rs |   |     |   |   |       | 131 |

|    |      | A.1.3.   | Visualiz  | ation   |        |       |      |     |      |      |     |     |     |   |    |     |    |   |     |   |   |       | 130 |

|    |      | A.1.2.   | Interface | e and I | Data I | Exch  | ang  | е.  |      |      |     |     |     |   |    |     |    |   |     |   |   |       | 130 |

Bibliography

#### 143

## **List of Figures**

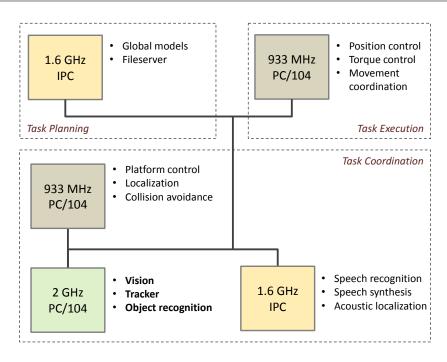

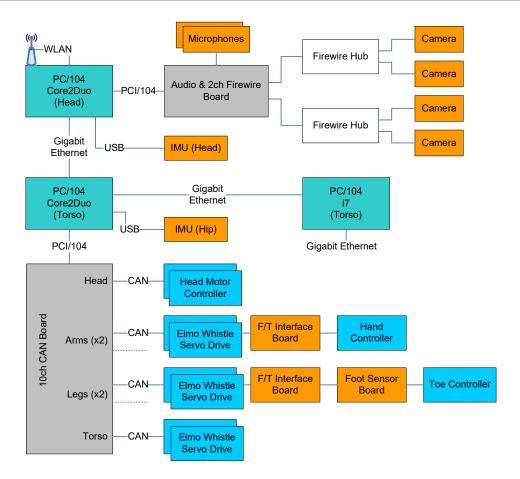

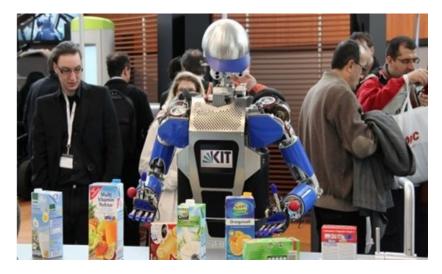

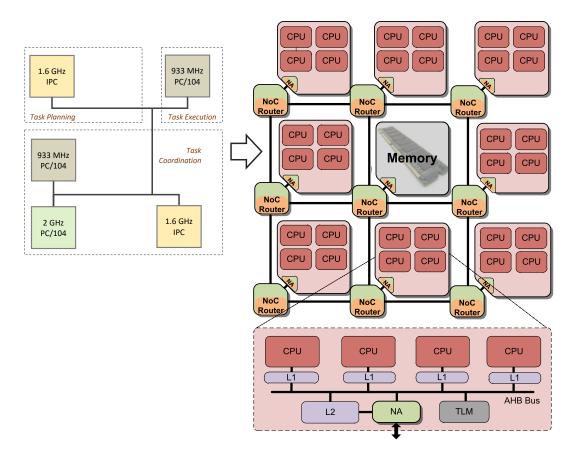

| <ol> <li>1.1.</li> <li>1.2.</li> <li>1.3.</li> </ol>                                                                                     | The humanoid robot ARMAR-III with 43 degrees of freedom. The robot con-<br>sists of an active head with cameras for vision, two arms and two five-fingered<br>hands, a torso and a holonomic mobile platform [1]                                                                                                                                                                                                                                                                                                                 | 3<br>6<br>7                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

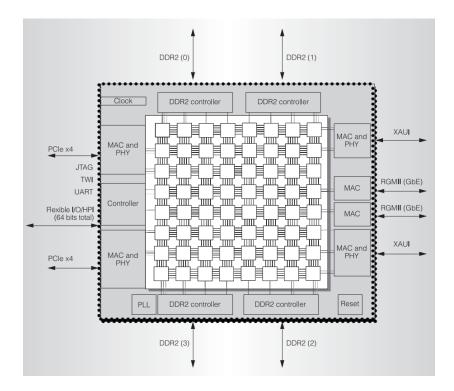

| 2.1.<br>2.2.                                                                                                                             | Block diagram of the TILE64 processor [3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12<br>13                                                             |

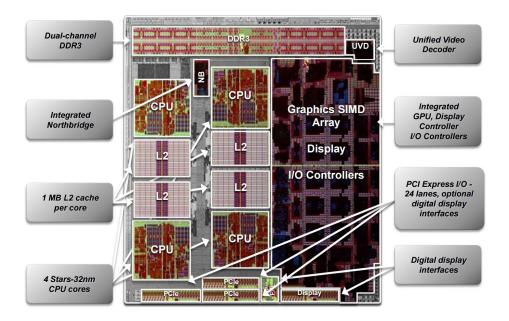

| 2.3.<br>2.4.                                                                                                                             | AMD's fusion APU (Llano) [5]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13<br>14<br>15                                                       |

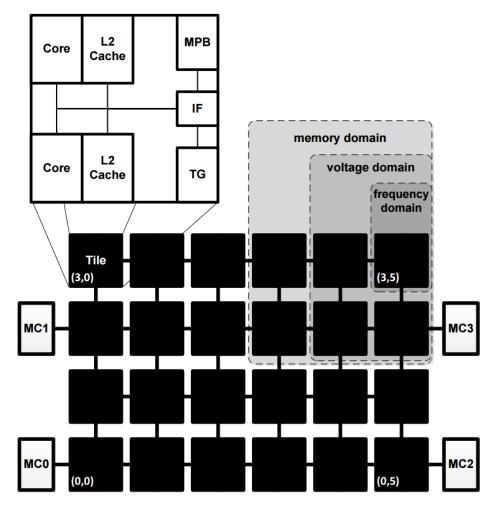

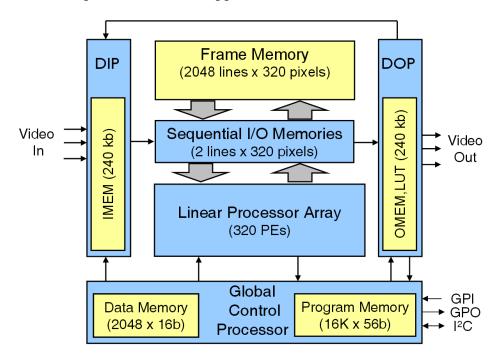

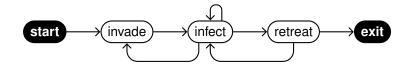

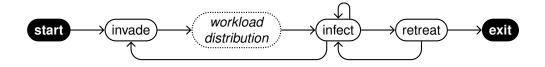

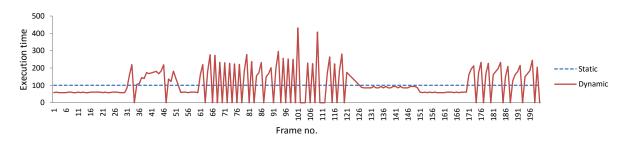

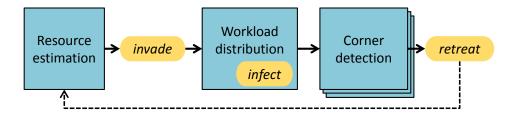

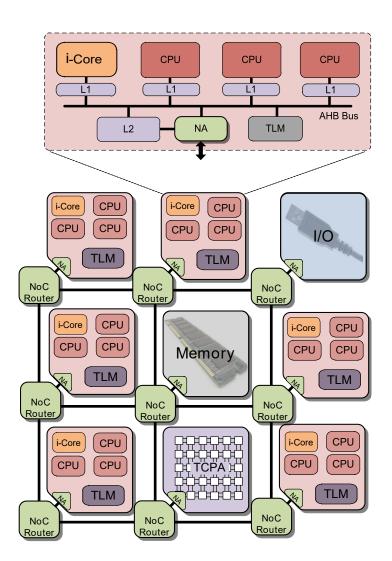

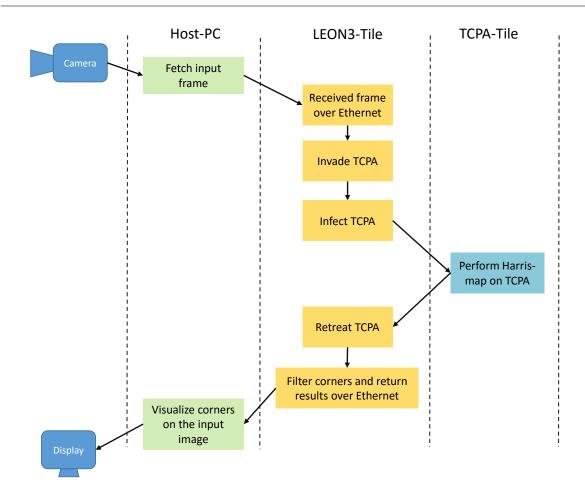

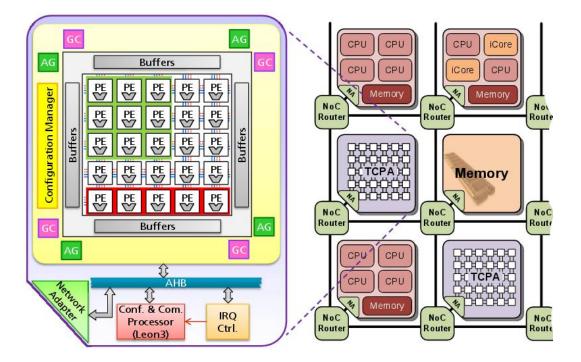

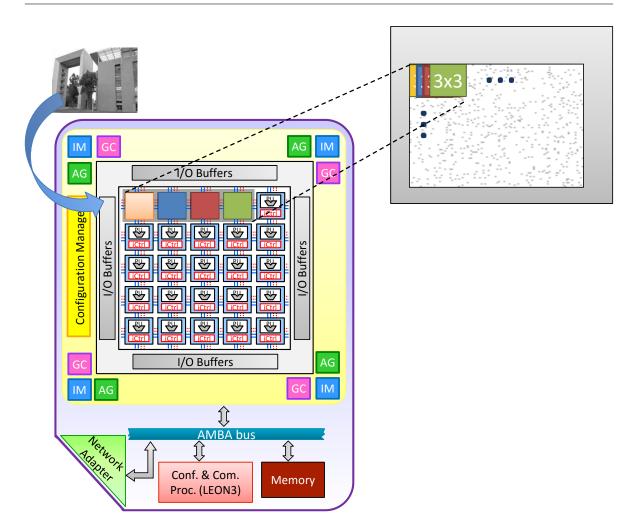

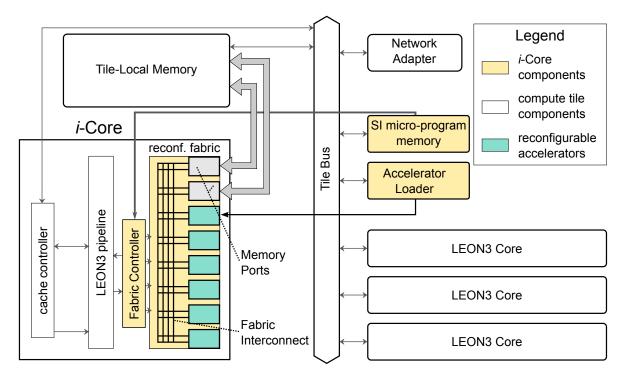

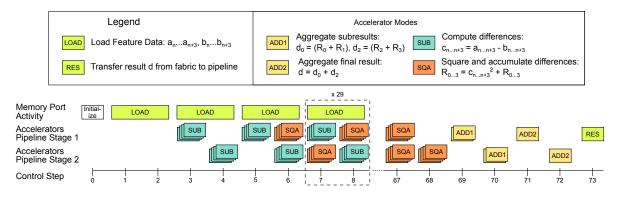

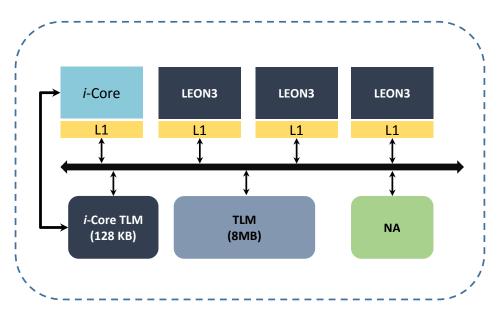

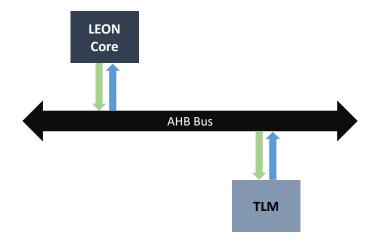

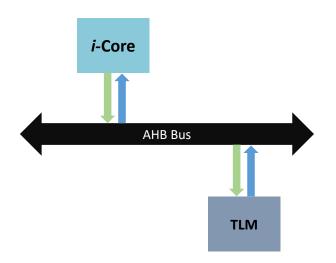

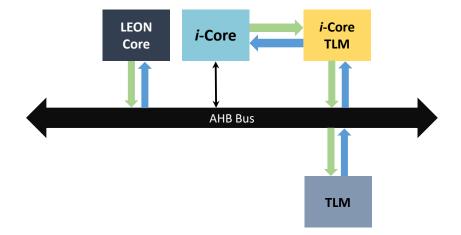

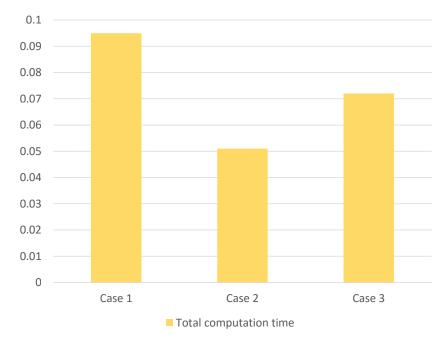

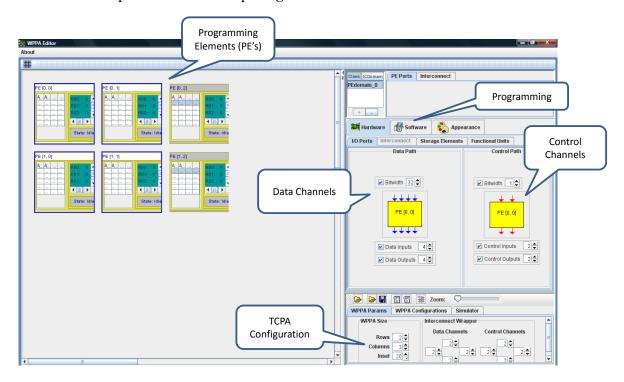

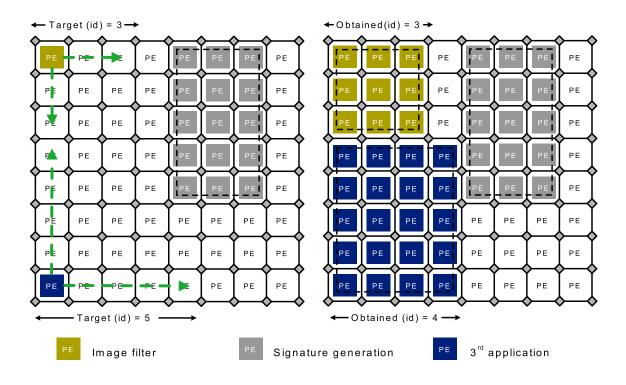

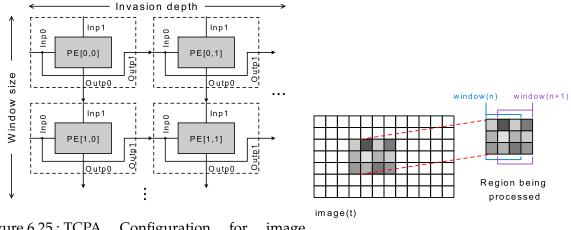

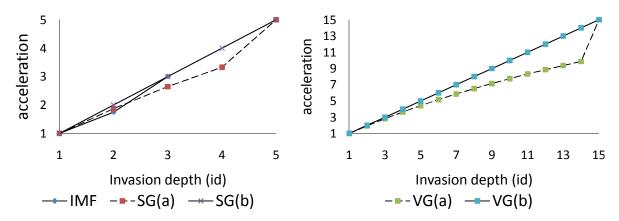

| <ol> <li>3.5.</li> <li>3.6.</li> <li>3.7.</li> <li>3.8.</li> <li>3.9.</li> <li>3.10.</li> <li>3.11.</li> </ol>                           | Structure of an invasive program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20<br>20<br>21<br>23<br>24<br>26<br>28<br>29<br>30<br>31<br>31<br>33 |

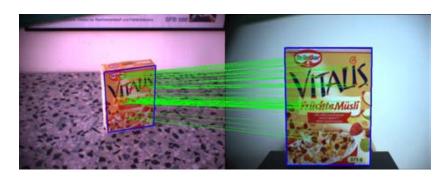

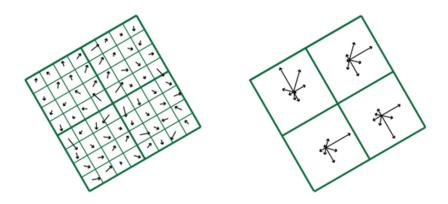

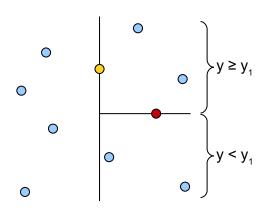

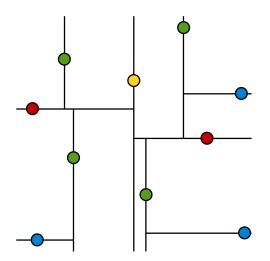

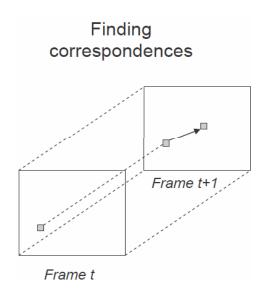

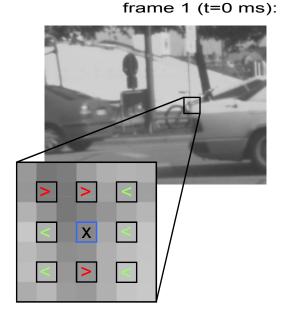

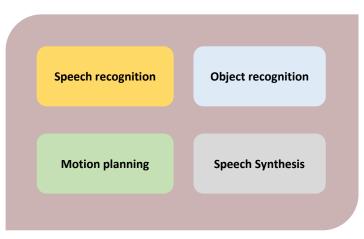

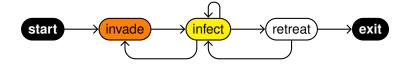

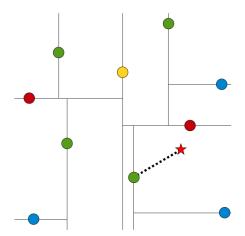

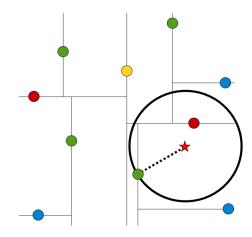

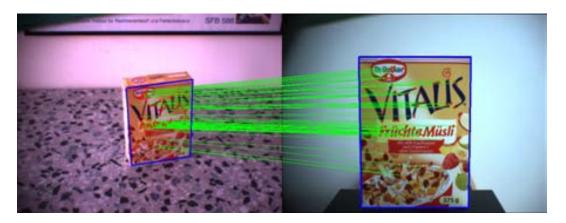

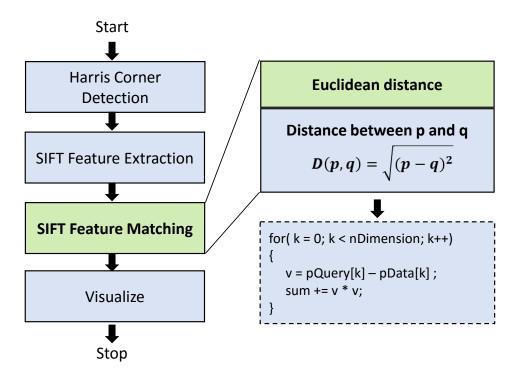

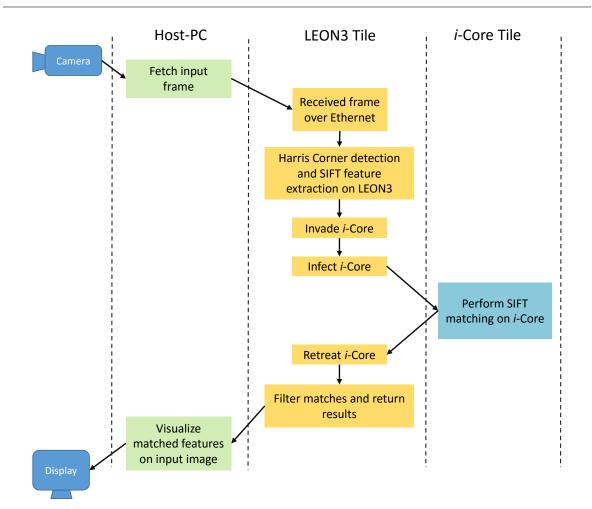

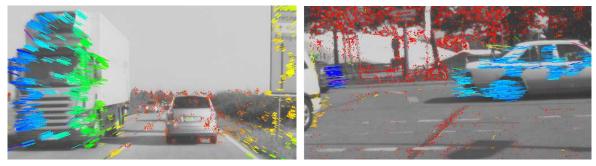

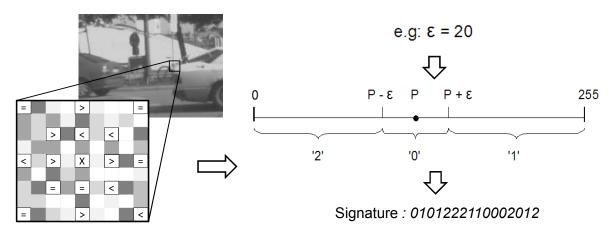

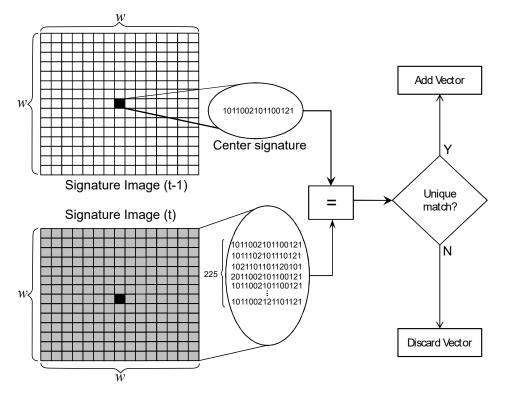

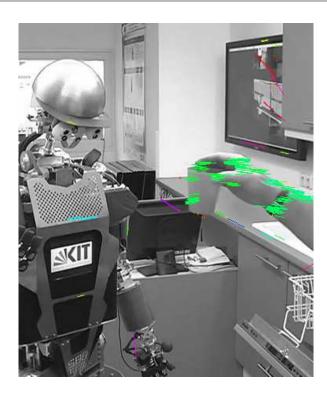

| <ul> <li>4.1.</li> <li>4.2.</li> <li>4.3.</li> <li>4.4.</li> <li>4.5.</li> <li>4.6.</li> <li>4.7.</li> <li>4.8.</li> <li>4.9.</li> </ul> | Humanoid robot ARMAR recognizing objects around itHarris SIFT object recognition [11]Data FlowOutput from Harris Corner detection algorithm (detected corners are high-<br>lighted using green dots)Computation of SIFT descriptor from sampled pixelsConstruction of KD-Tree (recursively build a kd-tree in the right half-space by<br>picking the some point and splitting the data horizontally through it)A completely constructed KD-TreeResult from Harris-SIFT based object recognition techniqueOptical flow definition | 35<br>36<br>37<br>38<br>40<br>41<br>41<br>41<br>42<br>43             |

| 4.10.                                                                                                                                    | Census transformation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 43<br>44<br>44                                                       |

|                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                      |

| 5.1.  | Conventional compute units used on the ARMAR robot (left) and the newly          | 4 -      |

|-------|----------------------------------------------------------------------------------|----------|

|       | proposed MPSoC architecture (right)                                              | 45       |

| 5.2.  | Various algorithms combined to perform object grasping                           | 46       |

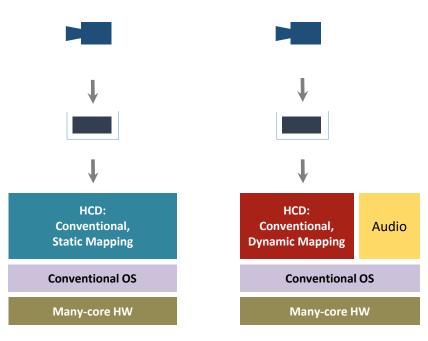

| 5.3.  | Evaluation model for Harris Corner detection with dedicated HW (left) vs.        |          |

|       | shared HW (right)                                                                | 47       |

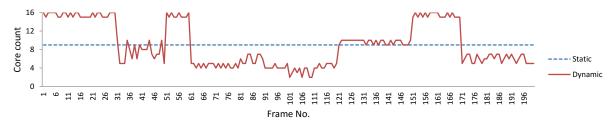

| 5.4.  | Variation in available resources for Harris Corner detection [12]                | 48       |

| 5.5.  | Variation in processing interval based on available resources [12]               | 48       |

| 5.6.  | Structure of an invasive program                                                 | 48       |

| 5.7.  | Harris corner detection (foreground and background pixels)                       | 50       |

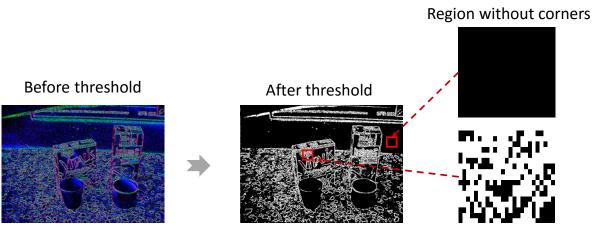

| 5.8.  | Pruning technique used in resource-aware Harris Corner detection                 | 50       |

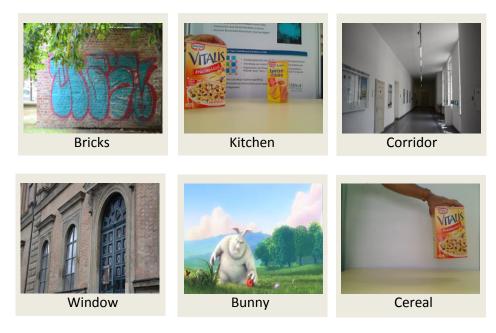

| 5.9.  | Snapshots of the video sequences used for evaluation [10]                        | 51       |

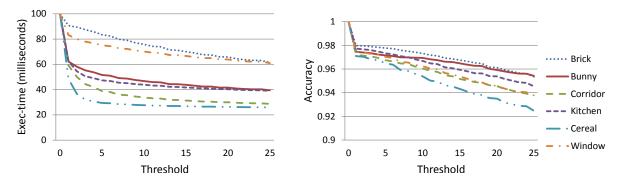

|       | Effects of pruning on execution time and accuracy for Harris detector [10]       | 52       |

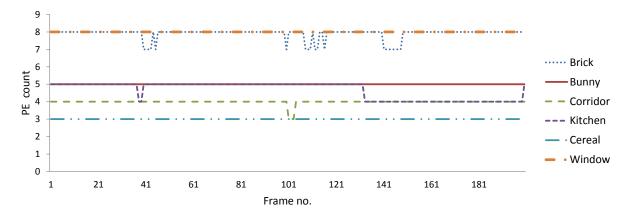

|       | Resource usage based on scene type (Harris detector using a threshold of 4) [10] | 53       |

|       | Flow diagram for the resource-aware corner detector [10]                         | 53       |

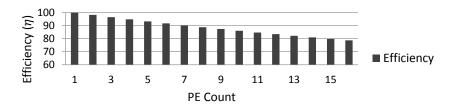

|       | Efficiency map for resource-aware Harris Corner detection on target HW [10]      | 54       |

|       | , 1                                                                              | 55       |

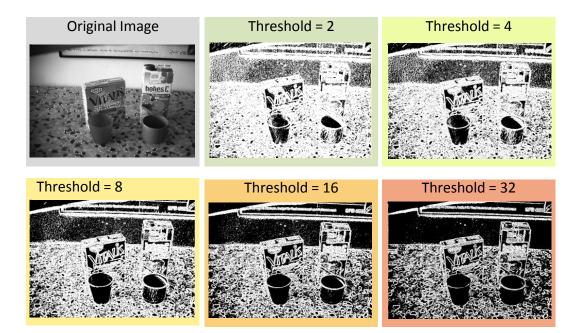

|       | Image samples demonstrating the pruning effect [10]                              | 55<br>56 |

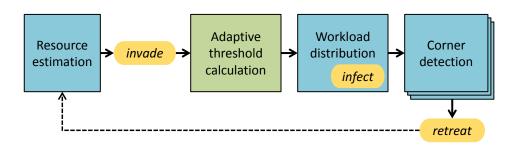

|       | Flow diagram for threshold estimation based on available resources [10]          |          |

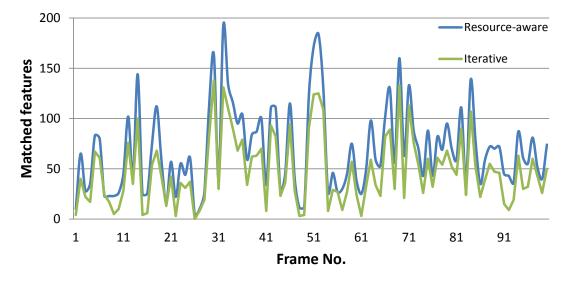

|       | Comparison between the conventional and resource-aware models [10]               | 57       |

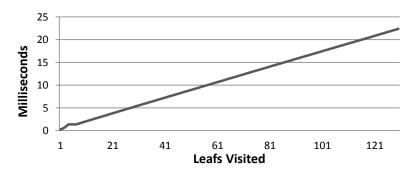

|       | Execution time for NN-search (static allocation) [13]                            | 61       |

|       | Dynamic resource usage during NN-search [13]                                     | 62       |