# Dynamic Partial Self-Reconfiguration of FPGAs for Digital Broadcasting Receiver Systems

# Michael Feilen

Vollständiger Abdruck von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktor-Ingenieurs (Dr.-Ing.)

genehmigten Dissertation.

Vorsitzender: Prof. Dr.-Ing. Wolfgang Utschick Prüfer der Dissertation: 1. Prof. Dr.-Ing. Walter Stechele

2. Prof. Raymond Knopp, Ph.D.

Die Dissertation wurde am 05.07.2016 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 21.02.2017 angenommen.

# **Abstract**

Partial reconfiguration of field-programmable gate arrays enhances the design-space by unconfined repurposing of logic elements to virtually enlarge the available resources of a programmable device. In this work, the benefits and drawbacks of partial FPGA reconfiguration in radio receiver systems will be outlined. The analysis comprises design considerations for self-adapting receiver systems, where resources are shared among different reconfigurable areas. The derivation of the resource requirements and explanation of the design complexity delivers an insight into the applicability of an adaptive receiver system using partial reconfiguration. In addition to the analysis of self-adapting systems, a framework for block-wise execution of receiver chain elements on partially reconfigurable systems will be introduced. Using this framework, the timing constraints for the execution and the delay implications of the receiver chain elements will be derived and analyzed by means of a prototype implementation. Given the previously derived approaches, an efficient algorithm for receiver chain partitioning will be introduced and analyzed in terms of efficiency and performance. Finally, it will be concluded that it is possible to implement resource-efficient adaptive receiver chains using partial FPGA reconfiguration and that new design tools are required to exploit the hardware possibilities of state-of-the art FPGAs.

# **Acknowledgments**

Writing this thesis was an exciting journey, and I thank all people who accompanied me during the time of my studies with their inspiration and patience. First, I would like to thank my supervising Professor Walter Stechele for his scientific reasoning and constructive advise – without his support, this work would not have been possible. I express my sincere appreciation to Professor Andreas Herkersdorf, head of the Institute for Integrated Systems for his engagement, for valuable discussions and for allowing me to be a part of his research team. Furthermore, I am grateful for fruitful discussions and constructive criticism by my colleague and friend Matthias Ihmig, who assisted me during my project work. In addition, I am thankful for the aspiring guidance and constructive feedback of Dirk Koch, Michael Vonbun and Lothar Stolz, who replied to my questions with scientific precision and a lively sense of humor. It was a pleasure to be able to supervise excellent students at the Technical University of Munich, namely, in chronological order: Stefan Strasser, Yu Qi, Ali Adan Malik, Philipp Schmidbauer, Anton Zahlheimer, Daniel Münch, Christian Schwarzbauer, Markus Gnadl, Hussein Alasadi, Andreas Iliopoulos, Michael Ruf and Korbinian Berthold. I am very thankful for their substantial contribution to my research. With the same gratitude I thank all staff members and Ph.D. colleagues at the institute for a brilliant research climate that shaped my scientific thinking, and Professor Andreas Steil, for his valuable feedback to meaningful questions. Warm thanks also to Norbert Niklasch, head of the IZ40 Sensor Signal Processing department at IABG, who inspired and encouraged me to put my results into words. Finally, I would like to thank the Bundesministerium für Wirtschaft und Technologie and TUV Rheinland for supporting my work in the context of the DEUFRAKO project under Grant 10 P 8012B.

With gratitude and love I thank Lena, Julius and Carla for their everlasting support.

Munich, June 2016

Michael Feilen

# **Contents**

| T | Intr | oductio  | on                                                              | 1  |

|---|------|----------|-----------------------------------------------------------------|----|

|   | 1.1  | Field-I  | Programmable Gate Arrays                                        | 1  |

|   |      | 1.1.1    | Dynamic Partial Self-Reconfiguration of FPGAs                   | 4  |

|   |      | 1.1.2    | Difference-Based DPR System Design Flow                         | 8  |

|   |      | 1.1.3    | Partition-Based DPR System Design Flow                          | 9  |

|   | 1.2  | Digita   | l Broadcasting Receivers                                        | 10 |

|   |      | 1.2.1    | Selected Standards                                              | 10 |

|   |      | 1.2.2    | Receiver Design and Properties                                  | 12 |

|   | 1.3  | Scope    | of this Work $\hdots$                                           | 13 |

|   | 1.4  | Struct   | ure of this Work                                                | 14 |

| 2 | FPC  | GA Self- | -Reconfiguration for Adaptive Radio Receivers                   | 16 |

|   | 2.1  | Relate   | ed-Work and Contribution                                        | 16 |

|   | 2.2  | FM Sc    | ound Broadcasting                                               | 18 |

|   | 2.3  |          | dularized FPGA-based FM Receiver                                | 21 |

|   |      | 2.3.1    | Receiver Modules                                                | 21 |

|   |      | 2.3.2    | Synthesis and Hardware Setup                                    | 34 |

|   | 2.4  | An Ml    | PX-based SNR Estimator for FM Radio                             | 39 |

|   |      | 2.4.1    | Estimator Requirements and Restrictions                         | 40 |

|   |      | 2.4.2    | FM Demodulation in Presence of Noise                            | 41 |

|   |      | 2.4.3    | MPX-Based Noise Power Estimator Design                          | 44 |

|   |      | 2.4.4    | Hardware Implementation                                         | 50 |

|   |      | 2.4.5    | SNR-Related Reconfiguration Conditions                          | 52 |

|   | 2.5  | An SN    | R-Adaptive FM Receiver using Partial Reconfiguration of FPGAs   | 54 |

|   |      | 2.5.1    | Single-Island Design                                            | 54 |

|   |      | 2.5.2    | Multi-Island Design                                             | 60 |

|   | 2.6  | Resour   | rce-Efficient Concurrent Receivers using DPR                    | 62 |

|   |      | 2.6.1    | Motivation                                                      | 62 |

|   |      | 2.6.2    | Proposed System                                                 | 65 |

|   |      | 2.6.3    | Resource-Shared Dual-Decoder Case Study                         | 65 |

|   | 2.7  | Summ     | ary                                                             | 70 |

| 3 | Сус  |          | A Reconfiguration for Sequential Processing of Receiver Modules | 72 |

|   | 3.1  |          | ed-Work and Contribution                                        | 73 |

|   | 3.2  | Systen   | m Model                                                         | 75 |

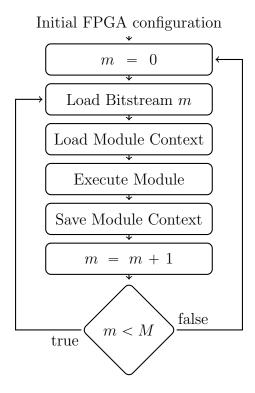

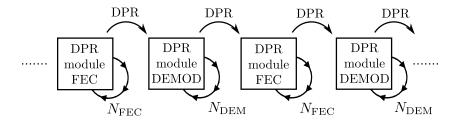

|   |      | 3.2.1    | Cyclic Reconfiguration Flow                                     | 75 |

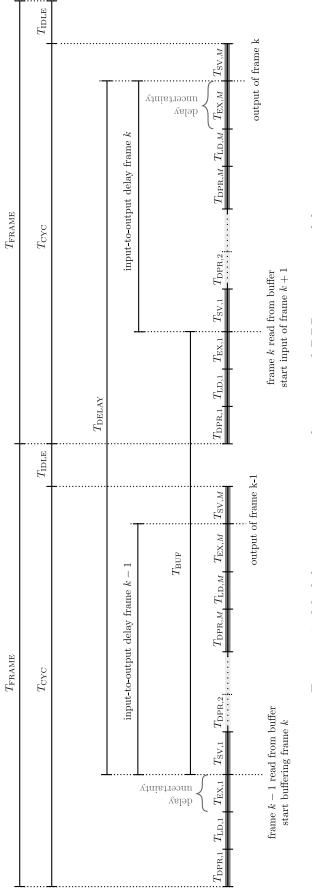

|   |      | 3.2.2    | Module Throughput and Data Framing                              | 77 |

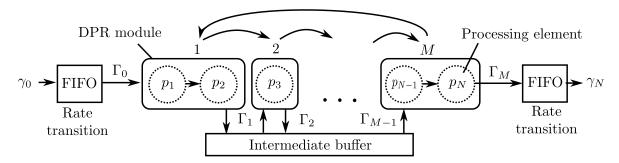

|   |      | 3.2.3    | Hardware Model                                                  | 80 |

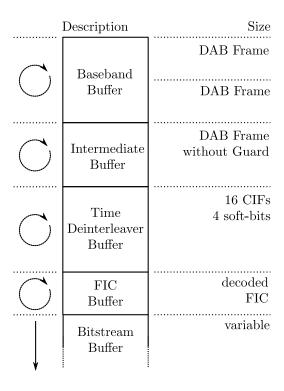

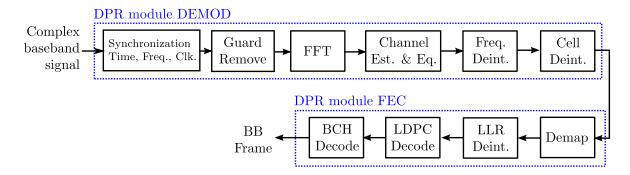

|   | 3.3  |                                                                            | 84  |

|---|------|----------------------------------------------------------------------------|-----|

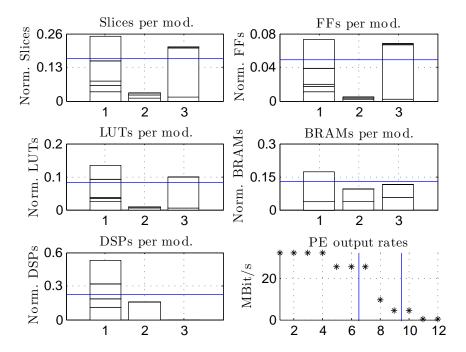

|   |      | 3.3.1 Resource Utilization and Dominating Processing Elements              | 88  |

|   |      | O I                                                                        | 90  |

|   |      | 3.3.3 Receiver Partitioning                                                | 92  |

|   |      | 3.3.4 Memory Throughput and Execution Time                                 | 93  |

|   |      | 3.3.5 Real-Time Constraints and Latency                                    | 97  |

|   | 3.4  | Cyclic DPR for DAB Receivers - Part II: Hardware Implementation 1          | .00 |

|   |      | 3.4.1 Static Environment of DPR System                                     | .01 |

|   |      | 3.4.2 DPR Simulation and Bitstream Generation Flow                         | .03 |

|   |      | 3.4.3 Resource Utilization and Comparison                                  | 06  |

|   |      | 3.4.4 Cyclic DPR Receiver Memory Requirements                              | 09  |

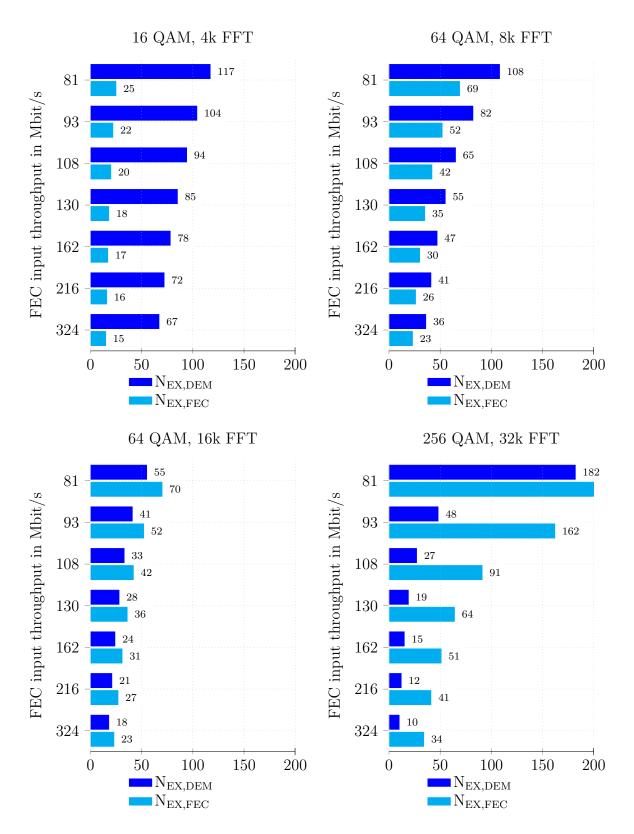

|   | 3.5  | Feasibility Analysis for a DVB-T2 Baseband Decoder using Cyclic DPR . $$ 1 | 12  |

|   |      | 3.5.1 System Architecture                                                  | 12  |

|   |      | 3.5.2 Real-Time Constraints                                                | 14  |

|   |      | 3.5.3 Feasibility Analysis                                                 | 16  |

|   |      | 3.5.4 Memory Constraints                                                   | 17  |

|   | 3.6  | Summary                                                                    | 21  |

| 4 | Higl | h-Level Receiver Partitioning for Cyclic FPGA Reconfiguration              | 22  |

|   | 4.1  | Related-Work and Contribution                                              | 22  |

|   | 4.2  | The Partitioning Problem                                                   | 23  |

|   | 4.3  | Performance Metrics for DPR Module Sets                                    | 25  |

|   |      | 4.3.1 Minimum Resource Variance Metric                                     | 25  |

|   |      | 4.3.2 Minimum Output Data Throughput Metric                                | 27  |

|   |      | 4.3.3 Combined Throughput and Variance Minimization Metric 1               | 28  |

|   | 4.4  |                                                                            | 28  |

|   | 4.5  | DAB Decoder Chain Partitioning                                             | 30  |

|   |      | 4.5.1 Weighting of Single Resource Elements                                | .31 |

|   | 4.6  |                                                                            | .33 |

| 5 | Con  | clusion and Outlook 1                                                      | 34  |

# **List of Figures**

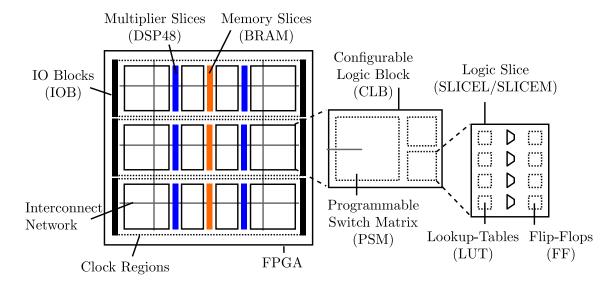

| 1.1  | FPGA application layer resource floorplan                                 | 2  |

|------|---------------------------------------------------------------------------|----|

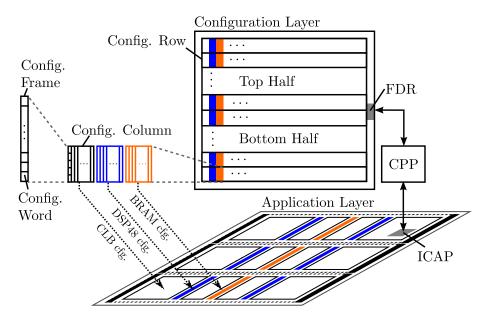

| 1.2  | FPGA configuration layer and application layer tiling                     | 3  |

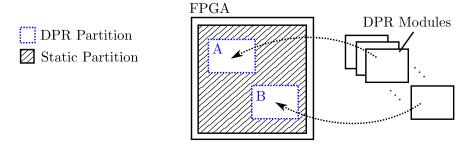

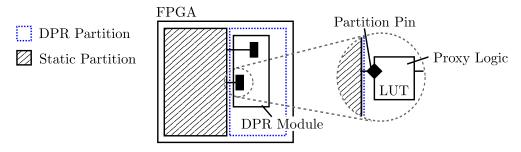

| 1.3  | Schematic diagram of a partially-reconfigurable FPGA system               | 5  |

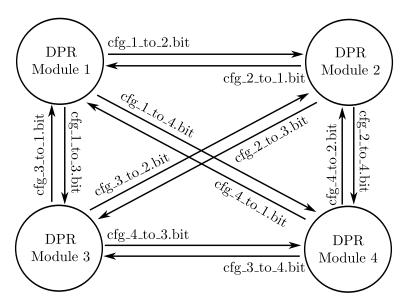

| 1.4  | Difference-based reconfiguration flow with four DPR modules               | 8  |

| 1.5  | Partition pins and proxy logic locations for partition-based DPR systems. | 9  |

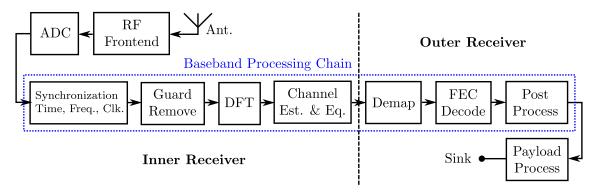

| 1.6  | OFDM receiver signal flow graph                                           | 12 |

| 1.7  | Structure of this thesis and major units of observation                   | 14 |

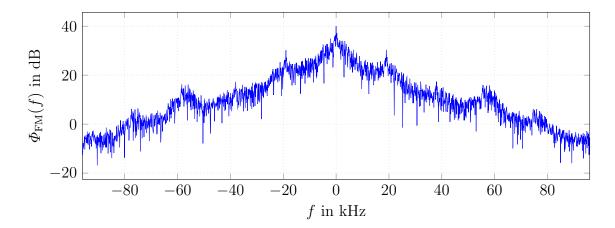

| 2.1  | Double-sided power spectral density of FM baseband signal                 | 19 |

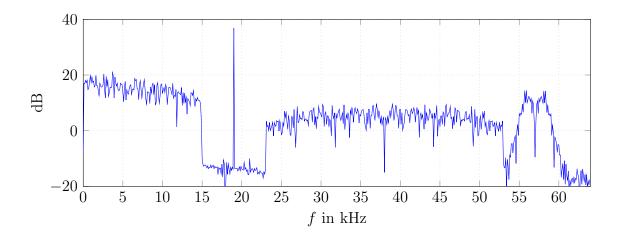

| 2.2  | Windowed one-sided power spectral density of FM multiplex signal          | 20 |

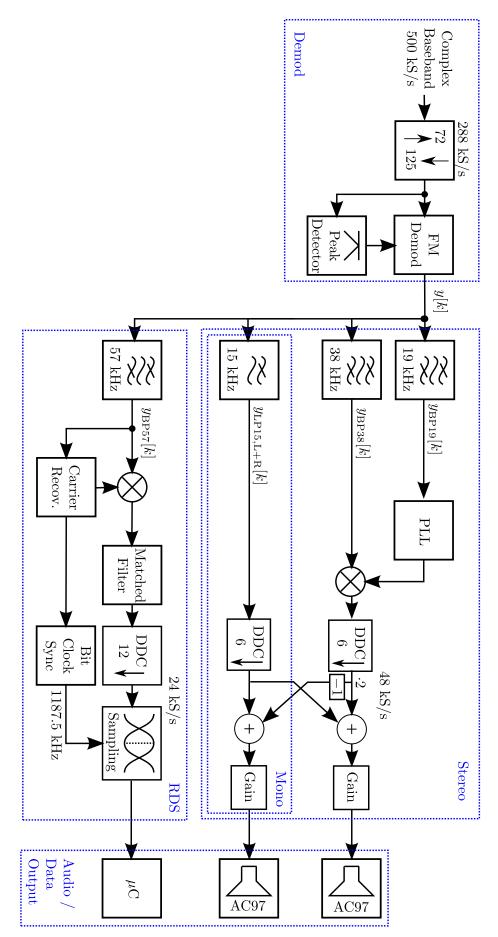

| 2.3  | FPGA-based FM/RDS receiver signal flow-graph                              | 22 |

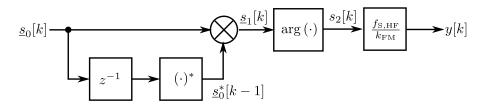

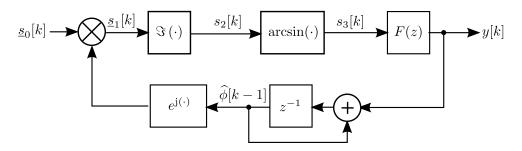

| 2.4  | Arcus-tangent quadrature discriminator for FM demodulation                | 25 |

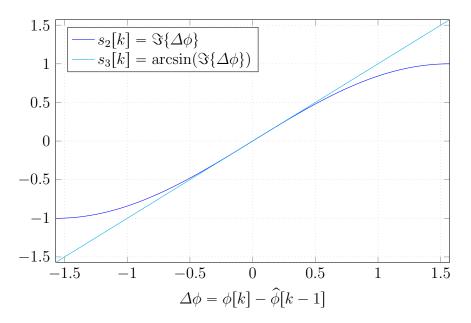

| 2.5  | FM digital PLL discriminator signal flow                                  | 26 |

| 2.6  | Digial PLL output signal and intermediate signal                          | 27 |

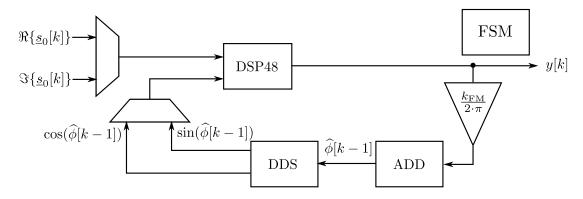

| 2.7  | Digital PLL hardware implementation                                       | 28 |

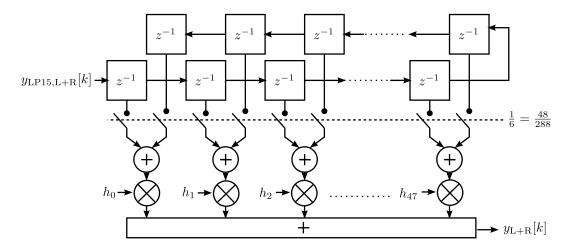

| 2.8  | Combined filtering and decimation for FM audio signal extraction          | 29 |

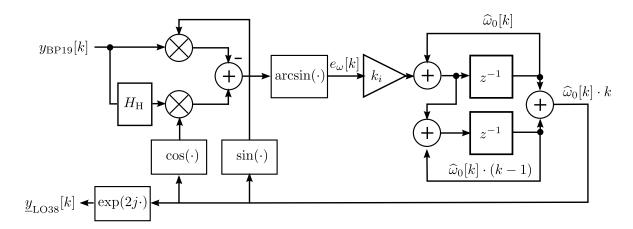

| 2.9  | MPX pilot DPLL angular frequency estimator                                | 30 |

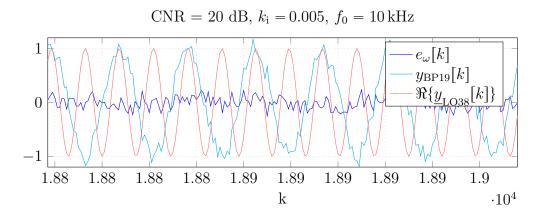

| 2.10 | Pilot PLL input and output signals with additive white Gaussian noise     | 31 |

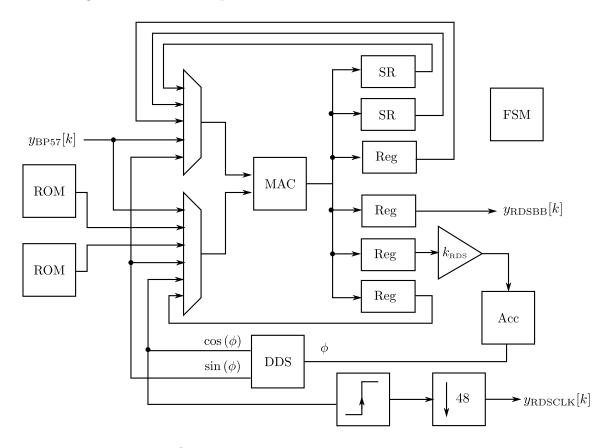

|      | FM RDS carrier and bit-clock recovery hardware implementation             | 32 |

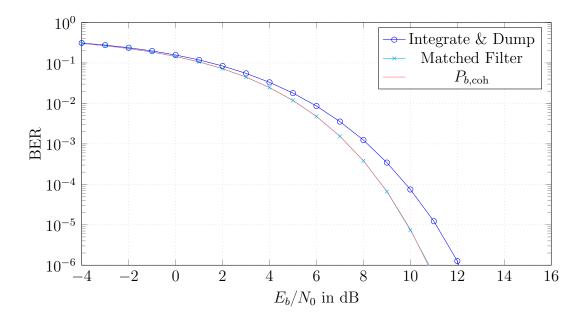

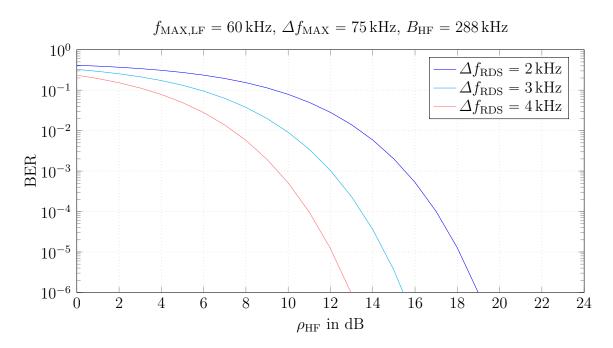

| 2.12 | BER performance of different RDS demodulator implementations              | 34 |

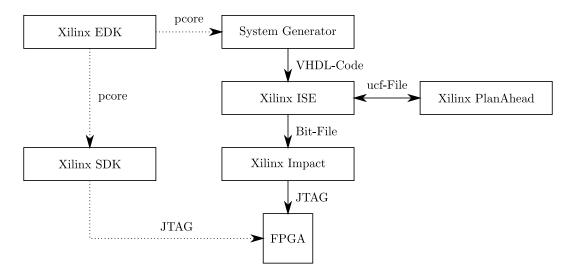

|      | FM receiver development and implementation tool-flow                      | 35 |

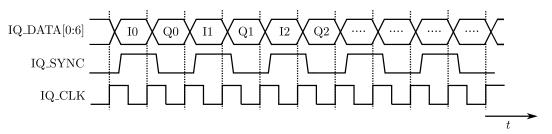

| 2.14 | Complex FM baseband signaling and clocking                                | 35 |

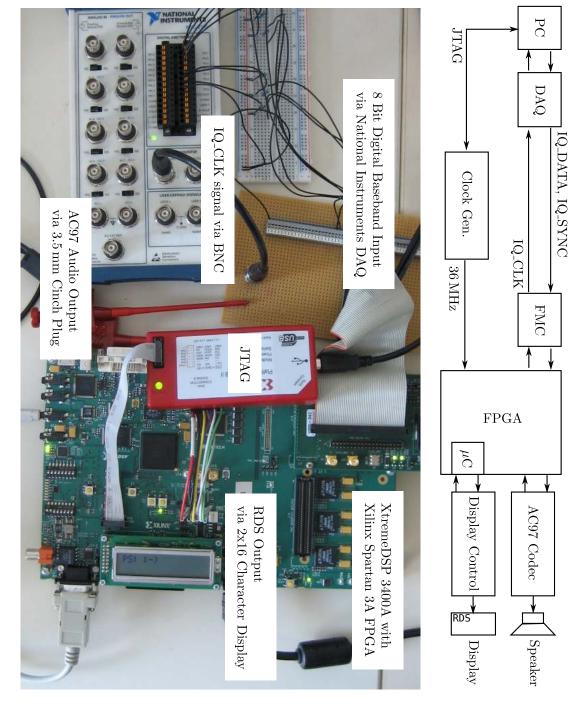

| 2.15 | Xilinx Spartan-3A FPGA with data-flow to PC DAQ board                     | 36 |

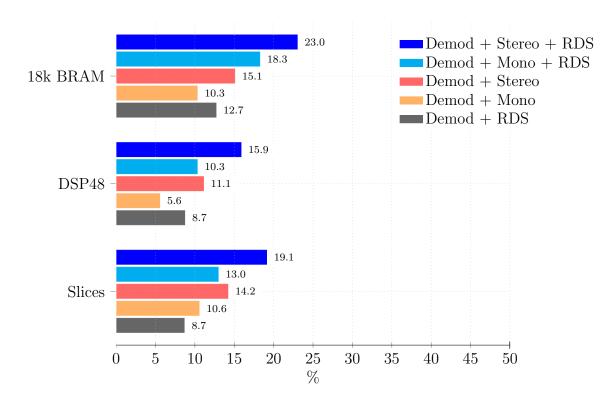

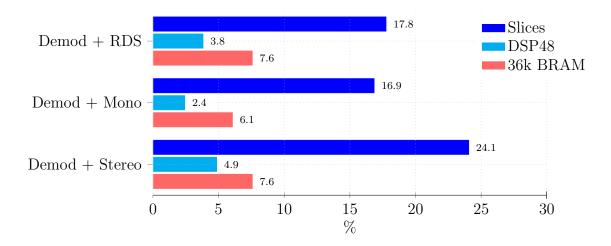

| 2.16 | FM receiver relative resource consumption on Xilinx XC3SD3400A FPGA.      | 38 |

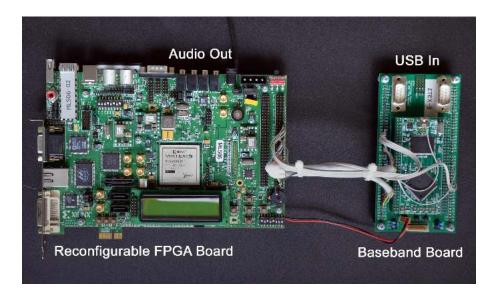

|      | Xilinx ML506 Virtex-5 FPGA board connected to Spartan-3 USB board.        | 39 |

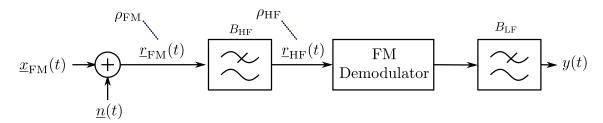

| 2.18 | FM demodulation in presence of AWGN                                       | 42 |

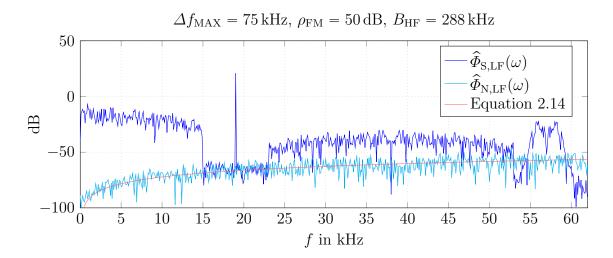

| 2.19 | Simulation and theory of MPX signal and noise PSD                         | 43 |

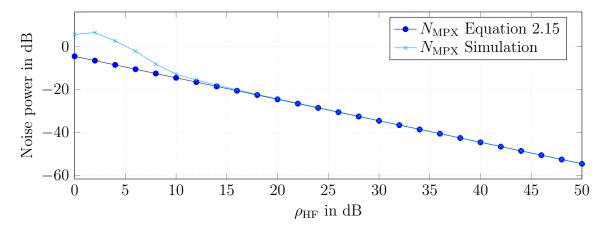

| 2.20 | MPX noise power in relation to FM signal-to-noise ratio                   | 44 |

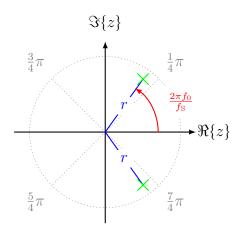

|      | Poles of discrete second-order IIR resonator inside $z$ -plane            | 46 |

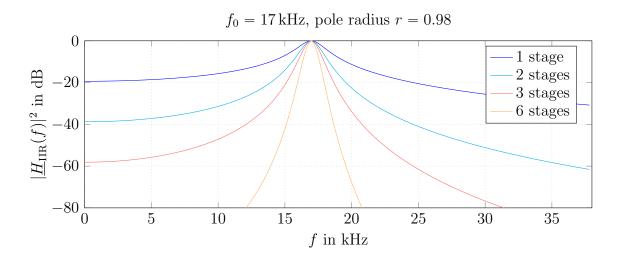

| 2.22 | Frequency response of cascaded IIR two-pole resonator                     | 47 |

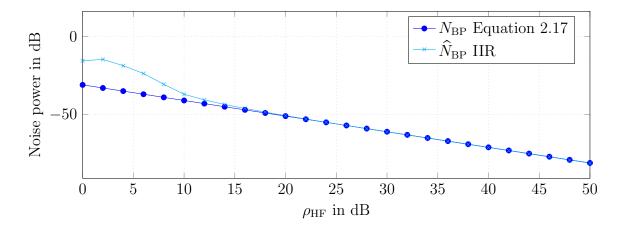

| 2.23 | Noise power estimation performance using a six-stage IIR resonator        | 48 |

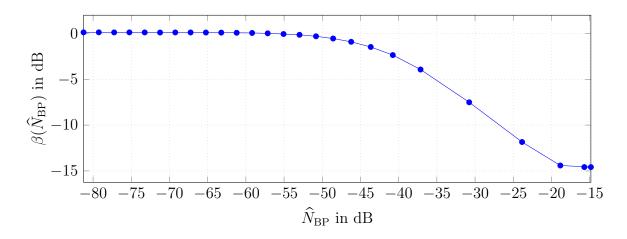

| 2.24 | Noise power correction fuction                                            | 49 |

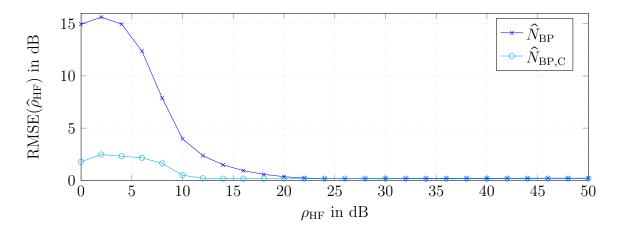

| 2.25 | Root-mean-squared error of FM signal-to-noise estimator output in dB      | 50 |

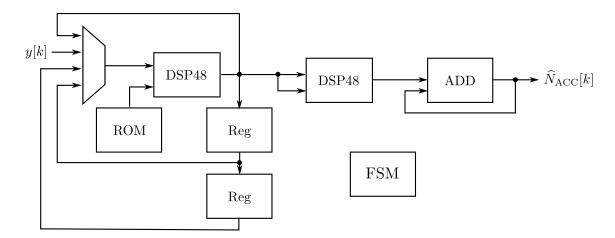

| 2.26 | Hardware implementation of an MPX-based noise estimator                   | 51 |

| 2.27 | BER approximation for coherent RDS demodulation against FM CNR            | 52 |

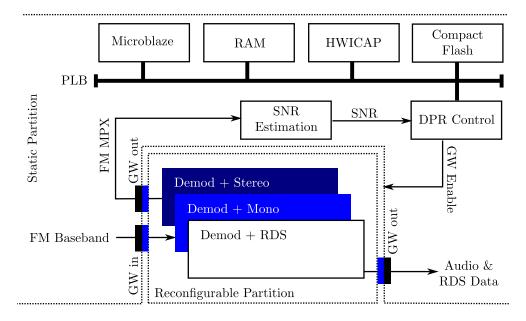

| 2.28 | Single-island reconfigurable FM receiver system design                    | 55 |

| 2.29 | FM receiver relative resource consumption of Xilinx XC5VSX50T FPGA.       | 56 |

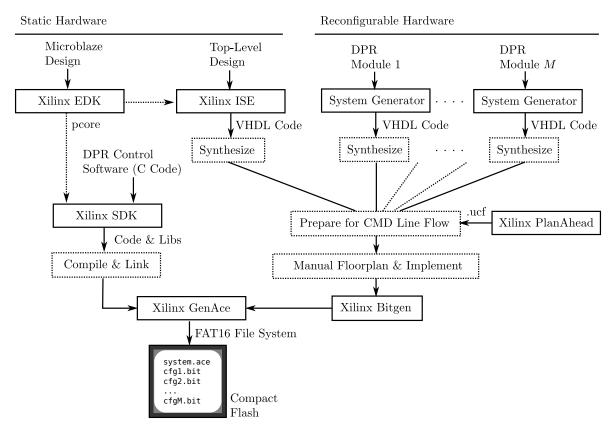

| 2.30 | DPR receiver system design tool-flow                                      | 57 |

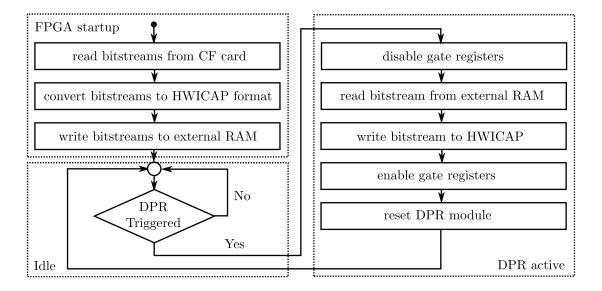

| 2.31 | Microblaze software bringup and reconfiguration loop flowchart            | 57 |

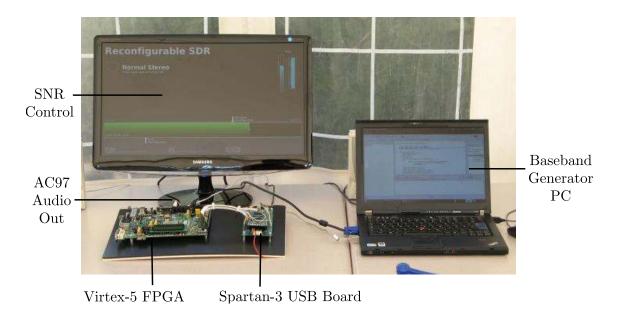

| 2.32 | Reconfigurable broadcast FM receiver demo system                          | 60                |

|------|---------------------------------------------------------------------------|-------------------|

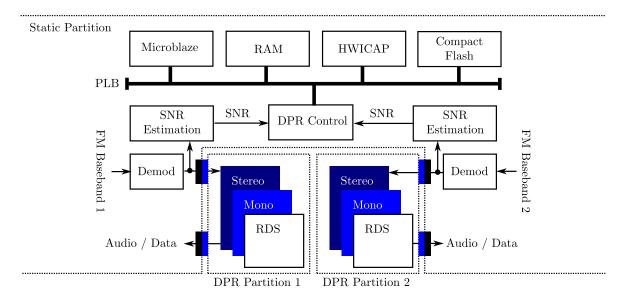

| 2.33 | Dual-partition reconfigurable FM receiver design                          | 61                |

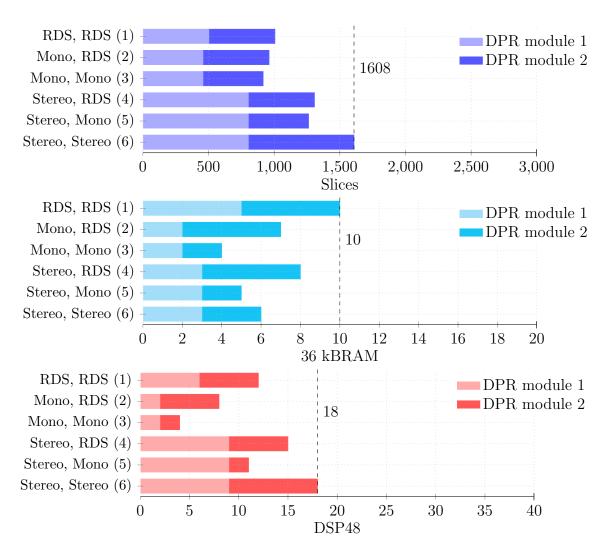

|      | MPX dual-decoder accumulated module resources on XC5VSX50T FPGA.          | 63                |

|      | MPX triple-decoder accumulated module resources on XC5VSX50T FPGA.        | 64                |

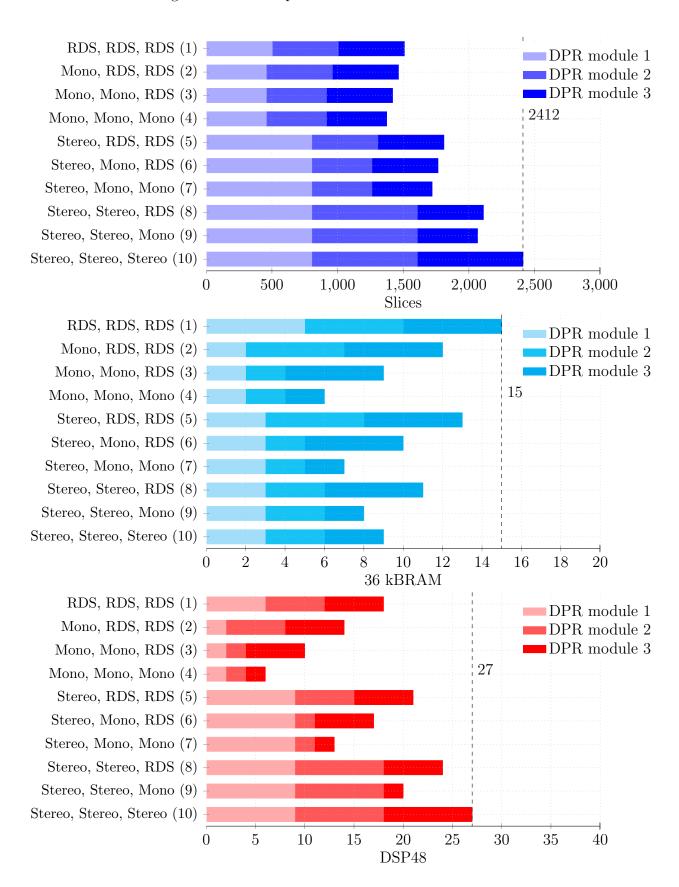

|      | Dual resource-sharing reconfigurable system design                        | 65                |

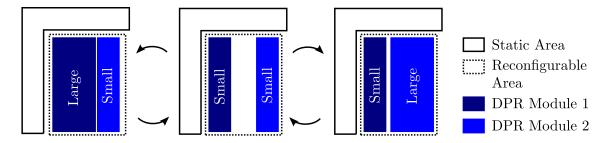

|      | Dual resource-sharing reconfigurable FM receiver system design            | 66                |

|      | Dual resource-sharing reconfigurable system design                        | 68                |

|      | Dual resource-sharing reconfigurable system design                        | 69                |

|      | FPGA floorplan showing routing leakage for adjacent partitions            | 70                |

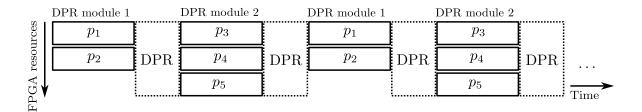

| 3.1  | Concurrent execution of processing elements in traditional designs        | 72                |

| 3.2  | Trading FPGA resources against time using cyclic DPR                      | 72                |

| 3.3  | Sequential chain of processing elements                                   | 75                |

| 3.4  | Cyclic module reconfiguration flow graph                                  | 76                |

| 3.5  | Sequential chain of DPR modules                                           | 77                |

| 3.6  | Cyclic execution flow-graph of DPR modules with throughput annotation.    | 78                |

| 3.7  | Module execution timing diagram and DPR processing delay                  | 79                |

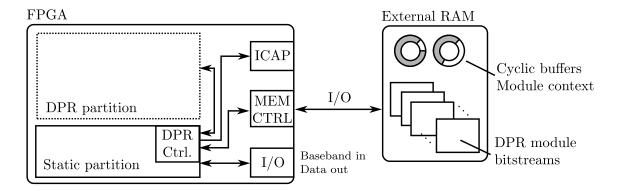

| 3.8  | Single-island FPGA reconfiguration hardware model                         | 81                |

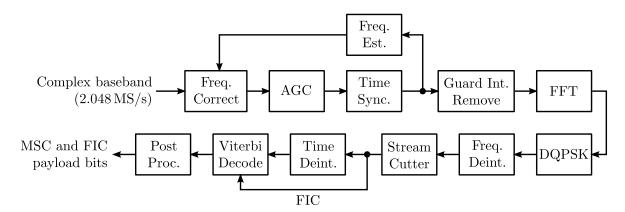

| 3.9  | Memory access pattern during DPR module processing                        | 82                |

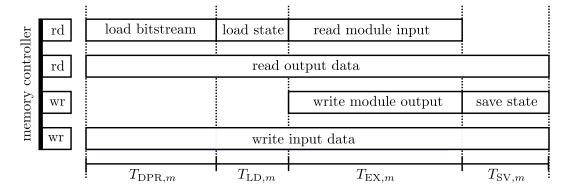

| 3.10 | Framing structure of DAB baseband stream                                  | 84                |

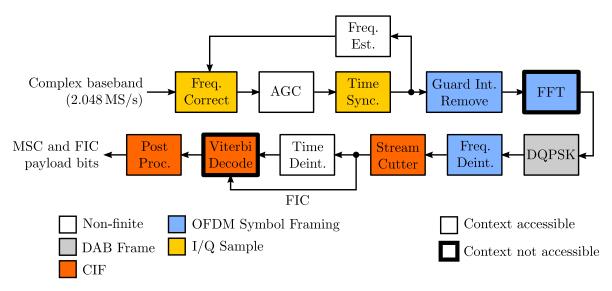

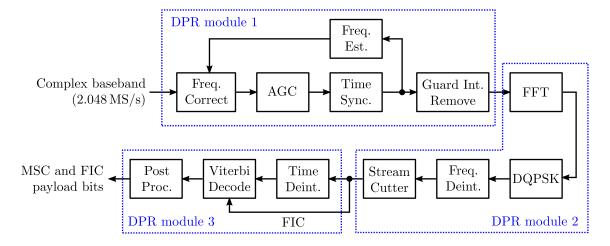

|      | DAB receiver processing element chain                                     | 85                |

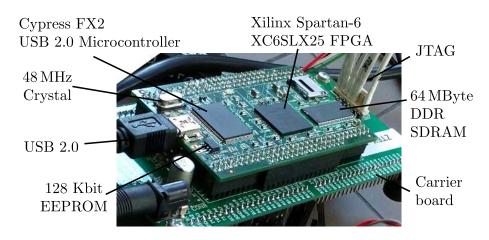

|      | ZTEX USB-FPGA-Module 1.11c with Xilinx Spartan-6 LX25                     | 86                |

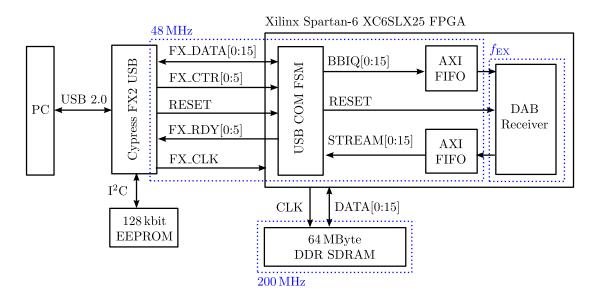

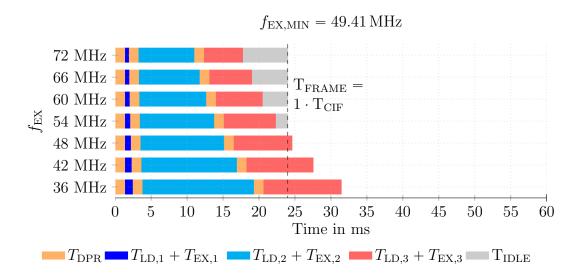

|      | DAB receiver system architecture on ZTEX FPGA platform                    | 87                |

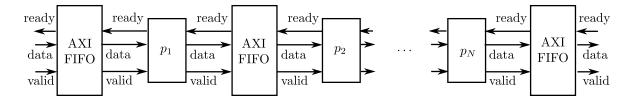

|      | DAB receiver PE synchronization using AXI streaming FIFOs                 | 88                |

|      | Annotated DAB chain graph with different context lifespans                | 91                |

|      | DAB chain partitioning into three DPR module                              | 92                |

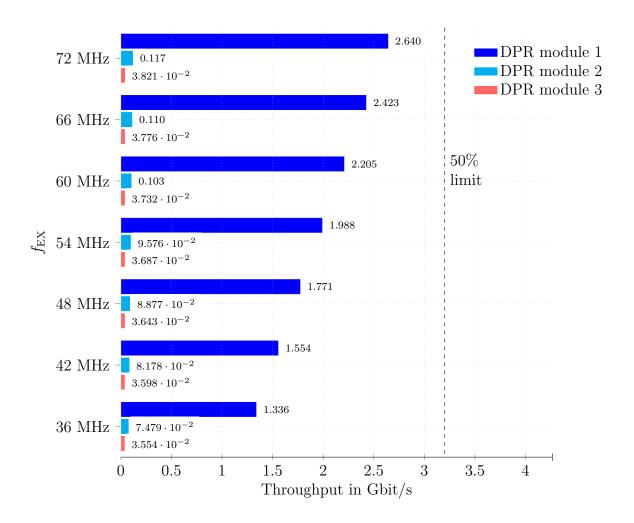

|      | Peak memory throughput during DPR module execution                        | 96                |

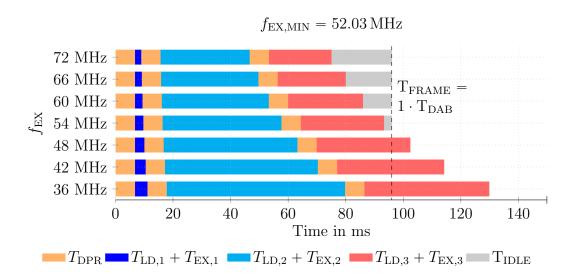

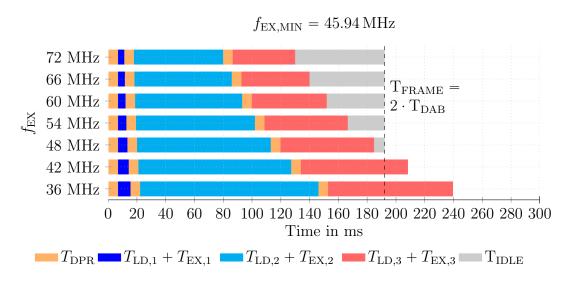

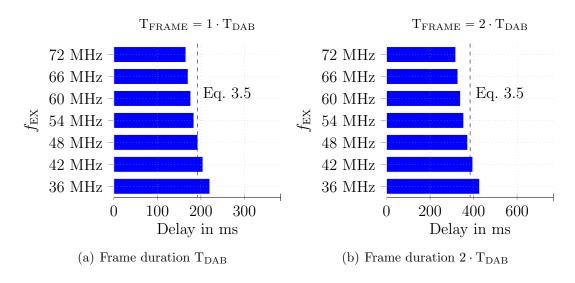

|      | Cycle time for DAB frame-based execution with 20 MHz ICAP                 | 98                |

|      | Cycle time using a duration of two DAB frames with 20 MHz ICAP            | 98                |

|      | Latency for DAB frame-based execution with 20 MHz ICAP                    | 99                |

|      | v                                                                         | 100               |

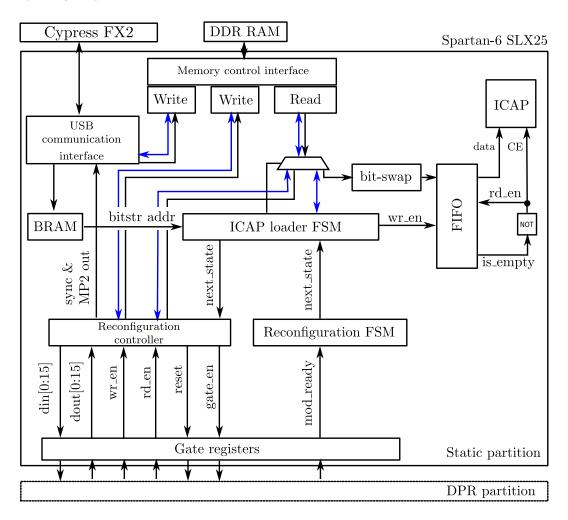

|      | Cyclic DPR system and DAB receiver signal and control flow                |                   |

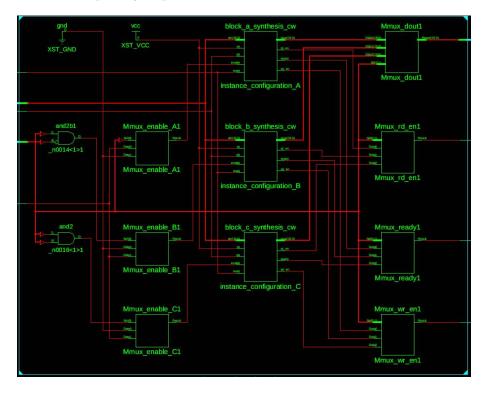

|      | Screenshot of the RTL simulation model for DAB receiver modules           |                   |

|      | Single-island test system for Spartan-6 FPGA reconfiguration              |                   |

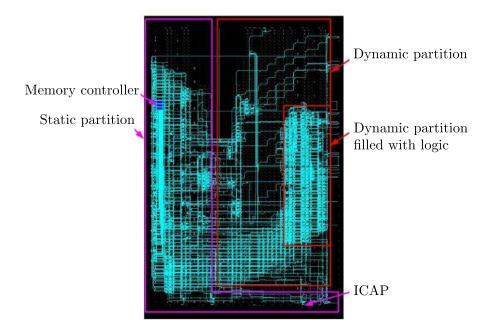

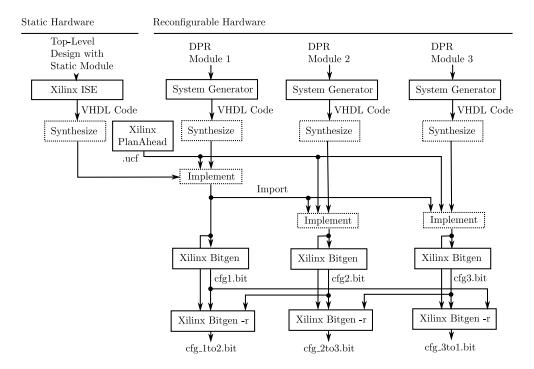

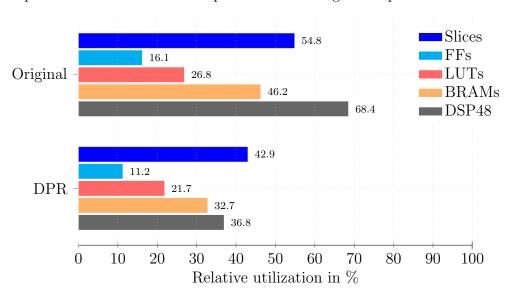

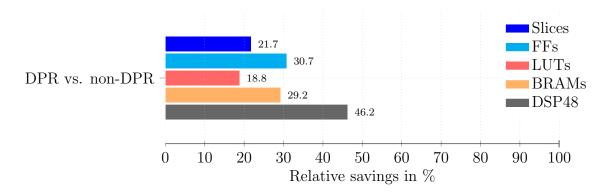

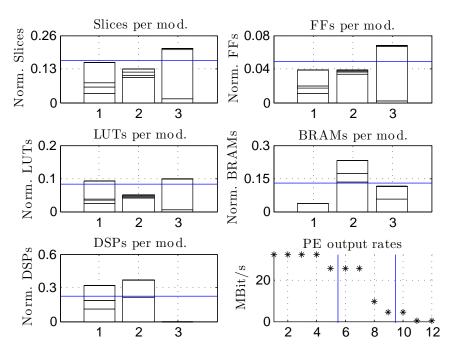

|      | <u> </u>                                                                  | 106               |

|      | <u>*</u>                                                                  | 107               |

|      | 0 0 1                                                                     | 108               |

|      | v i                                                                       | 111<br>110        |

|      | Signal flow-graph of a DVB-T2 receiver chain and DPR module partitioning. |                   |

|      | v e                                                                       | 113               |

|      | · ·                                                                       | $\frac{118}{120}$ |

|      |                                                                           | 120               |

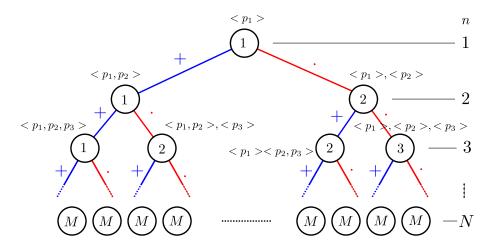

| 4.1  | v i i                                                                     | 124               |

| 4.2  |                                                                           | 131               |

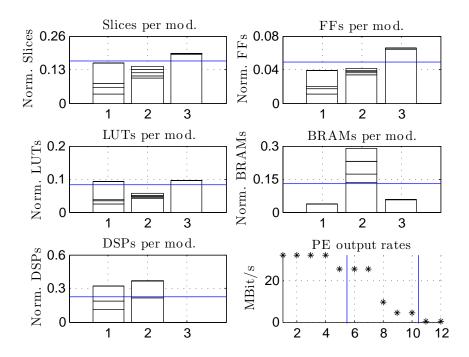

| 4.3  | Non-weighted resource partitioning of PEs favoring slices only            |                   |

| 4.4  | Non-weighted resource partitioning of PEs favoring BRAMs only             | 133               |

# **List of Tables**

| 1.1  | Xilinx Virtex FPGA configuration interface parameters                             | 4   |

|------|-----------------------------------------------------------------------------------|-----|

| 1.2  | European VHF frequency bands according to ITU-R 432-7                             | 10  |

| 2.1  | Overview of possible receiver configurations                                      | 23  |

| 2.2  | Receiver sampling rates at 36 MHz FPGA clock frequency                            | 24  |

| 2.3  | FM multiplex signal filter design parameters                                      | 28  |

| 2.4  | FM receiver resource consumption on Xilinx XC3SD3400A FPGA                        | 37  |

| 2.5  | SNR operation thresholds for different FM receiver module configurations.         | 53  |

| 2.6  | FM receiver resource consumption on Xilinx XC5VSX50T FPGA                         | 55  |

| 2.7  | Reconfiguration performance with HWICAP at PLB without DMA                        | 58  |

| 2.8  | Reconfiguration time estimates for single-island DPR partition                    | 59  |

| 2.9  | Resource consumption of single-island DPR receiver                                | 59  |

| 2.10 | Multi-island receiver resource requirements                                       | 61  |

| 2.11 | MPX accumulated module resources for resource-sharing implementation.             | 66  |

| 3.1  | Cyclic DPR module-related task durations according to Popp and Feilen.            | 77  |

| 3.2  | Hardware-related system model parameters                                          | 81  |

| 3.3  | DPR module implementation-related parameters                                      | 81  |

| 3.4  | Duration of the different DAB framing units                                       | 85  |

| 3.5  | DAB receiver processing elements description                                      | 86  |

| 3.6  | Xilinx implementation options for 2048-point FFT on Spartan-6 FPGA                | 88  |

| 3.7  | Xilinx implementation options for Viterbi decoder on Spartan-6 FPGA .             | 89  |

| 3.8  | Resource utilization and data throughput of DAB receiver PEs                      | 90  |

| 3.9  | DAB receiver resource utilization on ZTEX module 1.11c                            | 90  |

| 3.10 | DPR module resource utilization and I/O throughput                                | 93  |

|      | Number of cycles for the initialization and execution of the DPR modules.         | 95  |

|      |                                                                                   | 107 |

|      | -                                                                                 | 110 |

|      | V I                                                                               | 111 |

|      | 1                                                                                 | 113 |

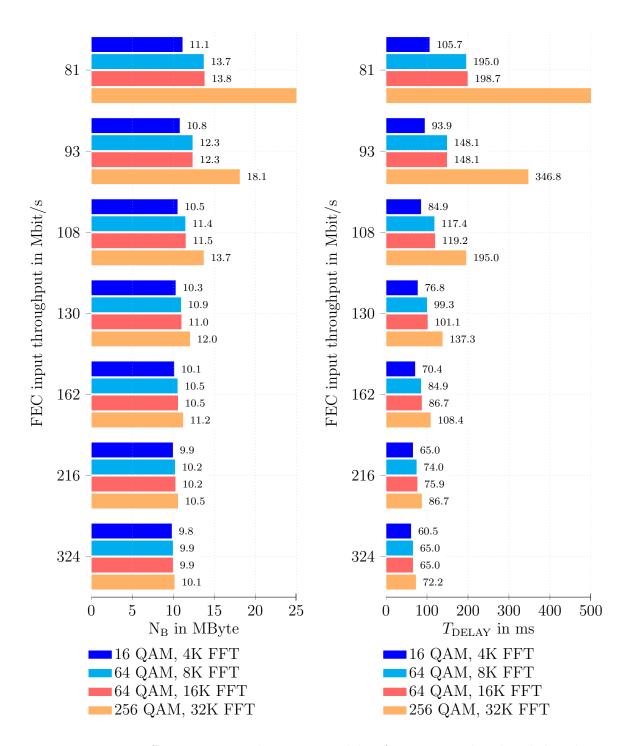

|      | Ü 111                                                                             | 114 |

| 3.17 | Minimum cycle times for $T_{\rm EX,FEC}=800\mu s$ and $T_{\rm EX,DEM,1k}=25\mu s$ | 117 |

| 4.1  | Resources and output data rates of the receiver PEs and accumulated               |     |

|      | resources of the balanced DPR modules                                             | 130 |

"Papa, wenn Deine Arbeit fertig ist, feiern wir ein Fest."

— Julius - 2015

# 1 Introduction

Increasing computational demands, stricter power constraints for mobile operation and ambitions to reduce the chip count put field-programmable gate arrays (FPGAs) in direct competition with application-specific integrated circuits (ASICs). For the development of modern receivers for digital broadcasting, cost-effective FPGA-based implementations with minimum resource utilization are of concern. Dynamic partial reconfiguration (DPR) of FPGAs provides additional degrees of freedom for the optimization of a design in terms of resources. In how far partial reconfiguration is feasible for the optimization of a particular receiver implementation and to what extend it imposes implications on the FPGA system design is within the scope of the outlined research. Considering the derived implications, design strategies for the realization of resource-economic receivers for digital broadcasting will be proposed and analyzed.

Explanations given in the following chapters require an understanding of FPGA architectures and properties of broadcast receivers. Knowledge required to comprehend the concepts to be presented will be summarized further on.

# 1.1 Field-Programmable Gate Arrays

Field-programmable gate arrays are configurable integrated circuits for implementing logical functions. The internal structure of an FPGA varies among manufacturers and by device family. Technology-wise, different FPGA memory cell types exist, such as flash-, anti-fuse- and static random-access memory (SRAM)-based memory cell designs. In terms of configurability and logic density, SRAM-based FPGAs are the most versatile choice for many applications. At the time of writing, the two leading manufacturers of SRAM-based FPGAs are Xilinx and Altera with a combined market share of almost 90 %, cf. [Joh11]. The company Xilinx Inc. was founded by Ross Freeman and Bernard Vonderschmitt in 1984, based on their patented "Logic Cell Array" technology [Gra04]. Support for dynamic partial reconfiguration of Xilinx FPGAs has been available since 2003 [BBHN04], whereas Altera made DPR officially available with the introduction of the Stratix V devices in 2013 [Rhe13]. A detailed report about modern FPGA architectures and technologies of various vendors is provided by Kuon et al. in [KTR08].

Due to the better tool support at the time of writing, the hardware-specific analysis in this work has been accomplished with Xilinx FPGAs. The tools that have been used for system design, synthesis and software development are Xilinx Integrated Synthesis Environment (ISE), Xilinx Software Development Kit (SDK), Xilinx Embedded Development Kit (EDK) and the latest Xilinx Vivado design suite. Signal processing systems have been designed using Xilinx System Generator together with Matlab/Simulink from Mathworks.

#### **FPGA Application Layer**

FPGAs provide different resources, such as lookup tables (LUTs), flip-flops (FFs), shift registers, hardware multipliers denoted as digital signal processing (DSP) units or DSP48 units, block random access memory (BRAM) and other components. Residing in the application layer, these resources can be configured by the user to perform certain tasks. Programmable internal routing networks in the same layer allow to interconnect the mentioned FPGA components and link them to external input and output (I/O) pins. For physical interaction with these pins, configurable I/O Blocks (IOBs) and special high-speed interfaces such as multi-gigabit serial I/O transceivers are provided.

Figure 1.1: FPGA application layer resource floorplan.

Figure 1.1 shows a typical resource floorplan of an SRAM-based FPGA. An FPGA-specific set of LUTs and FFs is denoted as configurable logic block (CLB). The CLB resources are interfaced to the FPGA wire network using programmable switching matrices (PSM). In addition to this wire network, FPGAs comprise user-programmable clock signal trees to supply internal sequential logic elements. A clock signal can be distributed within a certain clock region, either directly driven by an external clock input pin or by a programmable phase-locked loop (PLL) from a digital clock manager (DCM). Once configured, the CLB slices, hardware multipliers, dedicated memory blocks and wiring resources resemble the user-defined logic functionality implemented by the FPGA.

#### **FPGA Configuration Layer**

The configuration and memory state of the application layer is controlled by the *configuration layer* of the FPGA. Once the configuration is accomplished, the FPGA application layer will resemble the user-defined digital circuity. Xilinx FPGAs are equipped with a selectable microprocessor access port (SelectMAP) and a Joint Test Action Group (JTAG) configuration access port accessible via external I/O. Additionally, modern FPGAs provide a serial peripheral interface (SPI) and a byte peripheral interface (BPI). Data written to these ports is forwarded to a configuration packet processor (CPP), which interprets

the supplied bits and provides read and write access to the frame data register (FDR) and control registers. In modern Xilinx FPGAs, an internal configuration access port (ICAP) gives access to the CPP from inside the application layer, on Altera FPGAs this counterpart is called partial reconfiguration control block (PRCB). By writing to this controller, FPGA self-reconfiguration can be performed, i.e. triggered internally by user-defined logic operations.

Figure 1.2: FPGA configuration layer and application layer tiling.

In Figure 1.2, the configuration layer is schematically sketched. It is partitioned into multiple configuration rows, on modern devices sometimes split into a top half and into a bottom half. Each configuration row contains multiple configuration columns for the different resource elements, such as CLBs, DSP48 slices, BRAMs or IOBs. A configuration column holds an integer number of configuration frames, which are the smallest addressable storage units in an SRAM-based Xilinx FPGA. A configuration frame is composed of multiple configuration words and the number of bits per configuration frame is obtained by multiplying the configuration interface width by the configuration word count. It is possible that the data of one configuration frame may affect multiple resource elements in the application layer, e.g. the wiring of multiple CLBs. Within the application layer domain, a configuration datastream can be supplied through the ICAP to the CPP. Upon successful synchronization, the CPP will forward the configuration frame information embedded into this stream to the input FDR. After a complete frame has been written to the FDR, the register contents are transferred to the FPGA configuration memory and the application layer changes will be applied. For consistency checking and comparison, it is possible to read back configuration frames through the output FDR.

Table 1.1 depicts the configuration interface parameters for state-of-the-art Xilinx Virtex FPGAs. Since the parameters are spread across different documents, individual references have been provided. Xilinx undiscloses the number of frames per column for newer FPGAs, wherefore they have not been provided in this work for Virtex-6 and Virtex-7 devices. Configuration interface widths of 32 bits per configuration word are

| Xilinx FPGA Generation | #Cfg.Words<br>Cfg.Frame | $\frac{\text{\#CLBs}}{\text{Cfg.Column}}$ | #CLB/DSP/BRAM Cfg.Frames<br>Cfg.Column |

|------------------------|-------------------------|-------------------------------------------|----------------------------------------|

| Virtex-7               | 101 [Xil15a]            | 50 [Xil14]                                | N/A                                    |

| Virtex-6               | 81 [Xil15b]             | 40 [Xil14]                                | N/A                                    |

| Virtex-5               | 41 [Xil12d]             | 20 [Xil12c]                               | 36, 28, 30 [Xil12d]                    |

| Virtex-4               | 41 [Xil09b]             | 16 [Xil12c]                               | 22, 21, 20 [Xil08]                     |

Table 1.1: Xilinx Virtex FPGA configuration interface parameters.

used across all Virtex devices, together with a maximum configuration clock frequency of 100 MHz. Thus, read and write access to the CPP via the ICAP can be performed with a maximum rate of 3.2 Gbit/s. Note that the number of frames per column for BRAM resources refers to the interconnect configuration only, but not to the BRAM content, which requires a larger number of configuration frames [Xil12d]. It can be observed that, from one FPGA generation to the next, the configuration frame size increases in terms of words per frame, leading to an increased minimum configuration period.

#### **FPGA Configuration Bitstream**

The configuration datastream presented to the internal or external configuration interfaces is typically referred to as bitstream. In addition to command information it contains the configuration data with header information, such as row and column addresses for partial writes. In Xilinx FPGAs, synchronization to the bitstream is accomplished by the 32 bit sync-word 0xAA995566, where 0x indicates hexadecimal notation. The bitstream content is FPGA-specific and documented in the respective FPGA configuration user guide. Bitstreams with configuration data affecting only a subset of configuration frames are called partial bitstreams. Error detection and intellectual property protection can be employed by cyclic redundancy checksum (CRC) comparison commands and symmetric bitstream encryption according to the advanced encryption standard (AES). Further information on the bitstream format and other hardware-related details about the configuration architecture can be found in the respective FPGA configuration user guide.

Replacing specific portions in the FPGA application layer by writing partial bitstreams to the ICAP will be referred to as partial self-reconfiguration in this thesis. Achieving this without disturbing other application layer functions will be denoted as dynamic partial self-reconfiguration. Subsequently, the possibilities and constraints of this reconfiguration approach will be explained.

# 1.1.1 Dynamic Partial Self-Reconfiguration of FPGAs

Dynamic partial self-reconfiguration describes the ability of an FPGA to self-reconfigure an internal application layer partition, without interrupting the surrounding logic of this partition. A precise specification of the terming can be introduced as:

• Dynamic describes the ability to configure the FPGA (or portions of it) while a subset of logic resources and clock networks of the device remain operational. Typically, the continuously operating region is referred to as the static partition.

- Partial describes the ability to change parts of the FPGA application layer by updating a subset of configuration frames. The area in which one or multiple adjacent configuration columns and rows are changed is denoted as reconfigurable partition and is typically of rectangular shape in the resource floorplan.

- Self-Reconfiguration means that the FPGA provides an internal port to access the configuration layer from within the application layer. In case of Xilinx FPGAs, this port is called ICAP.

Temporal resource-multiplexing of FPGA resources is a major motivation for using partial FPGA reconfiguration, because re-using the FPGA resources for different features means being able to adapt to certain situations. A region of contiguous reconfigurable resources will herein after be referred to as reconfigurable partition or *DPR partition*. Typically, it is interfaced to the static partition using dedicated resource elements, further denoted as bus macros or *proxy logic*. Application subsets or features, specifically designed to be instantiated and to operate inside a DPR partition, will furthermore be referred to as *DPR module*.

Figure 1.3: Schematic diagram of a partially-reconfigurable FPGA system.

In Figure 1.3 a conceptual DPR system is sketched with two DPR partitions A and B of equal size and multiple DPR modules. Writing the partial bitstream of a DPR module to the reconfiguration interface updates one of the specific DPR partitions as coded in the bitstream, i.e. the partition the DPR module has been specifically implemented for.

Since it took about 20 years for DPR to grow from a research topic into a state-of-theart design methodology, it is necessary to introduce the research landmarks that lead to the concepts employed today. Subsequently, the current approaches will be put into context by a brief historical review.

#### A Historical Abstract of Dynamic Partial Reconfiguration

Conceptual ideas on dynamic FPGA reconfiguration appeared shortly after the first generation of FPGA devices emerged on the market in 1986. For example, in 1989, Gray and Kean announced "A new paradigm for computation" by the introduction of configurable array logic, referred to as CAL. The authors emblaze the possibilities of the structure in different case studies and emphasize the benefit to "restructure the hardware for a given algorithm" [GK89]. A few years later, Thomas C. Waugh presented SPLASH[Wau91], a reconfigurable linear logic array which allowed run-time reconfiguration of 32 individual Xilinx XC3090 FPGAs. These FPGAs did not provide self-reconfiguration, but reconfiguration was triggered externally.

#### 1 Introduction

A landmark coining the term dynamic reconfiguration was published in 1994 by Lysaght and J. Dunlop called "Dynamic Reconfiguration of FPGAs", where the authors describe the possibilities of run-time reconfiguration with state-of the art devices [LD94b]. At about the same time, the first adaptive signal processing implementation that made use of dynamic reconfiguration was presented in the work of Patrick Lysaght and Hugh Dick [LD94a]. In their publication, an implementation of a short-term autocorrelation function on a Xilinx 4005 and an Atmel AT6005 with externally-triggered reconfiguration is outlined. Furthermore, the authors compare the system complexity with a DSP system and conclude that, in terms of complexity, the autocorrelation FPGA setup was "not competitive today", and they predict that a "new hybrid device" with a microprocessor integrated into an FPGA would probably make the design competitive to a DSP.

In 1994 DeHon took the idea of time-multiplexed programmable hardware one step further and presented the concept of the dynamically programmable gate array (DPGA). The idea behind such a device is to have multiple logic configuration sets, so called "contexts", stored in an on-chip memory. The DPGA allows to quickly switch between the different contexts, and thus hardware functionality, at runtime. All context information is provided on load by a single configuration bitstream. The paper describes the benefits of "rapid reconfiguration" and mentions that DPGA array elements could be "reused in time". A first DPGA hardware prototype has been presented by Tau, Chen, Eslick and Brown at the Artificial Intelligence Laboratory of the Massachusetts Institute of Technology in 1995 (cf. [TCEB95]). The functionality and the routing of the gate array could be altered within a single clock cycle, thereby changing the functionality of a 4-input LUT together with a crossbar configuration. DeHon supervised this project and presented an analysis on the utilization of DPGAs in "DPGA Utilization and Application" one year later (cf. [DeH96]). As far as commercially available DPGAs are concerned, in 2008 Tabula, a company founded 2003 by Steve Teig, released the ABAX2 P1 DPGA called a 3PLD.

The temporal multiplexing of FPGA logic elements to subsequently execute blocks of a continuous processing pipeline has first been presented by Villasenor et al. in [VJS95]. The authors used a configurable logic array (CLAy31) and an erasable programmable read-only memory (EPROM) holding the configuration bitstreams, which were loaded by an external finite-state machine (FSM) on an Altera EP600 EPLD. Partial reconfiguration has not been used but instead the entire configuration of the FPGA has been swapped in a round-robin fashion. A similar idea for temporal multiplexing of processing blocks is revisited in Chapter 3 of this thesis.

Another landmark in reconfigurable computing is the work of Wirthlin and Hutchings, who in 1995 presented their Dynamic Instruction Set Computer, called DISC (cf. [WH95]), one of the first implementations using partial reconfiguration with the aim to reduce the reconfiguration time. DISC resembles a normal processor with the benefit of a run-time reconfigurable instruction set. A static "global controller" inside the National Semiconductor CLAy31 FPGA contains the necessary CPU components, such as status, data and address registers, program counter and instruction register. The column routing resources are used as shared control, data and address lines for the different reconfigurable modules. The authors quantify the reconfiguration overhead between 16 % and 71 % of the total operating time. About two years later, Wirthlin and Hutchings presented a metric to estimate the functional density of static and dynamic FPGA designs in [WH97]. The equations lead to the conclusion that, in general,

functional density reduces along with an increase in reconfiguration time. The authors propose to use partial reconfiguration of FPGAs to reduce the configuration time and thus increase the functional density of the system. Provided that the reconfigurable partition is small, the authors show that for a system with a high number of execution cycles per reconfigurable module, the functional density of a reconfigurable system exceeds the functional density of a static system. Another important work of the same decade is the time-multiplexed Artificial Neural Network system from Elderedge and Hutchings, presented 1996 (cf. [EH94]), where the logic of a Xilinx XC3090 FPGA is cyclically reconfigured between three distinct configurations.

Given the vital research on partial reconfiguration in the 1990s, Trimberger et al. proposed "the time multiplexed FPGA" in 1997 (cf. [TCJW97]). The work of Trimberger builds on top of the ideas of R. Ong, who filed a patent in 1995 for the design of an FPGA with DPGA functionality. The authors propose a new architecture based on a Xilinx XC4000E FPGA and suggest three modes of operation:

- 1. Logic-Engine Mode: Virtually enlarge the combinational logic by re-using, i.e. re-configuring, the FPGA LUTs within a "microcycle" or "user clock cycle". As the duration of a microcycle depends on the complexity of the time-multiplexed circuit, it is equal to one or multiple FPGA clock cycles. Trimberger suggests using flip-flops as intermediate buffers and also allow to feed-forward combinational outputs.

- 2. **Time-Share Mode:** Multiple LUT and Flip-flop resources can be reconfigured by a user-defined trigger. In contrast to (1), one reconfigurable module is executed for multiple FPGA clock cycles and then replaced by another module using dynamic reconfiguration.

- 3. Static Mode: The FPGA logic will not be affected by reconfiguration.

The approaches presented in this thesis require the FPGA to operate in time-share mode, where the configuration layer is re-written to update a subset of FPGA resources. Additionally, dynamic self-reconfigurability of the device is required, such that a continuously operating static FPGA partition can perform an update of a DPR partition by writing to the configuration layer controller. Although the first Xilinx Virtex devices supported partial reconfiguration, they did not provide an internal configuration controller. Hence, self-reconfiguration by internal wiring was not possible. With the introduction of the ICAP with the Xilinx Virtex-II Pro FPGA family, dynamic partial self-reconfiguration became available. Since then, several DPR architectures and applications for the Virtex-II Pro family have emerged. However, with one configuration frame spanning all primitives within a full device column, the Virtex-II FPGA application layer fabric did not allow a vertical, i.e. CLB row-wise, area partitioning, which was disadvantageous in terms of routing and area usage. With the introduction of configuration rows with a height of 16 CLBs per configuration column, Virtex-4 FPGAs abrogated this issue, thus enabling a fine-grained FPGA partitioning as presented in [LBM+06]. The improved tiling architecture of modern Xilinx FPGAs allow even more complex reconfigurable system designs with multiple DPR islands.

Today, improved vendor tool support makes the design of DPR systems much simpler as compared to the time when DPR was first introduced (cf. [Xil14]). However, designing

#### 1 Introduction

DPR systems is still challenging and requires to follow certain design steps and adhere to specific design rules. The process to create partially configurable systems will be referred to as *DPR system design flow*. Two popular flows will be subsequently explained: the difference-based flow and the partition-based flow.

#### 1.1.2 Difference-Based DPR System Design Flow

The difference-based design flow is described in [Xil07] and was originally referred to as "Small-bit Manipulation Flow". Possible use cases are the manipulation of BRAM contents, LUT equations or changing I/O standards. Albeit intended to be used for minor application-layer modifications, the flow has also been used for large-scale design modifications (cf. [KBT08] and [MNH+11a]). A difference-based bitstream can be generated using the Xilinx Bitgen command line tool with the option -r. The tool compares the bitstream of a module A with the native circuit description (NCD) of the destination module B and generates a bitstream with the differences of A and B. The resulting bitstream will contain the configuration layer modifications for A that lead to an application layer realization of B. Since generating a differential bitstream for a new configuration requires the knowledge of the previous configuration, the difference-based flow is disadvantageous for designs with more than two DPR modules as subsequently depicted.

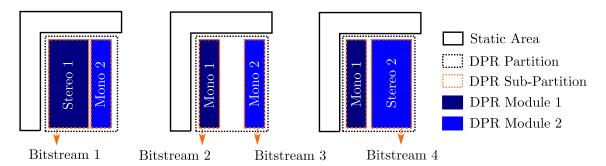

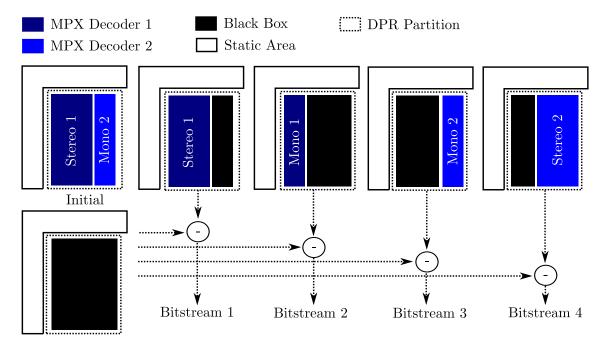

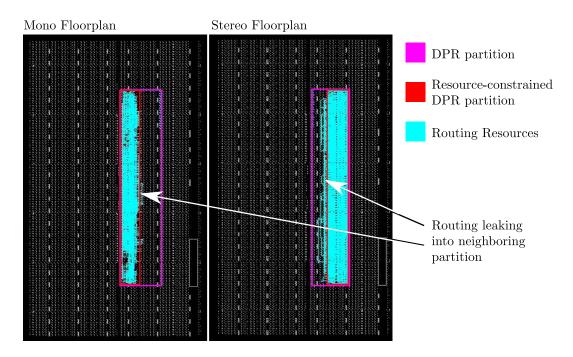

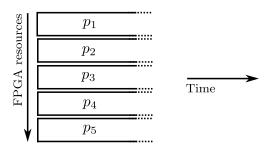

Figure 1.4: Difference-based reconfiguration flow with four DPR modules.

The graph in Figure 1.4 shows the differential bitstream configuration flow. Each edge of the graph represents a partial bitstream and the four DPR modules are represented by the nodes of the graph. Being able to switch from one module to any other module requires twelve independent differential bitstreams, and for a system with M DPR modules M(M-1) partial bitstreams would be required. By using blanking bitstreams this number can be reduced to 2M, i.e. one bitstream for loading and one for deletion, at the cost of one additional FPGA configuration cycle. Additionally, when using difference-based reconfiguration, changes in the signal routing might lead to errors in the static

partition or other reconfigurable partitions. This effect can be mitigated by the use of blocker macros, which feign that all routing resources outside the DPR partition have been occupied, thus forcing the routing algorithm to use interconnects inside the DPR partition only. At the time of writing, there is no vendor tool support for restricting the routing to certain areas. However, third party tools exist which make use of the Xilinx design language (XDL) for blocker macro generation [BKT11].

A rather modern design flow supported by Xilinx is the partition-based design flow, where routing and implementation of the DPR partitions can be performed independently as subsequently outlined.

#### 1.1.3 Partition-Based DPR System Design Flow

The partition-based flow is the DPR system design flow recommended by Xilinx and is documented in [Xil12c] for Xilinx ISE designs and in [Xil14] for designs created with Xilinx Vivado. It replaces the older module-based reconfiguration flow, which sometimes is referred to as early access partial reconfiguration (EAPR) flow, in relation to the naming of the respective Xilinx user guide.

Figure 1.5: Partition pins and proxy logic locations for partition-based DPR systems.

Using the partition-based design flow requires the definition of DPR partition boundaries, either by using tools like Xilinx PlanAhead or by manual definition of area constraints. The reconfigurable partition is allowed to enclose slices, block RAM and DSP units. Resources like DCMs, PLLs and I/O resources must reside in the static partition. For every signal, a LUT in route-through mode is used as proxy logic providing a partition pin to connect the static and dynamic regions (cf. Figure 1.5). These partition pins are inserted automatically by the tool chain but can also be specified manually using location constraints. Since the proxy logic is effectively a part of the static logic, it can be placed anywhere inside the reconfigurable region. In partition-based designs, LUT elements are used as proxy logic, providing unidirectional asynchronous communication between the static and dynamic partitions. Resource-wise one LUT is allocated per transition wire and signal direction. The locations of the proxy LUTs are fixed within the area of a DPR partition and must therefore be known at implementation time of each DPR module. During reconfiguration, the signals inside the DPR partition are undefined. Therefore, connections to the static parts of the design should be decoupled to avoid glitching input signals. When using the partition-based design flow, decoupling can be achieved using enable flip-flops inside the static region as recommended by Xilinx in [Xil12c]. Since registering also reduces the combinational path delay, the timing performance of the circuity can be improved at the cost of a unit delay.

#### 1 Introduction

Exploiting the possibilities of DPR for digital broadcast receivers is part of the analysis presented in the subsequent chapters and will therefore be explained in further detail.

# 1.2 Digital Broadcasting Receivers

According to the Collins English dictionary, an (analog) radio receiver is defined as "an apparatus that receives incoming modulated radio waves and converts them into sound" (cf. [Col11]). Instead of converting radio waves into sound, a digital receiver converts radio waves into information. Improvements in encoding and decoding of this information are the main driver for the introduction of new terrestrial, satellite and cable-wire broadcasting standards deployed world-wide. Efficient coding usually means low-bitrate high-quality audio and video source-coding as well as near Shannon limit channel coding (cf. [ESL04]).

The way the information is coded is typically specified by an expert group and the specification the group members agree on are commonly referred to as *standard*. Next, the most important broadcasting standards related to this work will be introduced.

#### 1.2.1 Selected Standards

The analysis presented in this work requires an introduction to the European terrestrial broadcasting standards terrestrial digital video broadcasting (DVB-T), digital audio broadcasting (DAB) and stereophonic analog frequency modulation (FM) including the radio data system (RDS). In Europe, these standards are operated mainly in the very high frequency (VHF) bands I to V according to ITU-R 432-7 (cf. [itu15]) as listed in Table 1.2.

| VHF Band | Start of Band      | End of Band       | Standard |

|----------|--------------------|-------------------|----------|

| I        | $47\mathrm{MHz}$   | $68\mathrm{MHz}$  | -        |

| II       | $87.5\mathrm{MHz}$ | $108\mathrm{MHz}$ | FM/RDS   |

| III      | $174\mathrm{MHz}$  | $230\mathrm{MHz}$ | DAB      |

| IV       | $470\mathrm{MHz}$  | $582\mathrm{MHz}$ | DVB-T    |

| V        | $582\mathrm{MHz}$  | $960\mathrm{MHz}$ | DVB-T    |

Table 1.2: European VHF frequency bands according to ITU-R 432-7.

For signal reception and physical layer decoding, each standard requires individual radio frequency (RF) hardware and baseband decoding chains. The baseband decoder can be implemented in hardware using FPGAs or ASICs or in software using Microprocessors. When implemented on an FPGA, dynamic partial reconfiguration can be utilized to reduce the resource consumption in comparison to static FPGA implementations, as derived further on in this work.

In order to classify the baseband decoder chains presented in the following chapters, important historical and technical cornerstones will be outlined in chronological order.

#### FM/RDS

After the ratification of the Copenhagen frequency plan in 1948 the first frequency-modulated audio broadcasts went on air in Europe. A few years later, the FM stereo-phonic multiplex (MUX) signal was standardized and enabled broadcasting of two independent audio channels. The desire to uniquely identify FM broadcasts, to transmit alternate frequency information and to carry traffic announcement signals lead to the development of RDS within the years 1975 and 1984 (cf. [Rds]). Later on, RDS was published as a standard by the International Electrotechnical Commission (IEC) in document 62106 Edition 3. The system will be explained in further detail in Chapter 2 in conjunction with an architecture for a reconfigurable FPGA-based FM receiver.

#### **DAB**

Research and development of the DAB system for the transmission of digital audio information dates back to the 1980s and was driven by several European research institutes, broadcasting companies and radio manufacturers within the EUREKA 147 project. First receiver system concepts based on orthogonal frequency division multiplexing (OFDM) were presented in 1989 by Floch et al. (cf. [LFHLC89]). Differential quadrature phaseshift keying (DQPSK) and punctured convolutional coding were proposed for DAB, allowing for efficient channel decoding using Viterbi's algorithm and channel equalization without dedicated channel estimation. Together with the invention of the MUSI-CAM audio codec presented in 1991 (cf. [DLU91]), the first generation DAB system was standardized in the early 1990s. In 2005, DAB+ emerged as next-generation radio system, using Reed-Solomon coding in concatenation with the convolutional code and high-efficiency advanced audio coding (HE-AAC) v2 for higher quality audio at lower bitrates. Nowadays, DAB and DAB+ are employed in several European countries as major digital technology for sound broadcasting. The system specification is published by the European Telecommunications Standards Institute (ETSI) in EN 300 401 [ets06]. The architecture of an FPGA-based DAB receiver for terrestrial reception in DAB mode I will be presented in Chapter 3 together with an approach to time-multiplex receiver components using partial reconfiguration of FPGAs.

#### **DVB-T**

In 1993, the Digital Video Broadcasting Group was formed by major European media interest groups to develop a new standard for digital video broadcasting (cf. [Dvb]). The standard for terrestrial video broadcasting (DVB-T) was ratified in 1997 and the first services went on air in Germany in 2002. Similar to DAB, DVB-T uses OFDM and convolutional coding. For transmit power efficiency reasons, coherent quadrature amplitude modulation (QAM) is used instead of DQPSK. Thus, in contrast to DAB, in DVB-T channel estimation and channel tracking are mandatory. In 2008, the successor DVB-T, called DVB-T2, was adopted by the ETSI in EN 302 755 [Ets08]. DVB-T2 promises to be 50 % more power efficient than DVB-T by using high-order QAM, fewer pilot signals and improved forward-error correction by concatenated low-density parity check code (LDPC) and Bose-Chaudhuri-Hocquenghem (BCH) codes. In terms of computational complexity, DVB-T2 is the most demanding terrestrial broadcasting standard. A proposal for the design of a reconfigurable FPGA-based DVB-T2 baseband decoder will be

outlined at the end of Chapter 3.

#### 1.2.2 Receiver Design and Properties

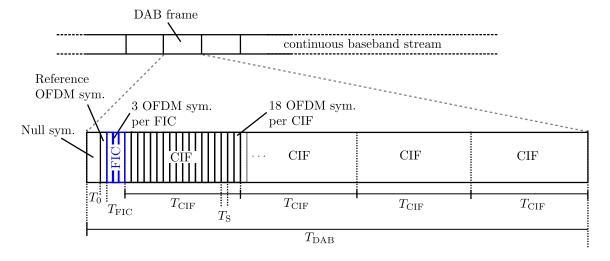

Spectral efficiency and the possibility to use low-complexity channel estimation and equalization routines have made OFDM the modulation scheme of choice for state-of-the-art digital terrestrial broadcasting. According to Speth et al. an OFDM receiver can be split into an inner and an outer part (cf. [SFFM99]). The inner receiver compensates for all signal impairments such as timing offsets, frequency offsets, sampling clock offsets and channel distortions and forwards the equalized carrier information to the outer receiver, where channel decoding is performed. Figure 1.6 shows a simplified signal flow-graph of an OFDM receiver including the inner and outer parts.

Figure 1.6: OFDM receiver signal flow graph.

The received signal is detected by the antenna and then down-converted in frequency and amplified in power using an RF frontend. Digitization of the frontend output signal is accomplished using an analog-to-digital converter (ADC) delivering a stream of quantized in-phase and quadrature values, referred to as *complex baseband signal*. The complex baseband signal is subsequently processed by a *baseband processing chain*, implemented on an FPGA and subject to optimization. At the output of the chain, the decoded bits are presented to a payload processor and forwarded to a sink for further processing. Although the OFDM chain shows the most important blocks for the decoding of various standards, each specific standard requires a tailored implementation.

The importance of the optimization of the baseband processing chain using DPR will be elaborated on in the forthcoming sections, whereas the design and optimization of other components, such as RF frontend, ADC or payload processor will not be concerned.

#### **Baseband Processing Chain**

The baseband processing chain is encircled by a blue dotted line in Figure 1.6. For simplicity reasons the diagram shows a feed-forward-oriented data flow, which hides the feedback structures of control loops typically used in receivers. The presence of feedback structures in block-wise executed receiver chains will be further investigated in Chapter 3.

At the input of the baseband chain, the time-domain synchronization stage corrects the frequency offset, the sampling rate offset and the temporal demodulation window offset. After the guard interval has been removed, the discrete Fourier transform (DFT) operation converts the signal into the frequency domain. The DFT is typically calculated using the computationally efficient fast Fourier transform (FFT) algorithm. If present, the pilot signals are extracted from the modulated carrier bins and subsequently used for channel estimation. Using simple zero-forcing or more advanced equalization methods, the impairments of the terrestrial broadcast channel are equalized and the modulated symbols are demapped. The obtained log-likelihood ratio (LLR) values, also called soft bits, are fed to a forward error correction (FEC) decoder for channel decoding. Depending on the type of channel decoder, the LLR values need to be interleaved to spread error bursts across a frame of data. Broadcast receivers typically use convolutional interleavers to keep the receiver input-to-output latency at a minimum. The decoded bits are then post-processed, for example by an energy dispersal sequence, and provided to a payload processor and a sink.

#### **Baseband Data-Flow**

Although feedback is typically employed for synchronization and equalization control loops, the data flow inside the receiver is mostly feed-forward-oriented. The data rate of the sequentially processed information stream is typically decreasing from the baseband input to the decoder output, i.e. the data rate of the complex baseband stream is the highest and the data rate of the output payload bitstream the lowest in the chain. Due to the DFT operation, data needs to be processed block-wise, which inherently leads to a latency in decoding. Additionally, the DFT block-size may be increasing or decreasing at integer rates due to transmission framing. In case of broadcasting receivers, interleaver frames or large FEC frames typically determine the latency of the system. The listed data-flow properties are important for the analysis in Chapter 3 and Chapter 4.

Subsequently, the scope and structure of this work will be outlined by a description of the research focus covered in the following chapters.

# 1.3 Scope of this Work

The research outlined in this work focuses on analyzing the benefits, limitations and possibilities of temporal hardware resource multiplexing for digital receiver chain implementations using dynamic partial reconfiguration of FPGAs. Contributions of this thesis and references to related works cover:

- Design aspects and benefits of reconfigurable hardware for self-adapting broadcast receivers.

- Impacts of cyclic partial reconfiguration for block-wise execution of radio receiver components by time-multiplexing of FPGA resources.

- Receiver chain partitioning for cyclic partial reconfiguration.

Since the scope of this work affects interdisciplinary subjects, the elaborated results comprises contributions in the fields of signal processing and digital circuit design for real-time systems.

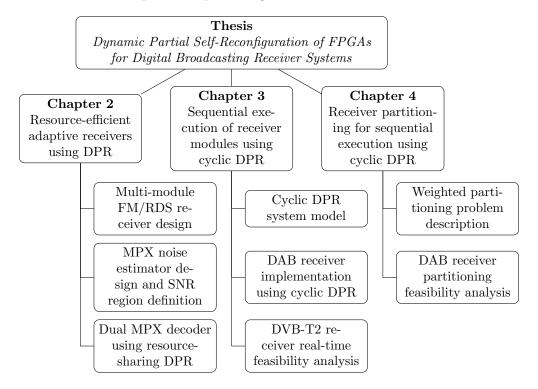

#### 1.4 Structure of this Work

In each of the following chapters one individual aspect of temporal FPGA resource multiplexing for digital signal processing chains will be discussed. Figure 1.7 shows the structure of this thesis in a hierarchical diagram together with the major units of observation. The first chapter is mostly self-contained, which means that despite minor referencing it is possible to follow the analysis of the second and third chapter without reading the first chapter. The description of related works, related contributions and bibliography are explained individually in each chapter. An overview of the structure and content of the subsequent chapters is given further on.

Figure 1.7: Structure of this thesis and major units of observation.

- Chapter 2: The design of a dynamically self-adapting FM/RDS radio receiver using DPR of a Xilinx Virtex-5 FPGA will be presented, where partial reconfiguration of the receiver is triggered using a signal-to-noise ratio (SNR) metric. In order to gain insight into the hardware complexity and system functionality, the receiver implementation, the hardware setup and the resource requirements will be outlined in detail. In addition, a method for receiver partitioning will be presented and a novel FM signal quality estimator will be proposed. Switching criteria for the reconfiguration of the dynamic partition will be derived from a receiver noise disturbance model and the tool-flow of the dynamically self-adapting system will be presented. Finally, a feasibility analysis for a multi-island resource-sharing reconfigurable system using vendor tools will be presented and the possibilities and limitations of the resource-sharing approach will be discussed.

- Chapter 3: The implications of cyclic reconfiguration for the sequential execution of signal processing chain elements will be presented in the third chapter.

Starting from a system model for cyclic reconfiguration, the requirements for a frame-wise execution of data will be derived. After presenting the buffering and latency implications on the processing chain, two feasibility studies for two digital broadcast receiver systems will be presented. Resource estimates for a low-cost Xilinx Spartan-6 FPGA will then be used to quantify the potential FPGA resource savings and the effect of buffering latency for real-world receivers.

- Chapter 4: An efficient method for processing chain partitioning of FPGA hardware designs using cyclic DPR will be elaborated. The partitioning problem will be formulated after the presentation of related works and an approach to solve the partitioning problem will be introduced. Using a weighted resource and latency metric, an approach for selecting suitable partitioning candidates will be derived and a novel approximation algorithm with linear time complexity will be presented. The chapter is concluded by a case study for the partitioning of a real-world DAB decoder chain.

- Chapter 5: A summary of the contributions and findings of this thesis will be presented in the last chapter, followed by an elaboration of potential future works.

# 2 FPGA Self-Reconfiguration for Adaptive Radio Receivers

The terrestrial broadcast transmission channel imposes impairments on the transmission signal leading to a signal degradation at the receiver. Since the signal reception quality influences the amount of information that can be recovered without error at the receiver, working groups usually define minimum receiver requirements by means of an impairment model. Thus, in conjunction with the specification of new radio standards, channel models, simulation parameters and receiver performance values are defined to ensure that a specified minimum performance can be achieved across all receiver implementations. Compared to implementations targeting a reception performance close to the theoretical optimum, minimum receiver requirements contain margins, leaving the developer with headroom for complexity of the employed decoding algorithms. Exploiting this headroom allows to use more or less complex algorithms and implementations. Adaptively switching between these more or less complex implementations using an FPGA is possible by dynamic partial reconfiguration. The analysis of reconfigurable architectures and the derivation of reconfiguration constraints for adaptive FPGA-based receiver systems is the research focus of this chapter.

Given an SNR-based reception quality metric, an adaptive FM receiver implementation using DPR will be presented. For this purpose, a novel SNR estimation routine will be derived and a set of meaningful SNR threshold values will be introduced. In addition to single-island and multi-island DPR solutions, a feasibility analysis for sharing FPGA resources of a single DPR partition between two DPR modules will be presented, where dynamic partial reconfiguration has been accomplished on a Xilinx Virtex-5 FPGA and the DPR system has been implemented using the vendor tool-flow as recommended by Xilinx.

The evaluation and design of adaptive signal processing chains is a wide research topic with many scientific contributions. Explaining the scope and categorizing the contributions of others is essential to put the matters of this work into context. Therefore, related works will be subsequently outlined together with a presentation of the achievements described in this work.

#### 2.1 Related-Work and Contribution

Dynamic partial reconfiguration of FPGAs is used for various applications in reconfigurable computing, audio and video processing as well as in software-defined radio (SDR) systems. Works related to adaptive receiver chains and cognitive SDR systems are related to the analysis presented in this chapter and of particular importance in the following depiction of adaptive FPGA-based receivers.

In [DGRB04], Roland et al. dynamically reconfigure a phase-shift keying (PSK) filter

on a Virtex 1000E FPGA for a cellular communication system using a modular design approach. The presented system is not self-adapting and an external DSP is controlling the reconfiguration process. Similarly, Delahaye et al. presented a partially reconfigurable software-defined radio system in [DPML07], where the exchange of a constellation mapper, convolutional coder and finite impulse response (FIR) filter using DPR is described. An SNR-driven reconfiguration system for WiMAX systems on a Xilinx Virtex-4 SX35 FPGA has been developed by Chitty et al. in [CKPLM10]. In his work, he describes a link-adaption algorithm using an SNR estimation stage and SNR threshold values as reconfiguration trigger, which is similar to the work presented in this chapter. The system is designed using the Xilinx modular design flow with a fixed DPR partition, and, in comparison to the approaches presented in this work, Chitty does not use the ICAP for internal reconfiguration but uses an external computer to trigger a reconfiguration by writing the partial bitstream to the SelectMAP interface.

Lotse et al. have investigated in bit error rate (BER)-adaptive reconfiguration of modulation schemes and dynamically adapted the constraint length of a convolutional code given a certain channel scenario (cf. [LFDN09]). The authors used a Virtex-II Pro and operated the BER decision engine on the Power PC core, which is also used to trigger the reconfiguration. To save power, the authors propose to clear the DPR region if no receive signal is present. In contrast to the subsequently presented approaches, the signal quality detection engine is operating in a fixed-size reconfigurable partition. Furthermore, the system in [LFDN09] requires a feedback path to the transmitter for link-adaption. In [MMT<sup>+</sup>08], Manet et al. describe the benefits and drawbacks of dynamic partial reconfiguration for signal processing applications. He describes the problem of partition fragmentation, i.e. when the DPR partition size can not be changed during runtime, by "wasted" resources. The described problem affects all previous works.

In this work, a hierarchical reconfiguration approach is described to overcome partition fragmentation and share resources between otherwise fixed DPR partitions. Design approaches based on new third-party tools that show the feasibility of hierarchically reconfigurable systems have been presented in [KB14]. In the subsequent sections, practical use-cases for the application of these new tools will be illustrated by means of a self-adapting FM receiver system. Serving as a basis of the outlined work, the concept of a resource-sharing SNR-adaptive receiver was first discussed in [MF10]. Two years later, a similar reconfigurable FM receiver prototype was presented in [KTB+12]. In addition to the published material, the major contribution of the work described in this chapter is the comprehensible description of the processing chain complexity, modularization possibilities and reconfiguration approaches to realize an SNR-adaptive system with vendor tools. The results highlight the limits and possibilities of reconfigurable receiver systems and provide insights into the practical feasibility of reconfigurable FPGA-based receiver systems in addition to the theory.

Given the outlined state-of-the art, the major contributions of this work are:

- The design of an FPGA-based SNR-adaptive FM receiver system using multiple DPR partitions.

- The evaluation of hierarchical partial reconfiguration for FPGA resource-sharing between two adaptive receivers.

- The design of a novel SNR estimation method based on estimating the noise power

in the band-gaps of the demodulated FM signal.

• A comprehensive description of the FM receiver implementation and complexity analysis in context of dynamic partial reconfiguration.

Understanding the following sections requires an introduction to FM sound broadcasting at VHF band II to be provided further on. In addition, hardware implementations of FM receiver components and the design of a self-adapting FM receiver system using multiple DPR partitions will be described.

# 2.2 FM Sound Broadcasting

Frequency modulation is a wide-spread analog modulation scheme used for audio and voice communications. In order to understand the derivations in the subsequent sections, a brief introduction to the baseband representation of an FM signal will be outlined. The notation follows that of Werner in [WM06] and Kammeyer in [Kam08]. In the further course of this section, the FM multiplex (MPX) signal structure will be presented and the implications of noise disturbances in FM broadcasting will be explained.

Given is the complex-valued angular-modulated baseband signal  $\underline{x}_{\text{FM}}(t)$  with constant amplitude  $A_{\text{FM}}$  and time-variant phase  $\phi(t)$  as follows

$$x_{\rm FM}(t) = A_{\rm FM} \cdot e^{j\phi(t)},\tag{2.1}$$

where underlining indicates complex baseband notation and j denotes the imaginary unit with the property  $j^2 = -1$ . The carrier power of the constant-envelope signal in Equation 2.1 at a resistive load of 1 Ohm is equal to  $A_{\text{FM}}^2$ . The signal  $\underline{x}_{\text{FM}}(t)$  has a time-variant angular frequency  $\omega(t)$  and the instantaneous angular frequency at a time instant t is equal to the first derivative of the phase function  $\phi(t)$ , i.e.

$$\omega(t) = \frac{d\phi(t)}{dt}. (2.2)$$

Equation 2.2 states that the information carried in  $\omega(t)$  is represented by the changes of the angular frequency over time, and this implies that the maximum frequency deviation of the baseband signal  $\underline{x}_{\text{FM}}(t)$  is determined by the peak values of  $\omega(t)$ . Therefore, the peak frequency deviation of  $\underline{x}_{\text{FM}}(t)$  can be expressed by

$$\Delta f_{\text{MAX}} = \frac{1}{2\pi} \max(|\omega(t)|),$$

where  $|\cdot|$  means taking the absolute value. Relating to a complex baseband representation of the FM signal, the peak frequency deviation reflects the maximum deviation of the instantaneous frequency from 0 Hz. Let the information carried in  $\omega(t)$  be represented by a continuous real-valued signal  $x_{\rm LF}(t)$ , e.g.  $x_{\rm LF}(t)$  could be an audio signal. According to the definition of frequency modulation, the instantaneous angular frequency  $\omega(t)$  is a linear function of  $x_{\rm LF}(t)$ , i.e.

$$\omega(t) = K_{\text{FM}} \cdot x_{\text{LF}}(t), \tag{2.3}$$

Figure 2.1: Double-sided power spectral density of FM baseband signal.

where  $K_{\rm FM}$  denotes the modulation coefficient. Given a source-signal peak-to-peak constraint of  $-1 \le x_{\rm LF}(t) \le 1$ , a modulation coefficient of  $K_{\rm FM} = 2\pi \Delta f_{\rm MAX}$  and the formulation in Equation 2.2, Equation 2.3 can be rewritten to

$$\frac{d\phi(t)}{dt} = 2\pi \Delta f_{\text{MAX}} \cdot x_{\text{LF}}(t). \tag{2.4}$$

Finally, Equation 2.4 can be reformulated by applying the second fundamental theorem of calculus to obtain the a signal model for frequency-modulated signals as

$$\phi(t) = 2\pi \Delta f_{\text{MAX}} \int_{0}^{t} x_{\text{LF}}(\tau) d\tau + \phi_{0},$$

where  $\phi_0$  describes a the phase offset at t=0. Figure 2.1 depicts the power spectral density (PSD) of a modulated FM audio baseband signal  $\Phi_{\rm FM}(f)$  showing an approximately triangular-shaped spectrum, which is characteristical for frequency-modulated signals. The PSD was calculated using a received on-air audio program of 1 second duration.

In the early days of FM sound broadcasting, a monophonic low-frequency signal  $x_{\rm LF}(t)$  has been used, either taken from a single channel audio source or from the sum of a stereo audio program. For stereo broadcasts, the LF signal has been modified while preserving backward-compatibility with older monaural receivers. According to the International Telecommunication Union (ITU) in ITU-R BS.450-3 [Itu01b], this is achieved by using the pilot-tone-based stereophonic multiplex signal, commonly referred to as MPX signal. Decoding the FM signal resembles the real-valued MPX signal. The windowed one-sided PSD of an audio broadcast is plotted in Figure 2.2.

As stated by the ITU in [Itu01a], in most countries the MPX signal consists of 4 components, where the continuous time-domain signals of the left and right MPX audio channels are denoted by L(t) and R(t), respectively:

• The sum audio channel  $S(t) = \frac{1}{2}(L(t) + R(t))$ , starting at around 15 Hz with a bandwidth of 15 kHz. Before MPX insertion, a pre-emphasis filter of first order with a time constant of 75  $\mu$ s or 50  $\mu$ s is applied to S(t).

Figure 2.2: Windowed one-sided power spectral density of FM multiplex signal.

- The sinusoidal pilot tone at a frequency of  $19\,\mathrm{kHz}$ , contributing at maximum  $8\,\%$  to  $10\,\%$  to the peak frequency deviation.

- The difference audio signal  $D(t) = \frac{1}{2}(L(t) R(t))$ , located at 38 kHz with a one-sided bandwidth of 15 kHz. The difference signal is generated using amplitude modulation with suppressed carrier. Before MPX insertion, a pre-emphasis with a time constant of 75  $\mu$ s or 50  $\mu$ s is applied to D(t).

- The RDS signal is represented by a continuous stream of differentially-encoded binary phase-shift keying (DEBPSK) symbols centered around 57 kHz in the FM multiplex. Manchester coding is used for DC free transmission to avoid potential cross-talk in existing stereo decoder PLLs [KM99]. The encoded bits are shaped with a square root-raised cosine pulse with a roll-off factor of  $\beta_{SRRC} = 1$ . With a gross data rate of 1187.5 bit/s, the Manchester-coded RDS signal has a one-sided bandwidth of 2.375 kHz and hence a two-sided bandwidth of roughly 4.8 kHz.

From the audio sum and difference signals, the left and right audio channels can be recovered by:

$$L(t) = S(t) + D(t) = \frac{1}{2} \cdot [(L(t) + R(t)) + (L(t) - R(t))]$$

$$R(t) = S(t) - D(t) = \frac{1}{2} \cdot [(L(t) + R(t)) - (L(t) - R(t))].$$

(2.5)

For a perfect audio channel separation based on Equation 2.5, a coherent demodulation of the difference signal is mandatory. Since the difference signal is in-phase with the 19 kHz pilot tone, coherent demodulation can be achieved by using a phase-locked oscillator running at 38 kHz. The RDS signal can be demodulated similarly, although an RDS carrier frequency estimation can also be performed by an independent carrier recovery loop.

In the next section, an SNR-adaptive receiver chain will be presented for an FM/RDS broadcast receiver chain.

#### 2.3 A modularized FPGA-based FM Receiver

The design of a digital FM receiver is similar to the design of its analog counterpart. However, in terms of linearity, the digital receiver has advantages over an analog design, which in case of an FM broadcast receiver results in a better stereo separation and RDS demodulation. Since the complexity of the decoding algorithms of a digital receiver determines the FPGA resources needed for the actual implementation, the algorithms and implementation-specific considerations will be introduced. Depicting the implementation also helps understanding the design approaches outlined in the following sections focusing on partial reconfiguration.

#### 2.3.1 Receiver Modules

The receiver has been designed with the goal in mind to obtain a modular hardware implementation for an SNR-adaptive operation in the FPGA. Therefore, the receiver chain has been sub-partitioned into four major processing blocks:

- 1. **FM demodulator:** The FM demodulator provides an estimate of the instantaneous frequency of the input signal. After FM demodulation, the FM multiplex signal is obtained, which contains the audio sum signal, the audio difference signal, a 19 kHz pilot carrier and the differentially-encoded BPSK data signal at 57 kHz.

- 2. Monaural sum signal audio decoder: The decoder extracts the monaural signal, which contains the sum of the left and right audio channels. It contains a combined decimation and low-pass stage to limit the LF audio signal to a frequency of 15 kHz.